(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7030825号

(P7030825)

(45)発行日 令和4年3月7日(2022.3.7)

(24)登録日 令和4年2月25日(2022.2.25)

(51)国際特許分類

|         |                  |         |       |         |

|---------|------------------|---------|-------|---------|

| B 8 1 B | 7/02 (2006.01)   | B 8 1 B | 7/02  |         |

| H 0 1 L | 25/065 (2006.01) | H 0 1 L | 25/08 | B       |

| H 0 1 L | 25/07 (2006.01)  | H 0 1 L | 21/60 | 3 1 1 Q |

| H 0 1 L | 25/18 (2006.01)  | B 8 1 C | 3/00  |         |

| H 0 1 L | 21/60 (2006.01)  | H 0 1 L | 21/88 | T       |

請求項の数 28 (全35頁) 最終頁に続く

(21)出願番号 特願2019-543246(P2019-543246)

(86)(22)出願日 平成29年12月20日(2017.12.20)

(65)公表番号 特表2020-509942(P2020-509942

A)

(43)公表日 令和2年4月2日(2020.4.2)

(86)国際出願番号 PCT/US2017/067742

(87)国際公開番号 WO2018/147940

(87)国際公開日 平成30年8月16日(2018.8.16)

審査請求日 令和2年10月28日(2020.10.28)

(31)優先権主張番号 62/457,116

(32)優先日 平成29年2月9日(2017.2.9)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/458,441

(32)優先日 平成29年2月13日(2017.2.13)

最終頁に続く

(73)特許権者 518065991

インヴェンサス ボンディング テクノロジーズ インコーポレイテッド

アメリカ合衆国 カリフォルニア州 95134 サンノゼ オーチャード パーク

ウェイ 3025

(74)代理人 100094569

弁理士 田中 伸一郎

(74)代理人 100103610

弁理士 吉田 和彦

(74)代理人 100109070

弁理士 須田 洋之

(74)代理人 100095898

弁理士 松下 満

(74)代理人 100098475

最終頁に続く

(54)【発明の名称】 接合構造物

## (57)【特許請求の範囲】

## 【請求項1】

接合構造物であって、

第1の導電性特徴部及び第1の非導電性特徴部を含む第1の界面特徴部を有する第1の素子と、

第2の導電性特徴部及び第2の非導電性特徴部を含む第2の界面特徴部を有する第2の素子であって、前記第1の界面特徴部の前記第1の導電性特徴部が介在する接着剤を用いずに前記第2の界面特徴部の前記第2の導電性特徴部に直接接合されると共に、前記第1の界面特徴部の前記第1の非導電性特徴部が介在する接着剤を用いずに前記第2の界面特徴部の前記第2の非導電性特徴部に直接接合されて、界面構造体を画定する、前記第2の素子と、

前記第2の素子の中又は上に配設された導電トレースと、

前記第1の素子の上面にあり、前記導電トレースと電気通信するボンドパッドと、

前記第1の素子又は前記第2の素子に結合された、若しくは前記第1の素子又は前記第2の素子と共に形成された集積デバイスと、

を備え、

前記第1の導電性特徴部と前記第2の導電性特徴部との間の接合界面が前記接合構造物の内部領域を実質的に包囲する、接合構造物。

## 【請求項2】

前記第1の素子と前記第2の素子との間に空洞を更に備える、請求項1に記載の接合構造

物。

**【請求項 3】**

前記接合構造物内に空洞が配設されない、請求項 1 に記載の接合構造物。

**【請求項 4】**

前記第 1 の導電性特徴部と前記第 2 の導電性特徴部との間の接合界面は、事実上の閉鎖プロファイルを画定し、前記第 1 及び第 2 の素子を接続し、前記事実上の閉鎖プロファイルは、外部環境から前記接合構造物の前記内部領域へと拡散する気体から、前記内部領域を実質的に封止する、請求項 1 に記載の接合構造物。

**【請求項 5】**

前記導電トレースから前記界面構造体を通って延び、前記ボンドパッドに接続する電気的相互接続部を更に備える、請求項 1 に記載の接合構造物。

10

**【請求項 6】**

前記第 1 及び第 2 の非導電性特徴部の一方又は両方は酸化ケイ素を含む、請求項 1 に記載の接合構造物。

**【請求項 7】**

前記第 1 の素子の上面に配設された複数のボンドパッドを更に備える、請求項 1 に記載の接合構造物。

**【請求項 8】**

前記集積デバイスは前記導電トレースに電気的に接続される、請求項 1 に記載の接合構造物。

20

**【請求項 9】**

前記ボンドパッドは前記接合構造物の最上面に対して凹んでいる、請求項 1 に記載の接合構造物。

**【請求項 10】**

前記第 2 の素子の側域が前記第 1 の素子の側域よりも大きい、請求項 1 に記載の接合構造物。

**【請求項 11】**

前記第 1 の導電性特徴部は複数の導電セグメントを含む、請求項 1 に記載の接合構造物。

**【請求項 12】**

前記複数の導電セグメントは一連の導電性ドットを含む、請求項 1\_1 に記載の接合構造物。

30

**【請求項 13】**

前記集積デバイスは前記空洞内に配設される、請求項 2 に記載の接合構造物。

**【請求項 14】**

前記第 1 の導電性特徴部と前記第 2 の導電性特徴部との間の前記接合界面は、不完全な環状パターンを含む、請求項 4 に記載の接合構造物。

**【請求項 15】**

前記電気的相互接続部は前記第 1 の素子を通って延びる、請求項 5 に記載の接合構造物。

**【請求項 16】**

前記電気的相互接続部は前記第 2 の素子の少なくとも一部を通って延びる、請求項 5 に記載の接合構造物。

40

**【請求項 17】**

前記第 1 の界面特徴部は、前記第 1 の素子の上面に対向する前記第 1 の素子の下面に配設される、請求項 1\_5 に記載の接合構造物。

**【請求項 18】**

接合構造物であって、

第 1 の導電性特徴部及び第 1 の非導電性特徴部を含む第 1 の界面特徴部を有する第 1 の素子と、

第 2 の導電性特徴部及び第 2 の非導電性特徴部を含む第 2 の界面特徴部を有する第 2 の素子であって、前記第 1 の界面特徴部の前記第 1 の導電性特徴部が介在する接着剤を用いずに前記第 2 の界面特徴部の前記第 2 の導電性特徴部に直接接合されると共に、前記第 1 の

50

界面特徴部の前記第1の非導電性特徴部が介在する接着剤を用いずに前記第2の界面特徴部の前記第2の非導電性特徴部に直接接合されて、界面構造体を画定する、前記第2の素子と、

前記第1の素子の上面にあるボンドパッドと、

前記第1の素子又は前記第2の素子に結合された、若しくは前記第1の素子又は前記第2の素子と共に形成された集積デバイスと、

前記ボンドパッドから前記第1の素子を通って延び、前記集積デバイスに電気的に接続する電気的相互接続部と、

を備え、

前記第1の導電性特徴部と前記第2の導電性特徴部との間の接合界面が前記接合構造物の内部領域を実質的に包囲する、接合構造物。 10

【請求項19】

前記電気的相互接続部は前記界面構造体を通って延びる、請求項18に記載の接合構造物。

【請求項20】

前記第2の素子の中又は上に導電トレースを更に備え、前記導電トレースは、前記集積デバイスと前記電気的相互接続部との間に電気通信を提供する、請求項18に記載の接合構造物。

【請求項21】

前記第1の素子と前記第2の素子との間に空洞を更に備える、請求項18に記載の接合構造物。 20

【請求項22】

前記界面構造体は前記集積デバイスの周囲に配設されて事実上の閉鎖プロファイルを画定し、前記第1及び第2の素子を接続し、前記事実上の閉鎖プロファイルは、外部環境から前記接合構造物の内部領域へと拡散する気体から、前記内部領域を実質的に封止する、請求項18に記載の接合構造物。

【請求項23】

前記電気的相互接続部は前記第2の素子の一部を通って延びる、請求項19に記載の接合構造物。

【請求項24】

接合構造物を形成する方法であって、

第1の導電性特徴部及び第1の非導電性特徴部を含む第1の界面特徴部を有する第1の素子、及び、第2の導電性特徴部及び第2の非導電性特徴部を含む第2の界面特徴部を有する第2の素子を提供することと、 30

前記第1の界面特徴部の前記第1の導電性特徴部と前記第2の界面特徴部の前記第2の導電性特徴部とを、介在する接着剤を用いずに直接接合することと、

前記第1の界面特徴部の前記第1の非導電性特徴部と前記第2の界面特徴部の前記第2の非導電性特徴部とを、介在する接着剤を用いずに直接接合することと、

を含み、

導電トレースが前記第2の素子の中又は上に配設され、

ボンドパッドが、前記第1の素子の上面に配設され、前記導電トレースと電気通信し、集積デバイスが、前記第1の素子又は前記第2の素子に結合される、若しくは前記第1の素子又は前記第2の素子と共に形成され、前記第1の導電性特徴部と前記第2の導電性特徴部との間の接合界面が、前記接合構造物の内部領域を実質的に包囲する、方法。 40

【請求項25】

前記ボンドパッドから前記第1の素子を通って延び、前記導電トレースに電気的に接続する電気的相互接続部を提供することを更に含む、請求項24に記載の方法。

【請求項26】

前記第1の界面特徴部は前記第1の素子の上面に配設され、前記ボンドパッドは事実上の閉鎖プロファイルの外側に配設される、請求項24に記載の方法。

【請求項27】

10

20

30

40

50

前記第1の導電性特徴部と前記第2の導電性特徴部とを接合すること及び前記第1の非導電性特徴部と前記第2の非導電性特徴部とを接合することの前に前記電気的相互接続部を提供することを更に含む、請求項25に記載の方法。

【請求項28】

前記第1の導電性特徴部と前記第2の導電性特徴部とを接合すること及び前記第1の非導電性特徴部と前記第2の非導電性特徴部とを接合することの後に前記電気的相互接続部を提供することを更に含む、請求項25に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

この分野は、概して接合構造物に関するものであり、具体的には、低減された横方向フットプリントを有する接合構造物に関する。

【0002】

(関連出願の相互参照)

本出願は、2017年2月9日出願の米国特許仮出願第62/457,116号、名称「BONDED STRUCTURE」、及び2017年2月13日出願の米国特許仮出願第62/458,441号に対する優先権を主張するものであり、その開示全体が参照により本明細書に組み込まれる。

【背景技術】

【0003】

20

半導体デバイスの製造及びパッケージングでは、例えば、汚染を低減する、又は集積デバイスに対する損傷を防止するために、一部の集積デバイスが外部環境から封止される。例えば、一部の微小電気機械システム(MEMS)デバイスは、はんだなど接着剤で基板に取り付けられたキャップによって画定される空洞を含む。

【発明の概要】

【発明が解決しようとする課題】

【0004】

30

しかしながら、一部の接着剤は気体に対して透過性であり得、その結果、気体は経時に接着剤を通過して空洞内に入り得る。水分又は水素若しくは酸素ガスなど一部の気体は、敏感な集積デバイスを損傷させ得る。はんだなど他の接着剤は、それら自体の長期信頼性問題をもたらす。したがって、集積デバイスのための改善された封止に対する継続的なニーズが依然として存在する。

【0005】

更に、デバイスが外部環境から封止されているかどうかにかかわらず、又はデバイスが空洞を含むかどうかにかかわらず、様々な種類の接合構造物では、外部デバイス、基板、又は他の素子に接続するためのボンドパッドは、パッケージ内又はデバイス上の貴重な空間又は領域を占有し得る。したがって、パッケージ又はデバイスの横方向フットプリントが低減される接合構造物を提供することが望ましい場合がある。

【図面の簡単な説明】

【0006】

40

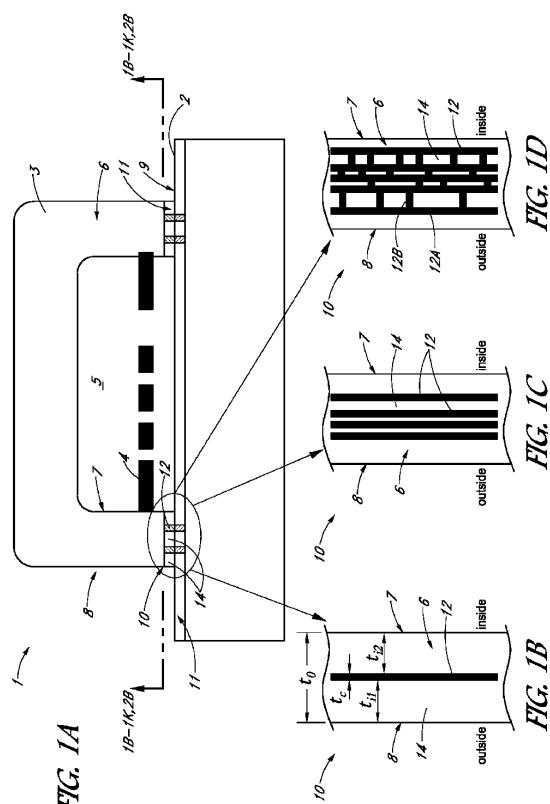

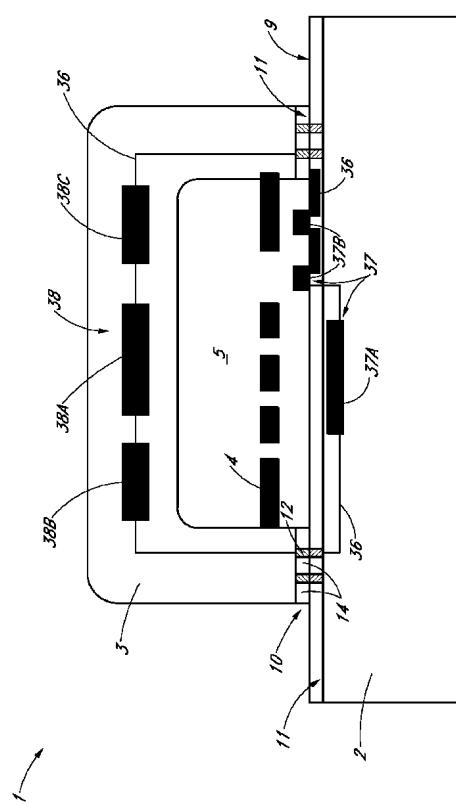

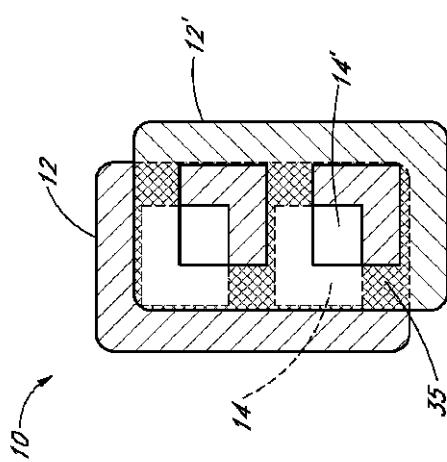

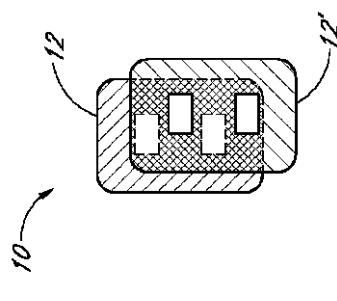

【図1A】様々な実施形態による、接合構造物の概略側断面図である。

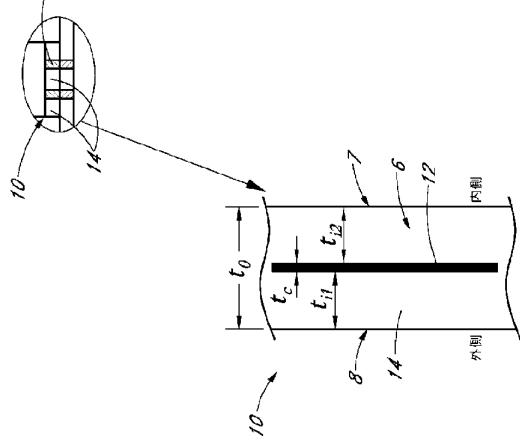

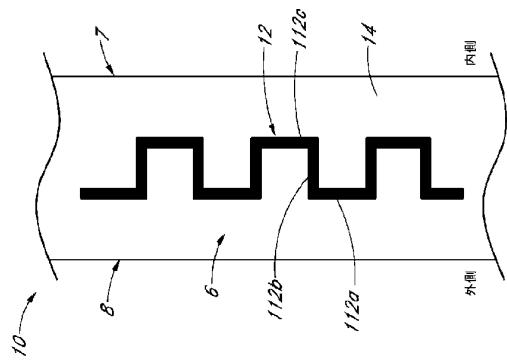

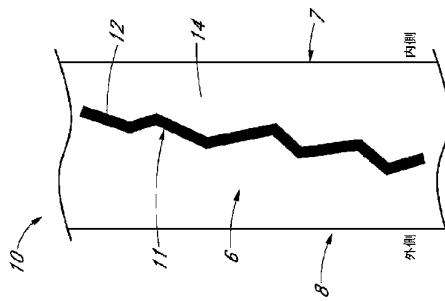

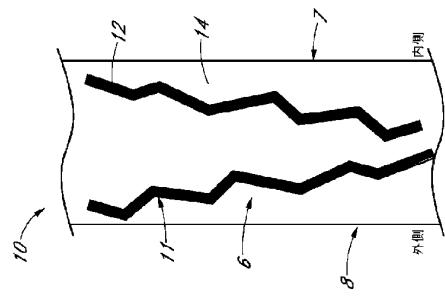

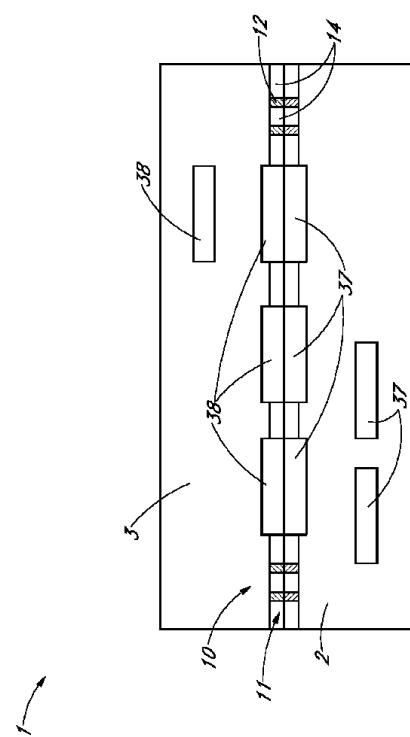

【図1B】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

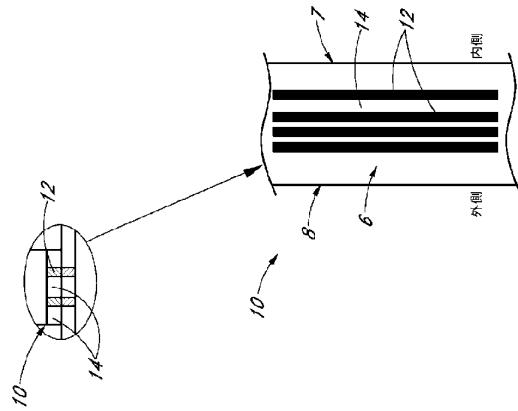

【図1C】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

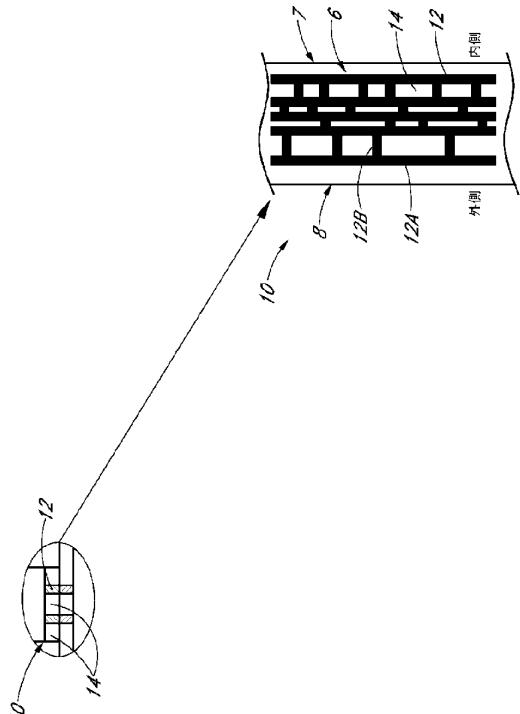

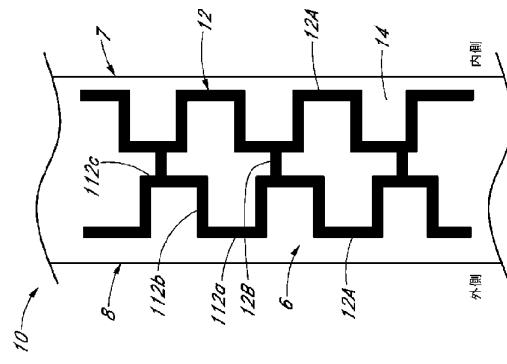

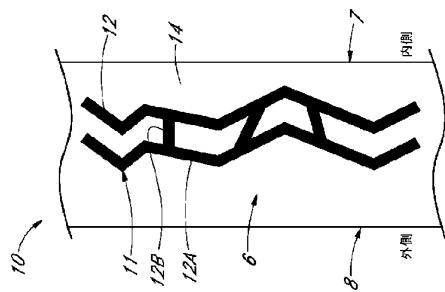

【図1D】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

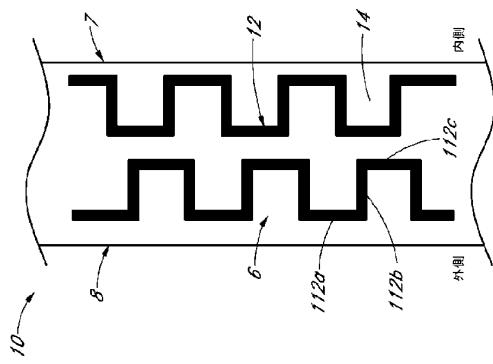

【図1E】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

【図1F】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分

50

概略断面平面図である。

【図 1 G】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

【図 1 H】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

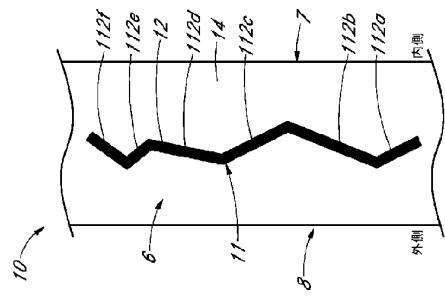

【図 1 I】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

【図 1 J】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

【図 1 K】接合構造物の接合界面に沿って画定された界面構造体の様々な実施形態の部分概略断面平面図である。

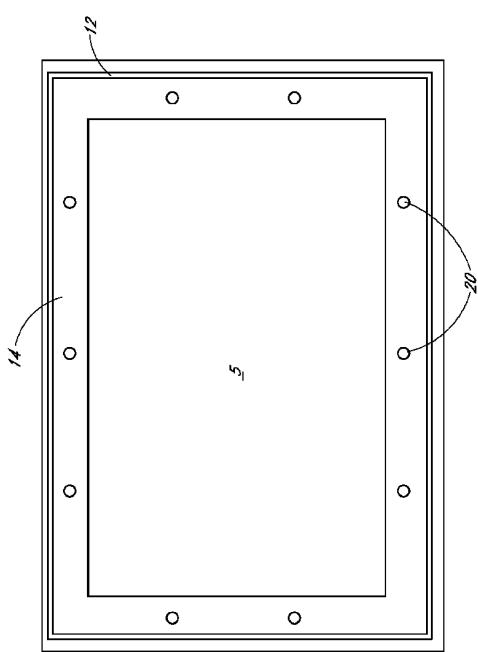

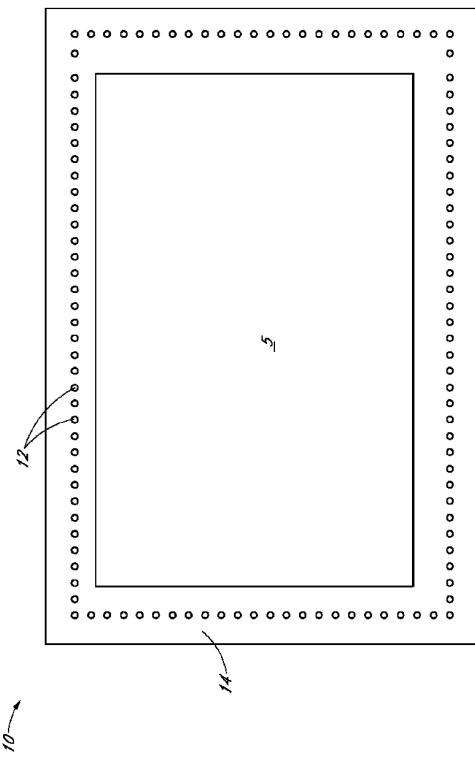

【図 2 A】図 1 A ~ 図 1 B に示す接合構造物の界面構造体の概略断面平面図である。

【図 2 B】接合界面を通って延在する、1つ以上の電気的相互接続部を有する、界面構造体の概略断面平面図である。

【図 2 C】図 1 C の界面構造体の概略断面平面図である。

【図 2 D】空洞の周囲に配設された複数の導電性界面特徴部を有して、事実上の環状プロファイルを画定する界面構造体の概略断面平面図であり、各導電性界面特徴部は、ほぼ環状のプロファイルを備える。

【図 2 E】空洞の周囲に配設された複数の導電性界面特徴部を有して、事実上の環状プロファイルを画定する界面構造体の概略断面平面図であり、複数の導電性特徴部は、間隙によって離隔された複数のセグメントを備える。

【図 2 F】いくつかの実施形態による、接合構造物の概略側断面図である。

【図 2 G】様々な実施形態による、接合構造物の概略側断面図である。

【図 2 H】平面図から見たときの一連の導電性ドット又は他の不連続形状を含む導電性界面特徴部を備える、界面構造体の概略平面図である。

【図 2 I】平面図から見たときの一連の導電性ドット又は他の不連続形状を含む導電性界面特徴部を備える、界面構造体の概略平面図である。

【図 2 J】第 1 の素子と第 2 の素子との間の接合界面の外側に位置付けられた 1 つ以上のボンドパッドを有する接合構造物の概略側断面図である。

【図 2 K】図 2 J に示す接合構造物の平面図である。

【図 2 L】様々な実施形態による、接合構造物の上面に配設された 1 つ以上のボンドパッドを有する接合構造物の概略側断面図である。

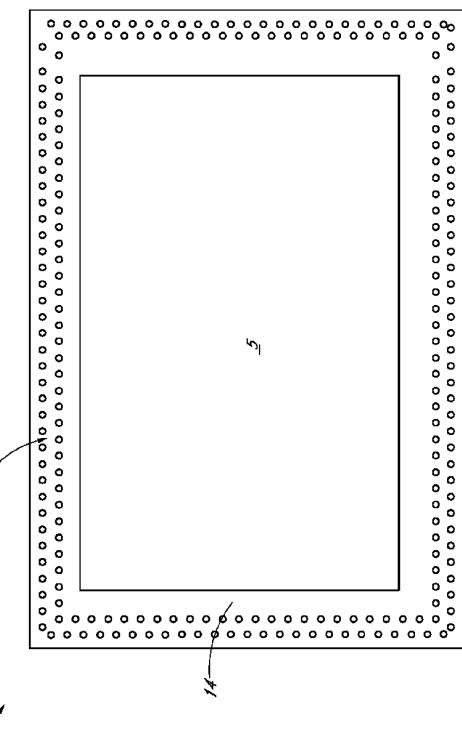

【図 2 M】図 2 L に示す接合構造物の平面図である。

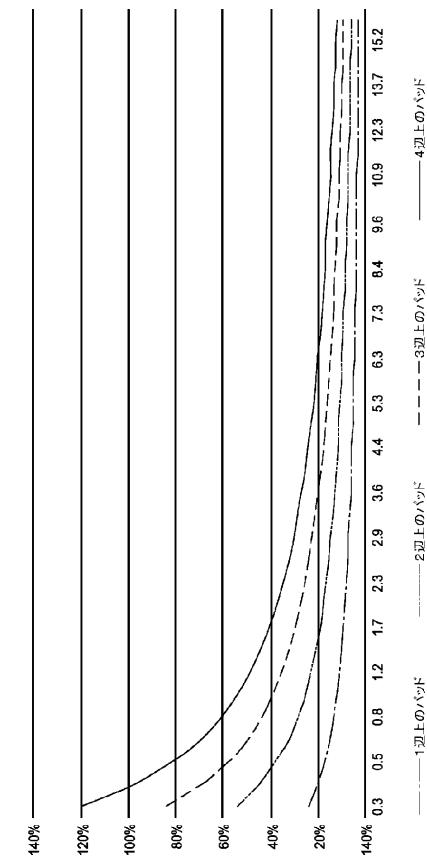

【図 2 N】ボンドパッドのレッジが接合構造物又はダイの 1 辺、2 辺、3 辺、又は 4 辺で除去された接合構造物の、ダイ面積に対するウエハ当たりの接合構造物又はダイの数の増加率をプロットするチャートである。

【図 2 O】別の実施形態による、接合構造物の概略側断面図である。

【図 3】界面構造体の導電性界面特徴部と接続されたクラック止めを含む接合構造物の一部の概略側断面図である。

【図 4 A】対応する界面特徴部が互いに接合されるときの位置ずれに対する許容度を増加させる接合構造物の概略平面図である。

【図 4 B】対応する界面特徴部が互いに接合されるときの位置ずれに対する許容度を増加させる接合構造物の概略平面図である。

【図 4 C】対応する界面特徴部が互いに接合されるときの位置ずれに対する許容度を増加させる接合構造物の概略平面図である。

【図 5 A】各半導体素子上の対応する界面特徴部が互いに接合されるときの位置ずれに対する許容度を増加させる、界面構造体の概略平面図である。

【図 5 B】各半導体素子上の対応する界面特徴部が互いに接合されるときの位置ずれに対する許容度を増加させる、界面構造体の概略平面図である。

【図 5 C】各半導体素子上の対応する界面特徴部が互いに接合されるときの位置ずれに対

10

20

30

40

50

する許容度を増加させる、界面構造体の概略平面図である。

【図 5 D】各半導体素子上の対応する界面特徴部が互いに接合されるときの位置ずれに対する許容度を増加させる、界面構造体の概略平面図である。

【図 6 A】別の実施形態による、各半導体素子上の対応する界面特徴部が互いに接合されるときの位置ずれに対する許容度を増加させる界面構造体の概略平面図である。

【図 6 B】別の実施形態による、各半導体素子上の対応する界面特徴部が互いに接合されるときの位置ずれに対する許容度を増加させる界面構造体の概略平面図である。

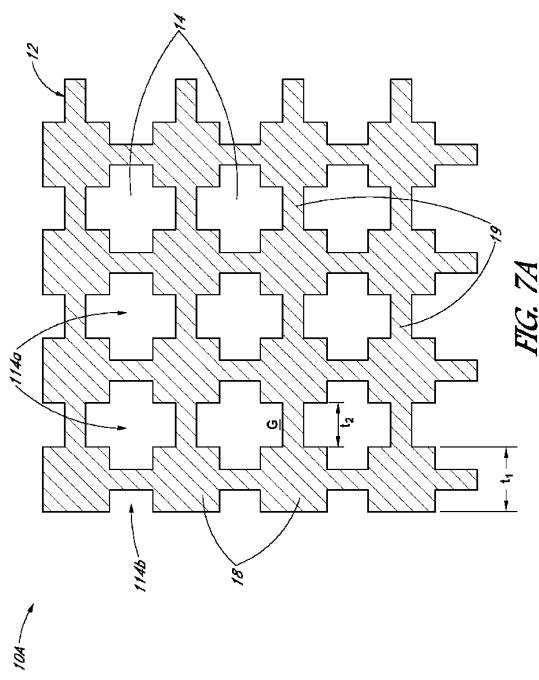

【図 7 A】非導電性界面特徴部の複数の内側領域が、交差する導電性界面特徴部によって画定される横方向格子構造体内に配設される、導電性界面特徴部の概略平面図である。

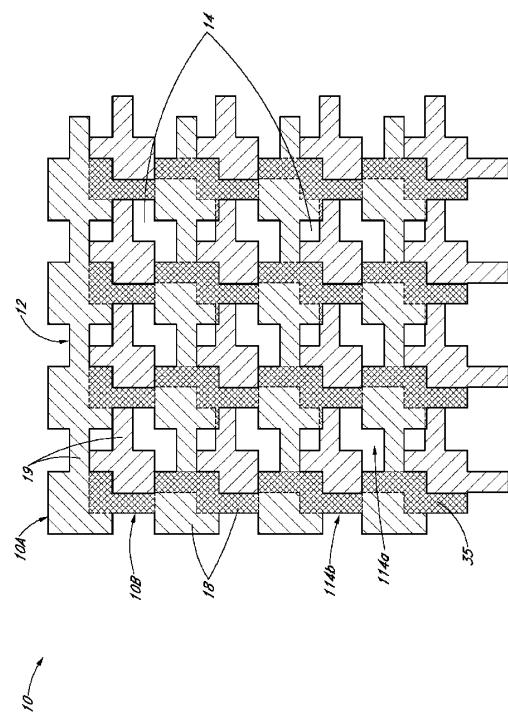

【図 7 B】2つの界面特徴部を接合することによって形成された接合界面構造体の概略平面図である。

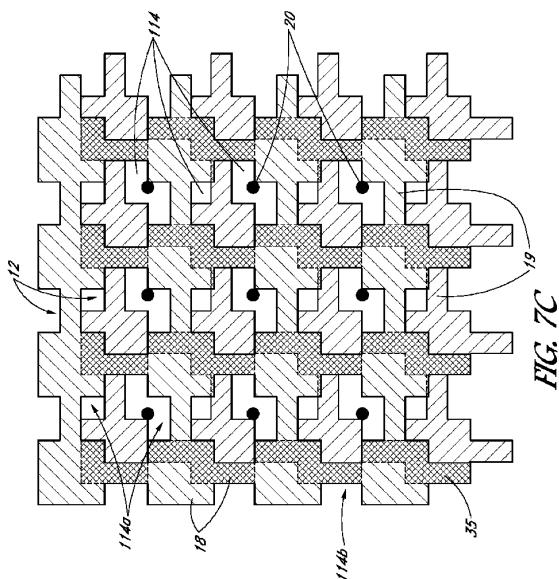

【図 7 C】非導電性界面特徴部の内側領域内に配設された複数の電気的相互接続部を有する、図 7 B の接合界面構造体の概略平面図である。

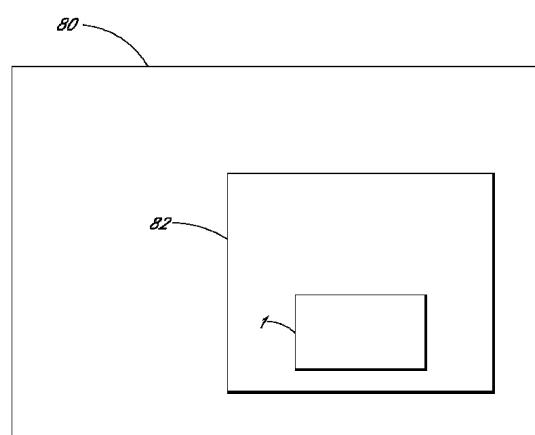

【図 8】様々な実施形態による、1つ以上の接合構造物を組み込む電子システムの概略図である。

#### 【発明を実施するための形態】

##### 【0007】

本明細書に開示される様々な実施形態は、半導体素子の集積デバイスを外部環境から事実上封止する方法で、2つの素子（半導体素子を含み得る）を接続する界面構造体に関する。例えば、いくつかの実施形態では、接合構造物は、界面構造体に沿って互いに接合された複数の半導体素子を備え得る。集積デバイスは、半導体素子に結合され得る、又は半導体素子と共に形成され得る。例えば、いくつかの実施形態では、接合構造物は、キャップ（第1の半導体素子）がキャリア（第2の半導体素子）に接合される、微小電気機械システム（MEMS）デバイスを備え得る。MEMS素子（集積デバイス）は、キャップ及びキャリアによって少なくとも部分的に画定された空洞内に配設され得る。

##### 【0008】

いくつかの構成では、界面構造体は、集積デバイスの周囲に配設された1つ以上の導電性界面特徴部と、第1及び第2の半導体素子を接続し、事実上の（effectively）環状プロファイル又は事実上の（effectively）閉鎖プロファイルを画定する、1つ以上の非導電性界面特徴部と、を備え得る。いくつかの実施形態では、界面構造体は、第1の導電性界面特徴部と、第2の導電性界面特徴部と、第1の導電性界面特徴部と第2の導電性界面特徴部との間に配設された固体状態の非導電性界面特徴部と、を備え得る。いくつかの実施形態では、各半導体素子は、関連する導電性界面特徴部を備え得、導電性界面特徴部は互い接合されて、2つの半導体素子を接続し得る。

##### 【0009】

本明細書に開示される様々な実施形態は、デバイス又はパッケージの縦横方向フットプリントを低減するための積層及び接合構造物に関する。接続界面特徴部は、2つの半導体素子の上面を介して接続して、上部素子の上面のボンドパッドに電気的に接続し得、2つの素子のうちの1つ以上には金属トレースが形成される。ボンドパッドは、素子間に画定された任意の空洞に露出した任意のデバイス（例えば、MEMS）など半導体素子の一方又は両方の内部の集積デバイスに電気的相互接続を提供し得、したがって、上部素子の不動産外の別個のボンドパッドは不要となる。空洞は、上部素子内に、上部素子内に、又は上部素子及び下部素子によって形成され得る。したがって、接合構造物の横方向の大きさは低減され得る。

##### 【0010】

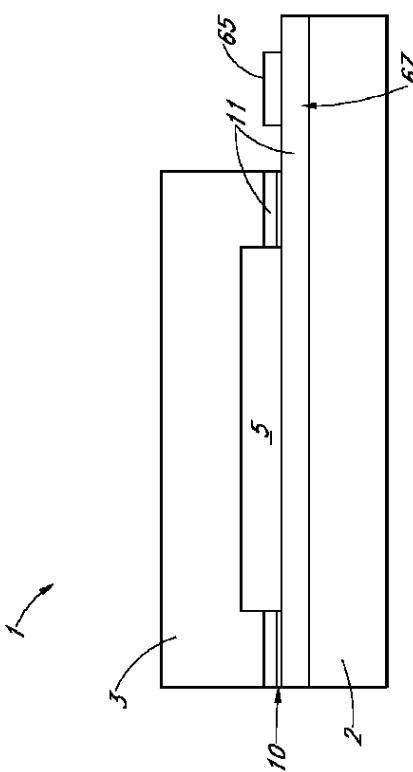

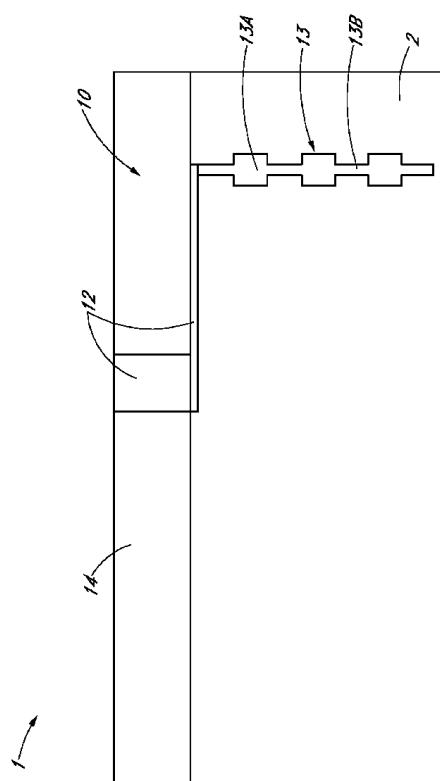

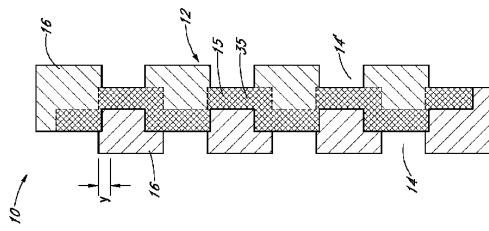

図1Aは、様々な実施形態による、接合構造物1の概略側断面図である。図2Aは、図1A～図1Bに示す接合構造物1の界面構造体10の概略断面平面図である。接合構造物1は、界面構造体10に沿って第2の半導体素子2に接合された第1の半導体素子3を含み得る。本明細書で説明するように、第1の半導体素子3及び第2の半導体素子2の対応する接合層11は、介在する接着剤を用いずに互いに直接接合され得る。以下に説明するよ

うに、界面構造体 10 は、周囲の非導電性界面特徴部 14 に埋め込まれた導電性界面特徴部 12 を含み得る。様々な実施形態では、バリア又はシード層（図示せず）は、非導電性界面特徴部 14 に設けられ得、例えば、特徴部 14 内に形成されたトレンチをライニングする。導電性界面特徴部 12（例えば、銅を含んでよい）は、存在する場合、バリア層上に設けられ得る。バリア層は、導電性界面特徴部 12 の材料が非導電性特徴部 14 に移動しないようにできる任意の好適な材料を含み得る。例えば、様々な実施形態では、バリア層は、窒化ケイ素（SiN）など絶縁材料、又はチタン（Ti）、窒化チタン（TiN）、チタンタングステン（TiW）、タンタル（Ta）、窒化タンタル（TaN）など導電性材料を含み得る。バリアとして機能する、及び／又は導電性界面特徴部 12 を電気的に絶縁するために、複数のライニング層が設けられ得る。

10

#### 【0011】

本明細書で説明するように、各素子 3、2 の接合層 11 は、接合して封止を画定し得る、導電性界面特徴部と、非導電性界面特徴部と、を含み得る。図 1A に示すように、界面特徴部 12、14 は、半導体素子内へと垂直に（例えば、接合層 11 内へ、かつそれを通して）延在し得、その結果、界面特徴部 12、14 は、一方の半導体素子から他方の半導体素子に向かう方向で、例えば、接合構造物に対して垂直に延在し得る。様々な実施形態では、界面特徴部 12 は、接合界面から接合界面の両側の各半導体素子の各半導体基板全体に延在し得る。第 1 及び第 2 の半導体素子は、集積デバイス 4 が少なくとも部分的に配設される空洞 5 を画定し得る。図示した実施形態では、第 1 の半導体素子 3 は、空洞を画定するように成形された、又は第 2 の半導体素子 2 内の空洞の上に配設されるキャップを備え得る。例えば、半導体素子 3 は、集積デバイス 4 の周囲に配設され、空洞 5 を外部環境から分離する壁 6 を備え得る。様々な実施形態では、壁 6 及びキャップは、シリコンなど半導体材料を含み得る。他の実施形態では、壁 6 及びキャップは、ポリマー、セラミック、ガラス、又は他の好適な材料を含み得る。空洞 5 は空気空洞を含み得る、又は好適な充填材料若しくは気体で充填され得る。第 1 及び第 2 の素子 2、3 は、本明細書において半導体素子として記載されるが、他の実施形態では、第 1 及び第 2 の素子 2、3 は、半導体材料を含んでも含まなくてもよい、任意の他の好適な種類の素子を含み得る。例えば、半導体材料を含まなくてよい、いくつかの実施形態において、素子 2、3 は様々な種類の光学デバイスを備え得る。他の実施形態では、光学デバイスは、半導体材料を含んでよい。

20

#### 【0012】

第 2 の半導体素子 2 は、第 1 の半導体素子 3 が接合される外面 9 を有するキャリアを備え得る。いくつかの実施形態では、キャリアは、半導体基板（例えば、導電性相互接続部を有するシリコンインターポーラー）、プリント基板（PCB）、セラミック基板、ガラス基板、又は任意の他の好適なキャリアを含み得る。かかる実施形態では、キャリアは、集積デバイス 4 と、より大きいパッケージ構造体又は電子システム（図示せず）との間で信号を転送できる。いくつかの実施形態では、キャリアは、集積デバイス 4 によって変換された信号を処理するように構成されているプロセッサダイなど集積デバイスダイを備え得る。図示の実施形態では、集積デバイス 4 は、MEMS スイッチ、加速度計、ジャイロスコープなど MEMS 素子を備える。集積デバイス 4 は、第 1 の半導体素子 3、若しくは第 2 の半導体素子 2 に結合され得る、又はそれと共に形成され得る。

30

#### 【0013】

いくつかの構成では、例えば、気体及び／又は汚染物質に対する露出など外部環境から集積デバイスダイ 4 を隔絶又は分離することが重要であり得る。例えば、一部の集積デバイスでは、水分又は気体（水素又は酸素ガスなど）に対する露出は、集積デバイス 4 又は他の構成要素の性能を損傷及び／又は変化させ得る。したがって、空洞 5 及び集積デバイス 4 を気体から事実上、つまり実質的に封止する（例えば、気密封止する、又はほぼ気密封止する）界面構造体 10 を提供することが重要であり得る。図 1A 及び図 2A に示すように、界面構造体 10 は、気体が構造物 1 の外面 8 から構造物 1 の内面 7 まで界面構造体 10 を通過しないように配置され得る。

40

#### 【0014】

50

開示される実施形態は、低気体透過速度を有する材料を用いることができ、空洞 5 への気体の進入を低減又は排除するように材料を配置できる。例えば、金属を通る一部の気体（水素ガスなど）の透過速度は、他の材料（誘電材料又はポリマーなど）を通る気体の透過速度よりも著しく低いことがある。例えば水素ガスは、外側表面 8 において、又はその付近で成分原子に解離し得る。解離した原子は、壁 6 又は界面構造体 10 に拡散し、内側表面 7 又はその付近で再結合してもよい。金属への水素ガスの拡散速度は、圧力の平方根にほぼ比例し得る。希ガスなど他の気体は、全く金属を透過しない場合がある。比較として、気体は、金属材料よりも速く（例えば、圧力に比例して）ポリマー又はガラス（酸化ケイ素）材料を通過し得るが、これは、気体分子が外壁 8 において原子に解離することなく通過し得る、又は金属材料は気体に対してより低い拡散性を有し得るためである。

10

#### 【 0 0 1 5 】

したがって、本明細書に開示される実施形態は、集積デバイス 4 の周囲に事実上の環状パターン又は閉鎖パターン（図 2 A ~ 図 2 E を参照）を画定する金属を有益に用いて、接合構造物の内部領域（例えば、空洞 5 及び / 又は集積デバイス 4 ）を外部環境及び有害気体から封止し得る。有利には、いくつかの実施形態では、金属パターンは、他の構成と比較して封止性を改善し得る完全閉鎖ループを集積デバイス 4 の周囲に備え得る。いくつかの実施形態では、金属パターンは、デバイス 4 の周囲に、例えば、ほぼ環状、又は部分的に環状など不完全な環状パターンを備え得、その結果、金属内に 1 つ以上の間隙が存在してよい。金属（銅など）を通る気体の透過速度は、誘電性又は非導電性材料（酸化ケイ素、窒化ケイ素など）を通る気体の透過速度よりも低いため、界面構造体 10 は、接合構造物 1 の内部領域に改善された封止をもたらし得る。

20

#### 【 0 0 1 6 】

しかしながら、いくつかの実施形態では、金属のみ又は有意な幅の金属線を含む界面構造体 10 を用いることは望ましくない場合がある。界面構造体 10 が幅広の金属線又はパターンを含む場合、金属は、化学機械研磨（C M P）又は他の加工工程中に著しいディッシングを受け得る。金属線のディッシングは、特に金属間及び誘電体間ハイブリッド直接接合技術を用いる場合に、第 1 の半導体素子 3 の金属線を第 2 の半導体素子 2 に接合する能力に悪影響を及ぼし得る。したがって、様々な実施形態では、界面構造体 10 は、1 つ以上の非導電性界面特徴部 14 を埋め込んだ、又は別の方法でそれに隣接する 1 つ以上の導電性界面特徴部 12 を含み得る。導電性界面特徴部は、空洞 5 内及び / 又は集積デバイス 4 への気体の透過を防止又は低減するために、有効なバリアを提供し得る。更に、導電性界面特徴部は十分に薄型化され得、ディッシングの悪影響を低減又は排除するように非導電性界面特徴部に組み入れられ得る、又は埋め込められ得る。

30

#### 【 0 0 1 7 】

本明細書に開示されるいくつかの実施形態では、界面構造体 10 は、第 1 の半導体素子上の第 1 の界面特徴部及び第 2 の半導体素子上の第 2 の界面特徴部によって画定され得る。第 1 の界面特徴部（導電性及び非導電性特徴部を含む）は、対応する第 2 の界面特徴部に接合されて、界面構造体 10 を画定し得る。いくつかの実施形態では、界面構造体 10 は、第 1 の半導体素子 3 及び第 2 の半導体素子 2 に別個に接合される別個の構造体を備え得る。例えば、いくつかの実施形態では、壁 6 は、フレームに面して設けられる、概ね平坦な半導体素子 3 を有する別個の開放フレームとして提供されてよい。第 2 の界面構造体（図示せず）は、開放フレームと半導体素子 3 との間に介在する接着剤を用いずに直接的に接合され、それによって、図 1 A に示すものに類似の密閉空洞 5 を形成する、介在構造体を備え得る。界面構造体 10 は、第 1 の半導体素子 3 と第 2 の半導体素子 2 との間に機械的接続及び / 又は電気的接続を提供してよい。いくつかの実施形態では、界面構造体 10 は素子 3 と素子 2 との間に機械的接続のみを提供してよく、これは、外部環境から空洞 5 及び / 又は集積デバイス 4 を封止するように機能し得る。他の実施形態では、界面構造体 10 はまた、例えば、接地及び / 又は電気信号の伝送用に素子 3 と素子 2 との間に電気的接続を提供してよい。図 4 A ~ 図 7 C に関連して以下により詳細に説明するように、導電性界面特徴部は、介在する接着剤を用いずに、かつ圧力、熱、及び / 又は電圧を付加せず

40

50

に、互いに直接接合され得る。例えば、第1及び第2の界面特徴部の接合面（例えば、接合層11）が調製され得る。これらの接合面では、研磨又は平坦化、活性化、及び好適な種での終端処理が行われ得る。例えば、様々な実施形態では、接合面は、1nm未満、例えば、0.5nm未満の二乗平均平方根（rms）表面粗さに研磨され得る。研磨された接合面は、わずかなエッティング又はプラズマ終端によって活性化され得る。様々な実施形態では、接合面は、窒素又は窒素含有種で、例えば、窒素含有溶液を使用してエッティングすることによって、又は窒素でのプラズマエッティングを使用することによって終端処理され得る。本明細書で説明するように、接合面は、接触させられて、圧力を付加せずに直接接合を形成し得る。いくつかの実施形態では、半導体素子3、2を加熱して、接合、例えば、導電性特徴部間の接合を強化し得る。直接接合法の更なる詳細は、少なくとも米国特許第9,385,024号、同第9,391,143号、及び同第9,431,368号に見出すことができ、それらの内容全体は、参照によりその全体があらゆる目的で本明細書に援用される。いくつかの実施形態では、両素子3、2の導電性界面特徴部12及び両素子3、2の非導電性界面特徴部14は、互いに同時に直接接合される。他の実施形態では、非導電性界面特徴部14は、最初に互いに直接接合され得、次いで導電性界面特徴部12は、隣接する非導電性界面特徴部14から、例えば20nm未満又は10nm未満窪んでいる、つまりやや凹んでいる導電性界面特徴部12を優先的に拡張する熱処理後、続いて互いに直接接合され得る。

#### 【0018】

図示した実施形態はMEMS接合構造物を目的としているが、開示される実施形態と併せて任意の好適な種類の集積デバイス又は構造体を使用できることを理解されたい。例えば、いくつかの実施形態では、第1及び第2の半導体素子は、集積デバイスダイ、例えば、プロセッサダイ及び/又はメモリダイを備え得る。加えて、開示される実施形態は空洞5を含むが、他の構成では、空洞が存在しなくてよい。例えば、本明細書に開示される実施形態は、外部環境及び気体から活性成分を封止することが望ましい場合がある、任意の好適な集積デバイス又は集積デバイスダイと共に用いられ得る。更に、開示される実施形態は、他の目的を達成するために使用され得る。例えば、いくつかの構成では、開示された界面構造体10が使用されて、不要な電磁放射線が構造体1に入ることを低減若しくは防止するため、及び/又は様々な種類の信号漏れを防止するために、電磁シールドが提供され得る。当然のことながら、空洞は、例えば構造体1の熱特性、電気的特性、又は機械的特性を改善し得る液体、気体、又は他の好適な物質などの任意の好適な流体で充填されてよい。

#### 【0019】

図1B～図1Kは、界面構造体10の様々な実施形態の概略部分断面平面図である。図示したパターンは、図1Aの空洞5など保護領域の周囲で、完全に環状又は不完全に環状（例えば、ほぼ環状）に延在して、事実上の環状プロファイル又は事実上の閉鎖プロファイルを画定し得ることが理解されるであろう。本明細書で使用するとき、事実上の環状構造体は、円環状構造体、並びに事実上の閉鎖プロファイル（例えば、正方形又は他の多角形）を画定する非円環状構造体を含んでよい。図1B～図1Kに示すように、界面構造体10は、1つ又は複数の導電性界面特徴部12と、1つ又は複数の非導電性界面特徴部14と、を含み得る。図1Aに示すように、導電性特徴部12及び非導電性特徴部14は、第1の半導体素子3、及び/又は第2の半導体素子2の一部を通って垂直に、例えば、接合層11の一部を通って垂直に延在できる。例えば、導電性特徴部12及び非導電性特徴部14は、第1の半導体素子3、及び/又は第2の半導体素子2を通って垂直に（例えば、半導体素子3、2の正面に対して非平行又は垂直な方向に）、少なくとも0.05マイクロメートル、少なくとも0.1マイクロメートル、少なくとも0.5マイクロメートル、又は少なくとも1マイクロメートルの垂直距離だけ延在し得る。例えば、導電性特徴部12及び非導電性特徴部14は、第1の半導体素子3、及び/又は第2の半導体素子2を通って0.05マイクロメートル～5マイクロメートルの範囲、0.05マイクロメートル～4マイクロメートルの範囲、0.05マイクロメートル～2マイクロメートルの範囲、

又は0.1マイクロメートル～5マイクロメートルの範囲の垂直距離だけ垂直に延在し得る。第1の半導体素子3、及び/又は第2の半導体素子2の一部を通って導電性特徴部12及び非導電性特徴部14を延在させることにより、界面構造体10の導電性特徴部12及び非導電性特徴部14は、半導体素子3と半導体素子2との間に間隙を設けずに封止を提供し得る。例えば、様々な構成では、導電性特徴部12及び非導電性特徴部14が素子3、2の半導体基板部分へと延在する場合、半導体及び金属のみからなる好ましい封止が形成され得る。半導体素子3、2上に設けられる導電性特徴部12及び非導電性特徴部14は、2つの半導体素子を接合するために概ね平坦な表面を提供してよい。

#### 【0020】

導電性界面特徴部12は、金属など任意の好適な導体を備え得る。例えば、導電性界面特徴部12は、銅、ニッケル、タンクステン、アルミニウム、又は空気、水素、窒素、水、水分など流体/気体に対して十分に不透過性である任意の他の好適な金属を含み得る。非導電性界面特徴部14は、誘電材料又は半導体材料など任意の好適な非導電性材料を含み得る。例えば、非導電性界面特徴部14は、いくつかの実施形態では、酸化シリコン又は炭化ケイ素窒化物を含み得る。有利には、導電性界面特徴部12及び非導電性界面特徴部14の両方を使用することは改善された封止を提供して、気体が外部環境から空洞5及び/又はデバイス4へと通過すること、並びにその逆に通過することを防止し得る。上述したように、金属など導体は、概して多くの気体に対して改善された封止を提供してよい。しかしながら、一部の非導電性材料(例えば、誘電体)は、特定の気体に対して導体、金属、又は半導体よりも透過性が低いことがある。導電性特徴部12を非導電性特徴部14と構造的に混在させることにより堅牢な封止が提供されて、多くの異なる種類の気体及び他の流体が空洞に入り、かつ/又はデバイス4に影響を及ぼすことを防止してよい。

10

#### 【0021】

図1Bの実施形態では、完全に環状であってよい1つの導電性界面特徴部12のみが提供される。導電性界面特徴部12は、1つ以上の非導電性界面特徴部14に埋め込まれて、事実上の環状プロファイル又は事実上の閉鎖プロファイルを画定し得る。例えば、いくつかの実施形態では、導電性界面特徴部12は、バルク非導電性材料に埋め込まれ得る。他の実施形態では、導電性界面特徴部12の両側に非導電性材料の層が設けられ得る。図2Aに示すように、導電性界面特徴部12は、完全に環状のパターンで空洞5及び/又は集積デバイス4の周囲に延在し得る。図2Aでは、例えば、導電性界面特徴部12は、空洞5及び/又はデバイス4の周囲を完全な環状又は閉鎖形状で延在し、その結果、非導電性特徴部14の非導電性材料は導電性界面特徴部12を横断しない、又はこれと交差しない。しかしながら、他の実施形態では(例えば、以下の図2D及び図2Eの説明を参照されたい)、導電性界面特徴部12の部分の間に1つ以上の間隙が存在してよいが、空洞5への直通路は存在しない。いくつかの実施形態では、導電性界面特徴部12の個々の素子は、不完全に環状であり得る。例えば、導電性界面特徴部12の個々の素子はほぼ環状であり得、例えば、空洞5及び/又は集積デバイス4の周囲に少なくとも180°、少なくとも270°、少なくとも350°、又は少なくとも355°(例えば、360°)だけ延在し、一方、協働して事実上の環状又は閉鎖界面構造体10を画定する。更に、上述したように、導電性界面特徴部12は、壁6の一部及び/又は第2の半導体素子2の対応する部分へと垂直に延在し得、これらに埋め込まれ得る。

20

30

#### 【0022】

図1B～図1Kの例示的パターンのいずれかを含む、図1Aの構造体は、例えば、堆積、パターニング、及びエッチングによって基板上に金属線を形成し、その上に酸化物を堆積させることによって、又はダマシン処理によってなど半導体製造技術によって形成され得る。望ましくは、接合される金属線は、包囲する非導電性材料と同一平面に、又は非導電性材料からわずかに(例えば、0.5nm～20nm)凹んで、若しくは突出して形成される。金属線の環状又はほぼ環状のパターンは、半導体加工を用いて両半導体素子3、2上に形成され、互いに直接接合して、気体拡散に対して有効な金属封止を作り出し得る。

40

#### 【0023】

50

界面構造体 10 は、1マイクロメートル～1mm の範囲、0.1マイクロメートル～100マイクロメートルの範囲、0.1マイクロメートル～50マイクロメートルの範囲、1マイクロメートル～25マイクロメートルの範囲、0.1マイクロメートル～10マイクロメートルの範囲、0.1マイクロメートル～1マイクロメートルの範囲、1マイクロメートル～10マイクロメートルの範囲の界面幅  $t_0$  を有し得る。導電性界面特徴部 12 は、0.1マイクロメートル～50マイクロメートルの範囲の導体幅  $t_c$  を有し得る。非導電性界面特徴部 14 は、0.1マイクロメートル～1mm の範囲、0.1マイクロメートル～100マイクロメートルの範囲、1マイクロメートル～25マイクロメートルの範囲、0.1マイクロメートル～10マイクロメートルの範囲、0.1マイクロメートル～1マイクロメートルの範囲、又は1マイクロメートル～10マイクロメートルの範囲の絶縁体幅  $t_i$  を有し得る。上で説明したように、図 1B に開示される界面構造体 10 は、空洞 5 に入り、かつ / 又はデバイス 4 と相互作用する気体に対して効果的な封止を有益に提供し得る。更に、本明細書に開示される界面構造体 10 は、所与の接合強度に対して他の種類の接合又は界面よりも狭い水平寸法であり得、これによりパッケージの総フットプリントを有利に低減できる。様々な実施形態では、界面構造体 10 は、非導電性特徴部 14（例えば、誘電体）によって、ほぼ又は完全に画定され得、その結果、接合された界面の大部分又は全体は非導電性材料を含む。上で説明したように、絶縁体の幅  $t_i$  は、非常に狭く（例えば、1マイクロメートル～100マイクロメートルの範囲、又は1マイクロメートル～50マイクロメートルの範囲）することができるが、その一方では、素子間に十分に強い接合界面を提供する。

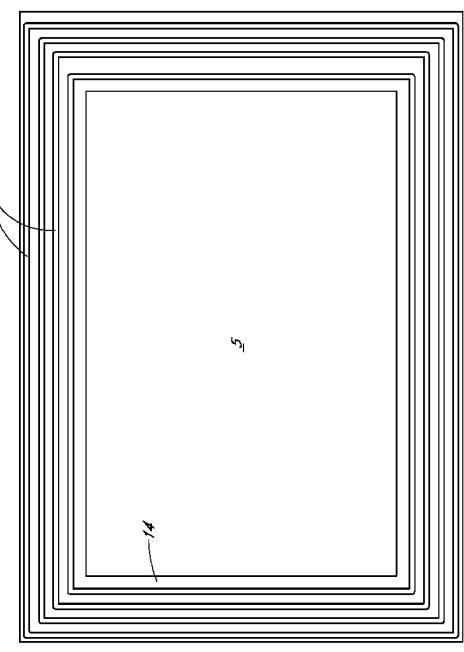

#### 【0024】

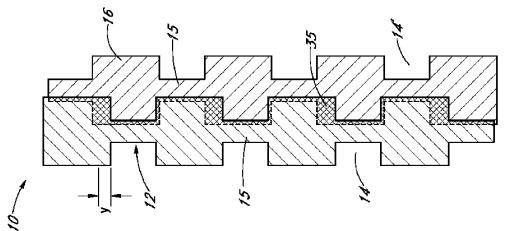

図 1C を参照すると、界面構造体 10 は、複数の導電性界面特徴部 12 と、隣接する導電性界面特徴部 12 間に配設された、介在する固体状態（例えば、非気体状）の非導電性界面特徴部 14 と、を含み得る。図 2C は、図 1C に示す界面構造体 10 の概略平面図である。図 1B の実装形態と同様に、界面構造体 12 は、集積デバイス 4 の周囲に配設され得、事実上の環状又は閉鎖プロファイル（例えば、様々な構成では完全な環又は不完全な環）に配置された導電性特徴部 12 を備えて、第 1 の半導体素子 3 及び第 2 の半導体素子 2 を接続し得る。図 1C 及び図 2C では、導電性特徴部 12 は、少なくとも 1 つの完全な（complete or absolute）環を備える。他の実施形態では、導電性特徴部は、異なる形状であり得るが、事実上の環状プロファイル又は閉鎖プロファイルを画定するように配置され得る。複数の導電性特徴部 12 を使用することにより、空洞 5 への気体流入を低減するように、高不透過性材料の複数の層を設けることができる。非導電性特徴部 14 によって離隔された複数の薄型導電性特徴部 12 を用いることにより、より幅広の特徴部と比較して、所定の程度の全体的な不透過性を得るために研磨によるディッシングの影響が低減され得る。したがって、様々な実施形態では、複数の導電性特徴部 12 は、例えば、デバイス 4 及び / 又は空洞 5 の周囲に同心円状に、ほぼ周囲に、又は全周に配置されて、有効な気体封止を提供し得る。

#### 【0025】

図 1D に移動すると、いくつかの実施形態では、導電性界面特徴部 12 は、空洞 5 及び / 又はデバイス 4 の周囲に事実上の環状パターン又は閉鎖パターンで配設された、複数の環状導体 12A と、隣接する環状導体 12A を接続する複数の横方向導体 12B と、を備え得る。有利には、環状導体 12A 及び横方向導体 12B の使用は、直接接合（以下に説明する）を用いる実装形態に増加した接触領域をもたらし得、導電性材料の有益な透過特性に起因して、改善された気体封止をもたらし得る。図 1B～図 1C の実施形態と同様に、図 1D の実施形態では、導電性界面特徴部 12 は閉ループを区切り得、その結果、非導電性特徴部 14 は導電性特徴部 12 と交差しない。

#### 【0026】

図 1E～図 1G は、複数の導電セグメント 112a～112c が端と端で接続され、隣接するセグメントに対して角度付けられた、捻転環状プロファイルを有する導電性界面特徴部 12 を示す。図 1B～図 1D の実施形態と同様に、特徴部 12 は、空洞 5 及び / 又はデ

10

20

30

40

50

バイス 4 の周囲で事実上の環状パターン又は閉鎖パターンで、例えば、完全な環状に配設され得る。図 1 E ~ 図 1 G に示す捻転プロファイルは、横断方向に互いに離隔された第 1 のセグメント 112a 及び第 2 のセグメント 112c を備え得る。第 1 及び第 2 のセグメント 112a、112c は、介在する横断セグメント 112b によって接続され得る。第 1 及び第 2 のセグメント 112a、112c は、空洞 5 及び / 又は集積デバイス 4 の周囲の少なくとも部分的な環状経路に概ね平行な方向に沿って方向付けられ得る。横断セグメント 112c は、第 1 及び第 2 のセグメント 112a、112c に対して横方向又は非平行に方向付けられ得る。いくつかの実施形態では、非導電性界面特徴部 14 は、導電性特徴部 12 を横断しなくてよい。

## 【 0027 】

導電性界面特徴部 12 の捻転環状プロファイルは、直線状の、又は捻転しない特徴部 12 と比較して、位置ずれに対する許容度の増加により直接接合を容易にでき、その一方で、研磨後のディッシングの影響に対する細線の利点を維持する。例えば、導電性界面特徴部 12 は、ディッシングの影響を低減するために十分に薄型であってよいが、接合のための整列を容易にするパターンを横断してよい。捻転プロファイルは、任意の数の導電性界面特徴部 12 を含み得る。例えば、図 1 E は、単一の導電性界面特徴部 12 を有する捻転プロファイルを示す。図 1 F は、介在する非導電性界面特徴部 14 によって横方向に離隔された複数の導電性界面特徴部 12 を示す。図 1 D と同様に、図 1 G では、離隔された環状導体 12A は、横方向導体 12B によって接合され得る。当業者は、他のパターンが好適であり得ることを理解するであろう。

## 【 0028 】

図 1 H ~ 図 1 K は、複数の導電セグメント 112a ~ 112f が端と端で接続され、1 つ以上の屈曲領域 11 を介して隣接するセグメントに対して角度付けられた、不規則な、又はジグザグ形の環状プロファイルを有する導電性界面特徴部 12 を示す。図 1 H ~ 図 1 K に示すように、セグメント 112a ~ 112f は不規則パターンで配置されてよく、セグメント 112a ~ 112f は異なる方向で角度付けされ、かつ / 又は異なる長さを有する。他の構成では、セグメント 112a ~ 112f は、環状プロファイルに沿って同一の角度、つまり周期的な角度の規則的パターンで配置されてよい。更に他の構成では、導電性特徴部 12 の各セグメント 112a ~ 112f は、湾曲し得る、又は別の方法で非線形であり得る。これらの特徴部はまた、直線セグメントに対して位置ずれに対する許容度を増加させてよく、その一方、ディッシングの影響を受けにくい比較的細い線を依然として用いており、したがって、金属間直接接合でより容易に用いられる。

## 【 0029 】

図 2 B は、界面構造体 10 を通って延在する 1 つ以上の電気的相互接続部を有する、界面構造体 10 の概略断面図である。図 2 A と同様に、導電性特徴部 12 は、空洞 5 及び / 又は集積デバイス 4 の周囲で界面構造体 10 内に配置されて、事実上の環状又は閉鎖プロファイル、例えば、完全な環状プロファイルを画定し得る。導電性特徴部 12 は細長い特徴部を備え得、長さは幅よりも長い（例えば、幅の少なくとも 5 倍の長さ、又は少なくとも幅の 10 倍の長さを有する）。しかしながら、図 2 A に示す界面構造体 10 とは異なり、図 2 B の界面構造体 10 は、1 つ以上の非導電性界面特徴部 14 を通って垂直に延在する 1 つ又は複数の電気的相互接続部 20 を含む。電気的相互接続部 20 は、構造体 1 の様々な構成要素間で信号を転送するように、集積デバイス 4 及び / 又は接合構造物 1 の他の構成要素と電気通信できる。いくつかの実施形態では、電気的相互接続部 20 は、第 1 の半導体素子 3 から第 2 の半導体素子 2 まで延在し得る。図 2 B に示すように、電気的相互接続部 20 は、導電性界面特徴部 12 から内側に、電気的に離隔され得、それ自体はまた、第 1 及び第 2 の半導体素子 3、2 内の回路を電気的に接続するように機能し得る。他の実施形態では、電気的相互接続部 20 は、導電性界面特徴部 12 から外側に離隔され得る。更に他の実施形態では、以下に説明するように、電気的相互接続部 20 は、複数の導電性界面特徴部 12 の間に配設された、介在する非導電性界面特徴部 14 を通って延在し得る。

## 【 0030 】

10

20

30

40

50

電気的相互接続部 20 は、界面構造体 10 を介して半導体素子 3、2 間に電気通信を提供し得る。したがって、界面構造体 10 に対して非平行な方向又は横断方向に相互接続部 20 を設けることにより、界面構造体 10 は、2 つの半導体素子 3、2 間の機械的接続及び電気的接続の両方として機能できるようにし得る。相互接続部 20 は、銅、アルミニウム、金など任意の好適な導体を備え得る。相互接続部 20 は、様々な構成で、導電トレース又はシリコン貫通ビアを備え得る。更に、上述のように、界面特徴部 12 はまた、従来の相互接続部 20 の有無にかかわらず、環状の、又はほぼ環状の電気的相互接続部として機能してよい。

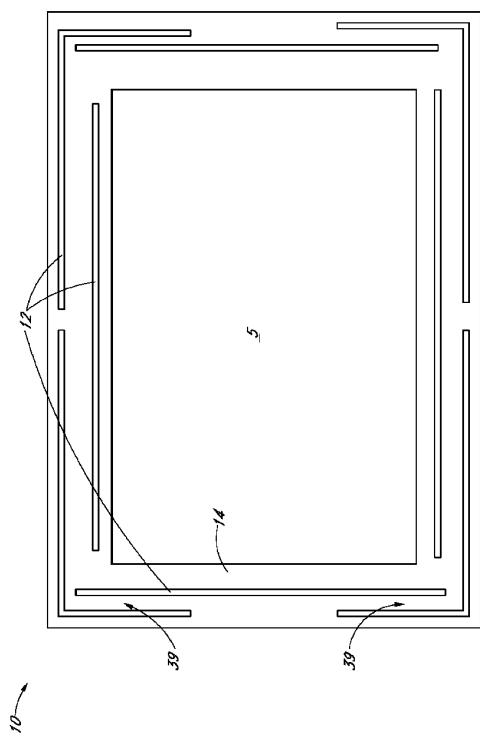

### 【 0 0 3 1 】

図 2 D は、空洞 5 の周囲に配設された複数の導電性界面特徴部 12 A、12 B を有して、事実上の環状、又は閉鎖プロファイルを画定する界面構造体 10 の概略断面平面図であり、各導電性界面特徴部 12 A、12 B は、不完全な環状特徴部、例えば、180° を超えて延在する、ほぼ環状の特徴部を備える。例えば、図 2 D に示すように、各導電性界面特徴部 12 A、12 B は U 字形構造を備え得、特徴部 12 B は、非導電性間隙 39 によって特徴部 12 A に対して内側に配設される。したがって、図 2 D では、各導電性界面特徴部 12 A、12 B は、ほぼ環状のプロファイルを備えてよいが、界面特徴部 12 A、12 B のいずれか 1 つは必ずしも閉ループを画定しないように、2 つの界面特徴部 12 A、12 B の間に間隙 39 を備える。図 2 D に示す構造体 10 は、導電性界面特徴部 12 A、12 B のパターンが組み合わさって空洞 5 の周囲に事実上の環状、又は事実上の閉鎖構造を形成するために、空洞 5 及び / 又はデバイス 4 への気体の透過を低減するのに依然として有効であり得る。一部の気体は、間隙 39 を透過してよいが、導電性界面特徴部 12 A、12 B の導電性材料に対する非導電性材料 14 内の気体のより高い拡散性を克服するために、ガスが空洞 5 に到達できる、かつ / 又はデバイス 4 に接触できるまでに非導電性材料を通る非常に長い経路を有するであろう。2 つの特徴部 12 A、12 B が本明細書に示されているが、任意の好適な数の特徴部 12 が使用され得ることを理解されたい。

### 【 0 0 3 2 】

図 2 E は、空洞 5 の周囲に配設された複数の導電性界面特徴部 12 を有して、事実上の環状又は閉鎖プロファイルを画定する界面構造体 10 の概略断面平面図であり、複数の導電性特徴部 12 は、非導電性間隙 39 によって離隔された複数のセグメントを備える。図 2 E に示す各導電性界面特徴部 12 を画定するセグメントは線形セグメントを含むが、他の実施形態では、セグメントは湾曲し得る。図 2 E では、一部又は全ての導電性界面特徴部 12 は、それ自体ではほぼ環状のパターンを画定しない場合がある。しかしながら、総合的には、図示した導電性界面特徴部 12 の配置によって画定されるパターンは、事実上の環状又は閉鎖パターンを画定してよい。したがって、特定の導電性界面特徴部 12 が環状でなくても、複数の導電性界面特徴部 12 の配置は、図 2 E に示すように、事実上の環状又は閉鎖パターンを画定して、外部環境から内部領域に入る気体から接合構造物の内部領域を封止し得る。

### 【 0 0 3 3 】

したがって、図 2 A ~ 図 2 E の実施形態は、事実上の環状、又は閉鎖拡散バリアを集合的に画定する導電性界面特徴部 12 及び非導電性界面特徴部 14 を含む、界面構造体 10 を備え得る。例えば、特定の導電性界面特徴部 12 は、事実上の環状パターン、つまり拡散バリアを画定するように、他の導電性及び非導電性界面特徴部と共に配置される、完全な環又は不完全な環（例えば、ほぼ環状）を備え得る。いくつかの実施形態では、導電性界面特徴部は、事実上の環状パターン、つまり拡散バリアを画定するように、空洞 5 及び / 又はデバイス 4 の周囲に配置される、直線又は曲線セグメントなど他の形状を備え得る。更に、図 2 D 及び図 2 E の実施形態は、例えば、別個の信号線接続、接地線接続、及び電力線接続用の別個の電気的接続としてそれぞれ機能し得る、複数の導電性セグメントを有利に提供し得る。これらのセグメントは合わせて、事実上の環状導電性パターンを提供して、拡散バリアとして機能し得る。本明細書に記載の事実上の環状パターンは、構造体 1 の敏感な構成要素に到達するために気体が移動する、より長い距離を有益に提供し得、構

10

20

30

40

50

造体 1 の透過性を低減し得る。

【 0 0 3 4 】

図 2 F は、いくつかの実施形態による、接合構造物 1 の概略側断面図である。図 2 F は、図 2 F において、第 1 の半導体素子 3 が、半導体素子 3 の様々な部分と共に形成された、又はそれと結合された、1 つ又は複数の電子部品 3 8 を備え得ることを除いて、図 1 A に類似である。例えば、図示のように、半導体素子 3 は、複数の電子部品 3 8 A ~ 3 8 C を備え得る。電子部品 3 8 A ~ 3 8 C は、任意の好適な種類の電子部品を含み得る。電子部品 3 8 は、集積回路（例えば、1 つ以上のトランジスタ）など任意の好適な種類のデバイスを含み得る。いくつかの実施形態では、電子部品 3 8 は、相互接続部（図 2 B を参照）、及び / 又は導電性界面特徴部 1 2 を介してデバイス 4、第 2 の半導体素子 2、及び / 又は他の構成要素と通信できる。例えば、電子部品 3 8 は、半導体素子 3 を通過する 1 つ以上の導電トレース 3 6 を介して第 2 の半導体素子 2 と通信できる。電子部品 3 8 及びトレース 3 6 は、堆積、リソグラフィ、エッチング、エッチングなど半導体加工技術によって画定され得、半導体素子 3 と一体化され得る。トレースは、例えば、複数の金属レベルを通して従来のバックエンドオブライン相互接続金属化によって形成されてよい。更に、図 2 F に示すように、本明細書に開示される実施形態のいずれかは、（例えば、半導体加工技術を用いて）第 2 の半導体素子 2 と共に形成された、又はそれと結合された、1 つ又は複数の電子部品 3 7 を含み得る。電子部品 3 7 は、集積回路など任意の好適な種類のデバイスを備え得、デバイス 4、第 1 の半導体素子 3、及び / 又は他の構成要素と通信できる。例えば、いくつかの実施形態では、1 つ以上の電子部品 3 7 A は、半導体素子 2 内で画定され得る（例えば、半導体素子 2 内に埋め込まれる、又は表面 9 に露出する）。いくつかの実施形態では、1 つ以上の電子部品 3 7 B は、半導体素子 2 の表面 9 において、又はその上に画定され得る。

【 0 0 3 5 】

図 2 G は、いくつかの実施形態による、接合構造物 1 の概略側断面図である。図 2 G は、図 2 G において、第 1 の半導体素子 3 と第 2 の半導体素子 2 との間に画定される空洞が存在しない場合があることを除いて、図 1 A 及び図 2 F に類似である。むしろ、図 2 G の実施形態では、第 1 及び半導体素子 3、2 は、介在する空洞を設けずに互いに接合されてよい。図示した実施形態では、本明細書に記載の実施形態と同様に、半導体素子 3、2 は、素子 3、2 の内部の周囲に事実上の環状パターン又はプロファイルを画定する界面構造体 1 0 によって互いに接合され得る。本明細書で説明するように、半導体素子 3、2 は、少なくとも界面構造体 1 0 に沿って互いに直接接合されて、事実上の環状プロファイルを画定し得、その中には画定された導電性及び非導電性界面特徴部を有する。界面構造体 1 0 の事実上の環状プロファイルは、本明細書に開示されるパターンのうちのいずれかを備え得る。図 2 G の接合構造物 1 に空洞が存在しない場合であっても、界面構造体 1 0 は、例えば気体など外部環境から構造物 1 の内部の敏感な電子回路又は構成要素 3 7 を保護するように、有効な封止を画定してよい。本明細書に開示される実施形態のいずれも、空洞を含まない接合構造物と併せて使用されてよいことを理解されたい。

【 0 0 3 6 】

更に、図 2 G に示すように、第 1 の半導体素子 3 は、素子 3 の表面若しくはその付近に、及び / 又は素子 3 の本体内に形成された 1 つ以上の電子部品 3 8 を備え得る。第 2 の半導体素子 3 は、素子 2 の表面若しくはその付近に、及び / 又は第 2 の半導体素子 3 の本体内に形成された 1 つ以上の電子部品 3 7 を備え得る。電子部品 3 7、3 8 は、トランジスタを含む電子回路など任意の好適な種類の素子を備え得る。構成要素 3 7、3 8 は、任意の好適な配置で素子 3、2 全体に配設され得る。図 2 G の実施形態では、第 1 及び第 2 の素子 3、2 は、プロセッサダイ、メモリダイ、センサダイの任意の組み合わせなどデバイスダイの任意の組み合わせを備え得る。図示した実施形態では、界面構造体 1 0 は、接合構造物 1 の内部を外部環境から封止するように、接合構造物 1 の外周の周囲に配設され得る。したがって、様々な実施形態では、接合構造物 1 の内部、例えば、界面構造体 1 0 によって画定された事実上の環状パターン内の領域は、直接接合されても、直接接合されなく

10

20

30

40

50

てもよい。図示した実施形態では、一部の部品 37、38 は、接合構造物 1 の内部領域内、例えば、界面構造体 10 によって画定された事実上の閉鎖プロファイル内に配設されてよい。第 1 の半導体素子 3 の第 1 の相互接続部及び第 2 の半導体素子 2 の第 2 の相互接続部は、接合構造物 1 の内部領域内で互いに直接接合されて、それぞれの素子 3、2 内の部品 37、38 を接続し得る。加えて、追加部品は、界面構造体 10 によって画定された内部領域の外側に配設されてよい。かかる追加部品（集積デバイスダイなど）はまた、内部領域の外側で互いに直接接合されてよい。

#### 【 0 0 3 7 】

図 2H 及び図 2I は、平面図から見たときの一連の導電性ドットを含む導電性界面特徴部 12 を備える界面構造体 10 の概略平面図である。図 2H では、導電性界面特徴部 12 は、空洞 5（又は概ね接合構造物の内部）の周囲に、密接して離隔されたドットの環を含む。図 2I では、導電性界面特徴部 12 は密接して離隔されたドットの複数の環を含み、界面構造体 10 の封止性を改善するように、特徴部の外側環が特徴部の内環に対して横方向にオフセットされている。図 2I には特徴部 12 の 2 つの環を示すが、導電性特徴部 12 は、事実上の環状パターンを画定するように互いに離隔されたドット又は不連続形状のメッシュを含み得ることを理解されたい。導電性界面特徴部 12 及び非導電性界面特徴部 14 は、協働して、2 つの半導体素子を接続する事実上の環状又は事実上の閉鎖パターンを画定し得る。図 2H～図 2I に示すドットは、丸形（例えば、円形又は橢円形）として示すが、他の実施形態では、ドットは多角形など任意の好適な不連続形状を含み得ることを理解されたい。更に、本明細書で説明するように、いくつかの実施形態では、導電性界面特徴部 12（例えば、ドット）は、2 つの半導体素子 3、2 間の接合特徴部としてのみ機能してよい。しかしながら、他の実施形態では、一部又は全ての導電性界面特徴部 12 は、電気的相互接続部（相互接続部 20 又はそれに接続されたパッドの端部など）として機能して、半導体素子 3、2 間に電気通信を提供してよい。図 2H 及び図 2I の特徴部は、本明細書に開示される様々な他の実施形態と組み合わされ得ることを理解されたい。

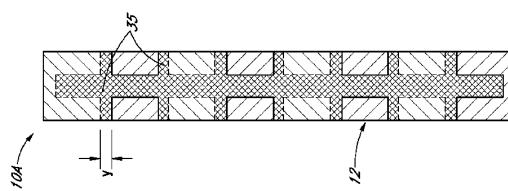

#### 【 0 0 3 8 】

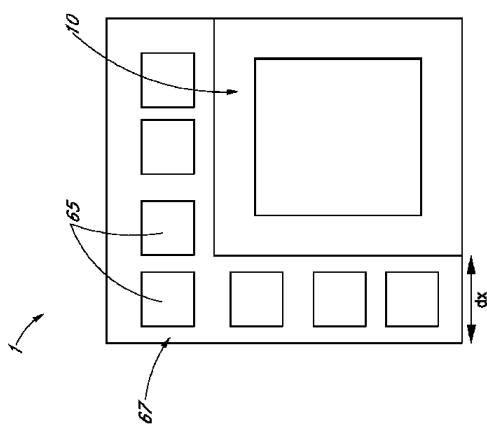

図 2J は、第 1 の素子 3 と第 2 の素子 2 との間（いくつかの実施形態では、半導体素子を含んでよい）の接合界面の外側に位置付けられた 1 つ以上のボンドパッド 65 を有する接合構造物 1 の概略側断面図である。図 2K は、図 2J に示す接合構造物 1 の平面図である。特に断らない限り、図 2J～図 2K に示す構成要素は、図 1A～図 2I の同様の番号が付された構成要素と同じであってよい、又は概して類似であってよい。例えば、接合構造物は、介在する接着剤を用いずに界面構造体 10 に沿って互いに直接接合された第 1 及び第 2 の素子 3、2 を含み得る。他の実施形態では、第 1 及び第 2 の素子 3、2 は、1 つ以上の接着剤など他の方法で接着されてよい。様々な実施形態では、各素子 3、2 の接合層 11 は、界面構造体 10 に沿って互いに直接接合し得る導電性界面特徴部を含み得る。いくつかの実施形態では、導電性界面特徴部は、本明細書の他の箇所に記載するように閉鎖形状を画定して、拡散に対して界面を封止し得る。いくつかの実施形態では、各素子 3、2 の接合層 11 は、接合して封止部及び事実上の閉鎖又は事実上の環状プロファイルを画定し得る、導電性及び非導電性界面特徴部（図示せず）を含み得る。第 1 及び第 2 の素子 3、2 は、集積デバイスが少なくとも部分的に配設される空洞 5 を画定し得る。図 2G に示すような他の実施形態では、2 つの素子 3、2 間に空洞が存在しなくてよい。他の実施形態では、隔絶された、又は埋め込まれた導電部分との任意の種類のハイブリッド接合が使用され得る。

#### 【 0 0 3 9 】

図 2J 及び図 2K に示すように、ボンドパッド 65 は、界面構造体 10 によって画定された、事実上の閉鎖プロファイルの外側に配設され得る。例えば、ボンドパッド 65 は、第 2 の素子 2 の外側レッジ部 67 上に配設され得る。ボンドパッド 65 は、第 2 の素子 2 内の回路に直接接続され得る。ボンドパッド 65 はまた、第 1 の素子 3、及び / 又は第 2 の素子 2 内に画定された導電トレース（図示せず）によって、第 1 の素子 3 内の回路に接続され得る。ボンドパッド 65 は、例えば、ワイヤボンド、はんだボール、又は他の電気コ

10

20

30

40

50

ネクタによって、パッケージ又はシステムボードなど外部構成要素と電気通信するように構成され得る。事実上の閉鎖プロファイルは、素子3によって、素子2によって、又は素子2、3の両方によって画定され得る。

【0040】

図2Kに示すように、レッジ部67は、接合界面構造体10の外側の接合構造物1の辺に沿ったレッジ幅d<sub>x</sub>を有し得る。レッジ幅d<sub>x</sub>は、構造物1の総フットプリントを必要に増加させ得る。様々な構成では、レッジ幅d<sub>x</sub>は、50マイクロメートル～250マイクロメートルの範囲、又は100マイクロメートル～200マイクロメートルの範囲であり得る。任意の好適な数のレッジ部が、接合界面構造体10の外周の周囲に設けられてよい。図2Kでは、例えばレッジ部67は、界面構造体10の2つの垂直辺又は非平行側辺に沿って設けられるが、他の実施形態では、2つのレッジ部67は、界面構造体10の2つの平行辺に沿って設けられてもよい、1つのレッジ部67のみが、界面構造体10の1辺のみに沿って設けられてよい、又は2つを超えるレッジ部67（例えば、3つ又は4つ）が、界面構造体10の2つを超える辺（例えば、3辺又は4辺）に沿って設けられ得る。非矩形要素では、他の辺数も可能である。

10

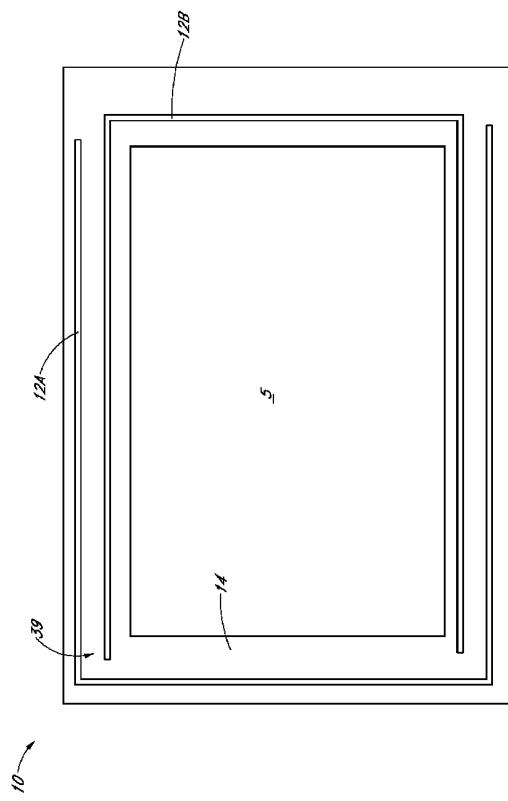

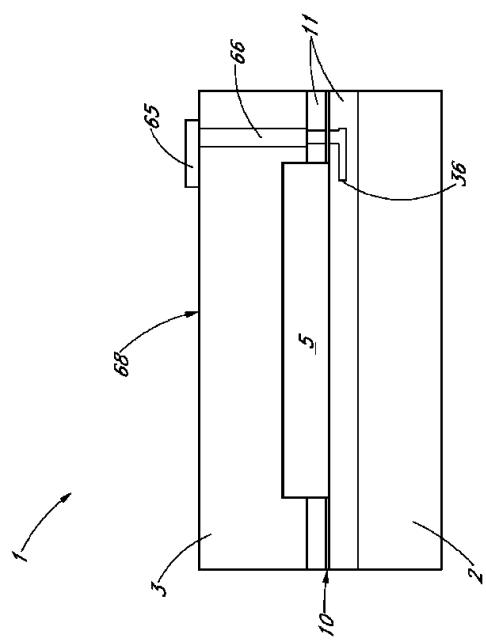

【0041】

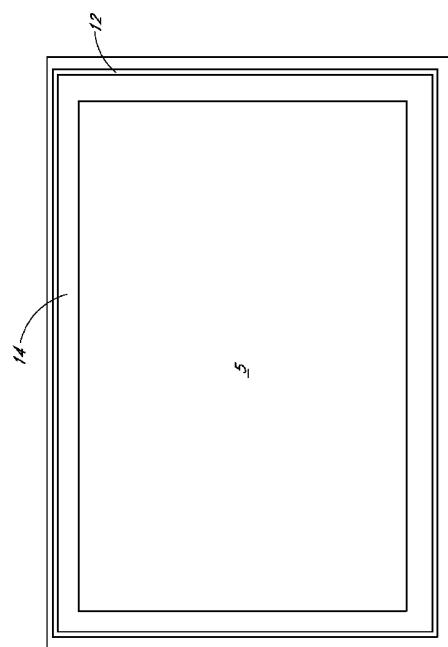

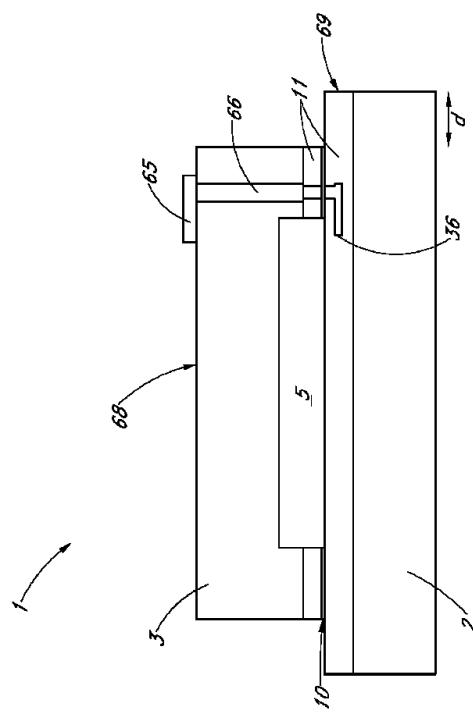

図2Lは、様々な実施形態による、接合構造物1の上面68に配設された1つ以上のボンドパッド65を有する接合構造物1の概略側断面図である。図2Mは、図2Lに示す接合構造物1の平面図である。図2Lに示されるように、1つ以上のボンドパッド65は、接合構造物1の外面又は上面68、例えば、第1の素子3の上面に設けられ得る。上面68上にあるものとして図示したが、当業者であれば、接合パッド65は、接合構造物の上面に対して凹んでいてよく、又はパッシベーション層の下に埋め込まれ、開口部によって露出してよいことを理解するであろう。上述したように、1つ以上の導電トレース36は、構造物1の様々な構成要素間に電気通信を提供し得る。図示した実施形態では、トレース36は、（例えば、非導電界面特徴部に埋め込まれてよい界面構造体10内の導電性界面特徴部によって）界面構造体10及び第1の素子3の本体を通って第2の素子2の導電トレース36から延在する導電相互接続部66によってボンドパッド65と接続できて、ボンドパッド65に電気的に接続する。相互接続部66はまた、第2の素子2の少なくとも一部分を通って延在して、第2の素子2の本体内に配設された（例えば、素子2の接合層11内に配設された）トレース36と接続してよい。他の実施形態では、相互接続部66は、例えば、トレース36又は他の導体が、第2の素子2の上面に（例えば、素子2の接合層11の上面に）配設される実施形態では、第2の素子2を貫通しなくてよい。導電トレース36及び相互接続66は、1つ以上のボンドパッド65のそれぞれに対して別個に設けられ得る。いくつかの実施形態では、1つ以上のボンドパッド65は、第1の素子3内の集積デバイス又は回路に接続してよく、したがって、界面を介して通信する相互接続部66又はトレース36と直接関連付けられていない。当然のことながら、上面68において複数のボンドパッド65と通信するトレース36及び相互接続部66は、第1の素子3と第2の素子2との間の界面に直接導体接合によって形成された任意の封止環（図示せず）から絶縁されるべきである。図2Lの接合構造物1は、空洞5を含むが、他の実施形態では、空洞は設けられなくてよい。様々な実施形態では、例えば、集積デバイスは、素子3（又は素子2）の表面若しくはその付近、及び／又は素子3（又は素子2）の本体内に配設され得る。

20

【0042】

有利には、界面構造体10を通って相互接続部66を設けることにより、図2J及び図2Kに示す構成と比較して、接合構造物1の総フットプリントを低減できる。例えば、界面構造体10を通って相互接続部66をルーティングすることによって、図2J及び図2Kのレッジ領域を除去でき、除去したレッジ領域ごとに横方向フットプリントをd<sub>x</sub>だけ低減できる。様々な実施形態において、図2L及び図2Mの実施形態は、ウエハ当たりの接合構造物の数を3%～125%の範囲で増加させ得る。例えば、1つのボンドパッドレッジ領域67を有する構造物1では、図2L～図2Mの実施形態は、ウエハ当たりの接合構

30

40

50

造物の数を 3 % ~ 3 0 % の範囲の量だけ増加させ得る。2 つのボンドパッドレッジ領域 6 7 を有する構造物 1 では、図 2 L ~ 図 2 M の実施形態は、ウエハ当たりの接合構造物の数を 7 % ~ 6 0 % の範囲の量だけ増加させ得る。3 つのボンドパッドレッジ領域 6 7 を有する構造物 1 では、図 2 L ~ 図 2 M の実施形態は、ウエハ当たりの接合構造物の数を 1 0 % ~ 9 0 % の範囲の量だけ増加させ得る。4 つのボンドパッドレッジ領域 6 7 を有する構造物 1 では、図 2 L ~ 図 2 M の実施形態は、ウエハ当たりの接合構造物の数を 1 6 % ~ 1 2 5 % の範囲の量だけ増加させ得る。

#### 【 0 0 4 3 】

本明細書に開示される様々な実施形態では、接合構造物 1 の上面にボンドパッド 6 5 を有する接合構造物 1 は、ウエハ当たりのダイの数 ( d p w ) ( 例えは、ウエハ当たりの接合構造物 ) を有益に増加させ得、ダイ又は接合構造物の 1 辺、2 辺、3 辺、及び / 又は 4 辺からレッジ又はレッジ領域を除去する。更に、図 2 N は、ボンドパッドレッジが接合構造物又はダイの 1 边、2 边、3 边、又は 4 边で除去された接合構造物の、ダイ面積に対するウエハ当たりの接合構造物又はダイの数の増加率をプロットするチャートである。図 2 N に示すように、例えは、4 边からレッジが除去された接合構造又はダイのウエハ当たりの接合構造物又はダイの数の増加率は、1 边からのみ除去されたものと比較して高い。

10

#### 【 0 0 4 4 】

図 2 O は、別の実施形態による、接合構造物 1 の概略側断面図である。特に断らない限り、図 2 O に示す構成要素は、図 2 L ~ 図 2 M の同様の番号が付された構成要素と同じであってよい、又は概して類似であってよい。図 2 L では、第 1 及び第 2 の素子 3 、 2 は、概ね横方向に同一の広がり有するものとして示されており、例えは、図 2 L に示すような素子 3 、 2 の全幅はほぼ同一である。しかしながら、図 2 L とは異なり、図 2 O では、素子のうちの 1 つ ( 例えは、下部、つまり第 2 の素子 2 ) は、第 1 の素子 3 よりも大きくてよい。例えは、図 2 O に示すように、第 2 の素子は、第 1 の素子 3 の外縁を越えて横方向に延在する棚部 6 9 を有し得る。それでもなお、接合構造物 1 の総フットプリントは、図 2 J ~ 図 2 K に示す構造物 1 と比較して比較的小さくてよい。例えは、棚部 6 9 は、図 2 O に示すように、距離 d だけ第 1 の素子 3 の外縁を超えてわずかに延在してよい。距離 d は十分に小さくてよく、その結果、第 1 及び第 2 の素子 3 、 2 を棚部 6 9 上のパッドにワイヤボンディングすることは困難又は不可能であり得る。いくつかの実施形態では、第 2 の素子 2 の側域、つまりフットプリントは、第 1 の素子 3 の側域、つまりフットプリントと同一であってよい ( 図 2 L を参照 ) 。図 2 O では、第 2 の素子 2 の側域、つまりフットプリントは、第 1 の素子 3 の面積又は側方フットプリントの 1 0 0 % ~ 1 2 5 % の範囲内、1 0 0 % ~ 1 1 0 % の範囲内、又は 1 0 0 % ~ 1 0 5 % の範囲内であり得る。様々な実施形態では、棚部 6 9 上にはボンドパッドが設けられなくてよい。実際、棚部 6 9 が存在する程度では、非常に狭く、不十分に幅広であって、ワイヤボンディングの余地がない場合がある。他の実施形態では、棚部 6 9 は、上部素子 3 の上面のボンドパッドに加えて、ボンドパッドを含んでよい。様々な実施形態では、棚部 6 9 の全体が、接合層 1 1 によって被覆され得る。いくつかの実施形態では、追加層、例えは、パッシベーション層が接合層の上に設けられ得、棚部 6 9 の上を含む素子 2 の全体に延在できる。図示していないが、パッシベーション層は、第 1 の素子 3 のフットプリント内のトレース 3 6 に接続された導体によって穿孔されてよいが、露出した棚部 6 9 内の導体によっては穿孔されない。図 2 J 、図 2 L 、及び図 2 O のトレース 3 6 は、接合層 1 1 内に配設されているものとして示すが、トレース 3 6 は、素子 2 の本体 ( 例えは、半導体素子のバルクシリコン又は半導体材料 ) 内に配設され得ることを理解されたい。

20

30

40

#### 【 0 0 4 5 】

相互接続部 6 6 は、任意の好適な方法で形成され得る。いくつかの実施形態では、相互接続 6 6 は、第 1 及び第 2 の素子 3 、 2 の接合前に形成され得る。他の実施形態では、相互接続 6 6 は、第 1 及び第 2 の素子 3 、 2 の接合後に形成され得る。いくつかの実施形態では、相互接続部 6 6 は、例えは、相互接続部 6 6 が最初に第 1 の素子 3 内に埋め込まれ、その後の除去又は薄型化プロセス ( エッティング、研削など ) によって露出し得る、ビアフ

50

アーストプロセスで形成され得る。他の実施形態では、相互接続部は、第1の素子3内にトレンチが画定され（例えば、エッチングされ）、絶縁ライナー及び金属相互接続部66がトレンチ内に堆積される、ビアラストプロセスで形成され得る。相互接続部66は、図2Lの第1の素子3の厚さを通って延在するものとして示しているが、他の構成では、相互接続部66はまた、又は代替的に、第2の素子2を通って延在してよい。更に、上述したように、いくつかの実施形態では、相互接続部66は、界面構造体10に沿って配設された導電性界面特徴部を介して第2の素子2と通信できる。いくつかの実施形態では、相互接続部66は、界面構造体10を通って延在し得、かつ／又はその内部に画定され得、その結果、相互接続部66は、界面構造体10の導電性界面特徴部の少なくとも一部を形成できる。例えば、いくつかの実施形態では、相互接続66は、接合前に第1の素子3の下面で露出され得、第2の素子2の対応する導電性特徴部（それ自体が別の相互接続を備えてよい）に直接接合し得る。上述の導電性特徴部と同様に、様々な実施形態では、バリア、シード、及び／又は絶縁層は、トレンチ及び／又は誘電体のビアを裏打ちでき、相互接続部36は、任意のかかるライナー上に設けられ得る。

#### 【0046】

図3は、界面構造体10の導電性界面特徴部12と接続されたクラック止め13を含む接合構造物1の一部の概略側断面図である。クラック止め13は、ダイ内のバックエンドオブライン相互接続構造を通って垂直に接続するにつれて、交互に幅広セグメント及び細幅セグメントを含み、したがって、半導体素子（例えば、第2の素子2）のうちの1つのクラックの伝搬を防止又は低減できる。機能デバイスダイのバックエンドオブライン（BEDOL）相互接続層に低K誘電体を導入することにより、誘電体の耐破壊特性が実質的に低減されてよく、シリコンの耐破壊特性と同等であっても、又は著しく低くてもよい。したがって、ダイの縁部において低K誘電体層のクラック及び層間剥離を防止することは、チップパッケージの相互作用から生じる応力下では困難であり得る。有利には、チップの縁部でのクラックは、チップの縁部付近の耐破壊性を増加させることによってクラッカー止めとして機能する、パターン付きの金属界面構造体（例えば、クラック止め13）を、低K誘電体の外周の周囲に組み込むことによって低減され得る。

#### 【0047】

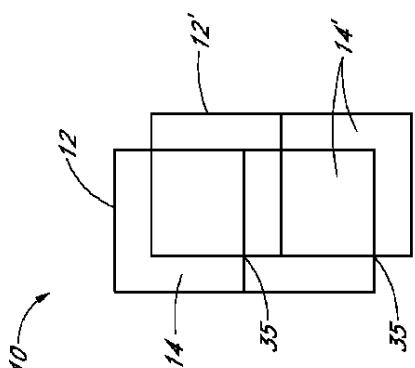

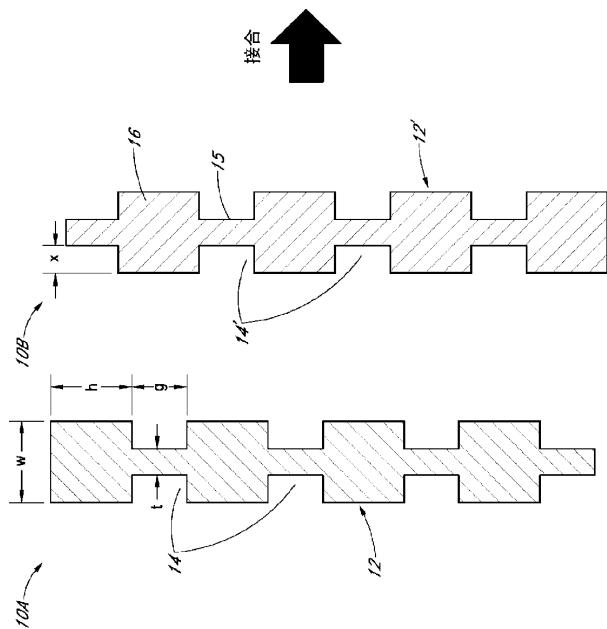

図4A～図4Cは、半導体素子3、2のそれぞれの対応する界面特徴部が互いに接合されたときの位置ずれに対する許容度を増加させる、界面構造体10の概略平面図である。いくつかの実施形態では、図4A～図4Cの接合構造体10は、隣接する半導体素子の対応する導電性界面特徴部12、12'が位置ずれしている場合に、有効な気体封止部を提供するように配置され得る。本明細書で説明するように、様々な実施形態において、界面構造体10は、第1の半導体素子3上に配設された第1の界面特徴部、及び第2の半導体素子2上に配設された第2の界面特徴部によって画定され得る。例えば、図4A～図4Cに示すように、第1の導電性界面特徴部12及び第1の非導電性界面特徴部14は、第1の半導体素子3上に配設され得る。第2の導電性界面特徴部12'及び第2の非導電性界面特徴部14'は、第2の半導体素子2上に配設され得る。第1及び第2の界面特徴部は、図1A～図2Bに関連して上述した材料を含み得る。例えば、様々な実施形態では、第1及び第2の導電性界面特徴部12、12'は、銅を含み得る。様々な実施形態では、第1及び第2の非導電性界面特徴部14、14'は、酸化シリコンを含み得る。

#### 【0048】

図1A～図2Bの接合構造物1と同様に、いくつかの実施形態では、図4A～図4Cの界面構造体10は、空洞5及び／又は集積デバイス4の周囲に延在して、事実上の環状パターンを画定し得、例えば、導電性特徴部は、事実上の環状のパターンを画定する完全な環又は不完全な環を区切り得る。事実上の環状パターンで界面構造体10を配設することにより、接合構造物1に入る気体から空洞5及び／又は集積デバイス4を有利に封止できる。しかしながら、他の実施形態では、図4A～図4Cの界面構造体10は、気体封止以外の用途、又はそれに追加した用途のための界面として使用され得る。例えば、図4A～図4Cの界面構造体10は、導電性特徴部が互いに接合されたときの位置ずれを考慮するた

めに、任意の用途で使用され得る。いくつかの実施形態では、図 4 A ~ 図 4 C の界面構造体 10 は、半導体素子間で 1 つ以上の直接的な電気的接続及び / 又は機械的接続を提供できる。様々な実施形態では、図 4 A ~ 図 4 C の界面構造体 10 は、集積デバイス 4 の周囲に環状パターンで配設されても、配設されなくてもよい。いくつかの実施形態では、例えば、界面構造体 10 は、図 7 C に関して以下に説明する相互接続部 20 などのために、半導体素子の対応する外面の複数の不連続な位置に配設されてよい。かかる実施形態では、界面構造体 10 は、半導体素子間の電気的相互接続部として機能し得る。第 1 及び第 2 の界面特徴部は、様々な方法で互いに接合され得る。いくつかの実施形態では、第 1 及び第 2 の界面特徴部は、介在する接着剤を用いずに、かつ圧力及び / 又は温度を付加せずに、互いに直接接合され得る。

10

#### 【 0 0 4 9 】

界面構造体 10 に直接接合を用いる実施形態では、第 1 及び第 2 の界面特徴部の接合面が調製され得る。例えば、第 1 の導電性界面特徴部 12 及び第 1 の非導電性界面特徴部 14 の接合面は、介在する接着剤を用いずに、かつ圧力又は電圧を付加せずに、第 2 の導電性界面特徴部 12' 及び第 2 の非導電性界面特徴部 14' の対応する接合面に直接接合され得る。これらの接合面では、研磨又は平坦化、活性化、及び好適な種での終端処理が行われ得る。接合面は接触させられて、圧力を付加せずに直接接合を形成し得る。いくつかの実施形態では、半導体素子 3、2 を加熱して、接合、例えば、導電性特徴部間の接合を強化し得る。開示された実施形態のそれぞれと併せて使用される直接接合プロセスの更なる詳細は、米国特許第 7,126,212 号、同第 8,153,505 号、同第 7,622,324 号、同第 7,602,070 号、同第 8,163,373 号、同第 8,389,378 号及び同第 8,735,219 号を通して、並びに米国特許出願第 14/835,379 号、同第 62/278,354 号、同第 62/303,930 号及び同第 15/137,930 号を通して見出すことができ、それらの各々の内容は、参照によりそのままあらゆる目的で本明細書に援用される。

20

#### 【 0 0 5 0 】

図 4 A の構造体 10 では、導電性界面特徴部 12、12' は比較的薄型であり、その結果、研磨からのディッシングが回避され、金属間直接接合が促進され得る。しかしながら、それぞれの界面特徴部が横方向に位置ずれしている場合、特徴部 12、12' の間の導電性接合部 35 は比較的小さい。図 4 A に示す導電性接合部 35 は、不十分な気体封止（及び / 又は不十分な電気的接続）をもたらし得る、隔絶された接触領域を含んでよい。

30

#### 【 0 0 5 1 】

したがって、図 4 B ~ 図 4 C に示すように、導電性界面特徴部 12、12' は、電気的接続の十分な導電性を確保し、また、より良好な拡散バリア (diffusion barrier) を提供するように、十分に幅広に作成され得る。図 4 B ~ 図 4 C の厚型導電性特徴部 12、12' は、有利には、より大きい導電性接合部 35 を可能にし、また、界面構造体 10 の気体封止能力（及び / 又は電気的接続）も改善する。図 4 B では、例えば、導電性特徴部 12、12' の厚さは、接合手順の最大位置ずれ許容度よりも厚くすることができる。したがって、接合手順が T の位置ずれ許容度を有する場合、導電性界面特徴部 12、12' の横方向厚さは、T 以上であり得る。様々な直接接合手順において、例えば、位置ずれ許容度 T は、0.1 マイクロメートル ~ 2.5 マイクロメートルの範囲であり得る。導電性特徴部 12、12' の厚さ寸法を接合プロセスの最大位置ずれ許容度 T に等しい、又はそれを超えるように決定することにより、導電性接合部 35 は、確実に閉鎖構造を形成できる。

40

#### 【 0 0 5 2 】

図 4 C の実施形態では、導電性界面特徴部 12、12' の厚さは、介在する非導電性界面特徴部 14、14' が設けられる空間よりも大きくなるように選択され得る。したがって、図 4 C では、導電性特徴部 12 は、非導電性特徴部 14、14' よりも厚くなり得る。このように導電性特徴部 12 の寸法を決定することにより、導電性特徴部 12、12' は、連続界面に沿って確実に嵌合できる。したがって、図 4 B ~ 図 4 C の比較的厚い導電性特徴部 12、12' は、位置ずれが存在しても、接合中に導電性界面特徴部 12、12' 間に有効な

50

接続を提供でき、連続界面は、拡散に対する環状又はほぼ環状のバリアを提供できる。

【0053】

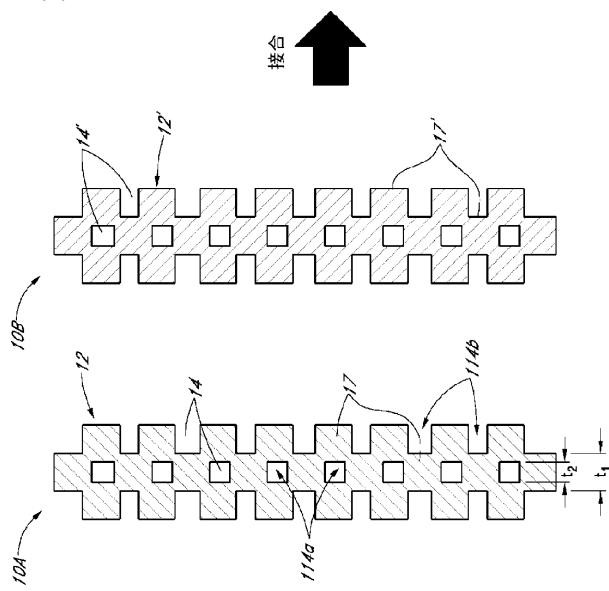

図5A～図5Dは、有効な金属拡散バリアを提供しつつ、各半導体素子3、2上の対応する界面特徴部10A、10Bが互いに接合されたときの位置ずれに対する許容度を増加させる界面構造体10の概略平面図である。図4A～図4Cに関連して上述したように、2つの対応する界面特徴部10A、10Bの接合（例えば、直接結合）時の位置ずれを考慮することは重要であり得る。界面特徴部10A、10Bは、第1及び第2の半導体素子3、2の外面上にそれぞれ配設され得る。界面特徴部10A、10Bは、1つ以上の非導電性界面特徴部14、14'内にも埋め込まれる、又はそれとも結合され得る、1つ以上の導電性界面特徴部12、12'を備え得る。いくつかの実施形態では、導電性界面特徴部12、12'は合わされて、介在する接着剤を用いずに直接接合され得る。いくつかの実施形態では、非導電性界面特徴部14、14'はまた、互いに直接結合され得る。他の実施形態では、素子は、接着剤を使用して接合され得る。導電性特徴部12、12'は、特徴部12、12'が互いに重複する領域に沿って導電性接合部35を画定し得る。

10

【0054】

位置ずれに対する許容度を増加させるために、導電性界面特徴部12、12'は、複数の細幅部分15と交互に配置され、それらと接続された複数の幅広部分16を含み得る。例えば、図5Aに示すように、各幅広部分16は、2つの細幅部分15の間に接続され得、各細幅部分15は、2つの幅広部分16の間に接続され得る。細幅部分15は、0.1マイクロメートル～25マイクロメートルの範囲の第1の幅tを有し得る。幅広部分は、t未満、かつ0.5マイクロメートル～50マイクロメートルの範囲の第2の幅wを有し得る。更に、図5Aに示すように、幅広部分16は、介在する非導電性界面特徴部14が配設され得る第1の距離gだけ互いに離隔され得、幅広部分16及び細幅部分15は端と端とで接続され得、細幅部分15は、第1の距離gと同一の長さを有し得る。第1の距離gは、0.1マイクロメートル～50マイクロメートルの範囲であり得る。薄型部分は、第2の距離hだけ互いから離隔され得、この距離はまた、幅広部分16の長さを構成してよい。第2の距離hは、0.2マイクロメートル～50マイクロメートルの範囲であり得る。更に、幅広部分16の最外縁部は、横方向オフセットxだけ細幅部分15の最外縁部に対してオフセットされ得、これは以下で説明するように、x方向における接合手順の最大位置ずれ許容度に対応し得る。横方向オフセットxは、0.1マイクロメートル～25マイクロメートルの範囲であり得る。

20

【0055】

有利には、幅広セグメント16は、上述のように、接合構造物1の気体封止能力を改善させるために設けられ得る。細幅セグメント14は、研磨により生じ得るディッシングの影響を低減するために設けられ得、それによって導体間直接接合を容易にする。図5Bは、それぞれの界面特徴部10A、10Bの位置ずれがほとんど又は全く存在しない、接合後の界面構造体10を示す。図5Bに示すように、導電性特徴部12、12'は、図5Aに示すようにy方向に半ピッチオフセットされて互いに完全に重複し、その結果、接合導電性領域は、大型の導電性接合部35において閉鎖経路を提供する。図5Bに示すように、位置ずれがほとんど又は全く存在しない場合、導電性特徴部12、12'は、導電性接合部35において横方向に、すなわち、横方向オフセットxと平行に完全に重複する。これは、幅広部分16の最外縁部の横方向オフセットが、接合手順の最大位置ずれ許容度xに対応するように選択され得るためである。例えば、特定の接合手順の横方向位置ずれ許容度xでは、第1の幅t及び第2の幅wは、 $x = (w - t) / 2$ の関係を満たすように選択され得る。接合中の長手方向位置ずれ許容度yでは、特定の接合手順に関して、第1の距離g及び第2の距離hは、 $y = (h - g) / 2$ の関係を満たすように選択され得る。これらの関係を満たすことにより、異なる半導体素子3、2の導電性特徴部12、12'の間の連続的な重複、つまり接合線を確保する。

30

【0056】

図5Cは、接合特徴部10A、10Bが位置ずれ許容度xだけ横方向に、また位置ずれ許

40

50

容度  $y$  だけ長手方向に位置ずれしているときの接合界面構造体 10 を示す。図 5 C に示すように、特定の接合手順について界面特徴部 10 A、10 B が  $x$  及び  $y$  だけ位置ずれしている場合であっても、結果として生じる接合界面構造体 10 は、導電性接合部 35 において導電性界面特徴部 12、12' の間に有意かつ連続的な重複を含み、拡散に対して事実上の環状拡散バリア、例えば、完全な環状又はほぼ環状のバリアを提供できる。

#### 【 0 0 5 7 】

図 5 D は、接合特徴部 10 A、10 B が、位置ずれ許容度  $x +$  第 1 の幅  $t$  だけ横方向に位置ずれしており、長手方向に  $(h - g) / 2$  未満だけ位置ずれしている場合の接合界面構造体 10 を示す。図 5 D に示すように、 $(h - g) / 2$  未満の（例えば、 $y$  に平行な）長手方向の位置ずれが存在する場合、図 5 D の接合界面構造体 10 は、接合手順の位置ずれ許容度  $x$  よりも更に大きい横方向の位置ずれに対応できる。これは、 $(h - g) / 2$  未満の長手方向の位置ずれが存在する場合、細幅部分 15 の追加の幅が、導電性接合部 35 における追加の接合領域に寄与し得るためである。重複接合領域は、図 5 C より横方向に細幅であるものの、金属間接合界面は連続的なままであり、例えば酸化物よりも良好な拡散バリアを提供する。

10

#### 【 0 0 5 8 】

図 6 A ~ 図 6 B は、別の実施形態による、各半導体素子 3、2 上の対応する界面特徴部 10 A、10 B が互いに接合されたときの位置ずれに対する許容度を増加させる界面構造体 10 の概略平面図である。図 6 A ~ 図 6 B の実施形態では、非導電性界面特徴部 14、14' は、複数の内側領域 114 a と、複数の外側領域 114 b と、を備え得る。内側領域 114 a は、導電性界面特徴部 12、12' によって（水平面内で）完全に包囲され得る。図示した実施形態では、複数の導電性界面特徴部 12、12' は、非導電性界面領域 14、14' の内側領域 114 a の周囲に（例えば、周囲一面に）配設される多数のブロック 17 を備え得る。非導電性界面領域 14、14' の外側領域 114 b は、隣接する外側ブロック 17 間の間隙に配設され得る。

20

#### 【 0 0 5 9 】

いくつかの実施形態では、ブロック 17 の第 1 の幅  $t_1$  は、内側領域 114 a 及び / 又は外側領域 114 b の第 2 の幅  $t_2$  より大きくてよい。例えば、いくつかの実施形態では、ブロック 17 の第 1 の幅  $t_1$  は、0.2 マイクロメートル ~ 2.5 マイクロメートルの範囲であり得る。内側領域 114 a 及び / 又は外側領域 114 b の第 2 の幅  $t_2$  は、0.1 マイクロメートル ~ 2.0 マイクロメートルの範囲であり得る。ブロック 17 の寸法を領域 114 a、114 b よりも大きくすることにより、図 6 B の接合界面構造体 10 に示すように、導電性特徴部 12、12' が有意な重複導電性接合部 35 を有することを可能にし得る。

30

#### 【 0 0 6 0 】

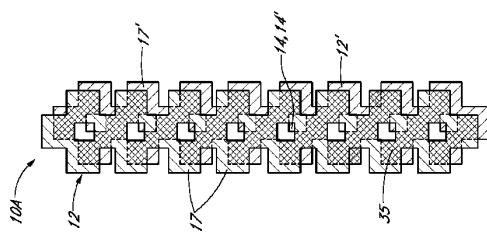

図 7 A は、非導電性界面特徴部 14 の複数の内側領域 114 a が格子内に配設されている（格子に包囲されている）、導電性界面特徴部 10 A の概略平面図である。例えば、図 7 A に示す界面特徴部 10 A は、交差する導電性界面特徴部 12 によって画定される交差格子構造体を備える。図 7 B は、2 つの界面特徴部 10 A、10 B を接合することによって形成された接合界面構造体 10 の概略平面図である。図 7 A に示すように、導電性特徴部 12 は、細幅導電セグメント 19 によって相互接続された複数の幅広ブロック 18 を含み得る。幅広ブロック 18 は、改善された気体封止能力を提供でき、細幅導電性セグメント 19 は、研磨手順によるディッシングの悪影響を回避するために設けられ得、それにより、金属間直接接合を容易にする。図 7 A では、ブロック 18 及びセグメント 19 は、導電性特徴部 12 が互いに垂直に配設される格子内に配置されている。しかしながら、他の実施形態では、特徴部 12 は、互いにに対して非垂直に配置され得る。

40

#### 【 0 0 6 1 】

図 7 A ~ 図 7 B では、ブロック 18 は、隣接するブロック 18 間に配設された間隙 G の第 2 の幅  $t_2$  よりも大きい第 1 の幅  $t_1$  を有し得る。例えば、いくつかの実施形態では、第 1 の幅  $t_1$  は、0.2 マイクロメートル ~ 5.0 マイクロメートルの範囲であり得る。第 2 の

50

幅  $t_2$  は、0.1 マイクロメートル～2.5 マイクロメートルの範囲であり得る。図 7 B に示すように、ブロック 18 をこのような方法で離隔させることにより、導電性接合部 35 に沿った導電性特徴部 12 間の大きな重複領域を有益に可能にし、このことは、接合構造物 1 を気体から封止するのに有益であり得る。

#### 【0062】

図 7 A～図 7 B に示す格子は、交差する導電線の格子を含むが、他の実施形態では、格子は、湾曲形状、周期的形状、又は不規則形状を含み得る。例えば、いくつかの実施形態では、格子は、相互接続された多角形のハニカム構造を含み得る。いくつかの実施形態では、格子は、複数の三角形、ヘリンボーンパターン、又は任意の他の好適な繰り返し形状の格子を含み得る。

10

#### 【0063】

図 7 C は、非導電性界面特徴部 14 の内側領域内 114a に配設された複数の電気的相互接続部 20 を有する、図 7 B の接合界面構造体 10 の概略平面図である。図 2 B に関連して上述したように、追加の導電性電気的相互接続部 20 を界面構造体 10 に組み込むことは有利であり得る。これにより、接合構造物 1 は、半導体素子 3、2 間で多数の信号線、電力線、及び / 又は接地線に気体封止及び電気通信を提供することが可能になる。図 7 C の実施形態では、例えば、導電性界面特徴部 12 及び非導電性界面特徴部 14 は、構造体に入る気体に対する効果的なバリアとして機能する、半導体素子 3、2 間の機械的接続を提供できる。導電性特徴部 12 は、幅よりも長い長さを有する細長い特徴部を備え得る。電気的相互接続部 20 は、内側領域 114a 内に配設され得、導電性特徴部 12 から電気的に絶縁され得る。相互接続部は、非導電性特徴部 14 を通って第 1 の半導体素子 3 から第 2 の半導体素子 2 まで垂直に延在して、半導体素子 3、2 間に電気通信を提供できる。2 つの導電性特徴部 12 の重複及び接合によって作り出される、事実上の環状パターン (annular pattern)、例えば、完全な環状又はほぼ環状のパターンもまた、2 つの半導体素子 3、2 間の追加的な、又は唯一の電気的接続として機能し得ることが理解されるであろう。

20

#### 【0064】

したがって、図 4 B～図 7 C の実施形態では、第 1 の半導体素子 3 は、第 1 の半導体素子 3 の外面の導電線から形成された、繰り返し形状の第 1 のパターンを含み得る。第 1 のパターンは、第 2 の導電性界面特徴部 12 から第 1 の間隔だけ離隔された第 1 の導電性界面特徴部 12 を含み得、第 1 の非導電性界面特徴部 14 は、第 1 及び第 2 の導電性界面特徴部 12 間に配設される。第 1 の導電性界面特徴部 12 は、第 1 の間隔よりも大きい第 1 の幅を有し得る。第 2 の半導体素子 2 は、第 2 の半導体素子 2 の外面の導電線から形成された、繰り返し形状の第 2 のパターンを含み得る。第 2 のパターンは、第 4 の導電性界面特徴部 12 から第 2 の間隔だけ離隔された第 3 の導電性界面特徴部 12 を含み得、第 2 の非導電性界面特徴部 14 は、第 3 及び第 4 の導電性界面特徴部 12 間に配設される。第 3 の導電性界面特徴部 12 は、第 2 の間隔よりも大きい第 2 の幅を有し得る。第 1 及び第 2 の導電性界面特徴部 12 は、第 3 及び第 4 の導電性界面特徴部 12 に接合されて、界面構造体 10 を画定し得る。第 1 及び第 2 のパターンは互いに対して横方向にオフセットされてよいが、接合された第 1 及び第 2 のパターンは、それでもなお、界面構造体 10 に沿って連続的な導電性接合領域 35 を区切り得る。

30

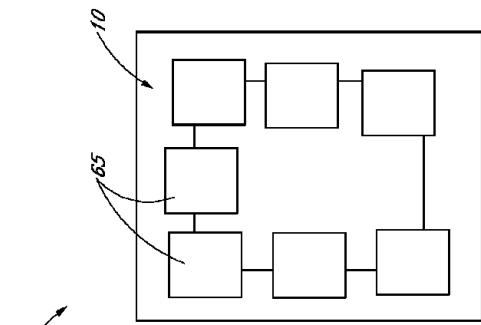

#### 【0065】

図 8 は、様々な実施形態による、1 つ以上の接合構造物 1 を組み込んだ電子システム 80 の概略図である。システム 80 は、モバイル電子デバイス（例えば、スマートフォン、タブレットコンピューティングデバイス、ラップトップコンピュータなど）、デスクトップコンピュータ、自動車又は自動車の構成要素、ステレオシステム、医療デバイス、カメラ又は任意の他の好適な種類のシステムなどの、任意の好適な種類の電子デバイスを備えることができる。いくつかの実施形態では、電子システム 80 は、マイクロプロセッサ、グラフィックプロセッサ、電子記録デバイス又はデジタルメモリを備えることができる。システム 80 は、例えば、1 つ以上のマザーボードによって、システム 80 に機械的及び電

40

50

気的に接続された 1 つ以上のデバイスパッケージ 8 2 を含むことができる。各パッケージ 8 2 は、1 つ以上の接合構造物 1 を備えることができる。図 8 に示すシステム 8 0 は、本明細書に示し、記載した接合構造物 1 及び関連付けられた界面構造体 1 0 のいずれかを備え得る。

【 0 0 6 6 】

一実施形態では、を備える接合構造物が開示される。接合構造物は、第 1 の界面特徴部を有する第 1 の素子と、第 2 の界面特徴部を有する第 2 の素子と、を含み得る。接合構造物は、第 1 の素子若しくは第 2 の素子に接合された、又はそれと共に形成された集積デバイスを含み得る。第 1 の界面特徴部は、第 2 の導電性界面特徴部に直接接合されて、界面構造体を画定し得る。界面構造体は集積デバイスの周囲に配設されて事実上の閉鎖プロファイルを画定し、第 1 及び第 2 の素子を接続できる。事実上の閉鎖プロファイルは、外部環境から内部領域へと拡散する気体から、接合構造物の内部領域を実質的に封止できる。

10

【 0 0 6 7 】

別の実施形態では、接合構造物は、第 1 の素子と、第 2 の素子と、を備える。接合構造物は、第 1 の素子又は第 2 の素子に接合された、又はその内部に形成された集積デバイスを含み得る。界面構造体は、第 1 の素子と第 2 の素子との間に配設され得る。界面構造体は、第 1 の素子から第 2 の素子に向かう方向に延在する第 1 の導電性界面特徴部と、第 1 の素子から第 2 の素子に向かう方向に延在する第 2 の導電性界面特徴部と、第 1 の導電性界面特徴部と第 2 の導電性界面特徴部との間に横方向に配設された、固体状態の非導電性界面特徴部と、を備え得る。界面構造体は集積デバイスの周囲に配設されて事実上の閉鎖プロファイルを画定し、第 1 の素子及び第 2 の素子を接続できる。

20

【 0 0 6 8 】

別の実施形態では、接合構造物は、第 1 の素子と、第 2 の素子と、を備える。集積デバイスは、第 1 の素子若しくは第 2 の素子に結合され得る、又はそれと共に形成され得る。界面構造体は、第 1 の素子と第 2 の素子との間に配設され得、界面構造体は、第 1 の素子から第 2 の素子に向かう方向に延在する。界面構造体は、第 1 の素子から第 2 の素子に向かう方向に延在する第 1 の細長い導電性界面特徴部と、第 1 の素子から第 2 の素子に向かう方向に延在する第 2 の細長い導電性界面特徴部と、を含み得る。第 1 及び第 2 の細長い導電性界面特徴部は、第 1 の素子から第 2 の素子への方向に延在する、介在する非導電性界面特徴部によって離隔され得る。第 1 及び第 2 の細長い導電性界面特徴部のそれぞれは、幅よりも長い長さを有し得る。電気的相互接続部は、集積デバイスと電気通信でき、電気的相互接続部は、第 1 の素子から第 2 の素子まで延在する。電気的相互接続部は、第 1 及び第 2 の導電性界面特徴部間の介在する非導電性界面特徴部を通って延在し得る。

30

【 0 0 6 9 】

別の実施形態では、接合構造物は、第 1 の素子の外面の導電線から形成された、第 1 の繰り返し形状のパターンを有する第 1 の素子を備える。第 1 のパターンは、第 2 の導電性界面特徴部から第 1 の間隔だけ離隔された第 1 の導電性界面特徴部を含み得、第 1 の非導電性界面特徴部は、第 1 及び第 2 の導電性界面特徴部間に配設される。第 1 の導電性界面特徴部は、第 1 の間隔よりも大きい第 1 の幅を有し得る。接合構造物は、第 2 の素子の外面の導電線から形成された、第 2 の繰り返し形状のパターンを有する第 2 の素子を備え得る。第 2 のパターンは、第 4 の導電性界面特徴部から第 2 の間隔だけ離隔された第 3 の導電性界面特徴部を備え得る。第 2 の非導電性界面特徴部は、第 3 及び第 4 の導電性界面特徴部間に配設され得、第 3 の導電性界面特徴部は、第 2 の間隔よりも大きい第 2 の幅を有する。第 1 及び第 2 の導電性界面特徴部は、第 3 及び第 4 の導電性界面特徴部に接合されて、界面構造体を画定し得る。第 1 及び第 2 のパターンは互いにに対して横方向にオフセットされ得るが、界面構造体に沿って連続的な導電性接合領域を区切る。

40

【 0 0 7 0 】

別の実施形態では、接合構造物が開示される。接合構造物は、第 1 の素子と、第 2 の素子と、を含み得る。集積デバイスは、第 1 の素子若しくは第 2 の素子に結合され得る、又はそれと共に形成され得る。界面構造体は、第 1 の素子と第 2 の素子との間に配設され得る

50

。界面構造体は、集積デバイスを横方向に包囲する第1の導電性界面特徴部を備え得る。導電性界面特徴部は、第1の素子と第2の素子との間に連続的に延在して、2つの素子間に電気的接続、機械的接続、又は熱的接続のうちの少なくとも1つを形成できる。非導電性界面特徴部は、第1の素子と第2の素子との間に連続的に延在し得る。

【0071】

別の実施形態では、接合構造物は、第1の界面特徴部を有する第1の素子と、第2の界面特徴部を有する第2の素子と、を含み得る。第1の界面特徴部は、第2の界面特徴部に接合されて、界面構造体を画定し得る。導電トレースは、第2の素子の中又はその上に配設され得る。ボンドパッドは、第1の素子の上面に設けられ、導電トレースと電気通信し得る。集積デバイスは、第1の素子若しくは第2の素子に結合され得る、又はそれと共に形成され得る。

10

【0072】

別の実施形態では、接合構造物は、第1の界面特徴部を有する第1の素子と、第2の界面特徴部を有する第2の素子と、を備え得る。第1の界面特徴部は、介在する接着剤を用いずに第2の界面特徴部に接合されて、界面構造体を画定し得る。ボンドパッドは、第1の素子の上面に配設され得る。集積デバイスは、第1の素子若しくは第2の素子に結合され得る、又はそれと共に形成され得る。電気的相互接続部は、ボンドパッドから第1の素子を通って延在して、集積デバイスに電気的に接続できる。

【0073】

別の実施形態では、接合構造物を形成する方法が開示される。本方法は、第1の界面特徴部を有する第1の素子と、第2の界面特徴部を有する第2の素子と、を提供することを含み得る。導電トレースは、第2の素子の中又はその上に配設され得る。本方法は、第1の界面特徴部と、第2の界面特徴部とを接合することを含み得る。ボンドパッドは、第1の素子の上面に配設され、導電トレースと電気的通信できる。集積デバイスは、第1の素子若しくは第2の素子に結合され得る、又はそれと共に形成され得る。

20

【0074】

開示された実施形態と先行技術に対して達成される利点とを要約する目的で、特定の目的及び利点が本明細書に記載されている。当然のことながら、任意の特定の実施形態に従つて、必ずしも全てのこののような目的又は利点が達成されない場合があることを理解されたい。したがって、例えば、当業者であれば、開示された実装形態が、本明細書で教示又は示唆され得る他の目的又は利点を必ずしも達成せずに、本明細書で教示又は示唆されるような1つの利点又は利点の群を達成又は最適化する方法で、具現化又は実施され得ることを認識するであろう。

30

【0075】

これらの実施形態の全てが本開示の範囲内にあることが意図されている。これら及び他の実施形態は、添付の図面を参照した実施形態の以下の詳細な説明から当業者には容易に明らかになり、特許請求の範囲は、開示されたいずれかの特定の実施形態に限定されない。本明細書ではこの特定の実施形態及び実施例が開示されているが、開示された実装形態は、具体的に開示された実施形態を超えて他の代替的な実施形態及び/又はそれらの使用と明らかな変更及び均等物とに及ぶことが当業者によって理解されるであろう。加えて、いくつかの変形例が詳細に示され説明されているが、本開示に基づいて、当業者には他の変更が明白であろう。また、実施形態の特定の特徴及び態様の様々な組み合わせ又は部分的組み合わせが作製されてもよく、依然として範囲内にあり得ることが企図される。開示された実施形態の様々な特徴及び態様を、開示された実装形態の様々なモードを形成するために、互いに組み合わせるか又は互いに置換することができることを理解されたい。したがって、開示された本明細書における主題の範囲は、上述した特定の開示された実施形態によって限定されるべきではなく、以下の特許請求の範囲の正読によってのみ決定されるべきであることが意図されている。

40

50

【図面】

【図 1 A】

【図 1 B】

10

【図 1 C】

【図 1 D】

30

40

50

【図 1 E】

【図 1 F】

10

【図 1 G】

【図 1 H】

20

【図 1 I】

【図 1 J】

30

40

50

【図 1 K】

【図 2 A】

FIG. 2A

10

【図 2 B】

FIG. 2B

30

【図 2 C】

FIG. 2C

40

10

10

50

【図 2 D】

【図 2 E】

FIG. 2E

10

20

【図 2 F】

FIG. 2F

【図 2 G】

FIG. 2G

30

40

50

【図 2 H】

【図 2 I】

10

20

FIG. 2I

【図 2 J】

FIG. 2J

【図 2 K】

FIG. 2K

30

40

50

1

5

10

2

1

10

65

67

1

10

65

67

10

65

67

Δx

【図 2 L】

FIG. 2L

【図 2 M】

FIG. 2M

10

20

【図 2 N】

ダイヤ面積に対するウエハ当たりのダイの増加量( $\text{cm}^2$ )

【図 2 O】

FIG. 2O

30

40

50

【図3】

FIG. 3

10

【図4 A】

FIG. 4A

20

【図4 B】

FIG. 4B

30

【図4 C】

FIG. 4C

40

50

【図 5 A】

【図 5 B】

FIG. 5B

10

【図 5 C】

FIG. 5C

20

【図 5 D】

FIG. 5D

30

40

50

【図 6 A】

【図 6 B】

FIG. 6B

10

【図 7 A】

FIG. 7A

【図 7 B】

FIG. 7B

20

30

40

50

【図 7 C】

【図 8】

FIG. 8

10

20

30

40

50

## フロントページの続き

(51)国際特許分類 F I

B 8 1 C 3/00 (2006.01)

H 0 1 L 21/3205(2006.01)

H 0 1 L 21/768 (2006.01)

H 0 1 L 23/522 (2006.01)

(33)優先権主張国・地域又は機関

米国(US)

## 早期審査対象出願

弁理士 倉澤 伊知郎

(74)代理人 100130937

弁理士 山本 泰史

(74)代理人 100162824

弁理士 石崎 亮

(72)発明者 エンクイスト ポール エム

アメリカ合衆国 ノースカロライナ州 27713 ダーラム カールトン クロッシング ドライブ

4715

(72)発明者 ワン リヤン

アメリカ合衆国 カリフォルニア州 94560 ニューアーク ソートン アベニュー 6125

アパートメント エイ

(72)発明者 カトカール ラジェッシュ

アメリカ合衆国 カリフォルニア州 95134 サンノゼ オーチャード パークウェイ 3025

(72)発明者 デラクルーズ ハビエル エイ

アメリカ合衆国 カリフォルニア州 95134 サンノゼ オーチャード パークウェイ 3025

(72)発明者 シタラム アルカルグド アール

アメリカ合衆国 カリフォルニア州 95134 サンノゼ オーチャード パークウェイ 3025

審査官 井上 和俊

(56)参考文献 特開2015-100886 (JP, A)

米国特許出願公開第2004/0259325 (US, A1)

米国特許出願公開第2013/0187245 (US, A1)

米国特許出願公開第2016/0002029 (US, A1)

国際公開第2014/074403 (WO, A1)

特開2008-130915 (JP, A)

特開平10-112517 (JP, A)

特開2009-238905 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

B 8 1 B 7 / 0 2

H 0 1 L 2 5 / 0 6 5

H 0 1 L 2 1 / 6 0

B 8 1 C 3 / 0 0

H 0 1 L 2 1 / 3 2 0 5