(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2008-0112281

(43) 공개일자 2008년12월24일

(51) Int. Cl.

*H01L 21/027* (2006.01)

(21) 출원번호 10-2008-7024655

(22) 출원일자 2008년10월08일

심사청구일자 없음

번역문제출일자 2008년10월08일

(86) 국제출원번호 PCT/US2007/005639

국제출원일자 2007년03월05일

(87) 국제공개번호 WO 2007/103343

국제공개일자 2007년09월13일

(30) 우선권주장

11/372,825 2006년03월09일 미국(US)

(71) 출원인

마이크론 테크놀로지, 임크.

미국 83716-9632 아이다호주 보이스 피.오. 박스

6 사우쓰 페드럴 웨이 8000

(72) 벌명자

아바트체브, 미르자페르, 케이.

미국 83716 아이다호주 보이스 사우스 만그로브

플레이스 6349

수브라마니안, 크루파카르, 무랄리

미국 83716 아이다호주 보이스 사우스 후크시아

플레이스 5541

조우, 바오수오

미국 83716 아이다호주 보이스 사우스 바바 스테

이션 웨이 4177

(74) 대리인

양영준, 백만기

전체 청구항 수 : 총 43 항

## (54) 집적 회로용 CD(Critical Dimension) 제어를 위한 트림 프로세스

## (57) 요 약

집적 회로용 CD(Critical Dimension) 제어를 위한 트림 프로세스를 채용하여 기판을 에칭하는 방법이 개시된다. 일 실시예에서, 에칭 방법은 타겟 층(120) 위에 제1 하드 마스크 층(130)을 제공하는 단계; 제1 하드 마스크 층(130) 위에 제2 하드 마스크 층(140)을 제공하는 단계; 제2 하드 마스크 층(140) 위에 포토레지스트 층(150)을 제공하는 단계; 포토레지스트 층(150)에 패턴을 형성하는 단계; 제2 하드 마스크 층(140)으로 패턴을 전사하는 단계; 및 제2 하드 마스크 층(140)의 상부의 포토레지스트 층(150)을 이용하여 제2 하드 마스크 층(140)을 트리밍하는 단계를 포함한다. 제2 하드 마스크 층(140)의 상면은 포토레지스트(150)에 의해 보호되고 타겟 층(120)은 트림 에칭 중에 오버라잉 제1 하드 마스크 층(130)에 의해 보호되며, 따라서 트림 에칭은 어그레시브 할 수 있다.

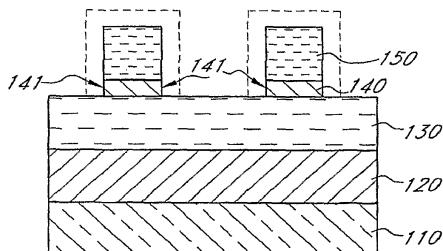

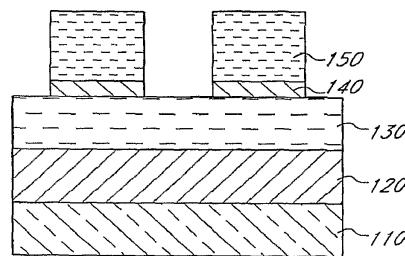

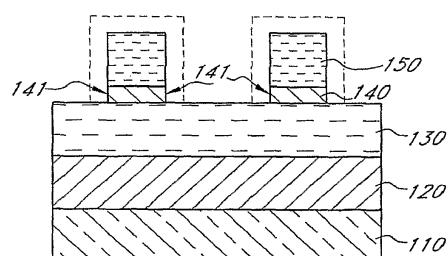

대 표 도 - 도1D

## 특허청구의 범위

### 청구항 1

집적 회로용 에칭(etching) 방법으로서,

타겟(target) 층 위에 제1 하드 마스크 층을 제공하는 단계;

상기 제1 하드 마스크 층 위에 제2 하드 마스크 층을 제공하는 단계;

상기 제2 하드 마스크 층 위에 레지스트(resist) 층을 제공하는 단계;

상기 레지스트 층에 패턴을 형성하는 단계;

상기 제2 하드 마스크 층으로 상기 패턴을 전사하는 단계; 및

상기 제2 하드 마스크 층의 상부의 상기 레지스트 층을 이용하여 상기 제2 하드 마스크 층을 트리밍(trimming)

하는 단계

를 포함하는 집적 회로용 에칭 방법.

### 청구항 2

제1항에 있어서,

상기 타겟 층은 절연체, 반도체, 및 금속으로 이루어진 그룹으로부터 선택된 물질을 포함하는 집적 회로용 에칭

방법.

### 청구항 3

제1항에 있어서,

상기 제1 하드 마스크 층은 비정질(amorphous) 탄소 층을 포함하는 집적 회로용 에칭 방법.

### 청구항 4

제1항에 있어서,

상기 제1 하드 마스크 층은 유기(organic) 하부층을 포함하는 집적 회로용 에칭 방법.

### 청구항 5

제1항에 있어서,

상기 제1 하드 마스크 층은 약 200Å부터 약 20,000Å까지의 두께를 갖는 집적 회로용 에칭 방법.

### 청구항 6

제1항에 있어서,

상기 제1 하드 마스크 층은 약 20:1 아래의 종횡비(aspect ratio)를 갖는 집적 회로용 에칭 방법.

### 청구항 7

제1항에 있어서,

상기 제2 하드 마스크 층은 무기(inorganic) 층을 포함하는 집적 회로용 에칭 방법.

### 청구항 8

제7항에 있어서,

상기 무기 층은 DARC(dielectric anti-reflective coating)를 포함하는 집적 회로용 에칭 방법.

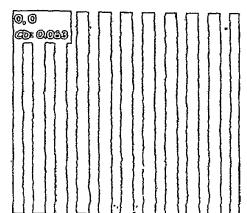

### 청구항 9

제7항에 있어서,

상기 무기 층은 실리콘 산질화물(oxynitride), 실리콘 산화물, 및 실리콘 질화물로 이루어진 그룹으로부터 선택된 물질을 포함하는 집적 회로용 에칭 방법.

### 청구항 10

제1항에 있어서,

상기 제2 하드 마스크 층은 실리콘 함유 유기 층을 포함하는 집적 회로용 에칭 방법.

### 청구항 11

제1항에 있어서,

상기 제2 하드 마스크 층은 약 50Å부터 약 1,000Å까지의 두께를 갖는 집적 회로용 에칭 방법.

### 청구항 12

제1항에 있어서,

상기 레지스트는 157nm 포토레지스트(photoresist), 193nm 포토레지스트, 및 248nm 포토레지스트로 이루어진 그룹으로부터 선택된 포토레지스트를 포함하는 집적 회로용 에칭 방법.

### 청구항 13

제1항에 있어서,

상기 패턴을 상기 제2 하드 마스크 층으로 전사하는 단계는 이방성(anisotropic) 에칭 프로세스를 사용하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 14

제13항에 있어서,

상기 이방성 에칭 프로세스를 사용하는 단계는, 플루오로카본(fluorocarbon) 기반의 플라즈마(plasma)를 사용하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 15

제1항에 있어서,

상기 제2 하드 마스크 층을 트리밍하는 단계는 상기 제2 하드 마스크 층의 피쳐(feature) 폭을 적어도 약 10Å 만큼 감소시키는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 16

제1항에 있어서,

상기 제2 하드 마스크 층을 트리밍하는 단계는 상기 레지스트 층 및 상기 제1 하드 마스크 층에 대하여 상기 제2 하드 마스크 층을 선택적으로 에칭하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 17

제1항에 있어서,

상기 제2 하드 마스크 층을 트리밍하는 단계는 상기 제1 하드 마스크 층의 에칭 속도보다 약 1에서 1,000배 사이의 더 빠른 속도로 상기 제2 하드 마스크 층을 에칭하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 18

제1항에 있어서,

상기 제2 하드 마스크 층을 트리밍하는 단계는 상기 제2 하드 마스크 층을 초당 약 1Å에서 10Å 사이의 속도로

에칭하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 19

제1항에 있어서,

상기 제2 하드 마스크 층을 트리밍하는 단계는 상기 제2 하드 마스크 층을 등방성으로(isotropically) 에칭하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 20

제1항에 있어서,

상기 제2 하드 마스크 층을 트리밍하는 단계는 상기 제2 하드 마스크 층을 플라즈마로 에칭하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 21

제20항에 있어서,

상기 플라즈마는 불소(fluorine) 함유 플라즈마를 포함하는 집적 회로용 에칭 방법.

### 청구항 22

제21항에 있어서,

상기 플라즈마는 NF<sub>3</sub> 기반의 플라즈마 및 SF<sub>6</sub> 기반의 플라즈마로 이루어진 그룹으로부터 선택된 플라즈마를 포함하는 집적 회로용 에칭 방법.

### 청구항 23

제1항에 있어서,

상기 제2 하드 마스크 층을 트리밍하는 단계는 습식(wet) 에칭 프로세스를 사용하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 24

제23항에 있어서,

상기 습식 에칭 프로세스를 사용하는 단계는, 완충(buffered) 산화물 에칭 프로세스를 사용하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 25

제24항에 있어서,

상기 완충 산화물 에칭 프로세스는 HF, NH<sub>4</sub>F, 및 H<sub>2</sub>O를 포함하는 에칭제(etchant)를 사용하는 것을 포함하는 집적 회로용 에칭 방법.

### 청구항 26

제1항에 있어서,

상기 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 상기 제1 하드 마스크 층으로 전사하는 단계를 더 포함하는 집적 회로용 에칭 방법.

### 청구항 27

제26항에 있어서,

상기 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 상기 제1 하드 마스크 층으로 전사하는 단계는 고밀도(high density) 플라즈마 에칭 프로세스를 사용하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 28

제27항에 있어서,

상기 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 상기 제1 하드 마스크 층으로 전사하는 단계는 상기 제2 하드 마스크 층의 에칭 속도보다 약 5배 이상 더 빠른 속도로 상기 제1 하드 마스크 층을 에칭하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 29

제26항에 있어서,

상기 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 상기 제1 하드 마스크 층으로 전사하는 단계는 황(sulfur) 및 산소 기반의 플라즈마를 사용하여 상기 제1 하드 마스크 층을 에칭하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 30

제29항에 있어서,

상기 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 상기 제1 하드 마스크 층으로 전사하는 단계는 10sccm에서 75sccm 사이의 황 이산화물을 프로세스 챔버(chamber)로 유입하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 31

제30항에 있어서,

상기 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 상기 제1 하드 마스크 층으로 전사하는 단계는 20sccm 및 60sccm 사이의 황 이산화물을 프로세스 챔버로 유입하는 단계를 포함하는 집적 회로용 에칭 방법.

### 청구항 32

제30항에 있어서,

상기 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 상기 제1 하드 마스크 층으로 전사하는 단계는 10sccm에서 100sccm 사이의 산소를 프로세스 챔버로 유입하는 단계를 더 포함하는 집적 회로용 에칭 방법.

### 청구항 33

제30항에 있어서,

상기 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 상기 제1 하드 마스크 층으로 전사하는 단계는 아르곤(argon)을 프로세스 챔버로 유입하는 단계를 더 포함하는 집적 회로용 에칭 방법.

### 청구항 34

제1항에 있어서,

상기 제2 하드 마스크 층 위에 BARC(bottom antireflective coating) 층을 제공하는 단계를 더 포함하는 집적 회로용 에칭 방법.

### 청구항 35

제34항에 있어서,

상기 BARC 층은 약 200Å부터 약 500Å까지의 두께를 갖는 집적 회로용 에칭 방법.

### 청구항 36

제1항에 있어서,

상기 집적 회로 디바이스는 메모리를 포함하는 집적 회로용 에칭 방법.

### 청구항 37

제1항에 있어서,

상기 집적 회로 디바이스는 마이크로프로세서를 포함하는 집적 회로용 에칭 방법.

### 청구항 38

제1항에 있어서,

상기 레지스트 층은 임프린트(imprint) 리소그래피(lithography) 레지스트를 포함하는 집적 회로용 에칭 방법.

### 청구항 39

집적 회로를 위한 마스킹(masking) 구조물로서,

타겟 층 위에 형성된 제1 하드 마스크 층;

상기 제1 하드 마스크 층 위에 형성된 제2 하드 마스크 층 - 상기 제2 하드 마스크 층은 상기 제1 하드 마스크 층을 커버하도록 구성된 마스킹 부분들을 갖는 패턴을 포함함 - ; 및

상기 제2 하드 마스크 층 위에 형성된 레지스트 층 - 상기 레지스트 층은 상기 제2 하드 마스크 층의 상기 마스킹 부분들에 대응하는 마스킹 부분들을 갖는 패턴을 포함함 -

을 포함하고,

상기 제2 하드 마스크 층의 상기 마스킹 부분들의 각각의 노출된 측면들은  $50\text{Å}_{\text{rms}}$  아래의 평균 거칠기(roughness)를 갖는 마스킹 구조물.

### 청구항 40

제39항에 있어서,

상기 제2 하드 마스크 층의 상기 마스킹 부분들의 각각의 노출된 측면들은 약  $10\text{Å}_{\text{rms}}$ 에서 약  $50\text{Å}_{\text{rms}}$  사이의 평균 거칠기를 갖는 마스킹 구조물.

### 청구항 41

제39항에 있어서,

상기 제2 하드 마스크 층의 상기 마스킹 부분들의 폭들은 상기 레지스트 층의 상기 대응하는 마스킹 부분들의 폭들과 실질적으로 동일한 마스킹 구조물.

### 청구항 42

제39항에 있어서,

상기 제2 하드 마스크 층의 상기 마스킹 부분들의 폭들은 상기 레지스트 층의 상기 대응하는 마스킹 부분들의 폭들보다 더 좁은 마스킹 구조물.

### 청구항 43

제42항에 있어서,

상기 제2 하드 마스크 층의 상기 마스킹 부분들의 각각의 상기 노출된 측면들은 상기 레지스트 층 아래로 적어도  $5\text{\AA}$ 만큼 리세스(recess)되는 마스킹 구조물.

## 명세서

### 기술분야

<1> 본 발명은 집적 회로 제조 분야에 관한 것으로, 특히 집적 회로용 CD(Critical Dimension) 제어를 위한 트림(trim) 프로세스에 관한 것이다.

## 배경 기술

- <2> 반도체 산업에서, 집적 회로(IC) 디바이스들은 더 빠르고, 더 작고, 및 더 효율적으로 되어왔다. 이러한 트렌드(trend)는 칩들에 회로 집적도들을 증가시키는 제조 기술의 발전과 함께 계속되어 왔다.

- <3> CD를 감소시키는 것은 회로 집적도들을 증가시키기 위한 중요한 방법들 중 하나이다. CD는 반도체 디바이스 제조 중에 형성될 수 있는 가장 작은 기하학적 피쳐(feature)들의 치수(상호접속(interconnect) 라인, 콘택트(contact)들, 트렌치(trench)들 등의 폭)이다. CD들은 더 작은 컴포넌트들 및 더 빠르고, 더 효율적인 회로들의 형성을 용이하게 하도록 감소될 필요가 있다.

- <4> CD를 감소시키는 하나의 방법은 단파장의 광을 채용하는 포토리소그래피(photolithography)를 사용하는 것이다. 그러나, 광의 파장이 감소함에 따라, 포토레지스트(photoresist) 물질들은 점점 광에 불투명하게 된다. 따라서, 현재의 포토리소그래피 기술은 CD를 감소시키는데 한계가 있다.

- <5> CD를 감소시키는 다른 방법은 포토리소그래피 프로세스에 의해 패턴(pattern)을 형성한 후에 에칭(etch) 프로세스에 의해 포토레지스트 패턴을 트리밍(trimming) 또는 수축(shrinking) 것이다. 피쳐 에지 거칠기(edge roughness)를 감소시키고, 피쳐들의 크기를 감소시키고, 및/또는 피쳐들 사이의 공간들을 증가시키기 위해 트림 프로세스가 일반적으로 사용된다. 그러나, 작은 CD들을 갖는 구조들 또는 하부 층들로의 에칭은 그러한 포토레지스트를 사용하는 경우에만 번거롭게 될 수 있다. 작은 피쳐들을 정의하기 위해 기판 내로 깊게 에칭하는 경우, 포토레지스트 패턴은 에칭 프로세스가 완료될 때까지 에칭 프로세스에 의해 변경된다. 이것은 기판이 원하는 패턴 밖으로 에칭되게 한다. 에칭 불량은 디바이스의 성능에 결함을 일으키고 수율(yield) 불량을 일으킬 수 있다. 이러한 문제를 피하기 위해, 포토레지스트로부터 기판으로 패턴을 전사하는데 하드 마스크가 사용되어 왔다.

- <6> CD를 감소시키는 또 다른 방법은 포토레지스트로부터 패턴을 전사한 후에 기판으로 패턴을 전사하기 전에 에칭 프로세스에 의해 하드 마스크를 수축하거나 트리밍하는 것이다. 그러나, 이 방법은 어떠한 문제들도 없는 것이 아니다. 하드 마스크의 패턴 폭을 수축하면서, 하드 마스크의 두께도 감소될 수 있다. 미국특허 제6,420,097 호는 하드 마스크가 포토레지스트 아래로 선택적으로 리세스(recess)되는 프로세스를 도시한다. 그러나, 하드 마스크를 수축하면서, 기판 또는 하드 마스크 아래의 관심 층도 하드 마스크의 개구부(opening)들을 통해 하드 마스크 에칭제(etchant)에 노출된다. 이러한 문제점들은 CD를 감소시키기 위한 어그레시브(aggressive) 에칭 프로세스의 사용을 방해한다. 또한, 프로세스는 리세스를 가능하게 하는 특정한 물질들의 사용에 한정되며, 이 경우라도 원하는 치수들로부터 편차들이 존재할 수 있다.

## 발명의 상세한 설명

- <7> 본 발명의 일 양태에서, 집적 회로용 에칭 방법이 개시된다. 그 방법은 타겟(target) 층 위에 제1 하드 마스크 층을 제공하는 단계; 제1 하드 마스크 층 위에 제2 하드 마스크 층을 제공하는 단계; 제2 하드 마스크 층 위에 포토레지스트 층을 제공하는 단계; 포토레지스트 층에 패턴을 형성하는 단계; 제2 하드 마스크 층으로 패턴을 전사하는 단계; 및 제2 하드 마스크 층의 상부의 포토레지스트 층을 이용하여 제2 하드 마스크 층을 트리밍하는 단계를 포함한다.

- <8> 상기 방법에서, 타겟 층은 절연체, 반도체, 및 금속으로 이루어진 그룹으로부터 선택된 물질을 포함할 수 있다. 제1 하드 마스크 층은 비정질(amorphous) 탄소 층을 포함할 수 있다. 제1 하드 마스크 층은 유기(organic) 하부층을 포함할 수 있다. 제1 하드 마스크 층은 약 200Å부터 약 20,000Å까지의 두께를 가질 수 있다. 제1 하드 마스크 층은 약 20:1 아래의 종횡비(aspect ratio)를 가질 수 있다.

- <9> 전술된 방법에서, 제2 하드 마스크 층은 무기(inorganic) 층을 포함할 수 있다. 무기 층은 DARC(dielectric anti-reflective coating)를 포함할 수 있다. 무기 층은 실리콘 산질화물(oxynitride), 실리콘 산화물, 또는 실리콘 질화물로 이루어진 그룹으로부터 선택된 물질을 포함할 수 있다. 제2 하드 마스크 층은 실리콘 함유 유기 층을 포함할 수 있다. 제2 하드 마스크 층은 약 50Å부터 약 1,000Å까지의 두께를 가질 수 있다. 그 방법에서, 포토레지스트는 13.5nm 포토레지스트, 157nm 포토레지스트, 193nm 포토레지스트, 및 248nm 포토레지스트로 이루어진 그룹으로부터 선택된 포토레지스트를 포함할 수 있다.

- <10> 전술된 방법에서, 패턴을 제2 하드 마스크 층으로 전사하는 단계는 이방성(anisotropic) 에칭 프로세스를 사용하는 단계를 포함할 수 있다. 이방성 에칭 프로세스를 사용하는 단계는 플루오로카본(fluorocarbon) 기반의 플라즈마(plasma)를 사용하는 단계를 포함할 수 있다. 그 방법에서, 제2 하드 마스크 층을 트리밍하는 단계는 제

2 하드 마스크 층의 폭을 적어도 약 10Å만큼 감소시키는 단계를 포함할 수 있다. 제2 하드 마스크 층을 트리밍하는 단계는 포토레지스트 층 및 제1 하드 마스크 층에 대하여 제2 하드 마스크 층을 선택적으로 에칭하는 단계를 포함할 수 있다. 제2 하드 마스크 층을 트리밍하는 단계는 제1 하드 마스크 층의 에칭 속도보다 약 1에서 1,000배 사이의 더 빠른 속도로 제2 하드 마스크 층을 에칭하는 단계를 포함할 수 있다. 제2 하드 마스크 층을 트리밍하는 단계는 초당 약 1Å에서 10Å사이의 속도로 제2 하드 마스크 층을 에칭하는 단계를 포함할 수 있다.

<11> 그 방법에서, 제2 하드 마스크 층을 트리밍하는 단계는 제2 하드 마스크 층을 등방성으로(isotropically) 에칭하는 단계를 포함할 수 있다. 제2 하드 마스크 층을 트리밍하는 단계는 제2 하드 마스크 층을 플라즈마로 에칭하는 단계를 포함할 수 있다. 플라즈마는 불소(fluorine) 함유 플라즈마를 포함할 수 있다. 플라즈마는 NF<sub>3</sub> 기반의 플라즈마 및 SF<sub>6</sub> 기반의 플라즈마로 이루어진 그룹으로부터 선택된 플라즈마를 포함할 수 있다. 대안적으로, 제2 하드 마스크 층을 트리밍하는 단계는 습식(wet) 에칭 프로세스를 사용하는 단계를 포함할 수 있다. 습식 에칭 프로세스를 사용하는 단계는 완충(buffered) 산화물 에칭 프로세스를 사용하는 단계를 포함할 수 있다. 완충 산화물 에칭 프로세스는 HF, NH<sub>4</sub>F, 및 H<sub>2</sub>O를 포함하는 에칭제를 사용하는 단계를 포함할 수 있다.

<12> 전술된 방법은 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 제1 하드 마스크 층으로 전사하는 단계를 더 포함할 수 있다. 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 제1 하드 마스크 층으로 전사하는 단계는 고밀도(high density) 플라즈마 에칭 프로세스를 사용하는 단계를 포함할 수 있다. 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 제1 하드 마스크 층으로 전사하는 단계는 제2 하드 마스크 층의 에칭 속도보다 약 5배 이상 더 빠른 속도로 제1 하드 마스크 층을 에칭하는 단계를 포함할 수 있다. 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 제1 하드 마스크 층으로 전사하는 단계는 황(sulfur) 및 산소 기반의 플라즈마를 사용하여 제1 하드 마스크 층을 에칭하는 단계를 포함할 수 있다. 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 제1 하드 마스크 층으로 전사하는 단계는 황 이산화물을 10sccm에서 75sccm 사이로 프로세스 챔버(processing chamber)로 유입하는 단계를 포함할 수 있다. 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 제1 하드 마스크 층으로 전사하는 단계는 황 이산화물을 20sccm에서 60sccm 사이로 프로세스 챔버로 유입하는 단계를 포함할 수 있다. 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 제1 하드 마스크 층으로 전사하는 단계는 산소를 10sccm에서 100sccm 사이로 프로세스 챔버로 유입하는 단계를 더 포함할 수 있다. 제2 하드 마스크 층의 트리밍으로부터 생성된 패턴을 제1 하드 마스크 층으로 전사하는 단계는 아르곤(argon)을 프로세스 챔버로 유입하는 단계를 더 포함할 수 있다.

<13> 전술된 방법은 제2 하드 마스크 층 위에 BARC(bottom antireflective coating) 층을 제공하는 단계를 더 포함할 수 있다. BARC 층은 약 200Å부터 500Å까지의 두께를 가질 수 있다.

<14> 본 발명의 다른 양태에서, 접적 회로 디바이스의 제조를 위한 방법이 개시된다. 그 방법은 기판 위에 제1 하드 마스크 층을 제공하는 단계; 제1 하드 마스크 층 위에 제2 하드 마스크 층을 제공하는 단계; 제2 하드 마스크 층 위에 패턴을 갖는 레지스트(resist)를 제공하는 단계; 레지스트의 패턴을 사용하여 제2 하드 마스크 층을 이방성으로 에칭하는 단계; 및 제2 하드 마스크 층의 상부의 레지스트를 이용하여 제2 하드 마스크 층을 등방성으로 에칭하는 단계를 포함한다.

<15> 그 방법에서, 접적 회로 디바이스는 메모리를 포함할 수 있다. 접적 회로 디바이스는 마이크로프로세서를 포함할 수 있다. 레지스트 층은 포토레지스트 및 임프린트(imprint) 리소그래피 레지스트로 이루어진 그룹으로부터 선택된 물질을 포함할 수 있다.

<16> 본 발명의 다른 양태에서, 접적 회로 디바이스용 CD 제어를 위한 트림 프로세스가 개시된다. 트림 프로세스는 기판 위에 제1 하드 마스크를 제공함으로써 트림 프로세스 중에 기판을 보호하는 단계 - 제1 하드 마스크는 패턴을 갖는 제2 하드 마스크 아래에 놓임 - ; 및 제2 하드 마스크의 상부에 레지스트를 제공함으로써 트림 프로세스 중에 제2 하드 마스크의 상면을 보호하는 단계를 포함한다.

<17> 본 발명의 또 다른 양태에서, 접적 회로용 마스킹(masking) 구조가 개시된다. 마스킹 구조는 타겟 층 위에 형성되는 제1 하드 마스크 층; 및 제1 하드 마스크 층 위에 형성되는 제2 하드 마스크 층 - 제2 하드 마스크 층은 제1 하드 마스크 층을 커버하도록 구성된 마스킹 부분들을 갖는 패턴을 포함함 - ; 및 제2 하드 마스크 층 위에 형성된 레지스트 층 - 레지스트 층은 제2 하드 마스크 층의 마스킹 부분들에 대응하는 마스킹 부분들을 갖는 패턴을 포함함 - 을 포함한다. 마스킹 구조에서, 제2 하드 마스크 층의 마스킹 부분들의 각각의 노출된 측면들은 약 50Å rms 아래의 평균 거칠기를 가질 수 있다. 제2 하드 마스크 층의 마스킹 부분들의 각각의 노출된 측면

들은 약 10Årms에서 약 50Årms 사이의 평균 거칠기를 가질 수 있다.

<18> 전술된 마스킹 구조에서, 제2 하드 마스크 층의 마스킹 부분들의 폭들은 레지스트 층의 대응하는 마스킹 부분들의 폭들과 실질적으로 동일할 수 있다. 대안적으로, 제2 하드 마스크 층의 마스킹 부분들의 폭들은 레지스트 층의 대응하는 마스킹 부분들의 폭들보다 더 좁을 수 있다. 제2 하드 마스크 층의 마스킹 부분들의 각각의 노출된 측면들은 레지스트 층 아래로 적어도 5Å 만큼 리세스될 수 있다.

<19> 본 발명의 또 다른 양태에서, 접적 회로를 제조하는 방법이 개시된다. 그 방법은 도핑(doping), 산화(oxidation), 질화(nitridation), 및 선택적 성막으로 이루어진 그룹으로부터 선택된 프로세스에 대하여 전술된 마스킹 구조를 사용하는 단계를 포함한다.

### 실시예

<30> 정의들

<31> 본 명세서의 맥락(context)에서, "반도체 기판"이라는 용어는 반도체 웨이퍼(단독으로 또는 반도체 웨이퍼 상에 그외의 물질들을 포함하는 접적 어셈블리들 중 어느 하나)와 같은 벌크(bulk) 반도체 물질들, 및 반도체 물질층들(단독으로 또는 그외의 물질들을 포함하는 접적 어셈블리들 중 어느 하나)을 포함하지만, 이에 한정되지 않는, 반도체 물질들을 포함하는 임의의 구성을 의미하도록 정의된다. "기판"이라는 용어는 전술된 반도체 기판들을 포함하지만, 이에 한정되지 않는, 임의의 지지 기판을 지칭한다. 또한 본 명세서의 맥락에서, "층"이라는 용어는 다르게 표시되지 않는 한 단일 및 복수 모두를 포함한다. 본 명세서에 사용된 바와 같이, "유기"라는 용어는 탄소 및 탄소 함유 물질들을 지칭하며, 따라서 포토레지스트뿐만 아니라 비정질 탄소도 포함한다. 본 명세서에 사용된, "황 산화물"은, 황 이산화물과 같은, 황과 산소의 조합을 본질적으로 포함하는 임의의 화합물을 의미한다는 것에 또한 유의한다.

<32> 본 명세서에 사용된, "타겟 층"이라는 용어는 반도체 디바이스들, 컴포넌트들, 또는 부분들이 오버라잉(overlying) 하드 마스크에 형성되는 패턴에 따라 형성되거나 또는 처리되는 층을 지칭한다. 타겟 층은 전술된 반도체 기판의 일부분이 될 수 있다. 타겟 층은 금속, 반도체, 및/또는 절연체로 형성될 수 있다. 타겟 층에서, 메모리들 또는 마이크로프로세서들 등의 접적 회로 디바이스들의 일부분들이 형성될 수 있다. 바람직한 실시예들에 대해 하드 마스크들을 통한 "프로세스"가 하드 마스크 패턴을 타겟 층으로 전사하기 위한 예칭으로서 기술되는 한편, 본 기술 분야의 당업자들은 그외의 실시예들에서 프로세스가 하드 마스크를 통한, 예를 들어, 산화, 질화, 선택적 성막, 도핑 등을 포함할 수 있다는 것을 이해할 것이다.

<33> 본 명세서에 사용된, "트리밍"이라는 용어는, 층의 거칠기를 클리닝(cleaning)하거나 또는 횡방향으로 층의 피쳐 폭을 감소시키는 것을 지칭한다. 그 용어는 "수축"이라는 용어와 상호변경하여 사용될 수 있다.

<34> 제1 레벨로부터 제2 레벨로 패턴을 전사하는 것은 제1 레벨의 피쳐들에 일반적으로 대응하는 피쳐들을 제2 레벨에 형성하는 것을 포함한다는 것 또한 이해될 것이다. 예를 들어, 제2 레벨의 라인들의 경로는 일반적으로 제1 레벨의 라인들의 경로를 따를 것이고 제2 레벨의 그외의 피쳐들의 위치는 제1 레벨의 유사한 피쳐들의 위치에 대응할 것이다. 그러나, 예를 들어, 트리밍 및 성장 단계들로 인해 피쳐들의 정교한 형태들 및 크기들은 제1 레벨로부터 제2 레벨까지 변경될 수 있다. 예를 들어, 예칭 화학(etch chemistry) 및 조건들에 따라, 전사된 패턴을 형성하는 피쳐들 사이의 상대적인 공간들 및 크기들은 제1 레벨의 패턴에 대하여 확대되거나 또는 축소될 수 있지만, 초기 "패턴"과 여전히 동일하다.

<35> 전체 예칭 프로세스

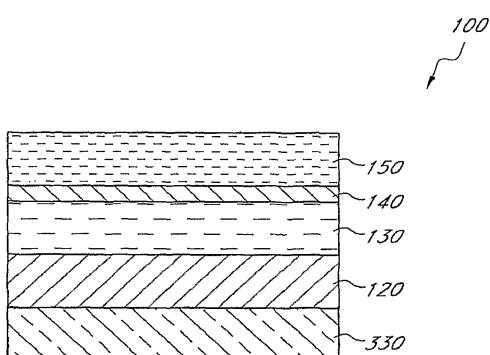

<36> 도 1A 내지 도 1F는 본 발명의 실시예에 따른 접적 회로용 예칭 방법을 도시한다. 도 1A를 참조하면, 타겟 층(120)이 기판(110) 위에 제공된다. 다음으로, 제1 하드 마스크 층(130)이 타겟 층(120) 위에 제공된다. 제2 하드 마스크 층(140)은 제1 하드 마스크 층(130) 위에 제공된다. 제2 하드 마스크 층(140)은 바람직하게는 제1 하드 마스크 층(130) 보다 더 얇다. 또한, 제2 하드 마스크 층(140)은 제1 하드 마스크 층(130)의 물질과 상이한 물질로 형성된다. 마지막으로, 포토레지스트 층(150)이 제2 하드 마스크 층(140) 위에 제공된다.

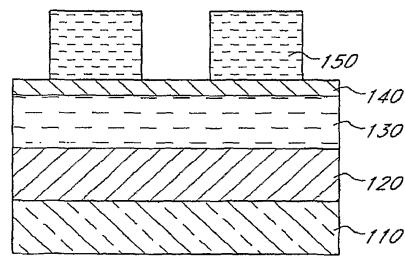

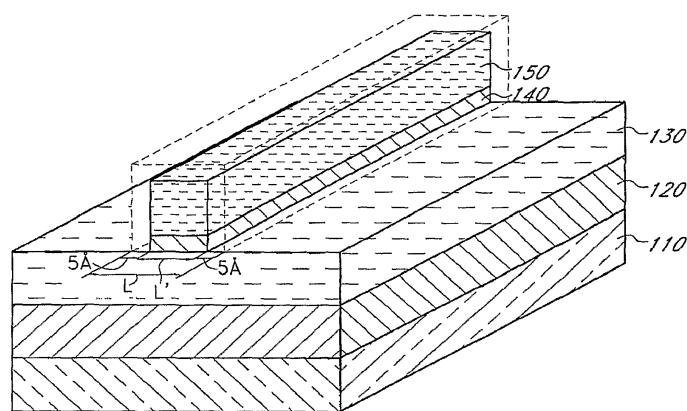

<37> 도 1B를 참조하면, 통상적인 포토리소그래피 기술과 같은 리소그래피를 사용하여, 포토레지스트 층(150)에 패턴이 형성된다. 다음으로, 도 1C에 의해 도시된 바와 같이 예칭 프로세스에 의해 패턴이 제2 하드 마스크 층(140)으로 전사된다. 다음으로, 제2 하드 마스크 층(140)은 등방성 예칭 프로세스에 의해 트리밍되거나 수축되는 한편 포토레지스트 층(150)은 도 1D에 도시된 바와 같이 제2 하드 마스크 층(140)의 상부에 존재한다.

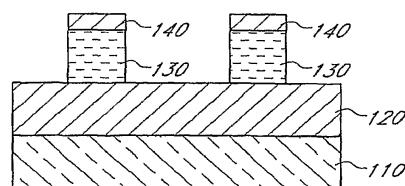

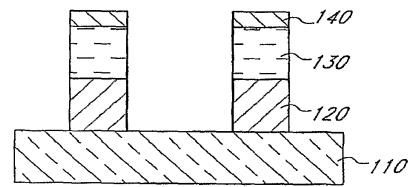

- <38> 다음으로, 제2 하드 마스크 층(140)의 패턴은 도 1E에 도시된 바와 같이 제1 하드 마스크 층(130)으로 전사된다. 일 실시예에서,  $\text{SO}_2$  기반의 플라즈마 DDE(dry develop etch)가 패턴을 제1 하드 마스크 층(130)으로 전사하는데 사용될 수 있다. DDE 프로세스를 사용하여, 제1 하드 마스크 층(130)은 타겟 층(120)을 에칭하는 하드 마스크를 형성하도록 에칭된다. 다음으로, 도시된 실시예에서, 도 1F에 도시된 바와 같이, 타겟 층(120)은 제1 하드 마스크 층(130)을 사용하여 처리된다. 에칭된 제2 하드 마스크 층(140)은, 도시된 바와 같이, 하드 마스크를 통해 타겟 층(120)을 처리하기 전에 제거될 수 있거나 또는 남겨질 수 있다. 각각의 상기 단계들은 이하에 상세하게 기술될 것이다.

- <39> 하드 마스크 층 생성

- <40> 도 1A는 일 실시예에 따라 제조될 접적 회로(IC)의 일부분(100)을 도시한다. 기판(110)은 일부분(100)의 하부에 제공된다. 도시된 실시예에서, 기판(110)은 실리콘 기판이다. 그외의 실시예들에서, 기판(110)은 그외의 유형의 반도체 물질들로 형성될 수 있다.

- <41> 타겟 층(120)은 기판(100) 위에 형성된다. 타겟 층(120)은 IC 제조 프로세스들을 통해 다양한 IC 컴포넌트들, 부품들, 및 구조들이 형성되는 층이다. 컴포넌트들, 부품들, 및 구조들의 예시들은 트랜지스터들, 캐패시터(capacitor)들, 저항기들, 다이오드들, 도전성 라인들, 전극들, 스페이서(spacer)들, 트렌치들 등을 포함한다. 타겟 층 물질의 종류는 타겟 층(120)에 형성될 디바이스의 유형에 의존한다. 타겟 층 물질들의 예시들은 절연체, 반도체, 및 금속을 포함하지만, 이에 한정되지 않는다.

- <42> 제1 하드 마스크 층(130)은 타겟 층(120) 위에 형성된다. 제1 하드 마스크 층(130)은 처리될(예를 들어, 에칭될) 구조 위에 놓인다. 제1 하드 마스크 층(130)은 타겟 층(120)으로 전사될 패턴을 제공한다. 제1 하드 마스크 층(130)은 유기 물질로 형성될 수 있다. 도시된 실시예에서, 제1 하드 마스크 층(130)은 비정질 탄소로 형성된다. 비정질 탄소의 바람직한 유형은 하부 층들에 포토 얼라인먼트(photo alignment)를 용이하게 하는 무색의, 투명한 탄소이다. 제1 하드 마스크 층(130)이 바람직하게는 두껍기 때문에, 불투명한 필름은 포토 얼라인먼트를 저해할 수 있다.

- <43> 그외의 실시예들에서, 제1 하드 마스크 층(130)은 포토레지스트 하부층으로서도 사용될 수 있는 중합체(polymeric) 물질로 형성될 수 있다. 바람직하게는, 중합체 물질은 통상적인 포토레지스트보다 탄소 함유량이 더 많은 유기 물질이다. 중합체 물질의 예시들은, 본 명세서에 참조로서 포함된 미국특허 제6,890,448호에 개시되어 있다. 또한, 중합체 물질은 Shipley Company, Marlborough, MA로부터 상업적으로 사용가능한 AR 계열의 비반사체(anti-reflectant)들이 될 수 있다.

- <44> 바람직하게는, 제1 하드 마스크 층(130)은 타겟 층(120)의 처리를 향상시키기 위해 꽤 두껍다. 제1 하드 마스크 층(130)은 바람직하게는 약  $200\text{\AA}$ 에서  $20,000\text{\AA}$  사이의 두께를 가지며, 더 바람직하게는  $500\text{\AA}$ 에서  $10,000\text{\AA}$  사이의 두께를 갖는다. 두꺼운 제1 하드 마스크 층(130)은 하드 마스크를 통한 처리에 더 유리하다. 그러나, 제1 하드 마스크 층의 두께는 종횡비에 의존한다. 제1 하드 마스크 층(130)의 종횡비는 기계적 안정성을 위해 바람직하게는 약 20:1 아래가 된다.

- <45> 제2 하드 마스크 층(140)은 제1 하드 마스크 층(130) 위에 형성된다. 제2 하드 마스크 층(140)은 제1 하드 마스크 층(130)으로 전사될 패턴을 제공한다. 제2 하드 마스크 층(140)은 바람직하게는 포토레지스트 층(150)의 라인폭보다 더 좁은 라인폭을 갖는 패턴을 제공한다.

- <46> 제2 하드 마스크 층(140)은 무기 물질 또는 실리콘 함유 유기 층으로 형성될 수 있다. 도시된 실시예에서, 제2 하드 마스크 층(140)은 DARC(dielectric anti-reflective coating), 예를 들어,  $\text{SiO}_x\text{N}_y$ (silicon-rich silicon oxynitride)로 형성된다. DARC 층은 층의 전체 무게에 대해 약 30wt%부터 약 80wt%까지의 양의 실리콘을 함유할 수 있다. 바람직하게는, DARC 층은 층의 전체 무게에 대해 35wt%부터 약 70wt%까지의 양의 실리콘을 함유할 수 있다. 다른 실시예에서, 제2 하드 마스크 층(140)은 실리콘, 실리콘 산화물( $\text{SiO}_2$ ) 또는 실리콘 질화물( $\text{Si}_3\text{N}_4$ )로 형성될 수 있다.

- <47> 다른 실시예에서, 제2 하드 마스크 층(140)은 실리콘 함유 유기 물질로 형성될 수 있다. 실리콘 함유 유기 물질은 제1 하드 마스크 층(130)이 형성될 수 있는 물질과 상이하다. 실리콘 함유 유기 층은 층의 전체 무게에 대해 약 10wt%부터 약 35wt%까지의 양의 실리콘을 포함할 수 있다. 예시적인 실리콘 함유 유기 물질은 SHB-A629(Shin Etsu)이다. 제2 하드 마스크 층(140)은 바람직하게는 약  $50\text{\AA}$ 에서  $1,000\text{\AA}$  사이의 두께를 가지며, 더 바람직하게는 약  $100\text{\AA}$ 에서  $700\text{\AA}$  사이의 두께를 갖는다.

<48> 포토레지스트 층 생성 및 패터닝

도 1A를 다시 참조하면, 포토레지스트 층(150)은 제2 하드 마스크 층(140) 위에 형성된다. 도시된 실시예에서, 포토레지스트 층(150)은, 248nm, 193nm, 157nm, 및 13.5nm를 포함하는, 리소그래피에 채용된 광의 일반적인 파장들에 민감한 포토레지스트로 형성될 수 있다. 바람직하게는, 포토레지스트 층(150)은 약 500Å에서 3000Å 사이의 두께를 가지며, 더 바람직하게는 약 1,000Å에서 2,000Å 사이의 두께를 갖는다. 도 1B에서, 포토레지스트 층(150)은 임의의 적절한 포토레지스트 처리 기술을 사용하여 패터닝된다.

<50> 그외의 실시예들에서, 레지스트 층(150)은 웨이퍼 위에 패턴을 활상(imaging)하기 위해 그외의 유형들의 리소그래피에 사용되는 레지스트로 형성될 수 있다. 그러한 리소그래피의 예시들은 자외선(UV) 리소그래피, EUV(extreme ultraviolet) 리소그래피, X-레이 리소그래피 및 임프린트 콘택트 리소그래피를 포함하지만, 이에 한정되지 않는다.

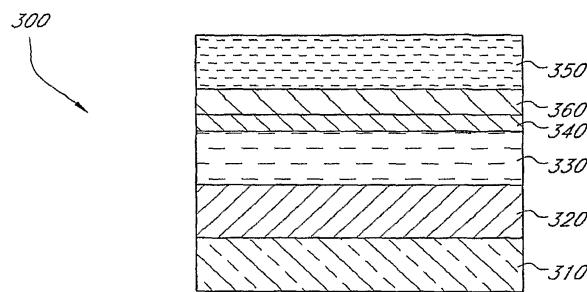

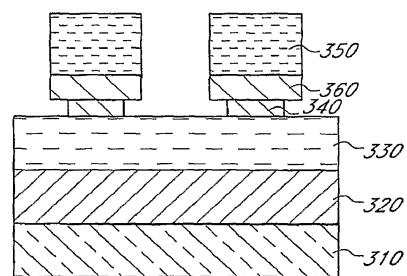

<51> 도 3A를 참조하면, BARC(bottom anti-reflective coating) 층(360)은 제2 하드 마스크 층(340)과 포토레지스트 층(350) 사이에 선택적으로 형성될 수 있다. 일반적으로 유기인, BARC들은 포토레지스트를 활성화하는 자외선(UV) 방사의 반사를 방지함으로써 해상도를 증가시킨다. BARC들은 폭넓게 사용가능하고, 보통 레지스트 물질 및 UV 파장의 선택에 기초하여 선택된다. 일반적으로 중합체 기반인, BARC들은 보통 수반되는 포토레지스트와 함께 제거된다. 선택적인 BARC 층(360)은 바람직하게는 약 200Å에서 500Å 사이의 두께를 가지며, 더 바람직하게는 약 300Å에서 400Å의 두께를 갖는다.

<52> 제2 하드 마스크로의 패턴 전사

<53> 포토레지스트(150)에 형성되는 패턴은 바람직하게는 플라즈마 에칭 프로세스를 사용하여 제2 하드 마스크(140)로 전사되며, 더 바람직하게는 고밀도 플라즈마 에칭 프로세스를 사용하여 제2 하드 마스크(140)로 전사된다. 바람직하게는, 플라즈마 에칭 프로세스는 이방성 에칭 프로세스이다.

<54> 도 1C에서, 포토레지스트 층(150)으로부터의 패턴은 제2 하드 마스크 층(140)으로 전사된다. 그 전사는 바람직하게는 프로세스 챔버에서 플루오로카본 플라즈마 건식 에칭을 사용하여 달성된다. 바람직하게는 고밀도 플라즈마를 채용하는, 건식 에칭은 레지스트 요소들의 치수들에 충실한 방법으로 제2 하드 마스크 층(140)의 패터닝을 제공하는데 사용될 수 있다. 전력 레벨들 및 유속들은 선택된 프로세스 챔버에 기초하여 변경될 것이다. 바람직한 챔버들은 Lam Research Corp.(Fremont, CA)의 TCP9400 및 TCP2300 폴리 에칭 챔버들 및 Applied Materials Corp.(Santa Clara, CA)의 DPS2 폴리 에칭 챔버를 포함한다. 본 기술 분야의 당업자들은, 포토레지스트 층(150)으로부터 제2 하드 마스크 층(140)으로 패턴을 전사하는데 사용될 수 있는 몇몇의 가능한 에칭 프로세스들이 존재한다는 것을 이해할 것이다.

<55> 바람직하게는, 제2 하드 마스크 층(140)을 에칭하는데 채용된 챔버는 다음 단계에서 제2 하드 마스크 층(140)을 트리밍하거나 또는 수축하는데 사용된다. 제2 하드 마스크 층(140)이 에칭된 후에, 챔버는 전이(transition) 단계 중에 퍼징(purge)된다. 이온화 전력이 챔버에 남겨지지만, 바이어스 전력은 턴 오프(turned off)된다. 제2 하드 마스크 층(140)의 에칭을 위해 사용된 플라즈마는 챔버로부터 퍼징된다.

<56> 제2 하드 마스크 트림

<57> 도 1D 및 도 4를 참조하면, 제2 하드 마스크 층(140)은 수축되거나 또는 트리밍되는 한편, 포토레지스트 층(150)은 제2 하드 마스크 층(140)의 상부에 존재한다. 트림 단계는 CD를 감소시키는 횡방향의 에칭을 일으킨다. 트림 단계는 또한 피쳐 에지 거칠기를 감소시킨다. 바람직하게는, 제2 하드 마스크 층의 에지들은 약 10Årms에서 약 100Årms 사이의 평균 거칠기( $R_a$ )를 갖는다. 바람직하게는, 이 트림 단계는 등방성 에칭 프로세스를 사용하여 수행된다.

<58> 도 4에서, 트림 단계 전의 제2 하드 마스크 층(140) 및 포토레지스트 층(150)이 점선들로 도시된다. 제2 하드 마스크 층(140)은 초기 라인폭 L을 갖는다. 트림 단계 후에, 제2 하드 마스크 층(140)은 감소된 라인폭 L'을 갖는다. 제2 하드 마스크 층(140)의 라인폭은 바람직하게는 적어도 약 10Å 만큼 감소된다. 다시 말하면, 초기 라인폭 L과 감소된 라인폭 L' 사이의 차는 바람직하게는 적어도 10Å이다. 에칭의 범위에 대하여, 제2 하드 마스크 층(140)의 각각의 노출된 측면들은 적어도 약 5Å 만큼 횡방향으로 에칭된다. 일 실시예에서, 75nm 라인의 라인폭은 64nm로 감소된다. 다른 실시예에서, 77nm 라인의 라인폭은 67nm로 감소된다.

<59> 건식 에칭 트리밍

- <60> Si<sub>x</sub>N<sub>y</sub> 또는 SiN을 포함하는 제2 하드 마스크 층(140)은 등방성 플라즈마 전식 에칭 프로세스를 사용하여 수축될 수 있다. 트림 단계에 채용되는 에칭제는 바람직하게는 제2 하드 마스크 층(140)을 선택적으로 에칭하도록 선택되는 한편, 제1 하드 마스크 층(130)만을 최소한으로 에칭하여, 기판을 보호한다. 특정한 실시예들에서, 제2 하드 마스크 층(140)은 제1 하드 마스크 층(130) 만큼 빠르게 에칭될 수 있지만, 제1 하드 마스크 층(130)보다 천천히 에칭될 수 없다. 바람직하게는, 제2 하드 마스크 층(140)은 제1 하드 마스크 층(130)의 에칭 속도보다 약 1에서 1000배 사이의 더 빠른 속도로 에칭되며, 더 바람직하게는 약 2에서 100배 사이의 더 빠른 속도로 에칭되며, 가장 바람직하게는 약 10에서 100배 사이의 더 빠른 속도로 에칭된다.

- <61> 일 실시예에서, 제2 하드 마스크 층(140) 및 오버라임 포토레지스트 층(150)은 선택성(selectivity)이 적거나 없는 에칭제를 사용하여 그 물질들 사이에서 에칭될 수 있다. 제2 하드 마스크 층(140)은 오버라임 포토레지스트 층(150)의 에칭 속도와 실질적으로 동일한 속도 또는 더 느린 속도로 에칭될 수 있다. 도 1D를 참조하면, 포토레지스트 층(150)은 제2 하드 마스크 층(140)의 에칭 속도만큼 빠른 속도로 에칭된다. 도 1D에서, 포토레지스트 층(150)은 제2 하드 마스크 층(140)만큼 많이 에칭되는 한편, 제2 하드 마스크 층(140)의 라인 에지 거칠기는 클리닝되거나 또는 제2 하드 마스크 층(140)은 원하는 피쳐 폭을 갖도록 수축된다.

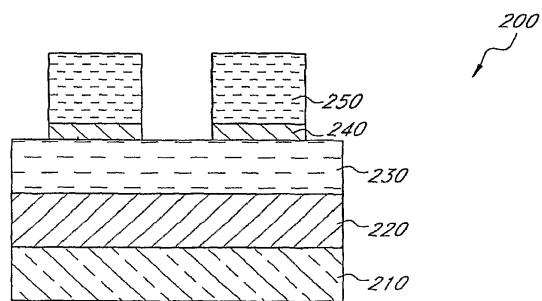

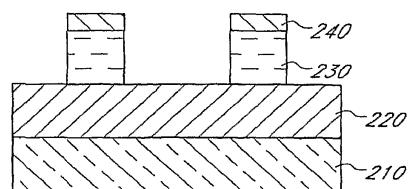

- <62> 포토레지스트 층이 1,000Å 아래의 두께를 갖는 그외의 실시예들에서, 포토레지스트(150)에 관하여 제2 하드 마스크 층(140)에 대하여 고선택성을 갖는 에칭제가 바람직하게는 트림 단계를 위해 사용된다. 도 2A 내지 도 2C는 본 발명의 실시예에 따라 고선택성을 갖는 에칭제를 사용하여 하드 마스크를 형성하는 부분적인 프로세스를 도시한다. 도 2A 내지 도 2C에서, 유사한 부분들이 도 1A 내지 도 1F의 참조 번호들과 유사한 참조 번호들로 참조되지만 번호들은 100만큼 증가된다. 도 2A를 참조하면, 타겟 층(220)은 기판(210) 위에 제공된다. 제1 하드 마스크 층(230)은 타겟 층(220) 위에 제공된다. 제2 하드 마스크 층(240)은 제1 하드 마스크 층(230) 위에 제공된다. 포토레지스트 층(250)은 제2 하드 마스크 층(240) 위에 제공된다. 포토레지스트 패터닝(도시되지 않음)은 도 1B를 참조하여 전술된 것과 유사한 또는 동일한 방법으로 수행된다.

- <63> 도 2A에서, 포토레지스트 층(250)의 패턴은 제2 하드 마스크 층(240)으로 전사된다. 패턴 전사 프로세스는 도 1C를 참조하여 전술된 것과 유사하거나 또는 동일하다.

- <64> 도 2B에서, 제2 하드 마스크 층(240)은 포토레지스트 층(250)에 대하여 선택적으로 에칭된다. 제2 하드 마스크 층(240)은 바람직하게는 포토레지스트 층(250)의 에칭 속도보다 약 2에서 1000배 사이의 더 빠른 속도로 에칭되며, 보다 바람직하게는 약 2 내지 100배 사이의 더 빠른 속도로 에칭된다. 고선택성 에칭제를 사용하면, 포토레지스트(250)는 최소한으로만 에칭되는 한편, 제2 하드 마스크 층(240)의 라인 에지 거칠기는 클리닝되거나 또는 제2 하드 마스크 층(240)은 원하는 피쳐 폭을 갖도록 수축되어, 도시된 바와 같이 리세스되거나 또는 언더커팅(undercutting)된다.

- <65> 도 2C에서, 제2 하드 마스크 층(240)의 패턴은 제1 하드 마스크 층(230)으로 전사된다. 제2 하드 마스크 층(240)으로부터 제1 하드 마스크 층(230)으로의 패턴 전사는 도 1E를 참조하여 이하에 상세하게 기술될 패턴 전사과 동일하거나 또는 유사하다.

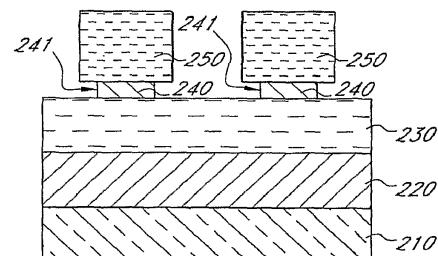

- <66> 다른 실시예에서, 도 3A 및 도 3B를 참조하면, BARC 층(360)은 포토레지스트 층(350)과 제2 하드 마스크 층(340) 사이에 형성된다. 도 3A 및 도 3B에서, 유사한 부분들이 도 1A 내지 도 1F의 참조 번호들과 유사한 참조 번호들로 참조되지만 번호들은 200만큼 증가된다. 본 실시예에서, BARC 층(360)은 포토레지스트 층(350)의 에칭 속도와 거의 동일한 속도로 에칭된다. 제2 하드 마스크 층(340)을 에칭하기 위한 고선택성 에칭제를 사용하면, 포토레지스트 층(350) 및 BARC 층(360)만이 최소한으로 에칭되는 한편, 제2 하드 마스크 층(340)의 라인 에지 거칠기는 감소되거나 또는 제2 하드 마스크 층(340)은 도 3B에 도시된 바와 같이 원하는 피쳐 폭을 갖도록 수축된다. 반면에, 제2 하드 마스크 층(340)에 대해 저선택성을 갖는 에칭제를 사용하면, 포토레지스트 및 BARC 층은 도 1A 내지 도 1F의 실시예와 유사한 제2 하드 마스크 층(340)의 속도와 거의 동일하거나 또는 더 빠른 속도로 수축된다.

- <67> 에칭 속도는 라인의 양 측면들에 대해 바람직하게는 약 2Å/sec에서 20Å/sec 사이의 속도, 즉 라인의 각각의 측면에서 약 1Å/sec에서 10Å/sec 사이의 속도이다. 바람직한 제2 하드 마스크 층(140, 240, 340)의 트림 단계를 위한 바람직한 에칭제는 불소 함유 플라즈마이다. 불소 함유 플라즈마는 NF<sub>3</sub> 또는 SF<sub>6</sub> 기반의 플라즈마를 포함할 수 있다.

- <68> 트림 단계를 위한 하나의 바람직한 챔버는 Lam Research Corp.의 TCP9400 폴리 에칭 챔버이다. 이 챔버를 사용

하면, 바람직한 전구체(precursor) 가스들은  $\text{NF}_3$  및 Ar을 포함한다. 단일 웨이퍼를 갖는 바람직한 실시예에서,  $\text{NF}_3$ 에 대한 유량(flow rate)은 바람직하게는 약 10sccm에서 50sccm 사이이고, 더 바람직하게는 약 15sccm에서 30sccm 사이이다. Ar에 대한 유량은 바람직하게는 약 15sccm에서 150sccm 사이이고, 더 바람직하게는 약 20sccm에서 75sccm 사이이다. 그 챔버에서, 압력은 바람직하게는 약 4mTorr에서 20mTorr 사이이고, 더 바람직하게는 약 5mTorr에서 15mTorr 사이이다. 바람직하게는 인-시츄(in situ)로 전달되는, 이온화 소스 전력은 바람직하게는 약 100W에서 400W 사이이고, 더 바람직하게는 약 150W에서 300W 사이이다. 바이어스 전력은 바람직하게는 약 0W이다. 웨이퍼 온도는 바람직하게는 약 -10°C에서 20°C 사이이고, 더 바람직하게는 약 0°C에서 10°C 사이이다. 다른 바람직한 챔버는 Applied Materials Corp.의 DPS2 폴리 에칭 챔버이다.

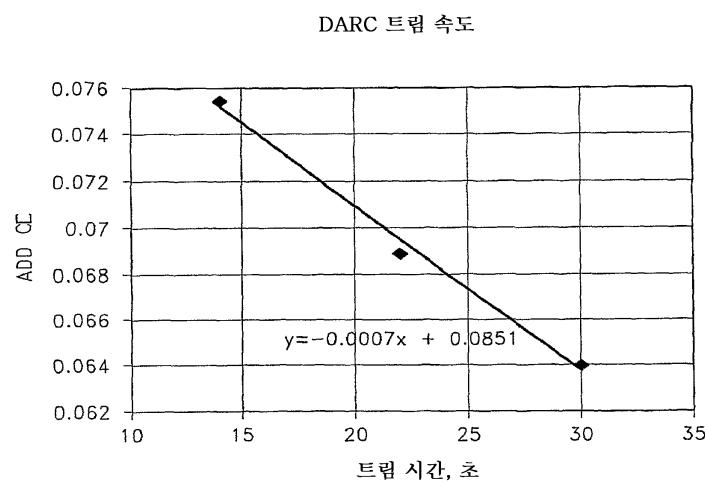

<69> 일 실시예에서, 1600Å 포토레지스트 층, 제2 하드 마스크 층으로서 730Å 실리콘 함유 유기 층, 및 제1 하드 마스크 층으로서 2500Å 유기 하부층을 포함하는 웨이퍼에서 트림 단계가 수행된다. 약 20sccm의  $\text{NF}_3$  및 약 30sccm의 Ar이 챔버로 유입된다. 챔버는 약 10mTorr의 압력 및 약 200W의 소스(유도(inductive)) 전력을 갖도록 구성된다. 이러한 조건들 하에서, 도 5에 도시된 바와 같이 피쳐 폭에 대하여 약 6Å/sec의 트림 속도가 얻어진다. 다시 말하면, 제2 하드 마스크 층의 노출된 부분의 각각의 측면에 대하여 약 3Å/sec의 에칭 속도가 얻어진다.

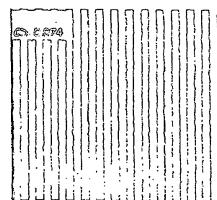

<70> 도 6A 내지 도 6C는, 스캐닝 전자 현미경으로 취해진, 전술된 트림 단계에 의해 트리밍된 하드 마스크 패턴들의 평면도들의 현미경사진들이다. 제2 하드 마스크 패턴들의 라인폭들은 도면들의 좌측 상단에 마이크로미터(micron) 단위로 도시된다. 트림 단계 전에, 제2 하드 마스크 층은 약 81nm의 초기 라인폭을 갖는다. 트림 단계 후에, 라인폭은 도면들(6A, 6B, 및 6C)에 도시된 바와 같이 약 74nm, 70nm, 및 69nm로 각각 감소된다. 라인폭이 약 74nm, 70nm, 및 69nm로 감소되는데 각각 약 12초, 19초 및 21초의 시간이 소요된다. 도 7은 도 6C의 확대도이다. 도 7에 도시된 제2 하드 마스크 층은 약 69nm의 라인폭을 갖는 트리밍된 패턴을 갖는다.

<71> 또한, 도 8은, 스캐닝 전자 현미경으로 취해진, 트리밍된 하드 마스크 패턴의 측횡단면 현미경사진이다. 도 8은 제2 하드 마스크 층으로부터 이하에 더 상세하게 기술될 제1 하드 마스크로의 패턴 전사 후에 라인/스페이스 패턴들의 횡단면을 도시한다. 전술된 바와 같이 트리밍된 제2 하드 마스크 층은 제1 하드 마스크 층의 상부에 남겨진다. 도 8은 우수한 충실도(fidelity) 및 합리적인 라인 에지 거칠기를 도시한다. 바람직하게는, 제2 하드 마스크 층의 에지들은 약 10Årms에서 약 100Årms 사이의 평균 거칠기( $R_a$ )를 가지고, 더 바람직하게는 약 50Årms 아래의 평균 거칠기( $R_a$ )를 가지며, 가장 바람직하게는 약 10Årms에서 약 50Årms 사이의 평균 거칠기( $R_a$ )를 갖는다.

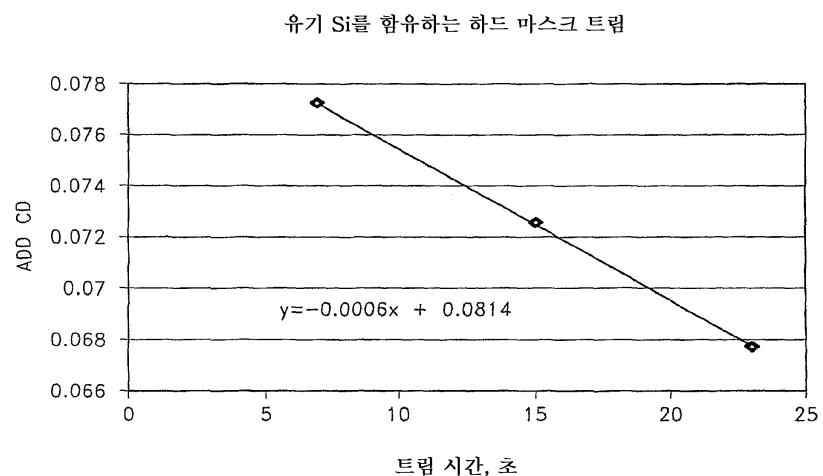

<72> 다른 실시예에서, 1600Å 포토레지스트 층, 400Å BARC 층, 제2 하드 마스크 층으로서의 260Å DARC 층, 및 제1 하드 마스크 층으로서의 2000Å 비정질 탄소 층을 포함하는 웨이퍼에서 트림 단계가 수행된다. 본 실시예에서, BARC 층은 도 3A 및 도 3B를 참조하여 전술된 실시예에서 사용된다. 약 20sccm의  $\text{NF}_3$  및 약 30sccm의 Ar이 챔버로 유입된다. 챔버는 약 10mTorr의 압력 및 약 200W의 바이어스 전력을 갖도록 구성된다. 이러한 조건들 하에서, 도 9에 도시된 바와 같이 피쳐 폭에 대하여 약 7Å/sec의 트림 속도가 얻어진다. 다시 말하면, 제2 하드 마스크 층의 노출된 부분의 각각의 측면에 대하여 약 3.5Å/sec의 에칭 속도가 얻어진다.

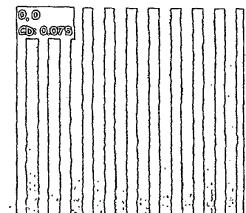

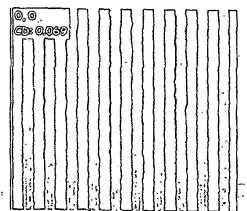

<73> 도 10A 내지 도 10C는, 스캐닝 전자 현미경으로 취해진, 제2 하드 마스크 층으로부터 이하에 더 상세하게 기술될 제1 하드 마스크로의 패턴 전사 후에 라인/스페이스 패턴들의 평면도들의 현미경사진들이다. 전술된 바와 같이 트리밍된 제2 하드 마스크 층은 제1 하드 마스크 층의 상부에 남겨진다. 제2 하드 마스크 패턴들의 라인폭들은 도면들의 좌측 상단에 마이크로미터 단위로 도시된다. 트림 단계 전에, 제2 하드 마스크 층은 약 85nm의 초기 라인폭을 갖는다. 트림 단계 후에, 도면들(10A, 10B, 및 10C)에 도시된 바와 같이 제2 하드 마스크 층의 라인폭은 약 75nm, 69nm, 및 63nm로 각각 감소된다. 라인폭이 약 75nm, 69nm, 및 63nm로 감소되는데 각각 약 14초, 23초 및 32초의 시간이 걸린다.

<74> 바람직하게는, 트림 단계를 위해 채용된 챔버는 제1 하드 마스크 층(130)을 에칭하는데 사용된다. 제2 하드 마스크 층(140)이 에칭된 후에, 챔버는 전이 단계 중에 페징된다. 이온화 소스 전력이 챔버에 남겨지지만, 바이어스 전력은 턴 오프된다. 제2 하드 마스크 층(140)의 트리밍에 사용된 플라즈마는 챔버로부터 페징된다.

#### 습식 에칭 트리밍

<76> 제2 하드 마스크 층은 등방성 습식 에칭 프로세스를 사용하여 수축될 수 있다. 제2 하드 마스크 층(140)이

$\text{SiO}_2$ 로 형성되는 일 실시예에서, 등방성 습식 에칭 프로세스를 위해 완충 산화물 에칭이 채용될 수 있다. 완충 산화물 에칭 용액은 HF,  $\text{NH}_4\text{F}$ , 및  $\text{H}_2\text{O}$ 를 함유한다. 일 실시예에서, 용액은 약 0.5wt.%에서 20wt.% 사이의 HF 농도로 사용되고, 더 바람직하게는 약 2wt.%에서 10wt.% 사이의 HF 농도로 사용된다. 기판 온도는 바람직하게는 약 15°C에서 80°C 사이이고, 더 바람직하게는 약 20°C에서 25°C 사이이다.

<77> 예시로서, 6.8%의 HF, 34%의  $\text{NH}_4\text{F}$ , 및 58.6%의  $\text{H}_2\text{O}$ 를 함유하는 완충 산화물 에칭 용액은 약 100nm/min의 속도로  $\text{SiO}_2$ 를 에칭한다. 에칭 프로세스의 지속시간은 제2 하드 마스크 층(140)의 원하는 라인폭에 기초하여 변경될 수 있다. 본 기술 분야의 당업자들은 완충 에칭 용액의 농도, 기판 온도, 및 에칭 지속시간이 제2 하드 마스크 층의 피쳐폭 또는 원하는 거칠기에 기초하여 선택될 수 있다는 것을 이해할 것이다.

<78> 트림 단계 중에, 제2 하드 마스크 층(140)의 상부에 포토레지스트 층(150)을 제공함으로써, 거칠기 및 CD를 감소시키도록 어그레시브 에칭 프로세스가 채용될 수 있다. 제2 하드 마스크 층(140)의 상부가 오버라잉 포토레지스트 층(150)에 의해 보호되기 때문에 그러한 어그레시브 에칭 프로세스는 제2 하드 마스크 층(140)의 두께를 감소시키지 않는다. 또한, 타겟 층(120) 위에 형성된 제1 하드 마스크 층(130)은 어그레시브 에칭 프로세스로부터 타겟 층(120)을 보호한다. 따라서, 타겟 층(120)에 대해 원하지 않는 손상없이 CD를 감소시키기 위해 더 어그레시브한 또는 더 긴 트림 단계가 수행될 수 있다. 그러한 더 어그레시브한 또는 더 긴 트림 단계는, 예를 들어, 메모리 어레이용 라인들, 도전체들, 캐퍼시터들 등의 고집적 어레이들 또는 마이크로프로세서들, 예를 들어, 로직 어레이들에 반복되는 패턴들을 형성하는 단계에 대하여 특히 유리하다.

#### 제1 하드 마스크로의 패턴 전사

<80> 도 1E를 참조하면, 수축된 또는 트리밍된 패턴은 제2 하드 마스크 층(140)으로부터 제1 하드 마스크 층(130)으로 전사된다. 도 1E에서, 제2 하드 마스크 층(140)의 패턴은 제1 하드 마스크 층(130)으로 전사된다. 제1 하드 마스크 층(130)은 바람직하게는 유기 물질로 형성되고, 더 바람직하게는 비정질 탄소로 형성된다. 바람직하게는, 에칭 프로세스는 DDE(dry develop etch) 프로세스이다. 바람직하게는, 에칭제는 황 및 산소를 포함하고 바람직하게는 플라즈마이다. 도시된 실시예에서, 황 이산화물( $\text{SO}_2$ ) 기반의 플라즈마는 DDE 탄소 에칭 단계로서 참조되는 프로세스에 에칭제로서 사용된다. 바람직하게는, 플라즈마 프로세스는 플라즈마를 지원하는 불활성 가스들을 사용한다.

<81> 제1 하드 마스크 층(130)에 대한 에칭 프로세스는 제2 하드 마스크 층(140) 및 하부 타겟 층(120)과 같은 그외의 층들에 관해 제1 하드 마스크 층(130)에 대하여 고선택성을 갖도록 수행된다. 바람직하게는, 제1 하드 마스크 층(130)은 제2 하드 마스크 층(140)의 에칭 속도보다 약 5배 이상 더 빠른 속도로 에칭되고, 더 바람직하게는 약 10에서 50배 사이의 더 빠른 속도로 에칭된다.

<82> 그러한 에칭을 위한 하나의 바람직한 챔버는 Lam Research Corp.의 TCP9400 폴리 에칭 챔버이다. 이 챔버에서, 압력은 바람직하게는 3mTorr에서 20mTorr 사이이고, 더 바람직하게는 약 5mTorr에서 15mTorr 사이이다. 바람직하게는 인-시츄로 전달되는, 이온화 소스 전력은 바람직하게는 175W에서 400W 사이이고, 더 바람직하게는 약 225W에서 350W 사이이다. 바이어스 전력은 바람직하게는 약 25W에서 125W 사이이고, 더 바람직하게는 약 30W에서 100W 사이이다. 전극 온도는 바람직하게는 약 -5°C에서 15°C 사이이고, 더 바람직하게는 약 0°C에서 10°C 사이이다. 이 챔버를 사용하는 경우, 바람직한 에칭제 가스들은  $\text{SO}_2$ ,  $\text{O}_2$ , 및 Ar을 포함한다. 단일 웨이퍼를 갖는 바람직한 실시예에서,  $\text{SO}_2$ 에 대한 유량은 바람직하게는 약 10sccm에서 75sccm 사이이고, 더 바람직하게는 약 20sccm에서 60sccm 사이이다.  $\text{O}_2$ 에 대한 유량은 바람직하게는 약 10sccm에서 100sccm 사이이고, 더 바람직하게는 약 20sccm에서 80sccm 사이이다. Ar에 대한 유량은 바람직하게는 약 0sccm에서 175sccm 사이이고, 더 바람직하게는 약 0sccm에서 140sccm 사이이다.

<83> 다른 바람직한 챔버인 Applied Materials Corp.의 IPS 산화물 에칭 챔버에서, 압력은 바람직하게는 5mTorr에서 20mTorr 사이이고, 더 바람직하게는 약 7mTorr에서 16mTorr 사이이다. 인-시츄 이온화 소스 전력은 바람직하게는 350W에서 1200W 사이이고, 더 바람직하게는 약 400W에서 1000W 사이이다. 바이어스 전력은 바람직하게는 약 40W에서 150W 사이이고, 더 바람직하게는 약 50W에서 130W 사이이다. 전극 온도는 약 -25°C에서 15°C 사이이고, 더 바람직하게는 약 -20°C에서 10°C 사이이다. 이 챔버를 사용하는 경우, 바람직한 에칭제 가스들은  $\text{SO}_2$ ,  $\text{O}_2$ ,  $\text{N}_2$  및 Ar을 포함한다. 단일 웨이퍼를 갖는 바람직한 실시예에서,  $\text{SO}_2$ 에 대한 유량은 바람직하게는 약 10sccm에서 75sccm 사이이고, 더 바람직하게는 약 20sccm에서 60sccm 사이이다.  $\text{O}_2$ 에 대한 유량은 바람직하게

는 약 0sccm에서 100sccm 사이이고, 더 바람직하게는 약 0sccm에서 90sccm 사이이다. Ar에 대한 유량은 바람직하게는 약 0sccm에서 175sccm 사이이고, 더 바람직하게는 약 0sccm에서 150sccm 사이이다. N<sub>2</sub>에 대한 유량은 바람직하게는 약 0sccm에서 125sccm 사이이고, 더 바람직하게는 약 0sccm에서 100sccm 사이이다.

<84> 바람직하게는 비정질 탄소인, 제1 하드 마스크 층(130)은 SO<sub>2</sub> 기반의 플라즈마를 사용하여 제2 하드 마스크 층(140)에 대해 고선택적으로 에칭된다. DDE 에칭 프로세스의 선택성은 타겟 층(120)의 피쳐들의 프린팅에 대하여 우수한 마스크를 제공하도록 돋는다.

<85> 또한, 제1 하드 마스크 층(130)은 바람직하게는 하부 타겟 층(120)에 대하여 고선택적으로 에칭된다. 바람직하게는, 제1 하드 마스크 층(130)은 타겟 층(120)의 에칭 속도보다 약 5배 이상 더 빠른 속도로 에칭되고, 더 바람직하게는 약 10배 더 빠른 속도로 에칭된다. 바람직한 물질들을 사용하면, 100:1 보다 큰 선택도가 달성될 수 있다. 이 에칭 프로세스 중에, 제2 하드 마스크 층(140)을 덮는 포토레지스트 층(150)도 에칭된다.

#### 타겟 층 에칭

<87> 도 1F를 참조하면, 제1 하드 마스크(130)가 패터닝되는 경우, 그것은 타겟 층(120)을 처리하도록(예를 들어, 에칭) 사용될 수 있다. 타겟 층(120)은 실리콘, 실리콘 산화물, 실리콘 질화물, 금속, 또는 집적 회로 제조 단계 중에 마스크를 통해 선택적으로 처리되는(예를 들어, 에칭되는) 것을 필요로 하는 임의의 그외의 물질로 형성될 수 있다. 바람직한 실시예에서, 타겟 층(120)은 동일한 챔버에서 처리되지만, 웨이퍼는 또한 후속 처리를 위해 상이한 챔버로 이송될 수 있다. 타겟 층(120)은 바람직하게는 선택된 타겟 층에 대하여 적절한 에칭 화학을 사용하여 에칭된다.

<88> 에칭 정지(stop) 층(도시되지 않음)은 제1 하드 마스크 층(130)과 타겟 층(120) 사이에 사용될 수 있다. 에칭 정지 층은 타겟 층(120)의 조성에 따라, DARC 및 실리콘 질화물을 포함하는, 제2 하드 마스크 층(140)에 사용되는 물질들과 유사한 물질들로 구성될 수 있다. 에칭 정지 층은, 제1 하드 마스크 층(130)에 대한 패턴 전사 또는 제1 하드 마스크 층(130)의 제거 동안 등과 같은, 제1 하드 마스크 층(130)의 에칭 중에 타겟 층(120)에 대한 손상을 방지한다. 이것은 금속화(metallization) 층과 같이, 타겟 층(120)이 금속인 경우에 특히 중요하다. DDE 챔버에서 에칭된 금속은 챔버를 오염시키고 처리 속도를 감소시킬 수 있다. 타겟 층(120)이 노출된 금속 층을 포함하는 경우, 웨이퍼는 바람직하게는 추가의 처리를 위한 금속 에칭 챔버로 이송된다. 타겟 층의 처리(예를 들어, 에칭)가 완료되는 경우, 임의의 나머지 하드 마스크 물질은 습식 에칭 단계와 같은 공자의 에칭 프로세스들에 의해 제거될 수 있다. 도시된 실시예에서, 타겟 층 에칭 단계 중에 제2 하드 마스크 층(140)은 제1 하드 마스크 층(130)의 상부에 남겨진다. 그외의 실시예들에서, 제2 하드 마스크 층(140)은 패터닝된 제1 하드 마스크(130)를 통해 타겟 층(120)을 처리하기 전에 제거될 수 있다. 전술된 타겟 층 에칭 단계 후에, 금속화와 같은 추가의 단계들이 집적 회로들을 완성하기 위해 수행된다.

#### 리소그래피의 그외의 유형들에 대한 애플리케이션

<90> 예시된 실시예에서, 트림 단계는 포토리소그래피와 결합하여 사용된다. 그외의 실시예들에서, 트림 단계는 임프린트 리소그래피와 같은 그외의 유형들의 리소그래피와 결합하여 사용될 수 있다. 임프린트 리소그래피는 기판으로 패턴들을 전사하기 위해 강성의 기계적 템플릿(template)을 사용하는 기술이다. 임프린트 리소그래피 프로세스에서, 광 경화성 물질이 제2 하드 마스크 층 위에 배치된다. 다음으로, 강성의 투명한(예를 들어, 석영(quartz)) 템플릿이 상기로부터, 소프트 레지스트를 임프린트하거나 또는 몰딩하는, 광 경화성 물질과 접촉된다. 광 경화성 물질은 광 및 패턴의 애플리케이션에 의해 경화되는 한편, 템플릿은 경화된 물질을 몰딩한다. 다음으로, 패턴이 제2 하드 마스크 층으로 전사된다. 후속하여, 제2 하드 마스크는 수축되는 한편, 경화된 물질은 제2 하드 마스크 층의 상부에 존재하고 하부의 제1 하드 마스크 층은 하부의 반도체 기판을 보호한다.

#### 마스킹 구조들

<92> 본 발명의 다른 양태는 집적 회로 제조를 위한 마스킹 구조를 제공한다. 마스킹 구조는 도핑, 산화, 질화, 및 선택적 성막 등의 다양한 프로세스들을 위해 사용될 수 있다. 도 1D를 참조하면, 마스킹 구조는 타겟 층(120) 위에 형성되는 제1 하드 마스크 층(130), 제1 하드 마스크 층(130) 위에 형성되는 제2 하드 마스크 층(140), 및 제2 하드 마스크 층(140) 위에 형성되는 레지스트 층(150)을 포함할 수 있다. 일부의 실시예들에서 타겟 층(120)은 트렌치들이 형성될 실리콘 웨이퍼 자체를 나타낸다는 것이 이해될 것이다. 제2 하드 마스크 층(140)은 제1 하드 마스크 층(130)을 커버하도록 구성된 마스킹 부분들을 갖는 패턴을 포함한다. 레지스트 층(150)은 제2 하드 마스크 층(140)의 마스킹 부분들에 대응하는 마스킹 부분들을 갖는 패턴을 갖도록 구성된다. 제2 하드

마스크 층(140)의 마스킹 부분들의 각각의 노출된 측면들(141)은 등방성으로 에칭된다.

<93> 일 실시예에서, 제2 하드 마스크 층의 마스킹 부분들의 각각의 노출된 측면들은 적어도 5Å 만큼 에칭된다. 제2 하드 마스크 층의 마스킹 부분들의 각각의 노출된 측면들은 약 10Årms에서 약 100Årms 사이의 RMS(root mean square) 거칠기를 가질 수 있고, 더 바람직하게는 약 50Årms 아래의 RMS 거칠기를 가질 수 있으며, 가장 바람직하게는 약 10Årms에서 약 50Årms 사이의 RMS 거칠기를 가질 수 있다. 제2 하드 마스크 층의 마스킹 부분들의 라인폭들은 도 1D에 도시된 바와 같이 레지스트 층의 대응하는 마스킹 부분들의 라인폭들과 실질적으로 동일하게 될 수 있다. 이 구조는 트림 단계 중에 제2 하드 마스크 층에 대하여 비선택적인 에칭제를 사용함으로써 얻어질 수 있다.

<94> 그외의 실시예들에서, 제2 하드 마스크 층의 마스킹 부분들의 라인폭들은 레지스트 층의 대응하는 마스킹 부분들의 라인폭들보다 더 좁게 될 수 있다. 이 구조는 도 2B에 도시된 바와 같이 트림 단계에서 제2 하드 마스크 층에 대하여 고선택성을 갖는 에칭제를 사용함으로써 얻어질 수 있다. 제2 하드 마스크 층의 노출된 표면들(241)은 포토레지스트 층 아래로 리세스된다.

<95> 본 발명이 특정한 바람직한 실시예들을 사용하여 기술되었지만, 본 명세서에 전술된 모든 특징들 및 장점들을 제공하지 않는 실시예들을 포함하는, 본 기술 분야의 당업자들에게 명확하게 이해되는 그외의 실시예들도 본 발명의 범주 내에 존재한다. 따라서, 본 발명의 범주는 첨부된 청구범위의 참조에 의해서만 정의된다.

### 도면의 간단한 설명

<20> 도 1A 내지 도 1F는 본 발명의 실시예에 따른 집적 회로용 에칭 프로세스를 도시하는 획단면 개략도이다.

<21> 도 2A 내지 도 2C는 본 발명의 실시예에 따른 고선택성 에칭제를 사용하여 하드 마스크를 형성하는 부분적인 프로세스를 도시한다.

<22> 도 3A 및 도 3B는 본 발명의 실시예에 따른 BARC 층을 사용하여 하드 마스크를 형성하는 부분적인 프로세스를 도시한다.

<23> 도 4는 도 1D의 부분적으로 형성된 집적 회로의 부분적인 투시도이다.

<24> 도 5는 본 발명의 실시예에 따른, 하드 마스크 층에 대한 트림 속도(rate)를 도시하는 그래프이다.

<25> 도 6A 내지 도 6C는, 스캐닝 전자 현미경으로 취해진, 도 5에 도시된 트림 속도로 트리밍된 하드 마스크 패턴들의 평면도들의 현미경사진들이다.

<26> 도 7은 도 6C의 확대도이다.

<27> 도 8은, 스캐닝 전자 현미경으로 취해진, 도 7의 트리밍된 하드 마스크 패턴의 측횡단면 현미경사진이다.

<28> 도 9는 본 발명의 실시예에 따른, 다른 하드 마스크 층에 대한 트림 속도를 도시하는 그래프이다.

<29> 도 10A 내지 도 10C는, 스캐닝 전자 현미경으로 취해진, 도 9에 도시된 트림 속도로 트리밍된 하드 마스크 패턴들의 평면도들의 현미경사진들이다.

### 도면

#### 도면1A

도면1B

도면1C

도면1D

도면1E

도면1F

도면2A

도면2B

도면2C

도면3A

도면3B

도면4

도면5

도면6A

도면6B

도면6C

도면7

도면8

도면9

도면10A

도면10B

도면10C