(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6239130号

(P6239130)

(45) 発行日 平成29年11月29日(2017.11.29)

(24) 登録日 平成29年11月10日(2017.11.10)

(51) Int.Cl.

F 1

|                   |                  |             |              |             |

|-------------------|------------------|-------------|--------------|-------------|

| <b>G06F 12/00</b> | <b>(2006.01)</b> | <b>G06F</b> | <b>12/00</b> | <b>550E</b> |

| <b>G06F 12/06</b> | <b>(2006.01)</b> | <b>G06F</b> | <b>12/06</b> | <b>521A</b> |

| <b>G06F 1/32</b>  | <b>(2006.01)</b> | <b>G06F</b> | <b>1/32</b>  | <b>B</b>    |

請求項の数 13 (全 16 頁)

(21) 出願番号 特願2016-544034 (P2016-544034)

(86) (22) 出願日 平成26年9月19日 (2014.9.19)

(65) 公表番号 特表2016-534484 (P2016-534484A)

(43) 公表日 平成28年11月4日 (2016.11.4)

(86) 國際出願番号 PCT/US2014/056659

(87) 國際公開番号 WO2015/042469

(87) 國際公開日 平成27年3月26日 (2015.3.26)

審査請求日 平成29年6月7日 (2017.6.7)

(31) 優先権主張番号 14/033,233

(32) 優先日 平成25年9月20日 (2013.9.20)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ハウゼン・ロ

アメリカ合衆国・カリフォルニア・921

21・サン・ディエゴ・モアハウス・ドラ

イブ・5775

最終頁に続く

(54) 【発明の名称】作業負荷に従ってメモリバス帯域幅を低減するためのシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項1】

メモリシステムにおける電力消費を節約するための方法であって、

システムオンチップ(SoC)に存在する複数のメモリクライアントの各々を高性能使用事例または低性能使用事例に割り当てるステップと、

前記SoCに存在する前記複数のメモリクライアントのうちの1つから、メモリバスを介して前記SoCに結合されたダイナミックランダムアクセスメモリ(DRAM)メモリシステムにアクセスするためのメモリ要求を受信するステップであって、前記メモリ要求が、前記メモリクライアントの性能使用事例を示すチャネル幅サイズ変更ビットを含む、ステップと、

前記メモリ要求内の前記チャネル幅サイズ変更ビットから、前記メモリクライアントからの前記メモリ要求が前記メモリバスの全幅未満を使用するための前記低性能使用事例に対応すると判断するステップと、

前記メモリ要求について前記メモリバスを前記全幅未満に動的にサイズ変更することによって、前記低性能使用事例に対応する前記メモリ要求に対するメモリ電力消費を節約するステップと

を備え、

バス幅を前記動的にサイズ変更するステップが、前記バス幅を第1のチャネル幅から第2のチャネル幅に低減するステップを含み、

前記バス幅を前記第1のチャネル幅から前記第2のチャネル幅に前記低減するステップが、前記SoC内のSoC物理レイヤデバイスおよび前記DRAMメモリシステム内のメモリ物理レイ

10

20

ヤデバイスを無効にするステップを備える、

方法。

**【請求項 2】**

前記メモリ要求を送信する前記メモリクライアントが、前記SoCに存在する中央処理装置(CPU)、グラフィックス処理装置(GPU)、およびデジタル信号プロセッサ(DSP)のうちの1つを備える、請求項1に記載の方法。

**【請求項 3】**

前記メモリバスがNビットチャネルを備え、前記メモリバスのバス幅を前記動的にサイズ変更するステップが、前記Nビットチャネルを(N-M)ビットチャネルに低減するステップを備える、請求項1に記載の方法。 10

**【請求項 4】**

前記メモリバスがシングルメモリチャネルを備える、請求項1に記載の方法。

**【請求項 5】**

バス幅を前記動的にサイズ変更するステップがさらに、

前記DRAMメモリシステムによって定義される最小アクセス長(MAL)を維持するために、前記シングルメモリチャネルにわたってビート数を増加させるステップとを備える、請求項4に記載の方法。 20

**【請求項 6】**

前記メモリバスがnチャネルバスを備える、請求項1に記載の方法。

**【請求項 7】**

メモリシステムにおける電力消費を節約するためのシステムであって、

システムオンチップ(SoC)に存在する複数のメモリクライアントの各々を高性能使用事例または低性能使用事例に割り当てるための手段と、

前記SoCに存在する前記複数のメモリクライアントのうちの1つから、メモリバスを介して前記SoCに結合されたダイナミックランダムアクセスメモリ(DRAM)メモリシステムにアクセスするためのメモリ要求を受信するための手段であって、前記メモリ要求が、前記メモリクライアントの性能使用事例を示すチャネル幅サイズ変更ビットを含む、手段と、

前記メモリ要求内の前記チャネル幅サイズ変更ビットから、前記メモリクライアントからの前記メモリ要求が前記メモリバスの全幅未満を使用するための前記低性能使用事例に対応すると判断するための手段と。 30

前記メモリ要求について前記メモリバスを前記全幅未満に動的にサイズ変更することによって、前記低性能使用事例に対応する前記メモリ要求に対するメモリ電力消費を節約するための手段と

を備え、

バス幅を動的にサイズ変更するための前記手段が、前記バス幅を第1のチャネル幅から第2のチャネル幅に低減するための手段を備え、

前記バス幅を前記第1のチャネル幅から前記第2のチャネル幅に低減するための前記手段が、前記SoC内のSoC物理レイヤデバイスおよび前記DRAMメモリシステム内のメモリ物理レイヤデバイスを無効にするための手段を備える、

システム。 40

**【請求項 8】**

前記メモリ要求を送信する前記メモリクライアントが、前記SoCに存在する中央処理装置(CPU)、グラフィックス処理装置(GPU)、およびデジタル信号プロセッサ(DSP)のうちの1つを備える、請求項7に記載のシステム。

**【請求項 9】**

前記メモリバスがNビットチャネルを備え、前記メモリバスのバス幅を動的にサイズ変更するための前記手段が、前記Nビットチャネルを(N-M)ビットチャネルに低減するための手段を備える、請求項7に記載のシステム。

**【請求項 10】**

前記メモリバスがシングルメモリチャネルを備える、請求項7に記載のシステム。 50

**【請求項 1 1】**

バス幅を動的にサイズ変更するための前記手段がさらに、

前記DRAMメモリシステムによって定義される最小アクセス長(MAL)を維持するために、

前記シングルメモリチャネルにわたってビート数を増加させるための手段と

を備える、請求項10に記載のシステム。

**【請求項 1 2】**

前記メモリバスがnチャネルバスを備える、請求項7に記載のシステム。

**【請求項 1 3】**

請求項1乃至6の何れか1項に記載の方法を実施するための命令を含む、コンピュータブログラム。

10

**【発明の詳細な説明】****【背景技術】****【0 0 0 1】**

コンピューティングデバイス(たとえば、ポータブルコンピューティングデバイス、タブレットコンピュータ、モバイルフォンなど)は、より高いピーク性能要件に対応するために、より増加したメモリ入力/出力(I/O)速度を要求し続けている。ピーク性能要件に対処するために、より速いI/O速度およびより広いメモリバスを有するコンピューティングデバイスを設計することが一般的である。しかしながら、増加したメモリ速度を有するコンピューティングデバイスは、増加した電力消費を必要とする。増加した電力消費は高性能I/Oの使用事例に対する許容できるトレードオフであり得るが、多くのコンピューティングデバイスの使用事例の大半は高性能I/Oを必要としない。たとえば、高性能I/Oは、オーディオ再生、音声呼、ビデオ再生などの低性能から中性能の使用事例にとっては好ましくないことがある。

20

**【0 0 0 2】**

メモリI/O動作を「低電力」モードに再構成することによって比較的低い性能のI/O使用的電力消費を低減するための既存の解決策がある。通常、これはメモリI/Oがより低い周波数で実行されることを意味する。より高い周波数で信号完全性のために使用される終端抵抗器は、「低電力」モードの間、無効にされることがある。さらに、信号振幅の変更も必要となることがある。これは適用可能な使用事例の間に電力消費を低減するのに役立ち得るが、周波数切替えは、実装形態に応じて通常2μsから50μsの望ましくない待ち時間を持たず。

30

**【発明の概要】****【課題を解決するための手段】****【0 0 0 3】**

メモリシステムにおける電力消費を節約するためのシステムおよび方法が開示される。一実施形態は、メモリシステムにおける電力消費を節約するための方法である。1つのそのような方法は、システムオンチップ(SoC)に存在するメモリクライアントから、メモリバスを介してSoCに結合されたダイナミックランダムアクセスメモリ(DRAM)メモリシステムにアクセスするためのメモリ要求を受信するステップと、メモリクライアントからのメモリ要求がメモリバスの全幅未満を使用するための性能使用事例に対応すると判断するステップと、メモリバスを全幅未満に動的にサイズ変更することによって、性能使用事例に対応するメモリ要求に対するメモリ電力消費を節約するステップとを備える。

40

**【0 0 0 4】**

別の実施形態は、メモリシステムにおける電力消費を節約するためのシステムである。1つのそのようなシステムは、DRAMメモリシステムと、システムオンチップ(SoC)とを備える。SoCは、メモリバスを介してDRAMメモリシステムに結合される。SoCは、1つまたは複数のメモリクライアントからの、DRAMメモリシステムにアクセスするためのメモリ要求を処理するための1つまたは複数のメモリコントローラを備える。メモリコントローラは、メモリバスのバス幅を動的にサイズ変更することによって、メモリ電力消費を選択的に節約するように構成される。

50

**【0005】**

図中、別段に規定されていない限り、同様の参照番号は、様々なる図の全体を通じて、同様の部分を指す。「102A」または「102B」などの文字指定を伴う参照番号の場合、文字指定は、同じ図に存在する2つの同様の部分または要素を区別することができる。参照番号がすべての図において同じ参照番号を有するすべての部分を包含する意図されるとき、参照番号の文字指定は省略される場合がある。

**【図面の簡単な説明】****【0006】**

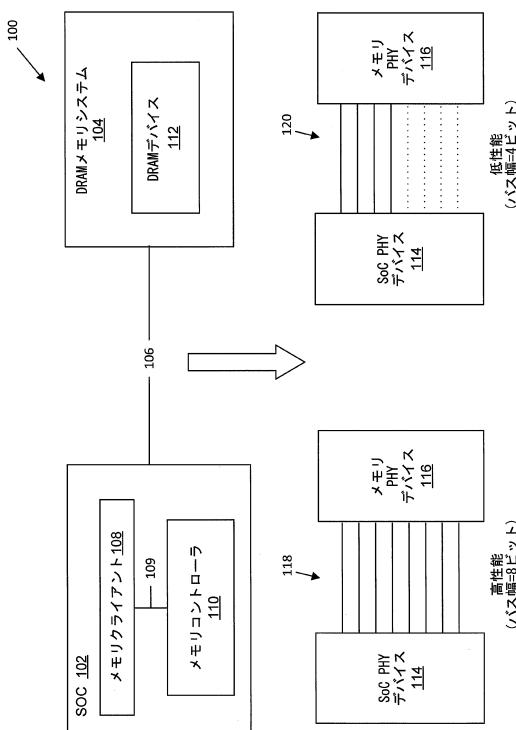

【図1】動的なメモリI/Oサイズ変更を使用してDRAMメモリ電力消費を節約するためのシステムの一実施形態のプロック図である。

10

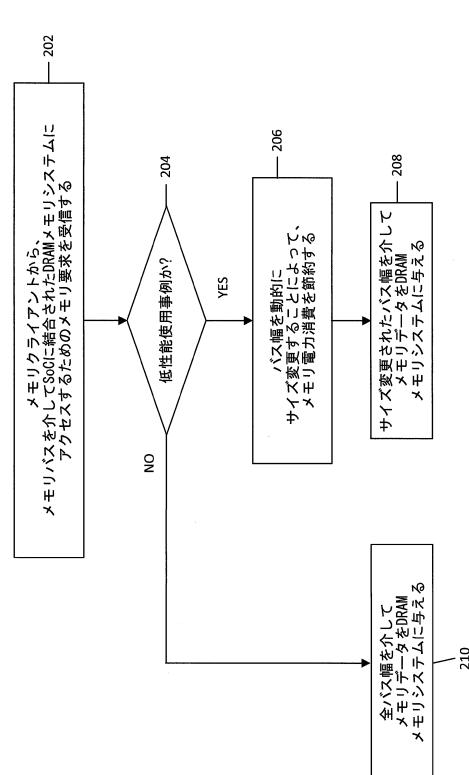

【図2】DRAMメモリ電力消費を節約するための図1のシステムで実施される方法の一実施形態を示すフローチャートである。

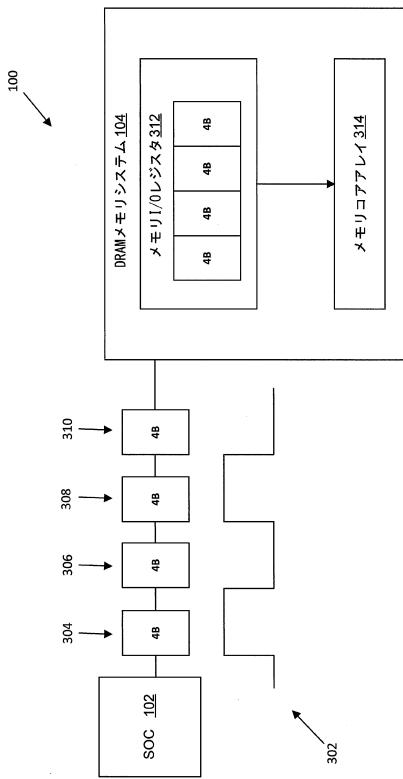

【図3】高性能モードの間の図1のシステムのシングルチャネル実施形態を示すプロック図である。

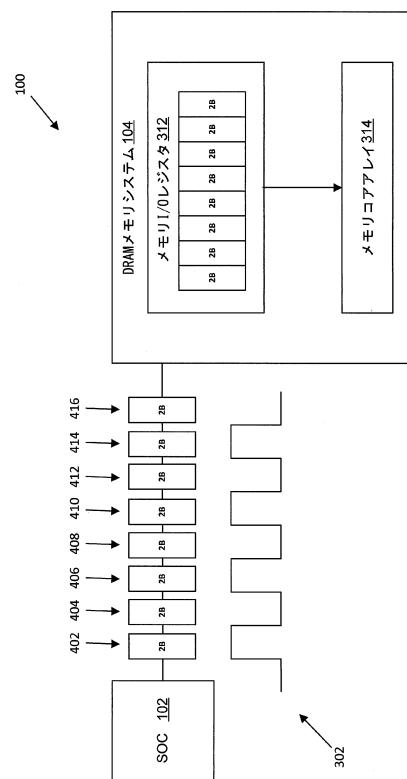

【図4】メモリ電力消費を節約するためにバス幅が動的にサイズ変更される低性能モードの間の図3のシステムを示すプロック図である。

【図5】高性能モードにおける図3のシステムの別のシングルチャネル実施形態を示すプロック図である。

【図6】低性能モードにおける図5のシステムを示す図である。

【図7】図1のシステムのデュアルチャネル実施形態を示すプロック図である。

20

【図8】図1のシステムの別のデュアルチャネル実施形態を示すプロック図である。

【図9】高性能モードにおける図8のシステムを示す図である。

【図10】低性能モードにおける図8のシステムを示す図である。

【図11】図1のシステムを組み込むポータブルコンピューティングデバイスの一実施形態のプロック図である。

**【発明を実施するための形態】****【0007】**

「例示的」という言葉は、本明細書では「一例、事例、または例示として役立つ」ことを意味するように使用される。「例示的」として本明細書で説明するいずれの態様も、必ずしも他の態様よりも好ましいか、または有利であると解釈されるわけではない。

30

**【0008】**

本明細書では、「アプリケーション」という用語は、オブジェクトコード、スクリプト、バイトコード、マークアップ言語ファイル、およびパッチなどの実行可能なコンテンツを有するファイルも含み得る。加えて、本明細書で言及する「アプリケーション」は、開封される必要があり得るドキュメント、またはアクセスされる必要がある他のデータファイルなどの本質的に実行可能ではないファイルも含み得る。

**【0009】**

「コンテンツ」という用語は、オブジェクトコード、スクリプト、バイトコード、マークアップ言語ファイル、およびパッチなどの実行可能なコンテンツを有するファイルも含み得る。加えて、本明細書で言及する「コンテンツ」は、開封される必要があり得るドキュメント、またはアクセスされる必要がある他のデータファイルなどの本質的に実行可能ではないファイルも含み得る。

40

**【0010】**

本明細書で使用する場合、「構成要素」、「データベース」、「モジュール」、「システム」などの用語は、ハードウェア、ファームウェア、ハードウェアとソフトウェアの組合せ、ソフトウェア、または実行中のソフトウェアのいずれかである、コンピュータ関連のエンティティを指すものとする。たとえば、構成要素は、限定はしないが、プロセッサ上で動作するプロセス、プロセッサ、オブジェクト、実行ファイル、実行スレッド、プログラム、および/またはコンピュータであり得る。例として、コンピューティングデバイス上で動作するアプリケーションと、コンピューティングデバイスの両方が、構成要素で

50

あり得る。1つまたは複数の構成要素は、プロセスおよび/または実行スレッド内に存在してもよく、構成要素は、1つのコンピュータに局所化されてもよく、および/または、2つ以上のコンピュータ間で分散されてもよい。加えて、これらの構成要素は、様々なデータ構造を記憶した様々なコンピュータ可読媒体から実行することができる。構成要素は、1つまたは複数のデータパケット(たとえば、信号によって、ローカルシステム、分散システム中の別の構成要素と対話する、および/または、インターネットなどのネットワークにわたって他のシステムと対話する、1つの構成要素からのデータ)を有する信号などに従って、ローカルプロセスおよび/またはリモートプロセスによって通信することができる。

#### 【0011】

10

本明細書では、「通信デバイス」、「ワイヤレスデバイス」、「ワイヤレス電話」、「ワイヤレス通信デバイス」、および「ワイヤレスハンドセット」という用語は、互換的に使用される。第3世代(「3G」)ワイヤレス技術および第4世代(「4G」)が出現したことによって、利用可能な帯域幅が拡大されたので、より多様なワイヤレス機能を備えた、より携帯が容易なコンピューティングデバイスが利用可能になっている。したがって、ポータブルコンピューティングデバイスは、セルラー電話、ペーパーレス、PDA、スマートフォン、ナビゲーションデバイス、またはワイヤレス接続もしくはワイヤレスリンクを有するハンドヘルドコンピュータを含み得る。

#### 【0012】

20

図1は、動的なメモリ入力/出力(I/O)サイズ変更を使用してメモリ電力消費を節約するためのシステム100を示す。システム100は、パーソナルコンピュータと、ワークステーションと、サーバと、セルラー電話、携帯情報端末(PDA)、ポータブルゲームコンソール、パームトップコンピュータ、またはタブレットコンピュータなどのポータブルコンピューティングデバイス(PCD)とを含む任意のコンピューティングデバイスに実装され得る。図1の実施形態に示すように、システム100は、メモリバス106を介してDRAMメモリシステム104に結合されたシステムオンチップ(SoC)102を備える。SoC102は、DRAMメモリシステム104からのメモリリソースを要求する1つまたは複数のメモリクライアント108を含む、様々なオンチップ構成要素を備える。メモリクライアント108は、1つまたは複数の処理装置(たとえば、中央処理装置(CPU)、グラフィックス処理装置(GPU)、デジタル信号プロセッサ(DSP)、ディスプレイプロセッサなど)、ビデオエンコーダ、またはDRAMメモリシステム104への読み取り/書き込みアクセスを要求する他のクライアントを備え得る。メモリクライアント108は、SoCバス109を介して1つまたは複数のメモリコントローラ110に接続される。

30

#### 【0013】

メモリコントローラ110は、DRAMメモリシステム104への読み取り/書き込みメモリ要求を受信し、処理するように構成される。メモリデータは、専用メモリチャネルを介してそれぞれのDRAMデバイス112に接続される1つまたは複数のメモリコントローラ110間で分散され得る。任意の数のDRAMデバイス112、メモリコントローラ110、およびメモリチャネルが、メモリの任意の望ましいタイプ、サイズ、および構成(たとえば、ダブルデータレート(DDR)メモリ)を有するシステム100で使用され得ることを諒解されたい。

#### 【0014】

40

図1に示すように、システム100は、適切な使用事例に2つの異なるチャネルモード、すなわち、(1)高性能チャネルモード118、および(2)低性能チャネルモード120を選択的に与えるように構成される。高性能使用事例は、メモリバス106の全幅を使用して高性能チャネルモードで処理され得る。図1の例では、メモリバス106の全幅は8ビットを備え得る。各ビットは、別個のピン、接続、または他の物理レイヤ構成要素を備え得る。高性能が必要とされない様々な使用事例(たとえば、オーディオ再生、携帯電話での音声呼、ビデオ再生など)があり得、メモリバス106の全幅未満を介して好適な性能が与えられ得ることを諒解されたい。比較的低い性能の使用事例(または電力節約が性能よりも好ましい他の状況)の場合、メモリ電力は、メモリバス106の幅を動的にサイズ変更することによって節約され得る。この点について、低性能使用事例は、メモリ電力の低減をもたらしながら、好

50

適な性能にメモリバス106の全幅未満が与えられ得る任意の状況を備え得ることを諒解されたい。たとえば、8ビットメモリバス106は、低性能チャネルモード120の間、4ビットメモリバス106にサイズ変更され得る。図1の実施形態に示すように、チャネル幅は、メモリバス106を備える8つのピン、接続、または他の物理レイヤ構成要素のうちの(破線で示す)4つを無効にすることによって2分の1に低減され得る。

#### 【0015】

図2は、動的なメモリI/Oサイズ変更を使用してメモリ電力を節約するためのシステム100によって実施される方法200の一実施形態を示す。ブロック202において、DRAMメモリシステム104にアクセスするためのメモリ要求は、メモリクライアント108から受信される。決定ブロック204において、システム100は、メモリ要求がメモリバス106の全幅を使用して高性能チャネルモード118で処理されるべきか、またはメモリバスの全幅未満を使用して低性能チャネルモード120で処理されるべきかを判断する。メモリクライアント108は電力または性能の選好を要求し得ることを諒解されたい。たとえば、一実施形態では、チャネル幅サイズ変更ビットは、削減するために読み取り/書き込みコマンドに含まれ得、これは追加の信号ピンのニーズを削減し得る。電力または性能の選好は、システム100によって検証され得る。他の実施形態では、メモリクライアント108は、予想されたまたは計算された性能要件に基づいて、高性能チャネルモード118または低性能チャネルモード120のいずれかに割り当てられ得る。システム100が高性能使用事例を判断した場合、ブロック210において、メモリデータは全バス幅を使用してDRAMメモリシステム104に与えられ得る。高性能が必要とされないまたは電力節約が性能よりも好ましいとシステム100が判断した場合、ブロック206において、メモリ電力はメモリバス106を動的にサイズ変更することによって節約され得る。ブロック208において、メモリデータは、サイズ変更されたバス幅を介してDRAMメモリシステム104に与えられ得る。

10

20

#### 【0016】

動的なメモリI/Oサイズ変更はシングルチャネルメモリシステムまたはマルチチャネルメモリシステムで実施され得ることを諒解されたい。図3～図6は、動的なメモリI/Oサイズ変更のシングルチャネル実装形態の様々な実施形態を示す。

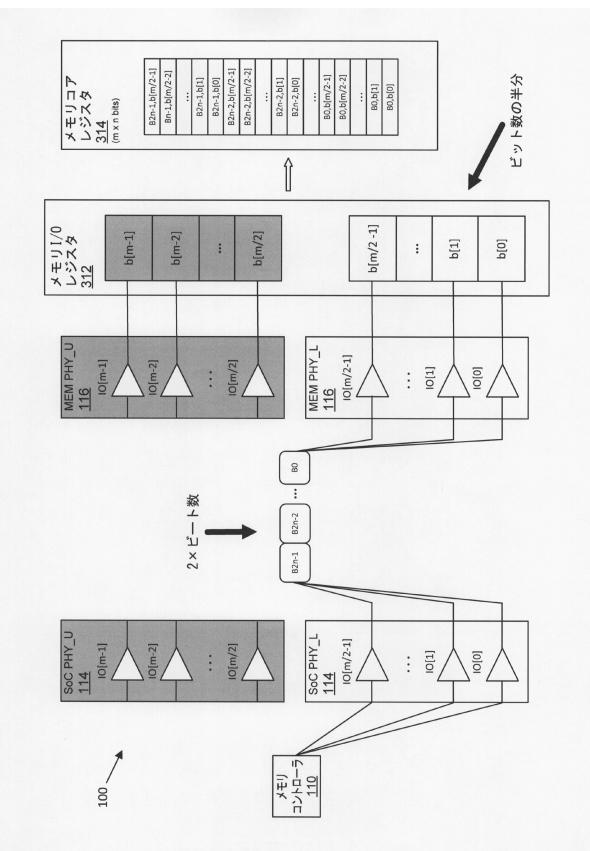

#### 【0017】

図3および図4は、DRAMメモリシステム104がLPDDR2メモリデバイスを備え、メモリバス106が32ビットバスを備える一例を示す。当技術分野で知られているように、DRAMメモリトランザクションは、クロック302に基づいたメモリバス106にわたる複数のビートから成る。ビート数(「バースト長」)は、固定で、DRAMデバイスのタイプに依存し得る。たとえば、DDRタイプデバイスは2のバースト長を有し、DDR2タイプデバイスは4のバースト長を有し、DDR3タイプデバイスは8のバースト長を有する、といった具合である。ビート数とバス幅の組合せは、最小アクセス長(MAL:minimum access length)として定義される。図3および図4の例における32ビット幅のLPDDR2は、各ビート304、306、308および310が4バイトを備える、16バイトのMALサイズ(4ビート×32ビット=128ビット=16バイト)を有する。DRAMメモリシステム104は、メモリバス106を介してビートの入来ストリームを受信し、入来ストリームをMALサイズのレジスタ(たとえば、メモリI/Oレジスタ312)に配置し、次いでそのレジスタがDRAMメモリコアアレイ314にロードされる、内部論理構造を備える。

30

40

#### 【0018】

図3は、全32ビットバス幅が使用される高性能チャネルモードにおける例示的なシステム100の動作を示す。図4は、32ビットチャネル幅が16ビットチャネル幅に2分の1に動的にサイズ変更される低性能チャネルモードの動作を示す。バス幅の半分を用いた事前定義された16バイトのMALサイズを維持するために、SoC102はビート数を2倍にするように構成される。図4に示すように、各ビート402、404、406、408、410、412、414、および416は、高性能チャネルモードで使用される4バイトではなく、2バイトで構成される。DRAMメモリシステム104は、8つの2バイトビートの入来ストリームを受信し、その入来ストリームを同じ16バイトのMALサイズのメモリI/Oレジスタ312に配置する。次いで、メモリI/Oレジスタ312は、DRAM内部構造を再構成するか、または低性能チャネルモードで利用可能な有効

50

なメモリ空間の量を低減する必要なしに、高性能チャネルモードの場合と同じ方法でメモリコアアレイ314にロードされる。

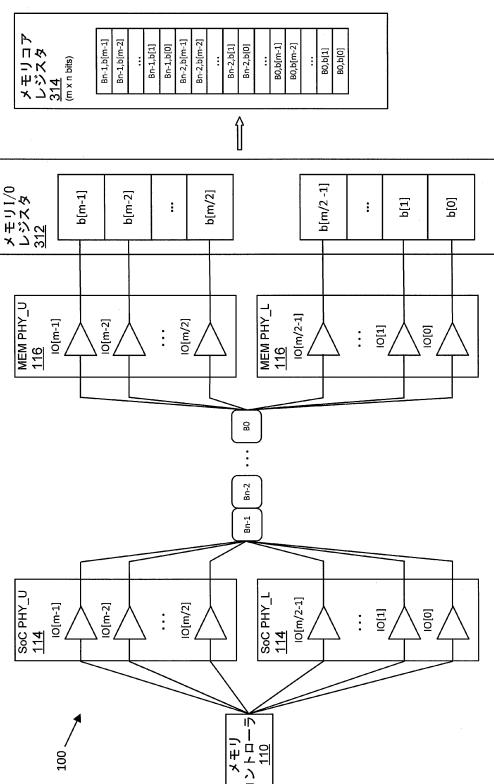

#### 【 0 0 1 9 】

図5および図6は、動的なメモリI/Oサイズ変更のシングルチャネル実装形態の別の実施形態を示す。図5は、高性能チャネルモードにおけるシステム100を示す。図6は、低性能チャネルモードにおけるシステム100を示す。SoC102は、1組のSoC物理レイヤデバイス114(SoC PHY\_UおよびSoC PHY\_L)とそれぞれのメモリ物理レイヤデバイス116(Mem PHY\_UおよびMem PHY\_L)との間でDRAMメモリシステム104へのメモリ要求を処理するためのメモリコントローラ110を備える。DRAMメモリシステム104は、メモリI/Oレジスタ312と、メモリコアアレイ314とを備える。

10

#### 【 0 0 2 0 】

図5を参照すると、SoC物理レイヤデバイス114およびメモリ物理レイヤデバイス116は、ビットをメモリバス106に与え、対応するビットをメモリバス106から受信するためのラインドライバを備える。SoC PHY\_UおよびメモリPHY\_Uは、ラインドライバ $10[m-1], 10[m-2] \dots 10[m/2]$ を備え、 $m=$ チャネル幅である。SoC PHY\_LおよびメモリPHY\_Lは、ラインドライバ $10[m/2-1] \dots 10[1] \dots 10[0]$ を備える。図5にさらに示すように、メモリバス106は、 $n$ 個のビートを備えるシングルメモリチャネルを備え、 $n=$ ビート数、 $B=$ シングル $m$ ビットビート、および $b=$ ビート(B)内の個々のビットである。メモリI/Oレジスタ312は入来データを受信および記憶し、入来データはメモリコアアレイ314にロードされる。

#### 【 0 0 2 1 】

20

図6に示すように、低性能チャネルモードでは、チャネル幅が $m$ から $m/2$ に低減され、望ましい電力節約をもたらすためにSoC PHY\_UおよびメモリPHY\_Uが無効にされる。バス幅の半分( $m/2$ )を用いて事前定義されたMALサイズを維持するために、SoC102はビート数を2倍( $2n$ )にするように構成される。メモリI/Oレジスタ312はビート数の半分を受信および記憶し、ビート数の半分はメモリコアアレイ314にロードされる。

#### 【 0 0 2 2 】

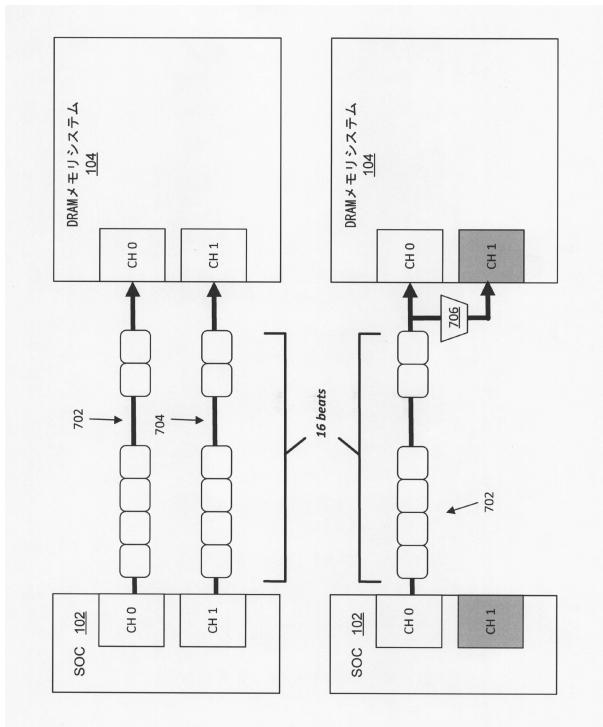

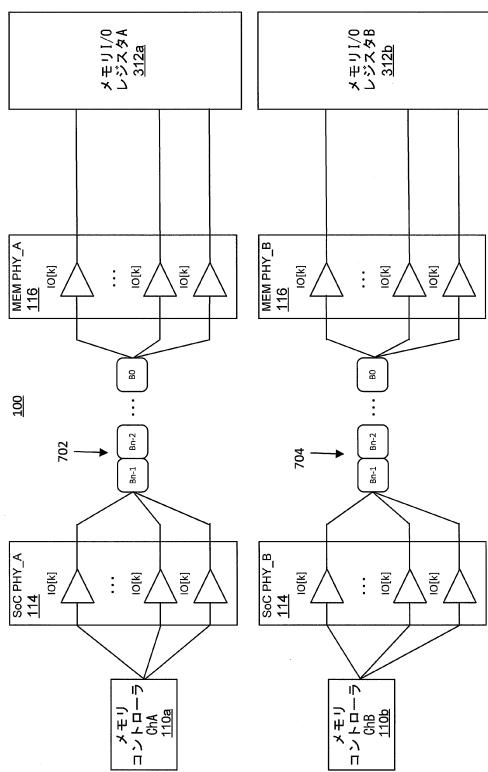

図7は、動的なメモリI/Oサイズ変更のデュアルチャネル実装形態の一実施形態を示す。SoC102およびDRAMメモリシステム104は、2つのメモリチャネル702および704(Ch0およびCh1)を備え得る。(図7の上の図に示す)高性能使用事例では、両方のチャネル702および704がアクティブであり、SoC:Ch0からの16ビートのデータがDRAM:Ch0に行き、SoC:Ch1からの16ビートのデータがDRAM:Ch1に行く。

30

#### 【 0 0 2 3 】

比較的低い性能の使用事例が所望されるとき、システム100は、たとえば、メモリチャネルのうちの1つを無効にすることによって、メモリチャネル幅のサイズを動的に再構成し得る。図7の下の図に示すように、所望の電力節約を実現するためにメモリチャネル704が無効にされ得る。アクティブなメモリチャネル702は、マルチプレクサ706によってデータがDRAM:Ch0とDRAM:Ch1との間で多重化された16ビートを備える。マルチプレクサ706はデータパス中の様々なポイント(たとえば、メモリI/Oレジスタ312の前または後、DRAMの内部または外部など)に配置され得ることを諒解されたい。

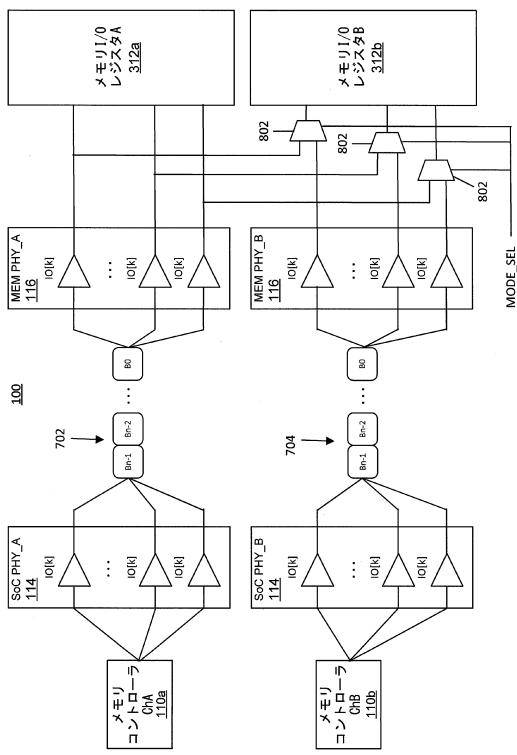

#### 【 0 0 2 4 】

40

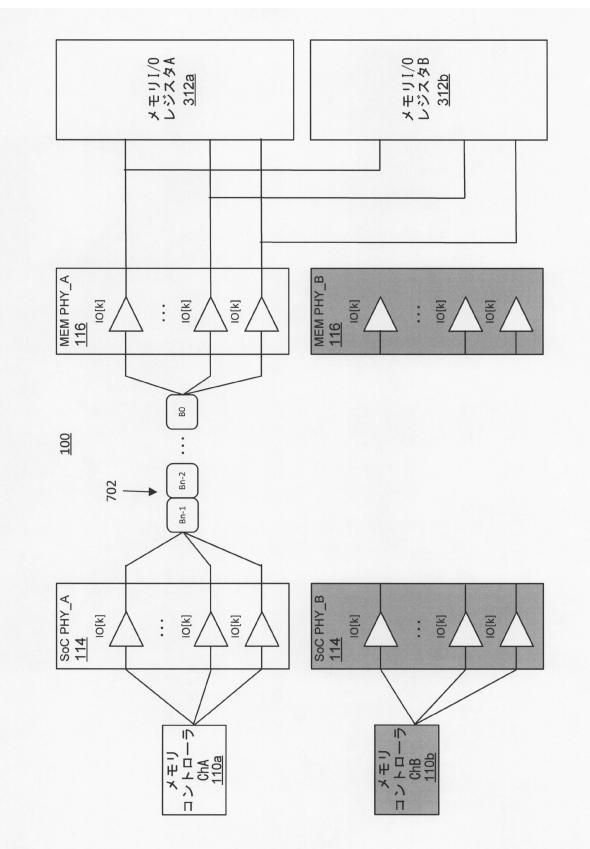

図8～図10は、動的なメモリI/Oサイズ変更のデュアルチャネル実装形態の別の実施形態を示し、図5および図6の場合と同じ参照記号、すなわち、 $m=$ チャネル幅、 $n=$ ビート数、および $B=$ シングル $m$ ビットビートに従う。図8に示すように、SoC102は2つのメモリコントローラ110aおよび110bを備える。メモリコントローラ110aは、SoC PHY\_AとメモリPHY\_Aとの間でDRAMメモリシステム104へのメモリ要求を処理するためのメモリチャネル702に対応する。メモリコントローラ110bは、SoC PHY\_BとメモリPHY\_Bとの間でDRAMメモリシステム104へのメモリ要求を処理するためのメモリチャネル704に対応する。高性能動作モード(図8および図9)では、メモリPHY\_Aからのメモリデータが受信され、メモリI/Oレジスタ312aに記憶される。メモリPHY\_Bからのメモリデータが受信され、メモリI/Oレジスタ312bに記憶される。

50

**【 0 0 2 5 】**

図8～図10にさらに示すように、SoC物理レイヤデバイス114aおよび114bならびにメモリ物理レイヤデバイス116aおよび116bは、複数のラインドライバ10[k]を備え得、 $m=$ チャネル幅、 $0 \leq k \leq m-1$ である。図8を参照すると、メモリPHY\_Aラインドライバ10[m-1]およびメモリPHY\_Bラインドライバ10[m-1]は、どのデータがメモリI/Oレジスタ312bに与えられるかを(MODE\_SELを介して)制御するためのマルチプレクサ802への入力を備え得る。低性能動作モード(図10)では、メモリバス幅を半分にし、所望の電力節約をもたらすために、メモリチャネル704が無効にされ得る。マルチプレクサ802は、メモリPHY\_Aラインドライバ10[m-1]からのデータをメモリI/Oレジスタ312aまたはメモリI/Oレジスタ312bのいずれかに選択的に与え得る。その他のメモリPHY\_AおよびメモリPHY\_Bラインドライバ10[k]が同様に多重化され得ることを諒解されたい。10

**【 0 0 2 6 】**

図5～図10に示す実施形態は、SoC102からのデータがDRAMメモリシステム104に書き込まれ得るメモリ書込み動作を実施することを諒解されたい。当業者は、上記で説明した方法が逆方向で適用され得ることと、DRAMメモリシステム104からのデータがSoC102に戻されるメモリ読み取り動作の間に電力節約が得られることとを諒解されよう。

**【 0 0 2 7 】**

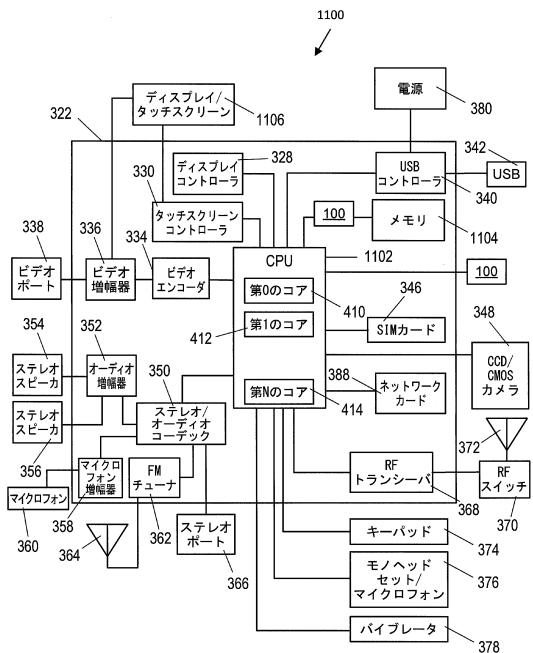

上述のように、システム100は任意の望ましいコンピューティングシステムに組み込まれ得る。図11は、例示的なポータブルコンピューティングデバイス(PCD)1100に組み込まれたシステム100を示す。システム100のいくつかの構成要素はSoC322(図11)に含まれ得るが、他の構成要素(たとえば、DRAMメモリシステム104)はSoC322に結合された外部構成要素を備え得ることが容易に諒解されよう。SoC322は、マルチコアCPU1102を含み得る。マルチコアCPU1102は、第0のコア410、第1のコア412および第Nのコア414を含み得る。コアのうちの1つは、たとえば、グラフィックス処理装置(GPU)を備え、他のコアのうちの1つまたは複数は、CPUを備え得る。20

**【 0 0 2 8 】**

ディスプレイコントローラ328およびタッチスクリーンコントローラ330は、CPU1102に結合され得る。一方、オンチップシステム322の外部にあるタッチスクリーンディスプレイ1106は、ディスプレイコントローラ328およびタッチスクリーンコントローラ330に結合され得る。30

**【 0 0 2 9 】**

図11は、ビデオエンコーダ334、たとえば位相反転線(PAL)エンコーダ、順次式カラーメモリ(SECAM)エンコーダ、または全米テレビジョン方式委員会(NTSC)エンコーダがマルチコアCPU1102に結合されることをさらに示す。さらに、ビデオ増幅器336は、ビデオエンコーダ334およびタッチスクリーンディスプレイ1106に結合される。また、ビデオポート338は、ビデオ増幅器336に結合される。図11に示すように、ユニバーサルシリアルバス(USB)コントローラ340は、マルチコアCPU1102に結合される。また、USBポート342は、USBコントローラ340に結合される。メモリ1104および加入者識別モジュール(SIM)カード346も、マルチコアCPU1102に結合され得る。メモリ1104は、SoC322に存在するか、または(図1に示すように)SoC322に結合され得る。メモリ1104は、上記で説明したように、DRAMメモリシステム104(図1)を備え得る。40

**【 0 0 3 0 】**

さらに、図11に示すように、デジタルカメラ348は、マルチコアCPU1102に結合され得る。例示的な態様では、デジタルカメラ348は、電荷結合デバイス(CCD)カメラまたは相補型金属酸化物半導体(CMOS)カメラである。

**【 0 0 3 1 】**

図11にさらに示すように、ステレオオーディオコーダ-デコーダ(コーデック)350は、マルチコアCPU1102に結合され得る。さらに、オーディオ増幅器352は、ステレオオーディオコーデック350に結合され得る。例示的な態様では、第1のステレオスピーカ354および第2のステレオスピーカ356は、オーディオ増幅器352に結合される。図11は、マイクロフォン50

増幅器358もステレオオーディオコーデック350に結合され得ることを示す。加えて、マイクロフォン360は、マイクロフォン増幅器358に結合され得る。特定の態様では、周波数変調(FM)ラジオチューナ362は、ステレオオーディオコーデック350に結合され得る。また、FMアンテナ364は、FMラジオチューナ362に結合される。さらに、ステレオヘッドフォン366は、ステレオオーディオコーデック350に結合され得る。

#### 【0032】

図11は、無線周波(RF)トランシーバ368がマルチコアCPU1102に結合され得ることをさらに示す。RFスイッチ370は、RFトランシーバ368およびRFアンテナ372に結合され得る。図11に示すように、キーパッド374は、マルチコアCPU1102に結合され得る。また、マイクロフォンを備えたモノヘッドセット376は、マルチコアCPU1102に結合され得る。さらに、バイブレータデバイス378は、マルチコアCPU1102に結合され得る。10

#### 【0033】

図11はまた、電源380がオンチップシステム322に結合され得ることを示す。特定の態様では、電源380は電力を必要とするPCD1100の様々な構成要素に電力を供給する直流(DC)電源である。さらに、特定の態様では、電源は、充電式DCバッテリー、または交流(AC)電源に接続されたAC-DC変換器から得られるDC電源である。

#### 【0034】

図11は、PCD1100がデータネットワーク、たとえばローカルエリアネットワーク、パーソナルエリアネットワーク、任意の他のネットワークにアクセスするために使用され得るネットワークカード388も含み得ることをさらに示す。ネットワークカード388は、Bluetooth(登録商標)ネットワークカード、WiFiネットワークカード、パーソナルエリアネットワーク(PAN)カード、パーソナルエリアネットワーク超低電力技術(PeANUT)ネットワークカード、テレビジョン/ケーブル/衛星チューナ、または当技術分野でよく知られている任意の他のネットワークカードであり得る。さらに、ネットワークカード388は、チップに組み込まれることがあり、すなわち、ネットワークカード388は、チップ内のフルソリューションであってもよく、別個のネットワークカード388でなくてもよい。20

#### 【0035】

図11に示すように、タッチスクリーンディスプレイ1106、ビデオポート338、USBポート342、カメラ348、第1のステレオスピーカ354、第2のステレオスピーカ356、マイクロフォン360、FMアンテナ364、ステレオヘッドフォン366、RFスイッチ370、RFアンテナ372、キーパッド374、モノヘッドセット376、バイブレータ378、および電源380は、オンチップシステム322の外部にあってもよい。30

#### 【0036】

本明細書で説明する方法ステップのうちの1つまたは複数は、上記で説明したモジュールなどのコンピュータプログラム命令としてメモリに記憶され得ることを諒解されたい。これらの命令は、本明細書で説明する方法を実行するために、対応するモジュールと組み合わせるかまたは協働して、任意の好適なプロセッサによって実行され得る。

#### 【0037】

本発明が説明した通りに機能するように、本明細書に記載されたプロセスまたはプロセスフロー内の特定のステップが他のステップよりも先行するのは当然である。しかしながら、そのような順序またはシーケンスが本発明の機能を変えない場合、本発明は記載されたステップの順序に限定されない。すなわち、本発明の範囲および趣旨から逸脱することなく、いくつかのステップは、他のステップの前に実行されるか、後に実行されるか、または他のステップと並行して(実質的に同時に)実行される場合があることを認識されたい。場合によっては、本発明から逸脱することなく、いくつかのステップが省略されてもよく、または実行されなくてもよい。さらに、「その後」、「次いで」、「次に」などの言葉は、ステップの順序を限定するものではない。これらの言葉は、単に例示的な方法の説明を通じて読者を導くために使用されている。40

#### 【0038】

加えて、プログラミングの当業者は、たとえば本明細書内のフローチャートおよび関連50

する説明に基づいて、コンピュータコードを書くか、または適切なハードウェアおよび/もしくは回路を識別して、開示された発明を容易に実施することができる。

#### 【0039】

したがって、特定の1組のプログラムコード命令または詳細なハードウェアデバイスの開示は、本発明をどのように製作および使用すべきかについて適切に理解するために必要であるとは見なされない。特許請求されるコンピュータ実施プロセスの発明性のある機能は、上記の説明において、かつ様々なプロセスフローを示し得る図面とともに、より詳細に説明される。

#### 【0040】

1つまたは複数の例示的な態様では、説明した機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せで実施され得る。ソフトウェアで実施される場合、機能は、1つまたは複数の命令もしくはコードとして、コンピュータ可読媒体上に記憶されるか、またはコンピュータ可読媒体上で送信され得る。コンピュータ可読媒体は、ある場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む、コンピュータ記憶媒体と通信媒体の両方を含む。記憶媒体は、コンピュータによってアクセスされ得る任意の利用可能な媒体であり得る。限定ではなく例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、NANDフラッシュ、NORフラッシュ、M-RAM、P-RAM、R-RAM、CD-ROMもしくは他の光ディスクストレージ、磁気ディスクストレージもしくは他の磁気記憶デバイス、または命令もしくはデータ構造の形態で所望のプログラムコードを搬送もしくは記憶するために使用され得、コンピュータによってアクセスされ得る任意の他の媒体を備え得る。

10

20

#### 【0041】

また、任意の接続が適切にコンピュータ可読媒体と呼ばれる。たとえば、ソフトウェアが、同軸ケーブル、光ファイバケーブル、ツイストペア、デジタル加入者線(「DSL」)、または赤外線、無線、およびマイクロ波などのワイヤレス技術を使用してウェブサイト、サーバ、または他のリモートソースから送信される場合、同軸ケーブル、光ファイバケーブル、ツイストペア、DSL、または赤外線、無線、およびマイクロ波などのワイヤレス技術は、媒体の定義に含まれる。

#### 【0042】

本明細書で使用する場合、ディスク(disk)およびディスク(disc)は、コンパクトディスク(disc)(「CD」)、レーザディスク(disc)、光ディスク(disc)、デジタル多用途ディスク(disc)(「DVD」)、フレキシブルディスク(disk)およびブルーレイディスク(disc)を含み、ディスク(disk)は通常、データを磁気的に再生し、ディスク(disc)は、データをレーザで光学的に再生する。上記の組合せもコンピュータ可読媒体の範囲内に含まれるべきである。

30

#### 【0043】

代替実施形態は、本発明の趣旨および範囲から逸脱することなく、本発明が関係する技術分野の当業者に明らかとなろう。したがって、選択された態様について図示し詳細に説明してきたが、以下の特許請求の範囲によって定義されるように、本発明の趣旨および範囲から逸脱することなく、各態様において様々な置換および改変が行われ得ることが理解されよう。

40

#### 【符号の説明】

#### 【0044】

- 100 システム

- 102 システムオンチップ、SoC

- 104 DRAMメモリシステム

- 106 メモリバス

- 108 メモリクライアント

- 109 SoCバス

- 110、110a、110b メモリコントローラ

50

|               |                                       |    |

|---------------|---------------------------------------|----|

| 112           | DRAMデバイス                              |    |

| 114           | SoC物理レイヤデバイス                          |    |

| 116           | メモリ物理レイヤデバイス                          |    |

| 118           | 高性能チャネルモード                            |    |

| 120           | 低性能チャネルモード                            |    |

| 200           | 方法                                    |    |

| 302           | クロック                                  |    |

| 304           | ビート                                   |    |

| 306           | ビート                                   |    |

| 308           | ビート                                   | 10 |

| 310           | ビート                                   |    |

| 312、312a、312b | メモリI/Oレジスタ                            |    |

| 314           | DRAMメモリコアアレイ、メモリコアアレイ、メモリコアレジスタ       |    |

| 322           | SoC                                   |    |

| 328           | ディスプレイコントローラ                          |    |

| 330           | タッチスクリーンコントローラ                        |    |

| 334           | ビデオエンコーダ                              |    |

| 336           | ビデオ増幅器                                |    |

| 338           | ビデオポート                                |    |

| 340           | ユニバーサルシリアルバス(USB)コントローラ               | 20 |

| 342           | USBポート                                |    |

| 346           | 加入者識別モジュール(SIM)カード                    |    |

| 348           | デジタルカメラ                               |    |

| 350           | ステレオオーディオコーダ-デコーダ(コーデック)、ステレオオーディオコーデ |    |

| ツク            |                                       |    |

| 352           | オーディオ増幅器                              |    |

| 354           | 第1のステレオスピーカ                           |    |

| 356           | 第2のステレオスピーカ                           |    |

| 358           | マイクロフォン増幅器                            |    |

| 360           | マイクロフォン                               | 30 |

| 362           | ラジオチューナ                               |    |

| 364           | FMアンテナ                                |    |

| 366           | ステレオヘッドフォン                            |    |

| 368           | 無線周波(RF)トランシーバ、RFトランシーバ               |    |

| 370           | RFスイッチ                                |    |

| 372           | RFアンテナ                                |    |

| 374           | キーパッド                                 |    |

| 376           | モノヘッドセット                              |    |

| 378           | バイブレータ                                |    |

| 380           | 電源                                    | 40 |

| 388           | ネットワークカード                             |    |

| 402           | ビート                                   |    |

| 404           | ビート                                   |    |

| 406           | ビート                                   |    |

| 408           | ビート                                   |    |

| 410           | ビート                                   |    |

| 412           | ビート                                   |    |

| 414           | ビート                                   |    |

| 416           | ビート                                   |    |

| 702           | メモリチャネル                               | 50 |

- 704 メモリチャネル

706 マルチプレクサ

1102 マルチコアCPU

1104 メモリ

1100 ポータブルコンピューティングデバイス、PCD

【図1】

【図2】

【図3】

【 図 4 】

【 四 5 】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

(72)発明者 デクスター・チュン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライヴ・577

5

審査官 後藤 彰

(56)参考文献 国際公開第2012/145432(WO,A2)

特開2010-181998(JP,A)

国際公開第2013/009442(WO,A2)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 00

G 06 F 12 / 06

G 06 F 1 / 32