(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-105277

(P2012-105277A)

(43) 公開日 平成24年5月31日(2012.5.31)

(51) Int.Cl.

HO3K 19/0185 (2006.01)

F 1

HO3K 19/00

1 O 1 D

テーマコード(参考)

5 J 0 5 6

審査請求 未請求 請求項の数 23 O L (全 34 頁)

(21) 出願番号 特願2011-247518 (P2011-247518)

(22) 出願日 平成23年11月11日 (2011.11.11)

(31) 優先権主張番号 61/412, 952

(32) 優先日 平成22年11月12日 (2010.11.12)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 10-2011-0005020

(32) 優先日 平成23年1月18日 (2011.1.18)

(33) 優先権主張国 韓国(KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do, Republic

of Korea

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】 レベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置

## (57) 【要約】

【課題】 向上された信頼性を有するレベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置が提供される。

【解決手段】 本発明のレベル変換器は、入力ノードを通じて受信される第1電圧ドメインの入力クロックに応じて第2電圧ドメインの出力クロックを発生する第1及び第2電圧変換回路を含み、第1及び第2電圧変換回路は同一の構造を有し、入力ノード及び出力ノードの間に並列に連結される。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

入力ノードと、

前記入力ノードを通じて受信される第1電圧ドメインの入力クロックに応じて第2電圧ドメインの出力クロックを発生するように構成される第1及び第2電圧変換回路と、

前記出力クロックを出力する出力ノードと、を含み、

前記第1及び第2電圧変換回路は同一な構造を有し、前記入力ノード及び出力ノードの間に並列に連結されるレベル変換器。

**【請求項 2】**

前記第1電圧変換回路は前記第2電圧ドメインで動作する少なくとも2つのインバータを含む請求項1に記載のレベル変換器。 10

**【請求項 3】**

前記第2電圧変換回路は前記第1電圧ドメインで動作する少なくとも1つのインバータと前記第2電圧ドメインで動作する少なくとも1つのインバータとを含む請求項1に記載のレベル変換器。

**【請求項 4】**

前記第2電圧ドメインで動作する少なくとも1つのインバータは前記第1電圧ドメインで動作する少なくとも1つのインバータの出力を受信するように構成される請求項3に記載のレベル変換器。

**【請求項 5】**

前記第1電圧変換回路は前記入力ノードの電圧にしたがって第2電圧又は接地電圧を出力する第1インバータ及び前記第1インバータの出力にしたがって前記第2電圧又は接地電圧を出力ノードに出力する第2インバータを含み、

前記第2電圧変換回路は前記入力ノードの電圧にしたがって前記第1電圧又は接地電圧を出力する第3インバータ及び前記第3インバータの出力にしたがって前記第2電圧又は接地電圧を前記出力ノードに出力する第4インバータを含む請求項1に記載のレベル変換器。

**【請求項 6】**

前記第1乃至第4インバータはCMOSインバータである請求項1に記載のレベル変換器。 30

**【請求項 7】**

第1電圧ドメインの第1クロックを発生するように構成される位相ロックループと、

前記第1クロックに応じて動作する周辺ブロック、オーディオブロック、ディスプレブロック、グラフィックブロック、イメージプロセシングブロック、及びコーデックブロックと、

前記第1クロックに基づいて、第2電圧ドメインの第2クロックを発生するレベル変換器と、

前記第2クロックに応じて動作するプロセッサーと、を含み、

前記レベル変換器は入力ノード及び出力ノードの間に並列に連結され、同一な構造を有する第1及び第2電圧変換回路と、を含むシステムオンチップ(SOC、System-On-Chip)。 40

**【請求項 8】**

前記第1電圧変換回路は前記第2電圧ドメインで動作し、直列に連結された第1及び第2インバータを含み、

前記第2電圧変換回路は前記第1電圧ドメインで動作する第3インバータ、及び前記第2電圧ドメインで前記第3インバータの出力に応じて動作する第4インバータを含む請求項7に記載のシステムオンチップ。

**【請求項 9】**

前記第2電圧ドメインの電圧レベルは前記第1電圧ドメインの電圧レベルより高い請求項7に記載のシステムオンチップ。 50

**【請求項 1 0】**

プロセッサーと、

前記プロセッサーの動作メモリーと、

前記プロセッサーの制御にしたがって外部と通信するように構成されるモデムと、

前記プロセッサーの制御にしたがってデータを格納するように構成される格納部と、

外部の信号を感知して前記プロセッサーに伝達するように構成される使用者インターフェイスと、

前記プロセッサーの制御にしたがって、ディスプレー部を通じて映像を表示するように構成されるディスプレー制御部と、

前記プロセッサーの制御にしたがって、スピーカーを通じて音を出力するように構成されるサウンド制御部と、

前記プロセッサーの制御にしたがってエンコーディング及びデコーディングを遂行するコーデック部と、

発振器の出力にしたがってクロックを発生するように構成されるクロック発生部と、

前記クロックに同期される第1電圧ドメインの第1クロックを発生する位相ロックループと、

前記第1クロックに応じて第2電圧ドメインの第2クロックを発生するように構成されるレベル変換器と、を含み、

前記プロセッサーは前記第2クロックに応じて動作し、

前記レベル変換器は入力ノード及び出力ノードの間に並列に連結され、同一な構造を有する第1及び第2電圧変換回路を含むマルチメディア装置。

**【請求項 1 1】**

前記レベル変換器は、

前記入力ノードの電圧にしたがって前記第2電圧ドメインの第2電圧又は接地電圧を出力する第1インバータと、

前記第1インバータの出力にしたがって前記第2電圧又は接地電圧を出力ノードに出力する第2インバータと、

前記入力ノードの電圧にしたがって前記第1電圧ドメインの第1電圧又は接地電圧を出力する第3インバータと、

前記第3インバータの出力にしたがって前記第2電圧又は接地電圧を前記出力ノードに出力する第4インバータと、を含む請求項10に記載のマルチメディア装置。

**【請求項 1 2】**

前記プロセッサー、動作メモリー、ディスプレー制御部、サウンド制御部、コーデック部、及び位相ロックループはシステムオンチップを構成し、

前記動作メモリー、ディスプレー制御部、サウンド制御部、及びコーデック部は前記第1クロックに応じて動作する請求項10に記載のマルチメディア装置。

**【請求項 1 3】**

前記プロセッサーの制御にしたがって、カメラから獲得されるイメージデータを処理するように構成されるイメージプロセシング部をさらに含む請求項10に記載のマルチメディア装置。

**【請求項 1 4】**

前記プロセッサー、ディスプレー制御部、サウンド制御部、イメージプロセシング部、動作メモリー、コーデック部、及び位相ロックループはシステムオンチップを構成し、

前記ディスプレー制御部、サウンド制御部、イメージプロセシング部、動作メモリー、及びコーデック部は前記第1クロックに応じて動作する請求項13に記載のマルチメディア装置。

**【請求項 1 5】**

前記プロセッサー、ディスプレー制御部、サウンド制御部、モデム、イメージプロセシング部、動作メモリー、コーデック部、及び位相ロックループはシステムオンチップに含まれ、

10

20

30

40

50

前記ディスプレー制御部、サウンド制御部、モデム、イメージプロセシング部、動作メモリー、及びコーデック部は前記第1クロックに応じて動作する請求項13に記載のマルチメディア装置。

**【請求項16】**

前記プロセッサー、ディスプレー制御部、サウンド制御部、動作メモリー、コーデック部、及び位相ロックループはシステムオンチップに含まれ、

前記ディスプレー制御部、サウンド制御部、動作メモリー、及びコーデック部は前記第1クロックに応じて動作する請求項13に記載のマルチメディア装置。

**【請求項17】**

前記プロセッサー、ディスプレー制御部、サウンド制御部、動作メモリー、及び位相ロックループはシステムオンチップに含まれ、10

前記ディスプレー制御部、サウンド制御部、及び動作メモリーは前記第1クロックに応じて動作する請求項13に記載のマルチメディア装置。

**【請求項18】**

前記プロセッサー、ディスプレー制御部、動作メモリー、及び位相ロックループはシステムオンチップに含まれ、

前記ディスプレー制御部、及び動作メモリーは前記第1クロックに応じて動作する請求項13に記載のマルチメディア装置。10

**【請求項19】**

前記プロセッサー、動作メモリー、及び位相ロックループはシステムオンチップに含まれ、20

前記動作メモリーは前記第1クロックに応じて動作する請求項13に記載のマルチメディア装置。

**【請求項20】**

前記プロセッサー、サウンド制御部、動作メモリー、及び位相ロックループはシステムオンチップに含まれ、

前記サウンド制御部及び動作メモリーは前記第1クロックに応じて動作する請求項13に記載のマルチメディア装置。

**【請求項21】**

前記プロセッサー、動作メモリー、モデム、格納部、使用者インターフェイス、ディスプレー制御部、ディスプレー部、サウンド制御部、スピーカー、発振器、クロック発生部、カメラ、イメージプロセシング部、コーデック部、及び位相ロックループはモバイル装置に含まれる請求項10に記載のマルチメディア装置。30

**【請求項22】**

前記プロセッサー、動作メモリー、モデム、格納部、使用者インターフェイス、ディスプレー制御部、ディスプレー部、サウンド制御部、スピーカー、発振器、クロック発生部、カメラ、イメージプロセシング部、コーデック部、及び位相ロックループはスマートテレビ(Smart Television)に含まれる請求項10に記載のマルチメディア装置。

**【請求項23】**

第1電圧変換回路と、40

入力ノードと出力ノードとの間に前記第1電圧変換回路と並列に連結される第2電圧変換回路と、を含み、

前記入力ノードに入力される第1電圧ドメインの第1クロックに応じて前記出力ノードから第2電圧ドメインの第2クロックが出力され、

前記第1クロックの立ち上がりエッジ及び前記第2クロックの立ち上がりエッジの間の遅延時間は前記第1クロックの立ち下がりエッジ及び前記第2クロックの立ち下がりエッジ間の遅延時間と同一であるレベル変換器。

**【発明の詳細な説明】**

**【技術分野】**

50

**【0001】**

本発明は電子回路に、より詳細にはレベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置に関する。

**【背景技術】****【0002】**

レベル変換器 (level shifter) は第1電圧ドメインの信号を受信し、第1電圧と異なる第2電圧ドメインの信号を出力する素子である。互いに異なる電圧を使用する複数の電圧ドメインの間でレベル変換器が使用される。

**【0003】**

システムオンチップ (SOC、System-On-Chip) は複数のIP (Intellectual Property) 及びプロセッサーを含む。プロセッサーはIPより速い動作速度を有する。プロセッサーの動作性能を向上させるために、プロセッサーへ供給されるクロックの電圧レベルはIPへ供給されるクロックの電圧レベルより高く設定され得る。プロセッサーへ供給されるクロックの電圧レベルを上昇させるために、システムオンチップ (SOC) でレベル変換器が使用され得る。10

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】韓国特許公開第10-2006-0119667号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

本発明の目的は向上された信頼性を有するレベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置を提供することにある。

**【課題を解決するための手段】****【0006】**

本発明の実施形態によるレベル変換器は、入力ノードと、前記入力ノードを通じて受信される第1電圧ドメインの入力クロックに応じて第2電圧ドメインの出力クロックを発生するように構成される第1及び第2電圧変換回路と、及び前記出力クロックを出力する出力ノードと、を含み、前記第1及び第2電圧変換回路は同一な構造を有し、前記入力ノード及び出力ノードの間に並列に連結される。30

**【0007】**

実施形態として、前記第1電圧変換回路は前記第2電圧ドメインで動作する少なくとも2つのインバータを含む。

**【0008】**

実施形態として、前記第2電圧変換回路は前記第1電圧ドメインで動作する少なくとも1つのインバータと前記第2電圧ドメインで動作する少なくとも1つのインバータとを含む。

**【0009】**

実施形態として、前記第2電圧ドメインで動作する少なくとも1つのインバータは前記第1電圧ドメインで動作する少なくとも1つのインバータの出力を受信するように構成される。

**【0010】**

実施形態として、前記第1電圧変換回路は前記入力ノードの電圧にしたがって第2電圧又は接地電圧を出力する第1インバータ及び前記第1インバータの出力にしたがって前記第2電圧又は接地電圧を出力ノードに出力する第2インバータを含み、前記第2電圧変換回路は前記入力ノードの電圧にしたがって前記第1電圧又は接地電圧を出力する第3インバータ及び前記第3インバータの出力にしたがって前記第2電圧又は接地電圧を前記出力ノードに出力する第4インバータを含む。

**【0011】**

10

20

30

40

50

実施形態として、前記第1乃至第4インバータはCMOSインバータである。

【0012】

本発明の実施形態によるシステムオンチップは、第1電圧ドメインの第1クロックを発生するように構成される位相ロックループ(PLL)と、前記第1クロックに応じて動作する周辺ブロック、オーディオブロック、ディスプレーブロック、グラフィックブロック、イメージプロセシングブロック、及びコーデックブロックと、前記第1クロックに基づいて、第2電圧ドメインの第2クロックを発生するレベル変換器と、前記第2クロックに応じて動作するプロセッサーを含み、前記レベル変換器は入力ノード及び出力ノードの間に並列に連結され、同一な構造を有する第1及び第2電圧変換回路を含む。

【0013】

実施形態として、前記第1電圧変換回路は前記第2電圧ドメインで動作し、直列に連結された第1及び第2インバータを含み、前記第2電圧変換回路は前記第1電圧ドメインで動作する第3インバータ、及び前記第2電圧ドメインで前記第3インバータの出力に応じて動作する第4インバータを含む。

【0014】

実施形態として、前記第2電圧ドメインの電圧レベルは前記第1電圧ドメインの電圧レベルより高い。

【0015】

本発明の実施形態によるマルチメディア装置は、プロセッサーと、前記プロセッサーの動作メモリーと、前記プロセッサーの制御にしたがって外部と通信するように構成されるモデルと、前記プロセッサーの制御にしたがってデータを格納するように構成される格納部と、外部の信号を感知して前記プロセッサーに伝達するように構成される使用者インターフェイス(User Interface)と、前記プロセッサーの制御にしたがって、ディスプレー部を通じて映像を表示するように構成されるディスプレー制御部と、前記プロセッサーの制御にしたがって、スピーカーを通じて音を出力するように構成されるサウンド制御部と、前記プロセッサーの制御にしたがってエンコーディング及びデコーディングを遂行するコーデック部と、発振器の出力にしたがってクロックを発生するように構成されるクロック発生部と、前記クロックに同期される第1電圧ドメインの第1クロックを発生する位相ロックループと、及び前記第1クロックに応じて第2電圧ドメインの第2クロックを発生するように構成されるレベル変換器と、を含み、前記プロセッサーは前記第2クロックに応じて動作し、前記レベル変換器は入力ノード及び出力ノードの間に並列に連結され、同一な構造を有する第1及び第2電圧変換回路を含む。

【0016】

実施形態として、前記入力ノードの電圧にしたがって前記第2電圧ドメインの第2電圧又は接地電圧を出力する第1インバータと、前記第1インバータの出力にしたがって前記第2電圧又は接地電圧を出力ノードに出力する第2インバータと、前記入力ノードの電圧にしたがって前記第1電圧ドメインの第1電圧又は接地電圧を出力する第3インバータと、及び前記第3インバータの出力にしたがって前記第2電圧又は接地電圧を前記出力ノードに出力する第4インバータを含む。

【0017】

実施形態として、前記プロセッサー、動作メモリー、ディスプレー制御部、サウンド制御部、コーデック部、及び位相ロックループはシステムオンチップに含まれ、前記動作メモリー、ディスプレー制御部、サウンド制御部、及びコーデック部は前記第1クロックに応じて動作する。

【0018】

実施形態として、前記プロセッサーの制御にしたがって、カメラから獲得されるイメージデータを処理するように構成されるイメージプロセシング部をさらに含む。

【0019】

実施形態として、前記プロセッサー、ディスプレー制御部、サウンド制御部、イメージプロセシング部、動作メモリー、コーデック部、及び位相ロックループはシステムオンチ

10

20

30

40

40

50

ップに含まれ、前記ディスプレー制御部、サウンド制御部、イメージプロセシング部、動作メモリー、及びコーデック部は前記第1クロックに応じて動作する。

#### 【0020】

実施形態として、前記プロセッサー、ディスプレー制御部、サウンド制御部、モデム、イメージプロセシング部、動作メモリー、コーデック部、及び位相ロックループはシステムオンチップに含まれ、前記ディスプレー制御部、サウンド制御部、モデム、イメージプロセシング部、動作メモリー、及びコーデック部は前記第1クロックに応じて動作する。

#### 【0021】

実施形態として、前記プロセッサー、ディスプレー制御部、サウンド制御部、動作メモリー、コーデック部、及び位相ロックループはシステムオンチップに含まれ、前記ディスプレー制御部、サウンド制御部、動作メモリー、及びコーデック部は前記第1クロックに応じて動作する。 10

#### 【0022】

実施形態として、前記プロセッサー、ディスプレー制御部、サウンド制御部、動作メモリー、及び位相ロックループはシステムオンチップに含まれ、前記ディスプレー制御部、サウンド制御部、及び動作メモリーは前記第1クロックに応じて動作する。

#### 【0023】

実施形態として、前記プロセッサー、ディスプレー制御部、動作メモリー、及び位相ロックループはシステムオンチップに含まれ、前記ディスプレー制御部、及び動作メモリーは前記第1クロックに応じて動作する。 20

#### 【0024】

実施形態として、前記プロセッサー、動作メモリー、及び位相ロックループはシステムオンチップに含まれ、前記動作メモリーは前記第1クロックに応じて動作する。

#### 【0025】

実施形態として、前記プロセッサー、サウンド制御部、動作メモリー、及び位相ロックループはシステムオンチップに含まれ、前記サウンド制御部及び動作メモリーは前記第1クロックに応じて動作する。 30

#### 【0026】

実施形態として、前記プロセッサー、動作メモリー、モデム、格納部、使用者インターフェイス、ディスプレー制御部、ディスプレー部、サウンド制御部、スピーカー、発振器、クロック発生部、カメラ、イメージプロセシング部、コーデック部、及び位相ロックループはモバイル装置に包含される。 30

#### 【0027】

実施形態として、前記プロセッサー、動作メモリー、モデム、格納部、使用者インターフェイス、ディスプレー制御部、ディスプレー部、サウンド制御部、スピーカー、発振器、クロック発生部、カメラ、イメージプロセシング部、コーデック部、及び位相ロックループはスマートテレビ(Smart Television)に包含される。

#### 【0028】

本発明の実施形態によるレベル変換器は、第1電圧変換回路と、及び入力ノードと出力ノードの間に前記第1電圧変換回路と並列に連結される第2電圧変換回路を含み、前記入力ノードに入力される第1電圧ドメインの第1クロックに応じて前記出力ノードから第2電圧ドメインの第2クロックが出力され、前記第1クロックの立ち上がりエッジ及び前記第2クロックの立ち上がりエッジ間の遅延時間は前記第1クロックの立ち下がりエッジ及び前記第2クロックの立ち下がりエッジ間の遅延時間と同一である。 40

#### 【発明の効果】

#### 【0029】

本発明によると、レベル変換器の出力クロックの高レベル区間の幅と低レベル区間の幅とが平準化される。したがって、向上された信頼性を有するレベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置が提供される。

#### 【図面の簡単な説明】

## 【0030】

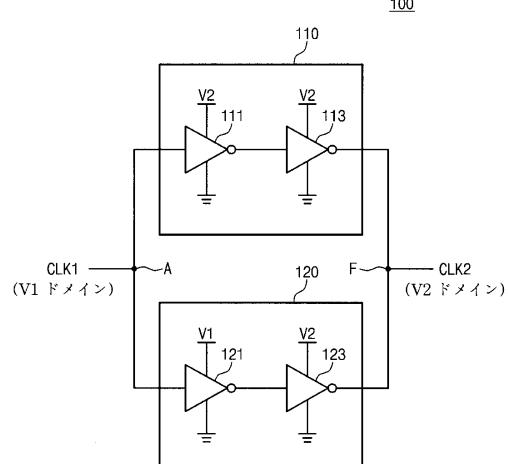

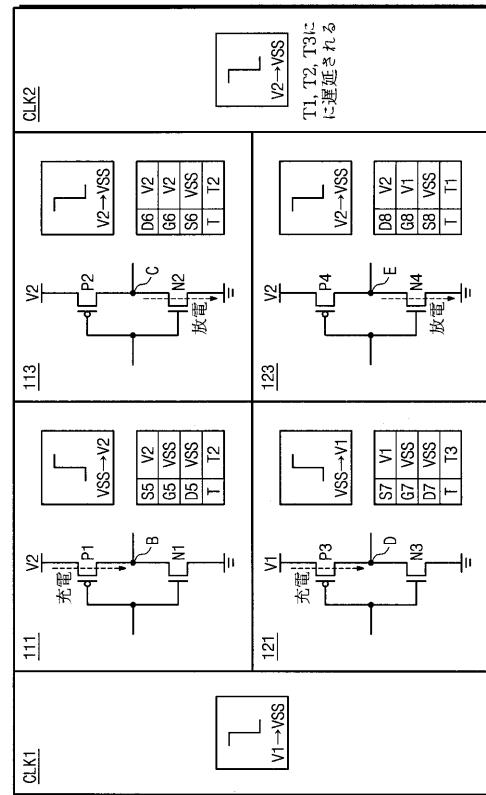

【図1】本発明の実施形態によるレベル変換器を示すブロック図である。

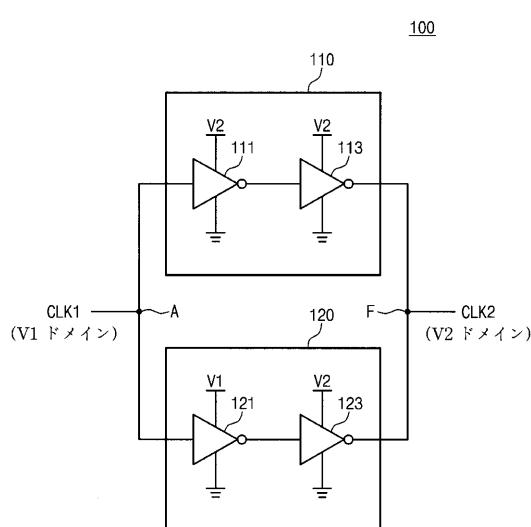

【図2】本発明の実施形態によるレベル変換器を示す回路図である。

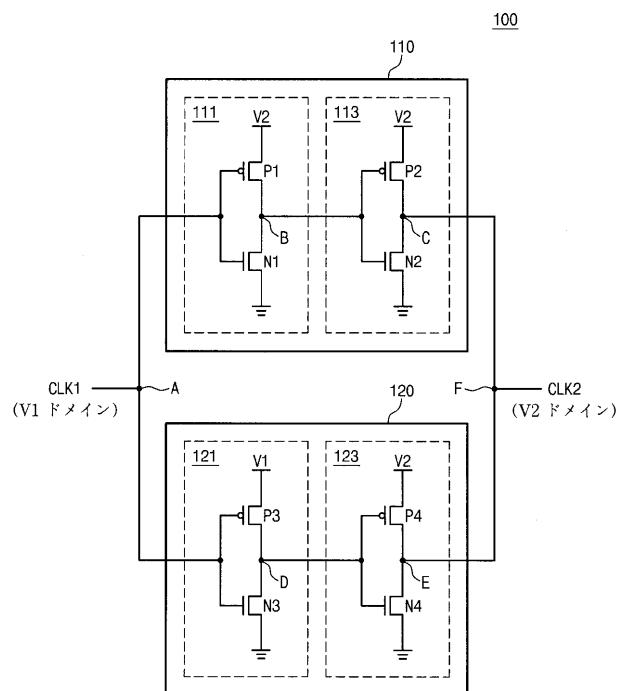

【図3】第1クロックが立ち上がる時、図2を参照して説明された第1乃至第4インバータの動作を示す図面である。

【図4】第1クロックが立ち下がる時、図2を参照して説明された第1乃至第4インバータの動作を示す図面である。

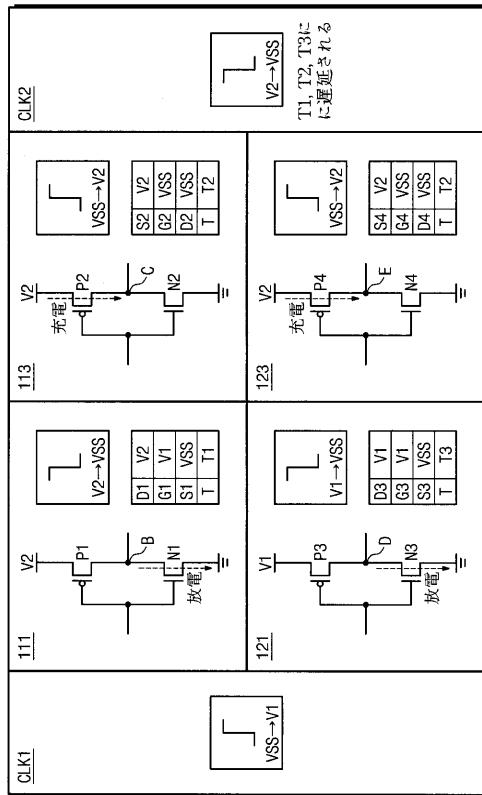

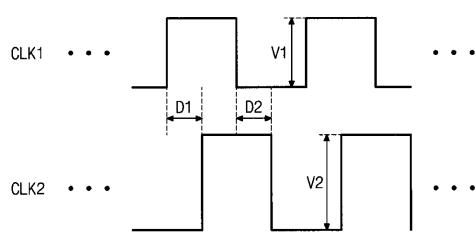

【図5】図1乃至図4を参照して説明されたレベル変換器の入力クロック及び出力クロックを示すタイミング図である。

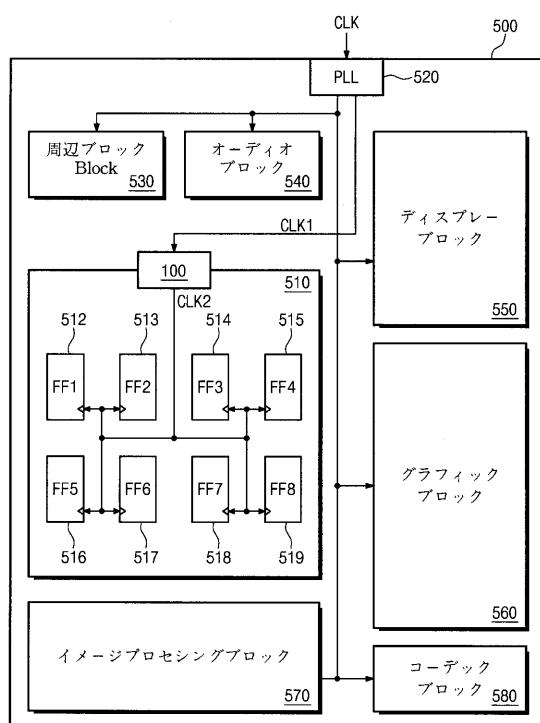

【図6】図1乃至図5を参照して説明されたレベル変換器を含むシステムオンチップを示すブロック図である。 10

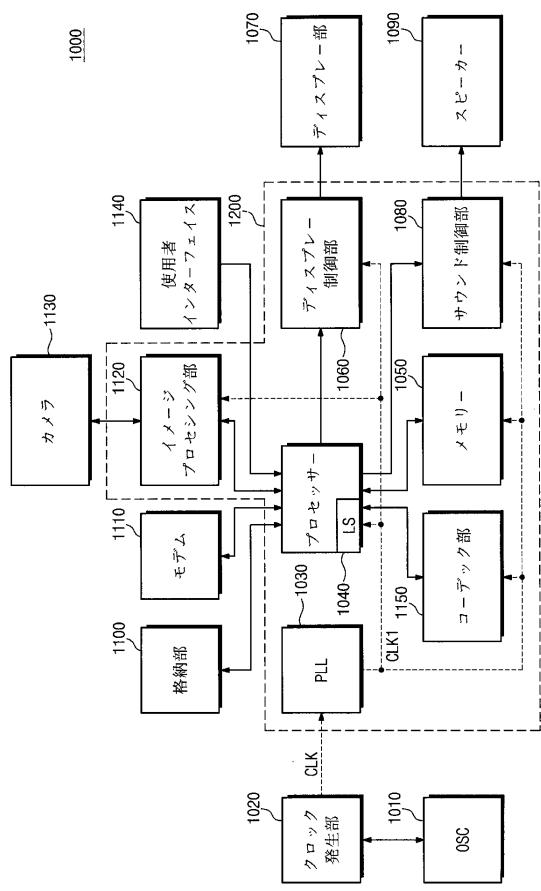

【図7】本発明の実施形態によるレベル変換器を含むマルチメディア装置の第1例を示すブロック図である。

【図8】本発明の実施形態によるレベル変換器を含むマルチメディア装置の第2例を示すブロック図である。

【図9】本発明の実施形態によるレベル変換器を含むマルチメディア装置の第3例を示すブロック図である。

【図10】本発明の実施形態によるレベル変換器を含むマルチメディア装置の第4例を示すブロック図である。 20

【図11】本発明の実施形態によるレベル変換器を含むマルチメディア装置の第5例を示すブロック図である。

【図12】本発明の実施形態によるレベル変換器を含むマルチメディア装置の第6例を示すブロック図である。

【図13】本発明の実施形態によるレベル変換器を含むマルチメディア装置の第7例を示すブロック図である。

【図14】本発明の実施形態によるレベル変換器を含むマルチメディア装置の第8例を示すブロック図である。

【図15】本発明の実施形態によるスマートフォンを示す図面である。

【図16】本発明の実施形態によるタブレットコンピューターを示す図面である。

【図17】本発明の実施形態によるモバイルコンピューターを示す図面である。 30

【図18】本発明の実施形態によるコンピューターを示す図面である。

【図19】本発明の実施形態によるテレビを示す図面である。

【発明を実施するための形態】

【0031】

以下で、本発明が属する技術分野で通常の知識を有する者が本発明の技術的思想を容易に実施できるように詳細に説明するために、本発明の実施形態を添付された図面を参照して説明する。

【0032】

図1は本発明の実施形態によるレベル変換器100を示すブロック図である。図1を参照すれば、レベル変換器100は第1電圧変換回路110及び第2電圧変換回路120を含む。第1及び第2電圧変換回路110、120は入力ノードA及び出力ノードFの間に並列に連結される。 40

【0033】

第1電圧変換回路110は入力ノードAを通じて第1電圧V1に対応する第1電圧ドメインの第1クロックCLK1を受信する。第1クロックCLK1は第1電圧V1のスイシング(swing)幅を有することができる。第1電圧変換回路110は受信された第1クロックCLK1に基づいて、第2電圧V2に対応する第2電圧ドメインの信号を発生する。第2クロックCLK2は第2電圧V2のスイシング幅を有することができる。

【0034】

第1電圧変換回路110は第1及び第2インバータ111、113を含む。第1インバ

10

20

30

40

50

ータ 111 は第 1 クロック CLK1 に応じて第 2 電圧 V2 及び接地電圧 VSS の中で 1 つを出力するように構成される。第 2 インバータ 113 は第 1 インバータ 111 の出力に応じて第 2 電圧 V2 及び接地電圧 VSS の中で 1 つを出力するように構成される。即ち、第 2 インバータ 113 は第 1 クロック CLK1 に同期される第 2 電圧ドメインの信号を出力する。

#### 【0035】

第 2 電圧変換回路 120 は入力ノード A を通じて第 1 電圧ドメインの第 1 クロック CLK1 を受信する。第 1 電圧変換回路 110 は受信された第 1 クロック CLK1 に基づいて第 2 電圧ドメインの信号を発生する。

#### 【0036】

第 2 電圧変換回路 120 は第 1 電圧変換回路 110 と同一な構造を有する。第 2 電圧変換回路 120 は第 3 及び第 4 インバータ 121、123 を含む。第 3 インバータ 121 は第 1 クロック CLK1 に応じて第 1 電圧 V1 及び接地電圧 VSS の中で 1 つを出力するように構成される。第 4 インバータ 123 は第 3 インバータ 121 の出力に応じて第 2 電圧 V2 及び接地電圧 VSS の中で 1 つを出力するように構成される。即ち、第 4 インバータ 123 は第 1 クロック CLK1 に同期される第 2 電圧ドメインの信号を出力する。

#### 【0037】

第 1 及び第 2 電圧変換回路 110、120 は出力ノード F で混合される。第 1 電圧変換回路 110 は第 1 クロック CLK1 に同期される第 2 電圧ドメインの信号を出力する。第 2 電圧変換回路 120 また第 1 クロック CLK1 に同期される第 2 電圧ドメインの信号を出力する。即ち、出力ノード F で、第 1 クロック CLK1 に同期される第 2 電圧ドメインの信号が生成される。出力ノード F の信号は第 2 電圧ドメインの第 2 クロック CLK2 へ出力される。

#### 【0038】

図 2 は本発明の実施形態によるレベル変換器 100 を示す回路図である。例示的に、図 1 を参照して説明された第 1 乃至第 4 インバータ 111、113、121、123 の内部回路が図示されている。例示的に、第 1 乃至第 4 インバータ 111、113、121、123 各々は CMOS インバータであり得る。しかし、第 1 乃至第 4 インバータ 111、113、121、123 の内部回路は図 2 に図示された回路に限定されない。

#### 【0039】

図 1 及び図 2 を参照すれば、第 1 インバータ 111 は第 1 PMOS ドランジスター P1 及び第 1 NMOS ドランジスター N1 を含む。第 1 PMOS ドランジスター P1 のゲートは入力ノード A に連結される。第 1 PMOS ドランジスター P1 の一端へ第 2 電圧 V2 が供給され、他端は出力ノード B に連結される。第 1 NMOS ドランジスター N1 のゲートは入力ノード A に連結される。第 1 NMOS ドランジスター N1 の一端は接地ノードに連結され、他端は出力ノード B に連結される。

#### 【0040】

第 2 インバータ 113 は第 1 インバータ 111 と同一な構造を有する。第 2 インバータ 113 は第 2 PMOS ドランジスター P2 及び第 2 NMOS ドランジスター N2 を含む。第 2 PMOS ドランジスター P2 のゲートは第 1 インバータ 111 の出力ノード B に連結される。第 2 PMOS ドランジスター P2 の一端へ第 2 電圧 V2 が供給され、他端は出力ノード C に連結される。第 2 NMOS ドランジスター N2 のゲートは第 1 インバータ 111 の出力ノード B に連結される。第 2 NMOS ドランジスター N2 の一端は接地ノードに連結され、他端は出力ノード C に連結される。

#### 【0041】

第 3 インバータ 121 は第 1 インバータ 111 と同一な構造を有する。第 3 インバータ 121 は第 3 PMOS ドランジスター P3 及び第 3 NMOS ドランジスター N3 を含む。第 3 PMOS ドランジスター P3 のゲートは入力ノード A に連結される。第 3 PMOS ドランジスター P3 の一端へ第 1 電圧 V1 が供給され、他端は出力ノード D に連結される。第 3 NMOS ドランジスター N3 のゲートは入力ノード A に連結される。第 3 NMOS ド

10

20

30

40

50

ランジスターN3の一端は接地ノードに連結され、他端は出力ノードDに連結される。

【0042】

第4インバータ123は第1インバータ111と同一な構造を有する。第4インバータ123は第4PMOSトランジスターP4及び第4NMOSトランジスターN4を含む。第4PMOSトランジスターP4のゲートは第3インバータ121の出力ノードDに連結される。第4PMOSトランジスターP4の一端へ第2電圧V2が供給され、他端は出力ノードEに連結される。第4NMOSトランジスターN4のゲートは第3インバータ121の出力ノードDに連結される。第4NMOSトランジスターN4の一端は接地ノードに連結され、他端は出力ノードEに連結される。

【0043】

図3は第1クロックCLK1が立ち上がる時、図2を参照して説明された第1乃至第4インバータ111、113、121、123の動作を示す図面である。図2及び図3を参考すれば、第1クロックCLK1は接地電圧VSSから第1電圧V1に上昇する。第1クロックCLK1が第1電圧V1である時、第1インバータ111の第1PMOSトランジスターP1はターンオフされ、第1NMOSトランジスターN1はターンオンされる。即ち、第1インバータ111の出力ノードBは接地ノードに連結される。

【0044】

第1クロックCLK1が接地電圧VSSである時、第1インバータ111の出力ノードBへ第1PMOSトランジスターP1を通じて第2電圧V2が供給される。したがって、第1クロックCLK1が接地電圧VSSから第1電圧V1に上昇する時、第1インバータ111の出力ノードBの電圧は第2電圧V2から接地電圧VSSへ放電される。

【0045】

具体的に、第1NMOSトランジスターN1のドレーンD1へ第2電圧V2が印加され、ゲートG1へ第1電圧V1が印加され、ソースS1へ接地電圧VSSが印加された状態で、第1NMOSトランジスターN1のチャンネルを通じて出力ノードBの電圧が放電される。この時、第1インバータ111の出力ノードBの電圧が接地電圧VSSへ放電されるのに所要される時間は第1時間T1であり得る。第1時間T1は第1インバータ111の出力ノードBの電圧が第1クロックCLK1の立ち上がりエッジ(rising edge)に同期されて立ち下がる時までの遅延時間であり得る。

【0046】

第1インバータ111の出力電圧が接地電圧VSSである時、第2インバータ113の第2NMOSトランジスターN2はターンオフされ、第2PMOSトランジスターP2はターンオンされる。即ち、第2インバータ113の出力ノードCへ第2電圧V2が供給される。

【0047】

第1インバータ111の出力電圧が第2電圧V2である時、第2インバータ113の出力ノードCへ第2NMOSトランジスターN2を通じて接地電圧VSSが供給される。したがって、第1インバータ111の出力電圧が第2電圧V2から接地電圧VSSに下降する時、第2インバータ113の出力ノードCの電圧は接地電圧VSSから第2電圧V2に充電される。

【0048】

具体的に、第2PMOSトランジスターP2のソースS2へ第2電圧V2が印加され、ゲートG2へ接地電圧VSSが印加され、ドレーンD2へ接地電圧VSSが印加された状態で、第2PMOSトランジスターP2のチャンネルを通じて出力ノードCの電圧が充電される。この時、第2インバータ113の出力ノードCの電圧が第2電圧V2に充電されるのに所要される時間は第2時間T2であり得る。第2時間T2は第2インバータ113の出力ノードCの電圧が第1インバータ111の出力電圧の立ち下がりエッジ(falling edge)に同期されて立ち上がる時までの遅延時間であり得る。

【0049】

第1クロックCLK1は接地電圧VSSから第1電圧V1に上昇する。第1クロックC

10

20

30

40

50

L K 1 が第1電圧 V 1 である時、第3インバータ 121 の第3PMOSトランジスター P 1 はターンオフされ、第3NMOSトランジスター N 3 はターンオンされる。即ち、第3インバータ 121 の出力ノード D へ接地電圧 VSS が供給される。

#### 【0050】

第1クロック CLK 1 が接地電圧 VSS である時、第3インバータ 121 の出力ノード D へ第3PMOSトランジスター P 3 を通じて第1電圧 V 1 が供給される。したがって、第1クロック CLK 1 が接地電圧 VSS から第1電圧 V 1 に上昇する時、第3インバータ 121 の出力ノード D の電圧は第1電圧 V 1 から接地電圧 VSS へ放電される。

#### 【0051】

具体的に、第3NMOSトランジスター N 3 のドレーン D 3 へ第1電圧 V 1 が印加され、ゲート G 3 へ第1電圧 V 1 が印加され、ソース S 3 へ接地電圧 VSS が印加された状態で、第3NMOSトランジスター N 3 のチャンネルを通じて出力ノード D の電圧が放電される。この時、第3インバータ 121 の出力ノード D の電圧が接地電圧 VSS へ放電されるのに所要される時間は第3時間 T 3 であり得る。第3時間 T 3 は第3インバータ 121 の出力ノード D の電圧が第1クロック CLK 1 の立ち上がりエッジ (falling edge) に同期されて立ち下がる時までの遅延時間であり得る。

#### 【0052】

第3インバータ 121 の出力が接地電圧 VSS である時、第4インバータ 123 の第4NMOSトランジスター N 4 はターンオフされ、第4PMOSトランジスター P 4 はターンオンされる。即ち、第4インバータ 123 の出力ノード E へ第2電圧 V 2 が供給される。

#### 【0053】

第3インバータ 121 の出力電圧が第1電圧 V 1 である時、第4インバータ 123 の出力ノード E へ第4NMOSトランジスター N 4 を通じて接地電圧 VSS が供給される。したがって、第3インバータ 121 の出力電圧が第1電圧 V 1 から接地電圧 VSS に下降する時、第4インバータ 123 の出力ノード E の電圧は接地電圧 VSS から第2電圧 V 2 に充電される。

#### 【0054】

具体的に、第4PMOSトランジスター P 4 のソース S 4 へ第2電圧 V 2 が印加され、ゲート G 4 へ接地電圧 VSS が印加され、ドレーン D 4 へ接地電圧 VSS が印加された状態で、第4PMOSトランジスター P 4 のチャンネルを通じて出力ノード E の電圧が充電される。この時、第4インバータ 123 の第4PMOSトランジスター P 4 のバイアス条件は第2インバータ 113 の第2PMOSトランジスター P 2 のバイアス条件と同一である。したがって、第4インバータ 123 の出力ノード E の電圧が第2電圧 V 2 へ充電されるのに所要される時間は第2時間 T 2 であり得る。第2時間 T 2 は第4インバータ 123 の出力ノード E の電圧が第3インバータ 121 の出力電圧の立ち下がりエッジに同期されて立ち上がる時までの遅延時間であり得る。

#### 【0055】

図4は第1クロック CLK 1 が立ち下がる時、図2を参照して説明された第1乃至第4インバータ 111、113、121、123 の動作を示す図面である。図2及び図4を参照すれば、第1クロック CLK 1 は第1電圧 V 1 から接地電圧 VSS に下降する。第1クロック CLK 1 が接地電圧 VSS である時、第1インバータ 111 の第1NMOSトランジスター N 1 はターンオフされ、第1PMOSトランジスター P 1 はターンオンされる。即ち、第1インバータ 111 の出力ノード B へ第2電圧 V 2 が供給される。

#### 【0056】

第1クロック CLK 1 が第1電圧 V 1 である時、第1インバータ 111 の出力ノード B へ第1NMOSトランジスター N 1 を通じて接地電圧 VSS が供給される。したがって、第1クロック CLK 1 が第1電圧 V 1 から接地電圧 VSS に下降する時、第1インバータ 111 の出力ノード B の電圧は接地電圧 VSS から第2電圧 V 2 に充電される。

#### 【0057】

10

20

30

40

50

具体的に、第1PMOSトランジスターP1のソースS5へ第2電圧V2が印加され、ゲートG6へ接地電圧VSSが印加され、ドレーンD6へ接地電圧VSSが印加された状態で、第1PMOSトランジスターP1のチャンネルを通じて出力ノードBの電圧が充電される。第1PMOSトランジスターP1のバイアス条件は図3を参照して説明された第2インバータ113の第2PMOSトランジスターP2のバイアス条件と同一である。したがって、第1インバータ111の出力ノードBの電圧が第2電圧V2に充電されるのに所要される時間は第2時間T2であり得る。第2時間T2は第1インバータ111の出力ノードBの電圧が第1クロックCLK1の立ち下がりエッジに同期されて立ち上がる時までの遅延時間であり得る。

## 【0058】

第1インバータ111の出力電圧が第2電圧V2である時、第2インバータ113の第2PMOSトランジスターP2はターンオフされ、第2NMOSトランジスターN2はターンオンされる。即ち、第2インバータ113の出力ノードCへ接地電圧VSSが供給される。

## 【0059】

第1インバータ111の出力電圧が接地電圧VSSである時、第2インバータ113の出力ノードCへ第2PMOSトランジスターP2を通じて第2電圧V2が供給される。したがって、第1インバータ111の出力電圧が接地電圧VSSから第2電圧V2に上昇した時に、第2インバータ113の出力ノードCの電圧は第2電圧V2から接地電圧VSSへ放電される。

## 【0060】

具体的に、第2NMOSトランジスターN2のドレーンD7へ第2電圧V2が印加され、ゲートG7へ第2電圧V2が印加され、ソースS7へ接地電圧VSSが印加された状態で、第2NMOSトランジスターN2のチャンネルを通じて出力ノードCの電圧が放電される。

## 【0061】

この時、トランジスターの種類がNMOSトランジスターであることを除外すれば、第2NMOSトランジスターN2のバイアス条件は第1インバータ111の第1PMOSトランジスターP1のバイアス条件と同一である。第2NMOSトランジスターN2のゲート-ソース電圧差は第2電圧V2であり、第1PMOSトランジスターP1のゲート-ソース電圧差また第2電圧V2である。第2NMOSトランジスターN2のドレーン-ソース電圧差は第2電圧V2であり、第1PMOSトランジスターP1のドレーン-ソース電圧差また第2電圧V2である。

## 【0062】

第1乃至第4インバータ111、113、121、123各々は1つのPMOSトランジスター及び1つのNMOSトランジスターを含む。第1乃至第4インバータ111、113、121、123の入力電圧が低レベルである時、第1乃至第4インバータ111、113、121、123の出力電圧はPMOSトランジスターP1～P4によって生成される。第1乃至第4インバータ111、113、121、123の入力電圧が高レベルである時、第1乃至第4インバータ111、113、121、123の出力電圧はNMOSトランジスターN1～N4によって生成される。

## 【0063】

低レベル出力及び高レベル出力を有するように、第1乃至第4インバータ111、113、121、123が形成され得る。例えば、高レベルを出力する時、充電する電流量と低レベルを出力する時、放電する電流量とが平準化されるように、第1乃至第4インバータ111、113、121、123が形成され得る。同一なバイアス条件で、第1乃至第4NMOSトランジスターN1～N4は第1乃至第4PMOSトランジスターP1～P4と同様に動作するように形成され得る。同一なバイアス条件で、第2NMOSトランジスターN2を通じて流れる電流の量は第1PMOSトランジスターP1を通じて流れる電流の量と同一であり得る。

10

20

30

40

50

## 【0064】

第2N MOSトランジスターN2のバイアス条件が第1PMOSトランジスターP1のバイアス条件と同一であるので、第2インバータ113の出力ノードCの電圧が接地電圧VSSへ放電されるのに所要される時間は第2時間T2であり得る。第2時間T2は第2インバータ113の出力ノードCの電圧が第1インバータ111の出力電圧の立ち上がりエッジに同期されて立ち下がる時までの遅延時間であり得る。

## 【0065】

第1クロックCLK1が接地電圧VSSである時、第3インバータ121の第3N MOSトランジスターN1はターンオフされ、第3PMOSトランジスターP3はターンオンされる。即ち、第3インバータ121の出力ノードDへ第1電圧V1が供給される。

10

## 【0066】

第1クロックCLK1が第1電圧V1である時、第3インバータ121の出力ノードDへ第3N MOSトランジスターN3を通じて接地電圧VSSが供給される。したがって、第1クロックCLK1が第1電圧V1から接地電圧VSSに下降する時、第3インバータ121の出力ノードDの電圧は接地電圧VSSから第1電圧V1に充電される。

## 【0067】

具体的に、第3PMOSトランジスターP3のソースS7へ第1電圧V1が印加され、ゲートG7へ接地電圧VSSが印加され、ドレーンD7へ接地電圧VSSが印加された状態で、第3PMOSトランジスターP3のチャンネルを通じて出力ノードDの電圧が充電される。

20

## 【0068】

この時、トランジスターの種類がPMOSトランジスターであることを除外すれば、第3PMOSトランジスターP2のバイアス条件は図3を参照して説明された第3N MOSトランジスターN3のバイアス条件と同一である。第3PMOSトランジスターP3のゲート-ソース電圧差は第1電圧V1であり、第3N MOSトランジスターN3のゲート-ソース電圧差また第1電圧V1である。第3PMOSトランジスターP3のドレーン-ソース電圧差は第1電圧V1であり、第3N MOSトランジスターN3のドレーン-ソース電圧差また第1電圧V1である。

## 【0069】

したがって、第3インバータ121の出力ノードDの電圧が第1電圧V1に充電されるのに所要される時間は第3時間T3であり得る。第3時間T3は第3インバータ121の出力ノードDの電圧が第1クロックCLK1の立ち下がりエッジに同期されて立ち上がる時までの遅延時間であり得る。

30

## 【0070】

第3インバータ121の出力電圧が第1電圧V1である時、第4インバータ123の第4PMOSトランジスターP4はターンオフされ、第4N MOSトランジスターN4はターンオンされる。即ち、第4インバータ123の出力ノードEへ接地電圧VSSが供給される。

## 【0071】

第3インバータ121の出力電圧が接地電圧VSSである時、第4インバータ123の出力ノードEへ第4PMOSトランジスターP4を通じて第2電圧V2が供給される。したがって、第3インバータ121の出力電圧が接地電圧VSSから第1電圧V1に上昇する時、第4インバータ123の出力ノードEの電圧は第2電圧V2から接地電圧VSSへ放電される。

40

## 【0072】

具体的に、第4N MOSトランジスターN4のドレーンD8へ第2電圧V2が印加され、ゲートG8へ第1電圧V1が印加され、ソースS8へ接地電圧VSSが印加された状態で、第4PMOSトランジスターP4のチャンネルを通じて出力ノードEの電圧が放電される。

## 【0073】

50

この時、第4インバータ123の第4N MOSトランジスターN4のバイアス条件は図3を参照して説明された第1N MOSトランジスターN1のバイアス条件と同一である。したがって、第4インバータ123の出力ノードEの電圧が接地電圧VSSへ放電されるのに所要される時間は第1時間T1であり得る。第1時間T1は第4インバータ123の出力ノードEの電圧が第3インバータ121の出力電圧の立ち上がりエッジに同期されて立ち下がる時までの遅延時間であり得る。

#### 【0074】

図5は図1乃至図4を参照して説明されたレベル変換器100の入力クロックCLK1及び出力クロックCLK2を示すタイミング図である。図1乃至図5を参照すれば、第1クロックCLK1がレベル変換器100へ入力される。第1クロックCLK1は第1電圧V1のスwing幅を有する。第1クロックCLK1は周期的に反復される立ち上がりエッジ及び立ち下がりエッジを有する。

10

#### 【0075】

第2クロックCLK2がレベル変換器100から出力される。第2クロックCLK2は第2電圧V2のスwing幅を有する。第1クロックCLK1の立ち上がりエッジに同期されて、第2クロックCLK2が立ち上がる。第2クロックCLK2は第1電圧変換回路110の第1及び第2インバータ111、113の充電と放電、及び第2電圧変換回路120の第3及び第4インバータ121、123の充電と放電によって上昇する。

20

#### 【0076】

図3を参照して説明されたように、第1クロックCLK1が上昇し、第1時間T1後に、第1インバータ111の出力電圧が減少して接地電圧VSSに到達する。第1インバータ111の出力電圧が下降し、第2時間T2後に、第2インバータ113の出力電圧が増加して第2電圧V2に到達する。第1クロックCLK1が上昇し、第3時間T3後に、第3インバータ121の出力電圧が下降して接地電圧VSSに到達する。第3インバータ121の出力電圧が下降し、第2時間T2後に、第4インバータ123の出力電圧が上昇して第2電圧V2に到達する。

20

#### 【0077】

第2及び第4インバータ113、123の出力電圧が混合されて第2クロックCLK2が形成される。即ち、第1クロックCLK1の立ち上がりエッジと第2クロックCLK2の立ち上がりエッジとの間の遅延D1は第1時間T1、第2時間T2、及び第3時間T3が加算されて発生される。

30

#### 【0078】

図4を参照して説明されたように、第1クロックCLK1が下降し、第2時間T2後に、第1インバータ111の出力電圧が上昇して第2電圧V2に到達する。第1インバータ111の出力電圧が上昇し、第2時間T2後に、第2インバータ113の出力電圧が下降して接地電圧VSSに到達する。第1クロックCLK1が下降し、第3時間T3後に、第3インバータ121の出力電圧が上昇して第1電圧V1に到達する。第3インバータ121の出力電圧が上昇し、第1時間T1後に、第4インバータ123の出力電圧が下降して接地電圧VSSに到達する。

40

#### 【0079】

第2及び第4インバータ113、123の出力電圧が混合されて、第2クロックCLK2が形成される。即ち、第1クロックCLKの立ち下がりエッジと第2クロックCLK2の立ち下がりエッジとの間の遅延D2は第1時間T1、第2時間T2、及び第3時間T3が加算されて発生される。

#### 【0080】

上述したように、第1及び第2クロックCLK1、CLK2の立ち上がりエッジの間の遅延D1を発生させる時間要因T1、T2、T3は立ち下がりエッジの間の遅延D2を発生させる時間要因T1、T2、T3と同一である。したがって、第1及び第2クロックCLK1、CLK2の立ち上がりエッジの間の遅延D1と立ち下がりエッジの間の遅延D2とは同一であり得る。

50

## 【0081】

立ち上がりエッジの間の遅延D1と立ち下がりエッジの間の遅延D2とが互に異なる場合、第2クロックCLK2の一周期の高レベル区間と低レベル区間との比率が可変され得る。

## 【0082】

例示的に、立ち上がりエッジの間の遅延D1が立ち下がりエッジの間の遅延D2より大きい場合、第2クロックCLK2の一周期の高レベル区間の比率は第1クロックCLK1の一周期の高レベル区間の比率より減少する。反対に、立ち下がりエッジの間の遅延D2が立ち上がりエッジの間の遅延D1より大きい場合、第2クロックCLK2の一周期の低レベル区間の比率は第1クロックCLK1の一周期の低レベル区間の比率より減少する。本発明の実施形態によれば、レベル変換器100は高レベル及び低レベル区間の比率(Duty ratio)を維持し、入力される第1クロックCLK1と他の電圧ドメインの第2クロックCLK2とを発生できる。したがって、レベル変換器100の出力クロックの信頼性が向上され得る。

10

## 【0083】

例示的に、第2電圧V2は第1電圧V1より低いか、或いは高いことができる。

## 【0084】

図6は図1乃至図5を参照して説明されたレベル変換器100を含むシステムオンチップ500(SOC、System-On-Chip)を示すブロック図である。図6を参照すれば、システムオンチップ500はプロセッサー510、位相ロックループ520、周辺ブロック530、オーディオブロック540、ディスプレーブロック550、グラフィックブロック560、イメージプロセシングブロック570、及びコーデックブロック580を含む。

20

## 【0085】

プロセッサー510は第1乃至第8フリップフロップ512～519を含む。プロセッサー510はレベル変換器100をさらに包含するか、又はレベル変換器100に連結され得る。レベル変換器100は位相ロックループ520から第1クロックCLK1を受信する。第1クロックCLK1は第1電圧V1のスイギングを有することができる。レベル変換器100は高レベル及び低レベル区間の比率を維持し、第1クロックCLK1に同期される第2クロックCLK2を発生する。第2クロックCLK2は第2電圧V2のスイギングを有することができる。第2電圧V2は第1電圧V1より大きくなり得る。

30

## 【0086】

レベル変換器100で発生された第2クロックCLK2はプロセッサー510のフリップフロップ512～519へ供給される。プロセッサー510のフリップフロップ512～519は第2クロックCLK2に応じて動作する。

## 【0087】

位相ロックループ520は外部からクロックCLKを受信する。位相ロックループ520は受信されたクロックCLKと同期される第1クロックCLK1を発生する。第1クロックCLK1はプロセッサー510のレベル変換器100、周辺ブロック530、オーディオブロック540、ディスプレーブロック550、グラフィックブロック560、イメージプロセシングブロック570、及びコーデックブロック580へ供給される。

40

## 【0088】

周辺ブロック530、オーディオブロック540、ディスプレーブロック550、グラフィックブロック560、イメージプロセシングブロック570、及びコーデックブロック580は第1クロックCLK1に応じて動作する。周辺ブロック530、オーディオブロック540、ディスプレーブロック550、グラフィックブロック560、イメージプロセシングブロック570、及びコーデックブロック580はIP(Intellectual Property)であり得る。

## 【0089】

オーディオブロック540はオーディオデータを処理できる。ディスプレーブロック5

50

50はモニター(図示せず)のようなディスプレー装置を制御する信号を発生できる。グラフィックブロック560はモニター(図示せず)のようなディスプレー装置に表示されるグラフィックデータを処理できる。イメージプロセシングブロック570はカメラ(図示せず)のような撮影装置によって撮影されるイメージデータを処理できる。コーデック580はオーディオデータのエンコーディング又はデコーディングを遂行できる。コーデック580はグラフィックデータのエンコーディング又はデコーディングを遂行できる。

#### 【0090】

図6に示したように、システムオンチップ500の周辺ブロック530、オーディオブロック540、ディスプレーブロック550、グラフィックブロック560、イメージプロセシングブロック570、及びコーデックブロック580は第1クロックCLK1に応じて動作する。プロセッサー510は第1電圧ドメインの第1クロックCLK1が変換された第2電圧ドメインの第2クロックCLK2に応じて動作できる。第2電圧V2は第1電圧V1より高いことができる。

10

#### 【0091】

レベル変換器100は図1乃至図5を参照して説明されたレベル変換器100であり得る。例示的に、レベル変換器100は入力ノードAと出力ノードFとの間に並列に連結され、同一な構造を有する第1及び第2電圧変換回路110、120を包含できる。レベル変換器100の入力クロックCLK1と出力クロックCLK2との立ち上がりエッジの間の遅延D1と立ち下がりエッジの間の遅延D2とは同一であり得る。したがって、第2クロックCLK2に応じて動作するプロセッサー510の信頼性、及びプロセッサー510を含むシステムオンチップ500の信頼性が向上される。

20

#### 【0092】

プロセッサー510が高速に動作するように設計される場合、プロセッサー510は第2クロックCLK2の立ち上がりエッジと立ち下がりエッジとの全てに同期されて動作できる。本発明の実施形態によるレベル変換器100は高レベル区間及び低レベル区間の比率を維持し、第1電圧ドメインの第1クロックCLK1を第2電圧ドメインの第2クロックCLK2に変換する。高レベル区間及び低レベル区間の比率が維持されれば、第2クロックCLK2の立ち上がりエッジと立ち下がりエッジとのマージン(margin)が最適化されて維持され得る。したがって、本発明の実施形態によるレベル変換器100が提供される時、第2クロックCLK2の立ち上がりエッジと立ち下がりエッジとの全てに同期されて動作するプロセッサー510及びシステムオンチップ500の信頼性が向上され得る。

30

#### 【0093】

図7は本発明の実施形態によるレベル変換器100を含むマルチメディア装置1000の第1例を示すブロック図である。図7を参照すれば、マルチメディア装置1000は発振器1010、クロック発生部1020、位相ロックループ1030、プロセッサー1040、メモリー1050、ディスプレー制御部1060、ディスプレー部1070、サウンド制御部1080、スピーカー1090、格納部1100、モデム1110、イメージプロセシング部1120、カメラ1130、使用者インターフェイス1140、及びコーデック部1150を含む。

40

#### 【0094】

発振器1010は特定周波数にしたがって発振する発振信号を発生する。発振信号はクロック発生部1020へ供給される。

#### 【0095】

クロック発生部1020は発振器1010から供給される発振信号に応じてクロック1020を発生する。クロックCLKは位相ロックループ1030へ供給され得る。

#### 【0096】

位相ロックループ1030はクロック発生部1020から受信されるクロックCLKに応じて第1クロックCLK1を発生するように構成される。第1クロックCLK1は受信されたクロックCLKと同期され得る。第1クロックCLK1はプロセッサー1040へ

50

供給され得る。

【0097】

プロセッサー1040はマルチメディア装置1000の諸般動作を制御するように構成される。プロセッサー1040はマルチメディア装置1000のハードウェア構成要素を制御する。プロセッサー1040はマルチメディア装置1000のソフトウェア構成要素を駆動する。

【0098】

プロセッサー1040は本発明の実施形態によるレベル変換器100を包含するか、又はレベル変換器100に連結され得る。レベル変換器100は位相ロックループ1030から供給される第1電圧ドメインの第1クロックCLK1に基づいて、第2電圧ドメインの第2クロックCLK2を発生する。第2クロックCLK2はプロセッサー1010の内部クロックに使用される。

10

【0099】

メモリー1050はプロセッサー1040の動作メモリーであり得る。例示的に、メモリー1050はSRAM(Static RAM)、DRAM(Dynamic RAM)、SDRAM(Synchronous DRAM)等のような揮発性メモリー、又はフラッシュメモリー、PRAM(Phase-change RAM)、MRAM(Magnetic RAM)、RRAM(Resistive RAM)(登録商標)、FRAM(Ferroelectric RAM)(登録商標)等のような不揮発性メモリーを包含できる。

20

【0100】

ディスプレー制御部1060はプロセッサー1040の制御にしたがって動作する。ディスプレー制御部1060はディスプレー部1070を通じて表示される映像を生成及び制御するように構成される。ディスプレー制御部1060はグラフィック処理ユニット(GPU、Graphic Processing Unit)を包含できる。

【0101】

ディスプレー部1070はディスプレー制御部1060によって生成された映像を表示するように構成される。ディスプレー部1070は液晶ディスプレー(LCD、Liquid Crystal Display)、有機発光ダイオード(OLED、Organic Light Emitting Diode)ディスプレー、アクティブマトリックス有機発光ダイオード(AMOLED、Active Matrix Organic Light Emitting Diode)ディスプレー、電子紙(electronic paper)等を包含できる。

30

【0102】

サウンド制御部1080はプロセッサー1040の制御にしたがって動作する。サウンド制御部1080はスピーカー1090を通じて出力されるサウンドを生成及び制御することができる。スピーカー1090はサウンド制御部1080のサウンド制御部1080はプロセッサー1040の制御にしたがって動作する。サウンド制御部1080はスピーカー1090を通じて出力されるサウンドを生成及び制御することができる。スピーカー1090はサウンド制御部1080の制御にしたがってサウンドを出力することができる。

40

【0103】

格納部1100はプロセッサー1040の制御にしたがって、データを格納するように構成される。格納部1100はフラッシュメモリー、PRAM(Phase-change RAM)、MRAM(Magnetic RAM)、RRAM(Resistive RAM)(登録商標)等のような不揮発性メモリーを包含できる。格納部1100はハードディスクドライブHDD、Hard Disk Drive)、ソリッドステートドライブ(SSD、Solid State Drive)を包含できる。

【0104】

50

モデム 1110 はプロセッサー 1040 の制御にしたがって外部と通信できる。例示的に、モデム 1110 は無線チャンネル又は有線チャンネルを通じて外部と通信できる。モデム 1110 は CDMA (Code Division Multiple Access)、GSM (Global System for Mobile communications) (登録商標)、CDMA 2000、WCDMA (Wideband Code Division Multiple Access)、LTE (Long Term Evolution)、WiBro (Wireless Broadband Internet)、Mobile WiMAX (World Interoperability)、Wi-Fi 等のような無線プロトコルにしたがって、外部と通信できる。モデム 1110 は ADSL (Asymmetric Digital Subscriber Line)、VDSL (Very high data rate Digital Subscriber Line)、ISDN (Integrated Services Digital Network) 等のような有線プロトコルにしたがって、外部と通信できる。

10

#### 【0105】

イメージプロセシング部 1130 はプロセッサー 1040 の制御に応じて動作する。イメージプロセシング部 1130 はカメラ 1140 によって撮影又は録画されるイメージデータを処理するように構成される。

#### 【0106】

使用者インターフェイス 1140 は外部から感知される信号をプロセッサー 1140 へ伝達するように構成される。例示的に、使用者インターフェイス 1120 はマイクロフォン (microphone)、タッチパッド (touch pad)、タッチスクリーン (touch screen)、ボタン、マウス、キーボード等を包含できる。

20

#### 【0107】

コーデック部 1150 はオーディオデータをエンコーディング又はデコーディングできる。コーデック部 1150 はビデオデータをエンコーディング又はデコーディングできる。

#### 【0108】

例示的に、位相ロックループ 1030、プロセッサー 1040、メモリー 1050、ディスプレー制御部 1060、サウンド制御部 1080、イメージプロセシング部 1120、及びコーデック部 1150 はシステムオンチップ 1200 を構成することができる。システムオンチップ 1200 は図 6 を参照して説明された構造を有することができる。プロセッサー 1040 は図 6 のプロセッサー 510 に対応することができる。メモリー 1050 は図 6 の周辺ブロック 530 に対応することができる。ディスプレー制御部 1060 は図 6 のディスプレーブロック 550 及びグラフィックブロック 560 に対応することができる。サウンド制御部 1080 は図 6 のオーディオブロック 540 に対応することができる。イメージプロセシング部 1120 は図 6 のイメージプロセシングブロック 570 に対応することができる。コーデック部 1150 は図 6 のコーデックブロック 580 に対応することができる。

30

#### 【0109】

クロック発生部 1020 は発生されたクロック CLK をシステムオンチップ 1200 へ供給し、マルチメディア装置 1000 の構成要素の中でクロック CLK を必要とする他の構成要素へ供給することができる。

40

#### 【0110】

システムオンチップ 1200 の位相ロックループ 1030 は受信されたクロック CLK に同期する第 1 クロック CLK1 を発生する。レベル変換器 100 は、図 1 乃至図 5 を参照して説明されたように、高レベル区間及び低レベル区間の比率を維持し、第 1 クロック CLK1 に基づいて第 2 クロック CLK2 を発生できる。プロセッサー 1040 は第 2 クロック CLK2 に基づいて動作できる。システムオンチップ 1200 の他の構成要素、即ち、メモリー 1050、ディスプレー制御部 1060、サウンド制御部 1080、イメ-

50

ジプロセシング部 1120、及びコーデック部 1150 は第 1 クロック CLK1 に応じて動作できる。

【0111】

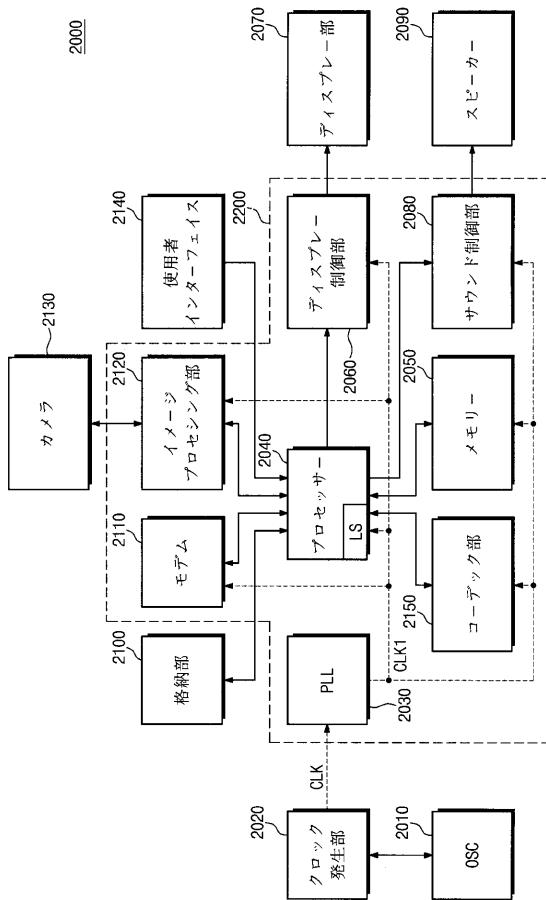

図 8 は本発明の実施形態によるレベル変換器 100 を含むマルチメディア装置 2000 の第 2 実施形態を示すブロック図である。図 8 を参照すれば、マルチメディア装置 2000 は発振器 2010、クロック発生部 2020、位相ロックループ 2030、プロセッサー 2040、メモリー 2050、ディスプレー制御部 2060、ディスプレー部 2070、サウンド制御部 2080、スピーカー 2090、格納部 2100、モデム 2110、イメージプロセシング部 2120、カメラ 2130、使用者インターフェイス 2140、及びコーデック部 2150 を含む。

10

【0112】

図 7 を参照して説明されたマルチメディア装置 1000 と比較すれば、マルチメディア装置 2000 で位相ロックループ 2030、プロセッサー 2040、メモリー 2050、ディスプレー制御部 2060、サウンド制御部 2080、モデム 2110、イメージプロセシング部 2120、及びコーデック部 2150 がシステムオンチップ 2200 を構成することができる。システムオンチップ 2200 は図 6 を参照して説明された構造を有することができる。プロセッサー 2040 は図 6 のプロセッサー 510 に対応することができる。メモリー 2050 及びモデム 2110 は図 6 の周辺ブロック 530 に対応することができる。ディスプレー制御部 2060 は図 6 のディスプレーブロック 550 及びグラフィックブロック 560 に対応することができる。サウンド制御部 2080 は図 6 のオーディオブロック 540 に対応することができる。イメージプロセシング部 2120 は図 6 のイメージプロセシングブロック 570 に対応することができる。コーデック部 2150 は図 6 のコーデックブロック 580 に対応することができる。

20

【0113】

クロック発生部 2020 は発生されたクロック CLK をシステムオンチップ 2200 へ供給し、マルチメディア装置 2000 の構成要素の中でクロック CLK を必要とする他の構成要素へ供給することができる。

【0114】

システムオンチップ 2200 の位相ロックループ 2030 は受信されたクロック CLK に同期する第 1 クロック CLK1 を発生する。レベル変換器 100 は、図 1 乃至図 5 を参照して説明されたように、高レベル区間及び低レベル区間の比率を維持し、第 1 クロック CLK1 に基づいて第 2 クロック CLK2 を発生できる。プロセッサー 2040 は第 2 クロック CLK2 に基づいて動作できる。システムオンチップ 2200 の他の構成要素、即ち、メモリー 2050、ディスプレー制御部 2060、サウンド制御部 2080、モデム 2110、イメージプロセシング部 2120、及びコーデック部 2150 は第 1 クロック CLK1 に応じて動作できる。

30

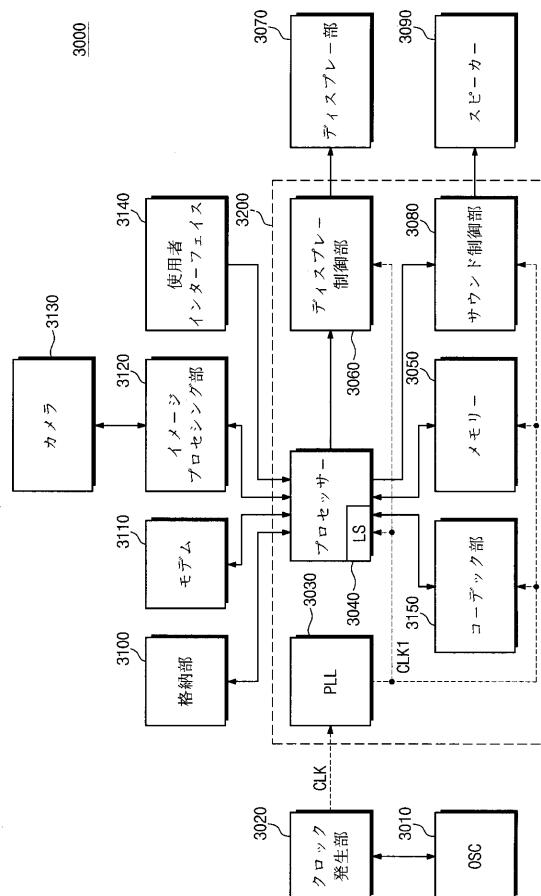

【0115】

図 9 は本発明の実施形態によるレベル変換器 100 を含むマルチメディア装置 3000 の第 3 実施形態を示すブロック図である。図 9 を参照すれば、マルチメディア装置 3000 は発振器 3010、クロック発生部 3020、位相ロックループ 3030、プロセッサー 3040、メモリー 3050、ディスプレー制御部 3060、ディスプレー部 3070、サウンド制御部 3080、スピーカー 3090、格納部 3100、モデム 3110、イメージプロセシング部 3120、カメラ 3130、使用者インターフェイス 3140、及びコーデック部 3150 を含む。

40

【0116】

図 7 を参照して説明されたマルチメディア装置 1000 と比較すれば、マルチメディア装置 3000 で位相ロックループ 3030、プロセッサー 3040、メモリー 3050、ディスプレー制御部 3060、サウンド制御部 3080、及びコーデック部 3150 がシステムオンチップ 2200 を構成することができる。

【0117】

50

クロック発生部 3020 は発生されたクロック CLK をシステムオンチップ 3200 へ供給し、マルチメディア装置 3000 の構成要素の中でクロック CLK を必要とする他の構成要素へ供給することができる。

#### 【0118】

システムオンチップ 3200 の位相ロックループ 3030 は受信されたクロック CLK に同期する第 1 クロック CLK 1 を発生する。レベル変換器 100 は、図 1 乃至図 5 を参照して説明されたように、高レベル区間及び低レベル区間の比率を維持し、第 1 クロック CLK 1 に基づいて第 2 クロック CLK 2 を発生できる。プロセッサー 3040 は第 2 クロック CLK 2 に基づいて動作できる。システムオンチップ 3200 の他の構成要素、即ち、メモリー 3050、ディスプレー制御部 3060、サウンド制御部 3080、及びコードック部 3150 は第 1 クロック CLK 1 に応じて動作できる。10

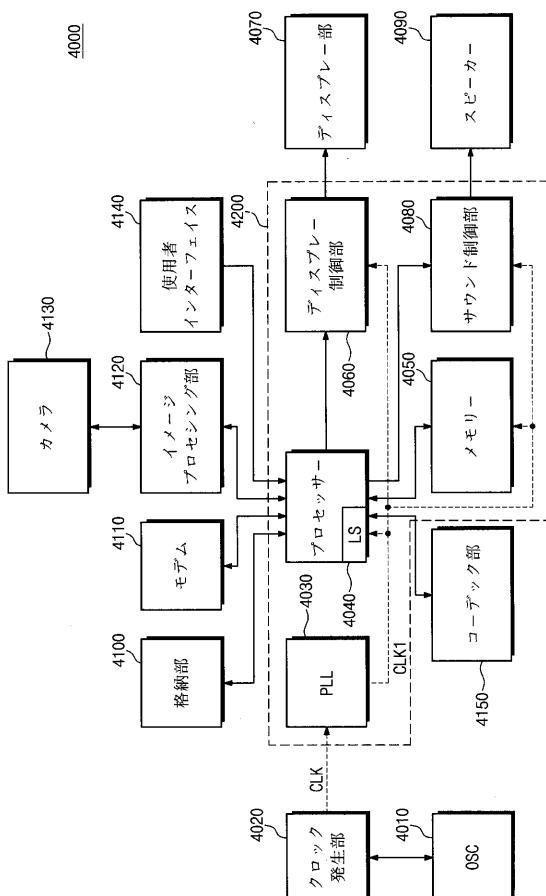

#### 【0119】

図 10 は本発明の実施形態によるレベル変換器 100 を含むマルチメディア装置 4000 の第 4 実施形態を示すブロック図である。図 10 を参照すれば、マルチメディア装置 4000 は発振器 4010、クロック発生部 4020、位相ロックループ 4030、プロセッサー 4040、メモリー 4050、ディスプレー制御部 4060、ディスプレー部 4070、サウンド制御部 4080、スピーカー 4090、格納部 4100、モデル 4110、イメージプロセシング部 4120、カメラ 4130、使用者インターフェイス 4140、及びコードック部 4150 を含む。

#### 【0120】

図 7 を参照して説明されたマルチメディア装置 1000 と比較すれば、マルチメディア装置 4000 で位相ロックループ 4030、プロセッサー 4040、メモリー 4050、ディスプレー制御部 4060、及びサウンド制御部 4080 がシステムオンチップ 4200 を構成することができる。20

#### 【0121】

クロック発生部 4020 は発生されたクロック CLK をシステムオンチップ 4200 へ供給し、マルチメディア装置 4000 の構成要素の中でクロック CLK を必要とする他の構成要素へ供給することができる。

#### 【0122】

システムオンチップ 4200 の位相ロックループ 4030 は受信されたクロック CLK に同期する第 1 クロック CLK 1 を発生する。レベル変換器 100 は、図 1 乃至図 5 を参照して説明されたように、高レベル区間及び低レベル区間の比率を維持し、第 1 クロック CLK 1 に基づいて第 2 クロック CLK 2 を発生できる。プロセッサー 4040 は第 2 クロック CLK 2 に基づいて動作できる。システムオンチップ 4200 の他の構成要素、即ち、メモリー 4050、ディスプレー制御部 4060、及びサウンド制御部 4080 は第 1 クロック CLK 1 に応じて動作できる。30

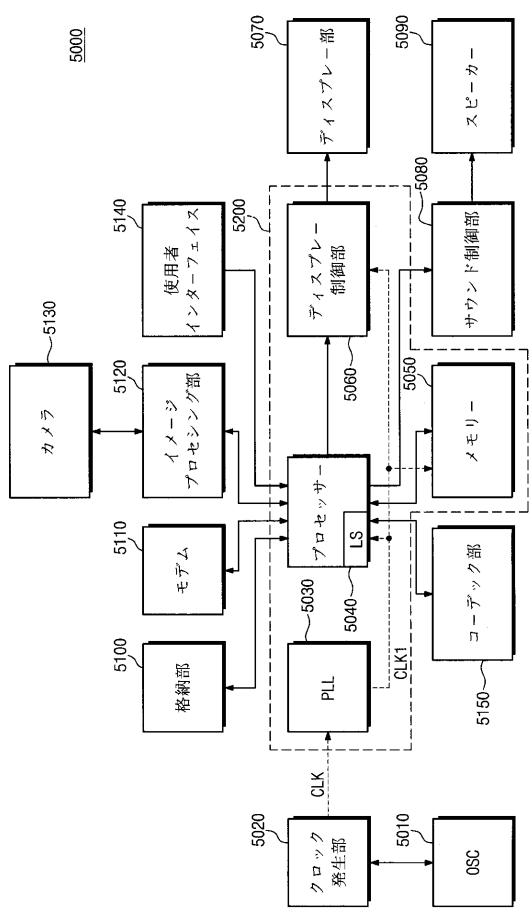

#### 【0123】

図 11 は本発明の実施形態によるレベル変換器 100 を含むマルチメディア装置 5000 の第 5 実施形態を示すブロック図である。図 11 を参照すれば、マルチメディア装置 5000 は発振器 5010、クロック発生部 5020、位相ロックループ 5030、プロセッサー 5040、メモリー 5050、ディスプレー制御部 5060、ディスプレー部 5070、サウンド制御部 5080、スピーカー 5090、格納部 5100、モデル 5110、イメージプロセシング部 5120、カメラ 5130、使用者インターフェイス 5140、及びコードック部 5150 を含む。40

#### 【0124】

図 7 を参照して説明されたマルチメディア装置 1000 と比較すれば、マルチメディア装置 5000 で位相ロックループ 5030、プロセッサー 5040、メモリー 5050、及びディスプレー制御部 5060 がシステムオンチップ 5200 を構成することができる。50

#### 【0125】

クロック発生部 5020 は発生されたクロック CLK をシステムオンチップ 5200 へ供給し、マルチメディア装置 5000 の構成要素の中でクロック CLK を必要とする他の構成要素へ供給することができる。

【0126】

システムオンチップ 5200 の位相ロックループ 5030 は受信されたクロック CLK に同期する第 1 クロック CLK 1 を発生する。レベル変換器 100 は、図 1 乃至図 5 を参照して説明されたように、高レベル区間及び低レベル区間の比率を維持し、第 1 クロック CLK 1 に基づいて第 2 クロック CLK 2 を発生できる。プロセッサー 5040 は第 2 クロック CLK 2 に基づいて動作できる。システムオンチップ 5200 の他の構成要素、即ち、メモリー 5050 及びディスプレー制御部 5060 は第 1 クロック CLK 1 に応じて動作できる。10

【0127】

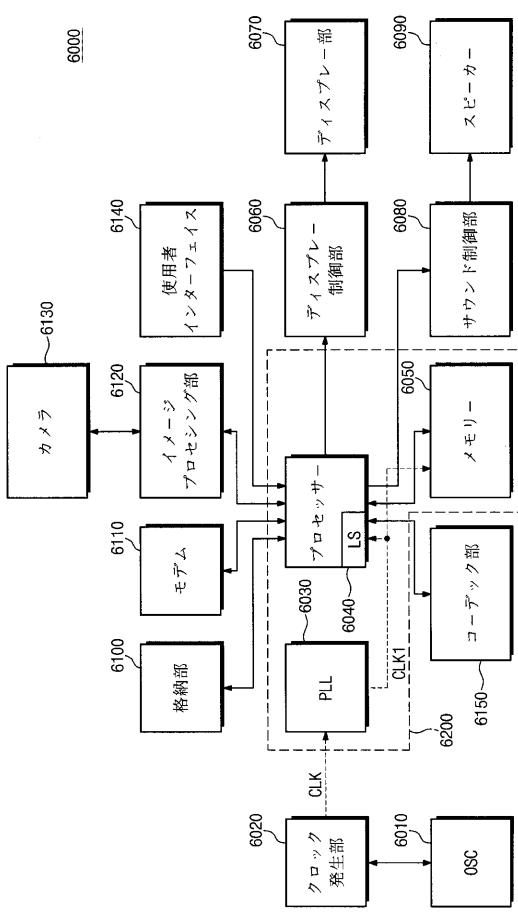

図 12 は本発明の実施形態によるレベル変換器 100 を含むマルチメディア装置 6000 の第 6 実施形態を示すブロック図である。図 12 を参照すれば、マルチメディア装置 6000 は発振器 6010、クロック発生部 6020、位相ロックループ 6030、プロセッサー 6040、メモリー 6050、ディスプレー制御部 6060、ディスプレー部 6070、サウンド制御部 6080、スピーカー 6090、格納部 6100、モデル 6110、イメージプロセシング部 6120、カメラ 6130、使用者インターフェイス 6140、及びコーデック部 6150 を含む。20

【0128】

図 7 を参照して説明されたマルチメディア装置 1000 と比較すれば、マルチメディア装置 6000 で位相ロックループ 6030、プロセッサー 6040、及びメモリー 6050 がシステムオンチップ 6200 を構成することができる。

【0129】

クロック発生部 6020 は発生されたクロック CLK をシステムオンチップ 6200 へ供給し、マルチメディア装置 6000 の構成要素の中でクロック CLK を必要とする他の構成要素へ供給することができる。

【0130】

システムオンチップ 6200 の位相ロックループ 6030 は受信されたクロック CLK に同期する第 1 クロック CLK 1 を発生する。レベル変換器 100 は、図 1 乃至図 5 を参照して説明されたように、高レベル区間及び低レベル区間の比率を維持し、第 1 クロック CLK 1 に基づいて第 2 クロック CLK 2 を発生できる。プロセッサー 6040 は第 2 クロック CLK 2 に基づいて動作できる。システムオンチップ 6200 の他の構成要素、即ち、メモリー 6050 は第 1 クロック CLK 1 に応じて動作できる。30

【0131】

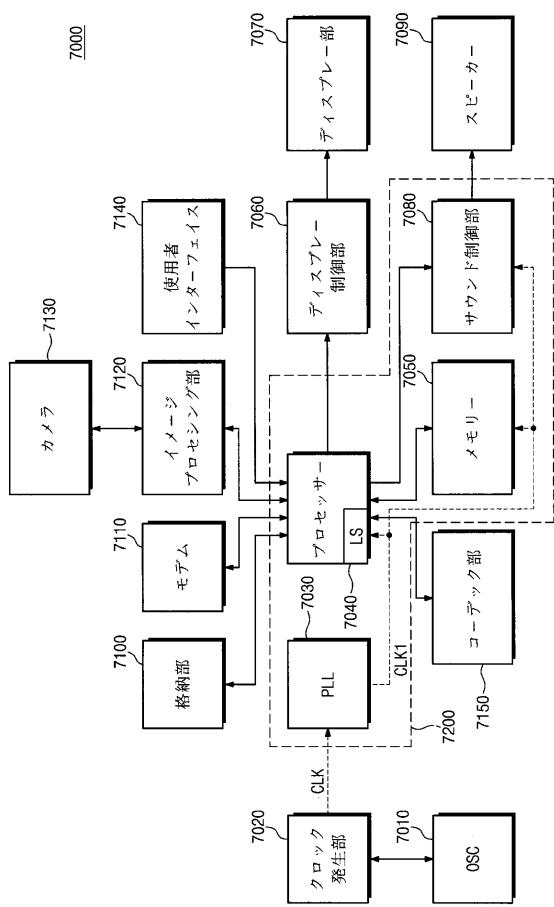

図 13 は本発明の実施形態によるレベル変換器 100 を含むマルチメディア装置 7000 の第 7 実施形態を示すブロック図である。図 13 を参照すれば、マルチメディア装置 7000 は発振器 7010、クロック発生部 7020、位相ロックループ 7030、プロセッサー 7040、メモリー 7050、ディスプレー制御部 7060、ディスプレー部 7070、サウンド制御部 7080、スピーカー 7090、格納部 7100、モデル 7110、イメージプロセシング部 7120、カメラ 7130、使用者インターフェイス 7140、及びコーデック部 7150 を含む。40

【0132】

図 7 を参照して説明されたマルチメディア装置 1000 と比較すれば、マルチメディア装置 7000 で位相ロックループ 7030、プロセッサー 7040、メモリー 7050、及びサウンド制御部 7080 がシステムオンチップ 7200 を構成することができる。

【0133】

クロック発生部 7020 は発生されたクロック CLK をシステムオンチップ 7200 へ供給し、マルチメディア装置 7000 の構成要素の中でクロック CLK を必要とする他の構成要素へ供給することができる。50

## 【0134】

システムオンチップ7200の位相ロックループ7030は受信されたクロックCLKに同期する第1クロックCLK1を発生する。レベル変換器100は、図1乃至図5を参照して説明されたように、高レベル区間及び低レベル区間の比率を維持し、第1クロックCLK1に基づいて第2クロックCLK2を発生できる。プロセッサー7040は第2クロックCLK2に基づいて動作できる。システムオンチップ7200の他の構成要素、即ち、メモリー7050及びサウンド制御部7080は第1クロックCLK1に応じて動作できる。

## 【0135】

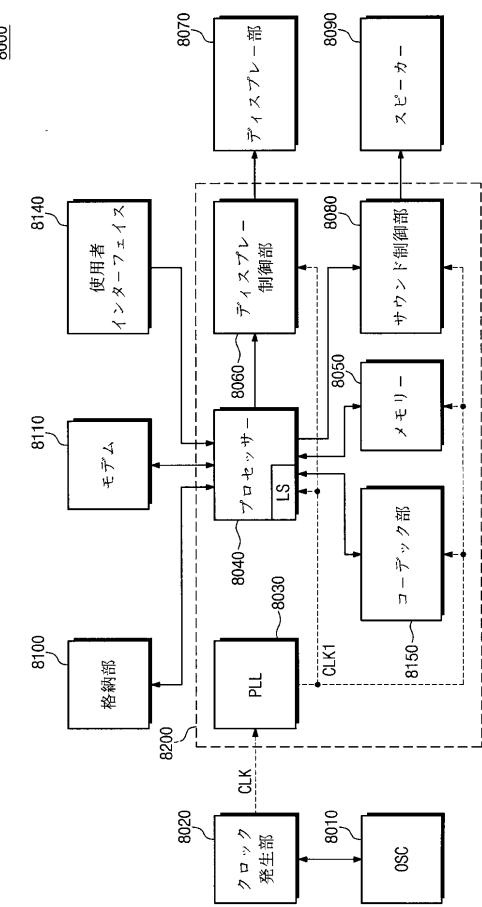

図14は本発明の実施形態によるレベル変換器100を含むマルチメディア装置800の第8実施形態を示すブロック図である。図14を参照すれば、マルチメディア装置800は発振器8010、クロック発生部8020、位相ロックループ8030、プロセッサー8040、メモリー8050、ディスプレー制御部8060、ディスプレー部8070、サウンド制御部8080、スピーカー8090、格納部8100、モデム8110、使用者インターフェイス8140、及びコーデック部8150を含む。

10

## 【0136】

図7を参照して説明されたマルチメディア装置1000と比較すれば、マルチメディア装置8000でイメージプロセシング部1120及びカメラ1130が提供されないことがある。及び、位相ロックループ8030、プロセッサー8040、メモリー8050、ディスプレー制御部8060、サウンド制御部8080、及びコーデック部8150がシステムオンチップ7200を構成することができる。

20

## 【0137】

クロック発生部8020は発生されたクロックCLKをシステムオンチップ8200へ供給し、マルチメディア装置8000の構成要素の中でクロックCLKを必要とする他の構成要素へ供給することができる。

## 【0138】

システムオンチップ8200の位相ロックループ8030は受信されたクロックCLKに同期する第1クロックCLK1を発生する。レベル変換器100は、図1乃至図5を参照して説明されたように、高レベル区間及び低レベル区間の比率を維持し、第1クロックCLK1に基づいて第2クロックCLK2を発生できる。プロセッサー8040は第2クロックCLK2に基づいて動作できる。システムオンチップ8200の他の構成要素、即ち、メモリー8050及びサウンド制御部8080は第1クロックCLK1に応じて動作できる。

30

## 【0139】

イメージプロセシング部2120～7120及びカメラ2130～7130が提供されないことを除外すれば、マルチメディア装置8000の構成要素の中でシステムオンチップ8200を構成する構成要素は図8乃至図13を参照して説明されたように可変され得る。

## 【0140】

図7乃至図14を参照して、本発明の実施形態によるマルチメディア装置が説明されたが、本発明の実施形態によるマルチメディア装置は多様な製品で具現され得る。例示的に、本発明の実施形態によるマルチメディア装置はコンピューター、UMPC(ultra Mobile PC)、ワークステーション、ネットブック(net-book)、PDA(Personal Digital Assistants)、ポータブル(portable)コンピューター、タブレットコンピューター(tablet computer)、無線電話機(wireless phone)、モバイルフォン(mobile phone)、スマートフォン(smart phone)、e-ブック(e-book)、PMP(portable multimedia player)、携帯用ゲーム機、ナビゲーション(navigation)装置、ブラックボックス(black box)、デジタルカメラ(digital camera)、DMB(Digital

40

50

l Multimedia Broadcasting) 再生器、3次元テレビ(3-dimensional television)、スマートテレビ(smart television)、デジタル音声録音機(digital audio recorder)、デジタル音声再生器(digital audio player)、デジタル映像録画器(digital picture recorder)、デジタル映像再生器(digital picture player)、デジタル動画録画器(digital video recorder)、デジタル動画再生器(digital video player)、情報を無線環境で送受信できる装置、ホームネットワークを構成する多様な電子装置の中で1つ、コンピューターネットワークを構成する多様な電子装置の中で1つ、テレマティクスネットワークを構成する多様な電子装置の中で1つ、RFID装置、又はコンピューティングシステムを構成する多様な構成要素の中で1つ等を構成することができる。10

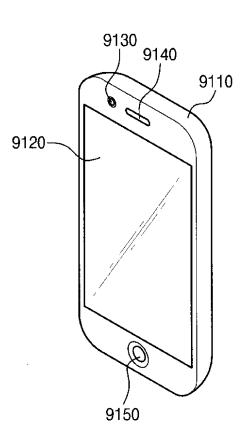

#### 【0141】

図15は本発明の実施形態によるスマートフォン9100を示す図面である。図15を参照すれば、スマートフォン9100は外部ケース9110、画面9120、カメラ9130、スピーカー9140、及び動作ボタン9150を含む。

#### 【0142】

画面9120は図7乃至図14を参照して説明されたディスプレー部1070～8070を構成することができる。カメラ9130は図7乃至図13を参照して説明されたカメラ1130～7130を構成することができる。動作ボタン9150は図7乃至図14を参照して説明された使用者インターフェイス1140～8140を構成することができる。画面9120がタッチスクリーンで形成される時、画面9120また使用者インターフェイス1140～8140を構成することができる。スピーカー9140は図7乃至図14を参照して説明されたスピーカー1090～8090に対応することができる。20

#### 【0143】

外部ケース9110の内部に、発振器1010～8010、クロック発生部1020～8020、位相ロックループ1030～8030、プロセッサー1040～8040、メモリー1050～8050、ディスプレー制御部1060～8060、サウンド制御部1080～8080、格納部1100～8100、モデム1110～8110、及びコーデック部1150～8150が提供され得る。外部ケース9110の内部に、イメージプロセシング部1120～7120がさらに提供され得る。メモリー1050～8050、ディスプレー制御部1060～8060、サウンド制御部1080～8080、格納部1100～8100、モデム1110～8110、イメージプロセシング部1120～7120、及びコーデック部1150～7150の中で少なくとも1つは位相ロックループ1030～8030及びプロセッサー1040～8040と共にシステムオンチップ1200～8200を構成することができる。30

#### 【0144】

クロック発生部1020～8020は発振器1010～8010から受信される発振信号に応じてクロックCLKを発生できる。クロックCLKはシステムオンチップ1200～8200へ供給され得る。位相ロックループ1030～8030はクロックCLKに同期される第1クロックCLK1を発生できる。第1クロックCLK1はシステムオンチップ1200～8200の構成要素へ供給され得る。プロセッサー1040～8040は本発明の実施形態によるレベル変換器100を包含するか、或いはレベル変換器100に連結され得る。レベル変換器100は高レベル区間の比率と低レベル区間の比率を維持し、第1電圧ドメインの第1クロックCLK1を第2電圧ドメインの第2クロックCLK2に変換する。プロセッサー1040～8040は第2クロックCLK2に応じて動作する。システムオンチップ1200～8200の他の構成要素は第1クロックCLK1に応じて動作する。40

#### 【0145】

図15に図示せぬが、スマートフォン9100の後面、上面、下面、及び側面の中で少

なくとも 1 つにディスプレー部 1070 ~ 8070、スピーカー 1090 ~ 8090、及び使用者インターフェイス 1140 ~ 8140 が追加的に提供され得る。また、スマートフォン 9100 に連結されるアクセサリー (accessory) として、ディスプレー部 1070 ~ 8070、スピーカー 1090 ~ 8090、及び使用者インターフェイス 1140 ~ 8140 が追加的に提供され得る。

#### 【0146】

図 16 は本発明の実施形態によるタブレットコンピューター 9200 を示す図面である。図 16 を参照すれば、タブレットコンピューター 9200 は外部ケース 9210、画面 9220、カメラ 9230、及び動作ボタン 9240 を含む。

#### 【0147】

画面 9220 は図 7 乃至図 14 を参照して説明されたディスプレー部 1070 ~ 8070 を構成することができる。カメラ 9230 は図 7 乃至図 13 を参照して説明されたカメラ 1130 ~ 7130 を構成することができる。動作ボタン 9240 は図 7 乃至図 14 を参照して説明された使用者インターフェイス 1140 ~ 8140 を構成することができる。画面 9220 がタッチスクリーンで形成される時、画面 9220 または使用者インターフェイス 1140 ~ 8140 を構成することができる。

#### 【0148】

外部ケース 9210 の内部に、発振器 1010 ~ 8010、クロック発生部 1020 ~ 8020、位相ロックループ 1030 ~ 8030、プロセッサー 1040 ~ 8040、メモリー 1050 ~ 8050、ディスプレー制御部 1060 ~ 8060、サウンド制御部 1080 ~ 8080、格納部 1100 ~ 8100、モデム 1110 ~ 8110、及びコーデック部 1150 ~ 8150 が提供され得る。外部ケース 9210 の内部に、イメージプロセシング部 1120 ~ 7120 がさらに提供され得る。メモリー 1050 ~ 8050、ディスプレー制御部 1060 ~ 8060、サウンド制御部 1080 ~ 8080、格納部 1100 ~ 8100、モデム 1110 ~ 8110、イメージプロセシング部 1120 ~ 7120、及びコーデック部 1150 ~ 7150 の中で少なくとも 1 つは位相ロックループ 1030 ~ 8030 及びプロセッサー 1040 ~ 8040 と共にシステムオンチップ 1200 ~ 8200 を構成することができる。

#### 【0149】

クロック発生部 1020 ~ 8020 は発振器 1010 ~ 8010 から受信される発振信号に応じてクロック CLK を発生できる。クロック CLK はシステムオンチップ 1200 ~ 8200 へ供給され得る。位相ロックループ 1030 ~ 8030 はクロック CLK に同期される第 1 クロック CLK 1 を発生できる。第 1 クロック CLK 1 はシステムオンチップ 1200 ~ 8200 の構成要素へ供給され得る。プロセッサー 1040 ~ 8040 は本発明の実施形態によるレベル変換器 100 を包含するか、或いはレベル変換器 100 に連結され得る。レベル変換器 100 は高レベル区間の比率と低レベル区間の比率とを維持し、第 1 電圧ドメインの第 1 クロック CLK 1 を第 2 電圧ドメインの第 2 クロック CLK 2 に変換する。プロセッサー 1040 ~ 8040 は第 2 クロック CLK 2 に応じて動作する。システムオンチップ 1200 ~ 8200 の他の構成要素は第 1 クロック CLK 1 に応じて動作する。

#### 【0150】

図 16 に図示せぬが、タブレットコンピューター 9200 の背面、上面、下面、及び側面の中で少なくとも 1 つへディスプレー部 1070 ~ 8070、スピーカー 1090 ~ 8090、及び使用者インターフェイス 1140 ~ 8140 が追加的に提供され得る。また、タブレットコンピューター 6200 に連結されるアクセサリー (accessory) として、ディスプレー部 1070 ~ 8070、スピーカー 1090 ~ 8090、及び使用者インターフェイス 1140 ~ 8140 が追加的に提供され得る。

#### 【0151】

図 17 は本発明の実施形態によるモバイルコンピューター 9300 を示す図面である。図 17 を参照すれば、モバイルコンピューター 9300 は外部ケース 9310、画面 93

10

20

30

40

50

20、カメラ9330、スピーカー9340、キーボード9350、及びタッチパッド9360を含む。

#### 【0152】

画面9320は図7乃至図14を参照して説明されたディスプレー部1070～8070を構成することができる。カメラ9330は図7乃至図13を参照して説明されたカメラ1130～7130を構成することができる。キーボード9350及びタッチパッド9360は図7乃至図14を参照して説明された使用者インターフェイス1140～8140を構成することができる。画面9320がタッチスクリーンで形成される時、画面9320また使用者インターフェイス1140～8140を構成することができる。スピーカー9340は図7乃至図14を参照して説明されたスピーカー1090～8090に対応することができる。10

#### 【0153】

外部ケース9310の内部に、発振器1010～8010、クロック発生部1020～8020、位相ロックループ1030～8030、プロセッサー1040～8040、メモリー1050～8050、ディスプレー制御部1060～8060、サウンド制御部1080～8080、格納部1100～8100、モデム1110～8110、及びコーデック部1150～8150が提供され得る。外部ケース9310の内部に、イメージプロセシング部1120～7120がさらに提供され得る。メモリー1050～8050、ディスプレー制御部1060～8060、サウンド制御部1080～8080、格納部1100～8100、モデム1110～8110、イメージプロセシング部1120～7120、及びコーデック部1150～7150の中で少なくとも1つは位相ロックループ1030～8030及びプロセッサー1040～8040と共にシステムオンチップ1200～8200を構成することができる。20

#### 【0154】

クロック発生部1020～8020は発振器1010～8010から受信される発振信号に応じてクロックCLKを発生できる。クロックCLKはシステムオンチップ1200～8200へ供給され得る。位相ロックループ1030～8030はクロックCLKに同期される第1クロックCLK1を発生できる。第1クロックCLK1はシステムオンチップ1200～8200の構成要素へ供給され得る。プロセッサー1040～8040は本発明の実施形態によるレベル変換器100を包含するか、或いはレベル変換器100に連結され得る。レベル変換器100は高レベル区間の比率と低レベル区間の比率とを維持し、第1電圧ドメインの第1クロックCLK1を第2電圧ドメインの第2クロックCLK2に変換する。プロセッサー1040～8040は第2クロックCLK2に応じて動作する。システムオンチップ1200～8200の他の構成要素は第1クロックCLK1に応じて動作する。30

#### 【0155】

モバイルコンピューター9300はノートブック型コンピューターコンピューター又はネットブックであり得る。図17に図示せざが、モバイルコンピューター9300の後面、上面、下面、及び側面の中で少なくとも1つへディスプレー部1070～8070、スピーカー1090～8090、及び使用者インターフェイス1140～8140が追加的に提供され得る。また、モバイルコンピューター9300に連結されるアクセサリー(accessory)として、ディスプレー部1070～8070、スピーカー1090～8090、及び使用者インターフェイス1140～8140が追加的に提供され得る。40

#### 【0156】

図18は本発明の実施形態によるコンピューター9400を示す図面である。図18を参照すれば、コンピューター9400は本体9410、モニター9420、及びキーボード9430を含む。

#### 【0157】

モニター9420は図7乃至図14を参照して説明されたディスプレー部1070～8070を構成することができる。キーボード9430は図7乃至図14を参照して説明さ50

れた使用者インターフェイス 1140～8140 を構成することができる。モニター 9420 がタッチスクリーンで形成される時、モニター 9420 また使用者インターフェイス 1140～8140 を構成することができる。

#### 【0158】

本体 9410 の内部に、発振器 1010～8010、クロック発生部 1020～8020、位相ロックループ 1030～8030、プロセッサー 1040～8040、メモリー 1050～8050、ディスプレー制御部 1060～8060、サウンド制御部 1080～8080、格納部 1100～8100、モデム 1110～8110、及びコーデック部 1150～8150 が提供され得る。本体 9410 の内部に、イメージプロセシング部 1120～7120 がさらに提供され得る。メモリー 1050～8050、ディスプレー制御部 1060～8060、サウンド制御部 1080～8080、格納部 1100～8100、モデム 1110～8110、イメージプロセシング部 1120～7120、及びコーデック部 1150～7150 の中で少なくとも 1 つは位相ロックループ 1030～8030 及びプロセッサー 1040～8040 と共にシステムオンチップ 1200～8200 を構成することができる。10

#### 【0159】

クロック発生部 1020～8020 は発振器 1010～8010 から受信される発振信号に応じてクロック CLK を発生できる。クロック CLK はシステムオンチップ 1200～8200 へ供給され得る。位相ロックループ 1030～8030 はクロック CLK に同期される第 1 クロック CLK 1 を発生できる。第 1 クロック CLK 1 はシステムオンチップ 1200～8200 の構成要素へ供給され得る。プロセッサー 1040～8040 は本発明の実施形態によるレベル変換器 100 を包含するか、或いはレベル変換器 100 に連結され得る。レベル変換器 100 は高レベル区間の比率と低レベル区間の比率とを維持し、第 1 電圧ドメインの第 1 クロック CLK 1 を第 2 電圧ドメインの第 2 クロック CLK 2 に変換する。プロセッサー 1040～8040 は第 2 クロック CLK 2 に応じて動作する。システムオンチップ 1200～8200 の他の構成要素は第 1 クロック CLK 1 に応じて動作する。20

#### 【0160】

図 18 に図示せすが、コンピューター 9400 の後面、上面、下面、及び側面の中で少なくとも 1 つへディスプレー部 1070～8070、スピーカー 1090～8090、及び使用者インターフェイス 1140～8140 が追加的に提供され得る。また、コンピューター 6400 に連結されるアクセサリー (accessory) として、ディスプレー部 1070～8070、スピーカー 1090～8090、及び使用者インターフェイス 1140～8140 が追加的に提供され得る。30

#### 【0161】

図 19 は本発明の実施形態によるテレビ 9500 を示す図面である。図 19 を参照すれば、テレビ 9500 は外部ケース 9510、画面 9520、及び動作ボタン 9530 を含む。

#### 【0162】

画面 9520 は図 7 乃至図 14 を参照して説明されたディスプレー部 1070～8070 を構成することができる。動作ボタン 9530 は図 7 乃至図 14 を参照して説明された使用者インターフェイス 1140～8140 を構成することができる。画面 9520 がタッチスクリーンで形成される時、画面 9520 また使用者インターフェイス 1140～8140 を構成することができる。40

#### 【0163】

外部ケース 9510 の内部に、発振器 1010～8010、クロック発生部 1020～8020、位相ロックループ 1030～8030、プロセッサー 1040～8040、メモリー 1050～8050、ディスプレー制御部 1060～8060、サウンド制御部 1080～8080、格納部 1100～8100、モデム 1110～8110、及びコーデック部 1150～8150 が提供され得る。外部ケース 9510 の内部に、イメージプロ

10

20

30

40

50

セシング部 1120 ~ 7120 がさらに提供され得る。メモリー 1050 ~ 8050、ディスプレー制御部 1060 ~ 8060、サウンド制御部 1080 ~ 8080、格納部 1100 ~ 8100、モデム 1110 ~ 8110、イメージプロセッシング部 1120 ~ 7120、及びコーデック部 1150 ~ 7150 の中で少なくとも 1 つは位相ロックループ 1030 ~ 8030 及びプロセッサー 1040 ~ 8040 と共にシステムオンチップ 1200 ~ 8200 を構成することができる。

#### 【0164】

クロック発生部 1020 ~ 8020 は発振器 1010 ~ 8010 から受信される発振信号に応じてクロック CLK を発生できる。クロック CLK はシステムオンチップ 1200 ~ 8200 へ供給され得る。位相ロックループ 1030 ~ 8030 はクロック CLK に同期される第 1 クロック CLK 1 を発生できる。第 1 クロック CLK 1 はシステムオンチップ 1200 ~ 8200 の構成要素へ供給され得る。プロセッサー 1040 ~ 8040 は本発明の実施形態によるレベル変換器 100 を包含するか、或いはレベル変換器 100 に連結され得る。レベル変換器 100 は高レベル区間の比率と低レベル区間の比率とを維持し、第 1 電圧ドメインの第 1 クロック CLK 1 を第 2 電圧ドメインの第 2 クロック CLK 2 に変換する。プロセッサー 1040 ~ 8040 は第 2 クロック CLK 2 に応じて動作する。システムオンチップ 1200 ~ 8200 の他の構成要素は第 1 クロック CLK 1 に応じて動作する。

#### 【0165】

テレビ 9500 は 3 次元テレビ及びスマートテレビであり得る。図 19 に図示せざが、テレビ 9500 の後面、上面、下面、及び側面の中で少なくとも 1 つへディスプレー部 1070 ~ 8070、スピーカー 1090 ~ 8090、及び使用者インターフェイス 1140 ~ 8140 が追加的に提供され得る。また、テレビ 6500 に連結されるアクセサリー (accessory) として、ディスプレー部 1070 ~ 8070、スピーカー 1090 ~ 8090、及び使用者インターフェイス 1140 ~ 8140 が追加的に提供され得る。例示的に、テレビ 9500 と通信するリモートコントローラー (remote controller) が使用者インターフェイス 1140 ~ 8140 に追加的に提供され得る。

#### 【0166】

本発明の詳細な説明では具体的な実施形態について説明したが、本発明の範囲と技術的思想で逸脱しない限度内で様々な変形が可能とする。したがって本発明の範囲は上述した実施形態に限定されることでなく、後述する特許請求の範囲のみでなくこの発明の特許請求の範囲と均等なことによって定まれなければならない。

#### 【符号の説明】

#### 【0167】

|           |                 |

|-----------|-----------------|

| 100       | レベル変換器          |

| 110       | 第 1 電圧変換回路      |

| 111       | 第 1 インバータ       |

| 113       | 第 2 インバータ       |

| 120       | 第 2 電圧変換回路      |

| 121       | 第 3 インバータ       |

| 123       | 第 4 インバータ       |

| N1 ~ N4   | NMOS トランジスター    |

| P1 ~ P4   | PMOS トランジスター    |

| 500       | システムオンチップ (SOC) |

| 510       | プロセッサー          |

| 512 ~ 519 | フリップフロップ        |

| 520       | 位相ロックループ        |

| 530       | 周辺プロック          |

| 540       | オーディオプロック       |

10

20

30

40

50

5 5 0 ディスプレーブロック

5 6 0 グラフィックブロック

5 7 0 イメージプロセシングブロック

5 8 0 コーデックブロック

1 0 0 0 ~ 8 0 0 0 マルチメディア装置

1 0 1 0 ~ 8 0 1 0 発振器

1 0 2 0 ~ 8 0 2 0 クロック発生部

1 0 3 0 ~ 8 0 3 0 位相ロックグループ

1 0 4 0 ~ 8 0 4 0 プロセッサー

1 0 5 0 ~ 8 0 5 0 メモリー

1 0 6 0 ~ 8 0 6 0 ディスプレー制御部

1 0 7 0 ~ 8 0 7 0 ディスプレー部

1 0 8 0 ~ 8 0 8 0 サウンド制御部

1 0 9 0 ~ 8 0 9 0 スピーカー

1 1 0 0 ~ 8 1 0 0 格納部

1 1 1 0 ~ 8 1 1 0 モデム

1 1 2 0 ~ 7 1 2 0 イメージプロセシング部

1 1 3 0 ~ 8 1 3 0 カメラ

1 1 4 0 ~ 8 1 4 0 使用者インターフェイス

1 1 5 0 ~ 8 1 5 0 コーデック部

9 1 0 0 スマートフォン

9 2 0 0 タブレットコンピューター

9 3 0 0 モバイルコンピューター

9 4 0 0 コンピューター

9 5 0 0 テレビ

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 7】

【図 1 8】

【図 19】

---

フロントページの続き

(72)発明者 具 滋天

大韓民国ソウル特別市江南区道谷洞（番地なし）道谷レクセルアパート102棟506号

(72)発明者 林 慶默

大韓民国京畿道華城市石隅洞（番地なし）ウミリンプンギョンチェアパート116棟3202号

F ターム(参考) 5J056 AA37 BB21 DD13 DD29 EE06 EE08 EE15 FF01 GG09 KK01