(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-161236

(P2010-161236A)

(43) 公開日 平成22年7月22日(2010.7.22)

(51) Int.Cl.

|      |         |           |

|------|---------|-----------|

| HO1L | 27/146  | (2006.01) |

| HO1L | 31/10   | (2006.01) |

| HO1L | 21/8234 | (2006.01) |

| HO1L | 27/088  | (2006.01) |

F 1

|      |       |      |

|------|-------|------|

| HO1L | 27/14 | A    |

| HO1L | 31/10 | G    |

| HO1L | 27/08 | 102B |

| HO1L | 27/08 | 102C |

テーマコード(参考)

|       |

|-------|

| 4M118 |

| 5FO48 |

| 5FO49 |

審査請求 未請求 請求項の数 10 O L (全 17 頁)

(21) 出願番号

特願2009-2917(P2009-2917)

(22) 出願日

平成21年1月8日(2009.1.8)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】光電変換装置の製造方法

(57) 【要約】 (修正有)

【課題】光電変換部がエッチングダメージを低減し、光電変換部における保護領域のオフセットの制御精度を向上する。

【解決手段】画素配列領域における転送トランジスタのゲート電極21を形成する第1の工程と、前記転送トランジスタのゲート電極21をマスクとしてイオンを注入し、第1の導電型の半導体領域を形成する第2の工程と、前記転送トランジスタのゲート電極21を覆うように絶縁膜30iを形成する第3の工程と、前記転送トランジスタのゲート電極21が前記絶縁膜30iにより覆われた状態で、前記転送トランジスタのゲート電極21と前記絶縁膜30iにおける前記転送トランジスタのゲート電極21の側面を覆う部分とをマスクとしてイオンを注入することにより、反対導電型である第2の導電型の前記保護領域14を形成し、前記半導体領域における前記保護領域14を除いた部分を前記第1の導電型の前記電荷蓄積領域とする第4の工程とを備える。

【選択図】図4

**【特許請求の範囲】**

**【請求項 1】**

電荷蓄積領域及び前記電荷蓄積領域の上に配された保護領域を有する光電変換部と、電荷電圧変換部と、前記電荷蓄積領域の電荷を前記電荷電圧変換部へ転送する転送トランジスタと、前記電荷電圧変換部の電圧に応じた信号を出力する出力部とをそれぞれ含む複数の画素が配列されるべき画素配列領域を有する光電変換装置の製造方法であって、

半導体基板の上に、前記画素配列領域における前記転送トランジスタのゲート電極を形成する第1の工程と、

前記半導体基板の前記画素配列領域に、第1の導電型の半導体領域を形成する第2の工程と、

前記半導体基板及び前記転送トランジスタのゲート電極を覆うように絶縁膜を形成する第3の工程と、

前記半導体基板及び前記転送トランジスタのゲート電極が前記絶縁膜により覆われた状態で、前記半導体基板における前記半導体領域に、前記転送トランジスタのゲート電極と前記絶縁膜における前記転送トランジスタのゲート電極の側面を覆う部分とをマスクとしてイオンを注入することにより、前記第1の導電型に対して反対導電型である第2の導電型の前記保護領域を形成するとともに、前記半導体領域における前記保護領域を除いた部分を前記第1の導電型の前記電荷蓄積領域とする第4の工程と、

を備えたことを特徴とする光電変換装置の製造方法。

**【請求項 2】**

前記光電変換装置は、前記画素配列領域の周辺に配された領域であって前記複数の画素を制御するためのMOSトランジスタを含む制御回路が配されるべき周辺領域をさらに有し、

前記第1の工程では、前記半導体基板の上に、前記転送トランジスタのゲート電極に加えて、前記周辺領域における前記MOSトランジスタのゲート電極を形成し、

前記第3の工程では、前記半導体基板、前記転送トランジスタのゲート電極、及び前記MOSトランジスタのゲート電極を覆うように前記絶縁膜を形成し、

前記第4の工程の後に、前記絶縁膜を覆うように他の絶縁膜を形成する第5の工程と、

前記MOSトランジスタのゲート電極の側面を覆う部分が残るよう、前記絶縁膜の前記周辺領域における部分と前記他の絶縁膜の前記周辺領域における部分とをエッチングすることにより、前記MOSトランジスタのゲート電極の側面に隣接した位置にサイドウォールスペーサを形成する第6の工程と、

をさらに備えた

ことを特徴とする請求項1に記載の光電変換装置の製造方法。

**【請求項 3】**

前記第3の工程では、前記絶縁膜をシリコン窒化物で形成し、

前記第5の工程では、前記他の絶縁膜をシリコン酸化物で形成する

ことを特徴とする請求項2に記載の光電変換装置の製造方法。

**【請求項 4】**

前記第4の工程では、前記絶縁膜の厚さを制御することにより、前記転送トランジスタのゲート電極の前記側面を含む平面からのゲート長方向における前記保護領域の境界のオフセットを制御する

ことを特徴とする請求項1から3のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 5】**

前記第4の工程では、前記ゲート電極の上方から前記半導体領域へ向かうように、前記半導体基板の法線に対する、0度より大きく10度より小さい角度でイオンを注入することを特徴とする、請求項1から4のいずれか1項に記載の光電変換装置の製造方法。

**【請求項 6】**

前記第4の工程は、

第1の条件でイオンを注入することにより、前記保護領域の一部として、前記第2の導

10

20

30

40

50

電型の不純物を第1の濃度で含む第1の層を形成する第1の注入工程と、

第2の条件でイオンを注入することにより、前記保護領域の他の一部として、前記第1の層の上に配される、前記第2の導電型の不純物を前記第1の濃度より高い第2の濃度で含む第2の層を形成する第2の注入工程と、

を含む

ことを特徴とする請求項1から5のいずれか1項に記載の光電変換装置の製造方法。

#### 【請求項7】

前記転送トランジスタのゲート電極の前記側面を含む平面からのゲート長方向における前記第1の層の境界のオフセットは、前記転送トランジスタのゲート電極の前記側面を含む平面からのゲート長方向における前記第2の層の境界のオフセットより大きい

10

ことを特徴とする請求項6に記載の光電変換装置の製造方法。

#### 【請求項8】

前記絶縁膜は、前記光電変換部の受光面における光の反射を防止する反射防止膜として機能する

ことを特徴する請求項1から7のいずれか1項に記載の光電変換装置の製造方法。

#### 【請求項9】

前記第3の工程では、低圧CVD法により、前記絶縁膜を形成する

ことを特徴とする請求項1から8のいずれか1項に記載の光電変換装置の製造方法。

#### 【請求項10】

前記第2の工程では、前記転送トランジスタのゲート電極をマスクとしてイオンを注入することにより、前記第1の導電型の半導体領域を形成する

20

ことを特徴とする請求項1から9のいずれか1項に記載の光電変換装置の製造方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、光電変換装置の製造方法に関する。

##### 【背景技術】

##### 【0002】

特許文献1には、特許文献1の図1に示すように、固体撮像装置のホトダイオードにおいて、電荷を蓄積するためのn型の半導体領域であるn層104と、そのn層104の上にp型の半導体領域であるp層105とを設けることが記載されている。特許文献1によれば、この構成により、ホトダイオードの受光面における暗電流を抑制できるとされている。

30

##### 【0003】

特許文献1には、そのホトダイオードにおいて、n層104から連続して転送MOSトランジスタのゲート領域103(制御電極)の下まで延在するバイパス領域106を設けることが記載されている。このバイパス領域106の幅は、特許文献1の図4に示すように、ホトレジスト609と制御電極603とをマスク材として斜めに(注入角度=7°で)BF2イオンを注入することにより制御される。あるいは、このバイパス領域106の幅は、特許文献1の図6に示すように、ホトレジスト1109と制御電極1103とサイドスペーサ1111とをマスク材として斜めに(注入角度=7°で)BF2イオンを注入することにより制御される。これにより、特許文献1によれば、バイパス領域の加工精度を向上できるとされている。

40

##### 【0004】

特許文献2には、特許文献2の図5(b)に示すように、画素配列領域101におけるゲート電極31,32と周辺回路領域102におけるゲート電極42とを形成後、n型不純物を導入してフォトダイオードの半導体領域33を形成することが記載されている。その後、p型不純物を導入してフォトダイオードを埋め込み構造とするための表面p型領域35を形成する。さらに、ゲート電極をマスクとしたイオン注入によりn型不純物を導入し、ソース、ドレインの一部を構成する半導体領域3,34,44を形成する。

50

**【 0 0 0 5 】**

特許文献 2 には、特許文献 2 の図 5 ( c ) に示すように、画素配列領域 101 及び周辺回路領域 102 を覆うように、シリコン窒化膜 36 を形成し、その上にシリコン酸化膜 37 を形成することが記載されている。

**【 0 0 0 6 】**

さらに、特許文献 2 には、特許文献 2 の図 5 ( d ) に示すように、周辺回路領域 102 のシリコン窒化膜 36 及びシリコン酸化膜 37 をエッチバックすることにより、周辺回路領域 102 のゲート電極 42 の側壁にサイドスペーサを形成することが記載されている。このとき、画素配列領域 101 には、その全面にシリコン窒化膜 36 及びシリコン酸化膜 37 が残存している。これにより、画素配列領域の MOS トランジスタにおける電界緩和層の幅を広くするとともに、周辺回路領域 102 の MOS トランジスタにおける電界緩和層の幅を狭くできる。この結果、特許文献 2 によれば、画素配列領域の MOS トランジスタのホットキャリアによる特性劣化の抑制と周辺回路領域の MOS トランジスタの高駆動能力実現とを両立することができるとされている。

10

【特許文献 1】特開 2005 - 123517 号公報

【特許文献 2】特開 2008 - 041726 号公報

**【発明の開示】****【発明が解決しようとする課題】****【 0 0 0 7 】**

20

特許文献 1 には、SiO 又は SiN からなる膜を半導体基板の全面に塗布した後に所定の部分だけ残してエッティングすることにより、サイドスペーサ 1111 を形成することが記載されている。具体的には、特許文献 1 の図 7 に示すように、SiO 又は SiN からなる膜とホトレジストとでホトダイオードをマスキングして保護した状態でエッティングを行うことにより、特許文献 1 の図 6 ( b ) に示すようなサイドスペーサ 1111 を形成する。これにより、特許文献 1 によれば、ホトダイオードで生じる暗電流を抑制できるとされている。

**【 0 0 0 8 】**

30

しかし、特許文献 1 の技術では、サイドスペーサ 1111 を形成する工程が終わった後に、ホトダイオードをマスキングしている膜やホトレジストをエッティングにより除去する際にホトダイオードがエッティングダメージを受ける可能性がある。

**【 0 0 0 9 】**

30

ところで、CMOS センサのような撮像装置において多画素化にともないチップ面積の低減が求められている。それに伴い、周辺回路（周辺領域における MOS トランジスタ）を微細化することが要求されている。それに対して、複数の画素が配された画素配列領域では、画素の寸法を微細化することよりも、転送トランジスタによるフォトダイオードからフロー・ティング・ディフュージョンへの電荷の転送効率を向上することが優先的に求められている。ここで、フォトダイオードが、電荷を蓄積するための n 型の不純物を含む電荷蓄積領域と、その電荷蓄積領域の上に配され p 型の不純物を含む保護領域とで構成されている場合を考える。フォトダイオードにおける暗電流低減と転送 MOS トランジスタによる電荷の転送効率の向上とを両立するためには、電荷蓄積領域の上における、転送 MOS トランジスタのゲート電極から適切なオフセットを有する位置に、保護領域を形成する必要がある。

40

**【 0 0 1 0 】**

50

仮に、このオフセットが小さすぎると、電荷蓄積領域に蓄積された電荷が転送 MOS トランジスタのチャネル領域へ向かう際に保護領域による電位障壁が妨げとなり、電荷の転送効率が低下する。仮に、このオフセットが大きすぎると、電荷蓄積領域における半導体基板の表面に露出する部分が広くなるので、フォトダイオードにおける暗電流が増加する。そこで、このオフセットは、フォトダイオードにおける暗電流低減と転送 MOS トランジスタによる電荷の転送効率の向上とを両立するために決められた値になるように、微細に制御する必要がある。

## 【0011】

特許文献2には、転送MOSトランジスタのゲート電極31からの表面p型領域のオフセットの制御精度をどのように向上するのかについて記載がない。

## 【0012】

本発明の目的は、光電変換装置において、光電変換部がエッチングダメージを受けることを低減するとともに、転送トランジスタのゲート電極からの光電変換部における保護領域のオフセットの制御精度を向上することにある。

## 【課題を解決するための手段】

## 【0013】

本発明の1つの側面に係る光電変換装置の製造方法は、電荷蓄積領域及び前記電荷蓄積領域の上に配された保護領域を有する光電変換部と、電荷電圧変換部と、前記電荷蓄積領域の電荷を前記電荷電圧変換部へ転送する転送トランジスタと、前記電荷電圧変換部の電圧に応じた信号を出力する出力部とをそれぞれ含む複数の画素が配列されるべき画素配列領域を有する光電変換装置の製造方法であって、半導体基板の上に、前記画素配列領域における前記転送トランジスタのゲート電極を形成する第1の工程と、前記半導体基板の前記画素配列領域に、前記転送トランジスタのゲート電極をマスクとしてイオンを注入することにより、第1の導電型の半導体領域を形成する第2の工程と、前記半導体基板及び前記転送トランジスタのゲート電極を覆うように絶縁膜を形成する第3の工程と、前記半導体基板及び前記転送トランジスタのゲート電極が前記絶縁膜により覆われた状態で、前記半導体基板における前記半導体領域に、前記転送トランジスタのゲート電極と前記絶縁膜における前記転送トランジスタのゲート電極の側面を覆う部分とをマスクとしてイオンを注入することにより、前記第1の導電型に対して反対導電型である第2の導電型の前記保護領域を形成するとともに、前記半導体領域における前記保護領域を除いた部分を前記第1の導電型の前記電荷蓄積領域とする第4の工程とを備えたことを特徴とする。

10

20

30

## 【発明の効果】

## 【0014】

本発明によれば、光電変換装置において、光電変換部がエッチングダメージを受けることを低減できるとともに、転送トランジスタのゲート電極からの光電変換部における保護領域のオフセットの制御精度を向上することができる。

## 【発明を実施するための最良の形態】

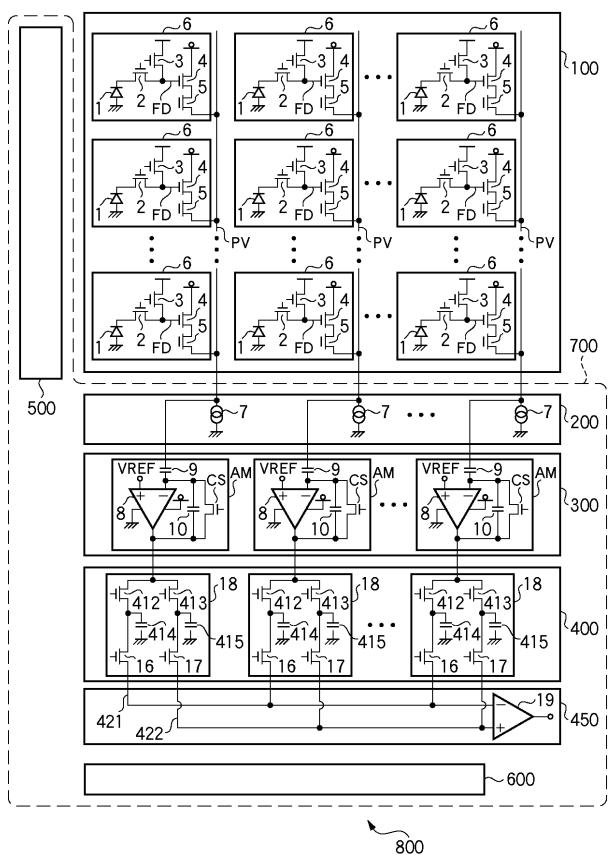

## 【0015】

本発明の実施形態に係る光電変換装置800の概略構成を、図1を用いて説明する。図1は、本発明の実施形態に係る光電変換装置800の構成を示す図である。

## 【0016】

光電変換装置800は、画素配列領域100及び周辺領域700を有する。画素配列領域100は、複数の画素が配列されるべき領域である。周辺領域700は、画素配列領域100の周辺に配された領域であって、複数の画素を制御するためのMOSトランジスタをそれぞれ含む複数の制御回路や読み出し経路となる回路が配されるべき領域である。

## 【0017】

画素配列領域100には、複数の画素6が行方向及び列方向に配列されている。

40

## 【0018】

各画素6は、光電変換部1、転送トランジスタ2、電荷電圧変換部FD、リセット部3、出力部4、及び選択部5を含む。

## 【0019】

光電変換部1は、光に応じた電荷(信号)を発生させて蓄積する。光電変換部1は、例えば、フォトダイオードである。光電変換部1は、後述するように、電荷を蓄積するための電荷蓄積領域11と、電荷蓄積領域11を保護するための保護領域14とを含む(図2参照)。

## 【0020】

転送トランジスタ2は、電荷蓄積領域11の電荷を電荷電圧変換部FDへ転送する。転

50

送トランジスタ 2 は、後述の垂直走査回路 500 からアクティブレベルの転送制御信号がゲートに供給された際にオンすることにより、電荷蓄積領域 11 の電荷を電荷電圧変換部 FD へ転送する。

#### 【0021】

電荷電圧変換部 FD は、転送された電荷を電圧に変換する。電荷電圧変換部 FD は、例えば、フローティングディファージョンである。

#### 【0022】

リセット部 3 は、電荷電圧変換部 FD をリセットする。リセット部 3 は、例えば、リセットトランジスタであり、垂直走査回路 500 からアクティブレベルのリセット制御信号がゲートに供給された際にオンすることにより、電荷電圧変換部 FD をリセットする。

10

#### 【0023】

出力部 4 は、電荷電圧変換部 FD の電圧に応じた信号を出力する。出力部 4 は、例えば、増幅トランジスタであり、列信号線 PV に接続された定電流源 7 とともにソースフォロワ動作を行うことにより、電荷電圧変換部 FD の電圧に応じた信号を列信号線 PV へ出力する。すなわち、出力部 4 は、リセット部 3 により電荷電圧変換部 FD がリセットされた状態で電荷電圧変換部 FD の電圧に応じたノイズ信号を列信号線 PV へ出力する。出力部 4 は、転送トランジスタ 2 により電荷蓄積領域 11 の電荷が電荷電圧変換部 FD へ転送された状態で電荷電圧変換部 FD の電圧に応じた光信号を列信号線 PV へ出力する。

#### 【0024】

選択部 5 は、画素 6 を選択状態 / 非選択状態にする。選択部 5 は、例えば、選択トランジスタであり、垂直走査回路 500 からアクティブレベルの転送制御信号がゲートに供給された際にオンすることにより、画素 6 を選択状態にする。選択部 5 は、垂直走査回路 500 からノンアクティブレベルの転送制御信号がゲートに供給された際にオフすることにより、画素 6 を非選択状態にする。

20

#### 【0025】

周辺領域 700 には、上記のように、複数の制御回路が配される。複数の制御回路は、垂直走査回路 500 、定電流源ブロック 200 、列アンプブロック 300 、保持容量ブロック 400 、水平走査回路 600 、及び出力アンプブロック 450 が配される。

#### 【0026】

垂直走査回路 500 は、画素配列領域 100 を垂直方向（列方向）に走査することにより、信号を読み出すべき行（読み出し行）を選択し、その選択した読み出し行から信号（ノイズ信号、光信号）が読み出されるようにする。垂直走査回路 500 は、複数の MOSトランジスタを含む。

30

#### 【0027】

定電流源ブロック 200 は、画素配列領域 100 における複数の列に接続された複数の列信号線 PV に対応して、複数の定電流源 7 を含む。各定電流源 7 は、例えば、MOSトランジスタを含む。

#### 【0028】

列アンプブロック 300 は、複数の列信号線 PV に対応して、複数の列アンプ部 AM を含む。複数の列アンプ部 AM は、行方向に配列されている。

40

#### 【0029】

各列アンプ部 AM は、例えば、差動増幅器 8 、クランプ容量 9 、帰還容量 10 、クランプ制御スイッチ CS を含む。各列アンプ部 AM は、差動増幅器 8 のオフセットを第 1 の信号として出力する。また、各列アンプ部 AM は、クランプ動作を行うことにより、光信号とノイズ信号との差分信号に差動増幅器 8 のオフセットが重畠された信号を第 2 の信号として出力する。クランプ制御スイッチ CS は、例えば、MOSトランジスタを含む。

#### 【0030】

保持容量ブロック 400 は、複数の列アンプ部 AM に対応して、複数の列信号保持部 18 を含む。複数の列信号保持部 18 は、行方向に配列されている。

#### 【0031】

50

各列信号保持部 18 は、第 1 の書込トランジスタ 412、第 2 の書込トランジスタ 413、第 1 の保持容量 414、第 2 の保持容量 415、第 1 のトランジスタ 16、及び第 2 のトランジスタ 17 を含む。

#### 【0032】

第 1 の書込トランジスタ (MOSトランジスタ) 412 は、オンした際に、列アンプ部 AM から出力された第 1 の信号を第 1 の保持容量 414 へ書き込む。その後、第 1 の書込トランジスタ 412 がオフすると、第 1 の保持容量 414 は第 1 の信号を保持する。

#### 【0033】

第 2 の書込トランジスタ (MOSトランジスタ) 413 は、オンした際に、列アンプ部 AM から出力された第 2 の信号を第 2 の保持容量 415 へ書き込む。その後、第 2 の書込トランジスタ 413 がオフすると、第 2 の保持容量 415 は第 2 の信号を保持する。

10

#### 【0034】

第 1 の転送トランジスタ (MOSトランジスタ) 16 は、オンした際に、第 1 の保持容量 414 に保持された第 1 の信号を第 1 の出力線 421 経由で出力アンプ 19 へ転送する。

#### 【0035】

第 2 の転送トランジスタ (MOSトランジスタ) 17 は、オンした際に、第 2 の保持容量 415 に保持された第 2 の信号を第 2 の出力線 422 経由で出力アンプ 19 へ転送する。

20

#### 【0036】

水平走査回路 600 は、保持容量ブロック 400 を水平方向 (行方向) に走査することにより、保持容量ブロック 400 に保持された読み出し行の信号における各列の信号が順次に出力アンプ 19 へ転送されるようにする。すなわち、水平走査回路 600 は、各列の第 1 のトランジスタ 16 及び第 2 のトランジスタ 17 を順次にオンさせる。

#### 【0037】

出力アンプブロック 450 は、第 1 の出力線 421、第 2 の出力線 422、及び出力アンプ 19 を含む。出力アンプ 19 は、第 1 の出力線 421 を介して伝達された第 1 の信号と第 2 の出力線 422 を介して伝達された第 2 の信号との差分をとる CDS 处理を行うことにより、画像信号を生成して出力する。出力アンプ 19 は、例えば、複数の MOSトランジスタを含む。

30

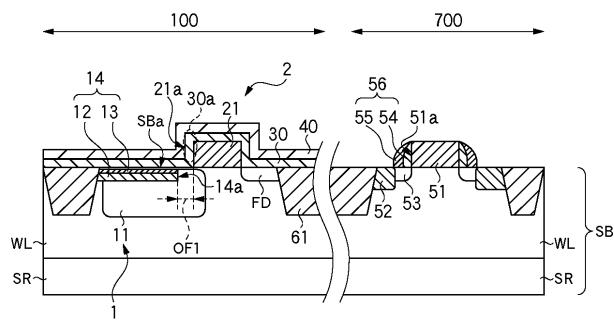

#### 【0038】

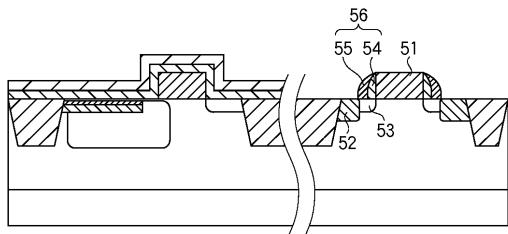

次に、本発明の実施形態に係る光電変換装置 800 の断面構成を、図 2 を用いて説明する。図 2 は、本発明の実施形態に係る光電変換装置 800 の断面構成を示す図である。

#### 【0039】

光電変換装置 800 は、半導体基板 SB、ゲート電極 21、ゲート電極 51、絶縁膜 30、絶縁膜 40、サイドウォールスペーサ 56 を備える。

#### 【0040】

半導体基板 SB は、半導体領域 SR、ウエル WL、素子分離部 61、光電変換部 1、電荷電圧変換部 FD、半導体領域 52、及び LDD 領域 53 を含む。半導体領域 SR、ウエル WL、及び素子分離部 61 は、画素配列領域 100 及び周辺領域 700 に配されている。光電変換部 1、及び電荷電圧変換部 FD は、画素配列領域 100 に配されている。半導体領域 52、及び LDD 領域 53 は、周辺領域 700 に配されている。

40

#### 【0041】

半導体領域 SR は、半導体基板 SB の表面 SBa から深い位置に配されている。半導体領域 SR は、第 1 の導電型 (例えば、N型) の不純物 (例えば、リン) を低濃度で含む。

#### 【0042】

ウエル WL は、半導体基板 SB における半導体領域 SR の上 (表面 SBa 側) に配されている。ウエル WL は、第 2 の導電型 (例えば、P型) の不純物 (例えば、ボロン) を低濃度で含む。第 2 の導電型は、第 1 の導電型に対して反対導電型である。

#### 【0043】

50

素子分離部 6 1 は、ウエルWLにおける複数の素子（例えば、光電変換部1、転送トランジスタ2におけるソース・ドレイン、MOSトランジスタにおけるソース・ドレイン）を分離するように配されている。素子分離部6 1 は、例えば、STI型の素子分離構造又はLOCOS型の素子分離構造をしている。

## 【0044】

光電変換部1は、電荷蓄積領域1 1及び保護領域1 4を含む。

## 【0045】

電荷蓄積領域1 1は、電荷を蓄積するための領域であり、第1の導電型（例えば、N型）の不純物（例えば、リン）をウエルWLより高い濃度で含む。

## 【0046】

保護領域1 4は、電荷蓄積領域1 1を保護するように、半導体基板SBにおける電荷蓄積領域1 1の上（表面SBa側）に配されている。保護領域1 4におけるゲート電極2 1に面した境界1 4 aは、ゲート電極2 1の側面2 1 aを含む平面からのゲート長方向におけるオフセットOF 1を有する位置に配されている。このオフセットOF 1は、後述のように、絶縁膜3 0の厚さを制御することにより制御されたものである。すなわち、保護領域1 4は、ゲート電極2 1と絶縁膜3 0におけるゲート電極2 1の側面2 1 aを覆う部分3 0 aとをマスクとして自己整合的に形成されたものである。

10

## 【0047】

保護領域1 4は、例えば2層構造をしており、第1の層1 2及び第2の層1 3を含む。第1の層1 2は、電荷蓄積領域1 1の上（表面SBa側）に配されている。第1の層1 2は、第2の導電型（例えば、P型）の不純物（例えば、ボロン）を第1の濃度で含む。第2の層1 3は、第1の層1 2の上（表面SBa側）に配されている。第2の層1 3は、第2の導電型の不純物を、第1の濃度より高い第2の濃度で含む。すなわち、表面SBa側の不純物濃度を高く、かつ、電荷蓄積領域1 1側の不純物濃度が低くになるように、第1の層1 2及び第2の層1 3を配置する。

20

## 【0048】

これにより、半導体基板SBの表面SBaから生じる暗電流を低減しつつ、電荷転送の際ににおける保護領域1 4による電位障壁を低くすることが可能となる。また、電荷蓄積領域1 1側の不純物濃度が低いことで電荷蓄積領域1 1の飽和電荷を低減してしまうことを抑制している。すなわち、保護領域1 4を2層構造にすることにより、電荷転送効率の向上と暗電流低減との両立が容易になる。

30

## 【0049】

なお、2回のイオン注入を要するので、製造コストと性能とのバランスを考慮し、構造を選択することができる。例えば、保護領域1 4は、1層構造でも良い。

## 【0050】

電荷電圧変換部FDは、電荷蓄積領域1 1から転送された電荷を一時的に保持するための領域であり、第1の導電型（例えば、N型）の不純物（例えば、リン）をウエルWLより高い濃度で含む。

30

## 【0051】

半導体領域5 2は、電荷を一時的に保持するための領域であり、第1の導電型（例えば、N型）の不純物（例えば、リン）をウエルWLより高い濃度で含む。半導体領域5 2は、上記のMOSトランジスタにおけるソース電極又はドレイン電極として機能する。半導体領域5 2は、後述するように、ゲート電極5 1とサイドウォールスペーサ5 6とをマスクとして自己整合的に形成されたものである。

40

## 【0052】

LDD領域5 3は、ゲート電極5 1に電圧が印加された際におけるゲート電極5 1と半導体領域5 2との電界を緩和するための領域であり、第1の導電型の不純物を半導体領域5 2より低い濃度で含む。LDD領域5 3は、後述するように、ゲート電極5 1をマスクとして自己整合的に形成されたものである。

## 【0053】

50

ゲート電極 2 1 は、画素配列領域 1 0 0 における半導体基板 S B の表面 S B a の上に配されている。ゲート電極 2 1 は、上記の転送トランジスタ 2 におけるゲート電極である。ゲート電極 2 1 の側面 2 1 a に隣接する位置には、サイドウォールスペーサが配されていない。

【 0 0 5 4 】

ゲート電極 5 1 は、周辺領域 7 0 0 における半導体基板 S B の表面 S B a の上に配されている。ゲート電極 5 1 は、上記の M O S トランジスタにおけるゲート電極である。ゲート電極 5 1 の側面 5 1 a に隣接する位置には、サイドウォールスペーサ 5 6 が配されている。

【 0 0 5 5 】

絶縁膜 3 0 は、画素配列領域 1 0 0 における半導体基板 S B 及びゲート電極 2 1 を覆うように延びている。絶縁膜 3 0 は、周辺領域 7 0 0 に配されていない。絶縁膜 3 0 は、例えば、シリコン窒化物で形成されている。

【 0 0 5 6 】

絶縁膜 4 0 は、画素配列領域 1 0 0 における絶縁膜 3 0 を覆うように延びている。絶縁膜 4 0 は、周辺領域 7 0 0 に配されていない。絶縁膜 4 0 は、例えば、シリコン酸化物で形成されている。

【 0 0 5 7 】

サイドウォールスペーサ 5 6 は、周辺領域 7 0 0 における半導体基板 S B の表面 S B a の上であってゲート電極 5 1 の側面 5 1 a に隣接する位置に配されている。サイドウォールスペーサ 5 6 は、第 1 の膜 5 4 及び第 2 の膜 5 5 を含む。第 1 の膜 5 4 は、ゲート電極 5 1 の側面 5 1 a に隣接して配されている。第 2 の膜 5 5 は、第 1 の膜 5 4 に隣接して配されている。第 1 の膜 5 4 は、絶縁膜 3 0 と同じ材料で形成されており、例えば、シリコン窒化物で形成されている。第 2 の膜 5 5 は、絶縁膜 4 0 と同じ材料で形成されており、例えば、シリコン酸化物で形成されている。なお、絶縁膜 3 0 と半導体基板 S B 及びゲート電極 2 1 との間、及び第 1 の膜 5 4 とゲート電極 5 1 との間にシリコン酸化物からなる膜を設けてもよい。

【 0 0 5 8 】

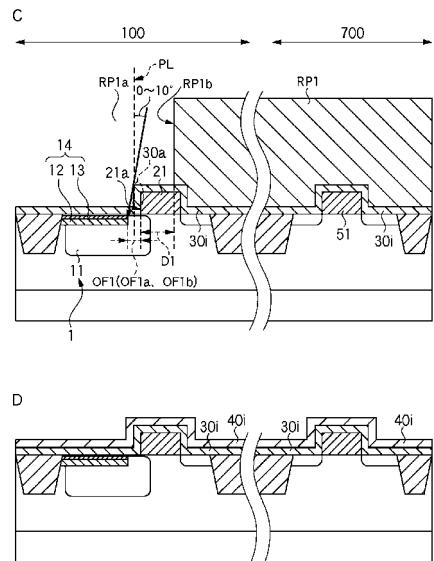

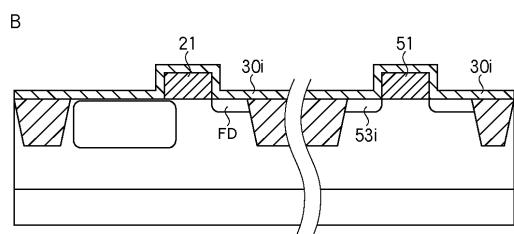

次に、本発明の実施形態に係る光電変換装置 8 0 0 の製造方法を、図 3 ~ 図 5 を用いて説明する。図 3 ~ 図 5 は、本発明の実施形態に係る光電変換装置 8 0 0 の製造方法を示す工程断面図である。

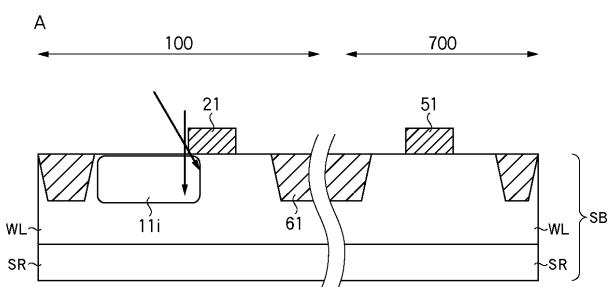

【 0 0 5 9 】

図 3 の A に示す工程（第 1 の工程）では、S T I 技術や L O C O S 技術などにより、半導体基板 S B に素子分離部 6 1 を形成する。そして、半導体基板 S B にイオンを注入することにより、第 2 の導電型（例えば、P 型）の不純物（例えば、ボロン）を低濃度で含むウエル W L を形成する。半導体基板 S B におけるイオンが注入されなかった領域は、第 1 の導電型（例えば、N 型）の不純物（例えば、リン）を低濃度で含む半導体領域 S R となる。

【 0 0 6 0 】

その後、半導体基板 S B の上に、ゲート電極及びゲート電極となるべきポリシリコン層を形成する。ポリシリコン層の上に、ゲート電極及びゲート電極に対応したパターンを有するレジストパターンを形成する。そのレジストパターンをマスクとして、半導体基板 S B の上に、画素配列領域 1 0 0 における転送トランジスタ 2 のゲート電極 2 1 と周辺領域 7 0 0 における M O S トランジスタのゲート電極 5 1 とを形成する。

【 0 0 6 1 】

そして（第 2 の工程）、半導体基板 S B 、ゲート電極 2 1 、及びゲート電極 5 1 の上に、周辺領域 7 0 0 の全面を覆い画素配列領域 7 0 0 における光電変換部 1 を形成すべき領域に対応した開口パターンを有するレジストパターンを形成する。半導体基板 S B の画素配列領域 7 0 0 に、開口パターン及びゲート電極 2 1 をマスクとしてイオンを注入することにより、第 1 の導電型の不純物を含む半導体領域 1 1 i を形成する。半導体領域 1 1 i

は、電荷蓄積領域 11 となるべき半導体領域である。半導体領域 11 i は、図 3 の A に示すように、ゲート電極 21 の斜め上方からゲート電極 21 下に向かうように傾斜した角度でイオンを注入することにより形成することが好ましい。

#### 【0062】

図 3 の B に示す工程では、半導体基板 SB、ゲート電極 21、及びゲート電極 51 の上に、電荷電圧変換部 FD に対応した第 1 の開口パターンと LDD 領域 53 に対応した第 2 の開口パターンとを有するレジストパターンを形成する。そして、半導体基板 SB の画素配列領域 100 に、第 1 の開口パターン及びゲート電極 21 をマスクとしてイオンを注入することにより、第 1 の導電型の不純物を含む電荷電圧変換部 FD を形成する。また、半導体基板 SB の周辺領域 700 に、第 2 の開口パターン及びゲート電極 51 をマスクとしてイオンを注入することにより、第 1 の導電型の不純物を低濃度で含む半導体領域 53 i を形成する。半導体領域 53 i は、LDD 領域 53 となるべき半導体領域である。10

#### 【0063】

その後（第 3 の工程）、低圧 CVD 技術（低圧 CVD 法）により、半導体基板 SB、画素配列領域 100 におけるゲート電極 21、及び周辺領域 700 におけるゲート電極 51 を覆うように絶縁膜 30 i を形成する。絶縁膜 30 i は、例えば、シリコン窒化物で形成する。低圧 CVD 技術によって形成される絶縁膜 30 i は、半導体基板 SB 上及びゲート電極（21, 51）側壁など異なる箇所で成膜される膜厚がほぼ同一となること、またその膜厚均一性が良好なことなどの利点が知られている。絶縁膜 30 i は、光電変換部 1 の受光面における光の反射を防止する反射防止膜として機能させることを考慮し、その膜厚を 40 nm ~ 55 nm とすることが好適である。20

#### 【0064】

特許文献 1 には、画素部における転送 MOS ドランジスタなどの MOS ドランジスタと周回路における MOS ドランジスタと同じプロセスで形成することにより、固体撮像装置の全てを低電圧系で構成することが記載されている。これにより、特許文献 1 によれば、低電圧動作が可能なラインセンサを得ることができるとされている。

#### 【0065】

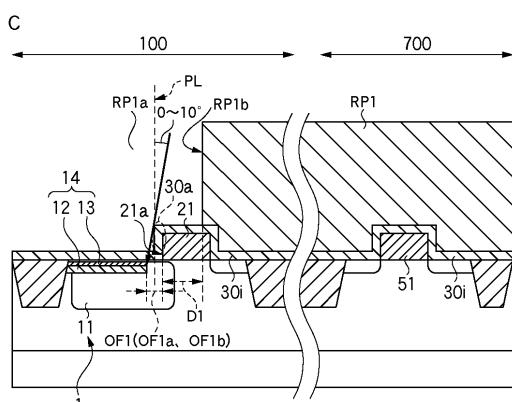

ここで、仮に、画素配列領域 100 におけるゲート電極 21 の側面に隣接した位置と周辺領域 700 におけるゲート電極 51 の側面に隣接した位置とにサイドウォールスペーサを形成すると仮定する。この場合、絶縁膜 30 i 及び後述する絶縁膜 40 i を全面的にエッチング（エッチバック）することにより、画素配列領域 100 及び周辺領域 700 におけるサイドウォールスペーサを形成することになる。このサイドウォールスペーサは、上方及び側方からのエッチングにより形成されるので、傾斜した側面を有する。上方からのエッチングに比べて側方からのエッチングは、そのエッチング量の制御が難しく、その傾斜した側面の傾斜角を高精度に制御することは困難である。このため、画素配列領域 100 におけるゲート電極 21 とサイドウォールスペーサとをマスクとしてイオンを注入した場合、ゲート電極 21 に対する保護領域 14 の位置を高精度に制御することが困難である。すなわち、ゲート電極 21 のゲート長方向におけるゲート電極 21 の側面 21 a を含む平面からの保護領域 14 の境界のオフセット OF 1 を高精度に制御することが困難である。30

#### 【0066】

それに対して、図 4 の C に示す工程（第 4 の工程）では、絶縁膜 30 i の上に、保護領域 14 を形成すべき領域に対応した開口パターン RP 1 a を有するレジストパターン RP 1 を形成する。半導体基板 SB における半導体領域 11 i に、レジストパターン RP 1 とゲート電極 21 と絶縁膜 30 i におけるゲート電極 21 の側面 21 a を覆う部分 30 a とをマスクとしてイオンを注入する。すなわち、半導体基板 SB、ゲート電極 21、及びゲート電極 51 を絶縁膜 30 i で覆った状態で、レジストパターン RP 1 とゲート電極 21 とゲート電極 21 の側面 21 a を覆う部分 30 a とをマスクとしてイオンを注入する。このとき、ゲート電極 21 の上方から半導体領域 11 i へ向かうように、半導体基板の法線 PL に対する 0 度より大きく 10 度より小さい角度でイオンを注入する。これにより、半4050

導体領域 11 i 内に第 2 の導電型の不純物を含む保護領域 14 を形成するとともに、半導体領域 11 i における保護領域 14 を除いた部分を、第 1 の導電型の不純物を含む電荷蓄積領域 11 i とする。

#### 【0067】

ここで、0 ~ 10° の小さな傾斜角度でイオンを注入するので、レジストパターン RP 1 の端面 RP 1 b のゲート電極 21 の側面 21 a を含む平面からの距離 D 1 が十分に確保されていれば、シャドーイングを抑えることができる。また、絶縁膜 30 i の厚さに応じて、ゲート電極 21 のゲート長方向におけるゲート電極 21 の側面 21 a を含む平面からの保護領域 14 の境界のオフセット OF 1 を制御する。すなわち、絶縁膜 30 i の厚さを制御することにより、オフセット OF 1 を高精度に制御することができる。

10

#### 【0068】

また、保護領域 14 を 2 層構造にする場合、第 1 の層 12 と第 2 の層 13 とを 2 回のイオン注入工程（第 1 の注入工程、第 2 の注入工程）によって形成をする。第 1 の注入工程では、第 1 の条件でイオンを注入することにより、保護領域 14 の一部として、電荷蓄積領域 11 i の上に配されるべき第 2 の導電型の不純物を第 1 の濃度で含む第 1 の層を形成する。第 2 の注入工程では、第 2 の条件でイオンを注入することにより、保護領域 14 の他の一部として、第 1 の層 12 の上に配され第 2 の導電型の不純物を第 1 の濃度より高い第 2 の濃度で含む第 2 の層 13 を形成する。第 2 の注入工程は、例えば、第 1 の注入工程の後に行う。これにより、第 2 の層 13 が第 1 の層 12 より浅くなるように、第 1 の層 12 及び第 2 の層 13 を含む保護領域 14 を形成する。また、第 2 の層 13 の不純物濃度が第 1 の層 12 の不純物濃度より濃くなるように、第 1 の層 12 及び第 2 の層 13 を含む保護領域 14 を形成する。

20

#### 【0069】

なお、第 1 の注入工程及び第 2 の注入工程におけるイオン注入の角度は、同一でもよい。あるいは、第 1 の注入工程におけるイオン注入の角度を第 2 の注入工程におけるイオン注入の角度より大きくしてもよい。これにより、ゲート電極 21 の側面 21 a を含む平面からの第 1 の層 12 の境界のオフセット OF 1 a を、ゲート電極 21 の側面 21 a を含む平面からの第 2 の層 13 の境界のオフセット OF 1 b より小さくなるように制御できる。この結果、電荷の転送路への保護領域による電位障壁の影響を小さくすることが可能となり、電荷の転送効率をさらに向上することができる。

30

#### 【0070】

そして、レジストパターン RP 1 を除去する。

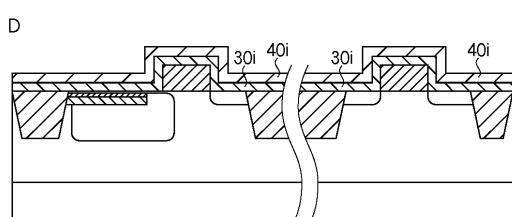

#### 【0071】

図 4 の D に示す工程（第 5 の工程）では、絶縁膜 30 i を覆うように絶縁膜（他の絶縁膜）40 i を形成する。このとき、絶縁膜 40 i の厚さを制御することにより、周辺領域 700 における後述するサイドウォールスペーサ 56 の幅 W 1 を調整することが可能となる（図 5 の E 参照）。絶縁膜 40 i は、例えば、シリコン酸化物で形成する。

#### 【0072】

ここで、仮に、画素配列領域 100 におけるゲート電極 21 の側面に隣接した位置と周辺領域 700 におけるゲート電極 51 の側面に隣接した位置とにサイドウォールスペーサを形成されていると仮定する。この場合、画素配列領域 100 及び周辺領域 700 におけるサイドウォールスペーサの幅は、ともに、上記のオフセット OF 1 に対応した大きさで形成されていることになる。この場合、サイドウォールスペーサ 56 の幅 W 1 を必要以上に大きくしなければならないので、周辺領域 700 における MOS ドラフィングの微細化が困難になる。

40

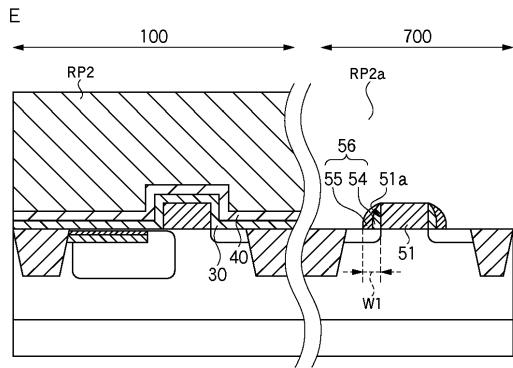

#### 【0073】

それに対して、図 5 の E に示す工程（第 6 の工程）では、絶縁膜 40 i の上に、画素配列領域 100 を覆い周辺領域 700 に対応した開口パターン RP 2 a を有するレジストパターン RP 2 を形成する。その開口パターン RP 2 a をマスクとしてエッチングを行う。すなわち、ゲート電極 51 の側面 51 a を覆う部分が残るように、絶縁膜 30 i の周辺領

50

域 700 における部分と絶縁膜 40i の周辺領域 700 における部分とをエッチングする。これにより、画素配列領域 100 における絶縁膜 30 及び絶縁膜 40 を形成するとともに、第 1 の膜 54 及び第 2 の膜 55 を含むサイドウォールスペーサ 56 を形成する。第 1 の膜 54 は、絶縁膜 30i の周辺領域 700 における部分のうちエッチングされずに残った部分である。第 2 の膜 55 は、絶縁膜 40i の周辺領域 700 における部分のうちエッチングされずに残った部分である。すなわち、画素配列領域 100 における要求される制約の影響を受けることなく、周辺領域 700 におけるサイドウォールスペーサ 56 の幅 W1 を狭くすることができるので、周辺領域 700 におけるMOSトランジスタの微細化が容易になる。

## 【0074】

図 5 の F に示す工程では、半導体領域 52 に対応した開口パターンを有するレジストパターンを形成する。その開口パターンとゲート電極 51 とサイドウォールスペーサ 56 とをマスクとしてイオンを注入する。これにより、第 1 の導電型の不純物を高濃度に含む半導体領域 52 を形成するとともに、半導体領域 53i におけるイオンが注入されなかった部分を、第 1 の導電型の不純物を低濃度に含む LDD 領域 53 とする。

10

## 【0075】

この後、画素配列領域 100 における絶縁膜 40 と周辺領域 700 における半導体基板、ゲート電極 51、及びサイドウォールスペーサ 56 とを覆うように、層間絶縁膜（図示せず）を形成する。その層間絶縁膜に、電荷電圧変換部 FD や半導体領域 52 を露出するコンタクトホールを形成し、その後、コンタクトホールに金属を埋め込んでコンタクトプラグを形成する。更に、金属配線形成、カラーフィルタ、マイクロレンズなどを形成し、光電変換装置とする。

20

## 【0076】

以上のように、本実施形態によれば、半導体基板 SB、ゲート電極 21、及びゲート電極 51 を絶縁膜 30i で覆った状態で、レジストパターン RP1 とゲート電極 21 とゲート電極 21 の側面 21a を覆う部分 30a とをマスクとしてイオンを注入する。これにより、保護領域を形成する。すなわち、画素配列領域における絶縁膜 30 や絶縁膜 40 のパターニングする工程が不要となるため、光電変換部 1 に対するエッチングダメージを低減することができる。

30

## 【0077】

また、ゲート電極 21 と絶縁膜 30i におけるゲート電極 21 の側面を覆う部分 30a とをマスクとして、自己整合的に光電変換部 1 における保護領域 14 を形成する。すなわち、絶縁膜 30i の厚さを制御することにより、ゲート電極 21 の側面 21a を含む平面からのゲート長方向における保護領域 14 の境界のオフセット OF1 を制御する。これにより、転送トランジスタのゲート電極の側面を含む平面からのゲート長方向における保護領域の境界のオフセット OF1 の制御精度を向上することができる。

## 【0078】

したがって、光電変換装置において、光電変換部がエッチングダメージを受けることを低減できるとともに、転送トランジスタのゲート電極からの光電変換部における保護領域のオフセットの制御精度を向上することができる。

40

## 【0079】

また、画素配列領域においてサイドウォールサペーサを形成せずに、周辺領域において MOSトランジスタのゲート電極に隣接した位置にサイドウォールスペーサを形成する。これにより、画素配列領域における要求される制約の影響を受けることなく、周辺領域におけるサイドウォールスペーサの幅を狭くすることができるので、周辺領域におけるMOSトランジスタを微細化することが容易になる。

## 【0080】

したがって、周辺領域におけるMOSトランジスタを微細化することができるとともに、画素配列領域における転送トランジスタからの保護領域のオフセットの制御精度を向上することができる。

50

## 【0081】

また、ゲート電極と絶縁膜におけるゲート電極の側面を覆う部分とをマスクとしてイオン注入を行うので、光電変換部における保護領域を半導体基板に対して垂直に近い角度でイオン注入して形成することができる。そのため、保護領域の製造ばらつきを低減でき、半導体基板の表面で発生する暗電流によるノイズを低減することが可能となる。従って、より小さい画素寸法の光電変換装置の製造に適した製造方法を提供することができる。

## 【0082】

さらに、上記のような製造方法によって、少ない工数で、画素配列領域における光電変換部の保護領域及び周辺領域におけるトランジスタのLDD構造をそれぞれ制御よく形成することが可能となる。

10

## 【0083】

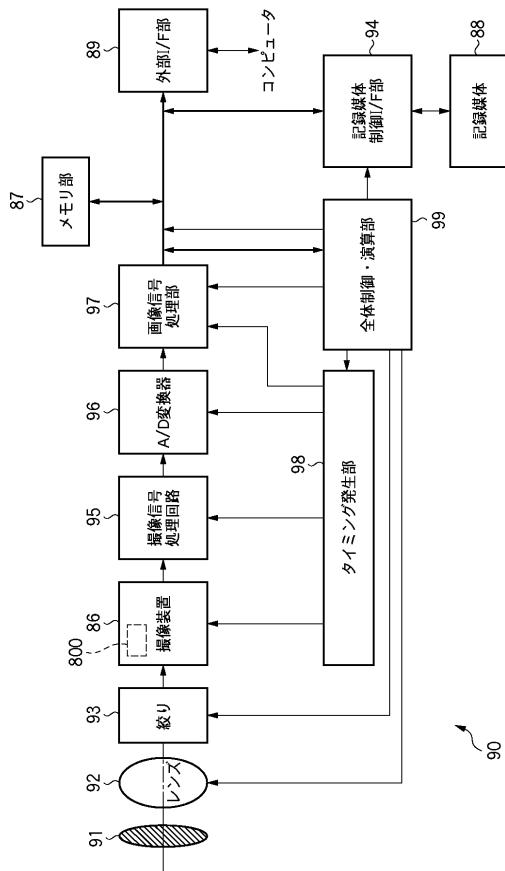

次に、本発明の光電変換装置を適用した撮像システムの一例を図6に示す。

## 【0084】

撮像システム90は、図6に示すように、主として、光学系、撮像装置86及び信号処理部を備える。光学系は、主として、シャッター91、レンズ92及び絞り93を備える。撮像装置86は、光電変換装置800を含む。信号処理部は、主として、撮像信号処理回路95、A/D変換器96、画像信号処理部97、メモリ部87、外部I/F部89、タイミング発生部98、全体制御・演算部99、記録媒体88及び記録媒体制御I/F部94を備える。なお、信号処理部は、記録媒体88を備えなくても良い。

20

## 【0085】

シャッター91は、光路上においてレンズ92の手前に設けられ、露出を制御する。

## 【0086】

レンズ92は、入射した光を屈折させて、撮像装置86の光電変換装置800の撮像面(画素配列領域100)に被写体の像を形成する。

## 【0087】

絞り93は、光路上においてレンズ92と光電変換装置800との間に設けられ、レンズ92を通過後に光電変換装置800へ導かれる光の量を調節する。

30

## 【0088】

撮像装置86の光電変換装置800は、光電変換装置800の撮像面に形成された被写体の像を画像信号に変換する。撮像装置86は、その画像信号を光電変換装置800から読み出して出力する。

## 【0089】

撮像信号処理回路95は、撮像装置86に接続されており、撮像装置86から出力された画像信号を処理する。

## 【0090】

A/D変換器96は、撮像信号処理回路95に接続されており、撮像信号処理回路95から出力された処理後の画像信号(アナログ信号)を画像信号(デジタル信号)へ変換する。

40

## 【0091】

画像信号処理部97は、A/D変換器96に接続されており、A/D変換器96から出力された画像信号(デジタル信号)に各種の補正等の演算処理を行い、画像データを生成する。この画像データは、メモリ部87、外部I/F部89、全体制御・演算部99及び記録媒体制御I/F部94などへ供給される。

## 【0092】

メモリ部87は、画像信号処理部97に接続されており、画像信号処理部97から出力された画像データを記憶する。

## 【0093】

外部I/F部89は、画像信号処理部97に接続されている。これにより、画像信号処理部97から出力された画像データを、外部I/F部89を介して外部の機器(パソコン等)へ転送する。

50

**【0094】**

タイミング発生部98は、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97に接続されている。これにより、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97へタイミング信号を供給する。そして、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97がタイミング信号に同期して動作する。

**【0095】**

全体制御・演算部99は、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94に接続されており、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94を全体的に制御する。

10

**【0096】**

記録媒体88は、記録媒体制御I/F部94に取り外し可能に接続されている。これにより、画像信号処理部97から出力された画像データを、記録媒体制御I/F部94を介して記録媒体88へ記録する。

**【0097】**

以上の構成により、光電変換装置800において良好な画像信号が得られれば、良好な画像（画像データ）を得ることができる。

**【0098】**

なお、本発明は前述の実施形態に限定されることなく、適宜変更可能である。例えば、ウエルWLは第2導電型ではなく第1導電型（例えば、N型）の不純物を低濃度で含む領域でもよい。また、ウエルWLはイオンを注入することによって形成してもよい。更に、電荷蓄積領域となるべき半導体領域11iは、ゲート電極21の形成前に、レジストパターンをマスクに用いて形成してもよい。

20

**【図面の簡単な説明】****【0099】**

【図1】本発明の実施形態に係る光電変換装置800の構成を示す図。

【図2】本発明の実施形態に係る光電変換装置800の断面構成を示す図。

【図3】本発明の実施形態に係る光電変換装置800の製造方法を示す工程断面図。

【図4】本発明の実施形態に係る光電変換装置800の製造方法を示す工程断面図。

30

【図5】本発明の実施形態に係る光電変換装置800の製造方法を示す工程断面図。

【図6】第1実施形態に係る光電変換装置を適用した撮像システムの構成図。

**【符号の説明】****【0100】**

90 撮像システム

800 光電変換装置

【図1】

【図2】

【図3】

【図4】

【 図 5 】

F

【 四 6 】

---

フロントページの続き

(72)発明者 三島 隆一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 下津佐 峰生

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 成瀬 裕章

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 4M118 AA10 AB01 BA14 CA04 DD04 EA01 EA03 EA06 EA07 EA15

EA16 FA06 FA25 FA27 FA28 FA33 GC07 GD04

5F048 AB10 AC01 BB01 BB03 BC01 BC03 BC06 BC18 BE05 BG12

BG13 DA25 DA27 DA30

5F049 MA02 NA05 NA08 NA20 NB05 PA10 QA04 RA02 RA08 SS02

SZ03 TA12