(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5368397号

(P5368397)

(45) 発行日 平成25年12月18日(2013.12.18)

(24) 登録日 平成25年9月20日(2013.9.20)

|              |            |

|--------------|------------|

| (51) Int.Cl. | F 1        |

| HO1L 21/338  | (2006.01)  |

| HO1L 29/812  | (2006.01)  |

| HO1L 21/28   | (2006.01)  |

| HO1L 29/47   | (2006.01)  |

| HO1L 29/872  | (2006.01)  |

|              | HO1L 29/80 |

|              | HO1L 21/28 |

|              | HO1L 29/48 |

|              | HO1L 21/28 |

|              | HO1L 29/58 |

|              | F          |

|              | 301B       |

|              | F          |

|              | 301R       |

|              | Z          |

請求項の数 14 (全 25 頁) 最終頁に続く

|            |                              |           |                               |

|------------|------------------------------|-----------|-------------------------------|

| (21) 出願番号  | 特願2010-200298 (P2010-200298) | (73) 特許権者 | 000004226                     |

| (22) 出願日   | 平成22年9月7日(2010.9.7)          |           | 日本電信電話株式会社                    |

| (62) 分割の表示 | 特願2005-93163 (P2005-93163)   |           | 東京都千代田区大手町二丁目3番1号             |

|            | の分割                          | (74) 代理人  | 110001243                     |

| 原出願日       | 平成17年3月28日(2005.3.28)        |           | 特許業務法人 谷・阿部特許事務所              |

| (65) 公開番号  | 特開2011-29648 (P2011-29648A)  | (72) 発明者  | 谷保 芳孝                         |

| (43) 公開日   | 平成23年2月10日(2011.2.10)        |           | 東京都千代田区大手町二丁目3番1号 日本電信電話株式会社内 |

| 審査請求日      | 平成22年9月7日(2010.9.7)          | (72) 発明者  | 嘉数 誠                          |

|            |                              |           | 東京都千代田区大手町二丁目3番1号 日本電信電話株式会社内 |

|            |                              | (72) 発明者  | 牧本 俊樹                         |

|            |                              |           | 東京都千代田区大手町二丁目3番1号 日本電信電話株式会社内 |

最終頁に続く

(54) 【発明の名称】電界効果トランジスタおよびその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半絶縁性基板上に積層されたアンドープA1N層と、

該アンドープA1N層上に積層されたSiドープn型A1N層と、

該Siドープn型A1N層上に積層されたA1<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層と、

該A1<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層上に積層されたA1Nキャップ層と、

該A1Nキャップ層上に、高濃度Siドープn型A1N層を介して形成されたドレイン電極およびソース電極と、

前記A1Nキャップ層上に形成されたゲート電極とを備え、

前記Siドープn型A1N層のSi濃度は、 $5 \times 10^{16} \text{ cm}^{-3} \sim 5 \times 10^{18} \text{ cm}^{-3}$ であり、前記A1<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層のA1組成Xは、0.9以下であり、前記A1<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層の膜厚t (nm)は、 $t < 20 + 200 \times X$ の関係を満たし、前記高濃度Siドープn型A1N層のSi濃度は、 $5 \times 10^{19} \text{ cm}^{-3}$ 以上であり、

前記ゲート電極の材料は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つが含まれ、前記A1Nキャップ層の表面とPd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つの材料が接触していることを特徴とする電界効果トランジスタ。

## 【請求項 2】

半絶縁性基板上に積層されたアンドープA1N層と、

該アンドープAlN層上に積層されたSiドープn型AlN層と、

該Siドープn型AlN層上に積層されたAl<sub>1-x</sub>Ga<sub>1-x</sub>Nチャネル層と、

該Al<sub>1-x</sub>Ga<sub>1-x</sub>Nチャネル層上に積層されたAlNキャップ層と、

該AlNキャップ層と前記Al<sub>1-x</sub>Ga<sub>1-x</sub>Nチャネル層の一部を除去した部分に、高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層を介して形成されたドレイン電極およびソース電極と、

前記AlNキャップ層上に形成されたゲート電極とを備え、

前記Siドープn型AlN層のSi濃度は、 $5 \times 10^{16} \text{ cm}^{-3}$  ~  $5 \times 10^{18} \text{ cm}^{-3}$  であり、前記Al<sub>1-x</sub>Ga<sub>1-x</sub>Nチャネル層のAl組成Xは、0.9以下であり、前記Al<sub>1-x</sub>Ga<sub>1-x</sub>Nチャネル層の膜厚t(nm)は、 $t < 20 + 200 \times X$ の関係を満たし、前記高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層のSi濃度は、 $5 \times 10^{19} \text{ cm}^{-3}$  以上であり、Al組成XとYとの関係は、Y=Xであり、

前記ゲート電極の材料は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つの材料が接触していることを特徴とする電界効果トランジスタ。

#### 【請求項3】

半絶縁性基板上に積層されたアンドープAlN層と、

該アンドープAlN層上に積層され、膜厚が1分子層以下のSi層と、

該Si層上に積層され、膜厚が15nm以下のAlNキャップ層と、

該AlNキャップ層と前記Si層と前記アンドープAlN層の一部を除去した部分に、高濃度Siドープn型AlN層を介して形成されたドレイン電極およびソース電極と、

前記AlNキャップ層上に形成されたゲート電極とを備え、

前記高濃度Siドープn型AlN層のSi濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$  以上であることを特徴とする電界効果トランジスタ。

#### 【請求項4】

半絶縁性基板上に積層されたアンドープAlN層と、

該アンドープAlN層上に積層され、膜厚が1分子層以下のSi層と、

該Si層上に積層され、膜厚が15nm以下のAlNキャップ層と、

該AlNキャップ層上に、高濃度Siドープn型AlN層を介して形成されたドレイン電極およびソース電極と、

前記AlNキャップ層上に形成されたゲート電極とを備え、

前記高濃度Siドープn型AlN層のSi濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$  以上であることを特徴とする電界効果トランジスタ。

#### 【請求項5】

前記高濃度Siドープn型AlN層と前記ドレイン電極およびソース電極との間に、高濃度Siドープn型Al<sub>z</sub>Ga<sub>1-z</sub>N組成傾斜層と、高濃度Siドープn型GaN層とを形成し、前記高濃度Siドープn型Al<sub>z</sub>Ga<sub>1-z</sub>N組成傾斜層のAl組成Zを、前記高濃度Siドープn型AlN層から前記高濃度Siドープn型GaN層に向けて1から0へと連続的に変化させ、前記高濃度Siドープn型Al<sub>z</sub>Ga<sub>1-z</sub>N組成傾斜層および前記高濃度Siドープn型GaN層のSi濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$  以上であることを特徴とする請求項1ないし4のいずれかに記載の電界効果トランジスタ。

#### 【請求項6】

前記高濃度Siドープn型AlN層と前記ドレイン電極およびソース電極との間に、高濃度Siドープn型AlN層と高濃度Siドープn型Al<sub>z</sub>Ga<sub>1-z</sub>N層とを交互に積層した超格子層を形成し、前記高濃度Siドープn型Al<sub>z</sub>Ga<sub>1-z</sub>N層のAl組成Zは、0~0.9であり、前記高濃度Siドープn型AlN層および前記高濃度Siドープn型Al<sub>z</sub>Ga<sub>1-z</sub>N層の膜厚は、5nm以下であり、記高濃度Siドープn型AlN層および前記高濃度Siドープn型Al<sub>z</sub>Ga<sub>1-z</sub>N層のSi濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$  以上であることを特徴とする請求項1ないし4のいずれかに記載の電界効果トランジ

ジスタ。

【請求項 7】

前記ドレイン電極およびソース電極は、Mo, W, Ta, Al, Tiのいずれか1つが含まれ、

前記高濃度Siドープn型AlN層、前記高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層、前記高濃度Siドープn型GaN層または前記超格子層の表面とTi, Al, W, Mo, Taのいずれか1つの材料が接触していることを特徴とする請求項6に記載の電界効果トランジスタ。

【請求項 8】

前記ゲート電極の材料は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つが含まれ、10

前記AlNキャップ層の表面とPd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つの材料が接触していることを特徴とする請求項3または4に記載の電界効果トランジスタ。

【請求項 9】

前記半絶縁性基板は、成長表面が(0001)面であるAlN基板、SiC基板、サファイア基板のいずれかであることを特徴とする請求項1ないし4のいずれかに記載の電界効果トランジスタ。

【請求項 10】

半絶縁性基板上にアンドープAlN層を積層し、Si濃度が $5 \times 10^{16} \text{ cm}^{-3} \sim 5 \times 10^{18} \text{ cm}^{-3}$ であるSiドープn型AlN層を、前記アンドープAlN層上に積層し、Al組成Xが0.9以下であり、膜厚t(nm)が $t < 20 + 200 \times X$ の関係を満たすAl<sub>X</sub>Ga<sub>1-X</sub>Nチャネル層を、前記Siドープn型AlN層上に積層し、膜厚が15nm以下のAlNキャップ層を、前記Al<sub>X</sub>Ga<sub>1-X</sub>Nチャネル層上に積層し、Al組成YがAl組成XとY-Xの関係を満たし、Si濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上である高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層を積層する第1の工程と、20

前記高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層の一部を、前記AlNキャップ層が露出するまでエッティングにより取り除く第2の工程と、

露出した前記AlNキャップ層上にゲート電極を形成する工程であって、前記ゲート電極は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つの材料が接触している、第3の工程と、30

前記高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層上にソース電極およびドレイン電極を形成する第4の工程と

を備えたことを特徴とする電界効果トランジスタの製造方法。

【請求項 11】

半絶縁性基板上にアンドープAlN層を積層し、Si濃度が $5 \times 10^{16} \text{ cm}^{-3} \sim 5 \times 10^{18} \text{ cm}^{-3}$ であるSiドープn型AlN層を、前記アンドープAlN層上に積層し、Al組成Xが0.9以下であり、膜厚t(nm)が $t < 20 + 200 \times X$ の関係を満たすAl<sub>X</sub>Ga<sub>1-X</sub>Nチャネル層を、前記Siドープn型AlN層上に積層し、膜厚が15nm以下のAlNキャップ層を、前記Al<sub>X</sub>Ga<sub>1-X</sub>Nチャネル層上に積層する第1の工程と、40

前記AlNキャップ層上に、Al組成YがAl組成XとY-Xの関係を満たし、Si濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上である高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層を、再成長により選択的に形成する第2の工程と、

前記AlNキャップ層上にゲート電極を形成する工程であって、前記ゲート電極は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つの材料が接触している、第3の工程と、

再成長により形成した前記高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層上にソース電極50

およびドレイン電極を形成する第4の工程と

を備えたことを特徴とする電界効果トランジスタの製造方法。

【請求項12】

半絶縁性基板上にアンドープAlN層を積層し、Si濃度が $5 \times 10^{16} \text{ cm}^{-3} \sim 5 \times 10^{18} \text{ cm}^{-3}$ であるSiドープn型AlN層を、前記アンドープAlN層上に積層し、Al組成Xが0.9以下であり、膜厚t(nm)が $t < 20 + 200 \times X$ の関係を満たすAl<sub>1-x</sub>Ga<sub>1-x</sub>Nチャネル層を、前記Siドープn型AlN層上に積層し、膜厚が15nm以下のAlNキャップ層を、前記Al<sub>1-x</sub>Ga<sub>1-x</sub>Nチャネル層上に積層する第1の工程と。

前記AlNキャップ層と前記Al<sub>1-x</sub>Ga<sub>1-x</sub>Nチャネル層の一部を、前記Siドープn型AlN層の近傍までエッティングにより取り除く第2の工程と。

10

露出した前記Siドープn型AlN層上に、Al組成YがAl組成XとY-Xの関係を満たし、Si濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上である高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層を、再成長により選択的に形成する第3の工程と。

前記AlNキャップ層上にゲート電極を形成する工程であって、前記ゲート電極は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つの材料が接触している、第4の工程と。

再成長により形成した前記高濃度Siドープn型Al<sub>Y</sub>Ga<sub>1-Y</sub>N層上にソース電極およびドレイン電極を形成する第5の工程と

20

を備えたことを特徴とする電界効果トランジスタの製造方法。

【請求項13】

半絶縁性基板上にアンドープAlN層を積層し、膜厚が1分子層以下のSi層を前記アンドープAlN層上に積層し、膜厚が15nm以下のAlNキャップ層を前記Si層上に積層する第1の工程と。

前記AlNキャップ層上に、Si濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上である高濃度Siドープn型AlN層を、再成長により選択的に形成する第2の工程と。

前記AlNキャップ層上にゲート電極を形成する第3の工程と。

再成長により形成した前記高濃度Siドープn型AlN層上にソース電極およびドレイン電極を形成する第4の工程と

30

を備えたことを特徴とする電界効果トランジスタの製造方法。

【請求項14】

半絶縁性基板上にアンドープAlN層を積層し、膜厚が1分子層以下のSi層を前記アンドープAlN層上に積層し、膜厚が15nm以下のAlNキャップ層を前記Si層上に積層する第1の工程と。

前記AlNキャップ層と前記Si層と前記アンドープAlN層の一部をエッティングにより取り除く第2の工程と。

露出した前記アンドープAlN層上に、Si濃度が $1 \times 10^{19} \text{ cm}^{-3}$ 以上である高濃度Siドープn型AlN層を、再成長により選択的に形成する第3の工程と。

前記AlNキャップ層上にゲート電極を形成する第4の工程と

40

再成長により形成した前記高濃度Siドープn型AlN層上にソース電極およびドレイン電極を形成する第5の工程と

を備えたことを特徴とする電界効果トランジスタの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電界効果トランジスタおよびその製造方法に関し、より詳細には、高耐圧で、高い動作電圧を有する高出力電子デバイスである電界効果トランジスタおよびその製造方法に関する。

【背景技術】

## 【0002】

ワイヤレス通信、電気自動車、電力制御などの多岐にわたる分野において、半導体電子デバイスの高出力化、高周波化、低損失化が望まれている。さらに、高温環境または放射線照射下といった厳しい環境での使用が要求されるようになってきている。このような厳しい仕様を追求する場合、半導体デバイスの動作限界は、半導体材料の物性値により制限されるため、バンドギャップエネルギーと降伏電界強度が大きい半導体材料が優位である。窒化アルミニウム（AlN）は、半導体では最大のバンドギャップエネルギーと最大の降伏電界強度を有し、金属並みの高い熱伝導率を示す。このため、AlNは、従来のSi、SiC、GaN系高出力電子デバイスに比べて、飛躍的な性能向上を実現することができる半導体材料であり、電力、通信、耐環境分野におけるエレクトロニクスの革新が期待されている。10

## 【0003】

AlNを用いた高出力電子デバイスを作製するためには、その周辺技術の開発が必要不可欠である。しかし、現在のところ、デバイスを作製するために必須である電極形成の技術すら確立されていない。一般的に、半導体材料は、バンドギャップが大きくなるに従い、良好な特性を有するオーム電極とショットキー電極の形成が困難になる。AlNは、半導体中ではバンドギャップエネルギーが最も大きいことから、良好な特性を有するオーム電極とショットキー電極を形成することは極めて困難である。このため、AlNにおいて、良好なオーム電極とショットキー電極を必要とする高出力電子デバイスを作製することは極めて困難である。20

## 【先行技術文献】

## 【非特許文献】

## 【0004】

【非特許文献1】副島成雅、他、「GaN基板を用いた縦型ショットキーダイオードの評価」、応用物理学会、平成16年秋季第65回学術講演会、予稿集1a-ZK-1、2004年

【非特許文献2】奥村元、「ワイヤードギャップ半導体高周波電子デバイス研究の現状と今後の展開」、応用物理、第73巻、第3号、第315～326頁、2004年

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

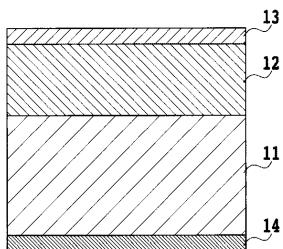

以下に、従来のGaNを用いた高出力電子デバイスの報告例について述べる。図1に、従来のGaNを用いたショットキーダイオードを示す（例えば、非特許文献1参照）。このショットキーダイオードの作製方法は、有機金属気相成長（MOCVD）法を用いて、n型GaN基板11上に、Siをドープしたn型GaN層12（厚さ5μm、キャリア濃度 $6 \times 10^{16} \text{ cm}^{-3}$ ）を成長させる。次に、n型GaN層12上にPt電極13（ショットキー電極）を形成し、基板11にAl/Au電極14（オーム電極）を形成する。

## 【0006】

このショットキーダイオードの素子耐圧は、約90Vである。この構造では、素子耐圧がGaNの絶縁破壊電界強度で決定されるので、その物性定数からくる限界以上に素子耐圧を上げることができない。従って、この構造では、素子耐圧が極めて高いショットキーダイオードを作製することができない。40

## 【0007】

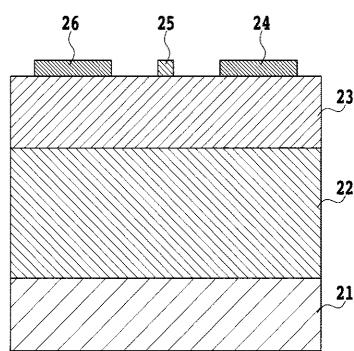

GaNを用いた高出力トランジスタとしては、GaN系ヘテロ構造電界効果トランジスタが一般的である（例えば、非特許文献2参照）。図2に、従来のGaN系ヘテロ構造電界効果トランジスタを示す。電界効果トランジスタの基本構造は、サファイアやSiCなどの基板21上に、1μm以上の厚いアンドープGaN層22を成長させ、その上にアンドープまたはSiドープAlGaNキャップ層23を成長させたシングルヘテロ構造が用いられる。AlGaNキャップ層23上にソース電極24、ゲート電極25、ドレイン電50

極 2 6 を形成する。

【 0 0 0 8 】

GaN層22とAlGaNキャップ層23との界面に二次元電子ガスが生成される。AlGaNキャップ層23をGaN層22上に成長させるため、AlGaNキャップ層23に大きな引張歪みが導入される。この引張歪みによる結晶欠陥の発生を抑制するためには、AlGaNキャップ層23のAl組成Xを、0.3以下にする必要がある。Al組成Xが0.3程度のAlGaNキャップ層23にゲート電極25を形成する構造では、ゲートリーエク電流が必然的に大きくなる。大きなゲートリーエク電流は、電界効果トランジスタの動作電圧を低下させてしまうという問題があった。

【 0 0 0 9 】

また、この構造では、高いキャリア濃度を得るために、AlGaNキャップ層23を20nm程度以上にする必要がある。しかし、AlGaNキャップ層23が厚くなると、相互コンダクタンスが低下するという問題があった。さらに、この構造では、最大動作電圧は、GaNの絶縁破壊強度で制約されるので、その物性定数からくる限界により、50Vから80V程度と低い。従って、GaN系ヘテロ構造電界効果トランジスタでは、高出力特性が極めて優れた電界効果トランジスタを作製することができない。

【 0 0 1 0 】

本発明は、このような問題に鑑みてなされたもので、その目的とするところは、高い動作電圧を有する電界効果トランジスタおよびその製造方法を提供することにある。

【課題を解決するための手段】

【 0 0 1 2 】

本発明は、このような目的を達成するために、請求項1に記載の発明は、AlN/AlGaN/AlN電界効果トランジスタであって、半絶縁性基板上に積層されたアンドープAlN層と、該アンドープAlN層上に積層されたSiドープn型AlN層と、該Siドープn型AlN層上に積層されたAl<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層と、該Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層上に積層されたAlNキャップ層と、該AlNキャップ層上に、高濃度Siドープn型AlN層を介して形成されたドレイン電極およびソース電極と、前記AlNキャップ層上に形成されたゲート電極とを備え、前記Siドープn型AlN層のSi濃度は、5×10<sup>16</sup>cm<sup>-3</sup>～5×10<sup>18</sup>cm<sup>-3</sup>であり、前記Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層のAl組成Xは、0.9以下であり、前記Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層の膜厚t(nm)は、t<20+200×Xの関係を満たし、前記高濃度Siドープn型AlN層のSi濃度は、5×10<sup>19</sup>cm<sup>-3</sup>以上であり、前記ゲート電極の材料は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つの材料が接触していることを特徴とする。

【 0 0 1 3 】

請求項2に記載の発明は、AlN/AlGaN/AlN電界効果トランジスタであって、半絶縁性基板上に積層されたアンドープAlN層と、該アンドープAlN層上に積層されたSiドープn型AlN層と、該Siドープn型AlN層上に積層されたAl<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層と、該Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層上に積層されたAlNキャップ層と、該AlNキャップ層と前記Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層の一部を除去した部分に、高濃度Siドープn型Al<sub>y</sub>Ga<sub>1-y</sub>N層を介して形成されたドレイン電極およびソース電極と、前記AlNキャップ層上に形成されたゲート電極とを備え、前記Siドープn型AlN層のSi濃度は、5×10<sup>16</sup>cm<sup>-3</sup>～5×10<sup>18</sup>cm<sup>-3</sup>であり、前記Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層のAl組成Xは、0.9以下であり、前記Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層の膜厚t(nm)は、t<20+200×Xの関係を満たし、前記高濃度Siドープn型Al<sub>y</sub>Ga<sub>1-y</sub>N層のSi濃度は、5×10<sup>19</sup>cm<sup>-3</sup>以上であり、Al組成XとYとの関係は、Y>Xであり、前記ゲート電極の材料は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つが含まれ、前記AlNキャップ層の表面とPd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Tiのいずれか1つ

10

20

30

40

50

の材料が接触していることを特徴とする。

【0014】

請求項3に記載の発明は、AlN/Si/AlN電界効果トランジスタであって、半絶縁性基板上に積層されたアンドープAlN層と、該アンドープAlN層上に積層され、膜厚が1分子層以下のSi層と、該Si層上に積層され、膜厚が15nm以下のAlNキャップ層と、該AlNキャップ層と前記Si層と前記アンドープAlN層の一部を除去した部分に、高濃度Siドープn型AlN層を介して形成されたドレイン電極およびソース電極と、前記AlNキャップ層上に形成されたゲート電極とを備え、前記高濃度Siドープn型AlN層のSi濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上であることを特徴とする。

【0015】

請求項4に記載の発明は、AlN/Si/AlN電界効果トランジスタであって、半絶縁性基板上に積層されたアンドープAlN層と、該アンドープAlN層上に積層され、膜厚が1分子層以下のSi層と、該Si層上に積層され、膜厚が15nm以下のAlNキャップ層と、該AlNキャップ層上に、高濃度Siドープn型AlN層を介して形成されたドレイン電極およびソース電極と、前記AlNキャップ層上に形成されたゲート電極とを備え、前記高濃度Siドープn型AlN層のSi濃度は、 $1 \times 10^{19} \text{ cm}^{-3}$ 以上であることを特徴とする。

【発明の効果】

【0016】

以上説明したように、本発明によれば、Si濃度を制限したSiドープn型AlN層を用いて電界効果トランジスタを作製するので、高い耐圧と高い動作電圧で動作する高出力電子デバイスを作製することが可能となる。

【図面の簡単な説明】

【0017】

【図1】従来のGaNを用いたショットキーダイオードを示す断面図である。

【図2】従来のGaN系ヘテロ構造電界効果トランジスタを示す断面図である。

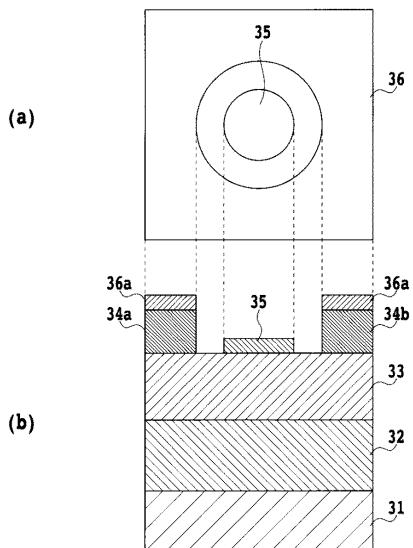

【図3】実施例1にかかるSiドープn型AlN層を用いたショットキーダイオードを示す図である。

【図4】実施例1のショットキーダイオードをエッチングにより作製する方法を示す図である。

【図5】実施例1のショットキーダイオードを再成長により作製する方法を示す図である。

【図6】実施例1のショットキーダイオードの電流-電圧特性を示す図である。

【図7】Siドープn型AlN層のSi濃度と耐圧の関係を示す図である。

【図8】高濃度Siドープn型AlN層のSi濃度と接触抵抗の関係を示す図である。

【図9】リフトオフにより除去できる高濃度Siドープn型Al<sub>1-y</sub>Ga<sub>1-y</sub>N層の膜厚とAl組成との関係を示す図である。

【図10】実施例2-1にかかるSiドープn型AlNを用いた縦型ショットキーダイオードを示す断面図である。

【図11】実施例2-2にかかるSiドープn型AlNを用いた縦型ショットキーダイオードを示す断面図である。

【図12】実施例2の縦型ショットキーダイオードの電流-電圧特性を示す図である。

【図13】実施例3にかかるSiドープn型AlN層を用いた電界効果トランジスタを示す図である。

【図14】実施例4-1にかかる電界効果トランジスタを示す断面図である。

【図15】実施例4-2にかかる電界効果トランジスタを示す断面図である。

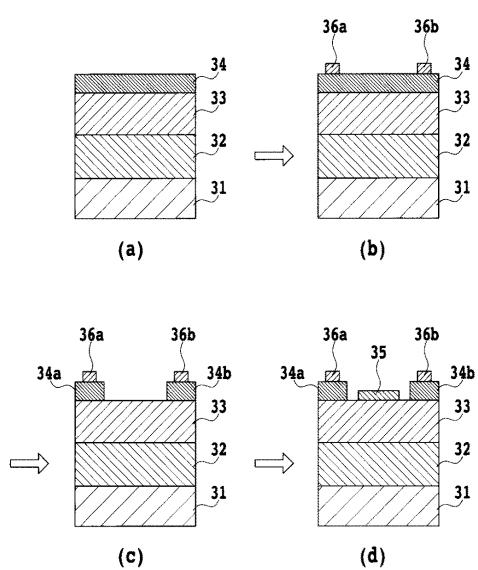

【図16】実施例4-2にかかる電界効果トランジスタを作製する方法を示す図である。

【図17】AlN/Al<sub>x</sub>Ga<sub>1-x</sub>N/AlN電界効果トランジスタのAl<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層の膜厚とAl組成Xとの関係を示す図である。

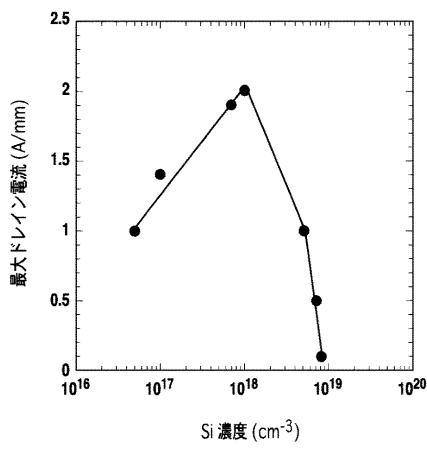

【図18】Siドープn型AlN層のSi濃度と最大ドレイン電流の関係を示す図である

10

20

30

40

50

。

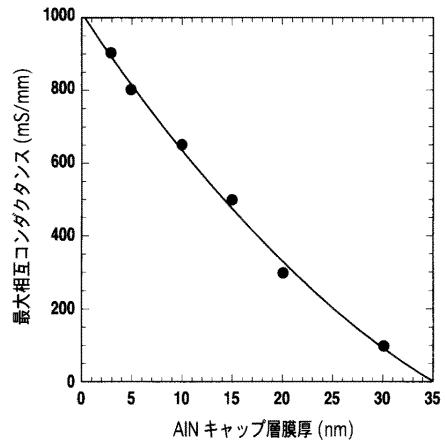

【図19】AlNキャップ層の膜厚と最大相互コンダクタンスの関係を示す図である。

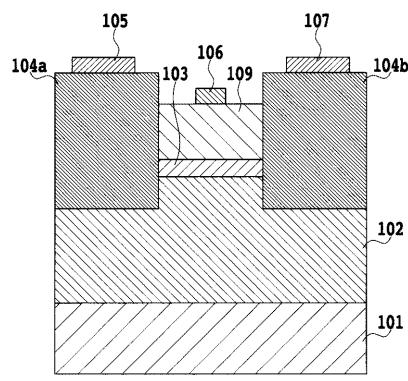

【図20】実施例5-1にかかるAlN/Si/AlN電界効果トランジスタを示す断面図である。

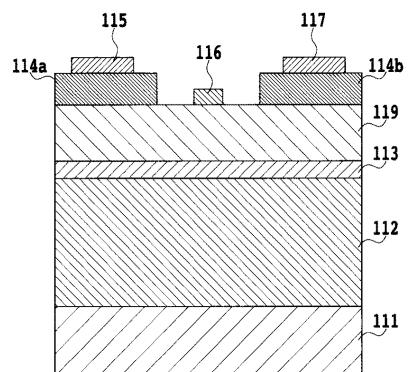

【図21】実施例5-2にかかるAlN/Si/AlN電界効果トランジスタを示す断面図である。

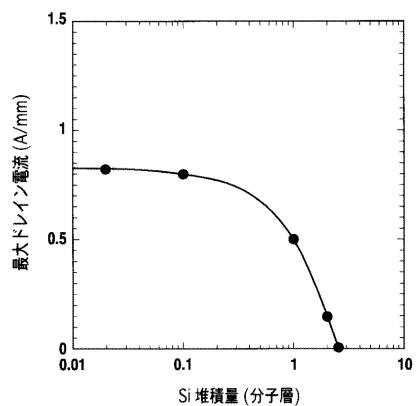

【図22】Si層の堆積量と最大ドレイン電流の関係を示す図である。

【発明を実施するための形態】

【0018】

以下、図面を参照しながら本発明の実施形態について詳細に説明する。本実施形態は、

10 Si濃度を制限したSiドープn型AlN層を、高出力電子デバイスに適用することを特徴とする。Si濃度を制限したSiドープn型AlN層を用いることにより、ショットキーダイオードの耐圧を大幅に増加させることができ、電界効果トランジスタの動作電圧を大幅に増加させることができる。

【実施例1】

【0019】

(ショットキーダイオードの作製)

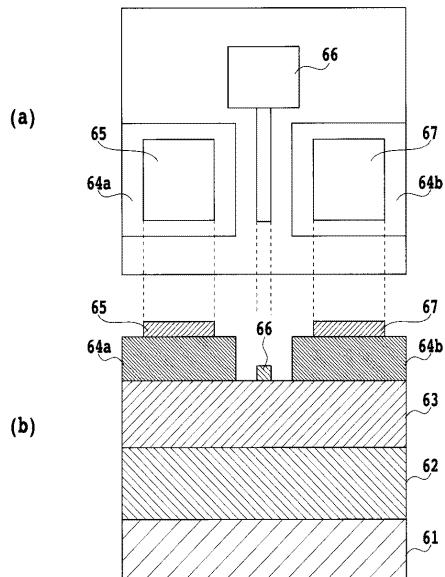

図3に、Siドープn型AlN層を用いたショットキーダイオードを示す。(a)は上面図、(b)は横断面図である。ショットキーダイオードは、半絶縁性基板であるAlN(0001)基板31上に、アンドープAlN層32、Siドープn型AlN層33が順に積層されている。さらに、Siドープn型AlN層33上に、ショットキー電極35と、高濃度Siドープn型AlN層34上に形成されたオーミック電極36とが積層されている。

【0020】

ショットキーダイオードは、MOCVD法により作製する。Al原料としてトリメチルアルミニウム(TMA)を、Ga原料としてトリメチルガリウム(TMGA)を、N原料としてアンモニア(NH<sub>3</sub>)を、Si原料としてシラン(SiH<sub>4</sub>)を用いる。成長温度は、1100である。製造方法は、(A)エッチングを用いる手法と(B)再成長を用いる手法の二通りがある。

【0021】

図4に、実施例1のショットキーダイオードを(A)エッチングにより作製する方法を示す。(図4(a))MOCVD法により、AlN(0001)基板31上に、膜厚0.5μmのアンドープAlN層32と、膜厚4μm、Si濃度 $1 \times 10^{17} \text{ cm}^{-3}$ のSiドープn型AlN層33と、膜厚10nm、Si濃度 $5 \times 10^{19} \text{ cm}^{-3}$ の高濃度Siドープn型AlN層34とをエピタキシャル成長させる。(図4(b))高濃度Siドープn型AlN層34上にオーミック電極(Ti/Al/Ti/Au)36を形成する。

【0022】

(図4(c))高濃度Siドープn型AlN層34の一部を、Siドープn型AlN層33が露出するまで、塩素ガスを用いたドライエッチング(反応性イオンエッチング)により取り除く。(図4(d))露出したSiドープn型AlN層33上にショットキー電極(Pd/Au)35を形成する。

【0023】

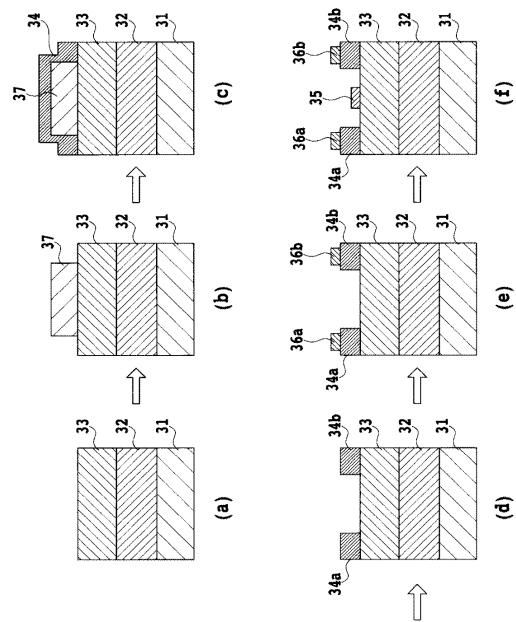

図5に、実施例1のショットキーダイオードを(B)再成長により作製する方法を示す。(図5(a))MOCVD法により、AlN(0001)基板31上に、膜厚0.5μmのアンドープAlN層32と、膜厚4μm、Si濃度 $1 \times 10^{17} \text{ cm}^{-3}$ のSiドープn型AlN層33とをエピタキシャル成長させる。(図5(b))Siドープn型AlN層33上に、SiO<sub>2</sub>マスク37をスパッタリング法により堆積する。(図5(c))MOCVD法により、膜厚10nm、Si濃度 $5 \times 10^{19} \text{ cm}^{-3}$ の高濃度Siドープn型AlN層34を再成長させる。

【0024】

10

20

30

40

50

(図5(d))リフトオフによりSiO<sub>2</sub>マスク37およびSiO<sub>2</sub>マスク37上の高濃度Siドープn型AlN層34を除去する。(図5(e))再成長により形成した高濃度Siドープn型AlN層34上にオーミック電極36を形成する。(図5(f))Siドープn型AlN層33上にショットキー電極35を形成する。

#### 【0025】

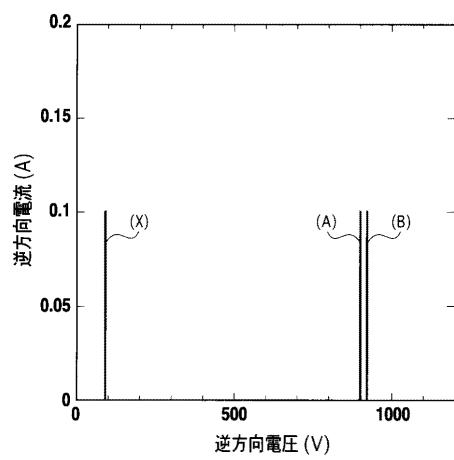

図6に、実施例1のショットキーダイオードの電流-電圧特性を示す。(A)は、エッチングにより作製したショットキーダイオードの、(B)は、再成長により作製したショットキーダイオードの、(X)は、従来のGaNを用いて作製したショットキーダイオードの電流-電圧特性である。従来のショットキーダイオードは、逆方向電圧90Vにおいて、逆方向電流が流れ始めるため、その耐圧は90V程度である。実施例1では、(A)エッチングにより作製したショットキーダイオードの耐圧は900V、(B)再成長により作製したショットキーダイオードの耐圧は920Vである。従来と比較して、ショットキーダイオードの耐圧を約10倍増加することができる。

#### 【0026】

このように高い耐圧が得られる理由は、AlNの絶縁破壊電界強度がGaNのそれよりも大きいこと、およびAlNとショットキー電極のショットキーバリアが非常に高く、リーケ電流が極めて低いためである。

#### 【0027】

一般的に、半導体表面をエッチングすると加工ダメージが導入され、これにより耐圧は減少する。しかし、実施例1では、(A)エッチングを用いる手法と(B)再成長を用いる手法とに関わらず、ショットキーダイオードはほぼ同様の高い耐圧を示す。AlNの場合に、エッチング加工を施しても、良好なショットキー特性が得られる理由は、エピタキシャル成長した結晶品質の良いAlNは、原子間結合力が強く、エッチングなどによってもダメージが導入されにくい性質を有するからである。電子デバイスの作製過程において、エッチング加工を用いることができれば、デバイス設計の自由度を高めることができる。

#### 【0028】

##### (Siドープn型AlN層のSi濃度範囲)

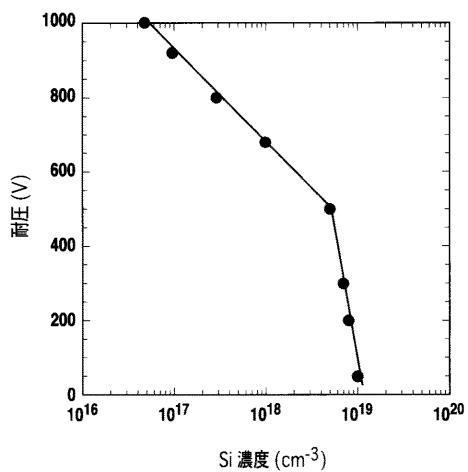

図7に、Siドープn型AlN層のSi濃度と耐圧の関係を示す。実施例1では、Siドープn型AlN層33のSi濃度を $1 \times 10^{17} \text{ cm}^{-3}$ とした。ここでは、図5に示した再成長による手法で、Si濃度を変えてショットキーダイオードを作製した。500V以上の耐圧は、Si濃度が $5 \times 10^{18} \text{ cm}^{-3}$ 以下において得られる。Si濃度が $5 \times 10^{16} \text{ cm}^{-3}$ では、耐圧は1000Vまで増加する。ただし、 $5 \times 10^{16} \text{ cm}^{-3}$ 以下では、ショットキーダイオードは動作しなくなる。これは、Si濃度が $5 \times 10^{16} \text{ cm}^{-3}$ 以下では、高い導電性を有するn型AlNが得られないからである。

#### 【0029】

一方、Si濃度が $5 \times 10^{18} \text{ cm}^{-3}$ 以上の場合、Si濃度の増加とともに、耐圧は急激に減少する。これより、Siドープn型AlNのSi濃度を $5 \times 10^{16} \text{ cm}^{-3}$ から $5 \times 10^{18} \text{ cm}^{-3}$ の範囲にすることで、高耐圧のショットキーダイオードを作製することができる。

#### 【0030】

##### (高濃度Siドープn型AlN層のSi濃度範囲)

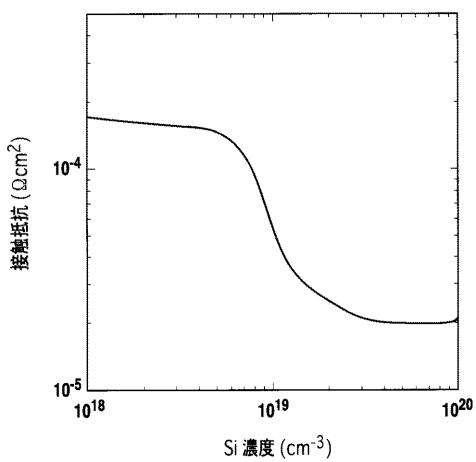

実施例1では、オーミック電極36とSiドープn型AlN層33との間に、高濃度Siドープn型AlN層34が挿入されている。高出力電子デバイスでは、電力損失を下げるためには、オーミック電極36の接触抵抗を下げる必要がある。図8に、高濃度Siドープn型AlN層のSi濃度と接触抵抗の関係を示す。

#### 【0031】

接触抵抗は、伝送線路(TLM)法を用いて求めた。Si濃度が $5 \times 10^{18} \text{ cm}^{-3}$ 以下の場合は、接触抵抗が $2 \times 10^{-4} \text{ cm}^2$ と高い。Si濃度を $1 \times 10^{19} \text{ cm}^{-3}$ 以上にすることにより、接触抵抗が $1 \times 10^{-4} \text{ cm}^2$ 以下へと大幅に低下する。さ

10

20

30

40

50

らに、Si濃度を $5 \times 10^{-9} \text{ cm}^{-3}$ 以上にすることにより、接触抵抗は $2 \times 10^{-5} \text{ cm}^2$ 以下まで低減できる。従って、オーミック電極36とSiドープn型AlN層33との間に挿入する高濃度Siドープn型AlN層34のSi濃度を、 $1 \times 10^{-9} \text{ cm}^{-3}$ 以上にすることにより、電力損失が極めて低い高出力電子デバイスを作製することができる。

#### 【0032】

(高濃度Siドープn型AlN層の膜厚)

図5を参照して述べたように、再成長によりショットキーダイオードを作製する場合、リフトオフにより $\text{SiO}_2$ マスク37および $\text{SiO}_2$ マスク上の高濃度Siドープn型AlN層34を除去する(図5(c)~(d))。従来のGaNを用いたショットキーダイオードの場合には、 $\text{SiO}_2$ マスク上にGaNが堆積しないので、容易にGaNを除去することができる。しかし、Alが含まれるAlNや $\text{Al}_y\text{Ga}_{1-y}\text{N}$ ( $0 < Y < 1$ 、以下、組成の範囲の表示は省略する)の場合には、 $\text{SiO}_2$ マスク上にAlNや $\text{Al}_y\text{Ga}_{1-y}\text{N}$ が堆積するために、それらを除去することは困難になる。

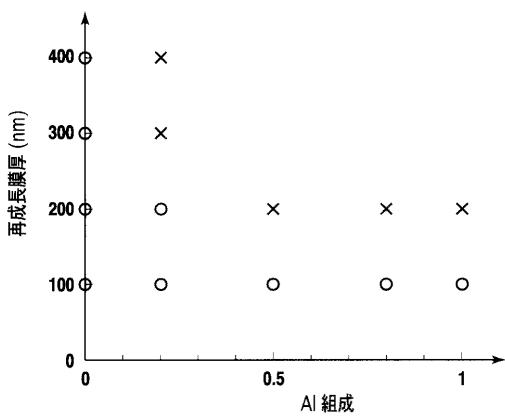

#### 【0033】

図9に、リフトオフにより除去できる高濃度Siドープn型 $\text{Al}_y\text{Ga}_{1-y}\text{N}$ 層の膜厚とAl組成との関係を示す。高濃度Siドープn型 $\text{Al}_y\text{Ga}_{1-y}\text{N}$ 層を再成長する場合に、リフトオフにより除去できる場合を○で、できなかった場合を×で示す。高濃度Siドープn型AlN(Al組成Y=1)の場合、その膜厚が100nm以下であれば、リフトオフにより除去できることがわかる。リフトオフにより除去できる高濃度Siドープn型 $\text{Al}_y\text{Ga}_{1-y}\text{N}$ 層の膜厚は、Al組成Yの減少とともに増加する。これより、再成長を用いて高濃度Siドープn型 $\text{Al}_y\text{Ga}_{1-y}\text{N}$ 層を形成する場合には、膜厚を100nm以下にする。

#### 【0034】

(基板材料)

実施例1では、絶縁性基板として半絶縁性AlN(0001)基板を用いている。基板材料と耐圧の関係について調べた結果を表1に示す。

#### 【0035】

##### 【表1】

表1 基板材料と耐圧の関係

| 基板    | 耐圧(V) |

|-------|-------|

| AlN   | 920   |

| SiC   | 800   |

| サファイア | 650   |

| GaN   | 150   |

| GaAs  | 30    |

| Si    | 50    |

#### 【0036】

図5を参照して述べたように、再成長によりショットキーダイオードを作製した。絶縁性基板として、半絶縁性AlN(0001)基板、半絶縁性SiC(0001)基板、絶縁性サファイア(0001)基板、半絶縁性GaN(0001)基板、半絶縁性GaAs(111)基板、および半絶縁性Si(111)基板を調べた。500V以上の耐圧は、半絶縁性AlN(0001)基板、半絶縁性SiC(0001)基板、および絶縁性サファイア(0001)基板においてのみ得られた。従って、Siドープn型AlNを用いた

10

20

30

40

50

高出力電子デバイスには、絶縁性基板として半絶縁性AlN(0001)基板、半絶縁性SiC(0001)基板、および絶縁性サファイア(0001)基板のいずれかを用いればよいことがわかる。

【実施例2】

【0037】

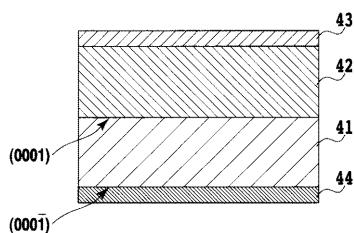

図10に、実施例2-1にかかるSiドープn型AlNを用いた縦型ショットキーダイオードを示す。(C)成長表面が(0001)面であるn型AlN基板を用いたショットキーダイオードである。作製工程は、最初に、(1)MOCVD法により、n型AlN(0001)基板41上に、膜厚4μm、Si濃度 $1 \times 10^{17} \text{ cm}^{-3}$ のSiドープn型AlN層42をエピタキシャル成長させる。(2)Siドープn型AlN層42上にショットキー電極(Pd/Au)43を形成する。(3)n型AlN(0001)基板41の裏面にオーミック電極(Ti/Al/Ti/Au)44を形成する。

10

【0038】

ここでは、n型AlN(0001)基板41を用いたが、n型SiC(0001)基板を用いても、Siドープn型AlN層42の成長表面は(0001)面となる。

【0039】

図11に、実施例2-2にかかるSiドープn型AlNを用いた縦型ショットキーダイオードを示す。(D)成長表面が(000-1)面(本明細書では、図10, 11に示したように、「1」に上付きバーの符号は、「-1」と表現する。)であるn型AlN基板を用いたショットキーダイオードである。作製工程は、最初に、(1)MOCVD法により、AlN(000-1)基板51上に、膜厚4μm、Si濃度 $1 \times 10^{17} \text{ cm}^{-3}$ のSiドープn型AlN層52と、膜厚10nm、Si濃度 $5 \times 10^{19} \text{ cm}^{-3}$ の高濃度Siドープn型AlN層53とをエピタキシャル成長させる。(2)高濃度Siドープn型AlN層53上にオーミック電極(Ti/Al/Ti/Au)54を形成する。(3)n型AlN(000-1)基板51の裏面にショットキー電極(Pd/Au)55を形成する。

20

【0040】

ここでは、n型AlN(000-1)基板51を用いたが、n型SiC(000-1)基板を用いても、Siドープn型AlN層52の成長表面は(000-1)面となる。

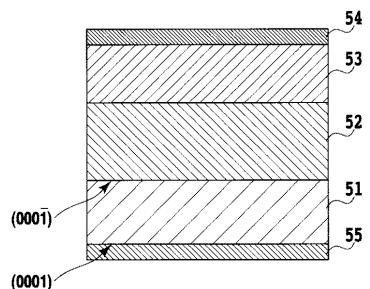

【0041】

30

図12に、実施例2の縦型ショットキーダイオードの電流-電圧特性を示す。(C)は、成長表面が(0001)面であるn型AlN基板を用いたショットキーダイオードの、(D)は、成長表面が(000-1)面であるn型AlN基板を用いたショットキーダイオードの、(X)は、従来のGaNを用いて作製したショットキーダイオードの電流-電圧特性である。従来のショットキーダイオードの耐圧は90V程度である。実施例2では、(C)成長表面が(0001)面であるn型AlN基板を用いたショットキーダイオードの耐圧は1000V、(D)成長表面が(000-1)面であるn型AlN基板を用いたショットキーダイオードの耐圧は900Vである。従来と比較して、ショットキーダイオードの耐圧を約10倍増加することができる。

40

【0042】

ここでは、n型AlN(0001)基板またはn型AlN(000-1)基板を用いたが、その代わりに、n型SiC(0001)基板またはn型SiC(000-1)基板を用いてもよい。ただし、耐圧は20%程度減少するが、従来のショットキーダイオードと比較しても、充分に高い耐圧のショットキーダイオードを作製することができる。

【実施例3】

【0043】

図13に、実施例3にかかるSiドープn型AlN層を用いた電界効果トランジスタを示す。ここでは、図4に示した(A)エッチングにより作製する方法と同様にして、電界効果トランジスタを作製する手順を示す。(1)MOCVD法により、半絶縁性基板であるAlN(0001)基板61上に、膜厚1.0μmのアンドープAlN層62と、膜厚

50

1.0  $\mu\text{m}$ 、Si濃度 $1 \times 10^{18} \text{ cm}^{-3}$ のSiドープn型AlN層63と、膜厚3nm、Si濃度 $5 \times 10^{19} \text{ cm}^{-3}$ の高濃度Siドープn型AlN層64をエピタキシャル成長する。(2)高濃度Siドープn型AlN層64上に、ドレイン電極65およびソース電極67(Ti/Al/Ti/Au)を形成する。

【0044】

(3)高濃度Siドープn型AlN層64の一部を、Siドープn型AlN層63が露出するまで、塩素ガスを用いたドライエッチング(反応性イオンエッチング)により取り除く。(4)露出したSiドープn型AlN層63上にゲート電極66(Pd/Au)を形成する。

【0045】

なお、図5に示した(B)再成長により作製する方法と同様にして、電界効果トランジスタを作製することもできる。

【0046】

実施例3にかかるSiドープn型AlN層を用いた電界効果トランジスタであって、(A)エッチングを用いる手法により作製した電界効果トランジスタと、(B)再成長を用いる手法により作製した電界効果トランジスタと、従来のGaNを用いて作成したヘテロ構造電界効果トランジスタの特性を表2に示す。

【0047】

【表2】

表2 AlN FET

10

20

|                    | 実施例3(A) | 実施例3(B) | 従来      |

|--------------------|---------|---------|---------|

| 最大動作電圧(V)          | 700     | 720     | 50~80   |

| 最大相互コンダクタンス(mS/mm) | 50      | 50      | 300~500 |

| 最大ドレイン電流(A/mm)     | 0.4     | 0.4     | 1~1.8   |

【0048】

従来の電界効果トランジスタは、最大動作電圧は80V程度である。実施例3では、(A)エッチングを用いる手法により作製した電界効果トランジスタの最大動作電圧は700V、(B)再成長を用いる手法により作製した電界効果トランジスタの最大動作電圧は720Vである。従来と比較して、電界効果トランジスタの動作電圧を約9倍も増加できる。

30

【実施例4】

【0049】

(電界効果トランジスタの作製)

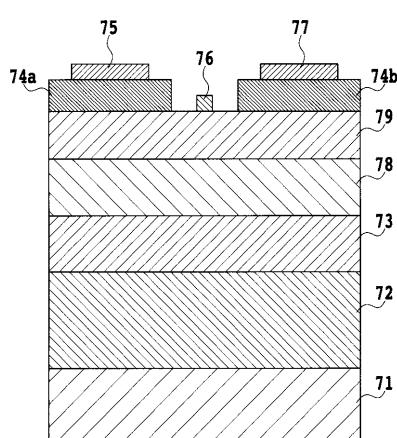

図14に、実施例4-1にかかる電界効果トランジスタを示す。ここでは、図5に示した(B)再成長により作製する方法と同様にして、(E)AlN/AlGaN/AlN電界効果トランジスタを作製する手順を示す。(1)MOCVD法により、AlN(0001)基板71上に、膜厚1 $\mu\text{m}$ のアンドープAlN層72と、膜厚0.5 $\mu\text{m}$ 、Si濃度 $1 \times 10^{18} \text{ cm}^{-3}$ のSiドープn型AlN層73と、Al組成X=0.8、膜厚30nmのAl<sub>1-X</sub>Ga<sub>1-X</sub>Nチャネル層78と、膜厚5nmのAlNキャップ層79をエピタキシャル成長させる。(2)SiO<sub>2</sub>マスクをスパッタリング法により堆積する。(3)MOCVD法により、膜厚40nm、Si濃度 $5 \times 10^{19} \text{ cm}^{-3}$ の高濃度Siドープn型AlN層74を再成長させる。

40

【0050】

(4)リフトオフによりSiO<sub>2</sub>マスクおよびSiO<sub>2</sub>マスク上の高濃度Siドープn型AlN層74を除去する。(5)再成長により形成した高濃度Siドープn型AlN層74上に、ドレイン電極75およびソース電極77(Ti/Al/Ti/Au)を形成する。(6)AlNキャップ層79上にゲート電極76(Pd/Au)を形成する。

50

## 【0051】

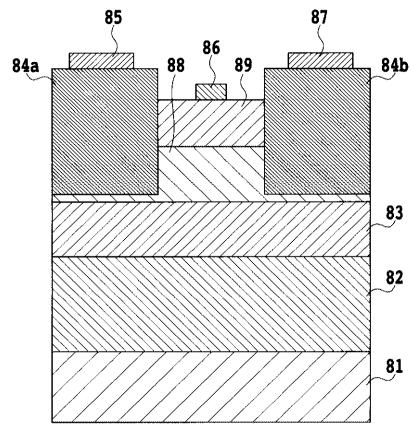

図15に、実施例4-2にかかる電界効果トランジスタを示す。(F)エッチングと再成長によりAlN/AlGaN/AlN電界効果トランジスタを作製する。電界効果トランジスタは、AlN(0001)基板81上に、アンドープAlN層82、Siドープn型AlN層83が順に積層されている。さらに、Siドープn型AlN層83上に、Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層88とAlNキャップ層89が積層されている。AlNキャップ層89とAl<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層88の一部を除去した部分に、高濃度Siドープn型Al<sub>y</sub>Ga<sub>1-y</sub>N層84が形成され、高濃度Siドープn型Al<sub>y</sub>Ga<sub>1-y</sub>N層84上にドレイン電極85およびソース電極87(Ti/Al/Ti/Au)が形成されている。AlNキャップ層89の残された部分には、ゲート電極86(Pd/Au)が形成されている。10

## 【0052】

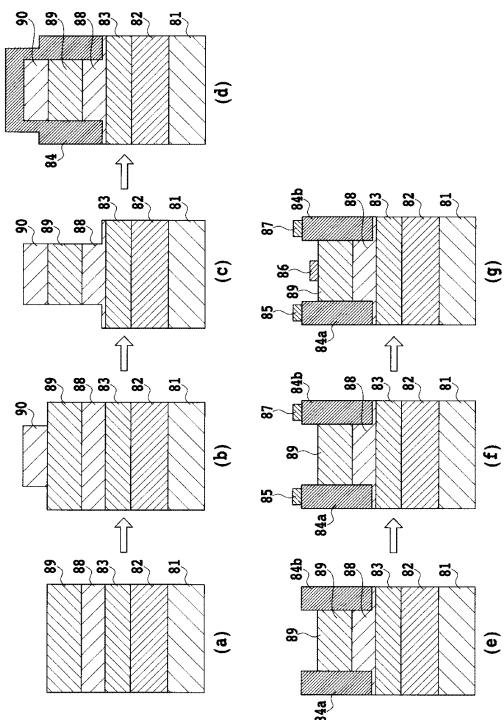

図16に、実施例4-2にかかる電界効果トランジスタを作製する方法を示す。(図16(a))MOCVD法により、AlN(0001)基板81上に、膜厚1μmのアンドープAlN層82と、膜厚0.5μm、Si濃度 $1 \times 10^{18} \text{ cm}^{-3}$ のSiドープn型AlN層83と、Al組成X=0.8、膜厚30nmのAl<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層88と、膜厚5nmのAlNキャップ層89とをエピタキシャル成長させる。(図16(b))SiO<sub>2</sub>マスク90をスパッタリング法により堆積する。(図16(c))AlNキャップ層89とAl<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層88の一部を、Al<sub>x</sub>Ga<sub>1-x</sub>Nチャネル層88が露出するまで、塩素ガスを用いたドライエッチング(反応性イオンエッチング)により取り除く。20

## 【0053】

(図16(d))MOCVD法により、Al組成Y=0.75、膜厚40nm、Si濃度 $5 \times 10^{19} \text{ cm}^{-3}$ の高濃度Siドープn型Al<sub>y</sub>Ga<sub>1-y</sub>N層84を再成長させる。(図16(e))リフトオフによりSiO<sub>2</sub>マスク90およびSiO<sub>2</sub>マスク90上の高濃度Siドープn型Al<sub>y</sub>Ga<sub>1-y</sub>N層84を除去する。(図16(f))再成長により形成した高濃度Siドープn型Al<sub>y</sub>Ga<sub>1-y</sub>N層84上に、ドレイン電極85とソース電極87とを形成する。(図16(g))AlNキャップ層89上にゲート電極86を形成する。30

## 【0054】

なお、図5に示した(B)再成長により作製する方法と同様にして、電界効果トランジスタを作製することもできる。

## 【0055】

(E)再成長により作製したAlN/AlGaN/AlN電界効果トランジスタと、(F)エッチングと再成長により作製したAlN/AlGaN/AlN電界効果トランジスタと、従来のGaNを用いて作成したヘテロ構造電界効果トランジスタの特性を表3に示す。

## 【0056】

## 【表3】

表3 AlN/AlGaN/AlN FET

|                    | 実施例4(E) | 実施例4(F) | 従来      |

|--------------------|---------|---------|---------|

| 最大動作電圧(V)          | 600     | 600     | 50~80   |

| 最大相互コンダクタンス(mS/mm) | 800     | 820     | 300~500 |

| 最大ドレイン電流(A/mm)     | 1.9     | 2       | 1~1.8   |

## 【0057】

従来の電界効果トランジスタは、最大動作電圧は80V程度である。実施例4では、(50

E) 再成長により作製した電界効果トランジスタの最大動作電圧は600V、(F)エッチングと再成長を用いて作製した電界効果トランジスタの最大動作電圧は600Vである。従来と比較して、電界効果トランジスタの動作電圧を約7.5倍増加することができる。さらに、AlN/Al<sub>1-x</sub>Ga<sub>x</sub>N/AlN電界効果トランジスタの最大相互コンタクタンスは、800mS/mm、最大ドレイン電流は2A/mm以上と非常に高い。これより、Al<sub>1-x</sub>Ga<sub>x</sub>Nチャネル層を、AlNキャップ層とSiドープn型AlN層とで挟むことにより、高出力特性が極めて優れた電界効果トランジスタを作製することができる。

## 【0058】

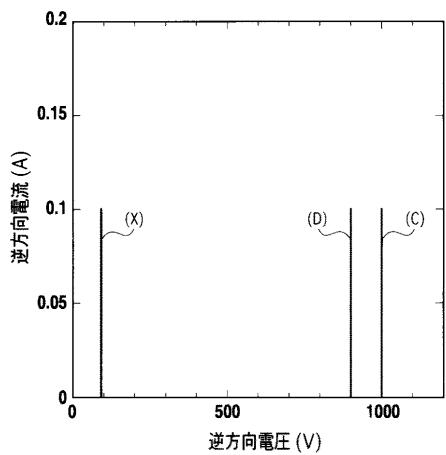

## (チャネル膜厚とAl組成)

図17に、AlN/Al<sub>1-x</sub>Ga<sub>x</sub>N/AlN電界効果トランジスタのAl<sub>1-x</sub>Ga<sub>x</sub>Nチャネル層の膜厚とAl組成Xとの関係を示す。実施例4では、Al<sub>1-x</sub>Ga<sub>x</sub>Nチャネル層78, 88のAl組成Xを0.8および膜厚を30nmとした。最大動作電圧が100V以上、最大相互コンタクタンスが500mS/mm以上、最大ドレイン電流が1A/mm以上と高出力特性が優れた電界効果トランジスタが得られる条件を○、特性が劣化する条件を×で示す。

## 【0059】

Al<sub>1-x</sub>Ga<sub>x</sub>Nチャネル層78, 88のAl組成Xが0.9を超えると、いかなる膜厚においても優れた特性は得られない。Al組成Xが0.9では膜厚を200nm以下、Al組成Xが0.7では膜厚を150nm以下、Al組成Xが0.5では膜厚を100nm以下、Al組成Xが0.2では膜厚を50nm以下、Al組成Xが0では膜厚を20nm以下においてのみ優れた特性が得られる。Al<sub>1-x</sub>Ga<sub>x</sub>Nチャネル層78, 88の膜厚をt(nm)とすると、Al組成Xが0.9以下において、

$$t < 20 + 200 \times X,$$

の条件下においてのみ、高出力特性が優れた電界効果トランジスタが得られる。

## 【0060】

また、高濃度Siドープn型Al<sub>1-y</sub>Ga<sub>y</sub>N層84のAl組成Yとの関係では、YXとするのがよい。ゲート電極86とソース電極87の接触抵抗を低減することができ、素子抵抗の低減により、電力損失が極めて低い高出力電子デバイスを作製することができる。

## 【0061】

## (Si濃度とドレイン電流)

図18に、Siドープn型AlN層のSi濃度と最大ドレイン電流の関係を示す。実施例4では、Siドープn型AlN層73, 83のSi濃度を $1 \times 10^{18} \text{ cm}^{-3}$ とした。1A/mm以上の最大ドレイン電流は、Si濃度が $5 \times 10^{16} \text{ cm}^{-3}$ から $5 \times 10^{18} \text{ cm}^{-3}$ の範囲においてのみ得られる。ただし、 $5 \times 10^{16} \text{ cm}^{-3}$ 以下では、電界効果トランジスタは動作しなくなる。これは、Si濃度が $5 \times 10^{16} \text{ cm}^{-3}$ 以下では、高い導電性を有するn型AlNが得られないからである。従って、Siドープn型AlN層73, 83のSi濃度を、 $5 \times 10^{16} \text{ cm}^{-3}$ から $5 \times 10^{18} \text{ cm}^{-3}$ の範囲にすることで、最大ドレイン電流が高い電界効果トランジスタを作製することができる。

## 【0062】

## (キャップ膜厚とgm)

図19に、AlNキャップ層の膜厚と最大相互コンダクタンスの関係を示す。実施例4では、AlNキャップ層79, 89の膜厚を5nmとした。500mS/mm以上の最大相互コンダクタンスは、AlNキャップ層79, 89の膜厚が15nm以下においてのみ得られる。膜厚を3nmにおいては、最大相互コンダクタンスは900mS/mmまで増加する。MOCVD法によりAlNキャップ層79, 89を成長させるため、AlNキャップ層79, 89の膜厚は0.5nmの精度で制御できる。従って、AlNキャップ層の膜厚を15nm以下にすることで、最大相互コンダクタンスが高い電界効果トランジスタを作製することができる。

## 【実施例5】

10

20

30

40

50

## 【0063】

(電界効果トランジスタの作製)

図20に、実施例5-1にかかるAlN/Si/AlN電界効果トランジスタを示す。

(G)エッティングと再成長により作製したAlN/Si/AlN電界効果トランジスタの構造を示す。ここでは、図16に示した実施例4-2の手順と同様にして、電界効果トランジスタを作製する手順を示す。(1)MOCVD法により、AlN(0001)基板101上に、膜厚1μmのアンドープAlN層102と、0.1分子層のSi層103と、膜厚8nmのAlNキャップ層109とをエピタキシャル成長させる。(2)SiO<sub>2</sub>マスクをスパッタリング法により堆積する。(3)AlNキャップ層109とSi層103の一部をアンドープAlN層102が露出するまで、塩素ガスを用いたドライエッティング(反応性イオンエッティング)により取り除く。

## 【0064】

(4)MOCVD法により、膜厚40nm、Si濃度 $5 \times 10^{19}$ cm<sup>-3</sup>の高濃度Siドープn型AlN層104を再成長させる。(5)リフトオフによりSiO<sub>2</sub>マスクを除去する。(6)再成長により形成した高濃度Siドープn型AlN層104上に、ドレイン電極105とソース電極107(Ti/Al/Ti/Au)とを形成する。(7)AlNキャップ層109上にゲート電極106(Pd/Au)を形成する。

## 【0065】

図21に、実施例5-2にかかるAlN/Si/AlN電界効果トランジスタを示す。

(H)再成長により作製したAlN/Si/AlN電界効果トランジスタの構造を示す。ここでは、図5に示した実施例1の手順と同様にして、電界効果トランジスタを作製する手順を示す。(1)MOCVD法により、AlN(0001)基板111上に、膜厚1μmのアンドープAlN層112と、0.1分子層のSi層113と、膜厚8nmのAlNキャップ層119とをエピタキシャル成長させる。(2)SiO<sub>2</sub>マスクをスパッタリング法により堆積する。(3)MOCVD法により、膜厚40nm、Si濃度 $5 \times 10^{19}$ cm<sup>-3</sup>の高濃度Siドープn型AlN層114を再成長する。

## 【0066】

(4)リフトオフによりSiO<sub>2</sub>マスクおよびSiO<sub>2</sub>マスク上の高濃度Siドープn型AlN層114を除去する。(5)再成長により形成した高濃度Siドープn型AlN層114上に、ドレイン電極115およびソース電極117(Ti/Al/Ti/Au)を形成する。(6)AlNキャップ層119上にゲート電極116(Pd/Au)を形成する。

## 【0067】

(G)エッティングと再成長により作製したAlN/Si/AlN電界効果トランジスタと、(H)再成長により作製したAlN/Si/AlN電界効果トランジスタと、従来のGaNを用いて作成したヘテロ構造電界効果トランジスタの特性を表4に示す。

## 【0068】

## 【表4】

表4 AlN/Si/AlN FET

|                    | 実施例5(G) | 実施例5(H) | 従来      |

|--------------------|---------|---------|---------|

| 最大動作電圧(V)          | 560     | 550     | 50~80   |

| 最大相互コンダクタンス(mS/mm) | 210     | 200     | 300~500 |

| 最大ドレイン電流(A/mm)     | 0.8     | 0.6     | 1~1.8   |

## 【0069】

従来の電界効果トランジスタは、最大動作電圧は80V程度である。実施例5では、(G)エッティングと再成長により作製したAlN/Si/AlN電界効果トランジスタの最

10

20

30

40

40

50

大動作電圧は 560V、(H)再成長により作製した AlN/Si/AlN 電界効果トランジスタの最大動作電圧は 550V である。従来と比較して、電界効果トランジスタの動作電圧を約 7 倍も増加することができる。

【0070】

(Si の膜厚)

図 22 に、Si 層の堆積量と最大ドレイン電流の関係を示す。前述のように、実施例 5 では、Si 層 103, 113 の堆積量を 0.1 分子層とした。0.5 A/mm 以上の最大ドレイン電流は、Si 層 103, 113 の堆積量が 1 分子層以下においてのみ得られる。ただし、Si 層を挿入しない場合には、電界効果トランジスタは動作しなくなる。従って、Si 層 103, 113 の堆積量を 1 分子層以下にすることで、最大ドレイン電流が高い電界効果トランジスタを作製することができる。

10

【実施例 6】

【0071】

上述したように、ショットキーダイオードのショットキー電極、電界効果トランジスタのゲート電極には、Pd/Au を用いた。これら電極には高い耐圧を有するショットキー特性が求められる。これら電極に用いる材料と耐圧の関係を調べた結果を表 5 に示す。

【0072】

【表 5】

表 5 金属材料と耐圧の関係

20

| 金属 | 耐圧 (V) |

|----|--------|

| Pd | 920    |

| Pt | 900    |

| Ni | 880    |

| Au | 850    |

| Mo | 750    |

| W  | 750    |

| Ta | 750    |

| Nb | 550    |

| Al | 520    |

| Ti | 500    |

| Mg | 200    |

| In | 100    |

30

【0073】

図 3 に示した実施例 1 のショットキーダイオードを作製して、耐圧の測定を行った。ショットキー電極に用いる金属材料として、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Ti, Mg, In を調べた。500V 以上の高い耐圧は、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Ti でのみ得られる。また、これらの電極の上に別の電極を積層した場合でも、Si ドープ n 型 AlN 層または AlN キャップ層の表面と Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Ti のいずれか最低 1 つが接触していれば、高い耐圧が得られる。

【実施例 7】

40

50

## 【0074】

(電極を形成する構造)

上述したように、ショットキーダイオードのオーミック電極、電界効果トランジスタのソース電極およびドレイン電極は、高濃度 Si ドープ n 型 AlN 層上に形成した。これらの電極には、低い接触抵抗を有するオーミック特性が求められる。オーミック電極を形成する構造とオーミック電極の接触抵抗の関係を調べた。接触抵抗は、伝送線路 (TLM) 法を用いて求めた。作製した構造は、次の 4 つである。

## 【0075】

(A) AlN (0001) 基板上にアンドープ AlN 層 (膜厚 0.5 μm)、Si ドープ n 型 AlN 層 (膜厚 4 μm、Si 濃度  $1 \times 10^{17} \text{ cm}^{-3}$ ) をエピタキシャル成長した構造。ここでは、高濃度 Si ドープ n 型 AlN 層を用いていない。10

(B) AlN (0001) 基板上にアンドープ AlN 層 (膜厚 0.5 μm)、Si ドープ n 型 AlN 層 (膜厚 4 μm、Si 濃度  $1 \times 10^{17} \text{ cm}^{-3}$ )、高濃度 Si ドープ n 型 AlN 層 (膜厚 10 nm、Si 濃度  $5 \times 10^{19} \text{ cm}^{-3}$ ) をエピタキシャル成長した構造。

(C) AlN (0001) 基板上にアンドープ AlN 層 (膜厚 0.5 μm)、Si ドープ n 型 AlN 層 (膜厚 4 μm、Si 濃度  $1 \times 10^{17} \text{ cm}^{-3}$ )、高濃度 Si ドープ n 型 AlN 層 (膜厚 3 nm、Si 濃度  $5 \times 10^{19} \text{ cm}^{-3}$ )、高濃度 Si ドープ n 型 Al<sub>z</sub> Ga<sub>1-z</sub> N 組成傾斜層 (Al 組成 z は 1 から 0 へと連続的に変化、膜厚 3 nm、Si 濃度  $5 \times 10^{19} \text{ cm}^{-3}$ )、高濃度 Si ドープ n 型 GaN 層 (膜厚 3 nm、Si 濃度  $5 \times 10^{19} \text{ cm}^{-3}$ ) をエピタキシャル成長した構造。20

(D) AlN (0001) 基板上にアンドープ AlN 層 (膜厚 0.5 μm)、Si ドープ n 型 AlN 層 (膜厚 4 μm、Si 濃度  $1 \times 10^{17} \text{ cm}^{-3}$ )、高濃度 Si ドープ n 型 AlN 層 (膜厚 3 nm、Si 濃度  $5 \times 10^{19} \text{ cm}^{-3}$ )、高濃度 Si ドープ n 型 AlN 層 (膜厚 3 nm、Si 濃度  $5 \times 10^{19} \text{ cm}^{-3}$ ) と高濃度 Si ドープ n 型 Al<sub>z</sub> Ga<sub>1-z</sub> N 層 (膜厚 3 nm、Al 組成 z = 0.2、Si 濃度  $5 \times 10^{19} \text{ cm}^{-3}$ ) とを交互に積層した超格子層 (5 周期) をエピタキシャル成長した構造。

## 【0076】

(A) から (D) の構造で得られた、オーミック電極の接触抵抗を表 6 に示す。

## 【0077】

【表 6】

表 6 オーミック電極の構造と接触抵抗

|                          | 接触抵抗 ( $\Omega \text{cm}^2$ ) |

|--------------------------|-------------------------------|

| (A) なし                   | $1 \times 10^{-2}$            |

| (B) 高濃度 Si ドープ n 型 AlN 層 | $2 \times 10^{-5}$            |

| (C) 高濃度 Si ドープ組成傾斜層      | $1 \times 10^{-5}$            |

| (D) 高濃度 Si ドープ超格子層       | $6 \times 10^{-6}$            |

## 【0078】

接触抵抗が低いほど、高周波での動作が可能であり、また損失を低減できる。(A) と (B) とを比較すると、Si ドープ n 型 AlN 層とオーミック電極の間に高濃度 Si ドープ AlN 層を挿入することにより、接触抵抗を 500 分の 1 以下に、大幅に低下できることがわかる。従って、高濃度 Si ドープ AlN 層を用いる構造により、高出力電子デバイスの高周波化と低損失化とを図ることができる。

## 【0079】

50

30

40

50

(B) と (C) とを比較すると、高濃度 Si ドープ n 型 Al N 層上に、さらに高濃度 Si ドープ n 型 Al<sub>z</sub> Ga<sub>1-z</sub> N 組成傾斜層、高濃度 Si ドープ n 型 Ga N 層を挿入することにより、接触抵抗を低下できることがわかる。(B) と (D) とを比較すると、高濃度 Si ドープ n 型 Al N 層上に、高濃度ドープ Al N / Al<sub>z</sub> Ga<sub>1-z</sub> N 超格子層を挿入することで、接触抵抗を低下できることがわかる。

## 【0080】

## (電極の種類)

上述したように、ショットキーダイオードのオーミック電極、電界効果トランジスタのソース電極およびドレイン電極には、Ti / Al / Ti / Au を用いた。これら電極には低い接触抵抗が求められる。これら電極に用いる材料と接触抵抗の関係を調べた結果を表 7 に示す。

## 【0081】

## 【表 7】

表 7 金属材料と接触抵抗の関係

| 金属 | 接触抵抗 ( $\Omega \text{cm}^2$ ) |

|----|-------------------------------|

| Pd | $8 \times 10^{-3}$            |

| Pt | $8 \times 10^{-3}$            |

| Ni | $1 \times 10^{-4}$            |

| Au | $1 \times 10^{-4}$            |

| Mo | $4 \times 10^{-5}$            |

| W  | $4 \times 10^{-5}$            |

| Ta | $4 \times 10^{-5}$            |

| Nb | $5 \times 10^{-4}$            |

| Al | $2.5 \times 10^{-5}$          |

| Ti | $2 \times 10^{-5}$            |

| Mg | $8 \times 10^{-3}$            |

| In | $2 \times 10^{-4}$            |

## 【0082】

上述した実施例 7 の (B) の構造を作製し、TLM 法により接触抵抗を測定した。これら電極に用いる金属材料として、Pd, Pt, Ni, Au, Mo, W, Ta, Nb, Al, Ti, Mg, In を調べた。 $10^{-5} \text{ cm}^2$  台の極めて低い接触抵抗は、Mo, W, Ta, Al, Ti でのみ得られる。また、これらの金属の上に別の金属を積層した場合でも、同様に低い接触抵抗が得られる。

## 【符号の説明】

## 【0083】

1 1 n 型 Ga N 基板

1 2 Si ドープ n 型 Ga N 層

1 3, 3 5, 4 3, 5 4 ショットキーディオード

1 4, 3 6, 4 4, 5 5 オーミック電極

10

20

30

40

50

2 1 基板

2 2 アンドープ G a N 層

2 3 S i ドープ A 1 G a N キャップ層

2 4 , 6 7 , 7 7 , 8 7 , 1 0 7 , 1 1 7 ソース電極

2 5 , 6 6 , 7 6 , 8 6 , 1 0 6 , 1 1 6 ゲート電極

2 6 , 6 5 , 7 5 , 8 5 , 1 0 5 , 1 1 5 ドレイン電極

3 1 , 4 1 , 6 1 , 7 1 , 8 1 , 1 0 1 , 1 1 1 A 1 N ( 0 0 0 1 ) 基板

3 2 , 6 2 , 7 2 , 8 2 , 1 0 2 , 1 1 2 アンドープ A 1 N 層

3 3 , 4 2 , 5 2 , 6 3 , 7 3 , 8 3 S i ドープ n 型 A 1 N 層

3 4 , 5 3 , 6 4 , 7 4 , 8 4 , 1 0 4 , 1 1 4 高濃度 S i ドープ n 型 A 1 N 層 10

3 7 , 9 0 S i O <sub>2</sub> マスク

5 1 A 1 N ( 0 0 0 - 1 ) 基板

7 8 , 8 8 A 1 <sub>x</sub> G a <sub>1 - x</sub> N チャネル層

7 9 , 8 9 , 1 0 9 , 1 1 9 A 1 N キャップ層

1 0 3 , 1 1 3 S i 層

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

---

フロントページの続き

|                         |              |   |

|-------------------------|--------------|---|

| (51)Int.Cl.             | F I          |   |

| H 01 L 29/423 (2006.01) | H 01 L 29/80 | H |

| H 01 L 29/778 (2006.01) | H 01 L 29/80 | M |

審査官 儀同 孝信

(56)参考文献 特開2003-273398 (JP, A)

特開平10-223652 (JP, A)

特許第2663641 (JP, B2)

特開平07-283237 (JP, A)

特開2000-277534 (JP, A)

特開2003-243423 (JP, A)

特開2001-326232 (JP, A)

特開2000-138234 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 338

H 01 L 21 / 28

H 01 L 29 / 423

H 01 L 29 / 47

H 01 L 29 / 778

H 01 L 29 / 812

H 01 L 29 / 872