(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4195802号

(P4195802)

(45) 発行日 平成20年12月17日(2008.12.17)

(24) 登録日 平成20年10月3日(2008.10.3)

(51) Int.Cl.

H04N 5/335 (2006.01)

H01L 27/146 (2006.01)

F 1

H04N 5/335

H04N 5/335

H01L 27/14E

Z

A

請求項の数 17 (全 17 頁)

(21) 出願番号 特願2002-215040 (P2002-215040)

(22) 出願日 平成14年7月24日 (2002.7.24)

(65) 公開番号 特開2003-169252 (P2003-169252A)

(43) 公開日 平成15年6月13日 (2003.6.13)

審査請求日 平成17年6月2日 (2005.6.2)

(31) 優先権主張番号 特願2001-288255 (P2001-288255)

(32) 優先日 平成13年9月21日 (2001.9.21)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 598054315

イーエヌジー株式会社

福岡県北九州市若松区青葉台西6丁目2番

9号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

最終頁に続く

(54) 【発明の名称】半導体撮像素子

## (57) 【特許請求の範囲】

## 【請求項1】

イメージセンサーを構成する画素回路において、画素毎に固有の検知受光信号の読み出し増幅率を、前記画素回路が利得係数を電気的にアナログ変調できるMOSトランジスタを信号読み出し増幅に用いることによって、周辺画素を含む近傍検知受光信号の平均信号で変調することを特徴とする、半導体撮像素子。

## 【請求項2】

前記画素回路において、前記MOSトランジスタの利得係数を変調するための制御ゲートには、周辺の平均受光量信号が入力されることを特徴とする、請求項1に記載の半導体撮像素子。

10

## 【請求項3】

前記周辺の平均受光量信号は、ウェルと基板間で形成されるダイオードと、前記ウェルの形状で設定される画素間の接続抵抗によって与えられることを特徴とする、請求項2に記載の半導体撮像素子。

## 【請求項4】

各画素の受光信号を与えるフォトダイオードを、前記ウェル内に形成することを特徴とする、請求項3に記載の半導体撮像素子。

## 【請求項5】

複数の画素を備え、

各前記画素は、自身および自身の周辺に配置された他の複数の画素のうちの少なくとも

20

一部の画素における光量に応じて調整される信号増幅率に従って、前記自身における入射光量に応じた電気信号を生成する画像信号生成回路と、

前記自身への入射光量に応じた第1の電位を第1のノードに生成するための第1の受光検知素子と、

前記少なくとも一部の画素への入射光量に応じた第2の電位を第2のノードに生成するための第2の受光検知素子とを含み、

前記画像信号生成回路は、前記第1および第2の電位の積に応じて前記電気信号を生成する、半導体撮像素子。

**【請求項6】**

前記信号増幅率は、前記少なくとも一部の画素における平均光量に応じて設定される、10

請求項5に記載の半導体撮像素子。

**【請求項7】**

前記複数の画素のそれぞれにおける前記信号増幅率は、前記少なくとも一部の画素における平均光量が小さい領域において、前記平均光量が大きい領域よりも相対的に大きく設定される、請求項5に記載の半導体撮像素子。

**【請求項8】**

前記第1の電位は、前記自身への入射光量の増加に応じて上昇し、前記第2の電位は、前記少なくとも一部の画素への入射光量の増加に応じて下降する、請求項7に記載の半導体撮像素子。20

**【請求項9】**

前記第1の電位は、前記自身への入射光量の増加に応じて下降し、

前記第2の電位は、前記少なくとも一部の画素への入射光量の増加に応じて上昇する、請求項7に記載の半導体撮像素子。

**【請求項10】**

前記第1の受光検知素子は、前記第1のノードから第1の固定電圧へ向かう方向を順方向として、前記第1のノードおよび前記第1の固定電圧の間に接続された第1のダイオードを有し、

前記第2の受光検知素子は、第2の固定電圧から前記第2のノードへ向かう方向を順方向として、前記第2のノードおよび前記第2の固定電圧の間に接続された第2のダイオードを有し、30

前記少なくとも一部の画素において、前記第2のノード同士は抵抗成分を介して電気的に結合される、請求項7に記載の半導体撮像素子。

**【請求項11】**

前記第1の受光検知素子は、第1の固定電圧から前記第1のノードへ向かう方向を順方向として、前記第1の固定電圧および前記第1のノードの間に接続された第1のダイオードを有し、

前記第2の受光検知素子は、前記第2のノードから第2の固定電圧へ向かう方向を順方向として、前記第2のノードおよび前記第2の固定電圧の間に接続された第2のダイオードを有し、

前記少なくとも一部の画素において、前記第2のノード同士は抵抗成分を介して電気的に結合される、請求項7に記載の半導体撮像素子。40

**【請求項12】**

前記画像信号生成回路は、制御ゲートへの印加電圧に応じて利得係数をアナログ変調可能な電界効果型トランジスタを含み、

前記電界効果型トランジスタの前記制御ノードは、前記第2のノードと接続され、

前記電界効果型トランジスタは、前記利得係数に従って前記第1のノードの電位を増幅することによって前記電気信号を生成する、請求項7に記載の半導体撮像素子。

**【請求項13】**

前記半導体撮像素子は、第1導電型の基板上に生成され、

前記半導体撮像素子は、50

前記基板上に形成された、前記第1導電型とは反対導電型の第2導電型のウェル領域をさらに備え、

前記第2の受光検知素子は、前記基板および前記ウェル領域の間の接合を用いて形成されるダイオードを有する、請求項7に記載の半導体撮像素子。

【請求項14】

前記第2のノードは、前記ウェル領域に相当する、請求項1\_3に記載の半導体撮像素子。

【請求項15】

前記半導体撮像素子は、

前記ウェル領域内に形成された前記第1導電型の第1拡散領域と、

10

前記第1拡散領域内に形成された前記第2導電型の第2拡散領域とをさらに備え、

前記第1および第2拡散領域は、各前記画素ごとに独立に設けられ、

前記第1の受光検知素子は、前記第1拡散領域および前記第2拡散領域の間の接合を用いて形成されるダイオードを有する、請求項1\_3に記載の半導体撮像素子。

【請求項16】

前記第1および第2のノードの電位を所定周期で所定電位にそれぞれリセットするためのリセット回路をさらに備える、請求項7に記載の半導体撮像素子。

【請求項17】

所定周期で前記第1のノードの電位を所定電位にリセットするとともに、前記第2のノードを固定のバイアス電圧と抵抗成分を介して電気的に結合するためのリセット回路をさらに備える、請求項7に記載の半導体撮像素子。

20

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

この発明は、ヒトの視覚感知特性に近い受光感知特性を実現する半導体撮像素子に関し、より特定的には、視野内に輝度差が大きい領域が混在しても、全領域で十分なコントラストを検知することができる半導体撮像装置に関する。従って、この発明技術は、高い視覚感知能力を有した撮像装置として様々な状況下で使用される、屋外を含む監視用カメラや車載用カメラなどに利用できる。

【0002】

30

【従来の技術】

C C D (Charge-coupled device) や C M O S (complementary metal-oxide semiconductor) イメージャーなどの固体撮像素子、所謂、半導体イメージセンサー（以下、「半導体撮像素子」とも称する）は、ビデオカメラやデジタルカメラを始めとして、今や携帯電話などにも内蔵されるようになり、廉価で消費電力の少ない撮像素子として広く普及している。

【0003】

しかしながら、半導体撮像素子の感知能力は、ヒトの視覚感知と比べて、大きく劣っている。ヒトの視覚では、一視野内に、4～5桁程度の輝度分布があつても、明るい所と暗い所のコントラストを十分に検知することが可能である。この優れたコントラスト感知能力は、網膜内にある受光細胞が、その光感応特性を個々の細胞毎に調整できる機能によって実現されている。

40

【0004】

これに対して、従来の半導体撮像素子では、全ての画素が同じ受光特性であることから、視野内の明るい所と暗い所で十分なコントラストを同時に得ることが困難であった。

【0005】

【発明が解決しようとする課題】

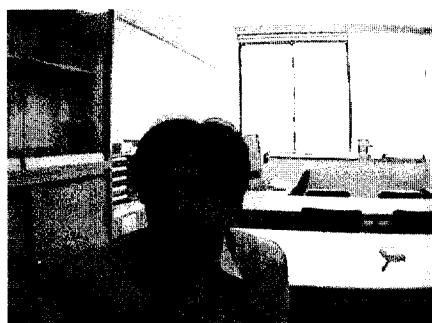

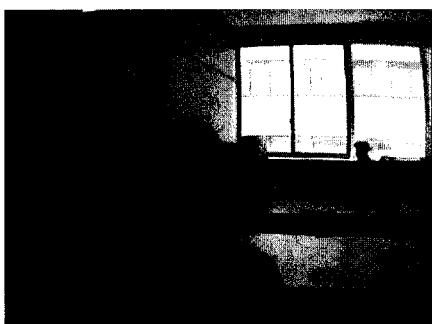

図14および図15は、従来の半導体撮像素子による撮像例を示す第1および第2の図である。

【0006】

50

図14および図15を参照して、これらの撮像例は、晴れた昼間に蛍光灯を点灯した室内から窓外を含む光景を撮影したものである。このような光景は、日常生活において、よく目にする、ありふれた状景である。このような普段の光景において、ヒトの目では、室内も窓外の光景も難無く十分なコントラストで見えることは、経験上、明白である。

#### 【0007】

しかしながら、従来の半導体撮像素子では、図14の撮像例のように、室内見えるように画素の受光感度特性を調整すると、窓の外が明るくなり過ぎて、明るい部分のコントラストを検知することができなくなる。一方、図15の撮像例のように、窓外の光景を十分なコントラストで見えるように調整すると、今度は室内が暗くなり過ぎて、暗い部分のコントラストを検知することが困難となる。このように、従来のイメージセンサーでは、視野内に明るい領域と暗い領域とが同時に混在する場合には、全領域で十分なコントラストを検知する能力が、ヒトの視覚検知と比べて大きく劣っていることが分かる。10

#### 【0008】

したがって、従来の半導体撮像素子をヒトの視覚に代わる視覚情報検知装置として用いるためには、このコントラスト感知能力の低さが、実用化する上で解決しなければならない、大きな課題の一つである。

#### 【0009】

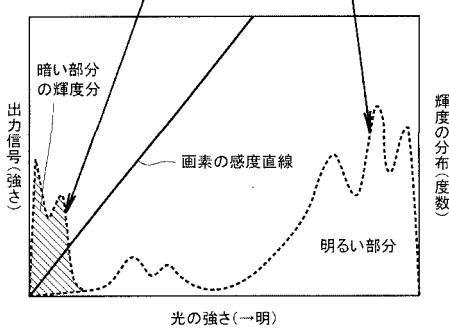

次に、図16を用いて従来の半導体撮像素子のコントラスト検知能力の低さを説明する。

#### 【0010】

一般的に、晴れた昼間の屋外の照度は、数万ルクス程度である。一方、蛍光灯を点灯した室内の照度は、太陽光が射し込まない所で約500ルクス程度で、暗い所では100ルクス以下になる。つまり、図14および15に示した撮像例では、図16内の輝度分布例で示すように、窓外の輝度分布と、室内の暗い部分（顔部分）の輝度分布は、各々の平均値で2～3桁も差があることになる。20

#### 【0011】

図14の撮像例では、室内の比較的明るい領域（500ルクス以下）において十分なコントラストを感知できるように、画素の受光感度特性が図16に示す感度直線になるように調整されている。しかし、既に述べたように、従来の半導体撮像素子では全ての画素が同じ感度特性を有しているので、このような受光感度特性で撮像すると、窓外の明るい部分は受光感度が飽和してしまい真っ白となる。一方、暗い部分においても、全体の1/5以下の振幅となり十分なコントラストを得ることができないことが分かる。このように、従来の半導体撮像素子では、我々が日常で多く遭遇する状景にすら、十分なコントラストを感知することができないことになる。30

#### 【0012】

この発明は、このような問題点を解決するためになされたものであって、この発明の目的は、一視野内の輝度分布が大きい場合であっても、明るい部分と暗い部分とを十分なコントラストで検知可能な半導体撮像素子を提供することである。

#### 【0013】

##### 【課題を解決するための手段】

この発明に従う半導体撮像素子は、イメージセンサーを構成する画素回路において、画素毎に固有の信号増幅率を調整できる機能を備えたことを特徴とする。40

#### 【0014】

好ましくは、画素回路は、画素固有の検知受光信号の読み出し増幅率を、周辺画素を含む近傍検知受光信号の平均信号で変調することを特徴とする。

#### 【0015】

さらに好ましくは、画素回路は、利得係数  $K$  を電気的にアナログ変調できるMOSトランジスタを信号読み出し増幅に用いることを特徴とする。

#### 【0016】

特にこのような構成においては、画素回路において、MOSトランジスタの利得係数  $K$  を変調するための制御ゲートには、周辺の平均受光量信号が入力される。50

**【0017】**

あるいは好ましくは、周辺の平均受光量信号は、ウェルと基板間で形成されるダイオードと、ウェルの形状で設定される画素間の接続抵抗によって与えられることを特徴とする。

**【0018】**

さらに好ましくは、各画素の受光信号を与えるフォトダイオードを、ウェル内に形成することを特徴とする。

**【0019】**

この発明の他の構成に従う半導体撮像素子は、複数の画素を備える。各画素は、自身および自身の周辺に配置された他の複数の画素のうちの少なくとも一部の画素における光量に応じて調整される信号増幅率に従って、自身における入射光量に応じた電気信号を生成する画像信号生成回路を含む。10

**【0020】**

好ましくは、信号増幅率は、少なくとも一部の画素における平均光量に応じて設定される。。

**【0021】**

また好ましくは、複数の画素のそれぞれにおける信号増幅率は、少なくとも一部の画素における平均光量が小さい領域において、平均光量が大きい領域よりも相対的に大きく設定される。

**【0022】**

あるいは好ましくは、各画素は、自身への入射光量に応じた第1の電位を第1のノードに生成するための第1の受光検知素子と、少なくとも一部の画素への入射光量に応じた第2の電位を第2のノードに生成するための第2の受光検知素子とをさらに含む。画像信号生成回路は、第1および第2の電位の積に応じて電気信号を生成する。20

**【0023】**

さらに好ましくは、第1の電位は、自身への入射光量の増加に応じて上昇し、第2の電位は、少なくとも一部の画素への入射光量の増加に応じて下降する。

**【0024】**

あるいは、さらに好ましくは、第1の電位は、自身への入射光量の増加に応じて下降し、第2の電位は、少なくとも一部の画素への入射光量の増加に応じて上昇する。

**【0025】**

また、さらに好ましくは、第1の受光検知素子は、第1のノードから第1の固定電圧へ向かう方向を順方向として、第1の固定電圧および第1のノードの間に接続された第1のダイオードを有し、第2の受光検知素子は、第2の固定電圧から第2のノードへ向かう方向を順方向として、第2のノードおよび第2の固定電圧の間に接続された第2のダイオードを有する。少なくとも一部の画素において、第2のノード同士は抵抗成分を介して電気的に結合される。30

**【0026】**

また、さらに好ましくは、第1の受光検知素子は、第1の固定電圧から第1のノードへ向かう方向を順方向として、第1の固定電圧および第1のノードの間に接続された第1のダイオードを有し、第2の受光検知素子は、第2のノードから第2の固定電圧へ向かう方向を順方向として、第2のノードおよび第2の固定電圧の間に接続された第2のダイオードを有する。少なくとも一部の画素において、第2のノード同士は抵抗成分を介して電気的に結合される。40

**【0027】**

あるいは好ましくは、画像信号生成回路は、制御ゲートへの印加電圧に応じて利得係数をアナログ変調可能な電界効果型トランジスタを含む。電界効果型トランジスタの制御ノードは、第2のノードと接続され、電界効果型トランジスタは、利得係数に従って第1のノードの電位を增幅することによって電気信号を生成する。

**【0028】**

また好ましくは、半導体撮像素子は、第1導電型の基板上に生成され、基板上に形成され50

た、第1導電型とは反対導電型の第2導電型のウェル領域をさらに備える。第2の受光検知素子は、基板およびウェル領域の間の接合を用いて形成されるダイオードを有する。

#### 【0029】

さらに好ましくは、第2のノードは、ウェル領域に相当する。

あるいは、さらに好ましくは、半導体撮像素子は、ウェル領域内に形成された第1導電型の第1拡散領域と、第1拡散領域内に形成された第2導電型の第2拡散領域とをさらに備える。第1および第2拡散領域は、各画素ごとに独立に設けられ、第1の受光検知素子は、第1拡散領域および第2拡散領域の間の接合を用いて形成されるダイオードを有する。

#### 【0030】

また好ましくは、半導体撮像素子は、第1および第2のノードの電位を所定周期で所定電位にそれぞれリセットするためのリセット回路をさらに備える。

#### 【0031】

あるいは好ましくは、半導体撮像素子は、所定周期で第1のノードの電位を所定電位にリセットするとともに、第2のノードを固定のバイアス電圧と抵抗成分を介して電気的に結合するためのリセット回路をさらに備える。

#### 【0032】

#### 【発明の実施の形態】

以下において、本発明の実施の形態を図面を参照して詳細に説明する。なお、以下の説明において、同一または相当部分については同一の参照符号を付すものとする。

#### 【0033】

#### [実施の形態1]

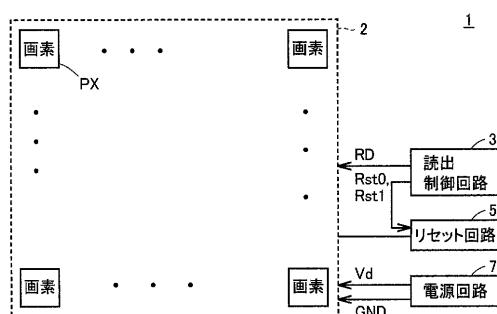

図1は、本発明の実施の形態に従う半導体撮像素子の構成を示す概略ブロック図である。

#### 【0034】

図1を参照して、本発明に従う半導体撮像素子1は、複数の画素PXが行列状に配置された画素アレイ2と、読出制御回路3と、リセット回路5と、電源回路7とを備える。

#### 【0035】

読出制御回路3は、画素アレイ2における画像データ生成タイミングを制御するための制御信号RDを生成する。リセット回路5は、各画素PXにおける受光検知素子の状態を定期的にリセットする。リセット回路5によるリセット動作タイミングは、読出制御回路3からのリセット信号Rst0, Rst1によって制御される。電源回路7は、画素アレイ2内の各画素に対して、電源電圧Vdおよび接地電圧GNDを供給する。

#### 【0036】

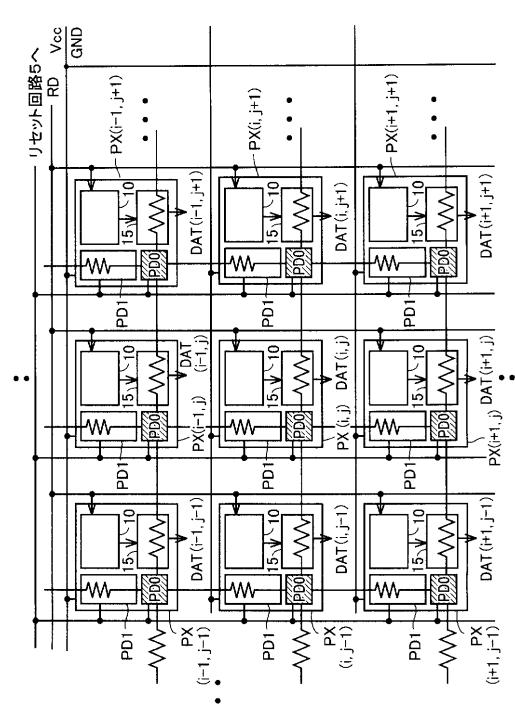

図2は、各画素の構成を説明するブロック図である。図2においては、行列状に配置された複数の画素のうちの、第i行・第j列(i, j:自然数)の画素PX(i, j)および、これに隣接する画素群が代表的に示される。

#### 【0037】

図2を参照して、各画素PXは、受光検知素子であるフォトダイオードPD0, PD1と、画素信号生成回路10と、画素データ生成回路15とを含む。

#### 【0038】

フォトダイオードPD1は、当該画素における入射光量に応じた電位を有する信号を生成する。フォトダイオードPD0は、周辺領域の複数の画素中のフォトダイオードPD0と、抵抗成分を介して電気的に結合される。これにより、各画素のフォトダイオードPD0は、当該画素の周辺領域における平均光量に対応する電位を有する信号を生成することができる。

#### 【0039】

図2の構成例においては、各画素は、隣接する4個の画素との間でフォトダイオードPD0同士が電気的に結合されている。たとえば、画素PX(i, j)は、画素PX(i, j+1), PX(i, j-1), PX(i-1, j)およびPX(i+1, j)との間で電気的に結合される。しかし、本願発明の適用は、このような構成に限定されず、各画素のフォトダイオードPD0は、周囲に配置された任意の個数の他の画素のフォトダイオード

10

20

30

40

50

P D 0 と接続する構成とすることができる。

#### 【 0 0 4 0 】

画素信号生成回路 1 0 は、フォトダイオード P D 0 および P D 1 のそれぞれの出力に応じて、制御信号 R D に応答したタイミングで、当該画素での入射光量に応じた画像信号を出力信号として生成する。画像信号は、フォトダイオード P D 0 の出力、すなわち当該画素の周辺領域における平均光量に基づいて自動調整された受光感度特性（信号増幅率）に従って、フォトダイオード P D 1 の出力、すなわち当該画素での光量に応じた強度を有する。

#### 【 0 0 4 1 】

したがって、各画素の受光感度特性は、当該画素の周辺領域における平均光量に基づいて自動調整されることになる。具体的には、各画素において、周辺の平均光量に反比例して、その画素の受光感度（信号増幅率）を大きくするように設定すればよい。すなわち、各画素は、暗い領域においては受光感度を相対的に大きく設定し、明るい領域においては受光感度を相対的に小さく設定するような自動調整機能を有する。

10

#### 【 0 0 4 2 】

画素データ生成回路 1 5 は、画素信号生成回路 1 0 からの出力信号（画素信号）をアナログ／デジタル変換して画像データ D A T を生成し、かつ生成された画像データを一時的に保持する。画像データ生成回路 1 5 に保持された画像データ D A T は、図示しない走査回路を用いて、画素単位、画素の行単位あるいは列単位、もしくは画素アレイ一括で、任意の範囲ごとに半導体撮像素子外部から読出しができる。なお、図示しない各画素においても、その内部構成および、周囲の画素との間における接続関係は、同様である。

20

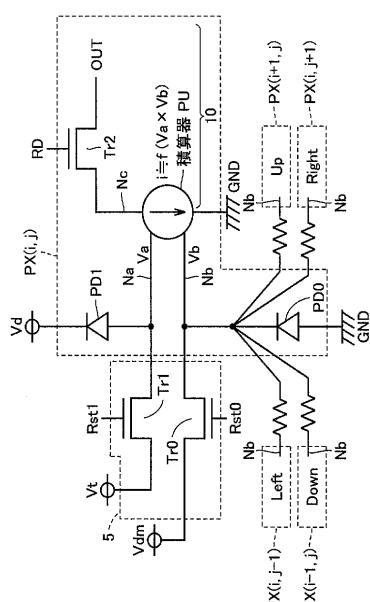

#### 【 0 0 4 3 】

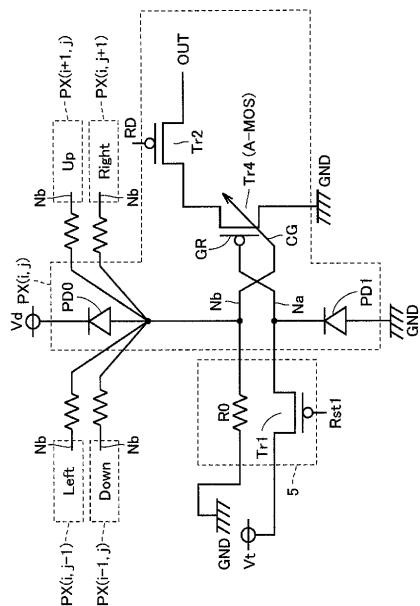

図 3 は、各画素の構成を詳細に示す回路図である。

図 3 を参照して、画素への入射光量に応じた電位 V a を与えるフォトダイオード P D 1 と、周辺の平均光量に応じた電位 V b を与えるフォトダイオード P D 0 とを有し、それぞれのフォトダイオードによって与えられた電位 V a および V b の積算結果を画素信号として読み出す回路構成となっている。

#### 【 0 0 4 4 】

フォトダイオード P D 1 は、ノード N a から電源電圧 V d へ向かう方向を順方向として、ノード N a および電源電圧 V d の間に接続される。フォトダイオード P D 0 は、接地電圧 G N D からノード N b へ向かう方向を順方向として、ノード N b および接地電圧 G N D の間に接続される。

30

#### 【 0 0 4 5 】

リセット回路 5 は、ノード N a とリセット電圧 V t との間に接続されたリセット用トランジスタ T r 1 と、ノード N b とリセット電圧 V d m との間に接続されたリセット用トランジスタ T r 0 とを有する。リセット用トランジスタ T r 0 および T r 1 は、リセット信号 R s t 0 および R s t 1 にそれぞれ応答してターンオンする。

#### 【 0 0 4 6 】

リセット電圧 V t は、リセット時に、フォトダイオード P D 1 に所定の逆バイアス電圧を印加するための電圧であり、接地電圧 G N D を用いることもできる。同様に、リセット電圧 V d m は、リセット時に、フォトダイオード P D 0 に所定の逆バイアス電圧を印加するための電圧であり、電源電圧 V d を用いることもできる。これらのバイアス電圧については、たとえば図 1 に示した電源回路 7 から供給する構成とすることができる。

40

#### 【 0 0 4 7 】

したがって、リセット回路 5 によるリセット動作によって、ノード N a および N b は、所定電圧（V t, V d m）と接続される。その後、フォトダイオード P D 1 には、当該画素での光量に応じた逆方向電流が生じるので、電位 V a は、当該画素の受光量に応じて時間的に変化する。

#### 【 0 0 4 8 】

図 2 で説明したように、各画素中のノード N b は、他の画素中のノード N b と抵抗成分を

50

介して電気的に結合される。たとえば、図3の構成においては、たとえば、画素 $PX(i, j)$ 中のノード $Nb$ は、上側( $up$ )の画素 $PX(i-1, j)$ 、下側( $down$ )の画素 $PX(i+1, j)$ 、左側( $left$ )の画素 $PX(i, j-1)$ および右側( $right$ )の画素 $PX(i, j+1)$ のそれぞれの内部のノード $Nb$ と、抵抗成分を介して電気的に結合されている。

#### 【0049】

したがって、ノード $Nb$ の電位は、当該画素内のフォトダイオード $PD0$ に生じる逆方向電流のみならず、電気的に結合された他の画素内のフォトダイオード $PD0$ に生じる逆方向電流の影響を受けて時間的に変化する。このように、周辺の画素内のフォトダイオード $PD0$ 同士を抵抗成分を介して接続することによって、当該画素の周辺光量に反比例した電位 $Vb$ をノード $Nb$ に生成できる。10

#### 【0050】

画素信号生成回路10は、積算器 $PU$ と読出選択スイッチトランジスタ $Tr2$ とを有する。積算器 $PU$ は、ノード $Na$ および $Nb$ のそれぞれの電位 $Va$ および $Vb$ の積に相関する電流 $i$ を、ノード $Nc$ および接地電圧 $GND$ の間に生成する。すなわち、積算器 $PU$ の電流特性式は $i = f(Va \times Vb)$ で示され、電流 $i$ は、電位 $Va$ および $Vb$ の積にはほぼ比例する。

#### 【0051】

読出選択スイッチトランジスタ $Tr2$ は、制御信号 $RD$ の活性化タイミングにおけるノード $Nc$ の電位を画像信号 $OUT$ として出力する。20

#### 【0052】

このような構成とすることにより、ノード $Na$ の電位 $Va$ が同レベルであっても、周辺の平均光量が少ない画素、つまり暗い部分の画素においては、ノード $Nc$ の電位は、相対的に高くなり、周辺の平均光量が多い画素、つまり明るい部分の画素では、ノード $Nc$ の電位は、相対的に低くなる。したがって、各画素の受光感度を、暗い領域においては大きくし明るい領域では小さくする、画素毎の信号増幅率制御を実現している。

#### 【0053】

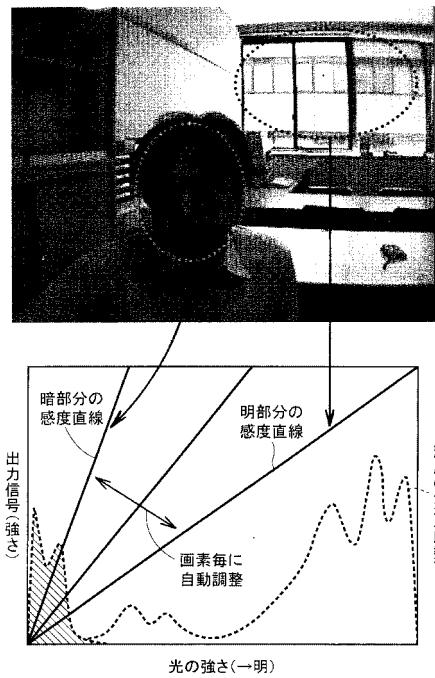

図4は、本発明に従う半導体撮像素子の画素特性を示す概念図およびその撮像例を示す図である。

#### 【0054】

図4を参照して、本発明に従う半導体撮像素子においては、受光感度特性を各画素毎に自動調整することによって、各画素毎に、周辺の平均光量に反比例してその画素における感度直線(信号増幅率)を変化させるよう(暗い所程増幅率を大きくする)、自動調整機能が実現される。さらに、このような機能を搭載した半導体撮像素子において、視野内の最も明るい部分で十分なコントラストが維持できるように全画素共通の蓄積時間(露光時間)を調整すれば、暗い部分の信号がその周辺の暗さに応じて増幅されるので、暗い部分のコントラストが増強され、画面の全領域で十分なコントラストが検知できるようになる。露光時間は、リセット信号 $Rst0, Rst1$ に応答してリセット動作が実行されてから、制御信号 $RD$ が活性化されるまでの期間に相当し、読出制御回路3によって設定される。この結果、図4に示される撮像例のように、明るい部分も暗い部分も十分なコントラストで検知できる半導体撮像素子を実現することができる。40

#### 【0055】

##### [実施の形態2]

実施の形態2においては、このような信号増幅率制御に適した、積算器 $PU$ の構成について説明する。実施の形態2においては、制御ゲートへの入力電圧に応じて利得係数 $K$ を制御することが可能なMOSトランジスタ(以下、「A-MOS(Adjustable-MOS)デバイス」とも称する)を用いて、画素毎に受光感度特性を自動調整する機能を実現する。

#### 【0056】

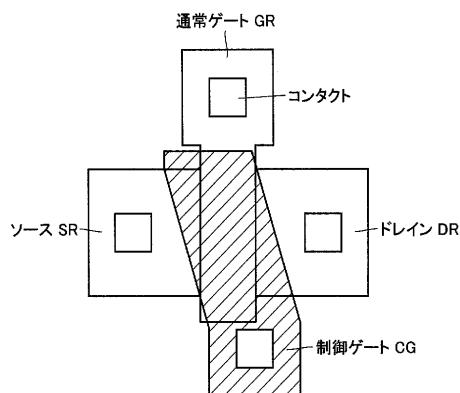

図5は、A-MOSデバイスの素子構成例を示す概念図である。

図5を参照して、A-MOSデバイスは、通常のMOSトランジスタと同様の通常ゲート50

G R、ソース S R およびドレイン D R に加えて、通常ゲートと一定角度を持つように形成される制御ゲート C G をさらに有する。

#### 【0057】

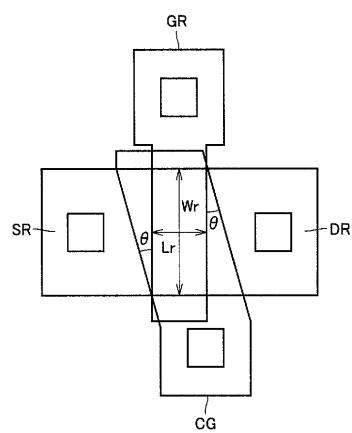

図 6 は、A - M O S デバイスの素子構成パラメータを示す概念図である。

図 6 を参照して、A - M O S デバイスは、通常ゲート G R のゲート長 L r、ゲート幅 W r および、通常ゲート G R と制御ゲート C G との成す角度  $\theta$  を素子構成パラメータとして有する。

#### 【0058】

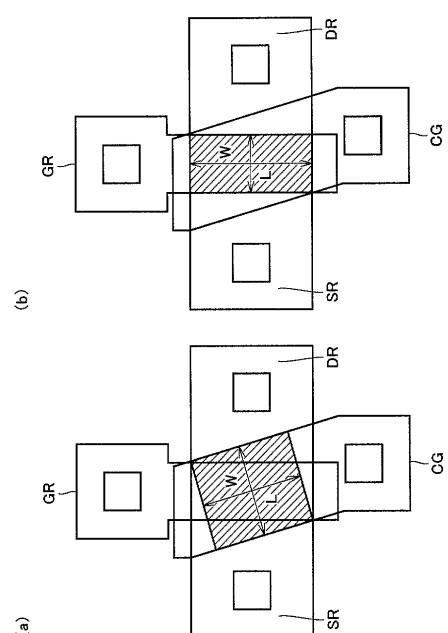

図 7 は、A - M O S デバイスにおける 变调の原理を説明する概念図である。図 7 ( a ) を参照して、制御ゲート C G 下チヤネルのコンダクタンスが通常ゲートと同等となるように、制御ゲート C G の印加電圧を設定した場合には、図中にハッチングで示した部分が実効的なゲート領域となる。すなわち、実効的なゲート長 L は、通常ゲート G R のゲート長 L r よりも長くなり、実効的なゲート幅 W は、通常ゲート G R のゲート幅 W r よりも狭くなるので、利得係数  $k$  は低下する。

10

#### 【0059】

一方、図 7 ( b ) を参照して、制御ゲート C G 下のチヤネルのコンダクタンスが通常ゲートよりも十分に大きくなるように、制御ゲート C G の印加電圧を設定した場合には、実効的なゲート幅 W およびゲート長 L は、通常ゲート G R のゲート幅 W r およびゲート長 L r と同等となる。

20

#### 【0060】

このように、A - M O S デバイスは、制御ゲート C G の印加電圧を変えることで、実効的なゲート長 L およびゲート幅 W をアナログ的に变調することができる。その結果、A - M O S デバイスは、制御ゲート電圧による利得係数  $k$  のアナログ变調を実現している。このように A - M O S デバイスは、10 ~ 1000 倍程度の 变调特性を、比較的コンパクトに実現できる特長を有している。A - M O S デバイスにおける利得係数  $k$  の变调特性は、図 6 に示したパラメータによって設定することができる。

#### 【0061】

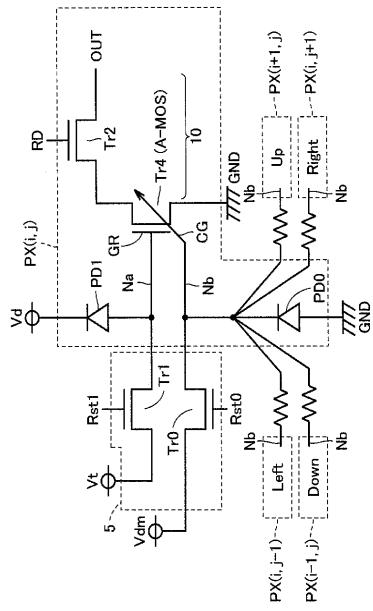

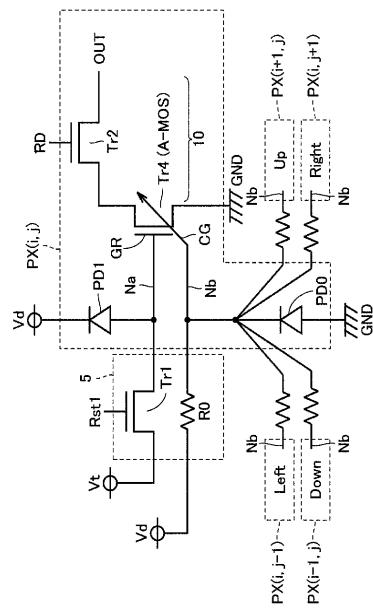

図 8 は、実施の形態 2 に従う各画素の構成を示す回路図である。

図 8 を参照して、実施の形態 2 に従う構成においては、積算器 P U に代えて、ノード N c および接地電圧 G N D の間に電気的に結合される A - M O S トランジスタ T r 4 が設けられる。A - M O S トランジスタ T r 4 の通常ゲート G R は、ノード N a と接続され、制御ゲート C G は、ノード N b と接続される。

30

#### 【0062】

このように、実施の形態 2 においては、画素への入射光量に応じて電位が変わるフォトダイオード P D 1 が A - M O S トランジスタ T r 4 の通常ゲートに接続され、周辺の平均光量に応じた電位ノード N b が A - M O S トランジスタ T r 4 の制御ゲートに接続された構成になっている。すでに説明したように、周辺の平均光量に応じた電位は、周辺の画素と抵抗成分を介して接続された平均光量検出用のフォトダイオード P D 0 によって与えられる。

#### 【0063】

40

この構成によって、周辺の平均光量が少ない画素、つまり暗い部分の画素では、A - M O S トランジスタの利得係数  $k$  を大きくし、明るい部分の画素では  $k$  を小さくする画素毎の制御を実現している。言い換えれば、A - M O S トランジスタによって、図 3 に示した積算器 P U の機能を実現することができる。

#### 【0064】

このような画素毎の 調整によって、実施の形態 1 と同様に、暗い部分の画素における信号增幅率は明るい部分の画素よりも大きくなる。その結果、暗い所のコントラストを高めることが可能となる。リセット回路 5 および、各画素のその他の部分の構成は、実施の形態 1 と同様であるので、詳細な説明は繰り返さない。

#### 【0065】

50

このように、A-MOSデバイスを各画素の信号読み出し増幅トランジスタとして用いれば、A-MOSデバイスの制御ゲートに周辺平均光量を示す電圧を与えるだけの比較的簡単な回路構成で、周辺が暗い時にその画素の増幅率を100倍程度まで高める自動調整機能を実現できると共に、この画素毎の自動調整機能を搭載することで生じる画素面積の増大を抑えることができる。

#### 【0066】

##### [実施の形態3]

実施の形態3においては、各画素に設けられる2個のフォトダイオードの効率的な配置について説明する。

#### 【0067】

10

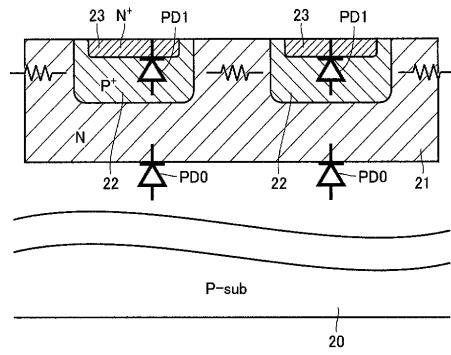

図9は、実施の形態3に従うフォトダイオードの配置例を示す構造図である。図9を参照して、半導体撮像素子が形成されるP型シリコン基板(P-sub)20と、P型シリコン基板20上に設けられたNウェル21との間に形成されるPN接合を用いて、周辺領域の平均光量を検知するためのフォトダイオードPD0が構成される。

#### 【0068】

さらに、当該Nウェル21内に形成されたP<sup>+</sup>領域22と、P<sup>+</sup>領域22内に形成されたN<sup>+</sup>領域23との間で形成されるPN接合を用いて、当該画素への入射光量を検知するためのフォトダイオードPD1が構成される。なお、P<sup>+</sup>領域22およびN<sup>+</sup>領域23の不純物濃度は、P型シリコン基板20およびNウェル21よりも比較的高い。

#### 【0069】

20

P<sup>+</sup>領域22およびN<sup>+</sup>領域23は、画素ごとに独立に設けられる。また、同一のNウェル21内に作製された複数の画素間は、Nウェルの拡散抵抗を介して電気的に結合される。すなわち、各画素におけるNウェル21は、図3の回路構成におけるノードNbに相当する。したがって、同一のNウェル21に作製された複数の画素間でノードNbが電気的に結合されて、平均光量が検知される。

#### 【0070】

あるいは、画素アレイ2全体を同一のNウェル上に形成してもよい。この場合には、各画素において、当該画素のフォトダイオードPD0と、他の画素のフォトダイオードPD0との間の電気抵抗値は、画素間の距離に対応して増大する。したがって、各画素におけるノードNbの電位Vbは、近接する画素への入射光量の影響を相対的に大きく受けるので、結果的には電位Vbによって画素周辺領域の平均光量を検知することができる。

30

#### 【0071】

実施の形態3に従うフォトダイオードの配置によれば、各画素に設けられる2個のフォトダイオードが縦構造で配置されている。さらに、周辺の画素間におけるフォトダイオード間の抵抗接続を、特別な配線等を設けることなくNウェルの形状で構成できる。したがって、各画素および画素アレイの面積の増大を防ぐことができる。

#### 【0072】

##### [実施の形態4]

図10は、実施の形態4に従う画素の構成を示す回路図である。

#### 【0073】

40

図10を図8と比較して、実施の形態4に従う構成においては、フォトダイオードPD0に対応して設けられるリセット用トランジスタTr0に代えて、抵抗器R0が、リセット電圧(たとえば電源電圧Vd)とノードNbとの間に接続される。その他の部分の構成は、図8と同様であるので、詳細な説明は繰り返さない。

#### 【0074】

このような構成としても、ノードNbは、当該画素および当該画素と電気的に結合された周辺画素内のフォトダイオードPD0への入射光量に応じた電位に落ち着くので、実施の形態1または2における構成と同様に、ノードNbの電位Vbによって画素周辺領域の平均光量を検知できる。したがって、周辺平均光量の検知動作について定期的なリセット操作を必要としないので、リセット回路5の構成を簡略化できる。なお、同様の構成は、実

50

施の形態 1 に従う図 3 に示した回路構成に対しても適用できる。

**【 0 0 7 5 】**

**[ 実施の形態 5 ]**

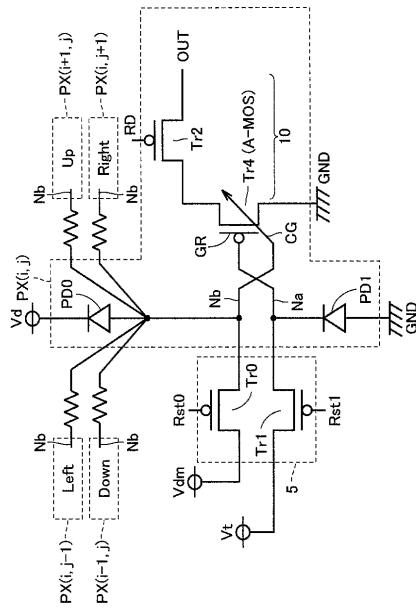

図 1 1 は、実施の形態 5 に従う画素の構成を示す回路図である。

**【 0 0 7 6 】**

図 1 1 を図 8 と比較して、実施の形態 5 に従う構成においては、実施の形態 2 に従う構成から、フォトダイオードの配置が入換えられている。すなわち、フォトダイオード P D 0 は、ノード N b から電源電圧 V d へ向かう方向を順方向として、ノード N b および電源電圧 V d の間に接続され、フォトダイオード P D 1 は、接地電圧 G N D からノード N a へ向かう方向を順方向として、接地電圧 G N D およびノード N a の間に接続される。これに対応して、読み出選択スイッチトランジスタ T r 2 および A - M O S トランジスタ T r 4 は、N チャネル型から P チャネル型に変更される。なお、同様の構成は、実施の形態 1 に従う図 3 に示した回路構成に対しても適用できる。10

**【 0 0 7 7 】**

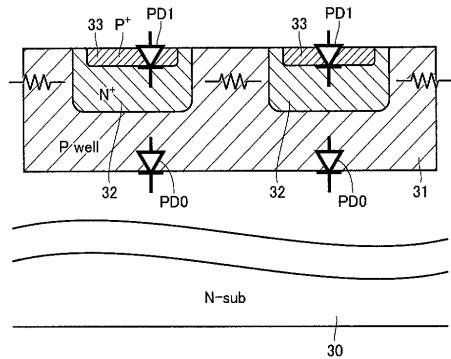

図 1 2 は、実施の形態 5 に従うフォトダイオードの配置例を示す構造図である。

**【 0 0 7 8 】**

図 1 2 を参照して、実施の形態 5 においては、半導体撮像素子が形成される N 型シリコン基板 ( N - S u b ) 3 0 上に設けられた P ウェル 3 1 との間に形成される P N 接合を用いて、画素周辺領域の平均光量を検知するためのフォトダイオード P D 0 が構成される。さらに、当該 P ウェル 3 1 内に形成された N<sup>+</sup> 領域 3 2 と、N<sup>+</sup> 領域 3 2 内に形成された P<sup>+</sup> 領域 3 3 との間で形成される P N 接合を用いて、当該画素への入射光量を検知するためのフォトダイオード P D 1 が構成される。20

**【 0 0 7 9 】**

図 9 に示した構造と同様に、N<sup>+</sup> 領域 3 2 および P<sup>+</sup> 領域 3 3 は、画素ごとに独立に設けられ、N<sup>+</sup> 領域 3 2 および P<sup>+</sup> 領域 3 3 の不純物濃度は、N 型シリコン基板 3 0 および P ウェル 3 1 よりも比較的高い。また、P ウェル 3 1 の設計については、図 9 における N ウェル 2 1 と同様にすればよい。

**【 0 0 8 0 】**

このように、フォトダイオードの配置を入換えた構成としても、実施の形態 1 または 2 と同様に、各画素毎において周辺平均光量に応じて感度直線（増幅率）を変化させるような自動調整機能を実現して、画面の全領域で十分なコントラストが検知できるようになる。さらに、実施の形態 3 と同様に、各画素ごとに 2 個のフォトダイオードを必要とする構成においても、各画素および画素アレイの面積の増大を防ぐことができる。30

**【 0 0 8 1 】**

**[ 実施の形態 6 ]**

図 1 3 は、実施の形態 6 に従う画素の構成を示す回路図である。

**【 0 0 8 2 】**

図 1 3 を図 1 1 と比較して、実施の形態 6 に従う構成においては、フォトダイオード P D 0 に対応して設けられるリセット用トランジスタ T r 0 に代えて、抵抗器 R 0 が、リセット電圧である接地電圧 G N D とノード N b との間に接続される。その他の部分の構成は、図 1 1 と同様であるので、詳細な説明は繰り返さない。40

**【 0 0 8 3 】**

このように、フォトダイオードの配置を入換えた構成においても、実施の形態 4 と同様に、リセット回路 5 の構成を簡略化した上で、画面の全領域で十分なコントラストが検知できるようになる。また、図 1 3 に従う回路構成においても、各画素に必要な 2 個のフォトダイオード P D 0 , P D 1 は、図 1 2 の構造図と同様に、各画素および画素アレイの面積の増大を防止して配置できる。

**【 0 0 8 4 】**

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、50

特許請求の範囲と均等の意味および範囲内のすべての変更が含まれることが意図される。

### 【0085】

#### 【発明の効果】

以上説明したように、この発明によれば、一般にC M O SイメージセンサーはS / N比が60 ~ 65dB程度なので、画面の中で最も暗い所の画質を20dB程度まで許せば、本発明の半導体撮像素子（イメージセンサー）は、数百倍程度の平均輝度差まで、十分なコントラストを全画面で検知できると見積られる。

### 【0086】

また、本発明の半導体撮像素子（イメージセンサー）は、受光感度特性を画素毎にアナログ調整できる機能を、コンパクトに実装できるので、従来のイメージセンサーと比べて感度および解像度で劣ることがない。 10

### 【0087】

さらに、本発明の半導体撮像素子（イメージセンサー）は、従来のイメージセンサーでは検知することが困難だった、同一視野内の大さな輝度差の画像を、十分なコントラストで検知することができ、ヒトの知覚能力に近い優れた撮像装置として利用することができる。従って、このイメージセンサーは、監視装置や車載用カメラ等の、急激な環境変化への対応が要求される分野で威力を発揮できる。

#### 【図面の簡単な説明】

【図1】 本発明の実施の形態に従う半導体撮像素子の構成を示す概略ブロック図である 20

。

【図2】 各画素の構成を説明するブロック図である。

【図3】 各画素の構成を詳細に示す回路図である。

【図4】 本発明に従う半導体撮像素子の画素特性を示す概念図およびその撮像例を示す図である。

【図5】 A - M O S デバイスの素子構成例を示す概念図である。

【図6】 A - M O S デバイスの素子構成パラメータを示す概念図である。

【図7】 A - M O S デバイスにおける 变調の原理を説明する概念図である。

【図8】 実施の形態2に従う各画素の構成を示す回路図である。

【図9】 実施の形態3に従うフォトダイオードの配置例を示す構造図である。 30

【図10】 実施の形態4に従う画素の構成を示す回路図である。

【図11】 実施の形態5に従う画素の構成を示す回路図である。

【図12】 実施の形態5に従うフォトダイオードの配置例を示す構造図である。

【図13】 実施の形態6に従う画素の構成を示す回路図である。

【図14】 従来の半導体撮像素子による撮像例を示す第1の図である（室内可視）。

【図15】 従来の半導体撮像素子による撮像例を示す第2の図である（室外可視）。

【図16】 従来の半導体撮像素子のコントラスト検知能力の低さを説明する図である。

#### 【符号の説明】

1 半導体撮像素子

2 画素アレイ

3 読出制御回路

5 リセット回路

7 電源回路

10 画素信号生成回路

15 画素データ生成回路

20 P型シリコン基板

21 Nウェル

22, 33 P<sup>+</sup>領域（不純物濃度が比較的高い）

23, 32 N<sup>+</sup>領域（不純物濃度が比較的高い）

30 N型シリコン基板

40

50

C G 制御ゲート

G N D 接地電圧

G R 通常ゲート

L 実効ゲート長 (A - M O S トランジスタ)

N a , N b , N c ノード

O U T 画像信号

P D 0 フォトダイオード (周辺画素平均受光検知用)

P D I フォトダイオード (当該画素内受光検知用)

P U 積算器

P X 画素

R 0 抵抗器

R s t 0 , R s t 1 リセット信号

T r 0 , T r 1 リセット用トランジスタ

T r 2 読出選択スイッチトランジスタ

T r 4 A - M O S トランジスタ (Adjustable - M O S トランジスタ)

V d 電源電圧

V d m , V t リセット電圧

W 実効ゲート幅 (A - M O S トランジスタ)

利得係数

10

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

---

フロントページの続き

(74)代理人 100109162

弁理士 酒井 將行

(74)代理人 100114812

弁理士 増田 義行

(72)発明者 有馬 裕

福岡県飯塚市川津680-4 九州工業大学マイクロ化総合技術センター内

審査官 徳 田 賢二

(56)参考文献 特開平08-149376(JP,A)

特開平08-331457(JP,A)

特開平06-189199(JP,A)

特開2000-340779(JP,A)

特開平11-274457(JP,A)

特開平11-274456(JP,A)

特開平03-253075(JP,A)

特開2001-203941(JP,A)

特開2001-086518(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/335

H01L 27/146