(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

26 May 2011 (26.05.2011)

(10) International Publication Number

**WO 2011/062058 A1**

(51) International Patent Classification:

*H01L 27/10* (2006.01) *H01L 21/8242* (2006.01)

*C23C 14/08* (2006.01) *H01L 27/088* (2006.01)

*C23C 16/42* (2006.01) *H01L 27/092* (2006.01)

*G11C 16/04* (2006.01) *H01L 27/105* (2006.01)

*H01L 21/363* (2006.01) *H01L 27/108* (2006.01)

*H01L 21/8234* (2006.01) *H01L 29/786* (2006.01)

*H01L 21/8238* (2006.01)

Kanagawa, 2430036 (JP). **KOYAMA, Jun. KATO, Kiyoshi.**

(21) International Application Number:

PCT/JP2010/069546

(22) International Filing Date:

27 October 2010 (27.10.2010)

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

2009-264623 20 November 2009 (20.11.2009) JP

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(72) Inventors; and

(75) Inventors/Applicants (for US only): **YAMAZAKI, Shunpei** [JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

Published:

— with international search report (Art. 21(3))

(54) Title: SEMICONDUCTOR DEVICE

**FIG. 1**

(57) **Abstract:** An object of the present invention is to provide a semiconductor device combining transistors integrating on a same substrate transistors including an oxide semiconductor in their channel formation region and transistors including non-oxide semiconductor in their channel formation region. An application of the present invention is to realize substantially non-volatile semiconductor memories which do not require specific erasing operation and do not suffer from damages due to repeated writing operation. Furthermore, the semiconductor device is well adapted to store multivalued data. Manufacturing methods, application circuits and driving/reading methods are explained in details in the description.

**WO 2011/062058 A1**

## DESCRIPTION

## SEMICONDUCTOR DEVICE

## 5 TECHNICAL FIELD

[0001]

The present invention relates to a semiconductor device using semiconductor elements and a manufacturing method thereof.

## 10 BACKGROUND ART

[0002]

Memory devices using semiconductor elements are roughly classified into volatile memory devices that lose their memory content when power supply is stopped and nonvolatile memory devices that can hold their memory content even when power supply is stopped.

[0003]

As a typical example of a volatile memory device, a dynamic random access memory (DRAM) is given. In a DRAM, a transistor included in a memory element is selected and an electric charge is accumulated in a capacitor, so that information is memorized.

[0004]

Owing to the above-described principle, a charge in a capacitor is lost when information data is read in a DRAM; thus, it is necessary to perform rewriting of the information data, so that information is memorized again after the information data reading. In addition, there is leakage of current in a transistor included in a memory element so that a charge accumulated at an electrode of the capacitor is lost or a charge flows into the capacitor, even if the transistor is not selected to perform any operation, whereby data holding period is short. Therefore, it is necessary to perform rewriting in a predetermined cycle (refresh operation) and it is difficult to reduce power consumption satisfactorily. Further, since memory content is lost when the power is not supplied to the DRAM, another memory device using a magnetic material or an optical material is needed to store information for a long period.

## [0005]

As another example of a volatile memory device, a static random access memory (SRAM) is given. In an SRAM, memory content is stored using a circuit such as a flip flop, so that refresh operation is not needed. In view of this point, 5 SRAM is advantageous over a DRAM. However, an inconvenient in that a cost per storage capacity becomes high because a circuit such as a flip flop is used. Further, in view of the point that memory content is lost when the power is not supplied, an SRAM is not superior to a DRAM.

## [0006]

10 As a typical example of a nonvolatile memory device, flash memory is given. A flash memory includes a floating gate between a gate electrode and a channel formation region in a transistor. A flash memory stores memory content by storing a charge in the floating gate, so that a data holding period is extremely long (semi-permanent), and thus has an advantage that refresh operation which is necessary 15 in a volatile memory device is not needed (for example, see Patent Document 1).

## [0007]

20 However, in flash memory, there is a problem in that a memory element does not function after performing writing operations a predetermined number of times because a gate insulating layer included in the memory element is deteriorated by a tunnel current occurring each time a writing operation is performed. In order to relieve an adverse effect of this phenomenon, a method consisting in equalizing the number of 25 writing operations between the memory elements is employed, for example. However, a complicated peripheral circuit is needed to apply this method. Further, even if such a method is employed, the basic problem of lifetime is not resolved. That is, a flash memory is unsuitable for applications in which information is rewritten with high frequency.

## [0008]

30 Further, high voltage is required to store a charge in the floating gate or to remove a charge in the floating gate. Furthermore, a relatively long time is required for storing or removing a charge and the speed of writing and erasing cannot easily be increased.

## [Reference]

[Patent Document]

[0009]

[Patent Document 1] Japanese Published Patent Application No. S57-105889

## 5 DISCLOSURE OF INVENTION

[0010]

In view of the above problem, one object of one embodiment of the present invention is to provide a semiconductor device having a new structure, the semiconductor device being capable of holding memory content in the state where power is not supplied and having no limitation on the number of writing operations. Another object of one embodiment of the present invention is to provide a semiconductor having a structure allowing using easily multivalued information.

[0011]

One embodiment of the present invention is a semiconductor device having a stack of a transistor using an oxide semiconductor and a transistor using a material other than an oxide semiconductor. For example, the semiconductor device can employ the following structures.

[0012]

One embodiment of the present invention is a semiconductor device including: a source line; a bit line; a first signal line; a plurality of second signal lines; a plurality of word lines; a plurality of memory cells connected in parallel between the source line and the bit line; a driver circuit for the second signal lines and the word lines to which an address signal is input and which drives the plurality of second signal lines and the plurality of word lines so that a memory cell specified by the address signal is selected from the plurality of memory cells; a driver circuit of the first signal line selecting and outputting any of a plurality of writing potentials to the first signal line; a reading circuit to which a potential of the bit line and a plurality of reference potentials are input and which read data by comparing the potential of the bit line and the plurality of reference potentials; a potential generating circuit generating and supplying the plurality of writing potentials and the plurality of reference potentials to the driver circuit of the first signal line and the reading circuit; and a boosting circuit supplying a potential to the potential generating circuit. One of the memory cells includes: a first transistor having

a first gate electrode, a first source electrode, and a first drain electrode; a second transistor having a second gate electrode, a second source electrode, and a second drain electrode; and a third transistor having a third gate electrode, a third source electrode, and a third drain electrode. The first transistor is provided over a substrate containing 5 a semiconductor material. The second transistor includes an oxide semiconductor layer. The first gate electrode and one of the second source electrode and the second drain electrode are electrically connected to each other. The source line and the first source electrode are electrically connected to each other. The first drain electrode and the third source electrode are electrically connected to each other. The bit line and the 10 third drain electrode are electrically connected to each other. The first signal line and the other of the second source electrode and the second drain electrode are electrically connected to each other. One of the second signal lines and the second gate electrode are electrically connected to each other. One of the word lines and the third gate electrode are electrically connected to each other.

15 [0013]

Additionally, in the above structure, the semiconductor device includes a capacitor electrically connected to the first gate electrode and one of the second source electrode and the second drain electrode.

[0014]

20 Another embodiment of the present invention is a semiconductor device including: a source line; a bit line; a first signal line; a plurality of second signal lines; a plurality of word lines; a plurality of memory cells connected in parallel between the source line and the bit line; a driver circuit for the second signal lines and the word lines to which an address signal is input and which drives the plurality of second signal lines 25 and the plurality of word lines so that a memory cell specified by the address signal is selected from the plurality of memory cells; a driver circuit of the first signal line selecting and outputting any of a plurality of writing potentials to the first signal line; a reading circuit to which a potential of the bit line and a plurality of reference potentials are input and which has a reference memory cell, and reads data by comparing 30 conductance of the specified memory cell and conductance of the reference memory cell; a potential generating circuit generating and supplying the plurality of writing potentials and the plurality of reference potentials to the driver circuit of the first signal

line and the reading circuit; and a boosting circuit supplying a potential to the potential generating circuit. One of the plurality of memory cells includes: a first transistor having a first gate electrode, a first source electrode, and a first drain electrode; a second transistor having a second gate electrode, a second source electrode, and a second drain electrode; and a third transistor having a third gate electrode, a third source electrode, and a third drain electrode. The first transistor is provided over a substrate containing a semiconductor material. The second transistor includes an oxide semiconductor layer. The first gate electrode and one of the second source electrode and the second drain electrode are electrically connected to each other. The source line and the first source electrode are electrically connected to each other. The first drain electrode and the third source electrode are electrically connected to each other. The bit line and the third drain electrode are electrically connected to each other. The first signal line and the other of the second source electrode and the second drain electrode are electrically connected to each other. One of the second signal lines and the second gate electrode are electrically connected to each other. One of the word lines and the third gate electrode are electrically connected to each other.

[0015]

Another embodiment of the present invention is a semiconductor device including: a source line; a bit line; a first signal line; a plurality of second signal lines; a plurality of word lines; a plurality of memory cells connected in parallel between the source line and the bit line; a driver circuit of the second line and the word line to which an address signal and a plurality of reference potentials are input and which drives the plurality of second signal lines and the plurality of word lines so that a memory cell specified by the address signal is selected from the plurality of memory cells and which 20 selects and outputs any of the plurality of reference potentials to one selected word line; a driver circuit of the first signal line selecting and outputting any of a plurality of writing potentials to the first signal line; a reading circuit to which the bit line is connected and which reads data by reading conductance of the specified memory cell to 25 read data; a potential generating circuit generating and supplying the plurality of writing potentials and the plurality of reference potentials to the driver circuit of the first signal line and the reading circuit; and a boosting circuit supplying a potential to the potential generating circuit. One of the memory cells includes: a first transistor having a first

gate electrode, a first source electrode, and a first drain electrode; a second transistor having a second gate electrode, a second source electrode, and a second drain electrode; and a capacitor. The first transistor is provided over a substrate containing a semiconductor material. The second transistor is includes an oxide semiconductor layer. The first gate electrode, one of the second source electrode and the second drain electrode, and one of electrodes of the capacitor are electrically connected to one another. The source line and the first source electrode are electrically connected to each other. The bit line and the first drain electrode are electrically connected to each other. The first signal line and the other of the second source electrode and the second drain electrode are electrically connected to each other. One of the second signal lines and the second gate electrode are electrically connected to each other. One of the word lines and the other of the electrodes of the capacitor are electrically connected to each other.

[0016]

In the above structure, the first transistor includes the following elements: a channel formation region provided over the substrate containing the semiconductor material, impurity regions formed with the channel formation region sandwiched therebetween, the first gate insulating layer over the channel formation region, a first gate electrode over the first gate insulating layer, and the first source electrode and the first drain electrode both of which are electrically connected to the impurity regions.

[0017]

Further, in the above structure, the second transistor includes the following elements: the second gate electrode over the substrate containing the semiconductor material, a second gate insulating layer over the second gate electrode, the oxide semiconductor layer over the second gate insulating layer, and the second source electrode and the second drain electrode both of which are electrically connected to the oxide semiconductor layer.

[0018]

In the above structure, the third transistor includes the following elements: a channel formation region provided over the substrate containing the semiconductor material, impurity regions formed with the channel formation region sandwiched therebetween, the third gate insulating layer over the channel formation region, a third

gate electrode over the third gate insulating layer, and the third source electrode and the third drain electrode both of which are electrically connected to the impurity regions [0019]

5 In the above structure, the substrate containing the semiconductor material is preferably a single crystal semiconductor substrate. In particular, the semiconductor material is preferably silicon. Further, as a substrate containing the semiconductor material, an SOI substrate may also be used.

[0020]

10 Preferably, in the above structure, the oxide semiconductor layer contains an In-Ga-Zn-O based oxide semiconductor material. In particular, the oxide semiconductor layer preferably contains an  $\text{In}_2\text{Ga}_2\text{ZnO}_7$  crystal. In addition, preferably, the hydrogen concentration of the oxide semiconductor layer is less than or equal to  $5 \times 10^{19}$  atoms /cm<sup>3</sup>. The off-state current of the second transistor is preferably less than or equal to  $1 \times 10^{-13}$  A.

15 [0021]

In addition, in the above structure, the second transistor can be provided in a region overlapping with the first transistor.

[0022]

20 Note that in this specification, "over" and "below" do not necessarily mean "directly on" and "directly under", respectively, in the description of a physical relationship between components. For example, the expression of "a first gate electrode over a gate insulating layer" may refer to the case where another component is interposed between the gate insulating layer and the first gate electrode. In addition, the terms "above" and "below" are just used for convenience of explanations and they 25 can be interchanged unless otherwise specified.

[0023]

30 In this specification, the term "electrode" or "wiring" does not limit the function of components. For example, an "electrode" can be used as a part of a "wiring", and the "wiring" can be used as a part of the "electrode". In addition, the term "electrode" or "wiring" can also mean a combination of a plurality of "electrodes" and "wirings", for example.

## [0024]

Further, functions of a "source" and a "drain" might be switched when transistors having different polarities are employed or a direction of current flow is changed in circuit operation, for example. Therefore, the terms "source" and "drain" 5 can be switched in this specification.

## [0025]

Note that in this specification, the expression of "electrically connected" includes the case of electrical connection through "an object having any electrical function". Here, there is no particular limitation on "an object having any electrical 10 function" as long as the object enables transmission and reception of an electrical signal between components connected by the object.

## [0026]

For example, the category "an object having any electrical function" can include a switching element such as a transistor, a resistor, an inductor, a capacitor, and 15 other elements having several functions, as well as electrodes and wirings.

## [0027]

In general, the term "SOI substrate" means a substrate having a silicon semiconductor layer over an insulating surface. In this specification, the term "SOI substrate" also means a substrate having a semiconductor layer using a material other 20 than silicon over an insulating surface. That is, a semiconductor layer included in the "SOI substrate" is not limited to a silicon semiconductor layer. Additionally, a substrate in an "SOI substrate" is not limited to a semiconductor substrate such as a silicon wafer, and may be a non-semiconductor substrate such as a glass substrate, a quartz substrate, a sapphire substrate, and a metal substrate. That is, an "SOI 25 substrate" also includes a conductive substrate and an insulating substrate over which a layer is formed using a semiconductor material. In addition, in this specification, a "semiconductor substrate" means a substrate of only a semiconductor material and also a general substrate of a material including a semiconductor material. In other words, in this specification, an "SOI substrate" is also included in the broad category of a 30 "semiconductor substrate".

## [0028]

Moreover, in this specification, a semiconductor material other than an oxide semiconductor may be any semiconductor material as long as it is a semiconductor material other than an oxide semiconductor material. For example, silicon, germanium, silicon germanium, silicon carbide, gallium arsenide, or the like can be given. Besides, an organic semiconductor material and the like can be used. Note that in the case where a material included in a semiconductor device and the like is not particularly specified, an oxide semiconductor material or a semiconductor material other than an oxide semiconductor material may be used.

[0029]

One embodiment of the present invention provides, in its lower portion, a semiconductor device including a transistor using a material other than an oxide semiconductor in its channel formation region, and, in its upper portion, a transistor using an oxide semiconductor in its channel formation region.

[0030]

A transistor using an oxide semiconductor has extremely low off-state current; therefore, by using the transistor, memory content can be stored for a relatively long time. That is, refresh operation can become unnecessary, or frequency of refresh operation can be reduced considerably, so that power consumption can be reduced substantially. Further, even in the case where power is not supplied, memory content can be stored for a long time.

[0031]

In addition, high voltage is not needed for writing information in the semiconductor device and there is no problem of deterioration of elements. For example, since there is no need to perform injection of electrons to a floating gate and extraction of electrons from a floating gate which are needed in a conventional nonvolatile memory, deterioration such as deterioration of a gate insulating layer does not occur. That is, the semiconductor device according to one embodiment of the present invention does not have a limit on the number of times of writing which is a problem in a conventional nonvolatile memory, and reliability thereof is drastically improved. Further, information is written according to an on state and an off state of the transistor, whereby high-speed operation can be easily realized. Additionally, when information is written, there is an advantage that operation for erasing the

previously stored information is not needed.

[0032]

Further, the transistor formed using a material other than an oxide semiconductor can be operated at sufficiently high speed; therefore, by using the 5 transistor, stored contents can be read out at high speed.

[0033]

Moreover, the semiconductor device according to one embodiment of the present invention can easily multivalue data by being provided with a boosting circuit, so that storage capacity can be increased.

10 [0034]

Accordingly, a semiconductor device having unprecedented characteristics can be realized by being provided with a combination of a transistor using a material other than an oxide semiconductor material and a transistor using an oxide semiconductor material.

15

## BRIEF DESCRIPTION OF DRAWINGS

[0035]

In the accompanying drawings:

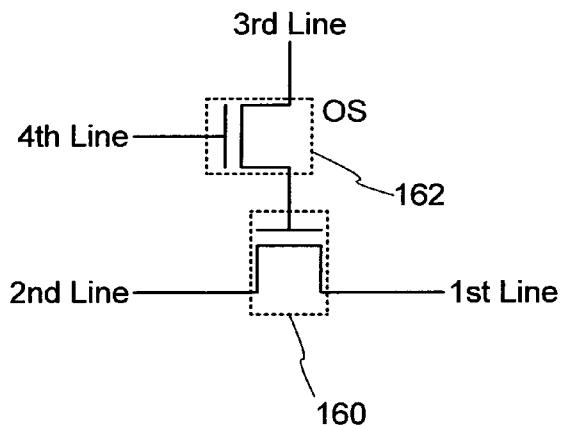

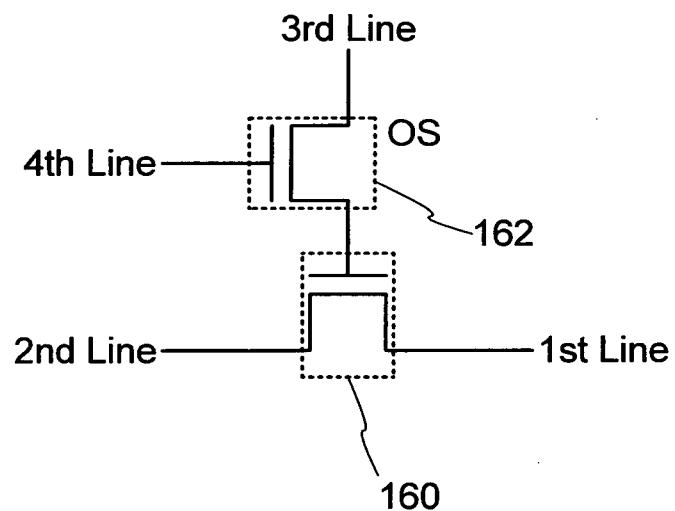

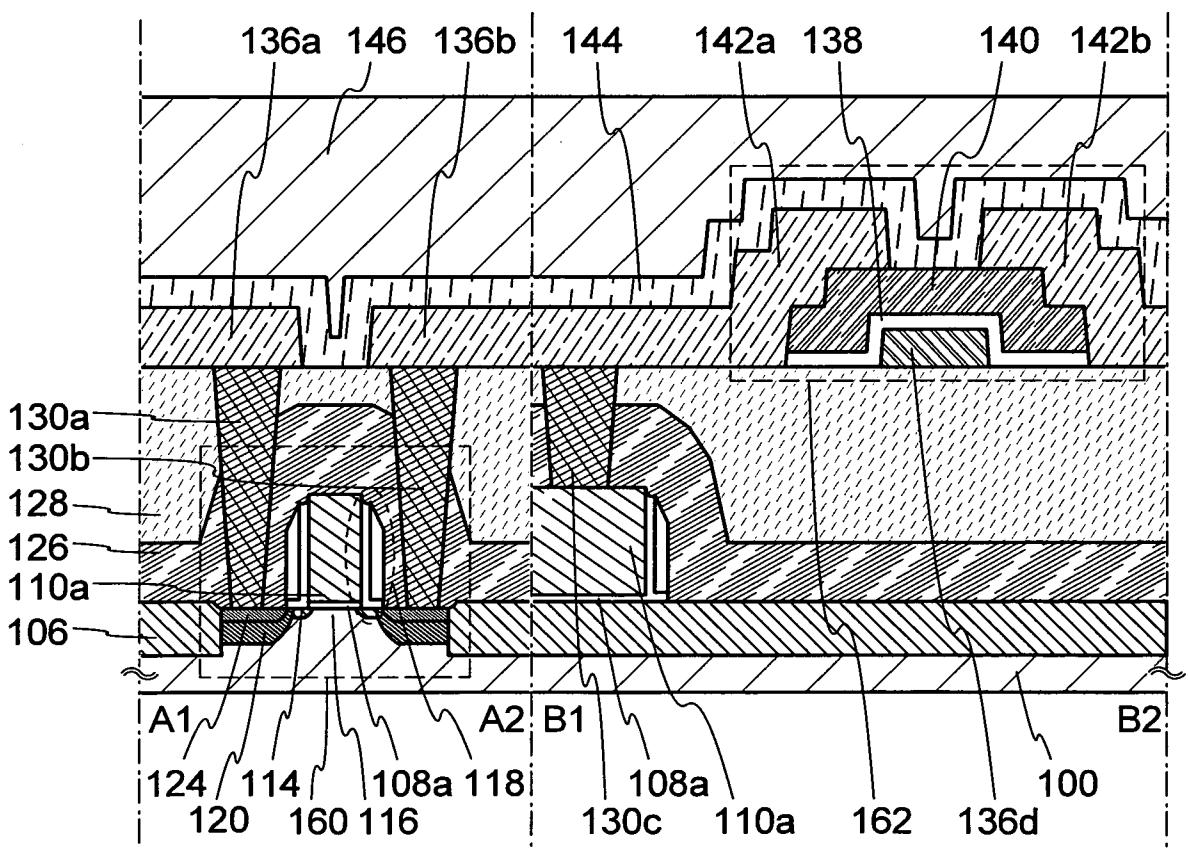

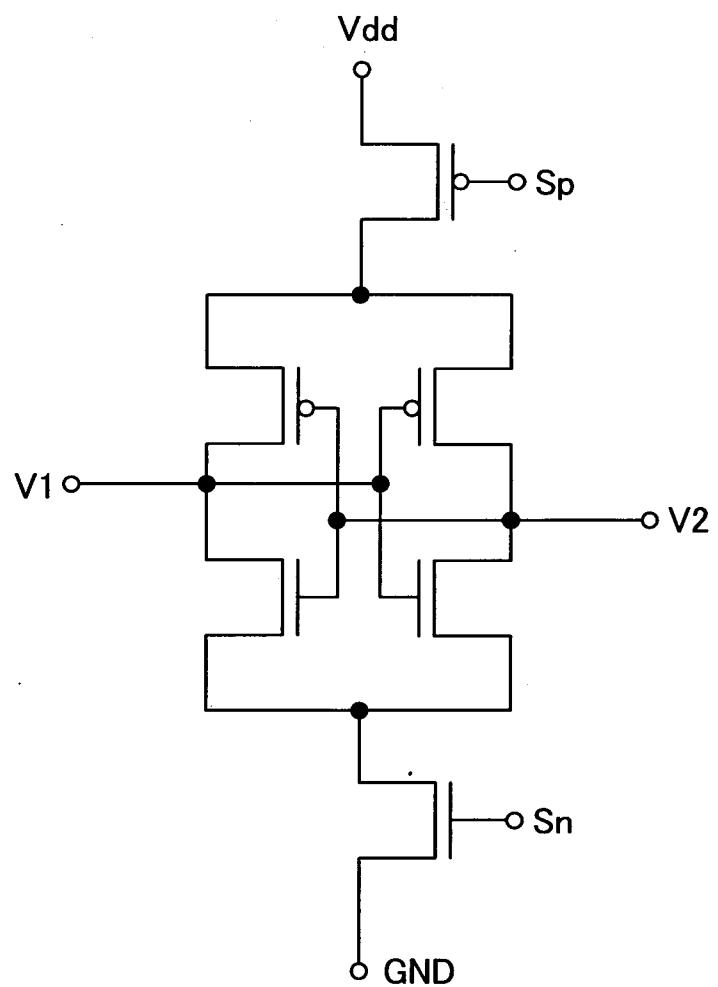

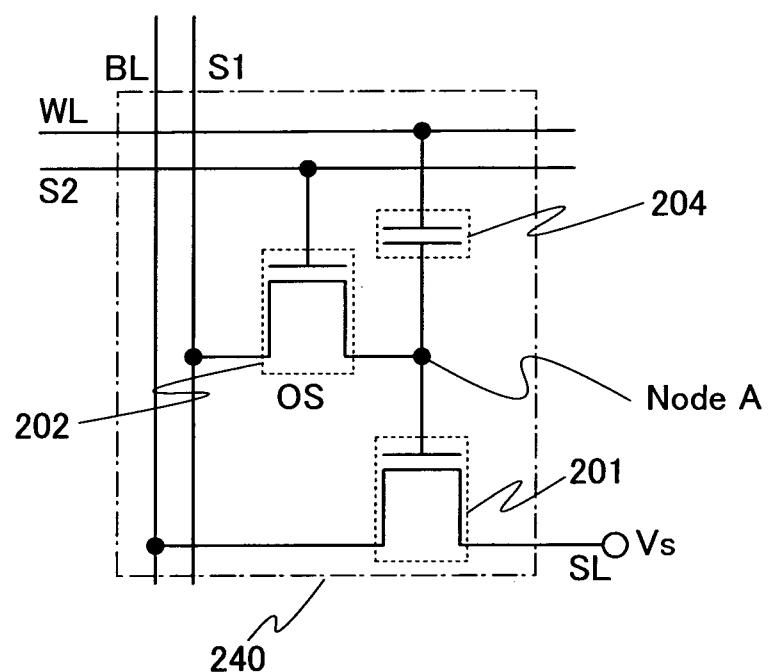

FIG. 1 is a circuit diagram for describing a semiconductor device;

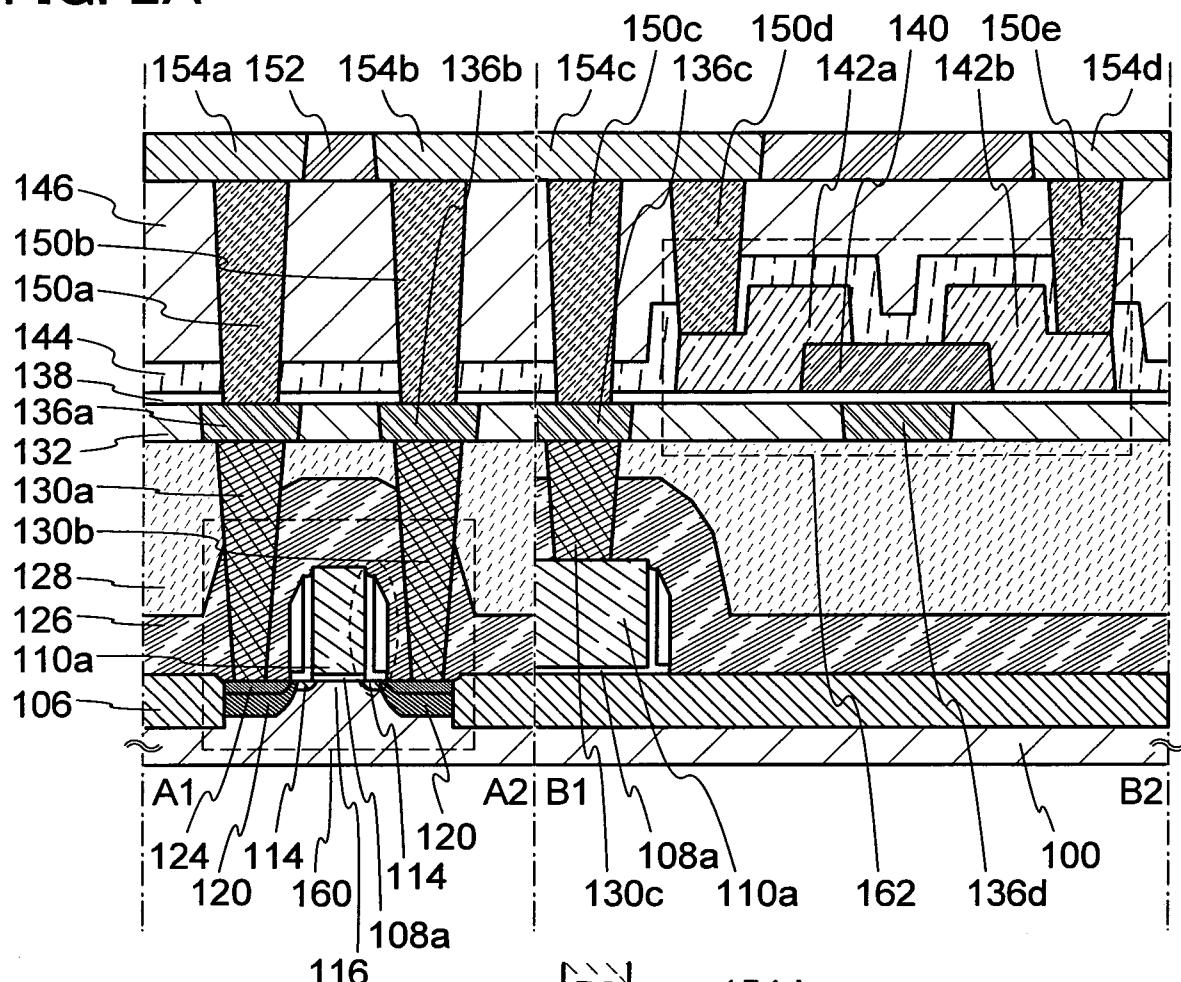

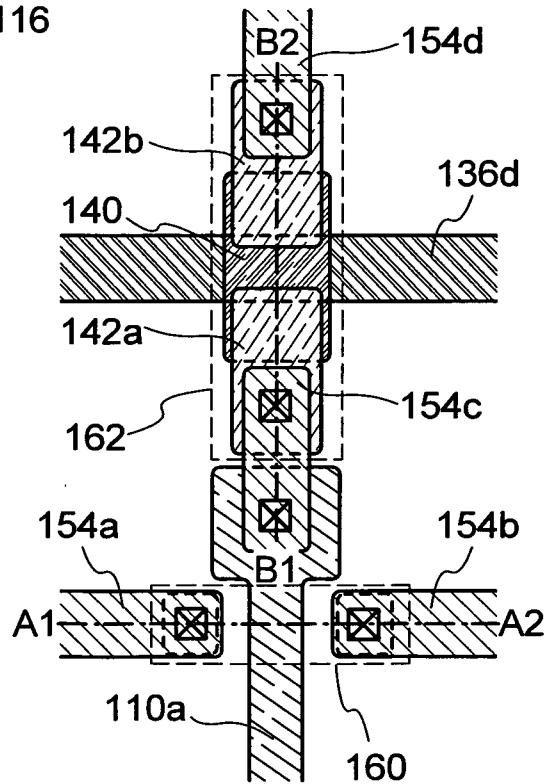

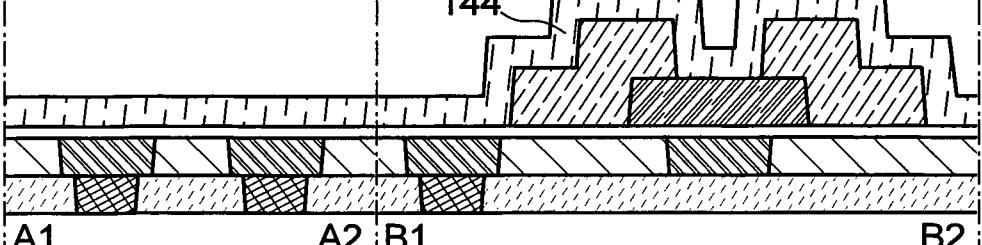

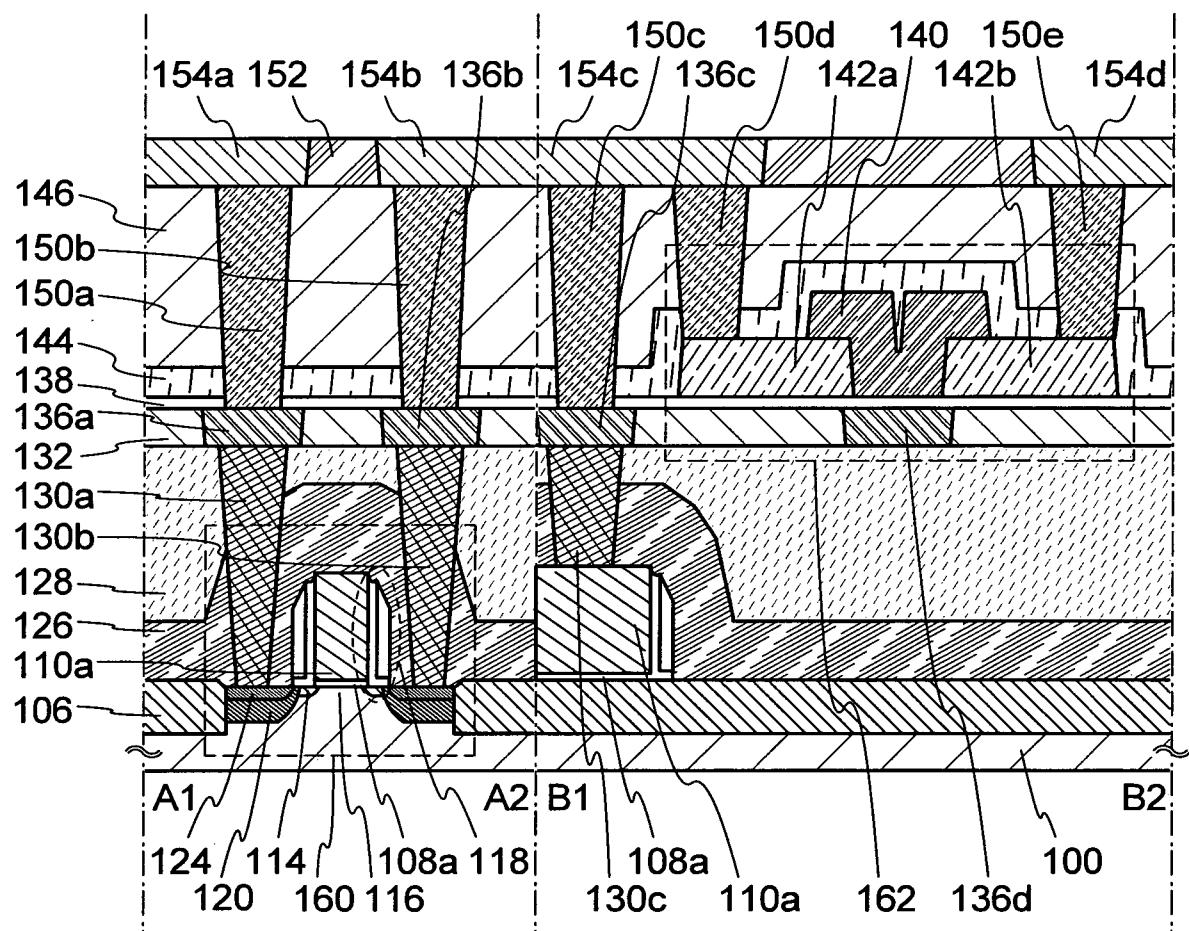

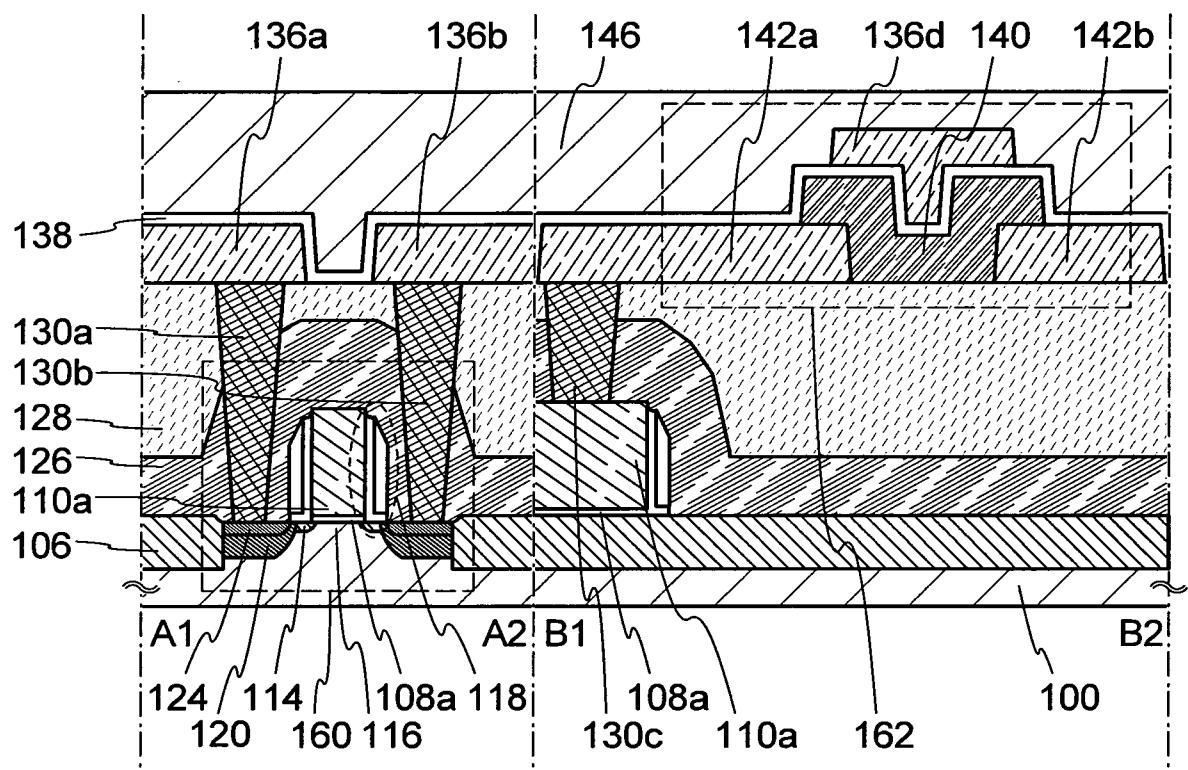

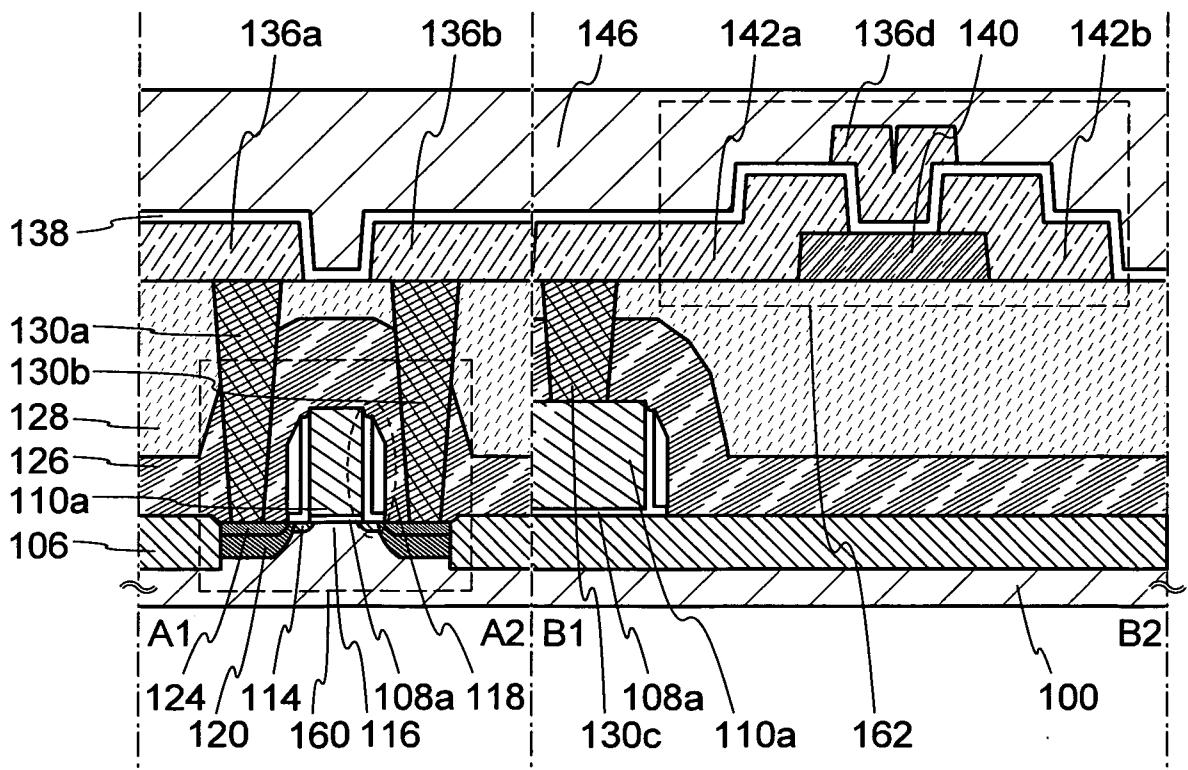

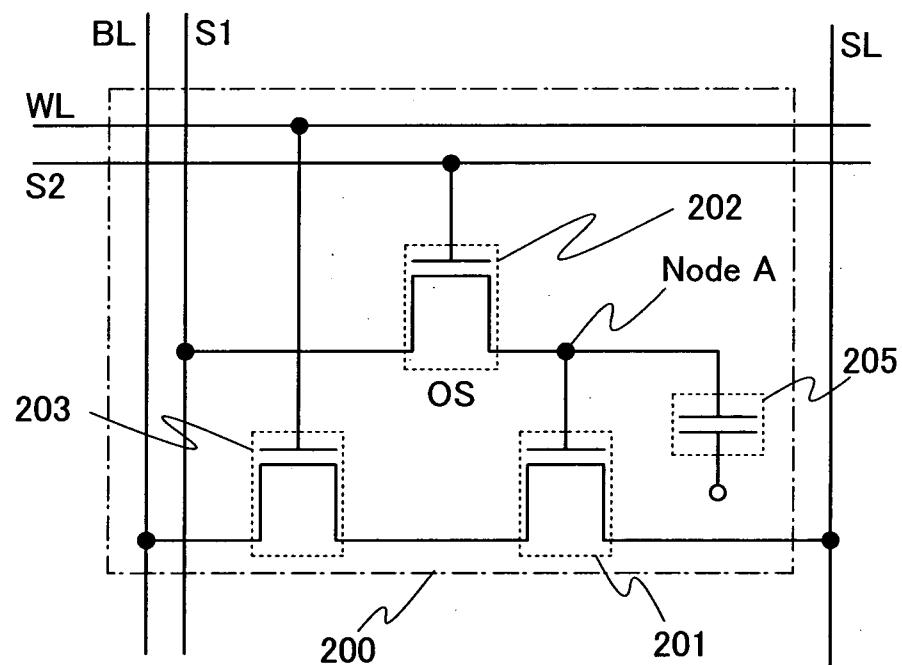

20 FIG. 2A is a cross-sectional view for describing a semiconductor device and FIG. 2B is a plan view for describing the semiconductor device;

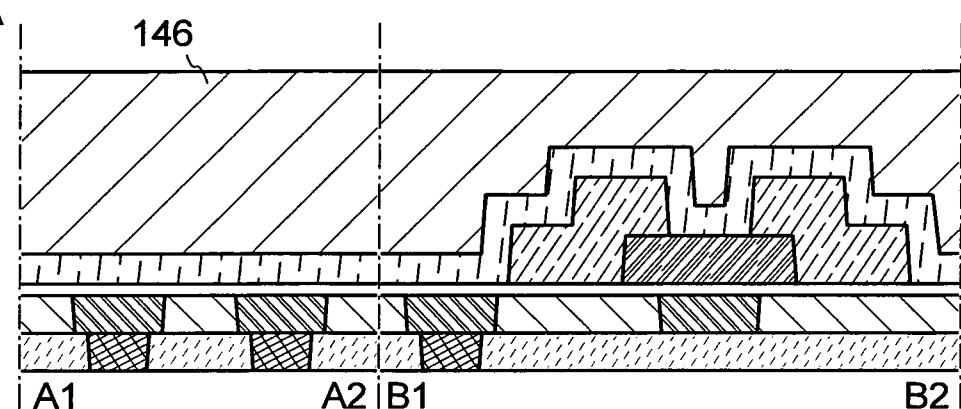

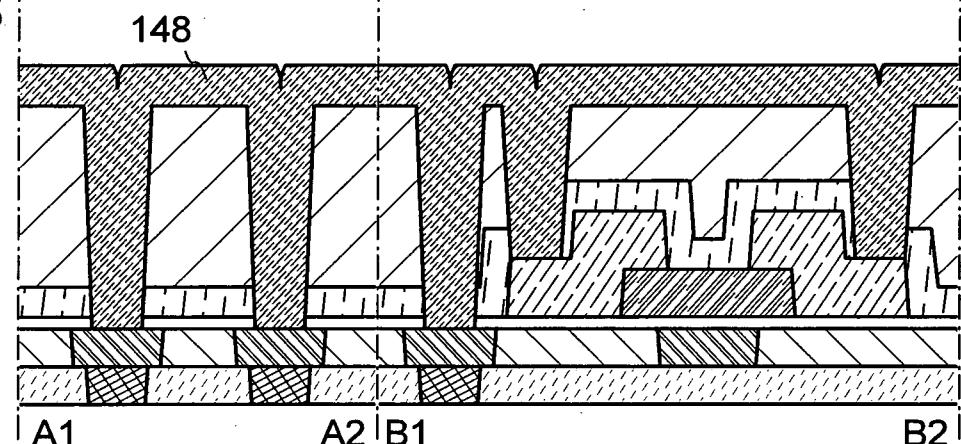

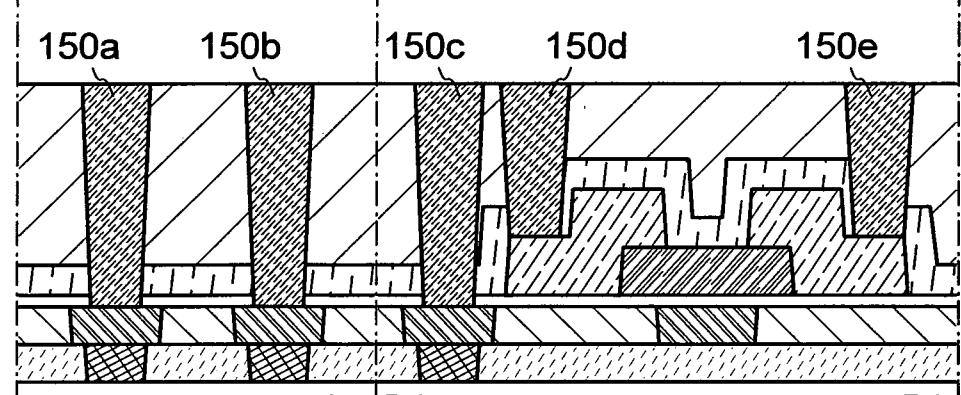

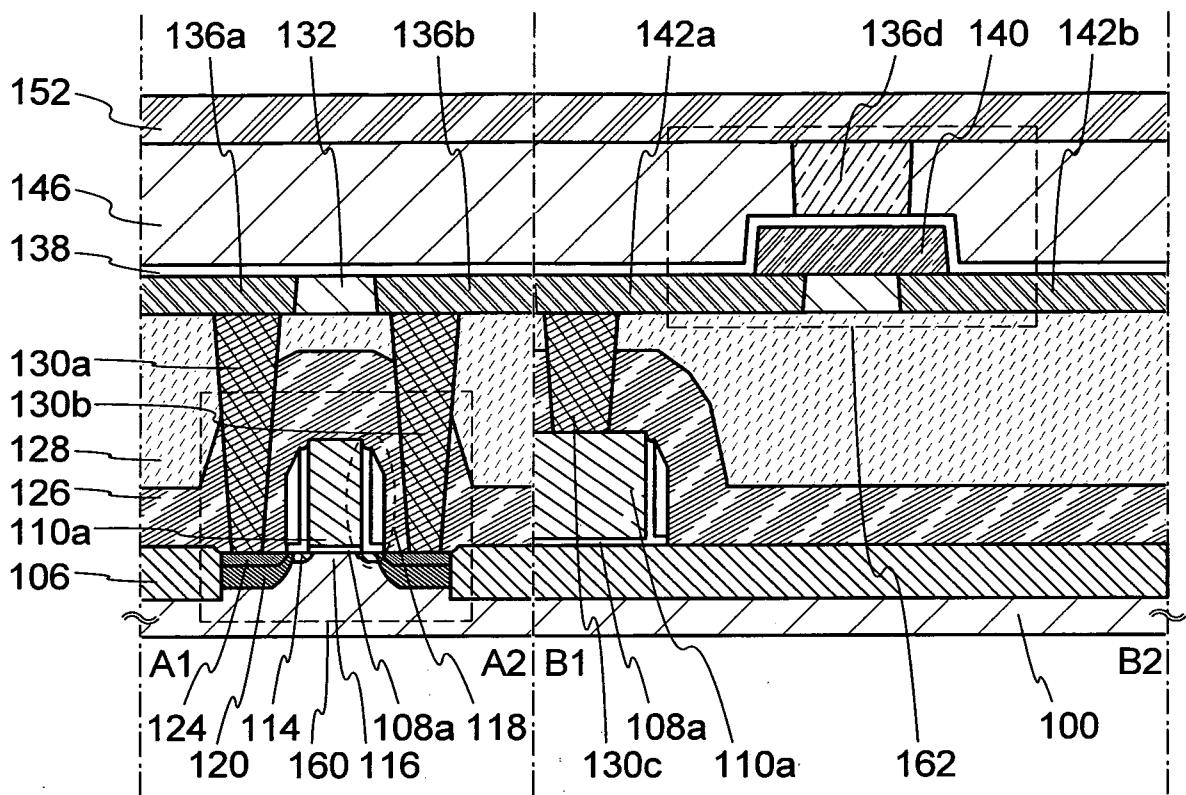

FIGS. 3A to 3H are cross-sectional views each for explaining a manufacturing step of a semiconductor device;

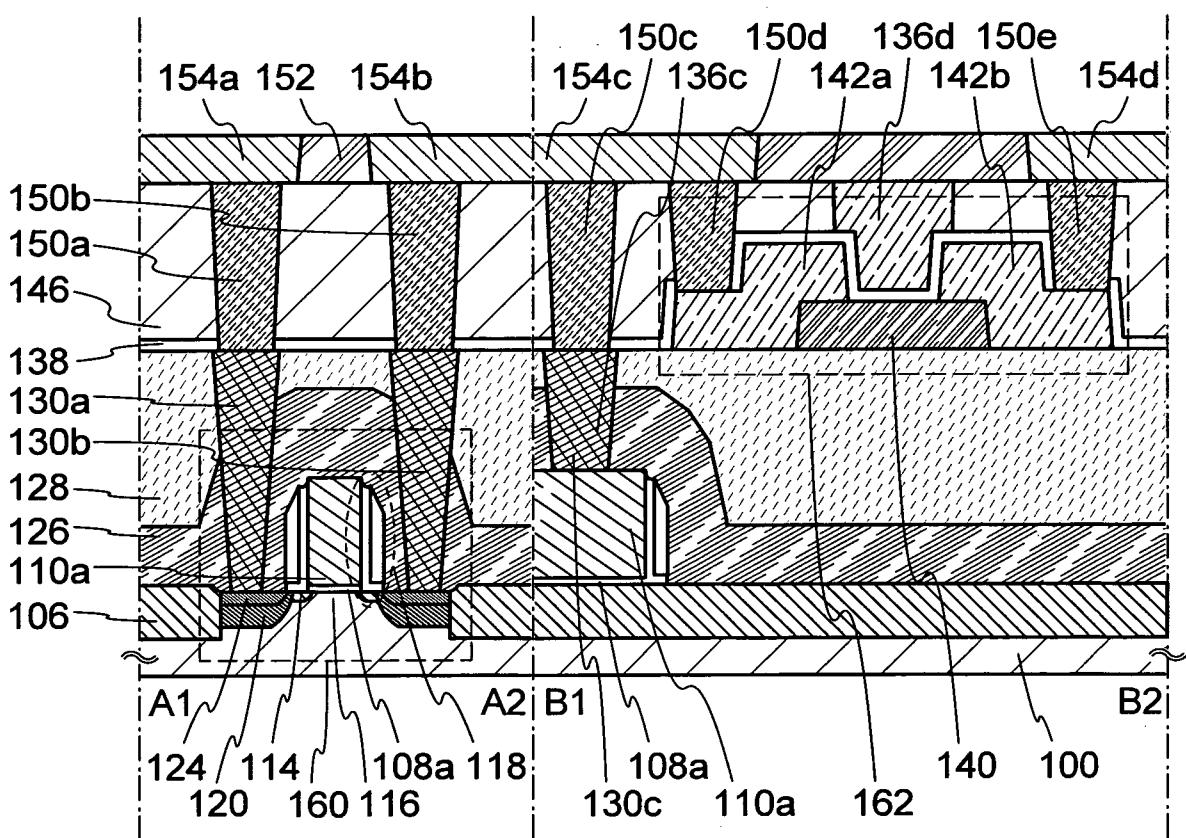

25 FIGS. 4A to 4G are cross-sectional views each for explaining a manufacturing step of a semiconductor device;

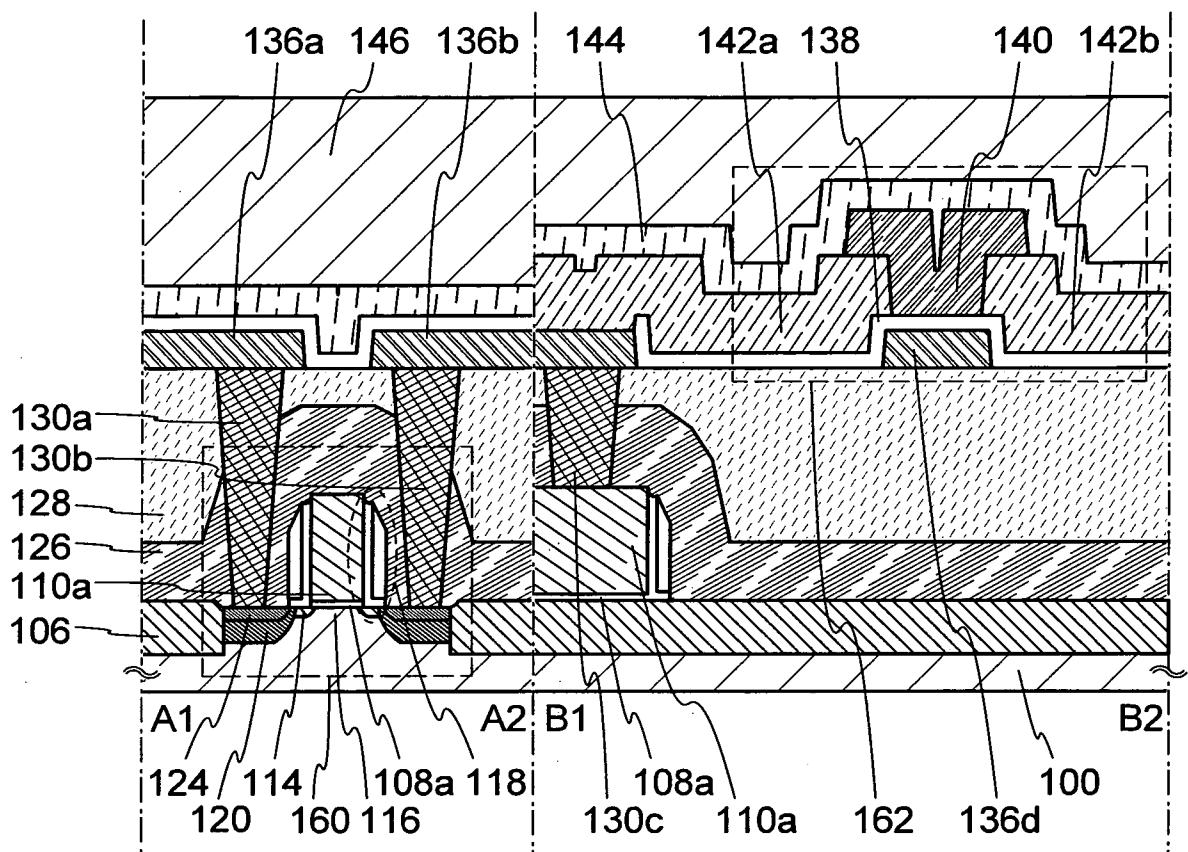

FIGS. 5A to 5D are cross-sectional views each for explaining a manufacturing step of a semiconductor device;

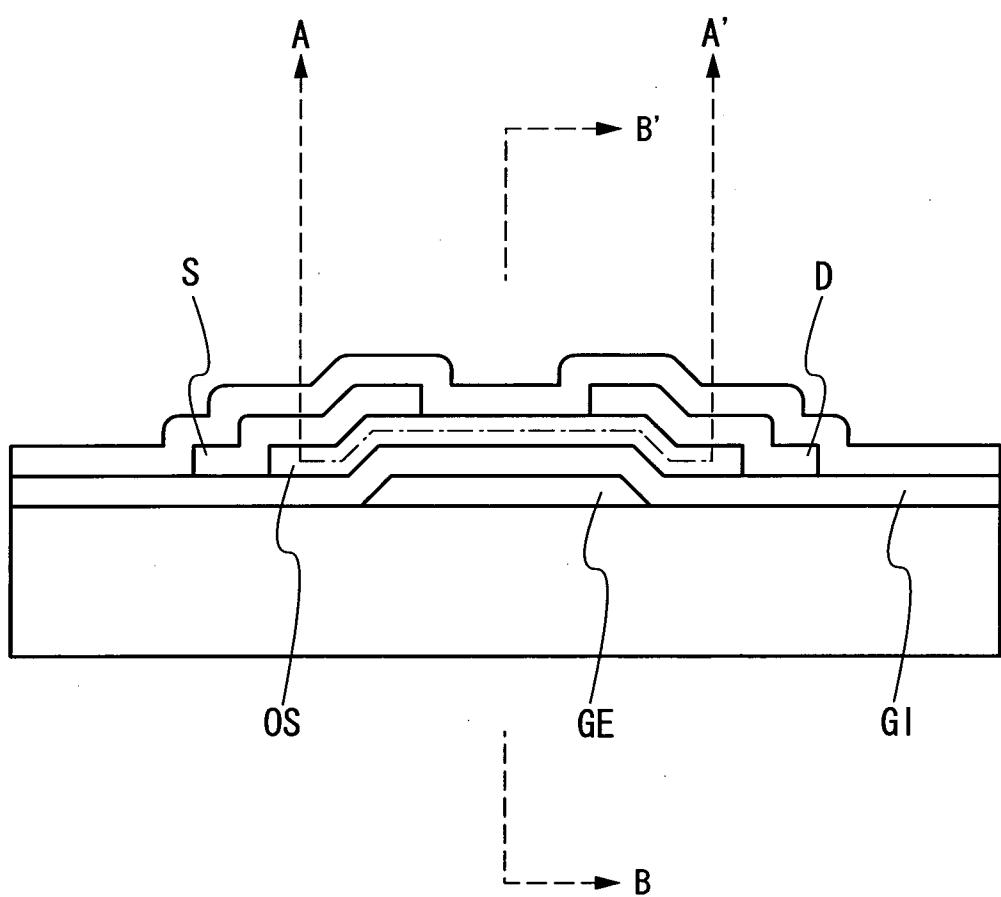

FIG. 6 is a cross-sectional view of a transistor formed using an oxide semiconductor;

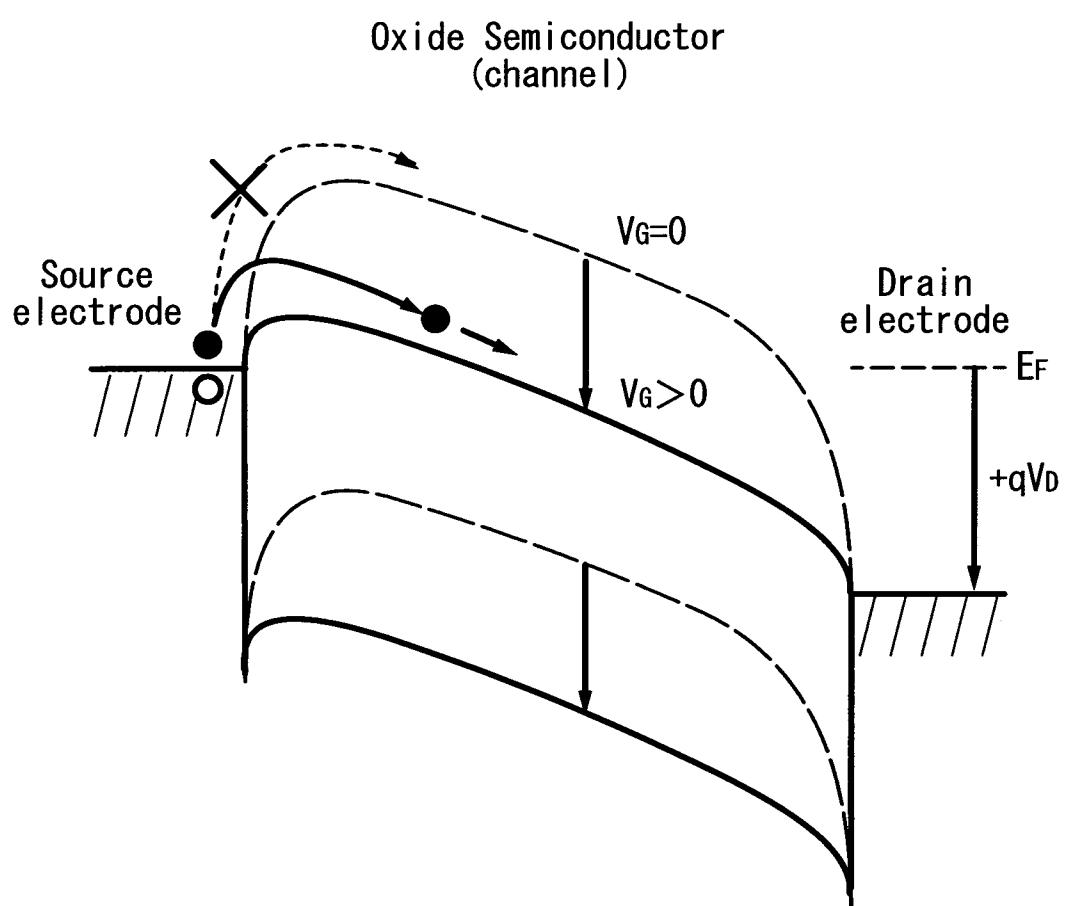

30 FIGS. 7 is an energy band diagram (schematic diagram) along an A-A' section in FIG. 6;

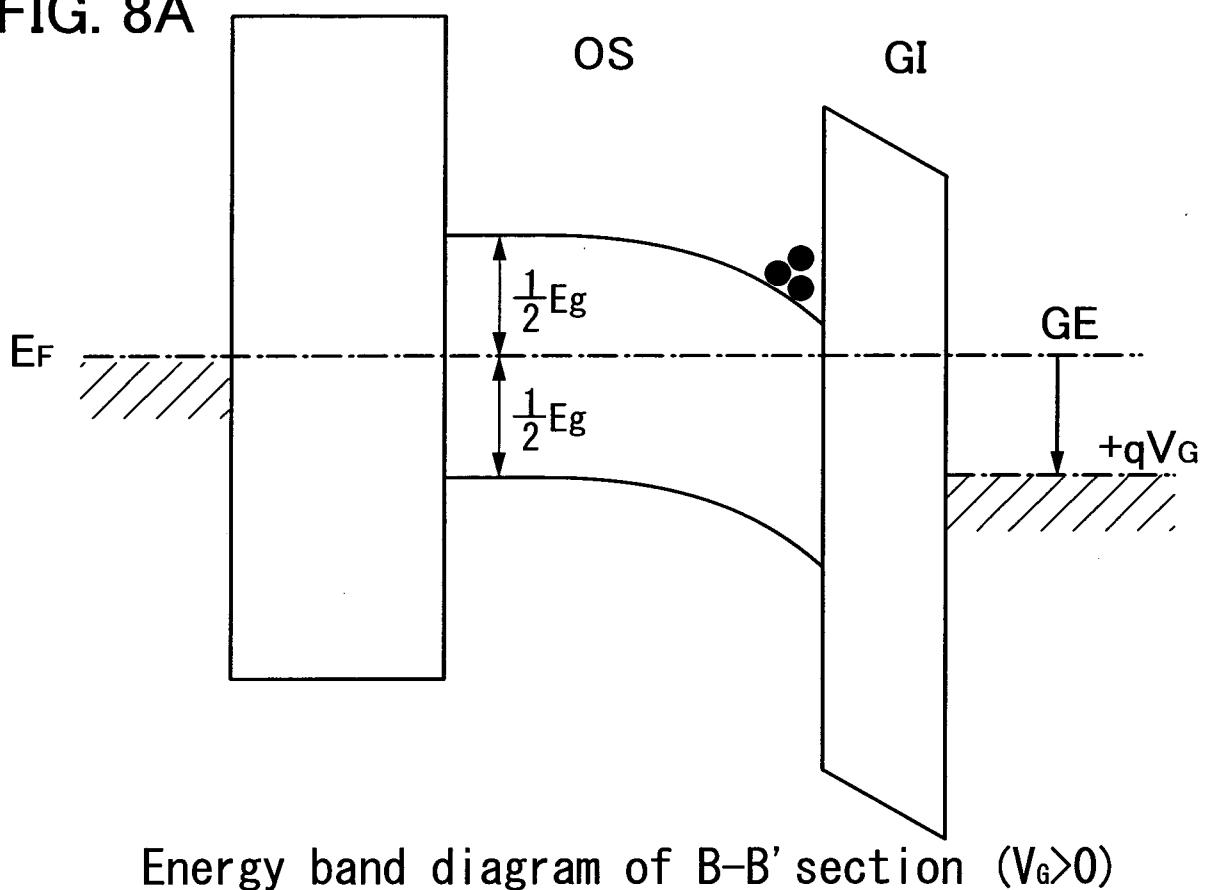

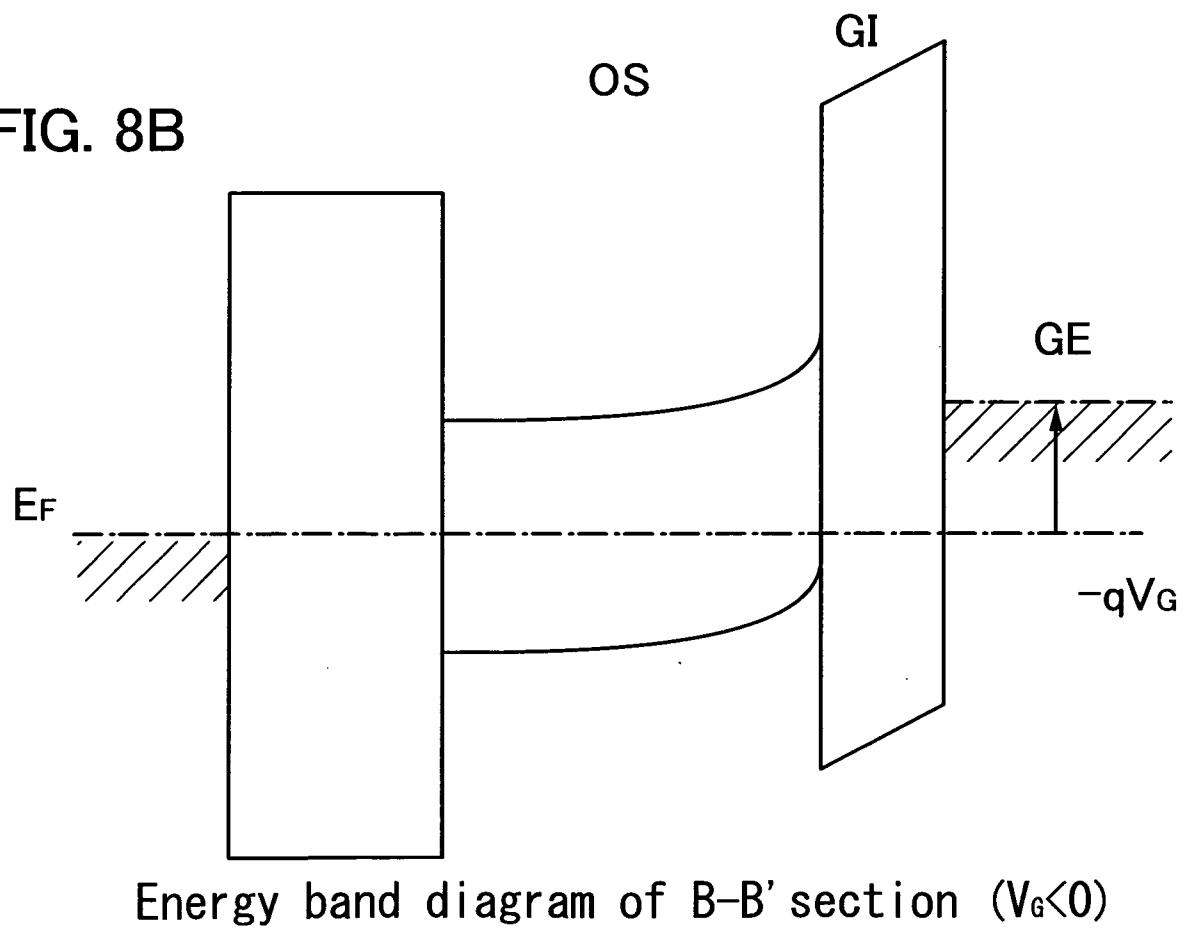

FIG. 8A is a diagram illustrating a state where a positive voltage ( $V_G > 0$ ) is applied to a gate electrode (GE), and FIG. 8B is a diagram illustrating a state where a negative potential ( $V_G < 0$ ) is applied to the gate electrode (GE);

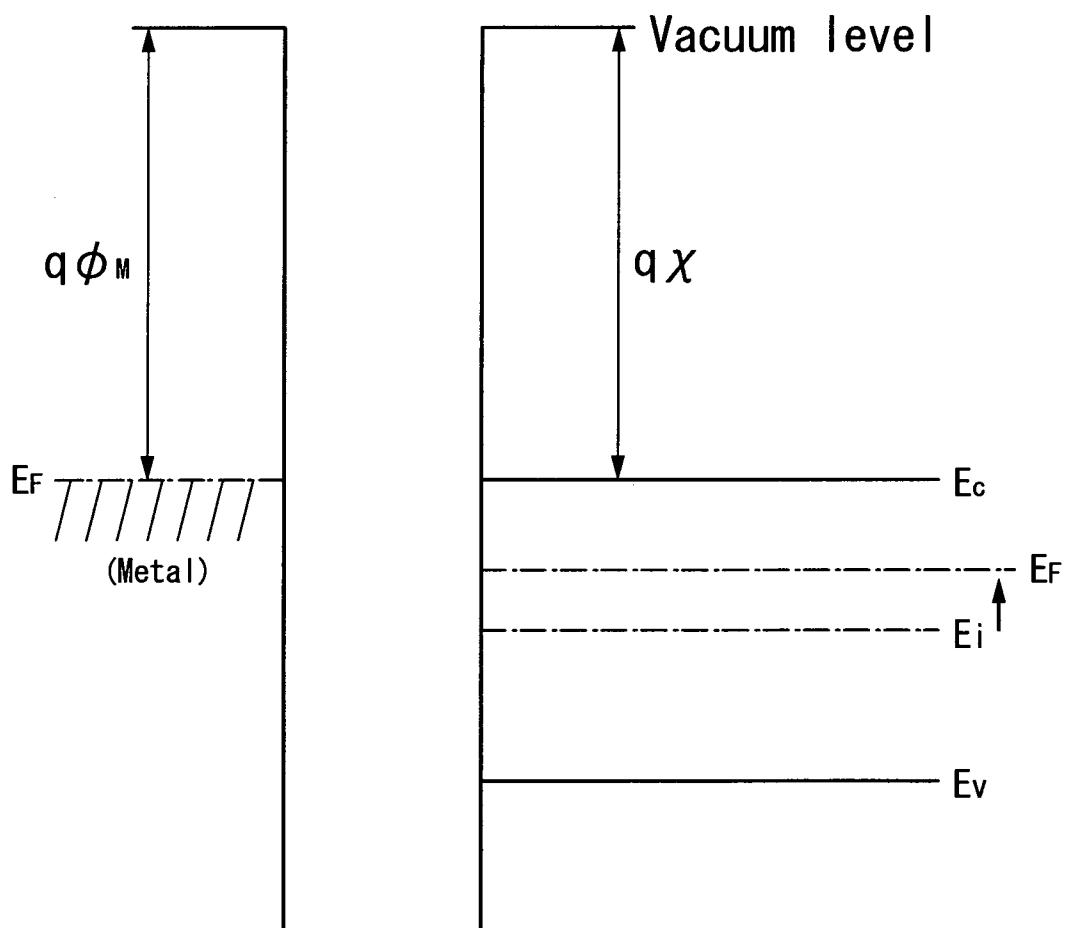

5 FIG. 9 is a diagram illustrating the relationship between the vacuum level and the electron affinity ( $\chi$ ) of an oxide semiconductor;

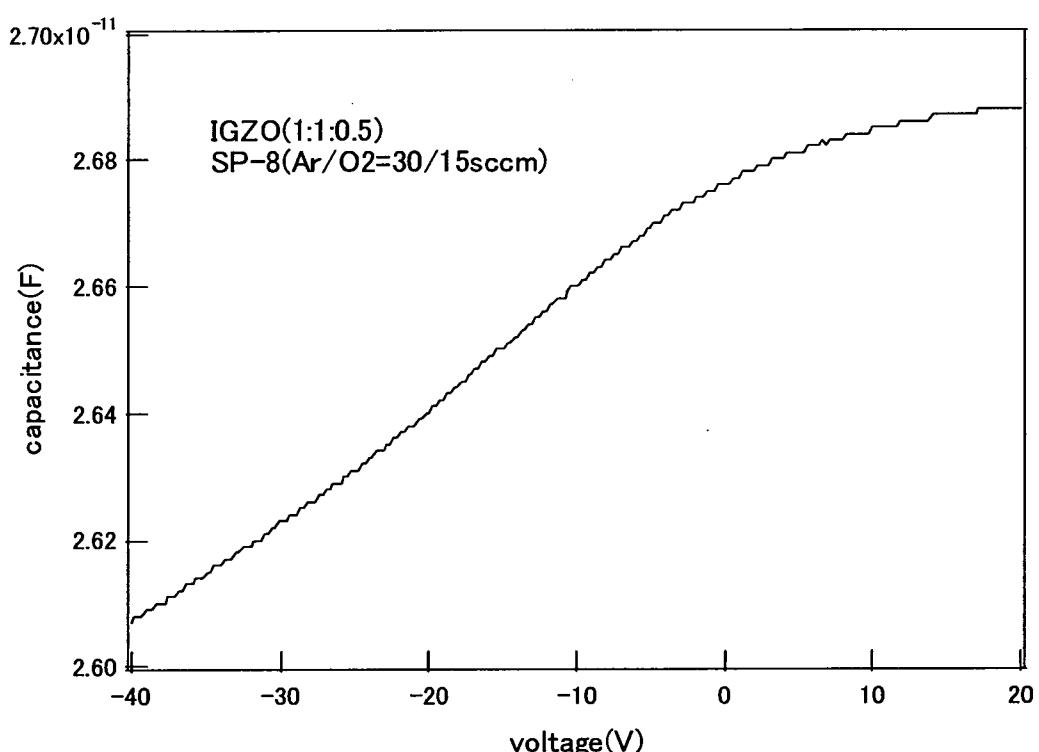

FIG. 10 is a graph illustrating a C-V characteristic;

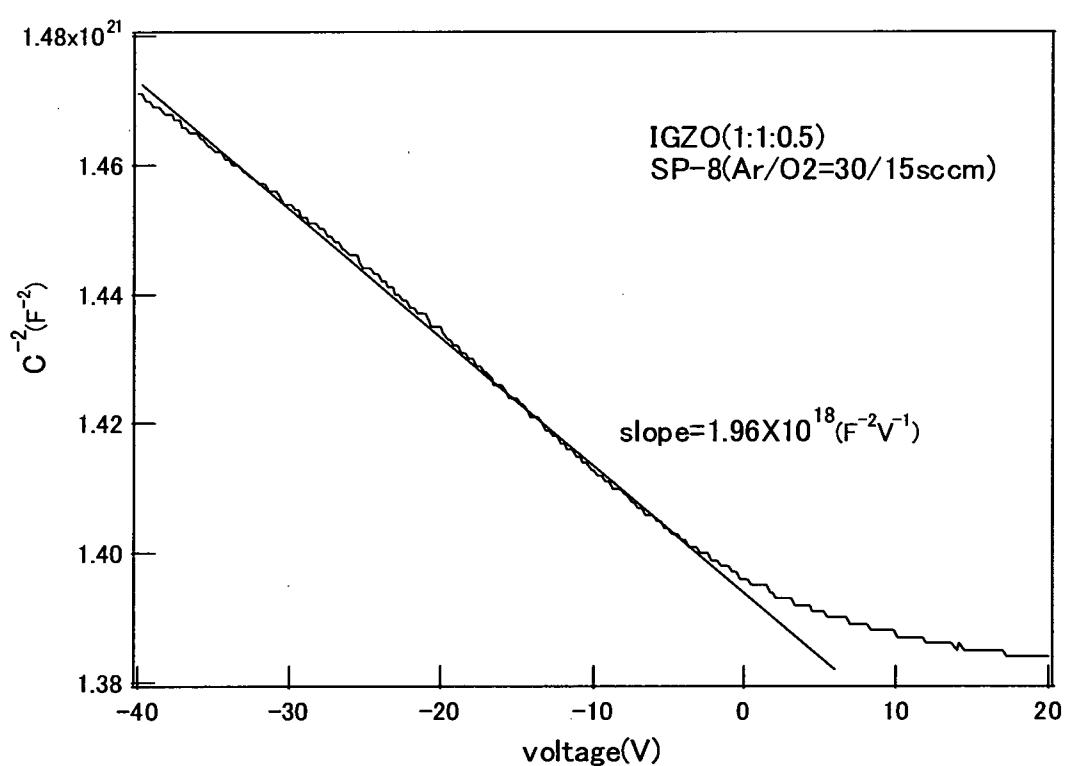

FIG. 11 is a graph illustrating a relation between  $V_g$  and  $(1/C)^2$ ;

FIG. 12 is a cross-sectional view for describing a semiconductor device;

10 FIGS. 13A and 13B are cross-sectional views for describing a semiconductor device;

FIGS. 14A and 14B are cross-sectional views for describing a semiconductor device;

FIGS. 15A and 15B are cross-sectional views for describing a semiconductor device;

15 FIG. 16 is a circuit diagram for describing a memory element;

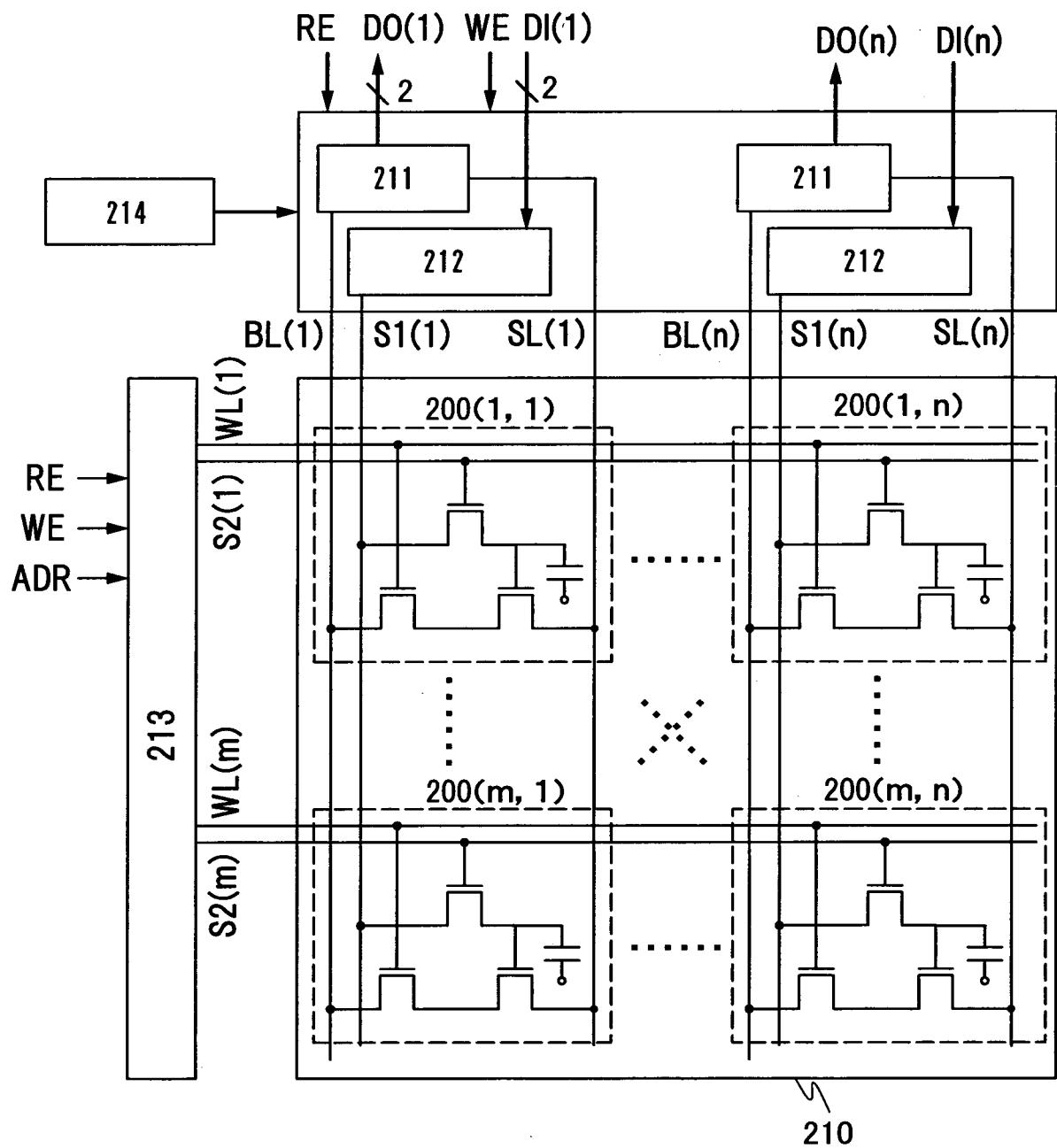

FIG. 17 is a circuit diagram for describing a semiconductor device;

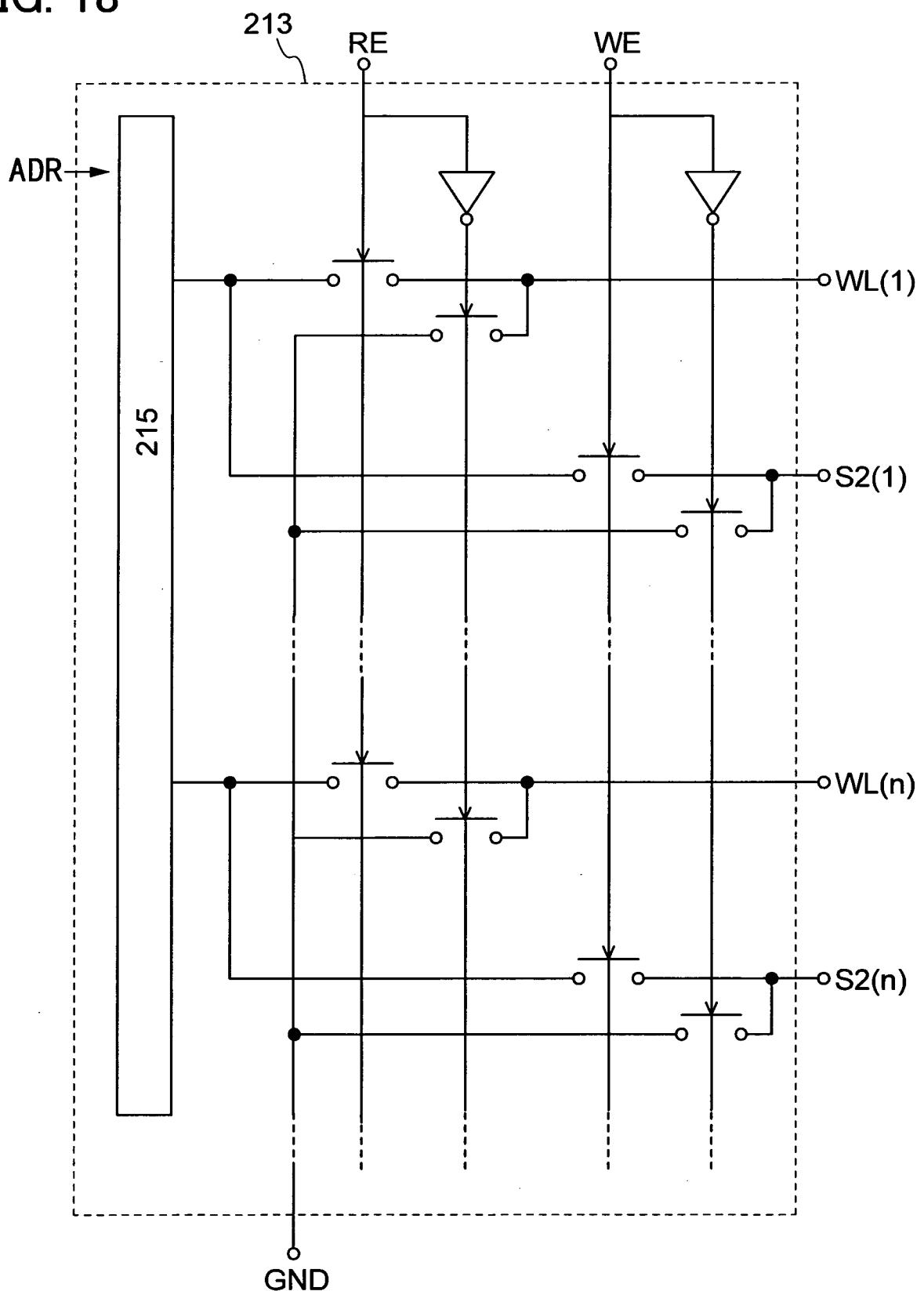

FIG. 18 is a circuit diagram for describing a driver circuit;

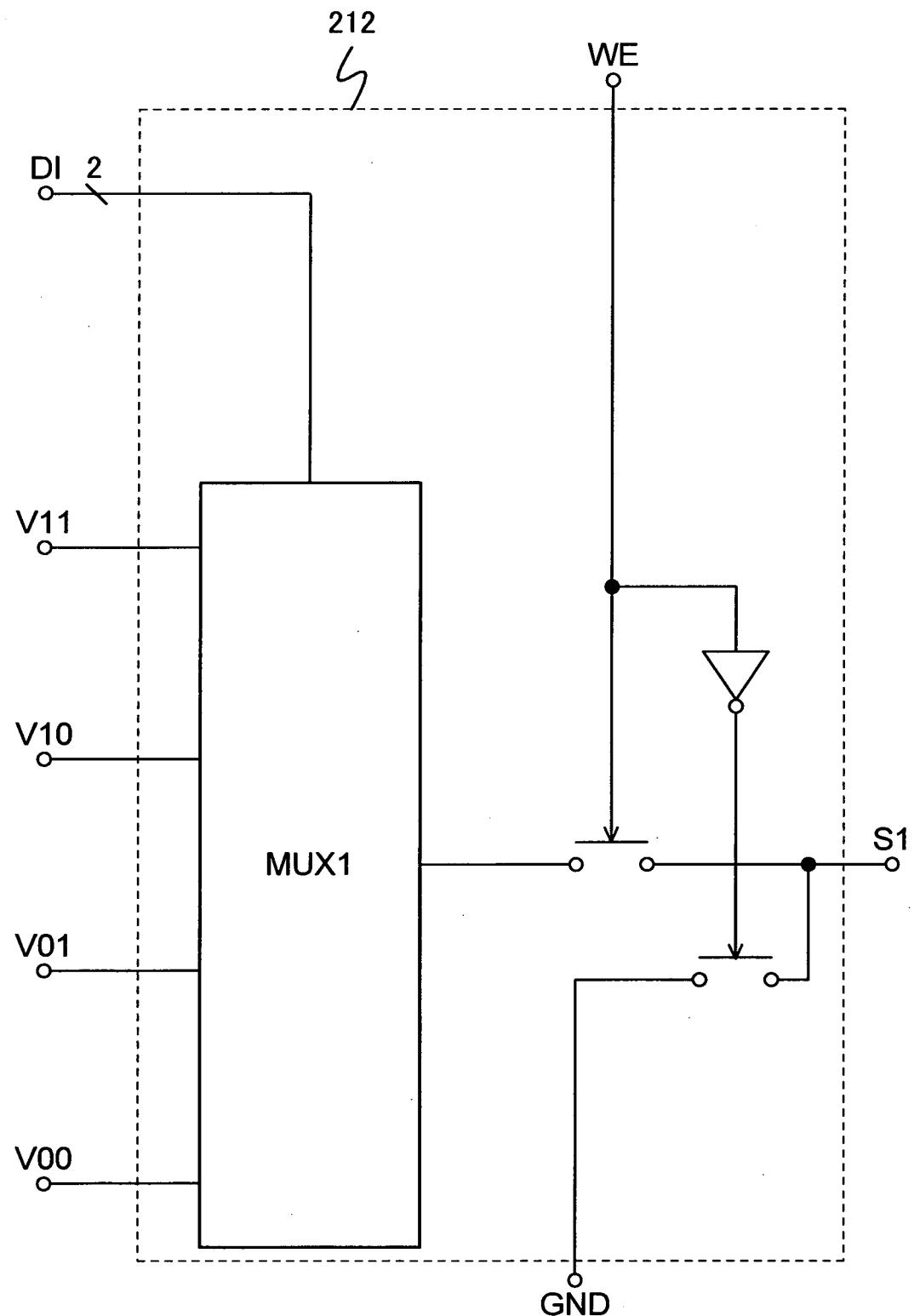

FIG. 19 is a circuit diagram for describing a driver circuit;

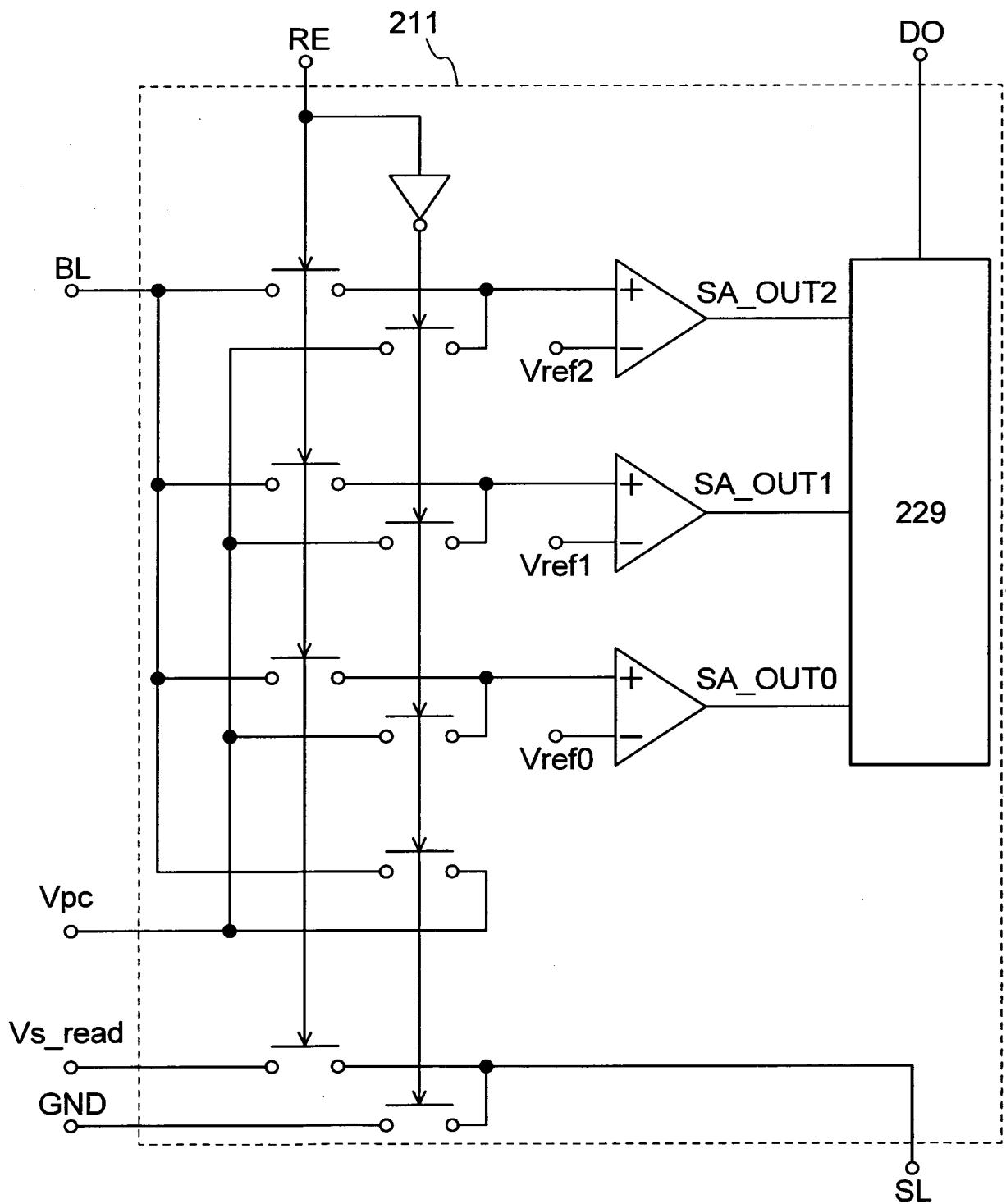

FIG. 20 is a circuit diagram for describing a reading circuit;

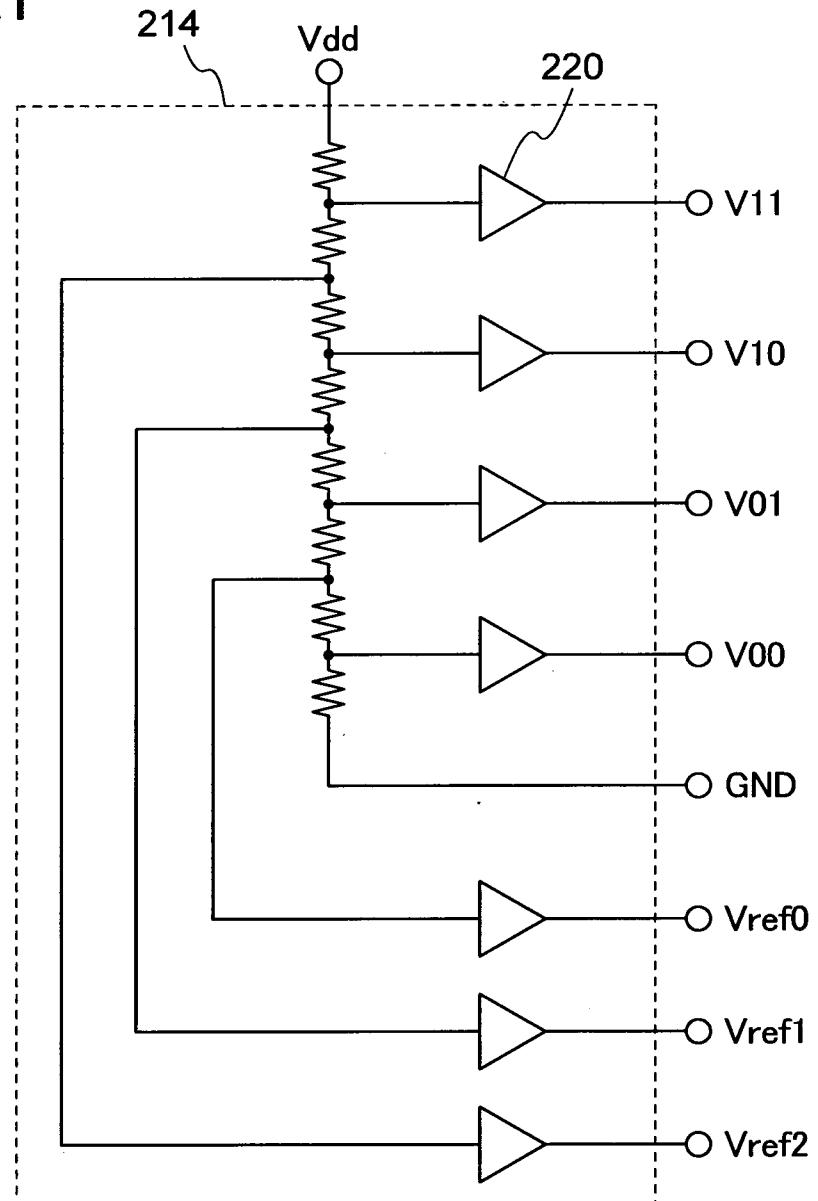

20 FIG. 21 is a circuit diagram for describing a potential generating circuit;

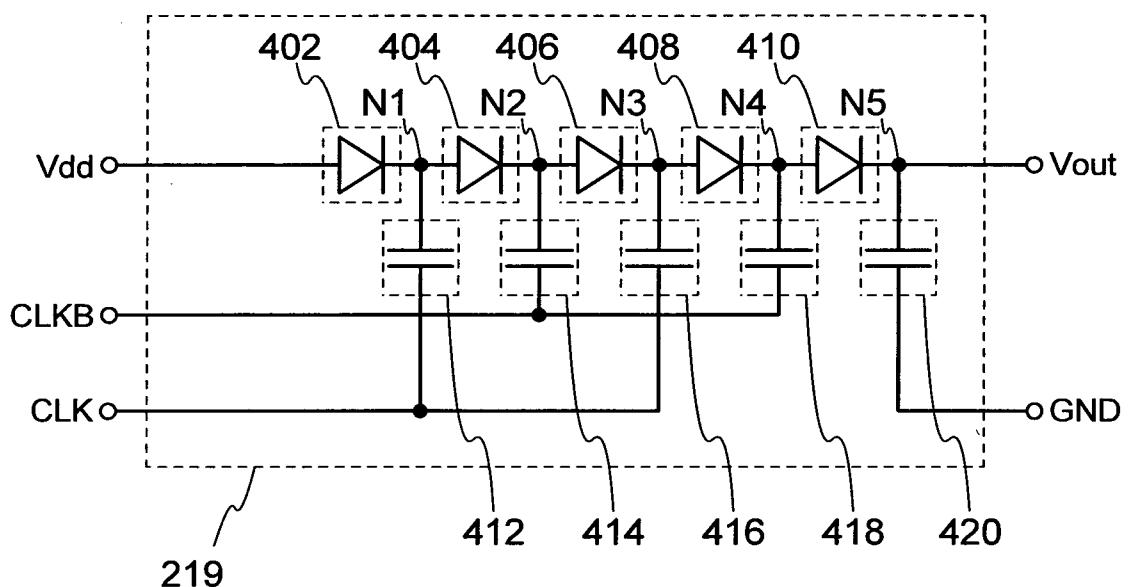

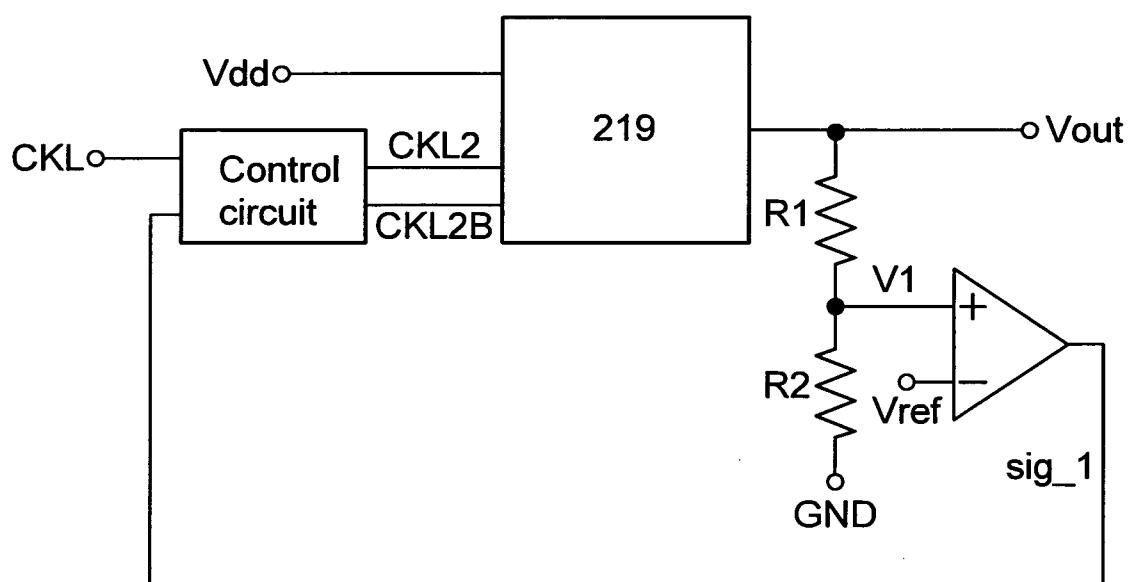

FIGS. 22A and 22B are circuit diagrams for describing a boosting circuit;

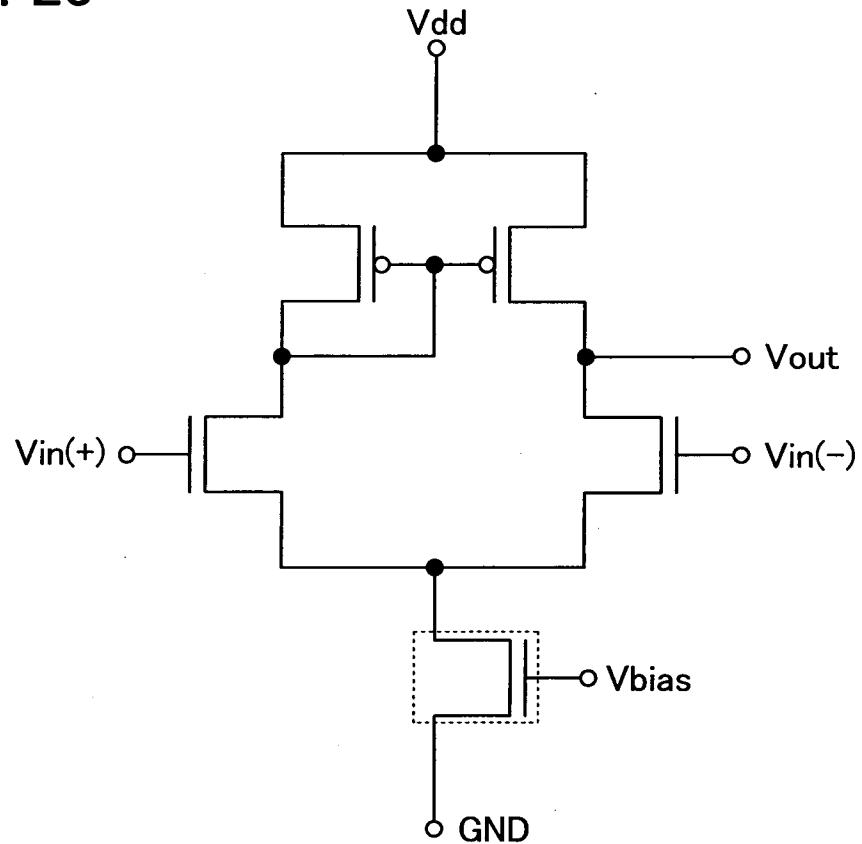

FIG. 23 is a circuit diagram for describing a differential sense amplifier circuit;

FIG. 24 is a circuit diagram for describing a latch sense amplifier;

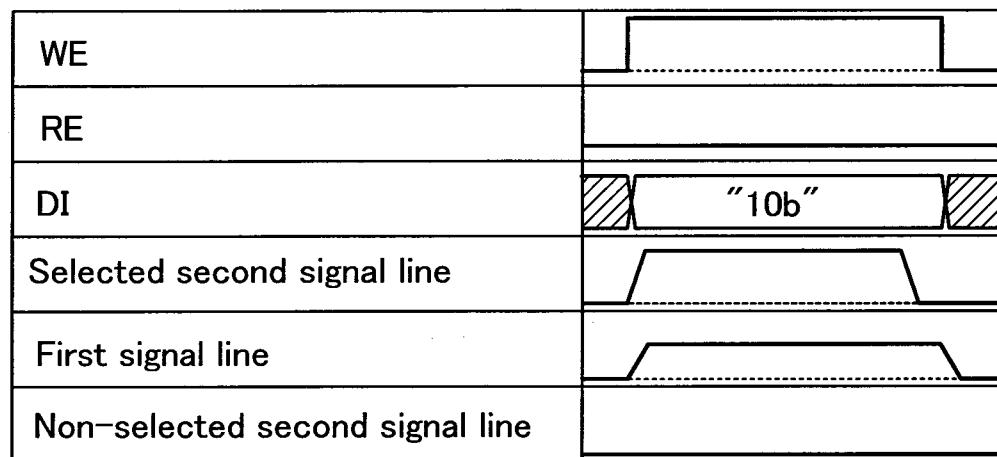

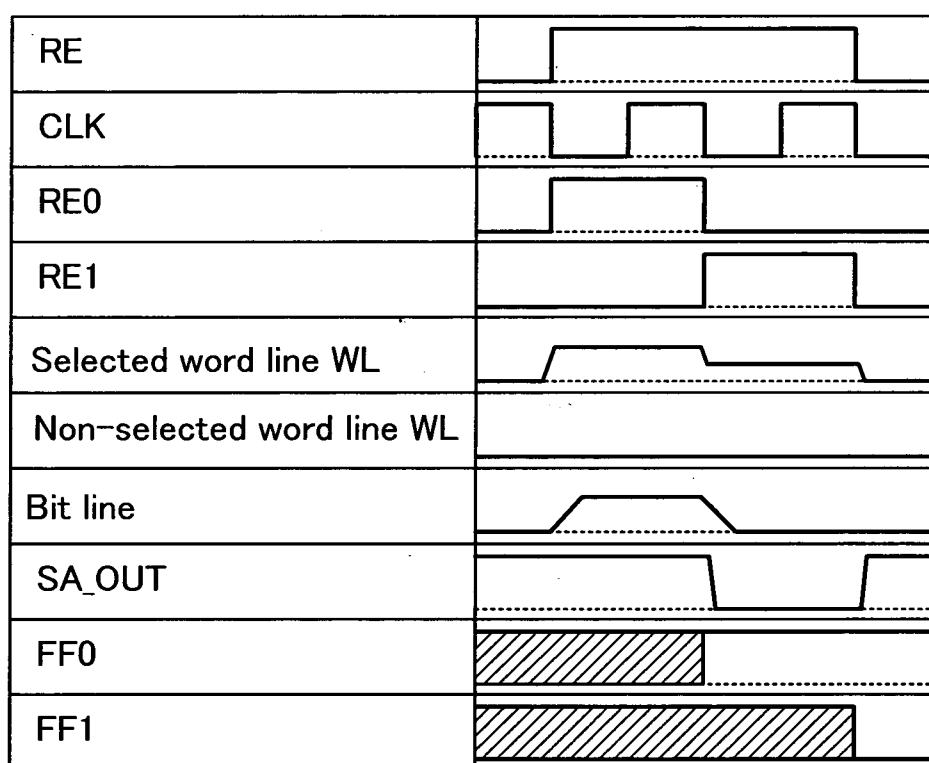

FIGS. 25A and 25B are timing charts for explaining an operation;

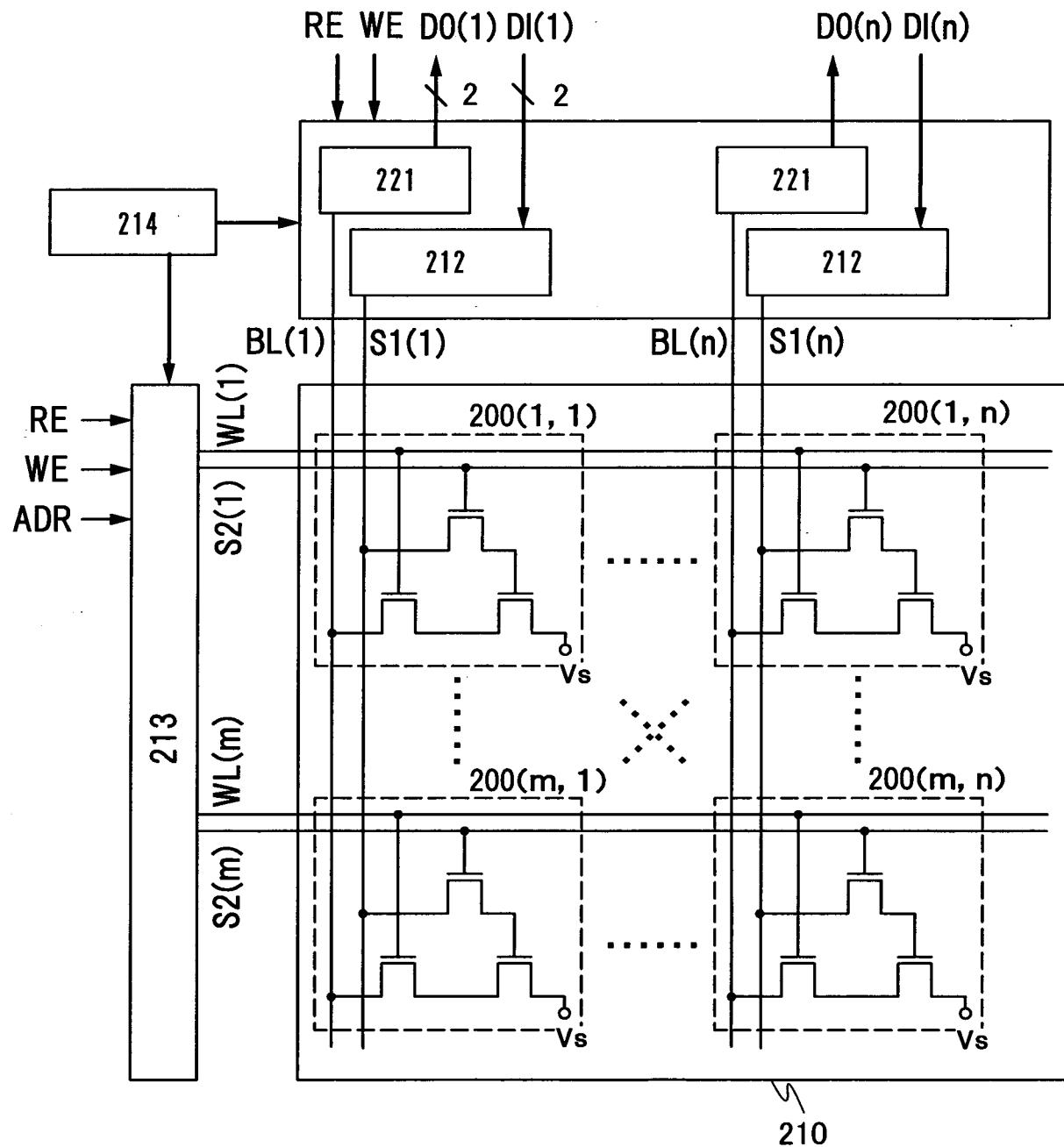

25 FIG. 26 is a circuit diagram for describing a semiconductor device;

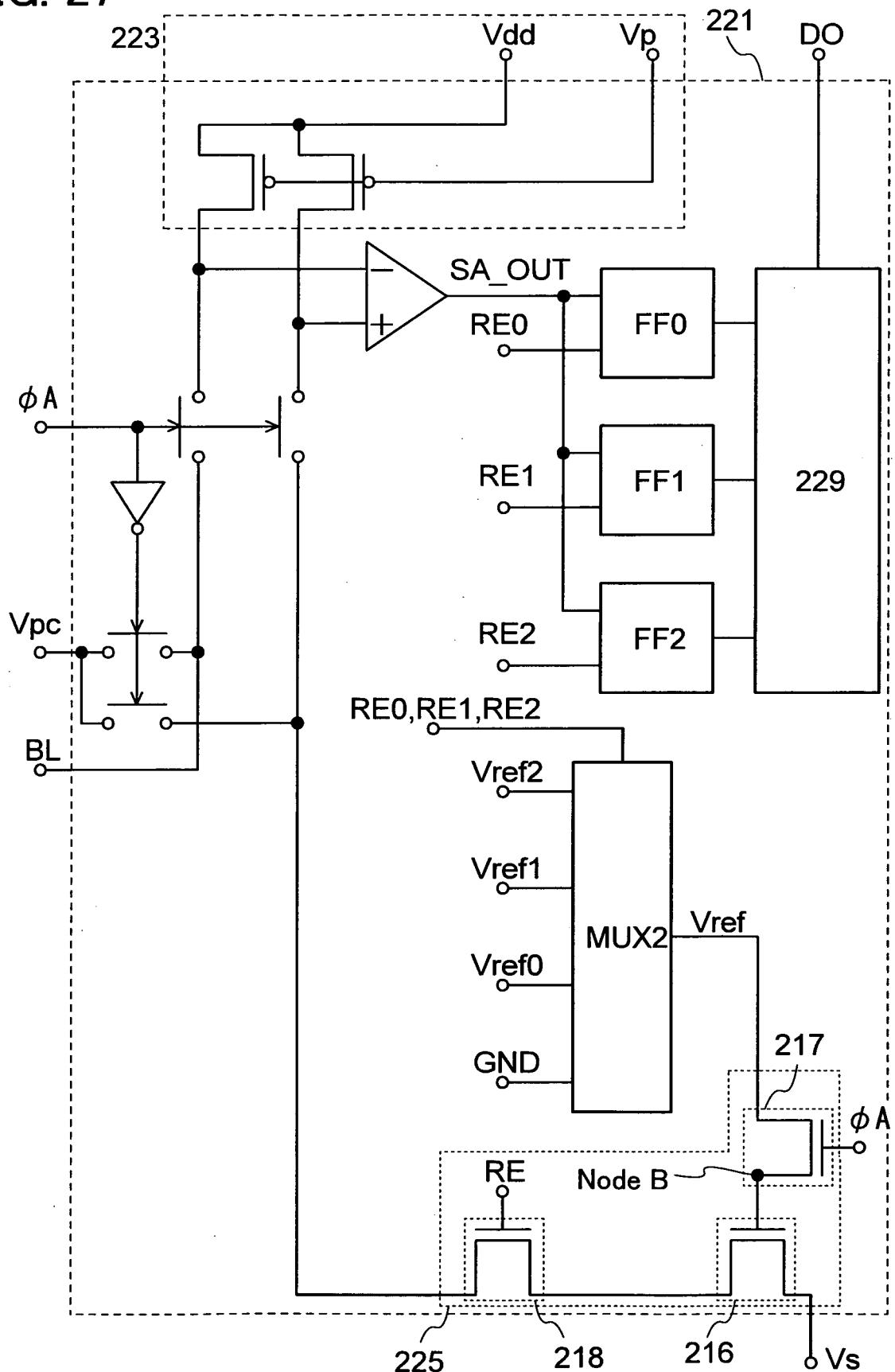

FIG. 27 is a circuit diagram for describing a reading circuit;

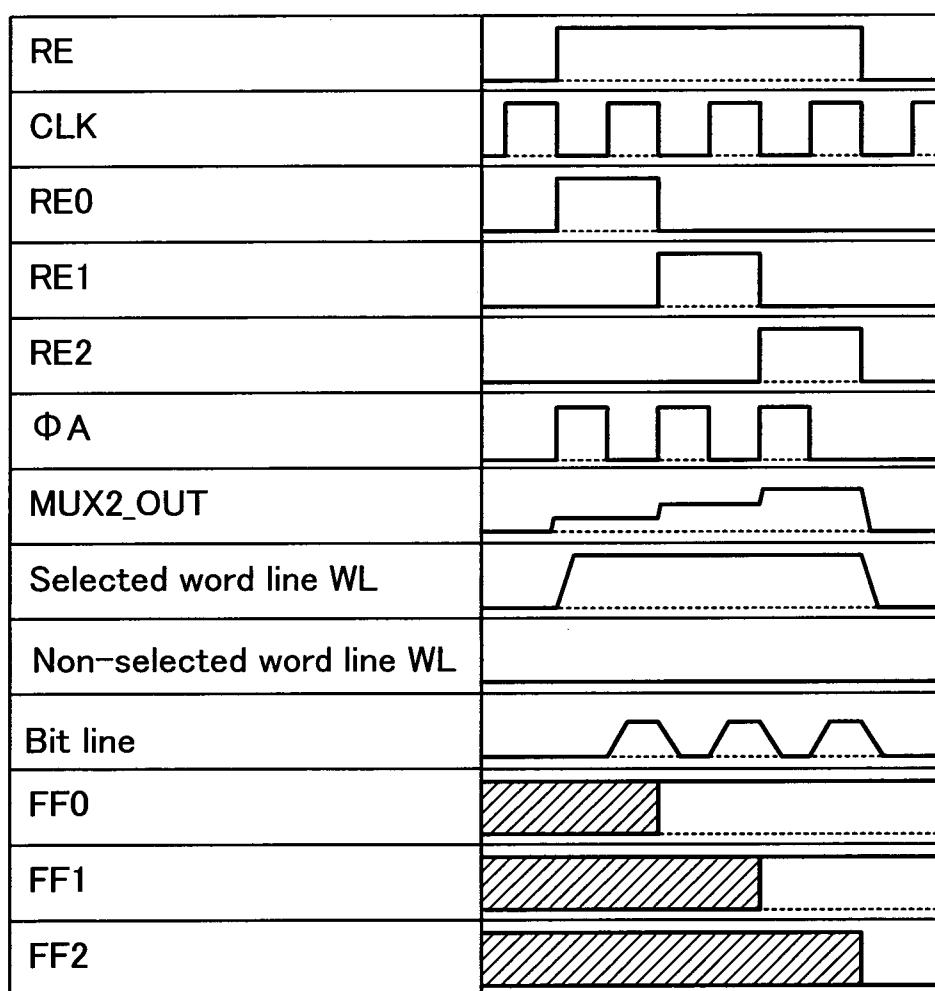

FIG. 28 is a timing chart for explaining an operation;

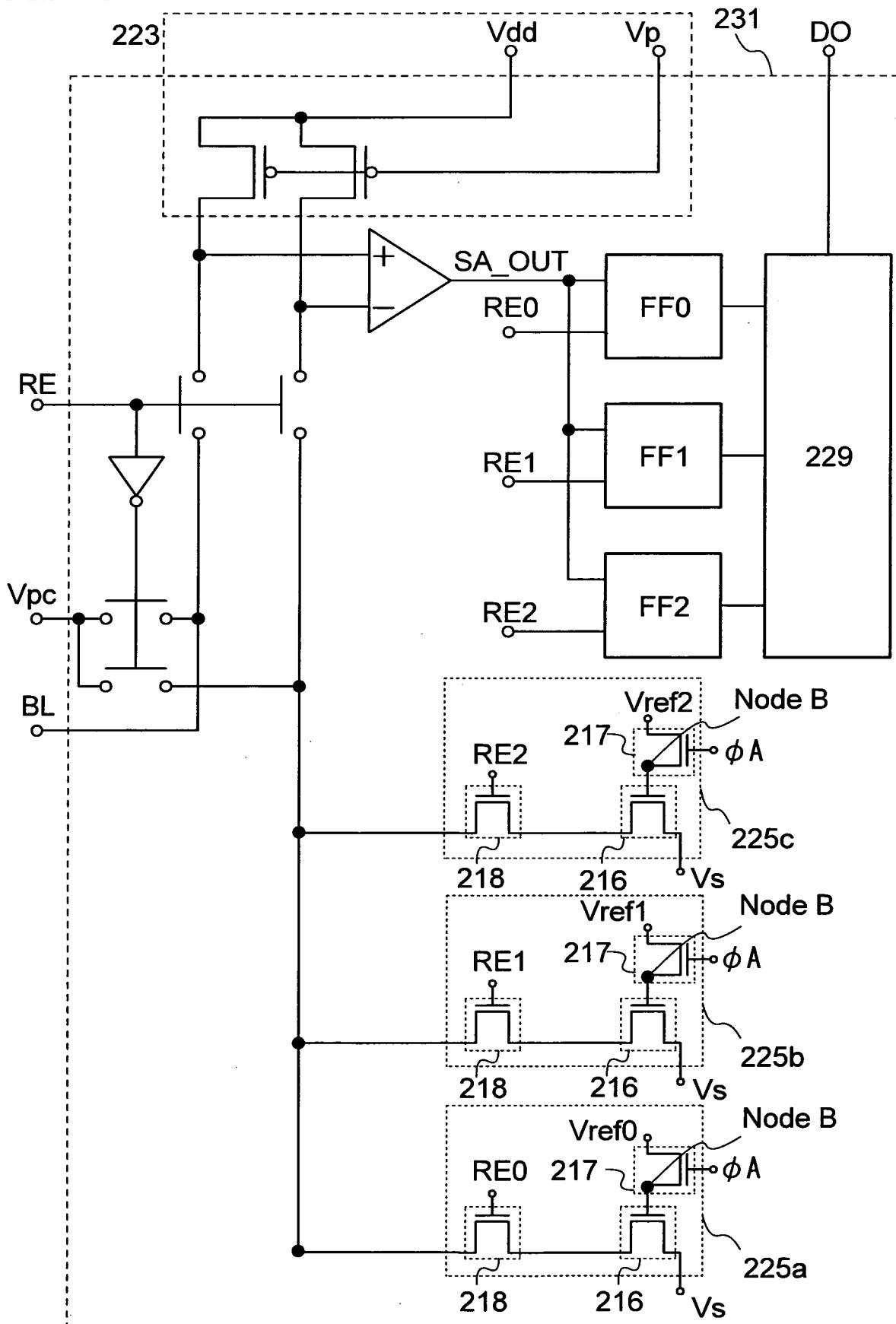

FIG. 29 is a circuit diagram for describing a reading circuit;

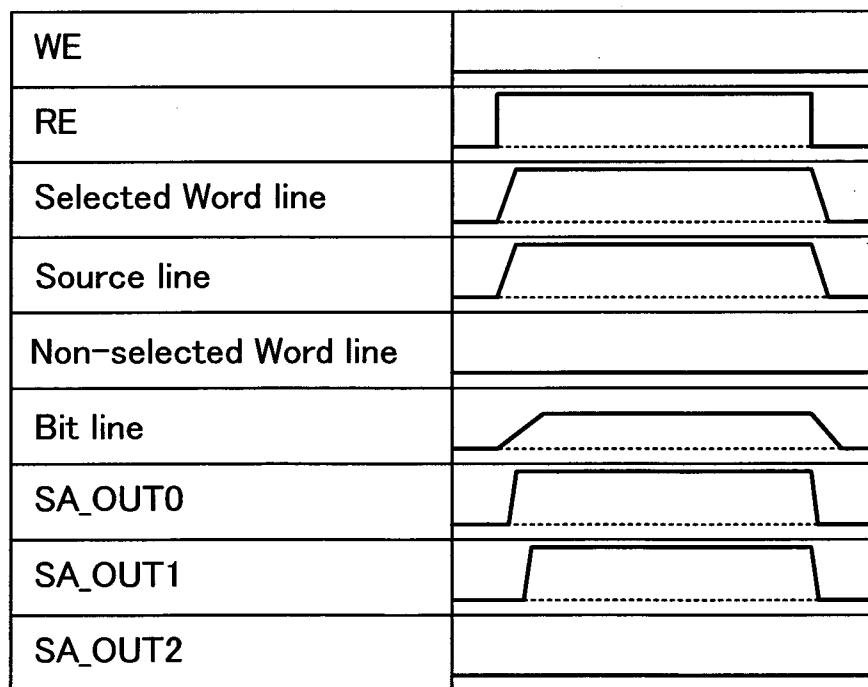

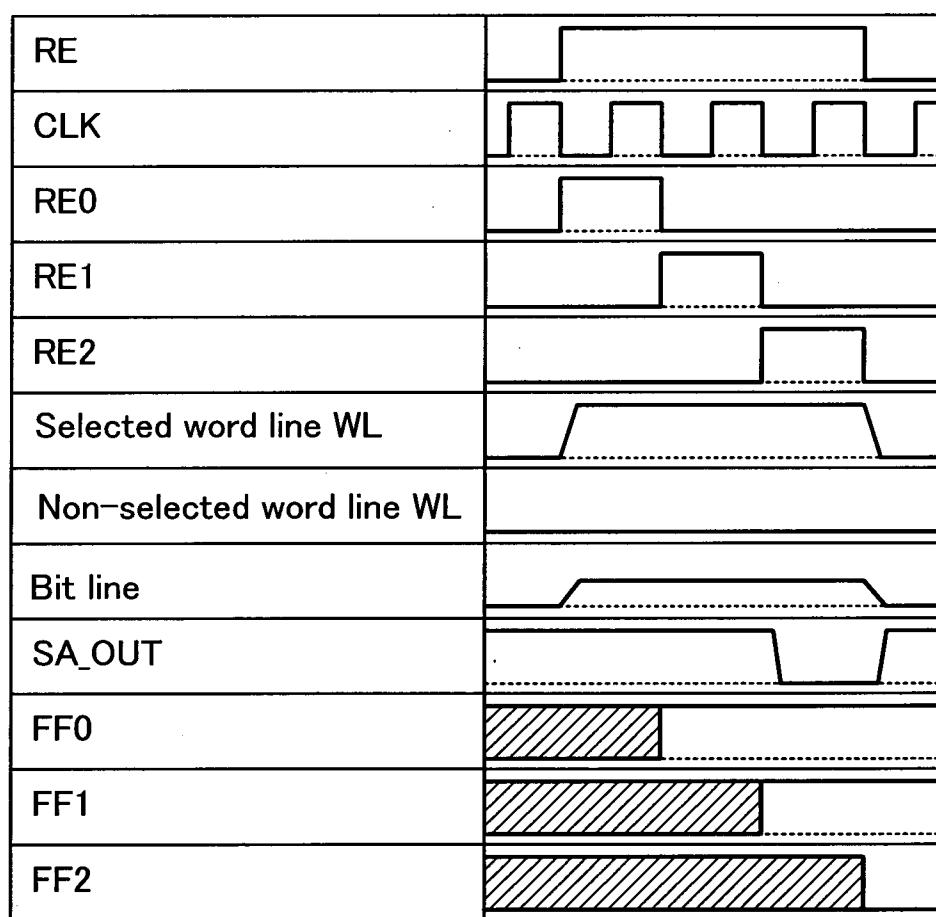

FIG. 30 is a timing chart for explaining an operation;

30 FIG. 31 is a circuit diagram for describing a memory element;

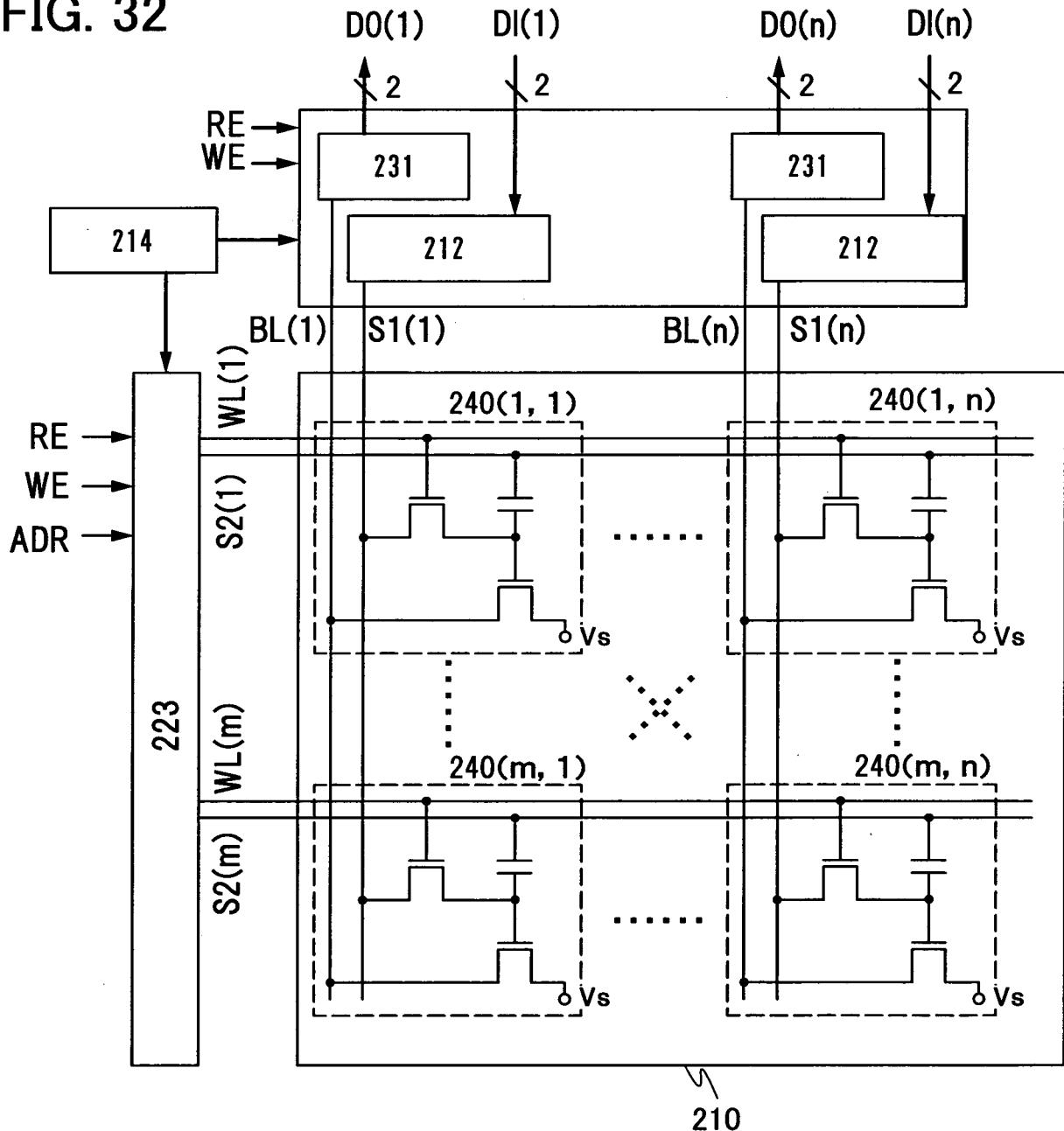

FIG. 32 is a circuit diagram for describing a semiconductor device;

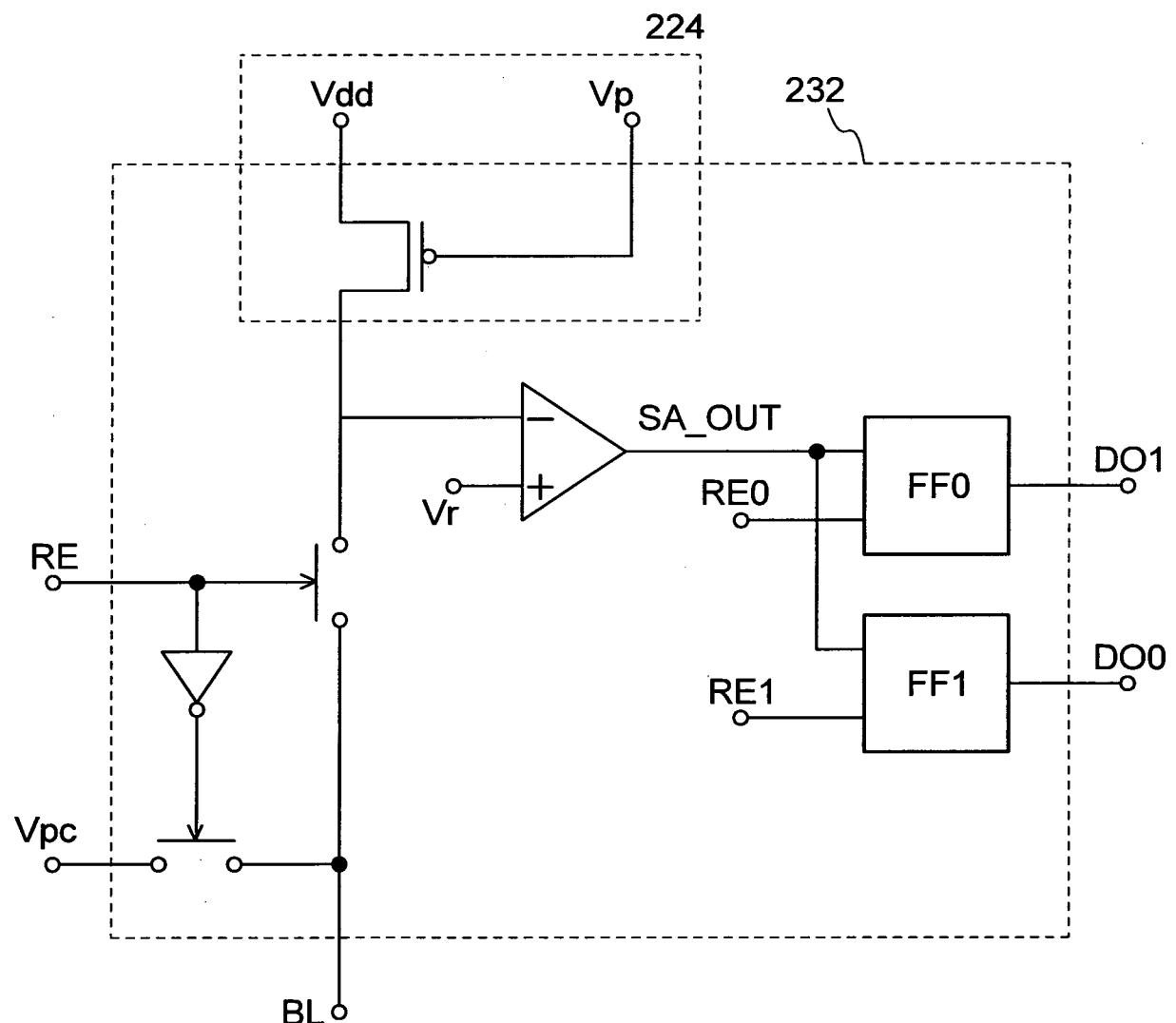

FIG. 33 is a circuit diagram for describing a reading circuit;

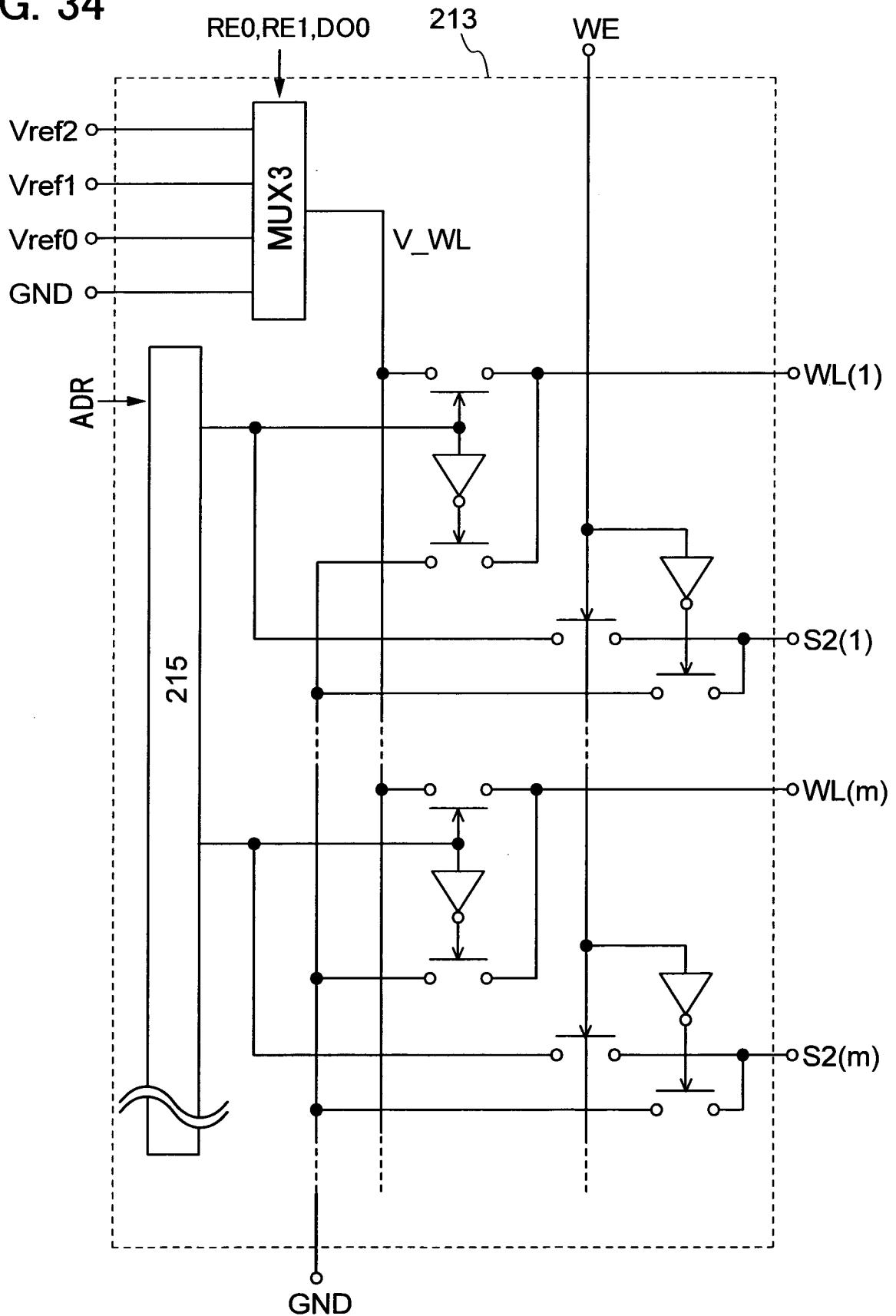

FIG. 34 is a circuit diagram for describing a driver circuit;

FIG. 35 is a timing chart for explaining an operation;

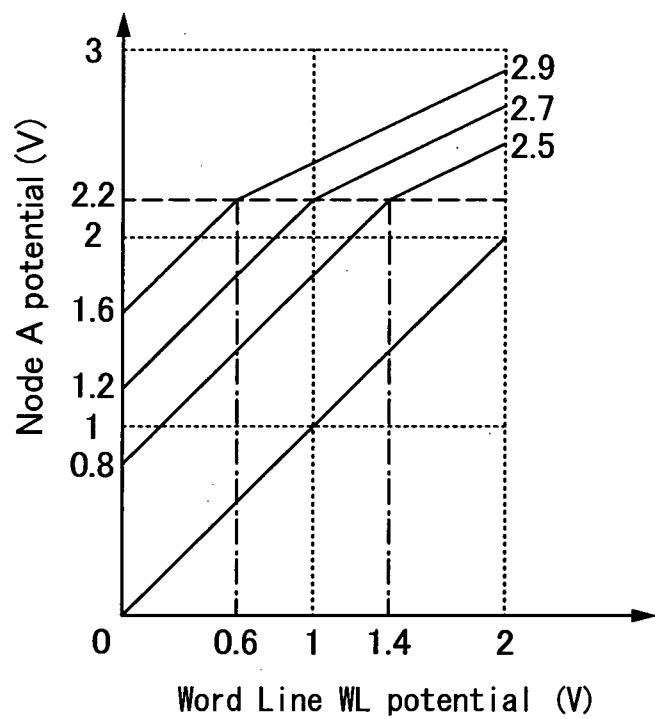

FIG. 36 is a graph illustrating a relation between a potential of a node A and a

5 potential of a word line; and

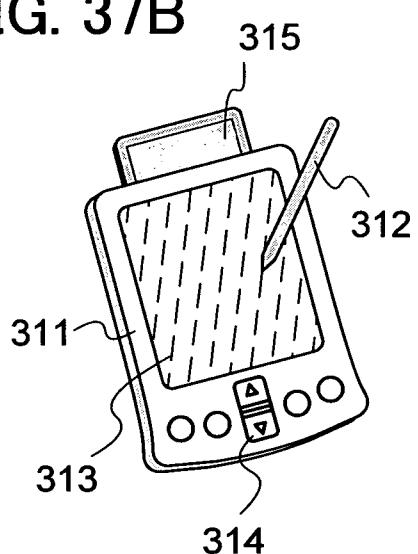

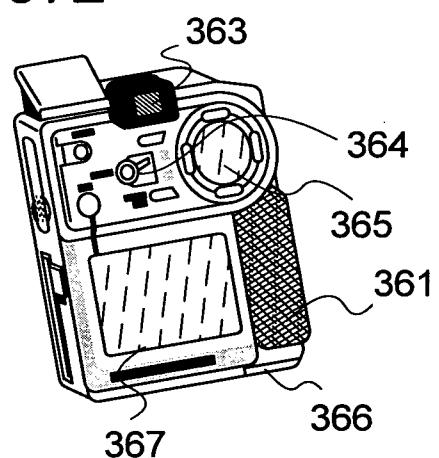

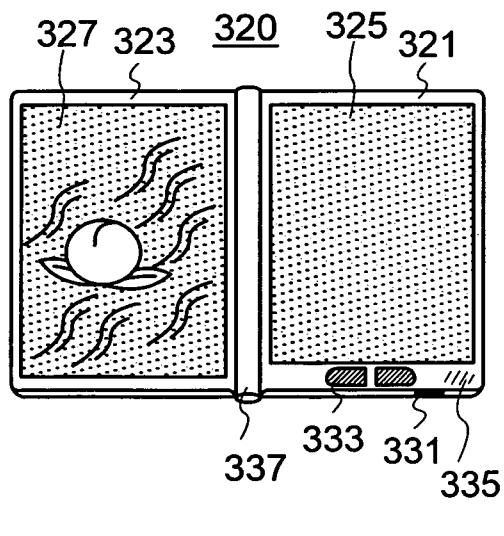

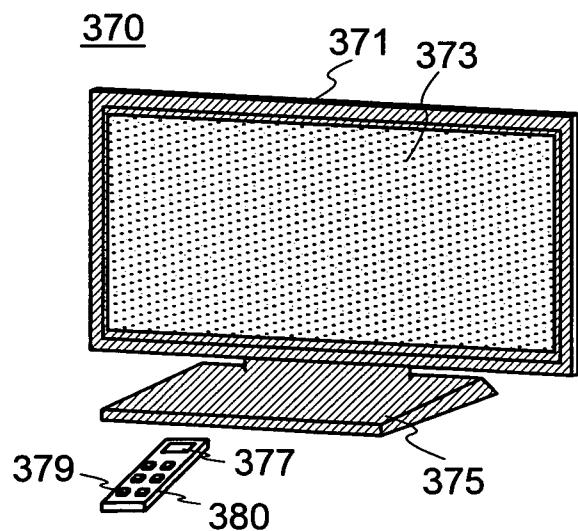

FIGS. 37A to 37F are diagrams each describing an electronic appliance.

## BEST MODE FOR CARRYING OUT THE INVENTION

[0036]

10 Hereinafter, examples of embodiments of the present invention will be described with reference to the drawings. Note that the present invention is not limited to the following descriptions and it will be readily appreciated by those skilled in the art that modes and details can be modified in various ways without departing from the spirit and the scope of the present invention. Therefore, the invention should not be 15 interpreted as being limited to the description of the following embodiment modes.

[0037]

Note that for the easy understanding, the position, size, range and the like of each component illustrated in the drawings and the like are not actual ones in some cases. Therefore, the present invention is not limited to the position, size, and range 20 and the like disclosed in the drawings and the like.

[0038]

Note that in this specification, ordinal numbers such as "first", "second", and "third" are used in order to avoid confusion among components, and the terms do not limit the components numerically.

25 [0039]

(Embodiment 1)

In this embodiment, structures and manufacturing methods of semiconductor devices according to one embodiment of the disclosed invention are described with reference to FIG. 1, FIGS. 2A and 2B, FIGS. 3A to 3H, FIGS. 4A to 4G, FIGS. 5A to 5D, 30 FIG. 6, FIGS. 7A and 7B, FIGS. 8A and 8B, FIG. 9, FIG. 10, FIG. 11, FIG. 12, FIGS. 13A and 13B, FIGS. 14A and 14B, and FIGS. 15A and 15B.

[0040]

<Circuit Configuration of Semiconductor Device>

FIG. 1 illustrates an example of a circuit configuration of a semiconductor device. The semiconductor device includes a transistor 160 which uses a material other than an oxide semiconductor and a transistor 162 which uses an oxide semiconductor. 5 Note that a mark "OS" is added to the transistor 162 in FIG. 1 to show that the transistor 162 uses an oxide semiconductor.

[0041]

Here, a gate electrode of the transistor 160 is electrically connected to one of a source electrode and a drain electrode of the transistor 162. A first wiring (which is 10 denoted as "1st Line" and also called a source line) and a second wiring (which is denoted as "2nd Line" and also called a bit line) are electrically connected to a source electrode of the transistor 160 and a drain electrode of the transistor 160, respectively. Further, a third wiring (which is denoted as "3rd Line" and also called a first signal line) 15 and a fourth wiring (which is denoted as "4th Line" and also called a second signal line) are electrically connected to the other of the source electrode and the drain electrode of the transistor 162 and to a gate electrode of the transistor 162, respectively.

[0042]

The transistor 160 which uses a material other than an oxide semiconductor can 20 operate at sufficiently high speed; thus, can read stored contents and the like at high speed. In addition, off-state current is extremely small in the transistor 162 which uses an oxide semiconductor. Therefore, when the transistor 162 is turned off, a potential of the gate electrode of the transistor 160 can be held for an extremely long time.

[0043]

The advantage that the potential of the gate electrode can be held for an 25 extremely long time enables writing, holding, and reading of information to be performed as described below.

[0044]

Description is made on writing and holding of information first. First, a potential of the fourth wiring is set to a potential putting the transistor 162 in an on state. 30 Accordingly, a potential of the third wiring is applied to the gate electrode of the transistor 160 (writing data operation). After that, the potential of the fourth wiring is

set to a potential putting the transistor 162 in an off state; accordingly, the potential of the gate electrode of the transistor 160 is held (holding data operation).

[0045]

Since the off-state current of the transistor 162 is extremely small, the potential of the gate electrode of the transistor 160 is held for a long time. For example, when the potential of the gate electrode of the transistor 160 is a potential putting the transistor 160 in an on state, the on state of the transistor 160 is kept for a long time. When the potential of the gate electrode of the transistor 160 is a potential to make the transistor 160 be in an off state, the off state of the transistor 160 is kept for a long time.

10 [0046]

Next, description is made on the reading of information operation. When an on state or an off state of the transistor 160 is kept as described above and a predetermined potential (a low potential) is applied to the first wiring, the value of a potential of the second wiring varies depending on a state of the transistor 160 which is an on state or an off state. For example, when the transistor 160 is in an on state, the potential of the second wiring is lowered by being affected by the potential of the first wiring. On the other hand, when the transistor 160 is in an off state, the potential of the second wiring is not changed.

[0047]

20 In this manner, by comparing the potential of the first wiring with the potential of the second wiring in a state where information is held, the information can be read.

[0048]

Then, description is made on rewriting of information. Rewriting of information is performed in a manner similar to that of the writing and holding of information which are described above. That is, the potential of the fourth wiring is set to a potential putting the transistor 162 in an on state, whereby the transistor 162 is put in an on state. Accordingly, the potential of the third wiring (a potential relating to new information) is applied to the gate electrode of the transistor 160. After that, the potential of the fourth wiring is set to a potential putting the transistor 162 in an off state, whereby the transistor 162 is put in an off state; thus, the new information is held.

30 [0049]

As described above, in the semiconductor device according to one embodiment

of the disclosed invention, information can be directly rewritten by performing rewriting of information. Erasing operation, necessary in a flash memory and the like, is thus not needed; therefore, reduction in operation speed due to erasing operation can be suppressed. In other words, high-speed operation of a semiconductor device is

5 realized.

[0050]

Note that, in the above description, an n-type transistor (an n-channel transistor) using electrons as carriers is used; however, a p-channel transistor using holes as carriers, needless to say, can be used instead of an n-channel transistor.

10 [0051]

It is also needless to say that a capacitor may be added to the gate electrode of the transistor 160 so that the potential of the gate electrode of the transistor 160 is easily held.

[0052]

15 <Plan Structure and Cross-Sectional Structure of a Semiconductor Device>

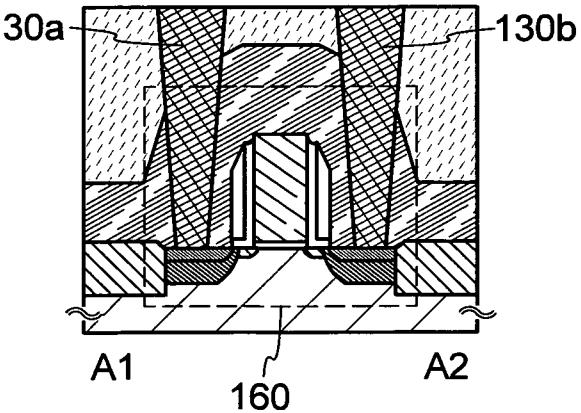

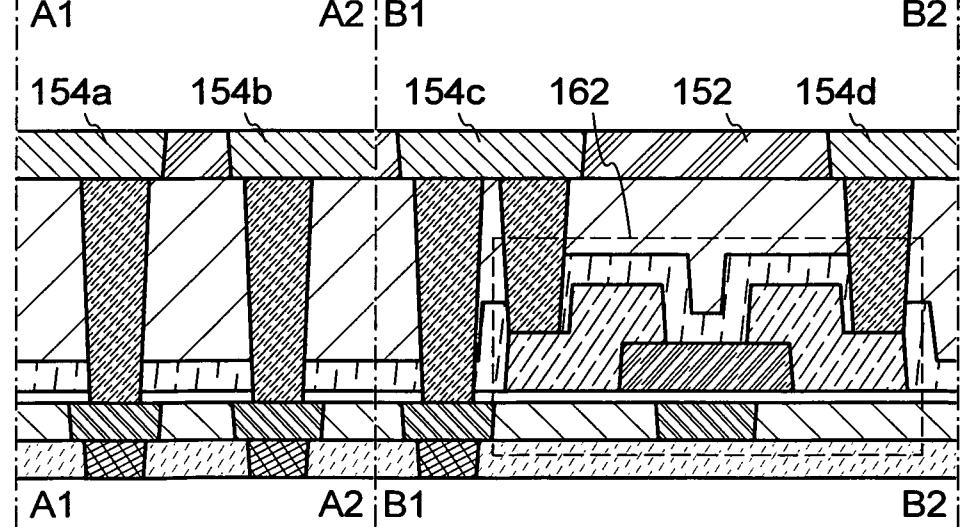

An example of a structure of the above semiconductor device is illustrated in FIGS. 2A and 2B. FIGS. 2A and 2B are a cross-sectional view of the semiconductor device and a plan view thereof, respectively. Here, FIG. 2A corresponds to a cross-section taken along line A1-A2 and line B1-B2 of FIG. 2B. The semiconductor device illustrated in FIGS. 2A and 2B includes the transistor 160 using a material other than an oxide semiconductor in a lower portion and the transistor 162 using an oxide semiconductor in an upper portion. Note that although n-channel transistors are described as the transistors 160 and 162, p-channel transistors may be employed. A p-channel transistor can be preferably used as the transistor 160, in particular.

25 [0053]

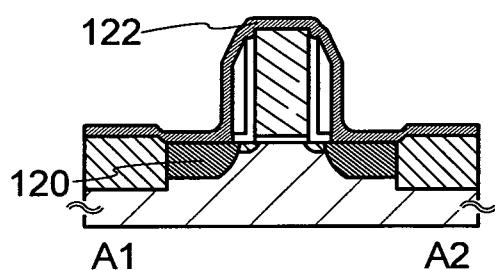

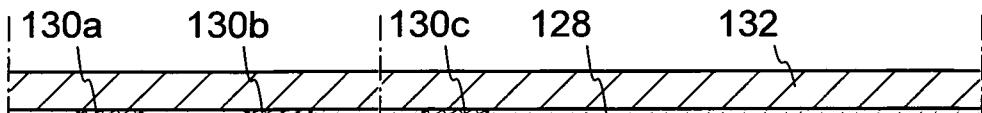

The transistor 160 includes: a channel formation region 116 which is provided in a substrate 100 containing a semiconductor material; impurity regions 114 between which the channel formation region 116 is sandwiched and high-concentration impurity regions 120 between which the channel formation region 116 is sandwiched (impurity regions 114 and high-concentration impurity regions 120 are also collectively called impurity regions); a gate insulating layer 108a provided over the channel formation region 116; a gate electrode 110a provided over the gate insulating layer 108a; a source

or drain electrode 130a electrically connected to a first impurity region 114 on one side of the channel formation region 116; and a source or drain electrode 130b electrically connected to a second impurity regions 114 on another side of the channel formation region 116.

5 [0054]

Here, sidewall insulating layers 118 are provided for side surfaces of the gate electrode 110a. Moreover, at least parts of the side wall insulating layers 118 are comprised between the high concentration impurity regions 120 formed in regions of the substrate 100, when seen from above, and metal compound regions 124 are present over the high concentration impurity regions 120. Further, an element insulation insulating layer 106 is formed over the substrate 100 so as to surround the p-type transistor 160, and an interlayer insulating layer 126 and an interlayer insulating layer 128 are formed so as to cover the p-type transistor 160. The source or drain electrode 130a is electrically connected to a first metal compound region 124 on the one side of the channel formation region 116, and the source or drain electrode 130b is electrically connected to a second metal compound region 124 on the other side of the channel formation region 116 through openings in the interlayer insulating layer 126 and the interlayer insulating layer 128. In other words, the source or drain electrode 130a is electrically connected to a first high concentration region 120 and to the first impurity region 114 which are on the one side of the channel formation region 116 through the first metal compound region 124 on the one side of the channel formation region 116, and the source or drain electrode 130b is electrically connected to a second high concentration region 120 and to the second impurity region 114 which are on the other side of the channel formation region 116 through the second metal compound region 124 on the other side the channel formation region 116. Further, the gate electrode 110a is electrically connected to an electrode 130c provided in a similar manner to the source or drain electrode 130a and the source or drain electrode 130b.

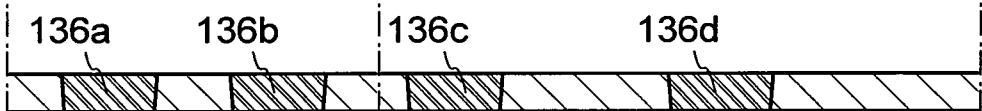

[0055]

The transistor 162 includes: a gate electrode 136d provided over the interlayer insulating layer 128; a gate insulating layer 138 provided over the gate electrode 136d; an oxide semiconductor layer 140 provided over the gate insulating layer 138; and a source or drain electrode 142a and a source or drain electrode 142b which are provided

over and electrically connected to the oxide semiconductor layer 140.

[0056]

Here, the gate electrode 136d is provided so as to be embedded in an insulating layer 132 which is formed over the interlayer insulating layer 128. Furthermore, 5 similarly to the gate electrode 136d, an electrode 136a, an electrode 136b, and an electrode 136c are formed in contact with the source or drain electrode 130a, the source or drain electrode 130b, and the electrode 130c, respectively.

[0057]

Over the transistor 162, a protective insulating layer 144 is provided in contact 10 with part of the oxide semiconductor layer 140. An interlayer insulating layer 146 is provided over the protective insulating layer 144. Here, in the protective insulating layer 144 and the interlayer insulating layer 146, openings reaching the source or drain electrode 142a and the source or drain electrode 142b are formed. In the openings, an electrode 150d and an electrode 150e are formed to be in contact with the source or 15 drain electrode 142a and the source or drain electrode 142b, respectively. Similarly to the electrodes 150d and 150e, an electrode 150a, an electrode 150b, and an electrode 150c are formed to be in contact with the electrode 136a, the electrode 136b, and the electrode 136c, respectively, through openings provided in the gate insulating layer 138, the protective insulating layer 144, and the interlayer insulating layer 146.

20 [0058]

Here, the oxide semiconductor layer 140 is preferably an oxide semiconductor layer highly purified by removing an impurity such as hydrogen. Specifically, 25 hydrogen concentration in the oxide semiconductor layer 140 is less than or equal to  $5 \times 10^{19}$  atoms /cm<sup>3</sup>, preferably, less than or equal to  $5 \times 10^{18}$  atoms /cm<sup>3</sup>, or more preferably, less than or equal to  $5 \times 10^{17}$  atoms /cm<sup>3</sup>. In addition, it is desirable that the oxide semiconductor layer 140 contain sufficient oxygen so that defects due to oxygen vacancies are reduced. In the oxide semiconductor layer 140 which is highly purified by sufficiently reducing the hydrogen concentration, carrier concentration is less than or equal to  $1 \times 10^{12}$  /cm<sup>3</sup>, preferably less than or equal to  $1 \times 10^{11}$  /cm<sup>3</sup>. In this manner, 30 by using an oxide semiconductor which is made to be an i-type (intrinsic) oxide semiconductor or a substantially i-type oxide semiconductor, the transistor 162 which

has extremely favorable off-state current characteristics can be obtained. For example, when a drain voltage  $V_d$  is +1 V or +10 V and a gate voltage  $V_g$  ranges from -5 V to -20 V, off-state current is less than or equal to  $1 \times 10^{-13}$  A. When the oxide semiconductor layer 140 which is highly purified by sufficiently reducing the hydrogen concentration and in which the defects due to oxygen vacancies are reduced is used and off-state current of the transistor 162 is reduced, a semiconductor device having a new structure can be realized. Note that the hydrogen concentration in the oxide semiconductor layer 140 was measured by secondary ion mass spectroscopy (SIMS).

[0059]

Furthermore, an insulating layer 152 is provided over the interlayer insulating layer 146. An electrode 154a, an electrode 154b, an electrode 154c, and an electrode 154d are provided so as to be embedded in the insulating layer 152. Here, the electrode 154a is in contact with the electrode 150a; the electrode 154b, the electrode 150b; the electrode 154c, the electrodes 150c and 150d; and the electrode 154d, the electrode 150e.

[0060]

That is, in the semiconductor device illustrated in FIGS. 2A and 2B, the gate electrode 110a of the transistor 160 is electrically connected to the source or drain electrode 142a of the transistor 162 through the electrodes 130c, 136c, 150c, 154c, and 150d.

[0061]

<Method for Manufacturing Semiconductor Device>

Next, an example of a method for manufacturing the above-described semiconductor device will be described. First, a method for manufacturing the transistor 160 in the lower portion will be described with reference to FIGS. 3A to 3H and next, a method for manufacturing the transistor 162 in the upper portion will be described with reference to FIGS. 4A to 4G and FIGS. 5A to 5D.

[0062]

<Method for Manufacturing a Transistor in a Lower Portion>

First, the substrate 100 which contains a semiconductor material is prepared (see FIG. 3A). As the substrate 100 which contains a semiconductor material, a single

crystal semiconductor substrate or a polycrystalline semiconductor substrate containing silicon, silicon carbide, or the like, a compound semiconductor substrate containing silicon germanium or the like, an SOI substrate, or the like can be used. Here, an example in which a single crystal silicon substrate is used as the substrate 100 containing a semiconductor material is described. Note that in general, the term "SOI substrate" means a substrate having a silicon semiconductor layer over an insulating surface. In this specification, the term "SOI substrate" also means a substrate having a semiconductor layer using a material other than silicon over an insulating surface. That is, a semiconductor layer included in the "SOI substrate" is not limited to a silicon semiconductor layer. In addition, the SOI substrate includes a substrate which has a semiconductor layer over an insulating substrate such as a glass substrate, with an insulating layer between the semiconductor layer and the insulating substrate.

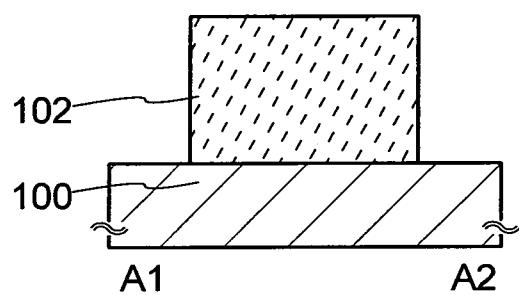

[0063]

Over the substrate 100, a protective layer 102 which functions as a mask for forming an element insulation insulating layer is formed (see FIG. 3A). As the protective layer 102, for example, an insulating layer formed using silicon oxide, silicon nitride, silicon nitride oxide, or the like can be used. Note that an impurity element giving n-type conductivity or an impurity element giving p-type conductivity may be added to the substrate 100 before or after the above step to control the threshold voltage of the transistor. As the impurity giving n-type conductivity, phosphorus, arsenic, or the like can be used when the semiconductor material contained in the substrate 100 is silicon. As the impurity giving p-type conductivity, boron, aluminum, gallium, or the like can be used, for example.

[0064]

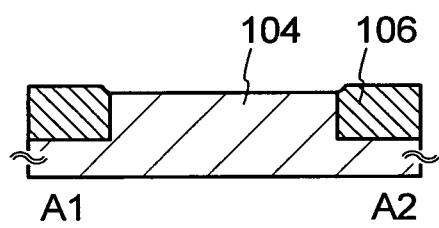

Next, part of the substrate 100 in a region which is not covered with the protective layer 102 (an exposed region) is removed by etching with the use of the above protective layer 102 as a mask. Thus, an insulated semiconductor region 104 is formed (see FIG. 3B). For the etching, dry etching is preferably performed, but wet etching can be performed. An etching gas and an etchant can be selected as appropriate depending on a material of the object to be etched.

[0065]

Next, an insulating layer is formed so as to cover the semiconductor region 104

and is selectively removed in a region which overlaps with the semiconductor region 104, whereby the element insulation insulating layer 106 is formed (see FIG. 3B). The insulating layer is formed using silicon oxide, silicon nitride, silicon nitride oxide, or the like. As a method for removing the insulating layer, there are etching and polishing 5 treatment such as CMP, and any of them can be employed. Note that the protective layer 102 is removed either after the semiconductor region 104 is formed or after the element insulation insulating layer 106 is formed.

[0066]

Then, an insulating layer is formed over the semiconductor region 104 and a 10 layer containing a conductive material is formed over the insulating layer.

[0067]

The insulating layer serves as a gate insulating layer later and preferably has a single-layer structure or a stacked-layer structure film containing silicon oxide, silicon 15 nitride oxide, silicon nitride, hafnium oxide, aluminum oxide, tantalum oxide, or the like obtained by using a CVD method, a sputtering method, or the like. Alternatively, the above insulating layer may be obtained by oxidizing or nitriding a surface of the semiconductor region 104 by high-density plasma treatment or thermal oxidation treatment. The high-density plasma treatment can be performed using, for example, a mixed gas of a combination of a rare gas such as He, Ar, Kr, or Xe and oxygen, nitrogen 20 oxide, ammonia, nitrogen, or hydrogen. There is no particular limitation on the thickness of the insulating layer, but the thickness can be greater than or equal to 1 nm and less than or equal to 100 nm, for example.

[0068]

The layer containing a conductive material can be formed using a metal 25 material such as aluminum, copper, titanium, tantalum, or tungsten. Alternatively, the layer containing a conductive material may be formed using a semiconductor material such as polycrystalline silicon containing a conductive material. There is also no particular limitation on a method for forming the layer containing a conductive material, and any of a variety of deposition methods such as an evaporation method, a CVD 30 method, a sputtering method, and a spin coating method is applicable. Note that in this embodiment, an example of the case where the layer containing a conductive material is formed using a metal material is described.

[0069]

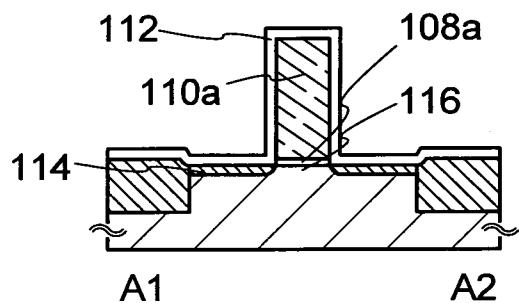

After that, by selectively etching the insulating layer and the layer containing a conductive material, the gate insulating layer 108a and the gate electrode 110a are formed (see FIG. 3C).

5 [0070]

Next, an insulating layer 112 which covers the gate electrode 110a is formed (see FIG. 3C). Phosphorus (P), arsenic (As), or the like is then added to the semiconductor region 104, whereby the impurity regions 114 with a shallow junction depth are formed (see FIG. 3C). Note that although phosphorus or arsenic is added 10 here so that an n-channel transistor is formed, an impurity element such as boron (B) or aluminum (Al) may be added in the case of forming a p-channel transistor. Note also that the channel formation region 116 is formed in the semiconductor region 104 under the gate insulating layer 108a by formation of the impurity regions 114 (see FIG. 3C). Here, the concentration of the added impurity can be set as appropriate; in the case 15 where a semiconductor element is highly miniaturized, the concentration is preferably set to be high. Further, a process in which the insulating layer 112 is formed after formation of the impurity regions 114 may be employed instead of the process employed here in which the impurity regions 114 are formed after formation of the insulating layer 112.

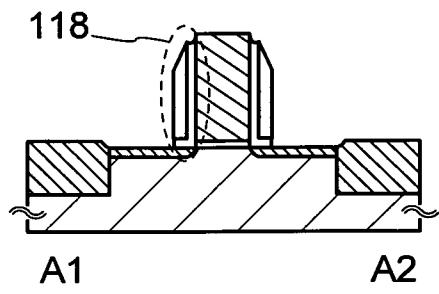

20 [0071]

Then, the sidewall insulating layers 118 are formed (see FIG. 3D). An insulating layer is formed so as to cover the insulating layer 112 and then is subjected to highly anisotropic etching, whereby the sidewall insulating layers 118 can be formed in a self-aligned manner. It is preferable that the insulating layer 112 be partly etched at 25 this time so that a top surface of the gate electrode 110a and top surfaces of the impurity regions 114 are exposed.

[0072]

After that, an insulating layer is formed so as to cover the gate electrode 110a, the impurity regions 114, the side wall insulating layers 118, and the like. Phosphorus (P), arsenic (As), or the like is then added to regions which are in contact with the impurity regions 114, whereby the high-concentration impurity regions 120 are formed 30 (see FIG. 3E). Next, the above insulating layer is removed and a metal layer 122 is

formed so as to cover the gate electrode 110a, the sidewall insulating layers 118, the high-concentration impurity regions 120, and the like (see FIG. 3E). Any of a variety of film formation methods such as a vacuum evaporation method, a sputtering method, and a spin coating method is applicable to formation of the metal layer 122. It is preferable that the metal layer 122 be formed using a metal material that reacts with a semiconductor material included in the semiconductor region 104 so as to form a metal compound having low resistance. Examples of such a metal material include titanium, tantalum, tungsten, nickel, cobalt, and platinum.

[0073]

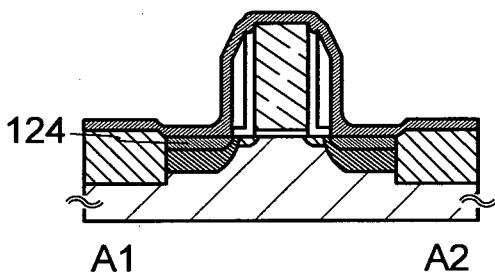

Next, heat treatment is performed, whereby the metal layer 122 reacts with the semiconductor material. Accordingly, the metal compound regions 124 which are in contact with the high-concentration impurity regions 120 are formed (see FIG. 3F). Note that, in the case of using polycrystalline silicon for the gate electrode 110a, a portion of the gate electrode 110a which is in contact with the metal layer 122 also has the metal compound region.

[0074]

As the heat treatment, irradiation with a flash lamp can be employed. Although it is needless to say that another heat treatment method may be used, a method by which heat treatment for an extremely short time can be achieved is preferably used in order to improve the controllability of chemical reaction in formation of the metal compound. Note that the metal compound regions 124 are formed through reaction of the metal material with the semiconductor material and have sufficiently high conductivity. By formation of the metal compound regions 124, electric resistance can be sufficiently reduced and element characteristics can be improved. The metal layer 122 is removed after formation of the metal compound regions 124.

[0075]

The interlayer insulating layers 126 and 128 are formed so as to cover the components formed in the above steps (see FIG. 3G). The interlayer insulating layers 126 and 128 can be formed using a material containing an inorganic insulating material such as silicon oxide, silicon nitride oxide, silicon nitride, hafnium oxide, aluminum oxide, or tantalum oxide. Alternatively, an organic insulating material such as polyimide or acrylic can be used. Note that although the interlayer insulating layer

126 and the interlayer insulating layer 128 have a two-layer structure here, the structure of the interlayer insulating layers is not limited to this. A surface of the interlayer insulating layer 128 is preferably subjected to CMP, etching, or the like so as to be flattened after the interlayer insulating layer 128 is formed.

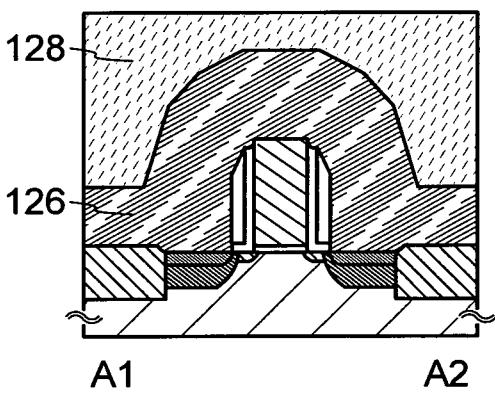

5 [0076]

After that, openings reaching the metal compound regions 124 are formed in the interlayer insulating layers, and then the source or drain electrode 130a and the source or drain electrode 130b are formed in the openings (see FIG. 3H). For example, the source or drain electrode 130a and the source or drain electrode 130b can be formed 10 as follows: a conductive layer is formed in a region including the openings by a PVD method, a CVD method, or the like; and then, part of the conductive layer is removed by etching, CMP, or the like.

[0077]

Note that in the case of forming the source or drain electrode 130a and the source or drain electrode 130b by removing part of the conductive layer, surfaces thereof are preferably processed to be flat. For example, in the case where a titanium film, a titanium nitride film, or the like is formed to have a small thickness in the region including the openings and a tungsten film is then formed so as to be embedded in the openings, CMP which is performed after that can remove an unnecessary portion of the tungsten film, titanium film, titanium nitride film, or the like, and improve the flatness 20 of the surfaces. By flattening surfaces including the surfaces of the source or drain electrode 130a and the source or drain electrode 130b as described above, favorable electrodes, wirings, insulating layers, semiconductor layers, or the like can be formed in a subsequent step.

25 [0078]

Note that although only the source or drain electrode 130a and the source or drain electrode 130b which are in contact with the metal compound regions 124 are described, an electrode which is in contact with the gate electrode 110a (e.g., the electrode 130c of FIG. 2A) and the like can be formed in the same step. There is no 30 particular limitation on a material used for the source or drain electrode 130a and the source or drain electrode 130b and any of a variety of conductive materials can be used. For example, a conductive material such as molybdenum, titanium, chromium, tantalum,

tungsten, aluminum, copper, neodymium, or scandium can be used.

[0079]

Through the above process, the transistor 160 which uses the substrate 100 containing a semiconductor material is formed. Note that electrodes, wirings, insulating layers, or the like may be formed as well after the above process is performed. When a multilayer wiring structure in which an interlayer insulating layer and a conductive layer are stacked is employed as a wiring structure, a highly-integrated semiconductor device can be provided.

[0080]

10 <Method for Manufacturing a Transistor in an Upper Portion>

Next, a process through which the transistor 162 is manufactured over the interlayer insulating layer 128 is described with reference to FIGS. 4A to 4G and FIGS. 5A to 5D. Note that the transistor 160 and the like below the transistor 162 are omitted in FIGS. 4A to 4G and FIGS. 5A to 5D, which illustrate a manufacturing process of a variety of electrodes over the interlayer insulating layer 128, the transistor 162, and the like.

[0081]

First, the insulating layer 132 is formed over the interlayer insulating layer 128, the source or drain electrode 130a, the source or drain electrode 130b, and the electrode 20 130c (see FIG. 4A). The insulating layer 132 can be formed by a PVD method, a CVD method, or the like. A material containing an inorganic insulating material such as silicon oxide, silicon nitride oxide, silicon nitride, hafnium oxide, aluminum oxide, or tantalum oxide can be used for the insulating layer 132.

[0082]

25 Next, openings reaching the source or drain electrode 130a, the source or drain electrode 130b, and the electrode 130c are formed in the insulating layer 132. At this time, another opening is formed in a region where the gate electrode 136d is to be formed. A conductive layer 134 is formed so as to be embedded in the openings (see FIG. 4B). The above openings can be formed by etching with the use of a mask, for example. The mask can be formed by exposure using a photomask, for example. For the etching, either wet etching or dry etching may be performed but dry etching is preferable in view of the fine patterning. The conductive layer 134 can be formed by a

film formation method such as a PVD method or a CVD method. Examples of a material for the conductive layer 134 include a conductive material such as molybdenum, titanium, chromium, tantalum, tungsten, aluminum, copper, neodymium, and scandium, an alloy of any of these, and a compound containing any of these (e.g., 5 nitride of any of these).

[0083]

Specifically, for example, the conductive layer 134 can be formed as follows: a titanium film is formed to have a small thickness by a PVD method in a region including the openings and a titanium nitride film is then formed to have a small 10 thickness by a CVD method; and then, a tungsten film is formed so as to fill the openings. Here, the titanium film formed by a PVD method has a function of reducing formation of an oxide film at an interface with an electrode in a lower portion (here, the source or drain electrode 130a, the source or drain electrode 130b, the electrode 130c, or the like) so that contact resistance with the lower electrode is reduced. In addition, the 15 subsequently formed titanium nitride film has a barrier property such that diffusion of a conductive material is prevented. Further, after a barrier film is formed using titanium, titanium nitride, or the like, a copper film may be formed by a plating method.

[0084]

After the conductive layer 134 is formed, part of the conductive layer 134 is 20 removed by etching, CMP, or the like so that the insulating layer 132 is exposed and the electrodes 136a, 136b, and 136c, and the gate electrode 136d are formed (see FIG. 4C). Note that when the electrodes 136a, 136b, and 136c, and the gate electrode 136d are formed by removing part of the above conductive layer 134, the process is preferably 25 performed so that flattened surfaces are obtained. By flattening surfaces of the insulating layer 132, the electrodes 136a, 136b, and 136c, and the gate electrode 136d, favorable electrodes, wirings, insulating layers, semiconductor layers, and the like can be formed in a subsequent step.

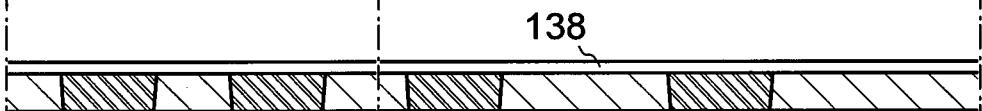

[0085]

After that, the gate insulating layer 138 is formed so as to cover the insulating 30 layer 132, the electrodes 136a, 136b, and 136c, and the gate electrode 136d (see FIG. 4D). The gate insulating layer 138 can be formed by a sputtering method, a CVD method, or the like. The gate insulating layer 138 preferably contains silicon oxide,

silicon nitride, silicon oxynitride, silicon nitride oxide, aluminum oxide, hafnium oxide, tantalum oxide, or the like. Note that the gate insulating layer 138 may have a single-layer structure or a stacked-layer structure. For example, the gate insulating layer 138 of silicon oxynitride can be formed by a plasma CVD method using silane 5 ( $\text{SiH}_4$ ), oxygen, and nitrogen as source gases. There is no particular limitation on the thickness of the gate insulating layer 138, but the thickness can be greater than or equal to 10 nm and less than or equal to 500 nm, for example. When a stacked-layer structure is employed, the gate insulating layer 138 is preferably formed by stacking a first gate insulating layer with a thickness greater than or equal to 50 nm and less than 10 or equal to 200 nm and a second gate insulating layer with a thickness greater than or equal to 5 nm and less than or equal to 300 nm over the first gate insulating layer.

[0086]

Note that an oxide semiconductor which is made to be an i-type oxide semiconductor or a substantially i-type oxide semiconductor by removing an impurity 15 (an oxide semiconductor which is highly purified) is extremely sensitive to an interface energy levels or to the electric charges trapping at the interface; therefore, when such an oxide semiconductor is used for an oxide semiconductor layer, an interface between the oxide semiconductor layer and a gate insulating layer is important. In other words, the gate insulating layer 138 which is to be in contact with the highly purified oxide 20 semiconductor layer needs to be of high quality.

[0087]

For example, a high-density plasma CVD method using microwave (2.45 GHz) is favorable because a dense and high-quality gate insulating layer 138 having high 25 withstand voltage can be formed thereby. In this manner, the density of energy levels at the interface can be reduced and interface characteristics can be favorable when the highly purified oxide semiconductor layer and the high quality gate insulating layer are in contact with each other.

[0088]

Needless to say, even when such a highly purified oxide semiconductor layer is 30 used, another method such as a sputtering method or a plasma CVD method can be employed as long as an insulating layer having good quality can be formed as the gate insulating layer. Alternatively, an insulating layer whose film quality and interface

characteristics are modified by heat treatment after being formed may be applied. In any case, a layer is acceptable which is of good quality as the gate insulating layer 138, and which reduces interface state density between the gate insulating layer and the oxide semiconductor layer so that a good interface is formed.

5 [0089]

Moreover, when an impurity is contained in an oxide semiconductor, in the bias temperature test (the BT test) at a temperature of 85 °C for 12 hours with electric field strength of  $2 \times 10^6$  V/cm, bond between impurities and the main components of the oxide semiconductor are cut by a strong electric field (B: bias) and a high temperature 10 (T: temperature), and generated dangling bonds lead to a drift in the threshold voltage ( $V_{th}$ ).

[0090]

On the other hand, a transistor which is stable even in the BT test can be provided by removing impurities in the oxide semiconductor, especially hydrogen or 15 water, and realizing good interface characteristics between the gate insulating layer and the oxide semiconductor layer as described above.

[0091]

Then, an oxide semiconductor layer is formed over the gate insulating layer 138 and processed by a method such as etching using a mask so that the oxide 20 semiconductor layer 140 having an island-shape is formed (see FIG. 4E).

[0092]

As the oxide semiconductor layer, an oxide semiconductor layer formed using any of the following materials can be applied: four-component metal oxides such as In-Sn-Ga-Zn-O; three-component metal oxides such as In-Ga-Zn-O, In-Sn-Zn-O, 25 In-Al-Zn-O, Sn-Ga-Zn-O, Al-Ga-Zn-O, and Sn-Al-Zn-O; two-component metal oxides such as In-Zn-O, Sn-Zn-O, Al-Zn-O, Zn-Mg-O, Sn-Mg-O, and In-Mg-O; single-component metal oxides such as In-O, Sn-O, and Zn-O. In addition, the above oxide semiconductor materials may contain SiO<sub>2</sub>.

[0093]

30 As the oxide semiconductor layer, a thin film represented by InMO<sub>3</sub> (ZnO)<sub>m</sub> ( $m > 0$ ) can be used. Here, M represents one or more metal elements selected from Ga, Al,

Mn, and Co. For example, M can be Ga, Ga and Al, Ga and Mn, Ga and Co, or the like. An oxide semiconductor film which represented by  $\text{InMO}_3$  ( $\text{ZnO})_m$  ( $m > 0$ ), which includes Ga as M, is referred to as an In-Ga-Zn-O-based oxide semiconductor, and a thin film of the In-Ga-Zn-O-based oxide semiconductor is referred to as an

5 In-Ga-Zn-O-based oxide semiconductor film (an In-Ga-Zn-O-based amorphous film).

[0094]

In this embodiment, as the oxide semiconductor layer, an amorphous oxide semiconductor layer is formed by a sputtering method with the use of an In-Ga-Zn-O-based oxide semiconductor target for film formation. Note that by adding 10 silicon to the amorphous oxide semiconductor layer, crystallization can be suppressed; therefore, the oxide semiconductor layer may be formed using a target which contains  $\text{SiO}_2$  at greater than or equal to 2 wt.% and less than or equal to 10 wt.%.

[0095]

As a target for forming the oxide semiconductor layer by a sputtering method, a 15 metal oxide containing zinc oxide as a main component can be used, for example. As the oxide semiconductor target for film formation containing In, Ga, and Zn, a target having a composition ratio of  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:1$  (molar ratio) or the like can also be used. Alternatively, as the oxide semiconductor target for film formation containing In, Ga, and Zn, a target having a composition ratio of  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:2$  (molar 20 ratio) or a target having a composition ratio of  $\text{In}_2\text{O}_3:\text{Ga}_2\text{O}_3:\text{ZnO} = 1:1:4$  (molar ratio) can be used. The filling rate of the oxide semiconductor target for film formation is greater than or equal to 90 % and less than or equal to 100 %, preferably greater than or equal to 95 % (e.g., 99.9 %). By using an oxide semiconductor target for film formation whose filling rate is high, a dense oxide semiconductor layer is formed.

25 [0096]

An atmosphere for formation of the oxide semiconductor layer is preferably a rare gas (typically argon) atmosphere, an oxygen atmosphere, or a mixed atmosphere of a rare gas (typically argon) and oxygen. Specifically, a high-purity gas, in which the concentration of impurities such as hydrogen, water, hydroxyl, and hydride is reduced to 30 a concentration of approximately several parts per million (and even better, to several parts per billion), is preferable.

## [0097]

At the time of forming the oxide semiconductor layer, the substrate is placed in a treatment chamber which is kept in a reduced-pressure state and the substrate temperature is higher than or equal to 100 °C and lower than or equal to 600 °C, 5 preferably, higher than or equal to 200 °C and lower than or equal to 400 °C. By forming the oxide semiconductor layer while the substrate is heated, the concentration of impurities contained in the oxide semiconductor layer can be reduced. In addition, damage due to sputtering is reduced. While moisture remaining in the treatment chamber is removed, a sputtering gas from which hydrogen and moisture are removed is 10 introduced, and the oxide semiconductor layer is formed with use of metal oxide as a target. In order to remove remaining moisture in the treatment chamber, a sorption vacuum pump is preferably used. A cryopump, an ion pump, or a titanium sublimation pump can be used. The evacuation unit may be a turbo pump provided with a cold trap. A hydrogen atom, a compound containing a hydrogen atom, such as water (H<sub>2</sub>O) 15 (and also preferably a compound containing a carbon atom), or the like is removed from the deposition chamber while reduced pressure is maintained with the cryopump, thereby reducing the concentration of impurities contained in the oxide semiconductor layer formed in the deposition chamber.

## [0098]

20 For example, the film formation conditions can be set as follows: the distance between a substrate and a target is 100 mm; the pressure is 0.6 Pa; the direct-current (DC) power is 0.5 kW; and the atmosphere is an oxygen atmosphere (the proportion of the oxygen flow rate is 100%). It is preferable that a pulsed direct-current (DC) power supply be used because powder substances (also referred to as particles or dust) can be 25 reduced and the film thickness can be uniform. The thickness of the oxide semiconductor layer is greater than or equal to 2 nm and less than or equal to 200 nm, preferably greater than or equal to 5 nm and less than or equal to 30 nm. Note that an appropriate thickness depends on an applied oxide semiconductor material, and the thickness of the oxide semiconductor layer may be set as appropriate depending on the 30 material.

## [0099]

Note that before the oxide semiconductor layer is formed by a sputtering method, dust attached to a surface of the gate insulating layer 138 is preferably removed by reverse sputtering in which an argon gas is introduced and plasma is generated. Here, the reverse sputtering means a method for improving the quality of a surface of the object to be processed by ions striking on the surface, while general sputtering is achieved by ions striking on a sputtering target. Methods for making ions strike the surface of the object to be processed include a method in which a high frequency voltage is applied on the surface in an argon atmosphere and plasma is generated in the vicinity of the substrate. Note that a nitrogen atmosphere, a helium atmosphere, an oxygen atmosphere, or the like may be used instead of the argon atmosphere.

[0100]

For the etching of the oxide semiconductor layer, either dry etching or wet etching may be used. Needless to say, a combination of dry etching and wet etching may be employed. The etching conditions (an etching gas, etching solution, etching time, temperature, or the like) are set as appropriate, depending on the material so that the oxide semiconductor layer can be etched into a desired shape.

[0101]

Examples of the etching gas for dry etching are a gas containing chlorine (a chlorine-based gas such as chlorine (Cl<sub>2</sub>), boron trichloride (BCl<sub>3</sub>), silicon tetrachloride (SiCl<sub>4</sub>), or carbon tetrachloride (CCl<sub>4</sub>)) and the like. Alternatively, a gas containing fluorine (a fluorine-based gas such as carbon tetrafluoride (CF<sub>4</sub>), sulfur hexafluoride (SF<sub>6</sub>), nitrogen trifluoride (NF<sub>3</sub>), or trifluoromethane (CHF<sub>3</sub>)); hydrogen bromide (HBr); oxygen (O<sub>2</sub>); any of these gases to which a rare gas such as helium (He) or argon (Ar) is added; or the like may be used.

[0102]

As a dry etching method, a parallel plate reactive ion etching (RIE) method or an inductively coupled plasma (ICP) etching method can be used. In order to etch the layer into a desired shape, the etching conditions (the amount of electric power applied to a coil-shaped electrode, the amount of electric power applied to an electrode on a substrate side, the temperature of the electrode on the substrate side, or the like) are set as appropriate.

[0103]

As an etchant used for wet etching, a mixed solution of phosphoric acid, acetic acid, and nitric acid, an ammonia hydrogen peroxide solution (31 wt% hydrogen peroxide in water: 28 wt% ammonia water: water = 5:2:2), or the like can be used. Alternatively, ITO07N (manufactured by Kanto Chemical Co., Inc.) or the like may be used.

5

[0104]

Then, the oxide semiconductor layer is preferably subjected to first heat treatment. By this first heat treatment, the oxide semiconductor layer can be dehydrated or dehydrogenated. The first heat treatment is performed at a temperature higher than or equal to 300 °C and lower than or equal to 750 °C, preferably, higher than or equal to 400 °C and lower than the strain point of the substrate. For example, the substrate is introduced into an electric furnace using a resistance heating element or the like and the oxide semiconductor layer 140 is subjected to heat treatment in a nitrogen atmosphere at a temperature of 450 °C for one hour. During this time, the oxide semiconductor layer 140 is prevented from being exposed to the air so that entry of water or hydrogen is prevented.

10

15

[0105]

Note that a heat treatment apparatus is not limited to an electrical furnace, and may include a device for heating an object to be processed by heat conduction or heat radiation given by a medium such as a heated gas or the like. For example, a rapid thermal anneal (RTA) apparatus such as a lamp rapid thermal anneal (LRTA) apparatus or a gas rapid thermal anneal (GRTA) apparatus can be used. An LRTA apparatus is an apparatus for heating an object to be processed by radiation of light (an electromagnetic wave) emitted from a lamp such as a halogen lamp, a metal halide lamp, a xenon arc lamp, a carbon arc lamp, a high pressure sodium lamp, or a high pressure mercury lamp. A GRTA apparatus is an apparatus for heat treatment using a high-temperature gas. As the gas, an inert gas which does not react with an object to be processed by heat treatment, such as nitrogen or a rare gas such as argon is used.

20

25

[0106]

For example, as the first heat treatment, GRTA may be performed as follows. The substrate is placed in an inert gas which has been heated to a high temperature of

650 °C to 700 °C, heated for several minutes, and taken out from the inert gas. GRTA enables high-temperature heat treatment for a short time. In addition, such heat treatment is applicable even when a temperature exceeds the strain point of the substrate because it takes only a short time.

5 [0107]

Note that the first heat treatment is preferably performed in an atmosphere which contains nitrogen or a rare gas (e.g., helium, neon, or argon) as its main component and does not contain water, hydrogen, or the like. For example, the purity of nitrogen or a rare gas (e.g., helium, neon, or argon) introduced into the heat treatment 10 apparatus is greater than or equal to 6 N (99.9999 %), preferably greater than or equal to 7 N (99.99999 %) (that is, the concentration of impurities is less than or equal to 1 ppm, preferably less than or equal to 0.1 ppm).

[0108]

In some cases, the oxide semiconductor layer might be crystallized to be a 15 microcrystalline layer or a polycrystalline layer depending on the condition of the first heat treatment or the material of the oxide semiconductor layer. For example, the oxide semiconductor layer may be crystallized to become a microcrystalline oxide semiconductor layer having a degree of crystallization of greater than or equal to 90 %, or greater than or equal to 80 %. Further, depending on the condition of the first heat 20 treatment or the material of the oxide semiconductor layer, the oxide semiconductor layer may become an amorphous oxide semiconductor layer containing no crystalline component.

[0109]

The oxide semiconductor layer might become an oxide semiconductor layer in 25 which a crystal (with a grain diameter greater than or equal to 1 nm and less than or equal to 20 nm, typically greater than or equal to 2 nm and less than or equal to 4 nm) is mixed in an amorphous oxide semiconductor (e.g. at a surface of the oxide semiconductor layer).

[0110]

30 In addition, electric characteristics of the oxide semiconductor layer can be changed by providing a crystal layer over the amorphous surface of the oxide

semiconductor layer. For example, in the case of forming the oxide semiconductor layer with the use of an In-Ga-Zn-O-based oxide semiconductor target for the film formation, the electric characteristics of the oxide semiconductor layer can be changed by forming a crystal portion represented by  $\text{In}_2\text{Ga}_2\text{ZnO}_7$  in which a crystal grains are aligned and which exhibits electrical anisotropy.

5 [0111]

More specifically, for example, by aligning the crystal grain in such a manner that the c-axis of  $\text{In}_2\text{Ga}_2\text{ZnO}_7$  is oriented in a direction perpendicular to a surface of the oxide semiconductor layer, conductivity in a direction parallel to the surface of the oxide semiconductor is improved, and an insulating property in the direction perpendicular to the surface of the oxide semiconductor layer can be increased. Further, such a crystal portion has a function of suppressing entry of an impurity such as water or hydrogen into the oxide semiconductor layer.

10 [0112]

15 Note that the above oxide semiconductor layer which includes the crystal portion can be formed by heating a surface of the oxide semiconductor layer by GRTA. When a sputtering target in which the amount of Zn is smaller than that of In or Ga is used, more favorable formation can be achieved.

[0113]

20 The first heat treatment performed on the oxide semiconductor layer 140 can be performed on the oxide semiconductor layer which has not yet been processed into the island-shaped layer. In that case, after the first heat treatment, the substrate is taken out of the heating apparatus and a photolithography step is performed.

[0114]

25 Note that the above heat treatment can dehydrate or dehydrogenate the oxide semiconductor layer 140 and thus can be called dehydration treatment or dehydrogenation treatment. It is possible to perform such dehydration treatment or dehydrogenation treatment at any timing, for example, after the oxide semiconductor layer is formed, after the source or drain electrodes are stacked over the oxide semiconductor layer 140, or after a protective insulating layer is formed over the source or drain electrodes. Such dehydration treatment or dehydrogenation treatment may be performed more than once.

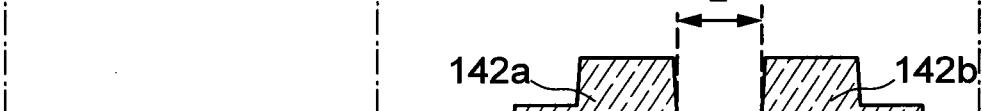

[0115]

Next, the source or drain electrode 142a and the source or drain electrode 142b are formed in contact with the oxide semiconductor layer 140 (see FIG. 4F). The source or drain electrode 142a and the source or drain electrode 142b can be formed in 5 such a manner that a conductive layer is formed so as to cover the oxide semiconductor layer 140 and then selectively etched.

[0116]

The conductive layer can be formed by a PVD method such as a sputtering method, a CVD method such as a plasma CVD method. As a material of the 10 conductive layer, an element selected from aluminum, chromium, copper, tantalum, titanium, molybdenum, and tungsten, an alloy containing any of the above elements as its component, or the like can be used. Further, a material containing one or more elements selected from manganese, magnesium, zirconium, beryllium, and thorium as a component may be used. A material in which aluminum and one or more elements 15 selected from titanium, tantalum, tungsten, molybdenum, chromium, neodymium, and scandium are combined is also applicable for the material of the conductive layer.

[0117]