(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-171703

(P2011-171703A)

(43) 公開日 平成23年9月1日(2011.9.1)

| (51) Int.Cl.                 | F 1        |         | テーマコード (参考) |

|------------------------------|------------|---------|-------------|

| <b>H01L 21/822</b> (2006.01) | H01L 27/04 | G       | 5 F 0 3 8   |

| <b>H01L 27/04</b> (2006.01)  | H01L 29/78 | 6 1 4   | 5 F 1 1 0   |

| <b>H01L 29/786</b> (2006.01) | H01L 29/78 | 6 1 8 B | 5 H 7 3 0   |

| <b>H02M 3/07</b> (2006.01)   | H01L 29/78 | 6 1 8 F |             |

|                              | H02M 3/07  |         |             |

審査請求 未請求 請求項の数 7 O L (全 75 頁)

|              |                              |          |                                                |

|--------------|------------------------------|----------|------------------------------------------------|

| (21) 出願番号    | 特願2010-240683 (P2010-240683) | (71) 出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成22年10月27日 (2010.10.27)     | (72) 発明者 | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2009-250396 (P2009-250396) | (72) 発明者 | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (32) 優先日     | 平成21年10月30日 (2009.10.30)     | (72) 発明者 | 高橋 圭<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 津吹 将志<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2010-12618 (P2010-12618)   |          |                                                |

| (32) 優先日     | 平成22年1月22日 (2010.1.22)       |          |                                                |

| (33) 優先権主張国  | 日本国 (JP)                     |          |                                                |

最終頁に続く

(54) 【発明の名称】電圧調整回路

## (57) 【要約】

【課題】トランジスタにおけるオフ電流を低減し、電圧調整回路における出力電圧の変換効率を向上させる。

【解決手段】ゲート、ソース、及びドレインを有し、ソース及びドレインの一方で第1の信号が入力され、ゲートにクロック信号である第2の信号が入力され、チャネル形成層として酸化物半導体層を有し、オフ電流が10aA / μm以下であるトランジスタと、第1の電極及び第2の電極を有し、第1の電極がトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極に高電源電圧及び低電源電圧が交互に与えられる容量素子と、を有し、第1の信号の電圧を昇圧又は降圧し、昇圧又は降圧した電圧である第3の信号を出力信号としてトランジスタのソース及びドレインの他方を介して出力する構成とする。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの一方に第1の信号が入力され、前記ゲートにクロック信号である第2の信号が入力され、チャネル形成層として酸化物半導体層を有し、オフ電流が $10 \text{ aA} / \mu\text{m}$ 以下であるトランジスタと、第1の電極及び第2の電極を有し、前記第1の電極が前記トランジスタのソース及び前記ドレインの他方に電気的に接続され、前記第2の電極に高電源電圧及び低電源電圧が交互に与えられる容量素子と、を有し、

前記第1の信号の電圧を昇圧又は降圧し、前記昇圧又は前記降圧した電圧である第3の信号を出力信号として前記トランジスタのソース及びドレインの他方を介して出力する電圧調整回路。10

**【請求項 2】**

請求項1において、

前記トランジスタのオフ電流は、 $100 \text{ zA} / \mu\text{m}$ 以下である電圧調整回路。

**【請求項 3】**

請求項1又は請求項2において、

前記酸化物半導体層のキャリア濃度は、 $5 \times 10^{14} / \text{cm}^3$ 以下である電圧調整回路。

**【請求項 4】**

互いに直列接続で電気的に接続されたn段（nは2以上の自然数）の単位昇圧回路と、前記n段の単位昇圧回路により昇圧された電圧を出力信号として出力する出力回路と、を有し、20

前記n段の単位昇圧回路のそれぞれは、

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの一方に第1の信号が入力される第1のトランジスタと、

第1の電極及び第2の電極を有し、前記第1の電極が前記第1のトランジスタのソース及び前記ドレインの他方に電気的に接続された第1の容量素子と、

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの他方が前記容量素子の第2の電極に電気的に接続された第2のトランジスタと、

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの一方が前記容量素子の第2の電極に電気的に接続された第3のトランジスタと、を含み、30

前記出力回路は、

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの一方が第n段目の単位昇圧回路における前記第1のトランジスタのソース及び前記ドレインの他方に電気的に接続された第4のトランジスタと、

第1の電極及び第2の電極を有し、前記第1の電極が前記第4のトランジスタのソース及び前記ドレインの他方に電気的に接続された第2の容量素子と、を含み、

前記第1のトランジスタ乃至前記第4のトランジスタのそれぞれは、チャネル形成層として酸化物半導体層を備え、オフ電流が $10 \text{ aA} / \mu\text{m}$ 以下であり、

$2K$  1段目（Kは1乃至n/2であり、2Kは自然数）の単位昇圧回路における前記第1のトランジスタのゲート及び前記第3のトランジスタのゲート、並びに2K段目の単位昇圧回路における前記第2のトランジスタのゲートに電気的に接続され、クロック信号が入力される第1のクロック信号線と、40

$2K$  1段目の単位昇圧回路における前記第3のトランジスタのゲート、並びに2K段目の単位昇圧回路における前記第1のトランジスタのゲート及び前記第3のトランジスタのゲートに電気的に接続され、前記クロック信号の反転クロック信号が入力される第2のクロック信号線と、をさらに有する電圧調整回路。

**【請求項 5】**

互いに直列接続で電気的に接続されたn段（nは2以上の自然数）の単位降圧回路と、前記n段の単位降圧回路により降圧された電圧を出力信号として出力する出力回路と、を有し、50

前記  $n$  段の単位降圧回路のそれぞれは、

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの一方に第 1 の信号が入力される第 1 のトランジスタと、

第 1 の電極及び第 2 の電極を有し、前記第 1 の電極が前記第 1 のトランジスタのソース及び前記ドレインの他方に電気的に接続された第 1 の容量素子と、

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの他方が前記容量素子の第 2 の電極に電気的に接続された第 2 のトランジスタと、

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの一方が前記容量素子の第 2 の電極に電気的に接続された第 3 のトランジスタと、を含み、

前記出力回路は、

ゲート、ソース、及びドレインを有し、前記ソース及び前記ドレインの一方が第  $n$  段目の単位降圧回路における前記第 1 のトランジスタのソース及び前記ドレインの他方に電気的に接続された第 4 のトランジスタと、

第 1 の電極及び第 2 の電極を有し、前記第 1 の電極が前記第 4 のトランジスタのソース及び前記ドレインの他方に電気的に接続された第 2 の容量素子と、を含み、

前記第 1 のトランジスタ乃至前記第 4 のトランジスタのそれぞれは、チャネル形成層として酸化物半導体層を備え、オフ電流が  $10 \text{ aA} / \mu\text{m}$  以下であり、

$2K$  1 段目 ( $K$  は 1 乃至  $n/2$  であり、 $2K$  は自然数) の単位降圧回路における前記第 1 のトランジスタのゲート及び前記第 2 のトランジスタのゲート、並びに  $2K$  段目の単位降圧回路における前記第 2 のトランジスタのゲートに電気的に接続され、クロック信号が入力される第 1 のクロック信号線と、

$2K$  1 段目の単位降圧回路における前記第 3 のトランジスタのゲート、並びに  $2K$  段目の単位降圧回路における前記第 1 のトランジスタのゲート及び前記第 3 のトランジスタのゲートに電気的に接続され、前記クロック信号の反転クロック信号が入力される第 2 のクロック信号線と、をさらに有する電圧調整回路。

#### 【請求項 6】

請求項 4 又は請求項 5 において、

前記第 1 のトランジスタ乃至前記第 4 のトランジスタのそれぞれのオフ電流は、 $100 \text{ zA} / \mu\text{m}$  以下である電圧調整回路。

#### 【請求項 7】

請求項 4 乃至請求項 6 のいずれか一項において、

前記第 1 のトランジスタ乃至前記第 4 のトランジスタのそれぞれの前記酸化物半導体層のキャリア濃度は、 $5 \times 10^{14} / \text{cm}^3$  以下である電圧調整回路。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明の一形態は、酸化物半導体を用いたトランジスタにより構成される電圧調整回路に関する。

#### 【背景技術】

#### 【0002】

絶縁表面を有する基板上に形成された半導体薄膜を用いて薄膜トランジスタ (TFT) を構成する技術が注目されている。薄膜トランジスタは、液晶テレビに代表されるような表示装置に用いられている。薄膜トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が公知であるが、その他の材料として酸化物半導体が注目されている。

#### 【0003】

酸化物半導体の材料としては、酸化亜鉛又は酸化亜鉛を成分とする材料が知られている。そして、電子キャリア濃度が  $10^{18} / \text{cm}^3$  未満である非晶質酸化物 (酸化物半導体) で形成された薄膜トランジスタが開示されている (特許文献 1 乃至 3)。

#### 【先行技術文献】

#### 【特許文献】

10

20

30

40

50

## 【0004】

【特許文献1】特開2006-165527号公報

【特許文献2】特開2006-165528号公報

【特許文献3】特開2006-165529号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

しかしながら、酸化物半導体は、薄膜形成工程において化学量論的組成からずれてしまう。例えば、酸素の過不足によって酸化物半導体の電気伝導度が変化してしまう。また、酸化物半導体の薄膜形成中に混入する水素が酸素(O) - 水素(H)結合を形成して電子供与体となり、電気伝導度を変化させる要因となる。さらにO - Hは極性分子なので、酸化物半導体によって作製される薄膜トランジスタのような能動デバイスに対して特性の変動要因となる。

10

## 【0006】

電子キャリア濃度が $10^{18} / \text{cm}^3$ 未満としても、酸化物半導体においては実質的にはN型であり、特許文献1乃至3に開示される薄膜トランジスタのオン・オフ比は $10^3$ 程度しか得られていない。このような薄膜トランジスタのオン・オフ比が低い理由はオフ電流が高いことによるものである。

20

## 【0007】

また、オフ電流の高いトランジスタを用いて例えば昇圧回路などの電圧調整回路を構成する場合、トランジスタがオフ状態のときであっても該トランジスタを介してリーク電流が流れてしまうため、所望の電圧への変換効率が悪くなるなどの問題がある。

## 【0008】

このような問題に鑑み、本発明の一態様は、安定した電気的特性（例えば、オフ電流がきわめて低減されている）を有する薄膜トランジスタを提供することを課題とする。また、電圧調整回路において所望の電圧への変換効率を高めることを課題とする。

30

## 【課題を解決するための手段】

## 【0009】

本発明の一形態は、電子供与体（ドナー）となる不純物を除去することにより高純度化させた、真性又は実質的に真性な半導体であり、シリコン半導体よりもエネルギーギャップが大きい酸化物半導体をチャネル形成層に有するトランジスタを用いて昇圧回路又は降圧回路などの電圧調整回路を構成するものである。これにより、トランジスタにおけるオフ状態のリーク電流（オフ電流）の低減を図り、さらにトランジスタにおけるオフ電流の低減により、所望の値の電圧への変換効率の向上を図る。

## 【0010】

酸化物半導体に含まれる水素濃度は、 $5 \times 10^{19} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{18} / \text{cm}^3$ 以下、より好ましくは $5 \times 10^{17} / \text{cm}^3$ 以下である。また、酸化物半導体に含まれる水素若しくはOH基は除去される。また、キャリア濃度は、 $5 \times 10^{14} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{12} / \text{cm}^3$ 以下である。

40

## 【0011】

また、酸化物半導体のエネルギーギャップは2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上であり、さらに、ドナーを形成する水素等の不純物を極力低減し、キャリア濃度を $1 \times 10^{14} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{12} / \text{cm}^3$ 以下となるようにする。

## 【0012】

さらに、上記酸化物半導体を有するトランジスタでは、チャネル幅 $1 \mu\text{m}$ あたりのオフ電流を $10 \text{ aA} / \mu\text{m}$  ( $1 \times 10^{-17} \text{ A} / \mu\text{m}$ )以下にすること、さらには $1 \text{ aA} / \mu\text{m}$  ( $1 \times 10^{-18} \text{ A} / \mu\text{m}$ )以下、さらには $10 \text{ zA} / \mu\text{m}$  ( $1 \times 10^{-20} \text{ A} / \mu\text{m}$ )以下、好ましくは、 $1 \text{ zA} / \mu\text{m}$  ( $1 \times 10^{-21} \text{ A} / \mu\text{m}$ )以下と、従来のシリコンを用いたトランジスタと比較しても非常に低くすることができる。さらに、トランジスタの

50

温度が 85 の場合であってもチャネル幅 1  $\mu\text{m}$ あたりのオフ電流を 100  $\text{zA}/\mu\text{m}$  ( $1 \times 10^{-19} \text{ A}/\mu\text{m}$ ) 以下、好ましくは 10  $\text{zA}/\mu\text{m}$  ( $1 \times 10^{-20} \text{ A}/\mu\text{m}$ ) 以下と、従来のシリコンを用いたトランジスタと比較しても非常に低くすることができる。

#### 【0013】

このように、水素濃度が十分に低減されて高純度化された酸化物半導体層を用いたトランジスタを用いることにより、従来のシリコンを用いたトランジスタを用いる場合と比較してもリーク電流による消費電力の少ない電圧調整回路を実現できる。

#### 【0014】

本発明の一態様は、ゲート、ソース、及びドレインを有し、ソース及びドレインの一方に第1の信号が入力され、ゲートにクロック信号である第2の信号が入力され、チャネル形成層として酸化物半導体層を有し、オフ電流が 10  $\text{aA}/\mu\text{m}$  以下であるトランジスタと、第1の電極及び第2の電極を有し、第1の電極がトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極に高電源電圧及び低電源電圧が交互に与えられる容量素子と、を有し、第1の信号の電圧を昇圧又は降圧し、昇圧又は降圧した電圧である第3の信号を出力信号としてトランジスタのソース及びドレインの他方を介して出力する電圧調整回路である。

#### 【0015】

互いに直列接続で電気的に接続された n 段 (n は 2 以上の自然数) の単位昇圧回路と、n 段の単位昇圧回路により昇圧された電圧を出力信号として出力する出力回路と、を有し、n 段の単位昇圧回路のそれぞれは、ゲート、ソース、及びドレインを有し、ソース及びドレインの一方で第1の信号が入力される第1のトランジスタと、第1の電極及び第2の電極を有し、第1の電極が第1のトランジスタのソース及びドレインの他方に電気的に接続された第1の容量素子と、ゲート、ソース、及びドレインを有し、ソース及びドレインの他方が容量素子の第2の電極に電気的に接続された第2のトランジスタと、ゲート、ソース、及びドレインを有し、ソース及びドレインの一方が容量素子の第2の電極に電気的に接続された第3のトランジスタと、を含み、出力回路は、ゲート、ソース、及びドレインを有し、ソース及びドレインの一方が第 n 段目の単位昇圧回路における第1のトランジスタのソース及びドレインの他方に電気的に接続された第4のトランジスタと、第1の電極及び第2の電極を有し、第1の電極が第4のトランジスタのソース及びドレインの他方に電気的に接続された第2の容量素子と、を含み、第1のトランジスタ乃至第4のトランジスタのそれぞれは、チャネル形成層として酸化物半導体層を備え、オフ電流が 10  $\text{aA}/\mu\text{m}$  以下であり、2K 1 段目 (K は 1 乃至 n / 2 であり、K は自然数) の単位昇圧回路における第1のトランジスタのゲート及び第3のトランジスタのゲート、並びに 2K 段目の単位昇圧回路における第2のトランジスタのゲートに電気的に接続され、クロック信号が入力される第1のクロック信号線と、2K 1 段目の単位昇圧回路における第3のトランジスタのゲート、並びに 2K 段目の単位昇圧回路における第1のトランジスタのゲート及び第3のトランジスタのゲートに電気的に接続され、クロック信号の反転クロック信号が入力される第2のクロック信号線と、をさらに有する電圧調整回路である。

#### 【0016】

互いに直列接続で電気的に接続された n 段 (n は 2 以上の自然数) の単位降圧回路と、n 段の単位降圧回路により降圧された電圧を出力信号として出力する出力回路と、を有し、n 段の単位降圧回路のそれぞれは、ゲート、ソース、及びドレインを有し、ソース及びドレインの一方で第1の信号が入力される第1のトランジスタと、第1の電極及び第2の電極を有し、第1の電極が第1のトランジスタのソース及びドレインの他方に電気的に接続された第1の容量素子と、ゲート、ソース、及びドレインを有し、ソース及びドレインの他方が容量素子の第2の電極に電気的に接続された第2のトランジスタと、ゲート、ソース、及びドレインを有し、ソース及びドレインの一方が容量素子の第2の電極に電気的に接続された第3のトランジスタと、を含み、出力回路は、ゲート、ソース、及びドレインを有し、ソース及びドレインの一方が第 n 段目の単位降圧回路における第1のトランジスタ

10

20

30

40

50

タのソース及びドレインの他方に電気的に接続された第4のトランジスタと、第1の電極及び第2の電極を有し、第1の電極が第4のトランジスタのソース及びドレインの他方に電気的に接続された第2の容量素子と、を含み、第1のトランジスタ乃至第4のトランジスタのそれぞれは、チャネル形成層として酸化物半導体層を備え、オフ電流が $10 \text{ aA} / \mu\text{m}$ 以下であり、 $2K - 1$ 段目( $K$ は $1$ 乃至 $n/2$ であり、 $K$ は自然数)の単位降圧回路における第1のトランジスタのゲート及び第2のトランジスタのゲート、並びに $2K$ 段目の単位降圧回路における第2のトランジスタのゲートに電気的に接続され、クロック信号が入力される第1のクロック信号線と、 $2K - 1$ 段目の単位降圧回路における第3のトランジスタのゲート、並びに $2K$ 段目の単位降圧回路における第1のトランジスタのゲート及び第3のトランジスタのゲートに電気的に接続され、クロック信号の反転クロック信号が入力される第2のクロック信号線と、をさらに有する電圧調整回路である。

10

## 【発明の効果】

## 【0017】

本発明の一態様により、トランジスタのリーク電流を低減し、不要な出力信号の電圧の降下又は上昇を低減することができるため、所望の電圧への変換効率を向上させることができる。

## 【図面の簡単な説明】

## 【0018】

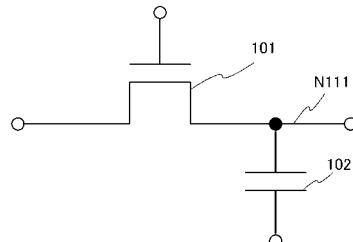

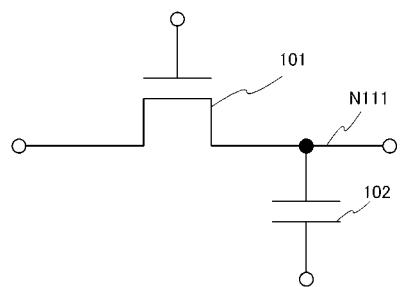

【図1】電圧調整回路の構成の一例を示す回路図。

【図2】図1に示す電圧調整回路の動作の一例を説明するためのタイミングチャート。

20

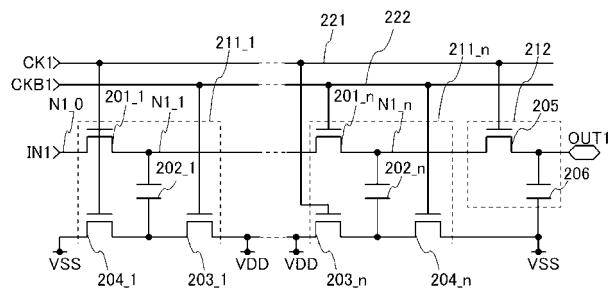

【図3】電圧調整回路の構成の一例を示す回路図。

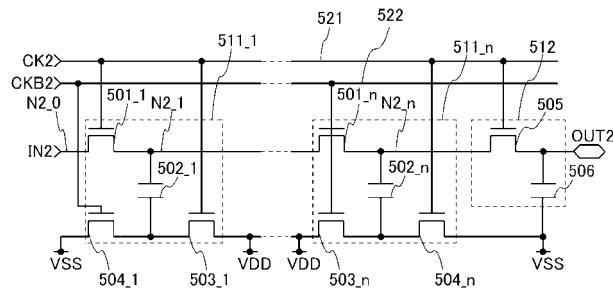

【図4】電圧調整回路の構成の一例を示す回路図

【図5】トランジスタを説明する図。

【図6】トランジスタの作製方法を説明する図。

【図7】トランジスタを説明する図。

【図8】トランジスタの作製方法を説明する図。

【図9】トランジスタを説明する図。

【図10】トランジスタの作製方法を説明する図。

【図11】酸化物半導体を用いた逆スタガ型の薄膜トランジスタの縦断面図。

【図12】図11に示すA-A'断面におけるエネルギー・バンド図(模式図)。

30

【図13】(A)ゲート電極1001に正の電位(+VG)が印加された状態を示す図(B)ゲート電極1001に負の電位(-VG)が印加された状態を示す図。

【図14】真空準位と金属の仕事関数(ΦM)、酸化物半導体の電子親和力(Φ)の関係を示す図。

【図15】酸化物半導体を用いたトランジスタの特性評価用回路図。

【図16】酸化物半導体を用いたトランジスタの特性評価用タイミングチャート。

【図17】酸化物半導体を用いたトランジスタの特性を示す図。

【図18】酸化物半導体を用いたトランジスタの特性を示す図。

【図19】酸化物半導体を用いたトランジスタの特性を示す図。

【図20】トランジスタの作製方法を説明する図。

40

【図21】トランジスタの作製方法を説明する図。

【図22】トランジスタの作製方法を説明する図。

【図23】トランジスタを説明する図。

【図24】トランジスタ及び容量素子を説明する図。

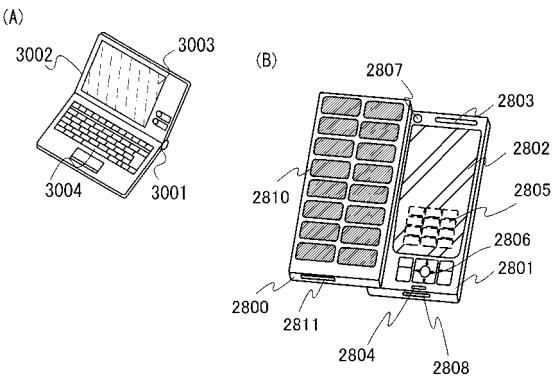

【図25】電子機器を説明する図。

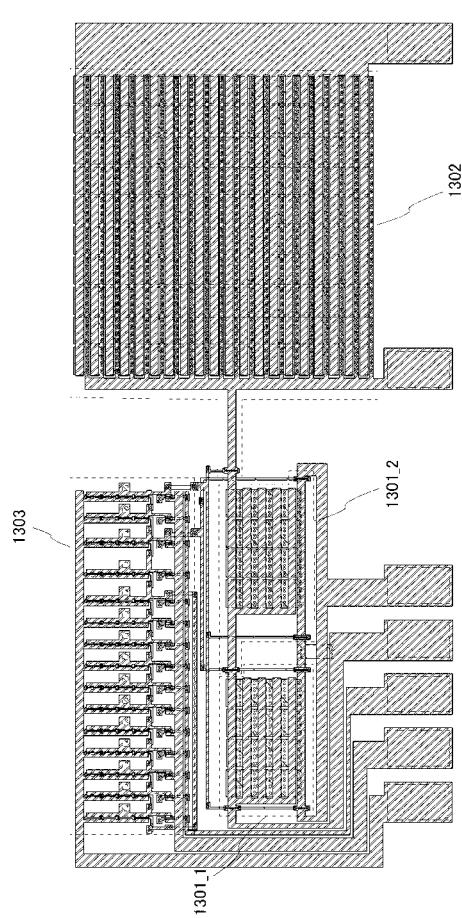

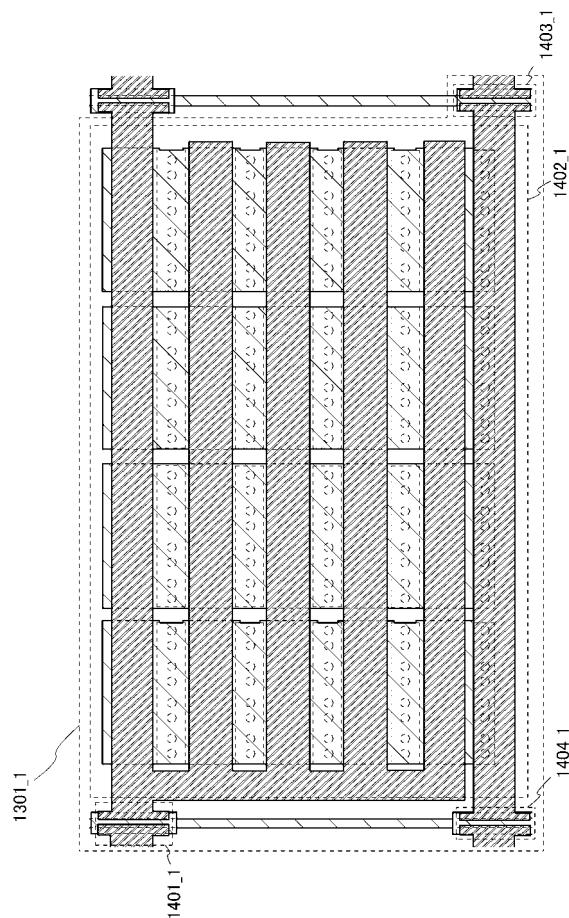

【図26】電圧調整回路のレイアウトを示す図。

【図27】電圧調整回路のレイアウトを示す拡大図。

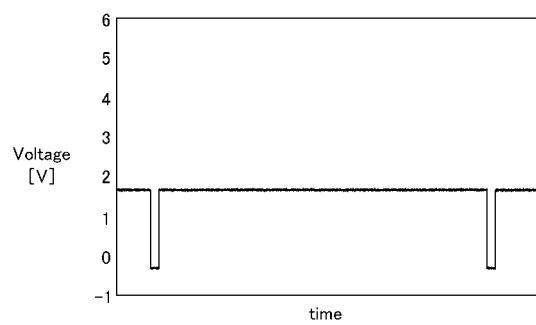

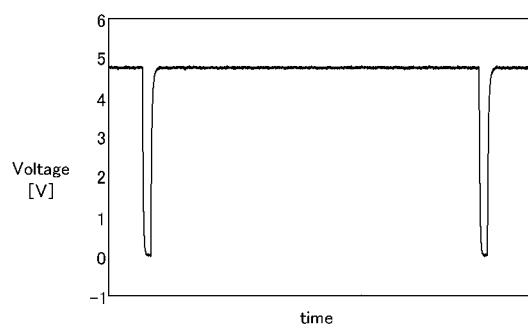

【図28】電圧調整回路の入出力信号の波形を示す図。

## 【発明を実施するための形態】

## 【0019】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではないとする。

## 【0020】

## (実施の形態1)

本実施の形態では、本発明の一態様である電圧調整回路について説明する。

## 【0021】

本実施の形態の電圧調整回路の構成の一例は、入力信号として信号S1及び信号S2が入力され、入力された信号S1を昇圧又は降圧し、信号S1の電圧を昇圧又は降圧した電圧である信号S3を出力信号として出力する機能を有する。さらに、本実施の形態の電圧調整回路の構成の一例について図1を用いて説明する。図1は、本実施の形態における電圧調整回路の構成の一例を示す回路図である。

10

## 【0022】

図1に示す電圧調整回路は、トランジスタ101と、容量素子102と、を有する。

## 【0023】

なお、本明細書において、トランジスタとして例えば電界効果トランジスタを用いることができる。

20

## 【0024】

また、本明細書において、電界効果トランジスタは、ゲート、ソース、及びドレインを少なくとも有する。電界効果トランジスタとしては、例えば薄膜トランジスタ(TFTともいう)を用いることができる。また、電界効果トランジスタとしては、例えばトップゲート型、又はボトムゲート型のトランジスタを用いることができる。

20

## 【0025】

ソースとは、ソース電極、及びソース配線の一部又は全部のことをいう。また、ソース電極とソース配線とを区別せずにソース電極及びソース配線の両方の機能を有する導電層をソースという場合がある。

30

## 【0026】

ドレインとは、ドレン電極、及びドレン配線の一部又は全部のことをいう。また、ドレン電極とドレン配線とを区別せずにドレン電極及びドレン配線の両方の機能を有する導電層をドレインという場合がある。

30

## 【0027】

ゲートとは、ゲート電極及びゲート配線の一部又は全部のことをいう。また、ゲート電極とゲート配線とを区別せずにゲート電極及びゲート配線の両方の機能を有する導電層をゲートという場合がある。

40

## 【0028】

また、本明細書において、トランジスタのソースとドレインは、トランジスタの構造や動作条件などによって互いに入れ替わるため、いずれがソース又はドレインであるかを限定することが困難である。そこで、本書類(明細書、特許請求の範囲又は図面など)においては、ソース及びドレインのいずれか一方をソース及びドレインの一方と表記し、他方をソース及びドレインの他方と表記する。

## 【0029】

また、本明細書における電界効果トランジスタは、チャネル形成層としての機能を有する酸化物半導体層を有するトランジスタである。なお、チャネル形成層の水素濃度は、 $5 \times 10^{19} \text{ atoms/cm}^3$ 以下、好ましくは $5 \times 10^{18} \text{ atoms/cm}^3$ 以下、さらに好ましくは $5 \times 10^{17} \text{ atoms/cm}^3$ 以下とする。該水素濃度は、例えば二次イオン質量分析法(SIMS: Secondary Ion Mass Spectroscopy)による値である。また、トランジスタのキャリア濃度は、 $1 \times 10^{14} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{12} / \text{cm}^3$ 以下とする。

## 【0030】

50

また、本明細書において、容量素子として例えば第1の電極と、第2の電極と、誘電体と、を有する構成の容量素子を用いることができる。

【0031】

トランジスタ101は、ソース及びドレインの一方に信号S1が入力され、ゲートに信号S2が入力され、ソース及びドレインの他方の電圧が信号S3の電圧となる。図1に示す電圧調整回路は、トランジスタ101のソース及びドレインの他方を介して信号S3を出力する。

【0032】

なお、一般的に電圧とは、2点間における電位の差（電位差ともいう）のことをいう。しかし、電圧と電位の値は、回路図などにおいていずれもボルト（V）で表されることがあるため、区別が困難である。そこで、本明細書では、特に指定する場合を除き、ある一点の電位と基準となる電位（基準電位ともいう）との電位差を、該一点の電圧として用いる場合がある。

10

【0033】

なお、本明細書において、信号として例えば電圧などを用いたアナログ信号又はデジタル信号を用いることができる。例えば電圧を用いた信号（電圧信号ともいう）としては、少なくとも第1の電圧状態及び第2の電圧状態を有する信号を用いることが好ましく、例えば第1の電圧状態としてハイレベルの電圧状態及び第2の電圧状態としてローレベルの電圧状態を有するデジタル信号などを用いることができる。なお、ハイレベルのときの電圧を電圧 $V_H$ 又は単に $V_H$ ともいい、ローレベルの電圧を電圧 $V_L$ 又は単に $V_L$ ともいう。また、第1の電圧状態の電圧及び第2の電圧状態の電圧は、各信号によって異なる場合があり、また、ノイズなどの影響があるため、第1の電圧状態の電圧及び第2の電圧状態の電圧は、一定値ではなく、それぞれ一定の範囲内の値であればよい。

20

【0034】

容量素子102は、第1の電極がトランジスタ101のソース及びドレインの他方に電気的に接続され、第2の電極に高電源電圧（電圧 $V_{DD}$ 又は単に $V_{DD}$ ともいう）又は低電源電圧（電圧 $V_{SS}$ 又は単に $V_{SS}$ ともいう）が与えられる。なお、容量素子102の第1の電極と、トランジスタ101のソース及びドレインの他方との接続箇所をノードN111ともいう。

30

【0035】

信号S1は、電圧調整回路の第1の入力信号（信号 $IN_{VC_1}$ ともいう）としての機能を有する。

【0036】

信号S2は、電圧調整回路の第2の入力信号（信号 $IN_{VC_2}$ ともいう）としての機能を有する。信号S2としては、例えばクロック信号を用いることができる。クロック信号は、第1の電圧状態と第2の電圧状態とが周期的に繰り返される信号である。クロック信号における第1の電圧状態及び第2の電圧状態の値は、適宜設定することができる。

40

【0037】

信号S3は、電圧調整回路の出力信号（信号 $OUT_{VC}$ ともいう）としての機能を有する。

【0038】

次に、図1に示す電圧調整回路の動作（駆動方法ともいう）の一例について図2を用いて説明する。図2は、図1に示す電圧調整回路の動作の一例を説明するためのタイミングチャートであり、信号S1、信号S2、及び信号S3、並びに容量素子102の第2の電極の電圧（電圧 $VC$ ともいう）の電圧波形をそれぞれ示したものである。なお、図2を用いて説明する図1に示す電圧調整回路の動作の一例では、信号S1をハイレベルとローレベルの2値のデジタル信号とし、トランジスタ101をN型トランジスタとし、信号S2がハイレベルとローレベルとが周期的に繰り返されるクロック信号であるとして説明する。

【0039】

図1に示す電圧調整回路は、複数の期間に分けて説明することができる。各期間における

50

動作について以下に説明する。

**【0040】**

期間151では、時刻A1にて、信号S1がハイレベルになり、信号S2がハイレベルになり、容量素子102の第2の電極に低電源電圧が与えられ、容量素子102の第2の電極の電圧VCはVLになる。

**【0041】**

このとき、トランジスタ101のソースとドレインの間が導通状態（オン状態ともいう）になり、ノードN111の電圧が上昇し始める。ノードN111の電圧は、V1まで上昇する。V1は、VHである。このとき、容量素子102の第1の電極と第2の電極の間に印加される電圧は、V1 - VLであり、信号S3の電圧は、V1になる。

10

**【0042】**

次に、期間152では時刻A2にて、信号S1がハイレベルのままであり、信号S2がローレベルになり、容量素子102の第2の電極に高電源電圧が与えられる。

**【0043】**

このとき、トランジスタ101は非導通状態（オフ状態ともいう）になり、容量素子102の第2の電極に与えられる電圧（電圧VC）が電圧VLから電圧VHに変化するため、容量素子102の第2の電極の電圧の変化に合わせて容量素子102の第1の電極の電圧も変化し始める。ノードN111の電圧は、電圧V1よりもさらに大きい値、すなわちV2まで上昇する。電圧V2は、2VHである。このとき、容量素子102の第1の電極と第2の電極の間に印加される電圧は、V2 - VHであり、信号S3の電圧は、V2になる。このように、期間152において、電圧調整回路の出力信号である信号S3の電圧は、電圧調整回路に入力される信号S1の電圧が昇圧された値となる。

20

**【0044】**

以上のように、本実施の形態の電圧調整回路では、入力された電圧信号を変化させ、入力された電圧信号よりも高い電圧又は低い電圧の信号を出力することができる。

**【0045】**

また、本実施の形態の電圧調整回路では、トランジスタとして、チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル形成層の水素濃度が $5 \times 10^{19}$ atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{18}$ atoms/cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{17}$ atoms/cm<sup>3</sup>以下であり、キャリア濃度が $1 \times 10^{14}/cm^3$ 以下、好ましくは $1 \times 10^{12}/cm^3$ 以下であるトランジスタを用いた構成である。該トランジスタを用いることにより、電圧調整回路における絶縁耐圧を向上させることができる。また、上記酸化物半導体層を含むトランジスタは、リーク電流が低いため、従来のトランジスタと比較して、容量素子に蓄積された電荷のリークを低減できるため、消費電力を低減し、また、出力信号の不要な電圧の降下又は上昇を低減し、所望の値の電圧への到達速度を格段に向上させることができ、所望の電圧への変換効率を向上させることができる。

30

**【0046】**

また、本実施の形態の電圧調整回路は、容量素子をトランジスタと同一工程により形成することができる。これにより、工程数の増加を抑制することができる。

40

**【0047】**

(実施の形態2)

本実施の形態では、本発明の一態様である電圧調整回路の一例として昇圧回路について説明する。

**【0048】**

本実施の形態における電圧調整回路の回路構成の一例について図3を用いて説明する。図3は、本実施の形態における電圧調整回路の回路構成の一例を示す回路図である。

**【0049】**

図3に示す電圧調整回路は、n段（nは2以上の自然数）の単位昇圧回路である単位昇圧回路211\_1乃至211\_nと、出力回路212と、を有する構成とみなすことができる。各回路の構成について以下に説明する。なお、図3では、一例としてnが偶数の場合

50

について示しているが、これに限定されず、奇数であってもよい。

【0050】

図3に示すn段の単位昇圧回路は、単位昇圧回路 $211\_1$ 乃至単位昇圧回路 $211\_n$ のn個の単位昇圧回路を用いて構成され、M段目(Mは2乃至nの自然数)の単位昇圧回路 $211\_M$ は、M-1段目の単位昇圧回路 $211\_M-1$ に電気的に接続される。

【0051】

単位昇圧回路 $211\_1$ 乃至単位昇圧回路 $211\_n$ のそれぞれ、すなわちk段目(kは2乃至nの自然数)の単位昇圧回路 $211\_k$ は、トランジスタ $201\_k$ と、容量素子 $202\_k$ と、トランジスタ $203\_k$ と、トランジスタ $204\_k$ と、を有する。

【0052】

M段目の単位昇圧回路 $211\_M$ におけるトランジスタ $201\_M$ のソース及びドレインの一方は、M-1段目の単位昇圧回路 $211\_M-1$ におけるトランジスタ $201\_M-1$ のソース及びドレインの他方に電気的に接続される。なお、M段目の単位昇圧回路 $211\_M$ におけるトランジスタ $201\_M$ のソース及びドレインの一方と、M-1段目の単位昇圧回路 $211\_M-1$ におけるトランジスタ $201\_M-1$ のソース及びドレインの他方との接続箇所をノード $N1\_M-1$ ともいい、1段目の単位昇圧回路 $211\_1$ におけるトランジスタ $201\_1$ のソース及びドレインの一方をノード $N1\_0$ ともいう。

10

【0053】

容量素子 $202\_k$ の第1の電極は、トランジスタ $201\_k$ のソース及びドレインの他方に電気的に接続される。

20

【0054】

トランジスタ $203\_k$ は、ソース及びドレインの一方に高電源電圧が与えられ、ソース及びドレインの他方が容量素子 $202\_k$ の第2の電極に電気的に接続される。

【0055】

トランジスタ $204\_k$ は、ソース及びドレインの一方が容量素子 $202\_k$ の第2の電極に電気的に接続され、ソース及びドレインの他方に低電源電圧が与えられる。

【0056】

さらに、 $2K-1$ 段目(Kは1乃至 $n/2$ であり、Kは自然数)の単位昇圧回路 $211\_2K-1$ は、トランジスタ $201\_2K-1$ のゲートがクロック信号線 $221$ に電気的に接続され、トランジスタ $203\_2K-1$ のゲートがクロック信号線 $222$ に電気的に接続され、トランジスタ $204\_2K-1$ のゲートがクロック信号線 $221$ に電気的に接続される。

30

【0057】

また、 $2K$ 段目の単位昇圧回路 $211\_2K$ は、トランジスタ $201\_2K$ のゲートがクロック信号線 $222$ に電気的に接続され、トランジスタ $203\_2K$ のゲートがクロック信号線 $221$ に電気的に接続され、トランジスタ $204\_2K$ のゲートがクロック信号線 $222$ に電気的に接続される。

【0058】

クロック信号線 $221$ にはクロック信号 $C_K1$ が入力され、クロック信号線 $222$ にはクロック信号 $C_{KB}1$ が入力される。

40

【0059】

さらに、1段目の単位昇圧回路 $211\_1$ は、トランジスタ $201\_1$ のソース及びドレインの一方に信号 $IN1$ が入力される。

【0060】

出力回路 $212$ は、 $n$ 段目の単位昇圧回路 $211\_n$ に電気的に接続される。

【0061】

さらに、トランジスタ $205$ は、ソース及びドレインの一方が $n$ 段目の単位昇圧回路 $211\_n$ におけるトランジスタ $201\_n$ のソース及びドレインの他方に電気的に接続される。また、トランジスタ $205$ のソース及びドレインの他方の電圧は、電圧調整回路の出力信号である信号 $OUT1$ の電圧になる。

50

**【 0 0 6 2 】**

さらに、 $n$  が奇数の場合にはトランジスタ 205 のゲートにクロック信号 CKB1 が入力され、 $n$  が偶数の場合にはトランジスタ 205 のゲートにクロック信号 CK1 が入力される。

**【 0 0 6 3 】**

容量素子 206 は、第 1 の電極がトランジスタ 205 のソース及びドレインの他方に電気的に接続され、第 2 の電極に低電源電圧が与えられる。また、容量素子 206 の容量は、他の単位昇圧回路 211\_k における容量素子 202\_k の容量より大きくすることが好ましい。これにより、電圧調整回路の出力信号、すなわち信号 OUT1 の電圧状態をより安定させることができる。

10

**【 0 0 6 4 】**

トランジスタ 201\_k、トランジスタ 203\_k、トランジスタ 204\_k、及びトランジスタ 205 のそれぞれとしては、チャネル形成層としての機能を有する酸化物半導体層を有するトランジスタを用いることができる。なお、チャネル形成層の水素濃度は、 $5 \times 10^{19}$  atoms/cm<sup>3</sup> 以下、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup> 以下、さらに好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup> 以下とする。該水素濃度は、例えば二次イオン質量分析法 (SIMS : Secondary Ion Mass Spectroscopy) による値である。またトランジスタ 201\_k、トランジスタ 203\_k、及びトランジスタ 204\_k、及びトランジスタ 205 のそれぞれのキャリア濃度は、 $1 \times 10^{14}/cm^3$  以下、好ましくは $1 \times 10^{12}/cm^3$  以下とする。

20

**【 0 0 6 5 】**

クロック信号 CK1 とクロック信号 CKB1 は、それぞれ電圧状態が変化するタイミングが異なるクロック信号であり、例えばクロック信号 CK1 がハイレベルになるとき、クロック信号 CKB1 はローレベルであることが好ましく、クロック信号 CKB1 がハイレベルになるとき、クロック信号 CK1 はローレベルであることが好ましい。クロック信号 CKB1 としては、例えばクロック信号 CK1 の反転信号を用いることができ、クロック信号 CKB1 は、例えばインバータなどの NOT 回路を用いてクロック信号 CK1 の電圧状態を反転させることにより生成することができる。クロック信号 CK1 及びクロック信号 CKB1 におけるハイレベル及びローレベルの電圧の値は、適宜設定することができる。また、クロック信号 CK1 は、例えばリングオシレータなどの発振回路とバッファ回路を用いて生成することもできる。また、図 3 に示す電圧調整回路では、クロック信号 CK1 及びクロック信号 CKB1 のみを用いる場合について示しているが、これに限定されず、本実施の形態における電圧調整回路では、3 相以上のクロック信号を用いることもできる。

30

**【 0 0 6 6 】**

以上のように、本実施の形態における電圧調整回路の一例は、 $n$  段の単位昇圧回路と、 $n$  段目の単位昇圧回路に電気的に接続された出力回路と、を有し、それぞれの単位昇圧回路は、スイッチング素子としての機能を有する複数のトランジスタと、容量素子を有し、複数のトランジスタを選択的にオン状態又はオフ状態にすることにより、電圧調整回路に入力された信号電圧を昇圧させ、昇圧した電圧を出力回路により電圧調整回路の出力信号として出力する構成である。また、本実施の形態における電圧調整回路の一例は、トランジスタとして、チャネル形成層としての機能を備えた、高純度化された酸化物半導体層を有するトランジスタを用いる。これにより、各ノードの電圧の保持時間を長くすることができ、また、目的の電圧までの到達時間を短くすることができ、電圧変換効率を向上させることができるもの。

40

**【 0 0 6 7 】**

次に、図 3 に示す電圧調整回路の動作の一例について説明する。なお、ここで説明する図 3 に示す電圧調整回路の動作の一例では、信号 IN1 をハイレベルとローレベルの 2 値のデジタル信号とし、トランジスタ 201\_k、トランジスタ 203\_k、トランジスタ 204\_k、及びトランジスタ 205 を N 型トランジスタとし、クロック信号 CK1 及びク

50

ロック信号 C K B 1 をハイレベルとローレベルとが周期的に繰り返されるクロック信号であるとして説明する。

#### 【 0 0 6 8 】

図 3 に示す電圧調整回路の動作は、複数の期間に分けて説明することができる。各期間における動作について以下に説明する。

#### 【 0 0 6 9 】

まず、第 1 の期間では、クロック信号 C K 1 がハイレベルになり、クロック信号 C K B 1 がローレベルになる。

#### 【 0 0 7 0 】

このとき、2 K - 1 段目の単位昇圧回路 2 1 1 \_ 2 K - 1 において、トランジスタ 2 0 1 \_ 2 K - 1 及びトランジスタ 2 0 4 \_ 2 K - 1 がオン状態になり、トランジスタ 2 0 3 \_ 2 K - 1 がオフ状態になる。トランジスタ 2 0 1 \_ 2 K - 1 がオン状態のとき、ノード N 1 \_ 2 K - 1 と、ノード N 1 \_ 2 K - 2 とが同じ電圧になる。このときのノード N 1 \_ 2 K - 1 の電圧を V \_ 2 K - 1 とする。また、トランジスタ 2 0 4 \_ 2 K - 1 がオン状態のとき容量素子 2 0 2 \_ 2 K - 1 の第 2 の電極には低電源電圧が与えられる。また、容量素子 2 0 2 \_ 2 K - 1 には ( V \_ 2 K - 1 ) - V S S の電圧が与えられる。

#### 【 0 0 7 1 】

次に、第 2 の期間では、クロック信号 C K 1 がローレベルになり、クロック信号 C K B 1 がハイレベルになる。

#### 【 0 0 7 2 】

このとき、2 K - 1 段目の単位昇圧回路 2 1 1 \_ 2 K - 1 において、トランジスタ 2 0 1 \_ 2 K - 1 及びトランジスタ 2 0 4 \_ 2 K - 1 がオフ状態になり、トランジスタ 2 0 3 \_ 2 K - 1 がオン状態になる。よって、容量素子 2 0 2 \_ 2 K - 1 の第 2 の電極の電圧が V H に上昇するため、容量素子 2 0 2 \_ 2 K - 1 の第 2 の電極の電圧の上昇に合わせて容量素子 2 0 2 \_ 2 K - 1 の第 1 の電極の電圧も上昇し始める。また、第 2 の期間では、2 K 段目の単位昇圧回路 2 1 1 \_ 2 K において、トランジスタ 2 0 1 \_ 2 K 及びトランジスタ 2 0 4 \_ 2 K がオン状態になり、トランジスタ 2 0 3 \_ 2 K がオフ状態になる。トランジスタ 2 0 1 \_ 2 K がオン状態のときノード N 1 \_ 2 K と、ノード N 1 \_ 2 K - 1 とが同じ電圧となる。このときのノード N 1 \_ 2 K の電圧を V \_ 2 K とする。また、トランジスタ 2 0 4 \_ 2 K がオン状態のとき、容量素子 2 0 2 \_ 2 K の第 2 の電極には低電源電圧が与えられる。また、容量素子 2 0 2 \_ 2 K には V \_ 2 K - V S S の電圧が与えられる。このように、第 2 の期間において、ノード N 1 \_ 2 K - 1 の電圧は、第 1 の期間におけるノード N 1 \_ 2 K - 1 の電圧が昇圧された値となる。

#### 【 0 0 7 3 】

次に、第 3 の期間では、第 1 の期間と同様にクロック信号 C K 1 がハイレベルになり、クロック信号 C K B 1 がローレベルになる。

#### 【 0 0 7 4 】

このとき、2 K 段目の単位昇圧回路 2 1 1 \_ 2 K において、トランジスタ 2 0 1 \_ 2 K 及びトランジスタ 2 0 4 \_ 2 K がオフ状態になり、トランジスタ 2 0 3 \_ 2 K がオン状態になる。よって、容量素子 2 0 2 \_ 2 K の第 2 の電極の電圧が V H に上昇するため、容量素子 2 0 2 \_ 2 K の第 2 の電極の電圧の上昇に合わせて容量素子 2 0 2 \_ 2 K の第 1 の電極の電圧も上昇し始める。また、第 3 の期間では、2 K - 1 段目の単位昇圧回路 2 1 1 \_ 2 K - 1 において、トランジスタ 2 0 1 \_ 2 K - 1 及びトランジスタ 2 0 4 \_ 2 K - 1 がオン状態になり、トランジスタ 2 0 3 \_ 2 K - 1 がオフ状態になる。トランジスタ 2 0 1 \_ 2 K - 1 がオン状態のときノード N 1 \_ 2 K - 1 と、ノード N 1 \_ 2 K - 2 とが同じ電圧になる。また、トランジスタ 2 0 4 \_ 2 K - 1 がオン状態のとき容量素子 2 0 2 \_ 2 K - 1 の第 2 の電極には低電源電圧が与えられる。また、容量素子 2 0 2 \_ 2 K - 1 には ( V \_ 2 K - 1 ) - V S S の電圧が与えられる。このように第 3 の期間において、ノード N 1 \_ 2 K の電圧は、第 2 の期間におけるノード N 1 \_ 2 K の電圧が昇圧された値となる。

#### 【 0 0 7 5 】

10

20

30

40

50

その後の動作においても上記に示す第1の期間乃至第3の期間の動作が繰り返し行われることにより、昇圧動作が行われる。このとき、nが奇数の場合には第2の期間にて、また、nが偶数の場合には第1の期間及び第3の期間にてトランジスタ205がオン状態になり、容量素子206の第1の電極の電圧が上昇し始め、容量素子206の第1の電極及び第2の電極の間に印加される電圧は、n段目の単位昇圧回路211\_nにおける容量素子202\_nの容量をC<sub>a1</sub>とし、容量素子206の容量をC<sub>b1</sub>とし、トランジスタ205がオフ状態のときのノードN1\_nの電圧をV<sub>a1</sub>とし、トランジスタ205がオフ状態のときの信号OUT1の電圧をV<sub>b1</sub>とし、容量素子206に負荷が電気的に接続された場合の負荷による消費電流が無視できる程度に低いと仮定すると、((C<sub>a1</sub> × V<sub>a1</sub>) + (C<sub>b1</sub> × V<sub>b1</sub>)) / (C<sub>a1</sub> + C<sub>b1</sub>)となり、図3に示す電圧調整回路は、信号IN1の電圧を昇圧し、電圧V<sub>IN1</sub>を昇圧した電圧である信号OUT1を出力信号として出力する。

10

## 【0076】

以上のように、本実施の形態の電圧調整回路の一例では、各単位昇圧回路において昇圧動作を行うことにより、入力された信号の電圧より大きい電圧の信号を出力信号として出力することができる。

## 【0077】

また、本実施の形態の電圧調整回路の一例は、チャネル形成層として高純度化された酸化物半導体層を用いたトランジスタをn段の単位昇圧回路及び出力回路におけるトランジスタに用いた構成である。これにより、電圧調整回路におけるトランジスタのリーク電流を低減し、出力信号の電圧の不要な降下又は上昇を低減することができ、昇圧動作により所望の電圧となるまでの到達速度を速くすることができ、所望の電圧への変換効率を向上させることができる。

20

## 【0078】

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

## 【0079】

## (実施の形態3)

本実施の形態では、本発明の一態様である電圧調整回路の他の一例として降圧回路について説明する。

30

## 【0080】

本実施の形態における電圧調整回路の回路構成の一例について図4を用いて説明する。図4は、本実施の形態における電圧調整回路の回路構成の一例を示す回路図である。

## 【0081】

図4に示す電圧調整回路は、n段(nは2以上の自然数)の単位降圧回路である単位昇圧回路511\_1乃至511\_nと、出力回路512と、を有する。なお、図4では、一例としてnが偶数であるとして示しているが、これに限定されず、奇数であってもよい。

## 【0082】

図4に示すn段の単位降圧回路は、単位降圧回路511\_1乃至単位降圧回路511\_nのn個の単位降圧回路を用いて構成され、m段目(mは2乃至nの自然数)の単位降圧回路511\_mは、m-1段目の単位降圧回路511\_{m-1}に電気的に接続される。

40

## 【0083】

単位降圧回路511\_1乃至単位降圧回路511\_nのそれぞれ、すなわちk段目の単位降圧回路511\_mは、トランジスタ501\_mと、容量素子502\_mと、トランジスタ503\_mと、トランジスタ504\_mと、を有する。

## 【0084】

m段目の単位降圧回路511\_mにおけるトランジスタ501\_mのソース及びドレインの一方は、m-1段目の単位降圧回路511\_{m-1}におけるトランジスタ501\_{m-1}のソース及びドレインの他方に電気的に接続される。m段目の単位降圧回路511\_mにおけるトランジスタ501\_mのソース及びドレインの一方と、m-1段目の単位降圧回路511\_{m-1}におけるトランジスタ501\_{m-1}のソース及びドレインの他方と

50

の接続箇所をノード N 2\_m - 1 ともいい、1 段目の単位降圧回路 5\_1\_1\_n におけるトランジスタ 5\_0\_1\_n のソース及びドレインの一方をノード N 2\_0 ともいう。

【0085】

容量素子 5\_0\_2\_m の第 1 の電極は、トランジスタ 5\_0\_1\_m のソース及びドレインの他方に電気的に接続される。

【0086】

トランジスタ 5\_0\_3\_m は、ソース及びドレインの一方に高電源電圧が与えられ、ソース及びドレインの他方が容量素子 5\_0\_2\_m の第 2 の電極に電気的に接続される。

【0087】

トランジスタ 5\_0\_4\_m は、ソース及びドレインの一方が容量素子 5\_0\_2\_m の第 2 の電極に電気的に接続され、ソース及びドレインの他方に低電源電圧が与えられる。

【0088】

さらに、2K - 1 段目の単位降圧回路 5\_1\_1\_2K - 1 は、トランジスタ 5\_0\_1\_2K - 1 のゲートにクロック信号 CK\_2 が入力され、トランジスタ 5\_0\_3\_2K - 1 のゲートにクロック信号 CK\_2 が入力され、トランジスタ 5\_0\_4\_2K - 1 のゲートにクロック信号 CK\_B\_2 が入力される。

【0089】

また、2K 段目の単位降圧回路 5\_1\_1\_2K は、トランジスタ 5\_0\_1\_2K のゲートがクロック信号線 5\_2\_2 に電気的に接続され、トランジスタ 5\_0\_3\_2K のゲートがクロック信号線 5\_2\_2 に電気的に接続され、トランジスタ 5\_0\_4\_2K のゲートがクロック信号線 5\_2\_1 に電気的に接続される。

【0090】

クロック信号線 5\_2\_1 には、クロック信号 CK\_2 が入力され、クロック信号線 5\_2\_2 には、クロック信号 CK\_B\_2 が入力される。

【0091】

さらに、1 段目の単位降圧回路 5\_1\_1\_1 は、トランジスタ 5\_0\_1\_1 のソース及びドレインの一方に信号 IN\_2 が入力される。

【0092】

出力回路 5\_1\_2 は、n 段目の単位降圧回路 5\_1\_1\_n に電気的に接続される。

【0093】

さらに、トランジスタ 5\_0\_5 は、ソース及びドレインの一方が n 段目の単位降圧回路 5\_1\_n におけるトランジスタ 5\_0\_1\_n のソース及びドレインの他方に電気的に接続される。また、トランジスタ 5\_0\_5 のソース及びドレインの他方の電圧は、電圧調整回路の出力信号である信号 OUT\_2 の電圧になる。

【0094】

さらに、n が奇数の場合にはトランジスタ 5\_0\_5 のゲートにクロック信号 CK\_B\_2 が入力され、n が偶数の場合にはトランジスタ 5\_0\_5 のゲートにクロック信号 CK\_2 が入力される。

【0095】

容量素子 5\_0\_6 は、第 1 の電極がトランジスタ 5\_0\_5 のソース及びドレインの他方に電気的に接続され、第 2 の電極に低電源電圧が与えられる。また、容量素子 5\_0\_6 の容量は、他の単位降圧回路 5\_1\_1\_k における容量素子 5\_0\_2\_k の容量より大きくすることができる。これにより、電圧調整回路の出力信号、すなわち信号 OUT\_2 の電圧状態をより安定させることができる。

【0096】

トランジスタ 5\_0\_1\_m、トランジスタ 5\_0\_3\_m、トランジスタ 5\_0\_4\_m、及びトランジスタ 5\_0\_5 のそれぞれとしては、チャネル形成層としての機能を有する酸化物半導体層を有するトランジスタを用いることができる。なお、チャネル形成層の水素濃度は、 $5 \times 10^{19} \text{ atoms/cm}^3$  以下、好ましくは  $5 \times 10^{18} \text{ atoms/cm}^3$  以下、さらに好ましくは  $5 \times 10^{17} \text{ atoms/cm}^3$  以下とする。該水素濃度は、例えば二

10

20

30

40

50

次イオン質量分析法 (S I M S : Secondary Ion Mass Spectroscopy) による値である。またトランジスタ 501\_k、トランジスタ 503\_k、及びトランジスタ 504\_k、及びトランジスタ 505 のそれぞれのキャリア濃度は、 $1 \times 10^{14} / \text{cm}^3$  以下、好ましくは  $1 \times 10^{12} / \text{cm}^3$  以下とする。

#### 【0097】

クロック信号 CK2 とクロック信号 CKB2 は、それぞれ電圧状態が変化するタイミングが異なるクロック信号であり、例えばクロック信号 CK2 がハイレベルになるとき、クロック信号 CKB2 はローレベルであることが好ましく、クロック信号 CKB2 がハイレベルになるとき、クロック信号 CK2 はローレベルであることが好ましい。クロック信号 CKB2 としては、例えばクロック信号 CK2 の反転信号を用いることができ、クロック信号 CKB2 は、例えばインバータなどのNOT回路を用いてクロック信号 CK2 の電圧状態を反転させることにより生成することができる。クロック信号 CK2 及びクロック信号 CKB2 におけるハイレベル及びローレベルの電圧の値は、適宜設定することができる。また、クロック信号 CK2 は、例えばリングオシレータなどの発振回路とバッファ回路を用いて生成することもできる。また、図4に示す電圧調整回路では、クロック信号 CK2 及びクロック信号 CKB2 のみを用いる場合について示しているが、これに限定されず、本実施の形態における電圧調整回路では、3相以上のクロック信号を用いることもできる。

10

#### 【0098】

以上のように、本実施の形態における電圧調整回路の一例は、n段の単位降圧回路と、n段目の単位降圧回路に電気的に接続された出力回路と、を有し、それぞれの単位降圧回路は、スイッチング素子としての機能を有する複数のトランジスタと、容量素子を有し、複数のトランジスタを選択的にオン状態又はオフ状態にすることにより、電圧調整回路に入力された信号電圧を降圧させ、降圧した電圧を出力回路により電圧調整回路の出力信号として出力する構成である。また、本実施の形態における電圧調整回路の一例は、トランジスタとして、チャネル形成層としての機能を備えた、高純度化された酸化物半導体層を有するトランジスタを用いる。これにより、各ノードの電圧の保持時間を長くすることができ、また、目的の電圧までの到達時間を短くすることができ、電圧変換効率を向上させることができる。

20

#### 【0099】

次に、図4に示す電圧調整回路の動作の一例について説明する。なおここで説明する図4に示す電圧調整回路の動作の一例では、信号IN2をハイレベルとローレベルの2値のデジタル信号とし、トランジスタ 501\_m、トランジスタ 503\_m、トランジスタ 504\_m、及びトランジスタ 505 をN型トランジスタとし、クロック信号 CK2 及びクロック信号 CKB2 がハイレベルとローレベルとが周期的に繰り返されるクロック信号であるとして説明する。

30

#### 【0100】

図4に示す電圧調整回路の動作は、複数の期間に分けて説明することができる。各期間における動作について以下に説明する。

40

まず第1の期間では、クロック信号 CK2 がハイレベルになり、クロック信号 CKB2 がローレベルになる。

#### 【0101】

このとき、2K-1段目の単位降圧回路 511\_2K-1において、トランジスタ 501\_2K-1 及びトランジスタ 503\_2K-1 がオン状態になり、トランジスタ 504\_2K-1 がオフ状態になる。トランジスタ 501\_2K-1 がオン状態のときノード N2\_2K-1 とノード N2\_2K-2 とが同じ電圧になる。このときノード N2\_2K-1 の電圧を V\_2K-1 とする。またトランジスタ 503\_2K-1 がオン状態のとき容量素子 502\_2K-1 の第2の電極には高電源電圧が与えられる。また、容量素子 502\_2K-1 には ( $V_{2K-1}$ ) - VDD の電圧が与えられる。

#### 【0102】

50

次に、第2の期間では、クロック信号CK2がローレベルになり、クロック信号CKB2がハイレベルになる。

#### 【0103】

このとき、2K-1段目の単位降圧回路511\_2K-1において、トランジスタ501\_2K-1及びトランジスタ503\_2K-1がオフ状態になり、トランジスタ504\_2K-1がオン状態になる。よって、容量素子502\_2K-1の第2の電極の電圧がV<sub>L</sub>に下降するため、容量素子502\_2K-1の第2の電極の電圧の下降に合わせて容量素子502\_2K-1の第1の電極の電圧も下降し始める。また、第2の期間では、2K段目の単位降圧回路511\_2Kにおいて、トランジスタ501\_2K及びトランジスタ503\_2Kがオン状態になる。トランジスタ501\_2Kがオン状態のときノードN2\_2KとノードN2\_2K-1とが同じ電圧になる。このとき、ノードN2\_2Kの電圧をV\_2Kとする。また、トランジスタ503\_2Kがオン状態のとき、容量素子502\_2Kの第2の電極には高電源電圧が与えられる。また、容量素子502\_2Kには、V\_2K-VDDの電圧が与えられる。このように、第2の期間において、ノードN2\_2K-1の電圧は、第1の期間におけるノードN2\_2Kの電圧が降圧された値となる。

10

#### 【0104】

次に、第3の期間では、クロック信号CK2がハイレベルになり、クロック信号CKB2がローレベルになる。

#### 【0105】

このとき、2K段目の単位降圧回路511\_2Kにおいて、トランジスタ501\_2K及びトランジスタ503\_2Kがオフ状態になり、トランジスタ504\_2Kがオン状態になる。容量素子502\_2Kの第2の電極の電圧がV<sub>L</sub>に下降するため、容量素子502\_2Kの第2の電極の電圧の下降に合わせて容量素子502\_2Kの第1の電極の電圧も下降し始める。また、第3の期間では、2K-1段目の単位降圧回路511\_2K-1において、トランジスタ501\_2K-1及びトランジスタ503\_2K-1がオン状態になりトランジスタ504\_2K-1がオフ状態になる。トランジスタ501\_2K-1がオン状態のときノードN2\_2K-1とノードN2\_2Kとが同じ電圧になる。また、トランジスタ503\_2K-1がオン状態のとき容量素子502\_2K-1の第2の電極には高電源電圧が与えられる。また、容量素子502\_2K-1には(V\_2K-1)-VDDの電圧が与えられる。このように第3の期間において、ノードN2\_2Kの電圧は、第2の期間におけるノードN2\_2Kの電圧が降圧された値となる。

20

30

#### 【0106】

その後の動作においても上記に示す第1の期間乃至第3の期間の動作が繰り返し行われることにより、降圧動作が行われる。このとき、nが奇数の場合には第2の期間にて、また、nが偶数の場合には第1の期間及び第3の期間にてトランジスタ505がオン状態になり、容量素子506の第1の電極の電圧が下降し始め、容量素子506の第1の電極及び第2の電極の間に印加される電圧は、n段目の単位降圧回路511\_nの容量素子502\_nの容量をC<sub>a2</sub>とし、容量素子506の容量をC<sub>b2</sub>とし、トランジスタ505がオフ状態のときのノードN2\_nの電圧をV<sub>a2</sub>とし、トランジスタ505がオフ状態のときの信号OUT2の電圧をV<sub>b2</sub>とし、容量素子506に負荷が電気的に接続された場合の負荷による消費電流が無視できる程度に低いと仮定すると、((C<sub>a2</sub> × V<sub>a2</sub>) + (C<sub>b2</sub> × V<sub>b2</sub>)) / (C<sub>a2</sub> + C<sub>b2</sub>)となり、図4に示す電圧調整回路は、信号IN2の電圧の降圧し、電圧V<sub>IN2</sub>を降圧した電圧である信号OUT2を出力信号として出力する。

40

#### 【0107】

以上のように、本実施の形態の電圧調整回路の一例では、各単位降圧回路において降圧動作を行うことにより、入力された信号の電圧より小さい電圧の信号を出力信号として出力することができる。

#### 【0108】

10

20

30

40

50

また、本実施の形態の電圧調整回路の一例は、チャネル形成層として高純度化された酸化物半導体層を用いたトランジスタをn段の単位降圧回路及び出力回路におけるトランジスタに用いた構成である。これにより、電圧調整回路におけるトランジスタのリーク電流を低減し、出力信号の電圧の不要な降下又は上昇を低減し、降圧動作により所望の電圧となるまでの到達速度を速くすることができ、所望の電圧への変換効率を向上させることができる。

#### 【0109】

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

#### 【0110】

##### (実施の形態4)

10

本実施の形態は、本明細書で開示する電圧調整回路を構成するトランジスタに適用できる薄膜トランジスタの例を示す。

#### 【0111】

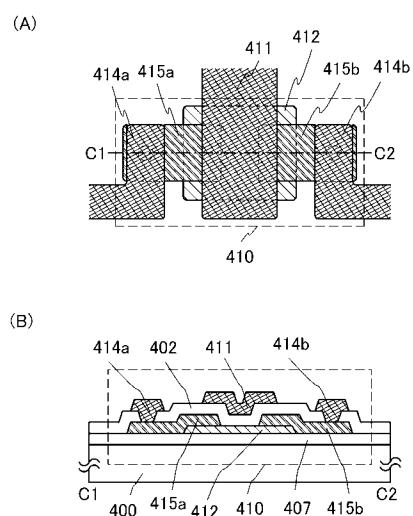

本実施の形態のトランジスタ及びトランジスタの作製方法の一形態を、図5及び図6を用いて説明する。

#### 【0112】

図5(A)(B)にトランジスタの平面及び断面構造の一例を示す。図5(A)(B)に示すトランジスタ410は、トップゲート構造の薄膜トランジスタの一つである。

#### 【0113】

図5(A)は、トップゲート構造のトランジスタ410の平面図であり、図5(B)は、図5(A)の線C1-C2における断面図である。

20

#### 【0114】

トランジスタ410は、絶縁表面を有する基板400上に、絶縁層407、酸化物半導体層412、ソース電極層又はドレイン電極層415a、及びソース電極層又はドレイン電極層415b、ゲート絶縁層402、ゲート電極層411を含み、ソース電極層又はドレイン電極層415a、及びソース電極層又はドレイン電極層415bのそれぞれに配線層414a、配線層414bが接して設けられ電気的に接続されている。

#### 【0115】

また、トランジスタ410をシングルゲート構造のトランジスタとするが、本実施の形態のトランジスタを、チャネル形成領域を複数有するマルチゲート構造のトランジスタとしてもよい。

30

#### 【0116】

以下、図6(A)乃至(E)を用い、絶縁表面を有する基板400上にトランジスタ410を作製する工程を説明する。

#### 【0117】

絶縁表面を有する基板400に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板400としては、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

40

#### 【0118】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料を用いることができる。なお、酸化ホウ素( $B_2O_3$ )と比較して酸化バリウム( $BaO$ )を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$ より $BaO$ を多く含むガラス基板を用いることが好ましい。

#### 【0119】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いてもよい。他にも、結晶化ガラスなどを用いることができる。また、プラスチック基板等も適宜用いることができる。また、基板としてシリコンなどの半導

50

体基板を用いることもできる。

【0120】

まず、絶縁表面を有する基板400上に下地膜となる絶縁層407を形成する。酸化物半導体層412と接する絶縁層407としては、酸化シリコン層、酸化窒化シリコン層( $\text{SiO}_x\text{N}_y$ とも呼ぶ、ただし、 $x > y > 0$ )、酸化アルミニウム層、又は酸化窒化アルミニウム層などの酸化物絶縁層を用いると好ましい。絶縁層407の形成方法としては、プラズマCVD法又はスパッタリング法等を用いることができるが、絶縁層407中に水素が多量に含まれないようにするためにには、スパッタリング法で絶縁層407を成膜することが好ましい。

【0121】

本実施の形態では、絶縁層407として、スパッタリング法により酸化シリコン層を形成する。基板400を処理室へ搬送し、水素及び水分が除去された高純度酸素を含むスパッタリングガスを導入しシリコン半導体のターゲットを用いて、基板400に絶縁層407として、酸化シリコン層を成膜する。また、基板400は、室温でもよいし、加熱されていてもよい。

【0122】

例えば、石英(好ましくは合成石英)を用い、基板温度108°C、基板とターゲットとの距離(T-S間距離)を60mm、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により酸化シリコン膜を成膜する。膜厚は100nmとする。なお、石英(好ましくは合成石英)に代えて、シリコンターゲットを酸化シリコン膜を成膜するためのターゲットとして用いることができる。なお、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

【0123】

この場合において、処理室内の残留水分を除去しつつ絶縁層407を成膜することが好ましい。絶縁層407に水素、水酸基又は水分が含まれないようにするためである。

【0124】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを備えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜し絶縁層407に含まれる不純物の濃度を低減できる。

【0125】

絶縁層407を成膜する際に用いるスパッタリングガスとしては、水素、水、水酸基又は水素化物などの不純物が、数濃度ppm程度、数濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

【0126】

スパッタリング法にはスパッタリング用電源に高周波電源を用いるRFスパッタリング法、直流電源を用いるDCスパッタリング法、又はパルス的にバイアスを与えるパルスDCスパッタリング法などがある。RFスパッタリング法は主に絶縁膜を成膜する場合に用いられ、DCスパッタリング法は主に金属膜を成膜する場合に用いられる。

【0127】

また、材料の異なるターゲットを複数設置できる多元スパッタリング装置もある。多元スパッタリング装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

【0128】

また、チャンバー内部に磁石機構を備えたマグнетロンスパッタリング法を用いるスパッタリング装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタリング法を用いるスパッタリング装置がある。

10

20

30

40

50

## 【0129】

また、スパッタリング法を用いる成膜方法として、成膜中にターゲット物質とスパッタリングガス成分とを化学反応させてそれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法もある。

## 【0130】

また、絶縁層407は積層構造でもよく、例えば、絶縁層407を、基板400側から窒化シリコン層、窒化酸化シリコン層( $\text{SiN}_{x\text{--}y}$ とも呼ぶ、ただし、 $x > y > 0$ )、窒化アルミニウム層、又は窒化酸化アルミニウムなどの窒化物絶縁層と、上記酸化物絶縁層とを積層する積層構造としてもよい。

## 【0131】

例えば、酸化シリコン層と基板との間に水素及び水分が除去された高純度窒素を含むスパッタリングガスを導入しシリコンターゲットを用いて窒化シリコン層を成膜する。この場合においても、酸化シリコン層と同様に、処理室内の残留水分を除去しつつ窒化シリコン層を成膜することが好ましい。

10

## 【0132】

なお、窒化シリコン層を形成する場合も、成膜時に基板を加熱してもよい。

## 【0133】

絶縁層407として窒化シリコン層と酸化シリコン層とを積層する場合、窒化シリコン層と酸化シリコン層を、同じ処理室において、共通のシリコンターゲットを用いて成膜することができる。先に窒素を含むスパッタリングガスを導入して、処理室内に装着されたシリコンターゲットを用いて窒化シリコン層を形成し、次に、スパッタリングガスを酸素を含むスパッタリングガスに切り替えて同じシリコンターゲットを用いて酸化シリコン層を成膜する。窒化シリコン層と酸化シリコン層とを大気に曝露せずに連続して形成することができるため、窒化シリコン層表面に水素や水分などの不純物が吸着することを防止することができる。

20

## 【0134】

次に、絶縁層407上に、膜厚2nm以上200nm以下の酸化物半導体膜を形成する。

## 【0135】

また、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室で絶縁層407が形成された基板400を予備加熱し、基板400に吸着した水素、水分などの不純物を脱離し排気することができる。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、後に形成するゲート絶縁層402の成膜前の基板400に行ってもよいし、後に形成するソース電極層又はドレイン電極層415a及びソース電極層又はドレイン電極層415bまで形成した基板400にも同様に行ってもよい。

30

## 【0136】

なお、酸化物半導体膜をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、絶縁層407の表面に付着しているゴミを除去することができる。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に高周波電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

40

## 【0137】

また、酸化物半導体膜を、スパッタリング法により成膜する。酸化物半導体膜としては、 $\text{In-Ga-Zn-O}$ 系、 $\text{In-Sn-Zn-O}$ 系、 $\text{In-Al-Zn-O}$ 系、 $\text{Sn-Ga-Zn-O}$ 系、 $\text{Al-Ga-Zn-O}$ 系、 $\text{Sn-Al-Zn-O}$ 系、 $\text{In-Zn-O}$ 系、 $\text{Sn-Zn-O}$ 系、 $\text{Al-Zn-O}$ 系、 $\text{In-O}$ 系、 $\text{In-Sn-O}$ 系、 $\text{Sn-O}$ 系、 $\text{Zn-O}$ 系の酸化物半導体膜を用いることができる。本実施の形態では、酸化物半導体膜を $\text{In-Ga-Zn-O}$ 系金属酸化物ターゲットを用いてスパッタリング法により成膜す

50

る。また、希ガス（代表的にはアルゴン）雰囲気下、酸素雰囲気下、又は希ガス（代表的にはアルゴン）及び酸素雰囲気下においてスパッタリング法により酸化物半導体膜を形成することができる。また、スパッタリング法を用いる場合、 $\text{SiO}_2$ を2重量%以上10重量%以下含むターゲットを用いて成膜を行ってもよい。

#### 【0138】

また、酸化物半導体膜を成膜する際に用いるスパッタリングガスとしては、水素、水、水酸基又は水素化物などの不純物が、数濃度 ppm 程度、数濃度 ppb 程度まで除去された高純度ガスを用いることが好ましい。

#### 【0139】

また、酸化物半導体膜をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、例えば、 $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 1$  [ molar 数比 ] の組成比である金属酸化物ターゲットを用いることができる。また、上記に示すターゲットに限定されず、例えば、 $\text{In}_2\text{O}_3 : \text{Ga}_2\text{O}_3 : \text{ZnO} = 1 : 1 : 2$  [ molar 数比 ] の組成比である金属酸化物ターゲットを用いてもよい。また、作製される金属酸化物ターゲットのうち、全体の体積に対して全体の体積から空隙などが占める空間を除いた部分の体積の割合（充填率ともいう）は、90%以上100%以下、好ましくは95%以上99.9%である。充填率の高い金属酸化物ターゲットを用いることにより形成した酸化物半導体膜は、緻密な膜となる。

#### 【0140】

減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタリングガスを導入し、金属酸化物をターゲットとして基板 40 上に酸化物半導体膜を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを備えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水 ( $\text{H}_2\text{O}$ ) など水素原子を含む化合物（より好ましくは炭素原子を含む化合物も含む）等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱してもよい。

#### 【0141】

成膜条件の一例としては、基板温度室温、基板とターゲットとの距離を 60 mm、圧力 0.4 Pa、直流 (DC) 電源 0.5 kW、酸素及びアルゴン（酸素流量 15 sccm : アルゴン流量 30 sccm = 1 : 2）雰囲気下の条件が適用される。なお、パルス直流 (DC) 電源を用いると、成膜時に発生する粉状物質（パーティクル、ゴミともいう）が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは 5 nm 以上 30 nm 以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

#### 【0142】

次に、酸化物半導体膜を第 1 のフォトリソグラフィ工程により島状の酸化物半導体層 41 2 に加工する（図 6 (A) 参照）。また、島状の酸化物半導体層 41 2 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0143】

なお、ここで酸化物半導体膜のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

#### 【0144】

ドライエッチングに用いるエッチングガスとしては、塩素を含むガス（塩素系ガス、例えば塩素 ( $\text{Cl}_2$ )、塩化硼素 ( $\text{BCl}_3$ )、塩化珪素 ( $\text{SiCl}_4$ )、四塩化炭素 ( $\text{CCl}_4$ ) など）が好ましい。

10

20

30

40

50

## 【0145】

また、フッ素を含むガス（フッ素系ガス、例えば四弗化炭素（ $\text{CF}_4$ ）、弗化硫黄（ $\text{SF}_6$ ）、弗化窒素（ $\text{NF}_3$ ）、トリフルオロメタン（ $\text{CHF}_3$ ）など）、臭化水素（ $\text{HBr}$ ）、酸素（ $\text{O}_2$ ）、これらのガスにヘリウム（ $\text{He}$ ）やアルゴン（ $\text{Ar}$ ）などの希ガスを添加したガス、などを用いることができる。

## 【0146】

ドライエッチング法としては、平行平板型RIE（Reactive Ion Etching）法や、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。10

## 【0147】

ウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO 07N（関東化学社製）を用いてもよい。

## 【0148】

また、ウェットエッチング後のエッチング液は、エッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。20

## 【0149】

所望の加工形状にエッチングできるように、材料に合わせてエッチング条件（エッチング液、エッチング時間、温度等）を適宜調節する。

## 【0150】

本実施の形態では、エッチング液として磷酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッチング法により、酸化物半導体膜を島状の酸化物半導体層412に加工する。

## 【0151】

本実施の形態では、酸化物半導体層412に、第1の加熱処理を行う。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。30

ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、酸化物半導体層への水や水素の混入を防ぐことにより、含有水素濃度が低い酸化物半導体層を得る。この第1の加熱処理によって酸化物半導体層412の脱水化又は脱水素化を行うことができる。

## 【0152】

なお、加熱処理装置は、電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA（Gas Rapid Thermal Anneal）装置、LRTA（Lamp Rapid Thermal Anneal）装置等のRTA（Rapid Thermal Anneal）装置を用いることができる。40

LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性ガスが用いられる。

## 【0153】

例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

## 【0154】

なお、第1の加熱処理においては、窒素、又はヘリウム、ネオン、若しくはアルゴン等の

10

20

30

40

50

希ガスに、水、水素などが含まれないことが好ましい。例えば、加熱処理装置に導入する窒素、又はヘリウム、ネオン、若しくはアルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

#### 【0155】

また、第1の加熱処理の条件、又は酸化物半導体膜の材料によっては、酸化物半導体層412が結晶化し、微結晶層又は多結晶層となる場合もある。例えば、結晶化率が90%以上、又は80%以上の微結晶の酸化物半導体層となる場合もある。また、第1の加熱処理の条件、又は酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半導体層となる場合もある。また、非晶質の酸化物半導体の中に微結晶部(粒径1nm以上20nm以下(代表的には2nm以上4nm以下))が混在する酸化物半導体層となる場合もある。

10

#### 【0156】

また、第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

#### 【0157】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にソース電極及びドレイン電極を積層させた後、ソース電極及びドレイン電極上にゲート絶縁層を形成した後、のいずれで行ってもよい。

20

#### 【0158】

次に、絶縁層407及び酸化物半導体層412上に、導電膜を形成する。例えば、スパッタリング法や真空蒸着法で導電膜を形成すればよい。導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、又は上述した元素を成分とする合金、若しくは上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、イットリウムのいずれか一又は複数から選択された材料を用いてもよい。また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。また、Alに、チタン(Ti)、タンタル(Ta)、タンクステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、若しくは窒化膜を用いてもよい。

30

#### 【0159】

第2のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bを形成した後、レジストマスクを除去する(図6(B)参照)。なお、形成されたソース電極層、ドレイン電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。

40

#### 【0160】

本実施の形態ではソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bとしてスパッタリング法により膜厚150nmのチタン膜を形成する。

#### 【0161】

なお、導電膜のエッチングの際に、酸化物半導体層412が除去されて、その下の絶縁層407が露出しないように、酸化物半導体膜及び絶縁膜のそれぞれの材料及びエッチング条件を適宜調節する。

#### 【0162】

本実施の形態では、導電膜としてTi膜を用いて、酸化物半導体層412には、In-Ga-Zn-O系酸化物半導体を用いて、エッチャントとしてアンモニア過水(アンモニア、水、過酸化水素水の混合液)を用いる。

50

## 【0163】

なお、第2のフォトリソグラフィ工程では、酸化物半導体層412の一部がエッチングされ、溝部(凹部)を有する酸化物半導体層となることもある。また、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0164】

第2のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体層412上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成される薄膜トランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm~数10nmと極めて波長が短い超紫外線(Extreme Ultraviolet)を用いて第2のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄膜トランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値を極めて小さくすることができるため、低消費電力化も図ることができる。

10

## 【0165】

次に、絶縁層407、酸化物半導体層412、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415b上にゲート絶縁層402を形成する(図6(C)参照)。

20

## 【0166】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。なお、ゲート絶縁層402中に水素が多量に含まれないようにするために、スパッタリング法でゲート絶縁層402を成膜することが好ましい。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

30

## 【0167】

また、ゲート絶縁層402としては、例えばHfO<sub>x</sub>(x>0)などを用いることもできる。ゲート絶縁層402としてHfO<sub>x</sub>などを用いることにより、酸化物半導体層側からゲート電極に向かって流れるリーク電流を低減することができる。

## 【0168】

また、ゲート絶縁層402を、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415b側から酸化シリコン層と窒化シリコン層を積層した構造とすることもできる。例えば、第1のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層(SiO<sub>x</sub>(x>0))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層としてスパッタリング法により膜厚50nm以上200nm以下の窒化シリコン層(SiN<sub>y</sub>(y>0))を積層して、膜厚100nmのゲート絶縁層としてもよい。本実施の形態では、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により膜厚100nmの酸化シリコン層を形成する。

40

## 【0169】

次に、第3のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってゲート絶縁層402の一部を除去して、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bに達する開口421a、421bを形成する(図6(D)参照)。

## 【0170】

次に、ゲート絶縁層402、及び開口421a、421b上に導電膜を形成した後、第4

50

のフォトリソグラフィ工程によりゲート電極層 411、配線層 414a、414b を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0171】

また、ゲート電極層 411、配線層 414a、414b を形成するための導電膜は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

#### 【0172】

例えば、ゲート電極層 411、配線層 414a、414b の 2 層の積層構造としては、アルミニウム層上にモリブデン層が積層された 2 層の積層構造、又は銅層上にモリブデン層を積層した 2 層構造、又は銅層上に窒化チタン層若しくは窒化タンタル層を積層した 2 層構造、窒化チタン層とモリブデン層とを積層した 2 層構造とすることが好ましい。3 層の積層構造としては、タングステン層又は窒化タングステン層と、アルミニウムとシリコンの合金又はアルミニウムとチタンの合金と、窒化チタン層又はチタン層とを積層した積層とすることが好ましい。なお、透光性を有する導電膜を用いてゲート電極層を形成することもできる。透光性を有する導電膜としては、透光性導電性酸化物等をその例に挙げることができる。

#### 【0173】

本実施の形態ではゲート電極層 411、配線層 414a、414b としてスパッタリング法により膜厚 150 nm のチタン膜を形成する。

#### 【0174】

次に、不活性ガス雰囲気下、又は酸素ガス雰囲気下で第 2 の加熱処理（好ましくは 200 以上 400 以下、例えば 250 以上 350 以下）を行う。本実施の形態では、窒素雰囲気下で 250 、 1 時間の第 2 の加熱処理を行う。また、第 2 の加熱処理は、トランジスタ 410 上に保護絶縁層や平坦化絶縁層を形成してから行ってもよい。

#### 【0175】

さらに、大気中、100 以上 200 以下、1 時間以上 30 時間以下の加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回繰り返して行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。

#### 【0176】

以上の工程で、水素、水分、水素化物、水酸化物の濃度が低減された酸化物半導体層 412 を有するトランジスタ 410 を形成することができる（図 6（E）参照）。

#### 【0177】

また、トランジスタ 410 上に保護絶縁層や、平坦化のための平坦化絶縁層を設けてもよい。例えば、保護絶縁層として酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。

#### 【0178】

また、平坦化絶縁層としては、ポリイミド、アクリル樹脂、ベンゾシクロブテン樹脂、ポリアミド、エポキシ樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k 材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁層を形成してもよい。

#### 【0179】

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成された Si-O-Si 結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いてもよい。また、有機基はフルオロ基を有して

10

20

30

40

50

いてもよい。

【0180】

平坦化絶縁層の形成法は、特に限定されず、その材料に応じて、スパッタリング法、SOG法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーティング、カーテンコーティング、ナイフコーティング等を用いることができる。

【0181】

上記のように、酸化物半導体膜を成膜するに際し、成膜時の雰囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより、酸化物半導体膜の安定化を図ることができる。

10

【0182】

また、本実施の形態に示すトランジスタと同一工程で本発明の一態様の電圧調整回路における容量素子を形成することもできる。トランジスタ及び容量素子を同一工程で形成することにより、工程数の増加を低減することができる。

【0183】

上記構造のトランジスタにすることにより、安定な電気特性を有し信頼性の高いトランジスタを提供することができる。また、該トランジスタはリーク電流が低いため、該トランジスタを用いて本発明の一態様である電圧調整回路を構成することにより、所望の値の電圧への到達速度を格段に向上させることができる。

20

【0184】

なお、本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0185】

（実施の形態5）

本実施の形態は、本明細書で開示する電圧調整回路を構成するトランジスタに適用できる薄膜トランジスタの他の例を示す。なお、実施の形態4と同一部分又は同様な機能を有する部分、及び工程は、実施の形態4と同様とすればよく、その繰り返しの説明は適宜省略する。また、同じ箇所の詳細な説明も適宜省略する。

30

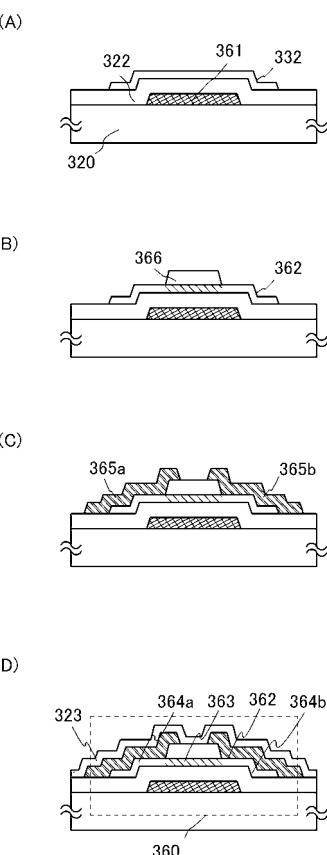

【0186】

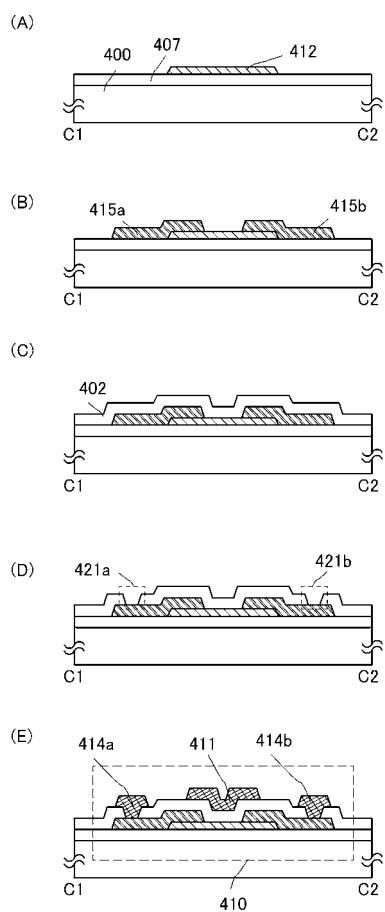

本実施の形態のトランジスタ及びトランジスタの作製方法の一形態を、図7及び図8を用いて説明する。

【0187】

図7(A)(B)にトランジスタの平面及び断面構造の一例を示す。図7(A)(B)に示すトランジスタ460は、トップゲート構造の薄膜トランジスタの一つである。

【0188】

図7(A)は、トップゲート構造のトランジスタ460の平面図であり、図7(B)は図7(A)の線D1-D2における断面図である。

【0189】

トランジスタ460は、絶縁表面を有する基板450上に、絶縁層457、ソース電極層又はドレイン電極層465a(465a1、465a2)、酸化物半導体層462、ソース電極層又はドレイン電極層465b、配線層468、ゲート絶縁層452、ゲート電極層461(461a、461b)を含み、ソース電極層又はドレイン電極層465a(465a1、465a2)は配線層468を介して配線層464と電気的に接続している。また、図示していないが、ソース電極層又はドレイン電極層465bもゲート絶縁層452に設けられた開口において他の配線層と電気的に接続する。

40

【0190】

以下、図8(A)乃至(E)を用い、絶縁表面を有する基板450上にトランジスタ460を作製する工程を説明する。

【0191】

まず、絶縁表面を有する基板450上に下地膜となる絶縁層457を形成する。

【0192】

50

本実施の形態では、絶縁層457として、スパッタリング法により酸化シリコン層を形成する。基板450を処理室へ搬送し、水素及び水分が除去された高純度酸素を含むスパッタリングガスを導入しシリコンターゲット又は石英(好ましくは合成石英)を用いて、基板450に絶縁層457として、酸化シリコン層を成膜する。なお、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

#### 【0193】

例えば、純度が6Nであり、石英(好ましくは合成石英)をターゲットとして用い、基板温度108、基板とターゲットとの距離(T-S間距離)を60mm、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により酸化シリコン膜を成膜する。膜厚は100nmとする。なお、石英(好ましくは合成石英)に代えてシリコンターゲットを酸化シリコン膜を成膜するためのターゲットとして用いることができる。10

#### 【0194】

この場合において、処理室内の残留水分を除去しつつ絶縁層457を成膜することが好ましい。絶縁層457に水素、水酸基又は水分が含まれないようにするためである。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜し絶縁層457に含まれる不純物の濃度を低減できる。

#### 【0195】

絶縁層457を成膜する際に用いるスパッタリングガスとしては、水素、水、水酸基又は水素化物などの不純物が、数濃度ppm程度、数濃度ppb程度まで除去された高純度ガスを用いることが好ましい。20

#### 【0196】

また、絶縁層457は積層構造でもよく、例えば、基板450側から窒化シリコン層、窒化酸化シリコン層、窒化アルミニウム層、窒化酸化アルミニウム層などの窒化物絶縁層と、上記酸化物絶縁層とを積層する積層構造としてもよい。

#### 【0197】

例えば、酸化シリコン層と基板上に水素及び水分が除去された高純度窒素を含むスパッタリングガスを導入しシリコンターゲットを用いて窒化シリコン層を成膜し、その後、酸化シリコン層を成膜する。この場合においても、酸化シリコン層と同様に、処理室内の残留水分を除去しつつ窒化シリコン層を成膜することが好ましい。30

#### 【0198】

次に、絶縁層457上に、導電膜を形成し、第1のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層又はドレイン電極層465a1、465a2を形成した後、レジストマスクを除去する(図8(A)参照)。ソース電極層又はドレイン電極層465a1、465a2は断面図では分断されて示されているが、連続した膜である。なお、形成されたソース電極層、ドレイン電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。

#### 【0199】

ソース電極層又はドレイン電極層465a1、465a2の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニア、ベリリウム、イットリウムのいずれか一又は複数から選択された材料を用いてもよい。また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。また、Alに、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、若しくは窒化膜を用いてもよい。4050

**【0200】**

本実施の形態ではソース電極層又はドレイン電極層465a1、465a2としてスパッタリング法により膜厚150nmのチタン膜を形成する。

**【0201】**

次に、絶縁層457上に、膜厚2nm以上200nm以下の酸化物半導体膜を形成する。

**【0202】**

次に、酸化物半導体膜を形成し、第2のフォトリソグラフィ工程により島状の酸化物半導体層462に加工する(図8(B)参照)。本実施の形態では、酸化物半導体膜としてIn-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタリング法により成膜する。

**【0203】**

減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタリングガスを導入し、金属酸化物をターゲットとして基板450上に酸化物半導体膜を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを備えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も含む)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱してもよい。

10

20

**【0204】**

酸化物半導体膜を成膜する際に用いるスパッタリングガスとしては、水素、水、水酸基又は水素化物などの不純物が、数濃度ppm程度、数濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

**【0205】**

成膜条件の一例としては、基板温度室温、基板とターゲットの距離を60mm、圧力0.4Pa、直流(DC)電源0.5kW、酸素及びアルゴン(酸素流量15sccm:アルゴン流量30sccm=1:2)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質が軽減でき、膜厚分布も均一となるため好ましい。酸化物半導体膜は、好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

30

**【0206】**

本実施の形態では、エッチング液として磷酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッチング法により、酸化物半導体膜を島状の酸化物半導体層462に加工する。

**【0207】**

本実施の形態では、酸化物半導体層462に、第1の加熱処理を行う。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、酸化物半導体層への水や水素の混入を防ぎ、酸化物半導体層を得る。この第1の加熱処理によって酸化物半導体層462の脱水化又は脱水素化を行うことができる。

40

**【0208】**

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。例えば、第1の加熱処理として、650~700の高温に加熱した不活性ガス中に基板を移動させ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

50

## 【0209】

なお、第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

## 【0210】

また、第1の加熱処理の条件、又は酸化物半導体層の材料によっては、酸化物半導体層462が結晶化し、微結晶膜又は多結晶膜となる場合もある。

## 【0211】

また、第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

## 【0212】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にさらにソース電極及びドレイン電極を積層させた後、ソース電極及びドレイン電極上にゲート絶縁層を形成した後、のいずれで行ってもよい。

## 【0213】

次に、絶縁層457及び酸化物半導体層462上に、導電膜を形成し、第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層又はドレイン電極層465b、配線層468を形成した後、レジストマスクを除去する(図8(C)参照)。ソース電極層又はドレイン電極層465b、配線層468はソース電極層又はドレイン電極層465a1、465a2と同様な材料及び工程で形成すればよい。

## 【0214】

本実施の形態ではソース電極層又はドレイン電極層465b、配線層468を形成するための導電膜としてスパッタリング法により膜厚150nmのチタン膜を形成する。本実施の形態では、ソース電極層又はドレイン電極層465a1、465a2とソース電極層又はドレイン電極層465bに同じチタン膜を用いる例のため、ソース電極層又はドレイン電極層465a1、465a2とソース電極層又はドレイン電極層465bとはエッチングにおいて選択比がとれない。よって、ソース電極層又はドレイン電極層465a1、465a2が、ソース電極層又はドレイン電極層465bのエッチング時にエッチングされないように、酸化物半導体層462に覆われないソース電極層又はドレイン電極層465a2上に配線層468を設けている。ソース電極層又はドレイン電極層465a1、465a2とソース電極層又はドレイン電極層465bとにエッチング工程において高い選択比を有する異なる材料を用いる場合には、エッチング時にソース電極層又はドレイン電極層465a2を保護する配線層468は、必ずしも設けなくてもよい。

## 【0215】

なお、導電膜のエッチングの際に、酸化物半導体層462が除去されないように、導電膜及び酸化物半導体膜のそれぞれの材料及びエッチング条件を適宜調節する。

## 【0216】

本実施の形態では、導電膜としてTi膜を用いて、酸化物半導体層462にはIn-Ga-Zn-O系酸化物半導体を用いて、エッチャントとしてアンモニア過水(アンモニア、水、過酸化水素水の混合液)を用いる。

## 【0217】

なお、第3のフォトリソグラフィ工程では、酸化物半導体層462の一部がエッチングされ、溝部(凹部)を有する酸化物半導体層となることもある。また、ソース電極層又はドレイン電極層465b、配線層468を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

10

20

30

40

50

## 【0218】

次に、絶縁層457、酸化物半導体層462、ソース電極層又はドレイン電極層465a1、465a2、及びソース電極層又はドレイン電極層465b上にゲート絶縁層452を形成する。

## 【0219】

ゲート絶縁層452は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。なお、ゲート絶縁層452中に水素が多量に含まれないようにするためにには、スパッタリング法でゲート絶縁層452を成膜することが好ましい。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。10

## 【0220】

また、ゲート絶縁層452としては、例えば $HfO_x$ ( $x > 0$ )などを用いることもできる。ゲート絶縁層452として $HfO_x$ などを用いることにより、酸化物半導体層側からゲート電極に向かって流れるリーク電流を低減することができる。

## 【0221】

ゲート絶縁層452は、ソース電極層又はドレイン電極層465a1、465a2、ソース電極層又はドレイン電極層465b側から酸化シリコン層と窒化シリコン層を積層した構造とすることもできる。本実施の形態では、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により膜厚100nmの酸化シリコン層を形成する。20

## 【0222】

次に、第4のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってゲート絶縁層452の一部を除去して、配線層468に達する開口423を形成する(図8(D)参照)。図示しないが開口423の形成時にソース電極層又はドレイン電極層465bに達する開口を形成してもよい。本実施の形態では、ソース電極層又はドレイン電極層465bへの開口はさらに層間絶縁層を積層した後に形成し、電気的に接続する配線層を開口に形成する例とする。

## 【0223】

次に、ゲート絶縁層452、及び開口423上に導電膜を形成した後、第5のフォトリソグラフィ工程によりゲート電極層461(461a、461b)、配線層464を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。30

## 【0224】

また、ゲート電極層461(461a、461b)、配線層464を形成するための導電膜は、モリブデン、チタン、クロム、タンタル、タンクステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

## 【0225】

本実施の形態ではゲート電極層461(461a、461b)、配線層464の形成するための導電膜としてスパッタリング法により膜厚150nmのチタン膜を形成する。40

## 【0226】

次に、不活性ガス雰囲気下、又は酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。本実施の形態では、窒素雰囲気下で250、1時間の第2の加熱処理を行う。また、第2の加熱処理は、トランジスタ460上に保護絶縁層や平坦化絶縁層を形成してから行ってもよい。

## 【0227】

さらに、大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。この加熱処理は、一定の加熱温度を保持して加熱してもよいし、室温から、50

100 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回繰り返して行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。

**【0228】**

以上の工程で、水素、水分、水素化物、水酸化物の濃度が低減された酸化物半導体層 462 を有するトランジスタ 460 を形成することができる（図 8（E）参照）。

**【0229】**

また、トランジスタ 460 上に保護絶縁層や、平坦化のための平坦化絶縁層を設けてもよい。なお、図示しないが、ゲート絶縁層 452、保護絶縁層や平坦化絶縁層にソース電極層又はドレイン電極層 465b に達する開口を形成し、その開口に、ソース電極層又はドレイン電極層 465b と電気的に接続する配線層を形成する。

10

**【0230】**

上記のように酸化物半導体膜を成膜するに際し、成膜時の雰囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

**【0231】**

また、本実施の形態に示すトランジスタと同一工程で本発明の一態様の電圧調整回路における容量素子を形成することもできる。トランジスタ及び容量素子を同一工程で形成することにより、工程数の増加を低減することができる。

20

**【0232】**

上記構造のトランジスタにすることにより、安定な電気特性を有し信頼性の高いトランジスタを提供することができる。また、該トランジスタはリーク電流が低いため、該トランジスタを用いて本発明の一態様である電圧調整回路を構成することにより、所望の値の電圧への到達速度を格段に向上させることができる。また、該トランジスタを用いて本発明の一態様である電圧調整回路を構成することにより、安定な電気特性を有し信頼性の高い電圧調整回路を提供することができる。

**【0233】**

なお、本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【0234】**

（実施の形態 6）

30

本実施の形態は、本明細書で開示する電圧調整回路を構成するトランジスタに適用できる薄膜トランジスタの他の例を示す。なお、実施の形態 4 又は実施の形態 5 と同一部分又は同様な機能を有する部分、及び工程は、実施の形態 4 又は実施の形態 5 と同様とすればよく、その繰り返しの説明は適宜省略する。また同じ箇所の詳細な説明も適宜省略する。本実施の形態で示すトランジスタ 425、426 は、実施の形態 1 乃至実施の形態 3 の電圧調整回路を構成するトランジスタとして用いることができる。

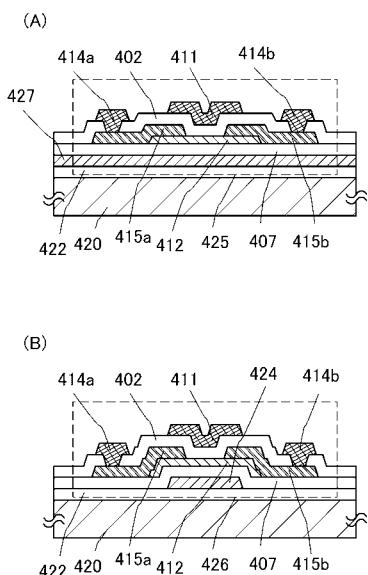

**【0235】**

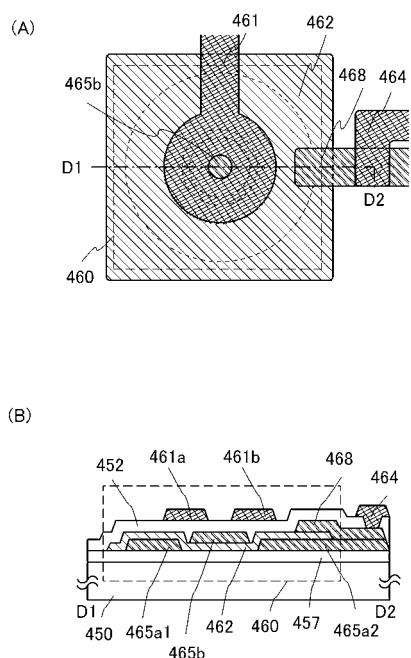

本実施の形態の薄膜トランジスタを、図 9 を用いて説明する。

**【0236】**

図 9（A）（B）に薄膜トランジスタの断面構造の一例を示す。図 9（A）（B）に示すトランジスタ 425、426 は、酸化物半導体層を導電層とゲート電極層とで挟んだ構造の薄膜トランジスタの一つである。

40

**【0237】**

また、図 9（A）（B）において、基板にシリコン基板を用いており、シリコン基板 420 上に設けられた絶縁層 422 上にトランジスタ 425、426 がそれぞれ設けられている。

**【0238】**

図 9（A）において、シリコン基板 420 に設けられた絶縁層 422 と絶縁層 407 との間に少なくとも酸化物半導体層 412 全体と重なるように導電層 427 が設けられている。

50

**【 0 2 3 9 】**

なお、図9( B )は、絶縁層422と絶縁層407との間の導電層が、導電層424のようにエッティングにより加工され、酸化物半導体層412の少なくともチャネル領域を含む一部と重なる例である。

**【 0 2 4 0 】**

導電層427、424は後工程で行われる加熱処理温度に耐えられる金属材料であればよく、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)から選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、又は上述した元素を成分とする窒化物などを用いることができる。また、単層構造でも積層構造でもよく、例えばタングステン層単層、又は窒化タングステン層とタングステン層とを積層する積層構造などを用いることができる。10

**【 0 2 4 1 】**

また、導電層427、424は、電位がトランジスタ425、426のゲート電極層411と同じでもよいし、異なっていても良く、第2のゲート電極層として機能させることもできる。また、導電層427、424の電位がGND、0Vという固定電位であってもよい。20

**【 0 2 4 2 】**

導電層427、424によって、トランジスタ425、426の電気特性を制御することができる。

**【 0 2 4 3 】**

また、導電層を設けることにより第2のゲート電極層を形成する構成に限定されず、例えば基板として半導体基板を用いる場合には該基板を熱酸化することにより該基板に形成された領域を第2のゲート電極層として機能させることもできる。

**【 0 2 4 4 】**

また、本実施の形態に示すトランジスタと同一工程で本発明の一態様の電圧調整回路における容量素子を形成することもできる。トランジスタ及び容量素子を同一工程で形成することにより、工程数の増加を低減することができる。

**【 0 2 4 5 】**

上記構造のトランジスタにすることにより、安定な電気特性を有し信頼性の高いトランジスタを提供することができる。また、該トランジスタはリーク電流が低いため、該トランジスタを用いて本発明の一態様である電圧調整回路を構成することにより、所望の値の電圧への到達速度を格段に向上させることができる。また、該トランジスタを用いて本発明の一態様である電圧調整回路を構成することにより、安定な電気特性を有し信頼性の高い電圧調整回路を提供することができる。30

**【 0 2 4 6 】**

なお、本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

**【 0 2 4 7 】**

(実施の形態7)

本実施の形態は、本明細書で開示する電圧調整回路を構成するトランジスタに適用できる薄膜トランジスタの例を示す。

**【 0 2 4 8 】**

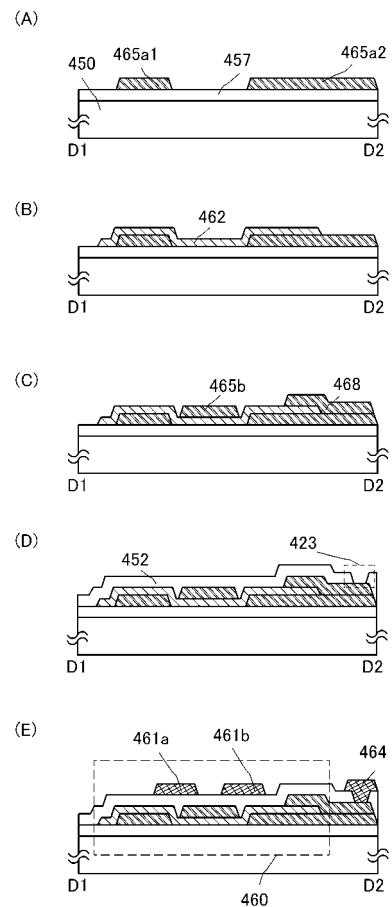

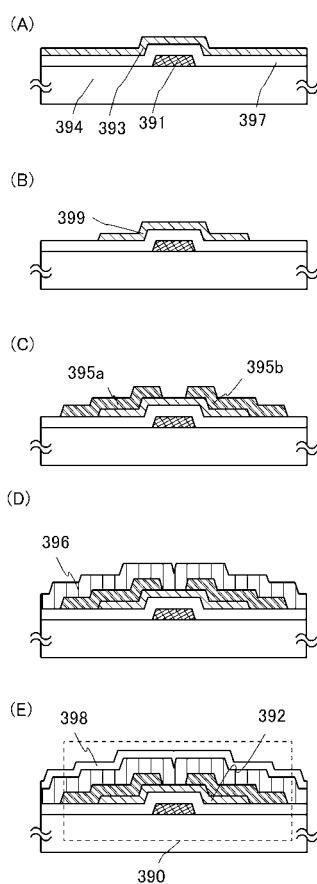

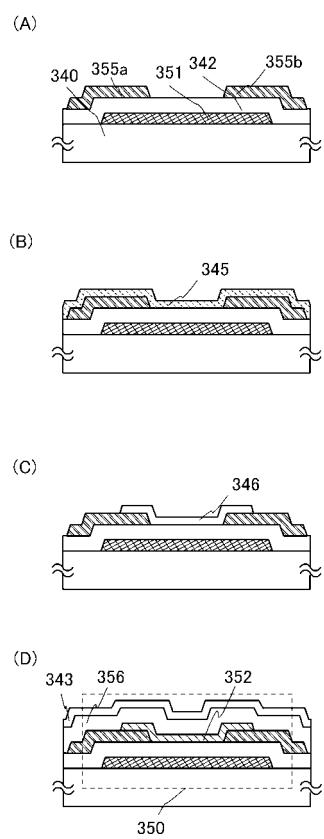

本実施の形態の薄膜トランジスタ及び薄膜トランジスタの作製方法の一形態を、図10を用いて説明する。

**【 0 2 4 9 】**

図10(A)乃至(E)に薄膜トランジスタの作製方法の一例を示す。図10(A)乃至(E)に示すトランジスタ390は、ボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

**【 0 2 5 0 】**

また、トランジスタ390をシングルゲート構造のトランジスタとするが、本実施の形態

10

20

30

40

50

のトランジスタを、チャネル形成領域を複数有するマルチゲート構造のトランジスタとしてもよい。

#### 【0251】

以下、図10(A)乃至(E)を用い、絶縁表面を有する基板394上にトランジスタ390を作製する工程を説明する。

#### 【0252】

まず、絶縁表面を有する基板394上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層391を形成する。形成されたゲート電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。10

#### 【0253】

絶縁表面を有する基板394に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板394としては、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

#### 【0254】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、酸化ホウ素( $B_2O_3$ )と比較して酸化バリウム(BaO)を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$ よりBaOを多く含むガラス基板を用いることが好ましい20

#### 【0255】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いてもよい。他にも、結晶化ガラスなどを用いることができる。また、プラスチック基板等も適宜用いることができる。また基板としてシリコンなどの半導体基板を用いることもできる。

#### 【0256】

また、下地膜となる絶縁膜を基板394とゲート電極層391との間に設けてもよい。下地膜は、基板394からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。30

#### 【0257】

また、ゲート電極層391を形成するための導電膜は、モリブデン、チタン、クロム、タンタル、タンクスチーン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

#### 【0258】

例えば、ゲート電極層391の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、銅層上にモリブデン層を積層した2層構造、銅層上に窒化チタン層若しくは窒化タンタル層を積層した2層構造、窒化チタン層とモリブデン層とを積層した2層構造、又は窒化タンクスチーン層とタンクスチーン層とを積層した2層構造とすることが好ましい。3層の積層構造としては、タンクスチーン層又は窒化タンクスチーン層と、アルミニウムとシリコンの合金又はアルミニウムとチタンの合金と、窒化チタン層又はチタン層とを積層した積層とすることが好ましい。なお、透光性を有する導電膜を用いてゲート電極層を形成することもできる。透光性を有する導電膜としては、透光性導電性酸化物等をその例に挙げることができる。40

#### 【0259】

次に、ゲート電極層391上にゲート絶縁層397を形成する。

#### 【0260】

10

20

30

40

50

ここで、不純物を除去することにより I 型化又は実質的に I 型化された酸化物半導体（高純度化された酸化物半導体）は界面準位、界面電荷に対して極めて敏感であるため、ゲート絶縁層との界面は重要である。そのため高純度化された酸化物半導体層に接するゲート絶縁層（G I）は、高品質化が要求される。

#### 【0261】

例えば、 $\mu$ 波（2.45 GHz）を用いた高密度プラズマCVDは、緻密で絶縁耐圧の高い高品質な絶縁膜を形成できるので好ましい。高純度化された酸化物半導体層と高品質ゲート絶縁層とが密接することにより、界面準位を低減して界面特性を良好にすることができるからである。ここで用いられる高密度プラズマ装置としては、 $1 \times 10^{11} / \text{cm}^3$ 以上のプラズマ密度を達成できる装置を用いることができる。

10

#### 【0262】

例えば、3 kW～6 kWのマイクロ波電力を印加してプラズマを発生させて、絶縁膜の成膜を行う。チャンバーに材料ガスとしてモノシランガス（SiH<sub>4</sub>）と亜酸化窒素（N<sub>2</sub>O）と希ガスを導入し、10 Pa～30 Paの圧力下で高密度プラズマを発生させてガラス等の絶縁表面を有する基板上に絶縁膜を形成する。その後、モノシランガスの供給を停止し、大気に曝すことなく亜酸化窒素（N<sub>2</sub>O）と希ガスとを導入して絶縁膜表面にプラズマ処理を行ってもよい。少なくとも亜酸化窒素（N<sub>2</sub>O）と希ガスとを導入して絶縁膜表面に行われるプラズマ処理は、絶縁膜の成膜より後に行う。チャンバーに導入するモノシランガス（SiH<sub>4</sub>）と亜酸化窒素（N<sub>2</sub>O）との流量比は、1：10から1：200の範囲とする。また、チャンバーに導入する希ガスとしては、ヘリウム、アルゴン、クリプトン、キセノンなどを用いることができるが、中でも安価であるアルゴンを用いることが好ましい。

20

#### 【0263】

もちろん、ゲート絶縁層397として良質な絶縁膜を形成できるものであれば、スパッタリング法やプラズマCVD法など他の成膜方法を適用することができる。また、成膜後の熱処理によってゲート絶縁膜の膜質、酸化物半導体との界面特性が改質される絶縁膜であってもよい。いずれにしても、ゲート絶縁膜としての膜質が良好であることは勿論のこと、酸化物半導体との界面準位密度を低減し、良好な界面を形成できるものであればよい。

#### 【0264】

さらに、 $85 \times 10^6 \text{ V/cm}$ 、12時間のゲートバイアス・熱ストレス試験（BT試験）においては、不純物が酸化物半導体に添加されていると、不純物と酸化物半導体の主成分との結合手が、強電界（B：バイアス）と高温（T：温度）により切断され、生成された未結合手がしきい値電圧（Vth）のドリフトを誘発することとなる。これに対して、本発明の一態様であるトランジスタは、酸化物半導体の不純物、特に水素や水等を極力除去し、上記のようにゲート絶縁層との界面特性を良好にすることにより、BT試験に対しても安定な薄膜トランジスタを得ることを可能としている。

30

#### 【0265】

また、ゲート絶縁層397としては、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。

40

#### 【0266】

また、ゲート絶縁層397としては、例えばHfO<sub>x</sub>（x > 0）などを用いることもできる。ゲート絶縁層397としてHfO<sub>x</sub>などを用いることにより、酸化物半導体層側からゲート電極に向かって流れるリーク電流を低減することができる。

#### 【0267】

また、ゲート絶縁層397は、酸化シリコン層と窒化シリコン層を積層した構造とするともできる。本実施の形態では、一例として圧力30 Pa、マイクロ波電力6 kWで高密度プラズマCVD法により膜厚100 nmの酸化窒化シリコン層を形成する。このときチャンバーに導入するモノシランガス（SiH<sub>4</sub>）と亜酸素窒素（N<sub>2</sub>O）との流量比は、1：10とする。

50

## 【0268】

また、ゲート絶縁層397、酸化物半導体膜393に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層391が形成された基板394、又はゲート絶縁層397までが形成された基板394を予備加熱し、基板394に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度は、100以上400以下好ましくは150

以上300以下である。なお、予備加熱室に設ける排気手段は、クライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。また、この予備加熱は、酸化物絶縁層396の成膜前に、ソース電極層又はドレイン電極層395a及びソース電極層又はドレイン電極層395bまで形成した基板394にも同様に行ってもよい。

10

## 【0269】

次に、ゲート絶縁層397上に、膜厚2nm以上200nm以下の酸化物半導体膜393を形成する(図10(A)参照)。

## 【0270】

なお、酸化物半導体膜393をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層397の表面に付着しているゴミを除去することが好ましい。

## 【0271】

酸化物半導体膜393はスパッタリング法により成膜する。酸化物半導体膜393は、例えばIn-Ga-Zn-O系、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、In-Sn-O系、Sn-O系、Zn-O系の酸化物半導体膜を用いることができる。本実施の形態では、酸化物半導体膜393をIn-Ga-Zn-O系金属酸化物ターゲットを用いてスパッタリング法により成膜する。また、酸化物半導体膜393は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素雰囲気下においてスパッタリング法により形成することができる。また、スパッタリング法を用いる場合、SiO<sub>2</sub>を2重量%以上10重量%以下含むターゲットを用いて成膜を行ってもよい。

20

## 【0272】

酸化物半導体膜393をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、例えば、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:1[mol数比]の組成比である金属酸化物ターゲットを用いることができる。また、上記に示すターゲットに限定されず、例えば、In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO=1:1:2[mol数比]の組成比である金属酸化物ターゲットを用いてもよい。また、作製される金属酸化物ターゲットの充填率は、90%以上100%以下、好ましくは95%以上99.9%である。充填率の高い金属酸化物ターゲットを用いることにより形成した酸化物半導体膜は、緻密な膜となる。

30

## 【0273】

減圧状態に保持された処理室内に基板を保持し、基板を室温又は400未満の温度に加熱する。そして、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタリングガスを導入し、金属酸化物をターゲットとして基板394上に酸化物半導体膜393を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを備えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も含む)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、クライオポンプにより処理室内に残留する水分を除去しながらスパッタリング成膜を行うことで、酸化物半導体膜393を成膜する際の基板温度は室温から4

40

50

00 未満とすることができる。

【0274】

成膜条件の一例としては、基板とターゲットの距離を60mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

【0275】

次に、酸化物半導体膜を第2のフォトリソグラフィ工程により島状の酸化物半導体層399に加工する(図10(B)参照)。また、島状の酸化物半導体層399を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0276】

また、ゲート絶縁層397にコンタクトホールを形成する場合、その工程は酸化物半導体層399の形成時に行うことができる。

【0277】

なお、ここで酸化物半導体膜393のエッチングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。

【0278】

ドライエッティングに用いるエッティングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl<sub>2</sub>)、塩化硼素(BCl<sub>3</sub>)、塩化珪素(SiCl<sub>4</sub>)、四塩化炭素(CC<sub>1</sub><sub>4</sub>)など)が好ましい。

【0279】

また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF<sub>4</sub>)、弗化硫黄(SF<sub>6</sub>)、弗化窒素(NF<sub>3</sub>)、トリフルオロメタン(CHF<sub>3</sub>)など)、臭化水素(HBr)、酸素(O<sub>2</sub>)、これらのガスにヘリウム(He)やアルゴン(Ar)などの希ガスを添加したガス、などを用いることができる。

【0280】

ドライエッティング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッティング法を用いることができる。所望の加工形状にエッティングできるように、エッティング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

【0281】

ウェットエッティングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITOON(関東化学社製)を用いてもよい。

【0282】

また、ウェットエッティング後のエッティング液はエッティングされた材料とともに洗浄によって除去される。その除去された材料を含むエッティング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッティング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

【0283】

所望の加工形状にエッティングできるように、材料に合わせてエッティング条件(エッティング液、エッティング時間、温度等)を適宜調節する。

【0284】

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体層399及びゲート絶縁層397の表面に付着しているレジスト残渣などを除去することが好ましい。

【0285】

10

20

30

40

50

次に、ゲート絶縁層 397、及び酸化物半導体層 399 上に、導電膜を形成する。導電膜をスパッタリング法や真空蒸着法で形成すればよい。導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、W から選ばれた元素、又は上述した元素を成分とする合金、若しくは上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、イットリウムのいずれか一又は複数から選択された材料を用いてもよい。また、導電膜は、単層構造でも、2 層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する 2 層構造、Ti 膜と、その Ti 膜上に重ねてアルミニウム膜を積層し、さらにその上に Ti 膜を成膜する 3 層構造などが挙げられる。また、Al に、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc) から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、若しくは窒化膜を用いてもよい。

10

## 【0286】

第 3 のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層又はドレイン電極層 395a、ソース電極層又はドレイン電極層 395b を形成した後、レジストマスクを除去する(図 10(C) 参照)。

20

## 【0287】

第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線や KrF レーザ光や ArF レーザ光を用いる。酸化物半導体層 399 上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成される薄膜トランジスタのチャネル長 L が決定される。なお、チャネル長 L = 25 nm 未満の露光を行う場合には、数 nm ~ 数 10 nm と極めて波長が短い超紫外線(Extreme Ultraviolet)を用いて第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄膜トランジスタのチャネル長 L を 10 nm 以上 1000 nm 以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値を極めて小さくできるため、低消費電力化も図ることができる。

20

## 【0288】

なお、導電膜のエッチングの際に、酸化物半導体層 399 が除去されないように、導電膜及び酸化物半導体膜のそれぞれの材料及びエッチング条件を適宜調節する。

30

## 【0289】

本実施の形態では、導電膜として Ti 膜を用いて、酸化物半導体層 399 には In-Ga-Zn-O 系酸化物半導体を用いて、エッチャントとしてアンモニア過水(アンモニア、水、過酸化水素水の混合液)を用いる。

## 【0290】

なお、第 3 のフォトリソグラフィ工程では、酸化物半導体層 399 の一部がエッチングされ、溝部(凹部)を有する酸化物半導体層となることもある。また、ソース電極層又はドレイン電極層 395a、ソース電極層又はドレイン電極層 395b を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

40

## 【0291】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

50

## 【0292】

$N_2O$ 、 $N_2$ 、又はArなどのガスを用いたプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

#### 【0293】

プラズマ処理を行った場合、酸化物半導体層の一部に接する保護絶縁膜となる酸化物絶縁層として酸化物絶縁層396を形成する(図10(D)参照)。本実施の形態では、酸化物半導体層399がソース電極層又はドレイン電極層395a、ソース電極層又はドレイン電極層395bと重ならない領域において、酸化物半導体層399と酸化物絶縁層396とが接するように形成する。

#### 【0294】

本実施の形態では、酸化物絶縁層396として、島状の酸化物半導体層399、ソース電極層又はドレイン電極層395a、ソース電極層又はドレイン電極層395bまで形成された基板394を室温又は100℃未満の温度に加熱し、水素及び水分が除去された高純度酸素を含むスパッタリングガスを導入しシリコン半導体のターゲットを用いて、欠陥を含む酸化シリコン層を成膜する。

10

#### 【0295】

例えば、純度が6Nであり、ボロンがドープされたシリコンターゲット(抵抗値0.01cm)を用い、基板とターゲットの距離(T-S間距離)を89mm、圧力0.4Pa、直流(DC)電源6kW、酸素(酸素流量比率100%)雰囲気下でパルスDCスパッタリング法により酸化シリコン膜を成膜する。膜厚は300nmとする。なお、シリコンターゲットに代えて石英(好ましくは合成石英)を酸化シリコン膜を成膜するためのターゲットとして用いることができる。なお、スパッタガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

20

#### 【0296】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層396を成膜することが好ましい。酸化物半導体層399及び酸化物絶縁層396に水素、水酸基又は水分が含まれないようにするためである。

#### 【0297】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを備えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水( $H_2O$ )など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層396に含まれる不純物の濃度を低減できる。

30

#### 【0298】

なお、酸化物絶縁層396として、酸化シリコン層に代えて、酸化窒化シリコン層、酸化アルミニウム層、又は酸化窒化アルミニウム層などを用いることもできる。

#### 【0299】

さらに、酸化物絶縁層396と酸化物半導体層399とを接した状態で100℃乃至400℃で加熱処理を行ってもよい。本実施の形態における酸化物絶縁層396は欠陥を多く含むため、この加熱処理によって酸化物半導体層399中に含まれる水素、水分、水酸基又は水素化物などの不純物を酸化物絶縁層396に拡散させ、酸化物半導体層399中に含まれる該不純物をより低減させることができる。

40

#### 【0300】

以上の工程で、水素、水分、水酸基又は水素化物の濃度が低減された酸化物半導体層392を有するトランジスタ390を形成することができる(図10(E)参照)。

#### 【0301】

上記のように酸化物半導体膜を成膜するに際し、成膜時の雰囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

50

**【0302】**

酸化物絶縁層上に保護絶縁層を設けてもよい。本実施の形態では、保護絶縁層398を酸化物絶縁層396上に形成する。保護絶縁層398としては、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いる。

**【0303】**

酸化物絶縁層396まで形成された基板394を100～400の温度に加熱し、水素及び水分が除去された窒素を含む高純度のスパッタリングガスを導入しシリコン半導体のターゲットを用いて保護絶縁層398として、窒化シリコン膜を成膜する。この場合においても、酸化物絶縁層396と同様に、処理室内の残留水分を除去しつつ保護絶縁層398を成膜することが好ましい。

**【0304】**

保護絶縁層398を形成する場合、保護絶縁層398の成膜時に100～400に基板394を加熱することで、酸化物半導体層399中に含まれる水素若しくは水分を酸化物絶縁層396に拡散させることができる。この場合上記酸化物絶縁層396の形成後に加熱処理を行わなくてもよい。

**【0305】**

酸化物絶縁層396として酸化シリコン層を、保護絶縁層398として窒化シリコン層を積層する場合、酸化シリコン層と窒化シリコン層と同じ処理室において、共通のシリコントーゲットを用いて成膜することができる。先に酸素を含むスパッタリングガスを導入して、処理室内に装着されたシリコントーゲットを用いて酸化シリコン層を形成し、次にスパッタリングガスを窒素を含むスパッタリングガスに切り替えて同じシリコントーゲットを用いて窒化シリコン層を成膜する。酸化シリコン層と窒化シリコン層とを大気に曝露せずに連続して形成することができるため、酸化シリコン層表面に水素や水分などの不純物が吸着することを防止することができる。この場合、酸化物絶縁層396として酸化シリコン層を形成し、保護絶縁層398として窒化シリコン層を積層した後、酸化物半導体層中に含まれる水素若しくは水分を酸化物絶縁層396に拡散させるための加熱処理（温度100乃至400）を行うとよい。

**【0306】**

保護絶縁層398の形成後、さらに大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回繰り返して行ってもよい。また、この加熱処理を、酸化物絶縁層396の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、ノーマリーオフとなる薄膜トランジスタを得ることができる。よって薄膜トランジスタの信頼性を向上できる。

**【0307】**

また、ゲート絶縁層上にチャネル形成領域とする酸化物半導体層を成膜するに際し、雰囲気中の残留水分を除去することで、該酸化物半導体層中の水素及び水素化物の濃度を低減することができる。

**【0308】**

上記の工程は、400以下の温度で行われるため、厚さが1mm以下で、一辺が1mを超えるガラス基板を用いる製造工程にも適用することができる。また、400以下の処理温度で全ての工程を行うことができる。

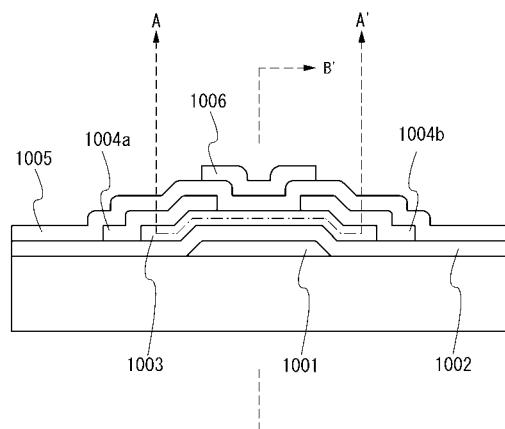

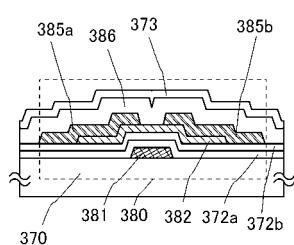

**【0309】**

さらに、図11に酸化物半導体を用いた逆スタガ型の薄膜トランジスタの縦断面図を示す。ゲート電極1001上にゲート絶縁膜1002を介して酸化物半導体層1003が設けられ、その上にソース電極1004a及びドレイン電極1004bが設けられ、ソース電極1004a及びドレイン電極1004bの上に酸化物絶縁層1005が設けられ、酸化物絶縁層1005を挟んで酸化物半導体層1003の上に導電層1006が設けられる。

**【0310】**

10

20

30

40

50

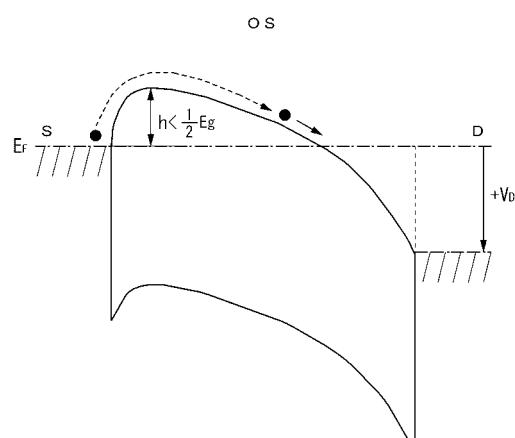

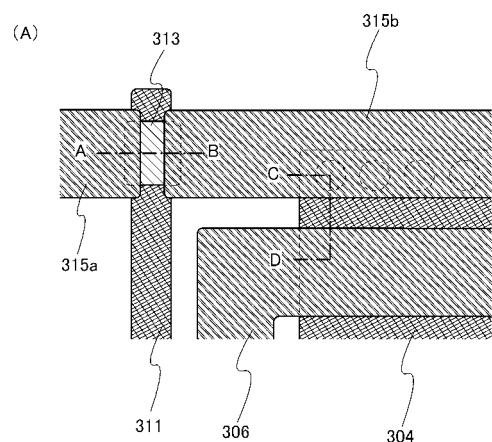

図12は、図11に示すA-A'断面におけるエネルギー・バンド図(模式図)を示す。図12(A)はソースとドレインの間の電圧を等電位( $V_D = 0V$ )とした場合を示し、図12(B)はソースに対しドレインに正の電位( $V_D > 0$ )を加えた場合を示す。

### 【0311】

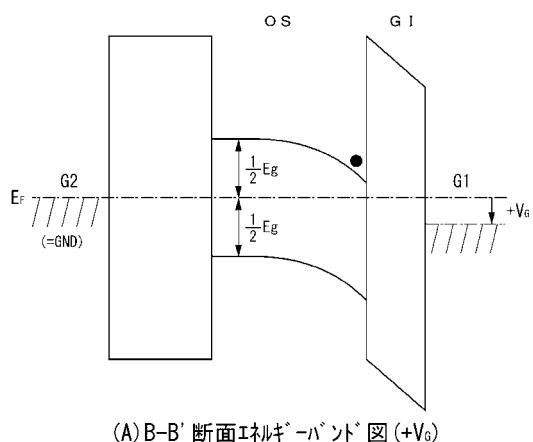

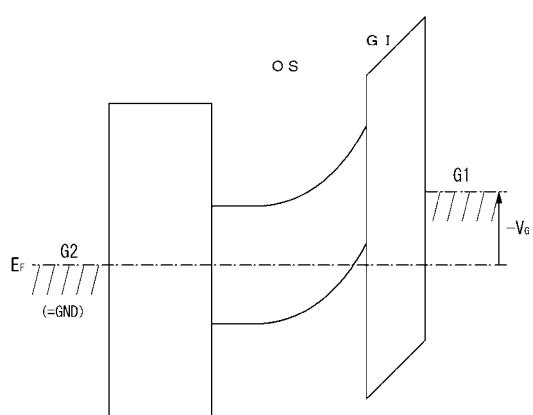

図13は、図11におけるB-B'の断面におけるエネルギー・バンド図(模式図)である。図13(A)はゲート(G1)に正の電位(+ $V_G$ )が印加された状態であり、ソースとドレインの間にキャリア(電子)が流れるオン状態を示している。また、図13(B)は、ゲート(G1)に負の電位(- $V_G$ )が印加された状態であり、オフ状態(少数キャリアは流れない)である場合を示す。

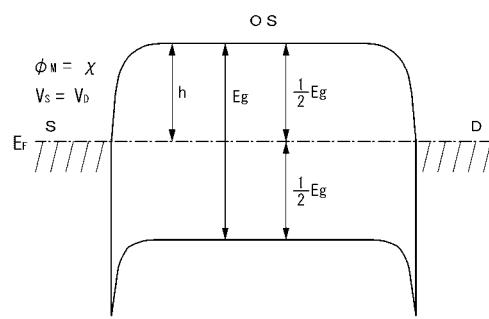

### 【0312】

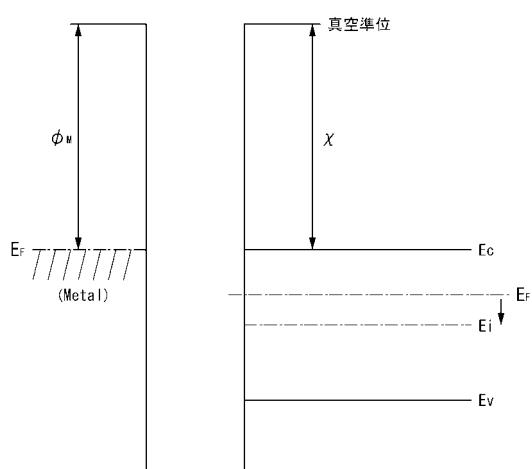

図14は、真空準位と金属の仕事関数( $\phi_M$ )、酸化物半導体の電子親和力( $\phi_A$ )の関係を示す。

### 【0313】

金属は縮退しているため、伝導帯中にフェルミ準位が位置する。一方、従来の酸化物半導体は一般にN型であり、その場合のフェルミ準位( $E_F$ )は、バンドギャップ中央に位置する真性フェルミ準位( $E_i$ )から離れて、伝導帯寄りに位置している。なお、酸化物半導体において、成膜方法にも依存するが、酸化物半導体層には多少の水素若しくは水が含有され、その一部が電子を供給するドナーとなり、N型化する一つの要因であることが知られている。

### 【0314】

これに対して本発明の一態様の電圧調整回路のトランジスタに適用する酸化物半導体は、N型不純物である水素を酸化物半導体から除去し、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより真性(I型)、又は実質的に真性な半導体としたものである。すなわち、不純物を添加してI型化するのではなく、水素や水等の不純物を極力除去したことにより、高純度化されたI型(真性半導体)又はそれに近づけることを特徴としている。そうすることにより、フェルミ準位は、真性フェルミ準位と同じレベルにまですることができる。

### 【0315】

酸化物半導体のバンドギャップ( $E_g$ )が3.15eVである場合、電子親和力( $\phi_A$ )は4.3eVと言われている。ソース電極及びドレイン電極を構成するチタン(Ti)の仕事関数は、酸化物半導体の電子親和力( $\phi_A$ )とほぼ等しい。この場合、金属-酸化物半導体界面において、電子に対してショットキー型の障壁は形成されない。

### 【0316】

すなわち、金属の仕事関数と酸化物半導体の電子親和力が等しい場合、両者が接触すると図12(A)で示すようなエネルギー・バンド図(模式図)が示される。

### 【0317】

図12(B)において、黒丸(●)は電子を示し、ドレインに正の電位が印加されると、電子はバリア( $h$ )を超えて酸化物半導体に注入され、ドレインに向かって流れる。この場合、バリア( $h$ )の高さは、ゲート電圧とドレイン電圧に依存して変化するが、正のドレイン電圧が印加された場合には、電圧印加のない図12(A)のバリアの高さ、すなわちバンドギャップ( $E_g$ )の1/2よりもバリア( $h$ )の高さは、小さい値となる。

### 【0318】

このとき、電子は、図13(A)で示すようにゲート絶縁膜と高純度化された酸化物半導体との界面における、酸化物半導体側のエネルギー的に安定な最低部を移動する。

### 【0319】

また、図13(B)において、ゲート電極1001に負の電位(逆バイアス)が印加されると、少数キャリアであるホールは実質的にゼロであるため、電流は限りなくゼロに近い値となる。

### 【0320】

例えば、薄膜トランジスタのチャネル幅Wが $1 \times 10^{-4} \mu m$ でチャネル長が $3 \mu m$ の素子

10

20

30

40

50

であっても、オフ電流が  $10^{-13}$  A 以下であり、サブスレッショルドスイング値 (S 値) が 0.1 V / dec. (ゲート絶縁膜厚 100 nm) である。

### 【0321】

さらに、高純度化された酸化物半導体を用いたトランジスタのオフ電流をさらに正確に求めた結果について、以下に説明する。

### 【0322】

高純度化された酸化物半導体を用いたトランジスタのオフ電流は、測定器の検出限界である  $1 \times 10^{-13}$  A 以下である。そこで、特性評価用素子を作製し、より正確なオフ電流の値（上記測定における測定器の検出限界以下の値）を求めた結果について、以下に説明する。

10

### 【0323】

はじめに、電流測定方法に用いた特性評価用素子について、図 15 を参照して説明する。

### 【0324】

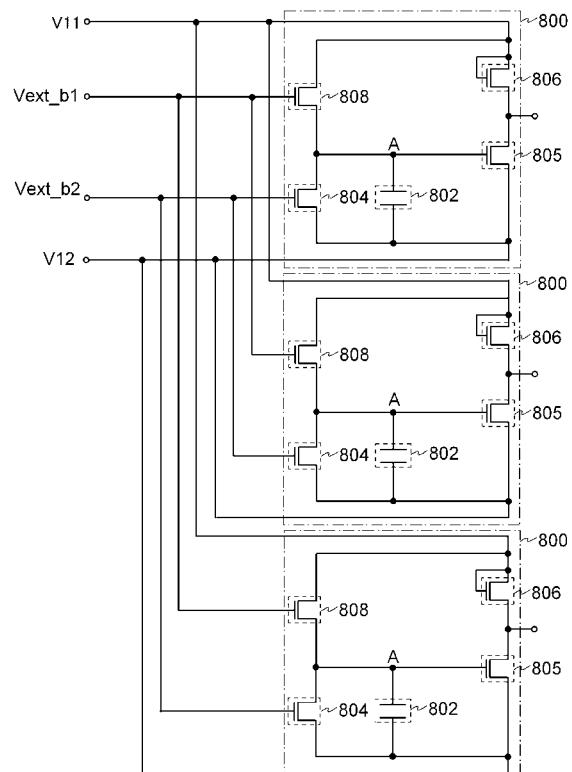

図 15 に示す特性評価用素子は、測定系 800 が 3 つ並列接続で電気的に接続される。測定系 800 は、容量素子 802、トランジスタ 804、トランジスタ 805、トランジスタ 806、及びトランジスタ 808 を有する。トランジスタ 804、トランジスタ 808 には、一例として実施の形態 4 に従って作製したトランジスタを使用した。

### 【0325】

トランジスタ 808 は、ソース及びドレインの一方で電圧 V11 が入力され、ゲートに電位 Vext\_b1 が入力される。電位 Vext\_b1 は、トランジスタ 808 のオン状態又はオフ状態を制御する電位である。

20

### 【0326】

トランジスタ 804 は、ソース及びドレインの一方がトランジスタ 808 のソース及びドレインの他方に電気的に接続され、ソース及びドレインの他方に電圧 V12 が入力され、ゲートに電位 Vext\_b2 が入力される。電位 Vext\_b2 は、トランジスタ 804 のオン状態又はオフ状態を制御する電位である。

### 【0327】

容量素子 802 は、第 1 端子及び第 2 端子を有し、第 1 端子がトランジスタ 804 のソース及びドレインの一方で電気的に接続され、第 2 端子がトランジスタ 804 のソース及びドレインの他方に電気的に接続される。なお、容量素子 802 の第 1 端子と、トランジスタ 808 のソース及びドレインの他方、トランジスタ 804 のソース及びドレインの一方、及びトランジスタ 805 のゲートとの接続箇所をノード A ともいう。

30

### 【0328】

トランジスタ 806 は、ソース及びドレインの一方で電位 V11 が入力され、ゲートが自身のソース及びドレインの一方で電気的に接続される。

### 【0329】

トランジスタ 805 は、ソース及びドレインの一方がトランジスタ 806 のソース及びドレインの他方に電気的に接続され、ソース及びドレインの他方に電位 V12 が入力される。

### 【0330】

なお、測定系 800 において、トランジスタ 806 のソース及びドレインの他方とトランジスタ 805 のソース及びドレインの一方との接続箇所が出力端子となっており、測定系 800 は、出力端子を介して電位 Vout を出力する。

40

### 【0331】

次に、図 15 に示す測定系を用いた電流測定方法について説明する。

### 【0332】

まず、オフ電流を測定するために電位差を付与する初期化期間の概略について説明する。初期化期間においては、電位 Vext\_b1 の値をトランジスタ 808 がオン状態になる値にし、トランジスタ 808 をオン状態にし、ノード A に電位 V11 を与える。ここで、電位 V11 は、例えれば高電位とする。また、トランジスタ 804 をオフ状態にしておく。

50

**【0333】**

その後、電位  $V_{ext\_b1}$  をトランジスタ 808 がオフ状態になる値にし、トランジスタ 808 をオフ状態にする。さらにトランジスタ 808 をオフ状態にした後に、電位  $V_1$  1を低電位とする。ここでも、トランジスタ 804 はオフ状態にしておく。また、電位  $V_{12}$  は電位  $V_{11}$  と同じ電位とする。以上により、初期化期間が終了する。初期化期間が終了した状態では、ノード A とトランジスタ 804 のソース電極及びドレイン電極の他方との間に電位差が生じ、また、ノード A とトランジスタ 808 のソース電極及びドレイン電極の一方との間に電位差が生じることになるため、トランジスタ 804 及びトランジスタ 808 には僅かに電荷が流れる。つまり、オフ電流が発生する。

**【0334】**

次に、オフ電流の測定期間の概略について説明する。測定期間においては、トランジスタ 804 のソース又はドレインの他方の電位（つまり電位  $V_{12}$ ）、及び、トランジスタ 808 のソース又はドレインの一方の電位（つまり電位  $V_{11}$ ）は低電位に固定しておく。一方で、測定期間中は、上記ノード A の電位は固定しない（浮遊状態とする）。これにより、トランジスタ 804 に電荷が流れ、時間の経過と共にノード A に保持される電荷量が変動する。そして、ノード A に保持される電荷量の変動に伴って、ノード A の電位が変動する。つまり、出力端子の出力電位である電位  $V_{out}$  も変動する。

**【0335】**

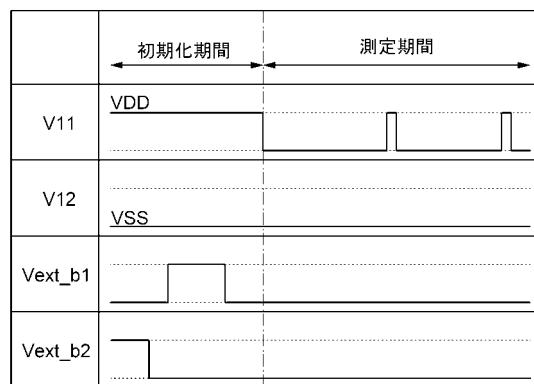

上記電位差を付与する初期化期間、及び、その後の測定期間における各電位の関係の詳細（タイミングチャート）を図 16 に示す。

10

20

**【0336】**

初期化期間において、まず、電位  $V_{ext\_b2}$  を、トランジスタ 804 がオン状態になるような電位（高電位）とする。これによって、ノード A の電位は  $V_{12}$  すなわち低電位（例えば  $V_{SS}$ ）となる。その後、電位  $V_{ext\_b2}$  を、トランジスタ 804 がオフ状態になるような電位（低電位）として、トランジスタ 804 をオフ状態とする。そして、次に、電位  $V_{ext\_b1}$  を、トランジスタ 808 がオン状態となるような電位（高電位）とする。これによって、ノード A の電位は  $V_{11}$ 、すなわち高電位（例えば  $V_{DD}$ ）となる。その後、 $V_{ext\_b1}$  を、トランジスタ 808 がオフ状態となるような電位とする。これによって、ノード A が浮遊状態となり、初期化期間が終了する。

**【0337】**

その後の測定期間においては、電位  $V_{11}$  及び電位  $V_{12}$  を、ノード A に電荷が流れ込み、又はノード A から電荷が流れ出すような電位とする。ここでは、電位  $V_{11}$  及び電位  $V_{12}$  を低電位（ $V_{SS}$ ）とする。ただし、出力電位  $V_{out}$  を測定するタイミングにおいては、出力回路を動作させる必要が生じるため、一時的に  $V_{11}$  を高電位（ $V_{DD}$ ）とすることがある。なお、 $V_{11}$  を高電位（ $V_{DD}$ ）とする期間は、測定に影響を与えない程度の短期間とする。

30

**【0338】**

上述のようにして電位差を与え、測定期間が開始されると、時間の経過と共にノード A に保持される電荷量が変動し、これに従ってノード A の電位が変動する。これは、トランジスタ 805 のゲートの電位が変動することを意味するから、時間の経過と共に、出力端子の出力電位  $V_{out}$  の電位も変化する。

40

**【0339】**

得られた出力電位  $V_{out}$  から、オフ電流を算出する方法について、以下に説明する。

**【0340】**

オフ電流の算出の前に、ノード A の電位  $V_A$  と、出力電位  $V_{out}$  との関係を求めておく。これにより、出力電位  $V_{out}$  からノード A の電位  $V_A$  を求めることができる。上述の関係から、ノード A の電位  $V_A$  は、出力電位  $V_{out}$  の関数として次式のように表すことができる。

**【0341】**

【数1】

$$V_A = F(V_{out})$$

【0342】

また、ノードAの電荷 $Q_A$ は、ノードAの電位 $V_A$ 、ノードAに接続される容量 $C_A$ 、定数(`const`)を用いて、次式のように表される。ここで、ノードAに接続される容量 $C_A$ は、容量素子802の容量と他の容量の和である。

【0343】

【数2】

$$Q_A = C_A V_A + const$$

10

【0344】

ノードAの電流 $I_A$ は、ノードAに流れ込む電荷(又はノードAから流れ出る電荷)の時間微分であるから、ノードAの電流 $I_A$ は次式のように表される。

【0345】

【数3】

$$I_A \equiv \frac{\Delta Q_A}{\Delta t} = \frac{C_A \cdot \Delta F(V_{out})}{\Delta t}$$

【0346】

20

このように、ノードAに接続される容量 $C_A$ と、出力端子の出力電位 $V_{out}$ から、ノードAの電流 $I_A$ を求めることができる。

【0347】

以上に示す方法により、オフ状態においてトランジスタのソースとドレイン間を流れるリーク電流(オフ電流)を測定することができる。

【0348】

本実施の形態では、高純度化した酸化物半導体を用いてトランジスタ804、トランジスタ808を作製した。トランジスタのチャネル長( $L$ )とチャネル幅( $W$ )の比は、 $L/W = 1/5$ とした。また、並列された各測定系800において、容量素子802の容量値をそれぞれ、100fF、1pF、3pFとした。

30

【0349】

なお、本実施の形態に係る測定では、 $VDD = 5V$ 、 $VSS = 0V$ とした。また、測定期間ににおいては、電位 $V11$ を原則として $VSS$ とし、10~300secごとに、100msecの期間だけ $VDD$ として $V_{out}$ を測定した。また、素子に流れる電流 $I$ の算出に用いられる $t$ は、約30000secとした。

【0350】

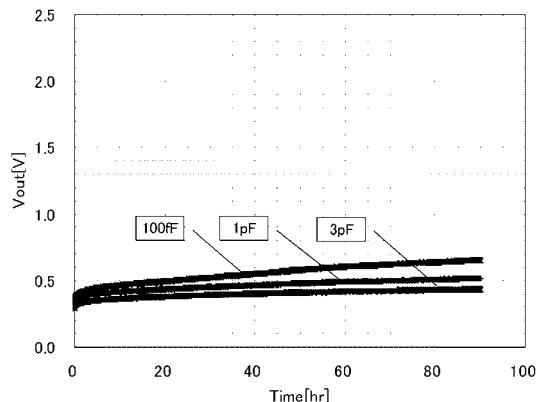

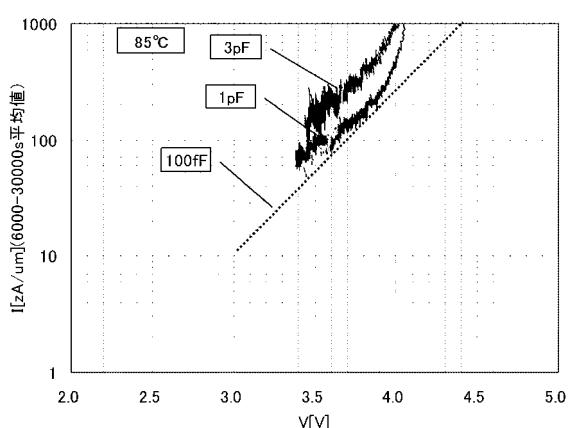

図17に、上記電流測定に係る経過時間 $Time$ と、出力電位 $V_{out}$ との関係を示す。90時間程度から、電位変化の様子が確認できる。

【0351】

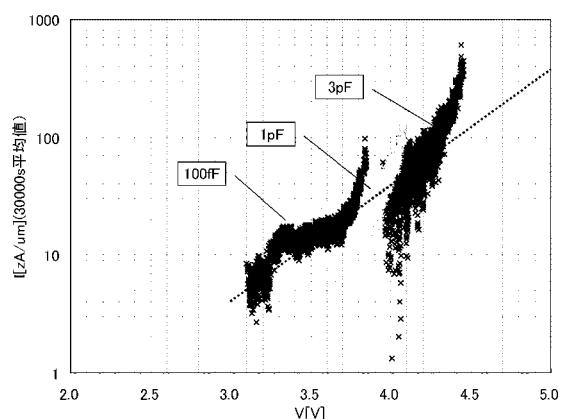

図18には、上記電流測定によって算出されたオフ電流を示す。なお、図18は、ソース-ドレイン電圧 $V$ と、オフ電流 $I$ との関係を表すものである。図18から、ソース-ドレイン電圧が4Vの条件において、オフ電流は約40zA/ $\mu m$ であることが分かった。また、ソース-ドレイン電圧が3.1Vの条件において、オフ電流は10zA/ $\mu m$ 以下であることが分かった。なお、1zAは $10^{-21}A$ を表す。

40

【0352】

さらに、上記トランジスタの温度が85°のときの上記電流測定によって算出されたオフ電流について図19に示す。図19は、85°のときのソース-ドレイン電圧 $V$ と、オフ電流 $I$ との関係を表すものである。図19から、ソース-ドレイン電圧が3.1Vの条件において、オフ電流は100zA/ $\mu m$ 以下であることが分かった。

【0353】

50

以上、高純度化された酸化物半導体を用いたトランジスタでは、オフ電流が十分に小さくなることが確認された。

【0354】

このように、酸化物半導体の主成分以外の不純物が極力含まれないように高純度化することにより、薄膜トランジスタの動作を良好にすることができる。

【0355】

また、本実施の形態に示すトランジスタと同一工程で本発明の一態様の電圧調整回路における容量素子を形成することもできる。トランジスタ及び容量素子を同一工程で形成することにより、工程数の増加を低減することができる。

【0356】

上記構造のトランジスタにすることにより、安定な電気特性を有し信頼性の高いトランジスタを提供することができる。また、該トランジスタはリーク電流が低いため、該トランジスタを用いて本発明の一態様である電圧調整回路を構成することにより、所望の値の電圧への到達速度を格段に向上させることができる。また、該トランジスタを用いて本発明の一態様である電圧調整回路を構成することにより、安定な電気特性を有し信頼性の高い電圧調整回路を提供することができる。

10

【0357】

なお、本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0358】

(実施の形態8)

20

本実施の形態は、本明細書で開示する電圧調整回路を構成するトランジスタに適用できる薄膜トランジスタの他の例を示す。

【0359】

本実施の形態の薄膜トランジスタ及び薄膜トランジスタの作製方法の一形態を図20を用いて説明する。

【0360】

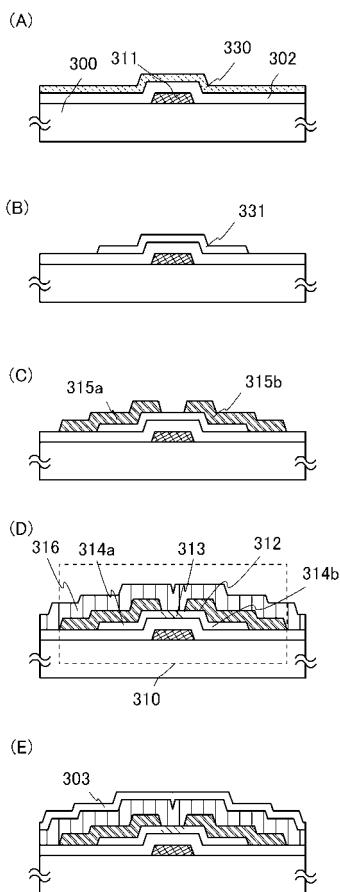

図20(A)乃至(E)に薄膜トランジスタの断面構造の一例を示す。図20(A)乃至(E)に示すトランジスタ310は、ボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

30

【0361】

また、トランジスタ310をシングルゲート構造のトランジスタとするが、本実施の形態のトランジスタを、チャネル形成領域を複数有するマルチゲート構造のトランジスタとしてもよい。

【0362】

以下、図20(A)乃至(E)を用い、絶縁表面を有する基板300上にトランジスタ310を作製する工程を説明する。

【0363】

まず、絶縁表面を有する基板300上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層311を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

40

【0364】

絶縁表面を有する基板300に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、基板300としては、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

【0365】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている

50

。なお、酸化ホウ素 ( $B_2O_3$ ) と比較して酸化バリウム ( $BaO$ ) を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$  より  $BaO$  を多く含むガラス基板を用いることが好ましい。

#### 【0366】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体となる基板を用いてもよい。他にも、結晶化ガラスなどを用いることができる。また、基板としてシリコンなどの半導体基板を用いることもできる。

#### 【0367】

下地膜となる絶縁膜を基板 300 とゲート電極層 311との間に設けてよい。下地膜は、基板 300 からの不純物元素の拡散を防止する機能があり、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜から選ばれた一又は複数の膜による積層により形成することができる。

#### 【0368】

また、ゲート電極層 311 を形成するための導電膜は、モリブデン、チタン、クロム、タンタル、タンクスチン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

#### 【0369】