(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(à n'utiliser que pour les commandes de reproduction)

2 652 689

(21) N° d'enregistrement national : 89 13048

(51) Int Cl<sup>5</sup> : H 03 M 1/36

(12)

## DEMANDE DE BREVET D'INVENTION

A1

(22) Date de dépôt : 02.10.89.

(30) Priorité :

(43) Date de la mise à disposition du public de la demande : 05.04.91 Bulletin 91/14.

(56) Liste des documents cités dans le rapport de recherche : Se reporter à la fin du présent fascicule.

(60) Références à d'autres documents nationaux apparentés :

(71) Demandeur(s) : SENN Patrice — FR et ABRIAL André — FR.

(72) Inventeur(s) : SENN Patrice et ABRIAL André.

(73) Titulaire(s) :

(74) Mandataire : de Beaumont Michel Cabinet Conseil.

(54) Convertisseur analogique/numérique à haute fréquence de conversion.

(57) La présente invention concerne un convertisseur analogique/numérique fournissant des mots logiques composés de P bits de poids fort et Q bits de poids faible. Ce convertisseur comprend un diviseur (2),  $2^P$  comparateurs de poids fort (5),  $2^Q$  comparateurs de poids faible (11) et un sélecteur (14). Les comparateurs de poids fort ont leurs deuxièmes entrées (E21) validées sur le signal d'horloge (H) et leurs premières entrées (E11) validées sur le signal d'horloge inverse ( $H^*$ ). Les comparateurs de poids faible ont leurs premières entrées (E12) validées sur le signal d'horloge inverse ( $H^*$ ) et leurs deuxièmes entrées (E22) validées sur le signal d'horloge (H).

A

La présente invention concerne des convertisseurs analogique/numérique à haute fréquence de conversion, et plus particulièrement de tels convertisseurs utilisables dans le domaine vidéo.

5 On connaît des convertisseurs appelés convertisseurs "flash" qui comprennent un diviseur de tension constitué par exemple par un réseau résistif fournissant  $2^N$  tensions de référence étagées. Pour convertir un signal analogique en mot de N bits, ils comportent  $2^N$  comparateurs dont chacun compare le

10 signal analogique à l'une des tensions de référence. Les sorties des comparateurs sont connectées à un dispositif de codage destiné à fournir les N bits du mot logique. Tous les comparateurs sont commandés en parallèle à chaque cycle d'horloge et la fréquence de conversion est égale à la fréquence de l'horloge.

15 Cependant, un tel nombre de comparateurs occupe une surface de circuit importante et entraîne une forte consommation.

Pour réduire ce nombre de comparateurs, on a prévu des convertisseurs appelés convertisseurs "demi-flash". Des signaux analogiques sont convertis en mots logiques composés de P bits de

20 poids fort et Q bits de poids faible ( $P + Q = N$ ). Les convertisseurs "demi-flash" comprennent  $2^P$  comparateurs dits comparateurs de poids fort pour fournir après codage, au cours d'une

première période d'horloge, les bits de poids fort et 2<sup>e</sup> comparateurs dits comparateurs de poids faible pour fournir après codage, au cours de la période d'horloge suivante, les bits de poids faible.

5           Mais de tels convertisseurs "demi-flash" ont une fréquence de conversion deux fois moins importante que celle des convertisseurs "flash". En outre, ils comprennent des moyens de conservation de la tension d'entrée analogique sur deux périodes d'horloge comme par exemple des échantillonneurs-bloqueurs.

10          Ainsi, un objet de la présente invention est de prévoir un convertisseur analogique/numérique de type "demi-flash" fonctionnant à haute fréquence de conversion.

15          Un autre objet de la présente invention est de prévoir un tel convertisseur simplifié n'utilisant aucun moyen de conservation du signal d'entrée analogique.

20          Pour atteindre ces objets, la présente invention prévoit un convertisseur analogique/numérique recevant des signaux analogiques sur une borne d'entrée et fournissant des mots logiques composés de P bits de poids fort et Q bits de poids faible. Ce convertisseur analogique/numérique comprend :

25          un diviseur délivrant sur des premières sorties 2<sup>P</sup> tensions principales séparées par des échelons réguliers, chaque échelon étant partagé en 2<sup>Q+1</sup> sous-échelons égaux, et délivrant sur des deuxièmes sorties, pour chaque échelon, 2<sup>Q</sup> tensions secondaires entre chaque paire de sous-échelons,

30          2<sup>P</sup> comparateurs de poids fort ayant chacun une première entrée connectée à la borne d'entrée, une deuxième entrée reliée à une première sortie distincte et une sortie connectée à un premier dispositif de codage qui est relié en sortie à P bornes de sortie de bits de poids fort,

2<sup>Q</sup> comparateurs de poids faible ayant chacun une première entrée connectée à la borne d'entrée et une sortie connectée à un deuxième dispositif de codage qui est relié en sortie à Q bornes de sortie de bits de poids faible,

un sélecteur connecté, d'une part, à une deuxième entrée de chacun des comparateurs de poids faible, d'autre part, aux deuxièmes sorties associées à chaque échelon et,

une horloge.

5 Selon un mode de réalisation de la présente invention, les comparateurs de poids fort ont leurs deuxièmes entrées validées sur le signal d'horloge pour une initialisation sur les tensions principales et leurs premières entrées validées sur le signal d'horloge inverse pour une comparaison par rapport à la

10 tension d'entrée analogique et pour déterminer un échelon.

Selon un mode de réalisation de la présente invention, le premier dispositif de codage comprend des moyens de commande du sélecteur pour établir, à l'issue de chaque comparaison des comparateurs de poids fort, une liaison entre les 2<sup>e</sup> deuxièmes

15 entrées des comparateurs de poids faible et les 2<sup>e</sup> deuxièmes sorties associées à l'échelon déterminé.

Selon un mode de réalisation de la présente invention, les comparateurs de poids faible ont leurs premières entrées validées sur le signal d'horloge inverse pour une initialisation

20 sur la tension d'entrée analogique et leurs deuxièmes entrées validées sur le signal d'horloge pour une comparaison par rapport aux tensions secondaires.

Ces objets, caractéristiques et avantages ainsi que d'autres de la présente invention seront exposés plus en détail

25 dans la description suivante d'un mode de réalisation particulier faite en relation avec les figures jointes parmi lesquelles :

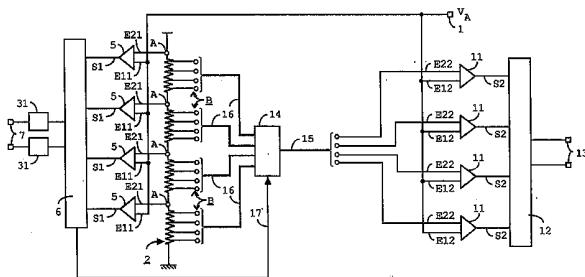

la figure 1 représente de façon schématique un convertisseur analogique/numérique ;

la figure 2 représente schématiquement un exemple de

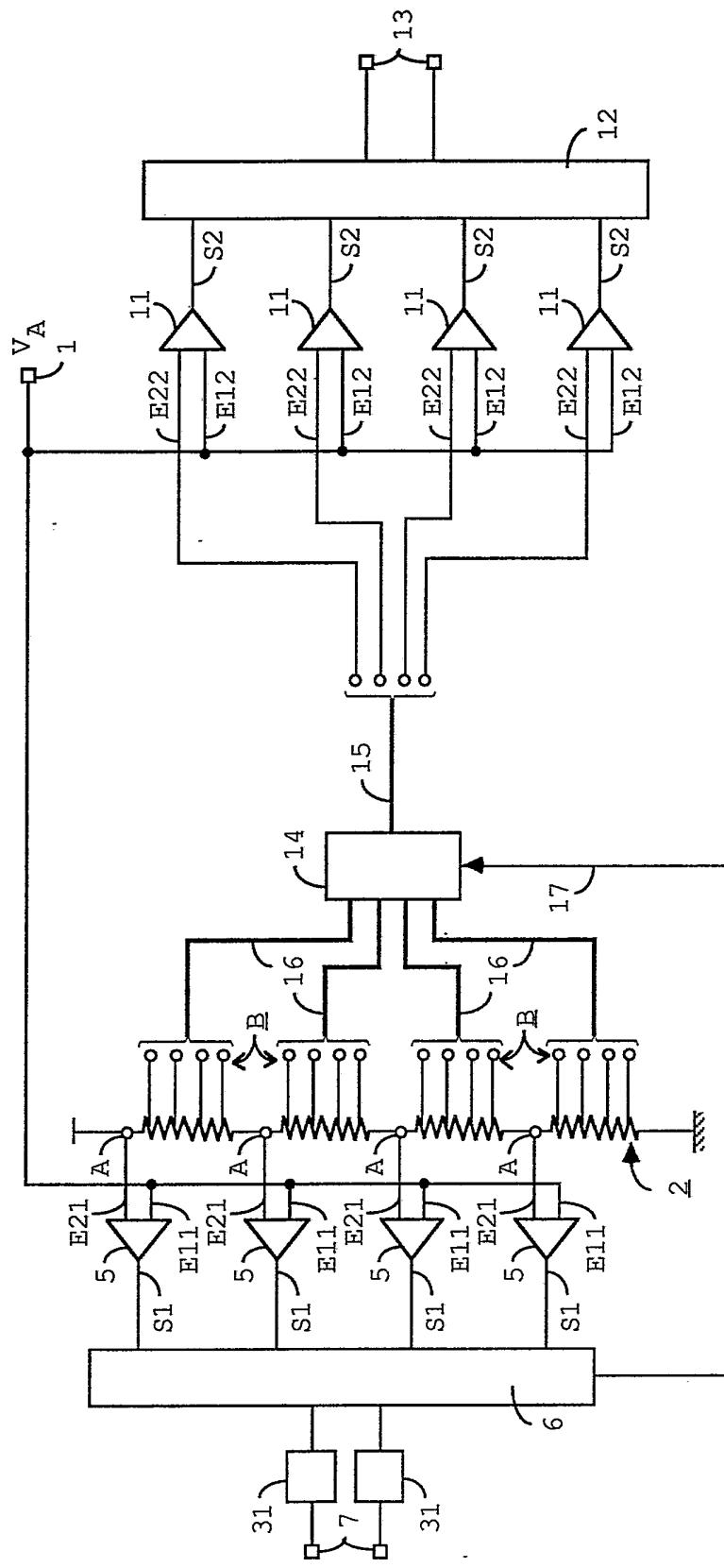

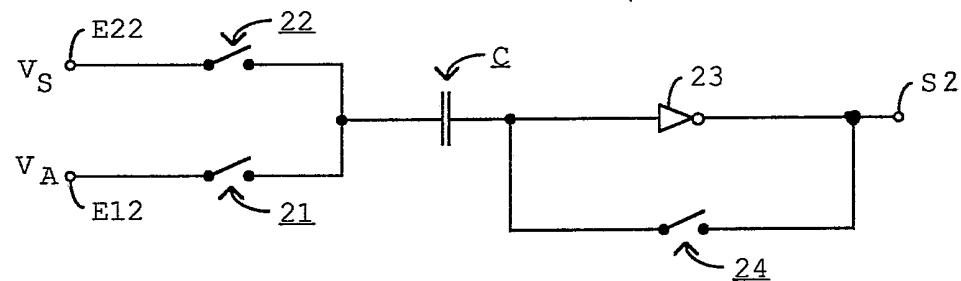

30 comparateur à auto-zéro utilisable dans un convertisseur analogique/numérique ;

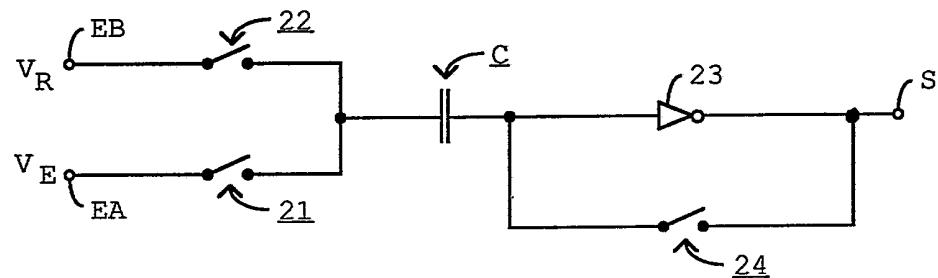

la figure 3 représente schématiquement un comparateur à auto-zéro utilisé en tant que comparateur de poids fort ; et

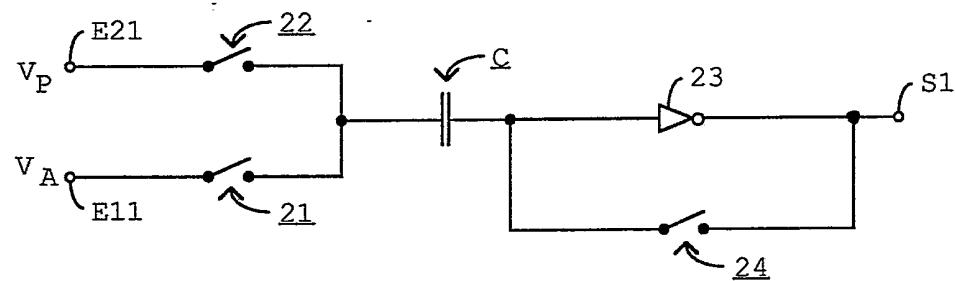

la figure 4 représente un comparateur à auto-zéro uti-

35 lisé en tant que comparateur de poids faible.

Pour une plus grande clarté, il est décrit un mode de réalisation d'un convertisseur analogique/numérique qui convertit des signaux analogiques en mots de 4 bits composés de  $P = 2$  bits de poids fort et  $Q = 2$  bits de poids faible. Il est cependant tout à fait possible de réaliser des convertisseurs analogique/numérique plus importants du même type fournissant par exemple des mots logiques de 8, 16 ou 32 bits.

La figure 1 représente un convertisseur analogique/numérique qui reçoit des signaux analogiques ( $V_A$ ) sur une borne d'entrée 1. Un diviseur de tension 2 fournit sur des sorties A quatre tensions principales de référence  $V_p$  séparées par des échelons réguliers. Chaque échelon est partagé en cinq sous-échelons égaux. Le diviseur fournit ainsi également, pour chaque tension principale, quatre tensions secondaires de référence  $V_s$  correspondant chacune à une valeur de tension entre une paire de sous-échelons. Au total, seize tensions secondaires de référence sont disponibles sur des sorties B du diviseur.

Quatre comparateurs de poids fort 5 ont chacun une première entrée E11 connectée à la borne d'entrée 1 et une deuxième entrée E21 à une sortie A distincte. Ils ont également une sortie S1 connectée à un premier dispositif de codage 6 qui est relié en sortie à deux bornes de sortie de bits de poids fort 7.

Quatre comparateurs de poids faible 11 ont chacun une première entrée E12 connectée à la borne d'entrée 1 et une sortie S2 connectée à un deuxième dispositif de codage 12 qui est relié en sortie à deux bornes de sortie de bits de poids faible 13. La deuxième entrée E22 de chacun de ces comparateurs est reliée à un sélecteur 14 par l'intermédiaire d'un câble à quatre connexions 15. Ce sélecteur est aussi relié à chaque ensemble de sorties secondaires B associé à un échelon par un câble à quatre connexions 16.

Le dispositif de codage 6 comprend des moyens de commande reliés à une entrée de commande 17 du sélecteur. La commande du sélecteur sera précisée ci-après.

Le convertisseur comprend en outre une horloge H (non représentée) dont le signal comporte à chaque période un niveau haut et un niveau bas.

La figure 2 représente schématiquement un comparateur à auto-zéro classique. Ce type de comparateur peut être utilisé aussi bien pour des comparateurs de poids fort que pour des comparateurs de poids faible.

Il comprend une capacité C dont une borne est reliée à la première entrée, désignée ici de façon générale par EA, du comparateur par un interrupteur 21 et à la deuxième entrée EB par un interrupteur 22. La deuxième borne de la capacité est connectée à l'entrée d'un inverseur 23 dont la sortie constitue la sortie S du comparateur. Un interrupteur supplémentaire 24 est monté en parallèle aux bornes de l'inverseur.

Pour comparer une tension  $V_E$  appliquée sur l'entrée EA à une tension de référence  $V_R$  appliquée sur l'entrée EB, les comparateurs à auto-zéro fonctionnent de la façon suivante. Dans une première phase appelée phase d'initialisation, l'interrupteur 21 est ouvert et les interrupteurs 22 et 24 sont fermés. L'inverseur est bouclé sur lui-même et sa tension d'entrée est égale à sa tension de seuil de basculement  $V_o$ . La charge Q de la capacité est donnée par  $Q = C (V_o - V_R)$ .

Dans une deuxième phase appelée phase de comparaison, l'interrupteur 21 est fermé et les interrupteurs 22 et 24 sont ouverts. L'inverseur a une impédance d'entrée très élevée, et la charge de la capacité est conservée. Ainsi, la nouvelle tension d'entrée  $V_{o^1}$  de l'inverseur est reliée à la tension  $V_o$  par la relation

$$V_{o^1} - V_E = V_o - V_R$$

ou encore

$$V_o^1 = V_o - (V_R - V_E)$$

On s'affranchit ainsi dans les comparateurs à auto-zéro des tensions parasites constantes.

La figure 3 représente un tel comparateur à auto-zéro utilisé en tant que comparateur de poids fort. Les entrées sont alors désignées par les références E11 et E21 comme sur la figure 1 et elles reçoivent la tension d'entrée analogique  $V_A$  et une 5 des tensions principales de référence  $V_p$ , respectivement. La sortie est désignée par S1.

Les interrupteurs 22 et 24 sont commandés par le signal d'horloge H. Ils sont fermés lorsque le signal H est à son niveau haut et ouverts sur les niveaux bas. Par contre, l'interrupteur 10 21 est commandé par le signal d'horloge inverse  $H^*$ , c'est-à-dire qu'il est fermé lorsque le signal inverse est à son niveau haut et ouvert sur les niveaux bas de  $H^*$ .

Les comparateurs de poids fort sont ainsi dans un état d'initialisation par rapport aux tensions principales de référence  $V_p$  lorsque le signal d'horloge est à un niveau haut, et 15 dans un état de comparaison en lisant la tension d'entrée analogique  $V_A$  lorsque le signal d'horloge inverse est à un niveau haut.

De préférence, les passages de niveau haut à niveau bas 20 des signaux d'horloge H et de niveau bas à niveau haut des signaux d'horloge inverses  $H^*$  sont sans recouvrement et séparés d'un petit intervalle de temps.

A la fin de chaque phase de comparaison des comparateurs de poids fort, une des tensions principales  $V_p$  qui 25 correspondent à un échelon particulier est déterminée. Le dispositif de codage délivre les bits de poids fort sur les bornes de sortie 7.

La figure 4 représente un comparateur à auto-zéro utilisé en tant que comparateur de poids faible. Les entrées E12 et 30 E22 reçoivent la tension d'entrée analogique  $V_A$  et une des tensions secondaires de référence  $V_s$ , respectivement.

L'interrupteur 22 est synchronisé sur le signal d'horloge H et les interrupteurs 21 et 24 sur le signal d'horloge inverse  $H^*$ . Quand le signal  $H^*$  est haut, les interrupteurs 21

et 24 sont fermés et l'interrupteur 22 est ouvert. Ainsi, tandis que les comparateurs de poids fort sont dans un état de comparaison et lisent la tension d'entrée analogique  $V_A$ , les comparateurs de poids faible sont dans un état d'initialisation 5 sur cette même tension d'entrée  $V_A$ .

Lorsque les comparateurs de poids fort terminent leurs comparaisons et qu'un échelon particulier est déterminé, le dispositif de codage 6 commande le sélecteur 14 pour établir une liaison entre les entrées E22 des comparateurs de poids faible et 10 l'ensemble de sorties B associé à l'échelon déterminé.

Quand le signal H est au niveau haut, l'interrupteur 22 est fermé et les interrupteurs 21 et 24 sont ouverts. Les comparateurs de poids faible sont dans un état de comparaison par rapport aux tensions secondaires de référence  $V_s$ . Les signaux 15 résultant des comparaisons sont envoyés au dispositif de codage 12 qui fournit en sortie les bits de poids faible sur les bornes de sortie 13.

Ainsi, les bits de poids fort sont fournis à la fréquence de l'horloge lorsque le signal  $H^*$  est haut, et les bits 20 de poids faible sont également fournis à la fréquence de l'horloge lorsque le signal H est haut. La fréquence de conversion du convertisseur est celle de l'horloge.

En outre, pour chaque conversion en mot logique, les comparateurs de poids fort et les comparateurs de poids faible 25 lisent simultanément la tension d'entrée analogique. Il n'est ainsi plus besoin de prévoir des moyens de conservation de la tension d'entrée analogique comme des échantillonneurs-bloqueurs.

Selon une variante de la présente invention, il est prévu entre chaque borne de sortie de bits de poids fort 7 et le 30 dispositif de codage 6 une bascule 31 utilisée pour retarder de sensiblement une demi-période la sortie des bits de poids fort de façon à fournir en même temps les bits de poids fort et les bits de poids faible.

REVENDICATIONS

1. Convertisseur analogique/numérique recevant des signaux analogiques sur une borne d'entrée (1) et fournissant des mots logiques composés de P bits de poids fort et Q bits de poids faible, comprenant :

- 5            un diviseur (2) délivrant sur des premières sorties (A) 2<sup>e</sup> tensions principales séparées par des échelons réguliers, chaque échelon étant partagé en 2<sup>e</sup>+1 sous-échelons égaux, et délivrant sur des deuxièmes sorties (B), pour chaque échelon, 2<sup>e</sup> tensions secondaires entre chaque paire de sous-échelons,

- 10          2<sup>e</sup> comparateurs de poids fort (5) ayant chacun une première entrée (E11) connectée à la borne d'entrée, une deuxième entrée (E21) reliée à une première sortie distincte et une sortie (S1) connectée à un premier dispositif de codage (6) qui est relié en sortie à P bornes de sortie de bits de poids fort (7),

- 15          2<sup>e</sup> comparateurs de poids faible (11) ayant chacun une première entrée (E12) connectée à la borne d'entrée et une sortie (S2) connectée à un deuxième dispositif de codage (12) qui est relié en sortie à Q bornes de sortie de bits de poids faible (13),

- 20          un sélecteur (14) connecté, d'une part, à une deuxième entrée (E22) de chacun des comparateurs de poids faible, d'autre part, aux deuxièmes sorties associées à chaque échelon,

une horloge (H),

les comparateurs de poids fort ayant leurs deuxièmes entrées validées sur le signal d'horloge (H) pour une initialisation sur les tensions principales et leurs premières entrées validées sur le signal d'horloge inverse (H\*) pour une comparaison par rapport à la tension d'entrée analogique et pour déterminer un échelon,

- 25

le premier dispositif de codage comprenant des moyens de commande du sélecteur pour établir, à l'issue de chaque comparaison des comparateurs de poids fort, une liaison entre les 2<sup>e</sup> deuxièmes entrées des comparateurs de poids faible et les 2<sup>e</sup> 5 deuxièmes sorties associées à l'échelon déterminé,

caractérisé en ce que les comparateurs de poids faible ont leurs premières entrées validées sur le signal d'horloge inverse ( $H^*$ ) pour une initialisation sur la tension d'entrée analogique et leurs deuxièmes entrées validées sur le signal 10 d'horloge ( $H$ ) pour une comparaison par rapport aux tensions secondaires.

2. Convertisseur analogique/numérique selon la revendication 1, caractérisé en ce que les comparateurs de poids fort et les comparateurs de poids faible sont des comparateurs à auto-15 zéro.

3. Convertisseur analogique/numérique selon la revendication 1, caractérisé en ce qu'il comprend en outre une bascule (31) entre chaque borne de sortie de bits de poids fort (7) et le premier dispositif de codage (6).

1/2

Figure 1

2/2

**Figure 2****Figure 3****Figure 4**

INSTITUT NATIONAL

de la

PROPRIETE INDUSTRIELLE

## RAPPORT DE RECHERCHE

établi sur la base des dernières revendications

déposées avant le commencement de la recherche

N° d'enregistrement

national

FR 8913048

FA 435991

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                         |                                                                                                                                                                                                                                                     | Revendications concernées de la demande examinée |  |  |

|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|

| Catégorie                                                                                     | Citation du document avec indication, en cas de besoin, des parties pertinentes                                                                                                                                                                     |                                                  |  |  |

| Y                                                                                             | 1988 IEEE SOLID-STATE CIRCUITS CONFERENCE, vol. 31, 17 - 19 fevrier 1988, pages 220-221, 376, IEEE, New York, US; T. MATSUURA et al.: "An 8b 20MHz CMOS half-flash A/D converter"<br>* Page 220, colonne 1, ligne 23 - colonne 2, ligne 18 *<br>--- | 1-2                                              |  |  |

| Y                                                                                             | GB-A-2 190 258 (RCA CORP.)<br>* Abstract *<br>-----                                                                                                                                                                                                 | 1-2                                              |  |  |

| DOMAINES TECHNIQUES<br>RECHERCHES (Int. Cl.5)                                                 |                                                                                                                                                                                                                                                     |                                                  |  |  |

| H 03 M 1/36                                                                                   |                                                                                                                                                                                                                                                     |                                                  |  |  |

| Date d'achèvement de la recherche                                                             |                                                                                                                                                                                                                                                     | Examinateur                                      |  |  |

| 18-06-1990                                                                                    |                                                                                                                                                                                                                                                     | GUIVOL Y.                                        |  |  |

| <b>CATEGORIE DES DOCUMENTS CITES</b>                                                          |                                                                                                                                                                                                                                                     |                                                  |  |  |

| X : particulièrement pertinent à lui seul                                                     | T : théorie ou principe à la base de l'invention                                                                                                                                                                                                    |                                                  |  |  |

| Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie     | E : document de brevet bénéficiant d'une date antérieure à la date de dépôt et qui n'a été publié qu'à cette date de dépôt ou qu'à une date postérieure.                                                                                            |                                                  |  |  |

| A : pertinent à l'encontre d'au moins une revendication ou arrière-plan technologique général | D : cité dans la demande                                                                                                                                                                                                                            |                                                  |  |  |

| O : divulgation non-écrite                                                                    | L : cité pour d'autres raisons                                                                                                                                                                                                                      |                                                  |  |  |

| P : document intercalaire                                                                     | .....                                                                                                                                                                                                                                               |                                                  |  |  |

| EPO FORM 1502 03/82 (P0413)                                                                   |                                                                                                                                                                                                                                                     |                                                  |  |  |

| & : membre de la même famille, document correspondant                                         |                                                                                                                                                                                                                                                     |                                                  |  |  |