(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4578618号

(P4578618)

(45) 発行日 平成22年11月10日(2010.11.10)

(24) 登録日 平成22年9月3日(2010.9.3)

|                         |                    |

|-------------------------|--------------------|

| (51) Int.Cl.            | F 1                |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 627 G |

| HO 1 L 29/786 (2006.01) | HO 1 L 21/20       |

| HO 1 L 21/20 (2006.01)  | HO 1 L 29/78 626 C |

|                         | HO 1 L 29/78 627 E |

請求項の数 19 (全 35 頁)

|              |                              |           |                                                |

|--------------|------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2000-142027 (P2000-142027) | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成12年5月15日 (2000.5.15)       | (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号    | 特開2001-53285 (P2001-53285A)  | (72) 発明者  | 荒井 康行<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成13年2月23日 (2001.2.23)       |           |                                                |

| 審査請求日        | 平成19年4月11日 (2007.4.11)       |           |                                                |

| (31) 優先権主張番号 | 特願平11-171485                 |           |                                                |

| (32) 優先日     | 平成11年5月15日 (1999.5.15)       |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                     |           |                                                |

| (31) 優先権主張番号 | 特願平11-152902                 |           |                                                |

| (32) 優先日     | 平成11年5月31日 (1999.5.31)       |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                     |           |                                                |

|              |                              | 審査官       | 綿引 隆                                           |

最終頁に続く

(54) 【発明の名称】半導体装置及びその作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ガラス基板上に TFT を有する半導体装置であって、

前記ガラス基板の主表面に密接して形成された熱伝導率が  $10 \text{ W m}^{-1} \text{ K}^{-1}$  以上であり透光性及び絶縁性を有する熱伝導層と、

前記熱伝導層上の選択された領域に、島状またはストライプ状に形成された熱伝導率が  $10 \text{ W m}^{-1} \text{ K}^{-1}$  未満の第1の絶縁層と、

前記第1の絶縁層上に選択的に形成された水素が添加された単一の結晶粒からなる半導体膜とを有し、

前記 TFT のチャネル形成領域は、前記水素が添加された単一の結晶粒からなる半導体膜に形成されていることを特徴とする半導体装置。 10

## 【請求項 2】

ガラス基板上に TFT を有する半導体装置であって、

前記ガラス基板の主表面に密接して形成された熱伝導率が  $10 \text{ W m}^{-1} \text{ K}^{-1}$  以上であり透光性及び絶縁性を有する熱伝導層と、

前記熱伝導層上の選択された領域に、島状またはストライプ状に形成された熱伝導率が  $10 \text{ W m}^{-1} \text{ K}^{-1}$  未満の第1の絶縁層と、

前記熱伝導層及び前記第1の絶縁層上に形成された第2の絶縁層と、

前記第2の絶縁層を介して前記第1の絶縁層上に選択的に形成され、水素が添加された単一の結晶粒からなる半導体膜とを有し、

10

20

前記TFTのチャネル形成領域は、前記水素が添加された单一の結晶粒からなる半導体膜に形成されていることを特徴とする半導体装置。

**【請求項3】**

請求項2において、前記第2の絶縁層の厚さは5~100nmであることを特徴とする半導体装置。

**【請求項4】**

請求項2または3において、前記第2の絶縁層は、含有酸素濃度が55atomic%以上70atomic%以下であり、かつ、含有窒素濃度が1atomic%以上20atomic%以下である酸化窒化シリコン膜であることを特徴とする半導体装置。

**【請求項5】**

請求項1乃至4のいずれか一において、前記熱伝導層は、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化シリコン、窒化ホウ素、薄膜ダイヤモンド、またはDLCであることを特徴とする半導体装置。

**【請求項6】**

請求項1乃至4のいずれか一において、前記熱伝導層は、Si、N、O、及びM(MはA1または希土類元素から選ばれた少なくとも一種)を含む化合物であることを特徴とする半導体装置。

**【請求項7】**

請求項1乃至6のいずれか一において、前記第1の絶縁層は、含有酸素濃度が55atomic%以上70atomic%以下であり、かつ、含有窒素濃度が1atomic%以上20atomic%以下である酸化窒化シリコン膜であることを特徴とする半導体装置。

**【請求項8】**

請求項1乃至7のいずれか一において、前記第1の絶縁層の端面における側壁の角度が、前記ガラス基板の主表面に対して10度以上40度未満であることを特徴とする半導体装置。

**【請求項9】**

請求項1乃至8のいずれか一において、前記半導体装置は、エレクトロルミネッセンス材料を用いた表示装置、または液晶表示装置であることを特徴とする半導体装置。

**【請求項10】**

請求項1乃至8のいずれか一において、前記半導体装置は、パーソナルコンピュータ、ビデオカメラ、携帯型情報端末、デジタルカメラ、デジタルビデオディスクプレーヤー、電子遊技機器、プロジェクター、またはナビゲーションシステムであることを特徴とする半導体装置。

**【請求項11】**

ガラス基板上にTFTを有する半導体装置の作製方法であって、

前記ガラス基板の主表面に密接して熱伝導率が10Wm<sup>-1</sup>K<sup>-1</sup>以上あり透光性及び絶縁性を有する熱伝導層を形成する工程と、

前記熱伝導層上の選択された領域に、島状またはストライプ状に形成された熱伝導率が10Wm<sup>-1</sup>K<sup>-1</sup>未満の第1の絶縁層を形成する工程と、

前記熱伝導層上及び前記第1の絶縁層上に非晶質半導体膜を形成する工程と、

前記非晶質半導体膜を結晶化させた後、前記第1の絶縁層上に单一の結晶粒からなる半導体膜を選択的に形成する工程と、

前記单一の結晶粒からなる半導体膜を水素化して、水素が添加された单一の結晶粒からなる半導体膜を形成する工程とを有し、

前記水素が添加された单一の結晶粒からなる半導体膜を用いて前記TFTのチャネル形成領域を形成することを特徴とする半導体装置の作製方法。

**【請求項12】**

ガラス基板上にTFTを有する半導体装置の作製方法であって、

前記ガラス基板の主表面に密接して熱伝導率が10Wm<sup>-1</sup>K<sup>-1</sup>以上あり透光性及

10

20

30

40

50

び絶縁性を有する熱伝導層を形成する工程と、

前記熱伝導層上の選択された領域に、島状またはストライプ状に形成された熱伝導率が

10 W m<sup>-1</sup> K<sup>-1</sup>未満の第1の絶縁層を形成する工程と、

前記熱伝導層及び前記第1の絶縁層上に第2の絶縁層を形成する工程と、

前記第2の絶縁層上に非晶質半導体膜を形成する工程と、

前記非晶質半導体膜を結晶化させた後、前記第2の絶縁層を介して前記第1の絶縁層上

に単一の結晶粒からなる半導体膜を選択的に形成する工程と、

前記単一の結晶粒からなる半導体膜を水素化して、水素が添加された単一の結晶粒から

なる半導体膜を形成する工程とを有し、

前記水素が添加された単一の結晶粒からなる半導体膜を用いて前記TFTのチャネル形

成領域を形成することを特徴とする半導体装置の作製方法。

**【請求項13】**

請求項12において、前記第2の絶縁層の厚さは5~100 nmであることを特徴とす

る半導体装置の作製方法。

**【請求項14】**

請求項12または13において、前記第2の絶縁層を、含有酸素濃度が55 atomic

c%以上70 atomic%以下であり、かつ含有窒素濃度が1 atomic%以上20

atomic%以下である酸化窒化シリコン膜で形成することを特徴とする半導体装置の

作製方法。

**【請求項15】**

請求項11乃至14のいずれか一において、前記熱伝導層を、酸化アルミニウム、窒化

アルミニウム、酸化窒化アルミニウム、窒化シリコン、窒化ホウ素、薄膜ダイヤモンド、

または DLC を用いて形成することを特徴とする半導体装置の作製方法。

**【請求項16】**

請求項11乃至14のいずれか一において、前記熱伝導層を、Si、N、O、及びM (M

はAlまたは希土類元素から選ばれた少なくとも一種)を含む化合物材料で形成するこ

とを特徴とする半導体装置の作製方法。

**【請求項17】**

請求項11乃至16のいずれか一において、前記第1の絶縁層を、含有酸素濃度が55

atomic%以上70 atomic%以下であり、かつ含有窒素濃度が1 atomic%以上20

atomic%以下である酸化窒化シリコン膜で形成することを特徴とする半

導体装置の作製方法。

**【請求項18】**

請求項11乃至17のいずれか一において、前記第1の絶縁層の端面における側壁の角

度が、前記ガラス基板の主表面に対して10度以上40度未満であることを特徴とする半

導体装置の作製方法。

**【請求項19】**

請求項11乃至18のいずれか一において、レーザー光の照射により前記非晶質半導体

膜の結晶化を行うことを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、絶縁表面を有する基板上に形成する結晶構造を有する半導体膜及びその作製方

法、並びに該半導体膜を活性層に用いた半導体装置及びその作製方法に関する。特に、結

晶質半導体膜で活性層を形成した薄膜トランジスタに関する。尚、本明細書中において半

導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、薄膜トランジス

タを用いて形成されるアクティブマトリクス型の液晶表示装置に代表される電気光学装置

、およびそのような電気光学装置を部品として搭載した電子装置を範疇とする。

**【0002】**

**【従来の技術】**

10

20

30

40

50

ガラスなどの透光性を有する絶縁基板上に非晶質半導体膜を形成し、レーザーアニール法や熱アニール法などで結晶化させた結晶質半導体膜を活性層とする薄膜トランジスタ（Thin Film Transistor:以下、TFTと記す）が開発されている。このTFTを作製するために主として使用される基板は、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板である。このようなガラス基板は石英基板と比べ耐熱性は劣るものの中価格は安価であり、大面積基板を容易に製造できる利点を有している。

#### 【0003】

レーザーアニール法はガラス基板の温度をあまり上昇させず、非晶質半導体膜にのみ高いエネルギーを与えて結晶化させることができる結晶化技術として知られている。特に、短波長光で大出力が得られるエキシマレーザーはこの用途において最も適していると考えられている。エキシマレーザーを用いたレーザーアニール法は、レーザービームを被照射面においてスポット状や線状となるように光学系で加工し、その加工されたレーザー光で被照射面を走査すること（レーザー光の照射位置を被照射面に対して相対的に移動させる）により行う。例えば、線状レーザー光を用いたエキシマレーザーアニール法は、その長手方向と直角な方向だけの走査で被照射面全体をレーザーアニールすることができ、生産性に優れることから TFT を用いる液晶表示装置の製造技術として主流となりつつある。

#### 【0004】

レーザーアニール法は様々な半導体材料の結晶化に適用できる。しかし、TFT の特性面から考慮すると、結晶質シリコン膜を活性層に用いると高い移動度を実現することができる所以で適していると考えられている。その技術は一枚のガラス基板上に画素部を形成する画素 TFT と、画素部の周辺に設けられる駆動回路の TFT を形成したモノシリック型の液晶表示装置を実現させた。

#### 【0005】

しかしながら、レーザーアニール法で作製される結晶質シリコン膜は複数の結晶粒の集合であり、結晶粒の位置と大きさがランダムであり、任意の位置に意図的に結晶粒を形成することは出来なかった。そのため、結晶性が最も重要視される TFT のチャネル形成領域を単一の結晶粒で形成することは殆ど不可能であった。結晶粒の界面（結晶粒界）には、非晶質構造や結晶欠陥などに起因する再結合中心や捕獲中心や結晶粒界におけるポテンシャル準位の影響により、キャリアの電流輸送特性が低下させる原因があった。そのことに起因して結晶性シリコン膜を活性層とする TFT は、単結晶シリコン基板に作製される MOS トランジスタの特性と同等なものは今日まで得られていない。

#### 【0006】

このような問題点を解決する方法として、結晶粒を大きくすると共に、その結晶粒の位置を制御して、チャネル形成領域から結晶粒界をなくすことは有効な手段として考えられる。例えば、「"Location Control of Large Grain Following Excimer-Laser Melting of Si Thin-Films", R.Ishihara and A.Burtsev, Japanese Journal of Applied Physics vol.37, No.3B, pp1071-1075, 1998」には、シリコン膜の温度分布を3次元的に制御して結晶の位置制御と大粒形化を実現する方法が開示されている。その方法によれば、ガラス基板上に高融点金属を成膜して、その上に部分的に膜厚の異なる酸化シリコン膜を形成し、その表面に非晶質シリコン膜を形成した基板の両面からエキシマレーザー光を照射することにより結晶粒径を数 μm に大きくできることが報告されている。

#### 【0007】

##### 【発明が解決しようとする課題】

上記 Ishihara らの方法は、非晶質シリコン膜の下地材料の熱特性を局所的に変化させて、基板への熱の流れを制御して温度勾配を持たせることを特徴としている。しかしながら、そのためにガラス基板上に高融点金属層 / 酸化シリコン層 / 半導体膜の3層構造を形成することが必要とされている。この半導体膜を活性層としてトップゲート型の TFT を形成することは構造的には可能であるが、半導体膜と高融点金属層との間で寄生容量が発生するので、消費電力が増加し、TFT の高速動作を実現することは困難となってしまう。

#### 【0008】

10

20

30

40

50

一方、高融点金属層がゲート電極を兼ねることによって、ボトムゲート型または逆スタガ型の TFT に対しては有効に適用できるものである。しかし、前記 3 層構造において、半導体膜の厚さを除いても、高融点金属層と酸化シリコン層の膜厚は、結晶化工程において適した膜厚と、TFT 素子としての特性において適した膜厚ちは必ずしも一致しないので、結晶化工程における最適設計と素子構造の最適設計とを両方同時に満足することはできない。

#### 【 0 0 0 9 】

また、透光性のない高融点金属層をガラス基板の全面に形成すると、透過型の液晶表示装置を製作することは不可能である。高融点金属層は熱伝導率が高いという点では有用であるが、高融点金属材料として代表的に使用されるクロム (Cr) 膜やチタン (Ti) 膜は内部応力が高いので、ガラス基板との密着性に問題が生じる可能性が高い。内部応力の影響はこの上層に形成する半導体膜へも及び、形成された結晶性半導体膜に歪みを与える力として作用することが憂慮される。10

#### 【 0 0 1 0 】

本発明はこのような問題点を解決するための技術であり、結晶粒の位置とその大きさを制御した結晶質半導体膜を作製し、さらにその結晶質半導体膜を TFT のチャネル形成領域に用いることにより高速動作が可能な TFT を実現する。さらに、そのような TFT を透過型の液晶表示装置やイメージセンサなどのさまざまな半導体装置に適用できる技術を提供することを目的とする。20

#### 【 0 0 1 1 】

##### 【課題を解決するための手段】

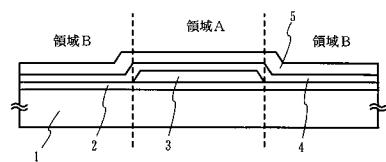

上記問題点を解決するための手段を図 1 を用いて説明する。基板 1 の主表面に密接して透光性と絶縁性を有する熱伝導層 2 を設け、その熱伝導層上の選択された領域に、島状またはストライプ状に形成した第 1 の絶縁層 3 を形成する。この上に第 2 の絶縁層 4、半導体膜 5 を積層させる。最初、半導体膜 5 は非晶質構造を有する半導体膜（非晶質半導体膜）で形成しておく。第 1 の絶縁層 3 及び第 2 の絶縁層 4 は熱伝導層 2 への熱の流出速度を制御するための機能を持たせるものである。第 2 の絶縁層 4 は省略することも可能である。いずれにしても、非晶質半導体膜 5 は基板上の第 1 の絶縁層 3 が設けられた領域と、それ以外の領域に連続して形成する。30

#### 【 0 0 1 2 】

非晶質構造を有する様に形成した半導体膜 5 は、結晶化の工程により結晶質半導体膜となる。結晶化の工程はレーザーアニール法で実施されるのが最も好ましい。特に、波長 400 nm 以下のレーザー光を発するエキシマレーザーを光源に使用すると、半導体膜を優先的に加熱することができるるので適している。エキシマレーザーは、パルス発振型または連続発光型を用いることができる。半導体膜 5 に照射する光は、光学系にて線状ビーム、スポット状ビーム、面状ビームなどとすることが可能であり、その形状に限定されるものはない。具体的なレーザーアニール条件は実施者が適宣決定するものとするが、本発明における結晶化の工程においては、概略以下のように溶融状態から固相状態に変遷する反応を行うものである。40

#### 【 0 0 1 3 】

レーザーアニール法では、照射するレーザー光（またはレーザービーム）の条件を最適なものとすることにより半導体膜を加熱溶融させ、結晶核の発生密度とその結晶核からの結晶成長を制御しようとしている。図 1 において破線で区別した領域 A は熱伝導層 2 上に第 1 の絶縁層 3 が設けられた領域である。領域 B は第 1 の絶縁層 3 が設けられていない周辺の領域を指している。エキシマレーザーのパルス幅は数 nsec ~ 数十 nsec、例えば 30 ns ec であるので、パルス発振周波数を 30 Hz として照射すると、半導体膜はパルスレーザー光により瞬時に加熱され、その加熱時間よりも遙かに長い時間冷却されることになる。レーザー光の照射により半導体膜は溶融状態となるが、領域 A では領域 B と比較して第 1 の絶縁層が形成されている分だけ体積が増えるため温度上昇が低くなる。一方、レーザー光の照射が終わった直後からは熱伝導層 2 を通して熱が拡散するので、領域 B の方が急激に50

冷却が始まり固相状態へ変化するのに対し、領域 A では相対的に緩やかに冷却される。

#### 【 0 0 1 4 】

結晶核は溶融状態から固相状態へ移る冷却過程で生成形成されるものと推定されているが、その核発生密度は、溶融状態の温度と冷却速度とに相関があり、高温から急冷されると核発生密度が高くなる傾向が経験的知見として得られている。従って、溶融状態から急激に冷却される領域 B では結晶核の発生密度が領域 A よりも高くなり、ランダムに結晶核が発生することにより複数の結晶粒が形成され、かつ領域 A に生成される結晶粒よりも粒形が相対的に小さくなる。一方、領域 A ではレーザー光の照射条件と、第 1 の絶縁層 3 および第 2 の絶縁層 4 を最適なものとすることで、溶融状態の温度とその冷却速度を制御することが可能となり、結晶核の発生数を 1 個として、大粒形の結晶を成長させることができ 10。

#### 【 0 0 1 5 】

このような結晶化を可能とするレーザーは、その他に YAG レーザー、 $\text{YVO}_4$  レーザー、YLF レーザーに代表される固体レーザーがある。これらの固体レーザーはレーザーダイオード励起のものが好ましく、その第 2 高調波 (532 nm)、第 3 高調波 (354.7 nm)、第 4 高調波 (266 nm) を用いる。照射条件はパルス発振周波数 1 ~ 10 kHz が可能となり、レーザーエネルギー密度を 300 ~ 600 mJ/cm<sup>2</sup> (代表的には 350 ~ 500 mJ/cm<sup>2</sup>) とする。そして幅 100 ~ 1000 μm、例えば 400 μm で線状に集光したレーザー光を基板全面に渡って照射する。この時の線状レーザー光の重ね合わせ率 (オーバーラップ率) は 80 ~ 98 % とする。 20

#### 【 0 0 1 6 】

結晶化の工程は、レーザーアニール法のみが適用されるものでなく、熱アニール法とレーザーアニール法とを組み合わせても良い。例えば、最初熱アニール法で非晶質半導体膜を結晶化させた後、さらにレーザー光を照射して結晶質半導体膜を形成することも可能である。熱アニール法には、触媒元素を用いる結晶化法を応用しても良い。

#### 【 0 0 1 7 】

このような結晶化の工程において、基板の主表面に密接して形成する熱伝導層 2 と第 1 の絶縁層 3 および第 2 の絶縁層 4 に用いる材料とその膜厚は、熱伝導の過渡的な現象を制御する目的で重要な選択項目となる。熱伝導層は、常温における熱伝導率が  $10 \text{ W m}^{-1} \text{ K}^{-1}$  以上である材料を用いることが必要となる。そのような材料として、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化シリコン、窒化ホウ素、から選ばれた一種または複数種を成分とする化合物を適用することができる。或いは、Si、N、O、M (M は Al または希土類元素から選ばれた少なくとも一種) からなる化合物としても良い。 30

#### 【 0 0 1 8 】

一方、第 1 の絶縁層 3 および第 2 の絶縁層 4 は、常温における熱伝導率が、 $10 \text{ W m}^{-1} \text{ K}^{-1}$  未満である材料を用いる。そのような熱伝導率を有する材料であり、かつ、ガラス基板上に形成する TFT の下地層として適しているものとして、酸化窒化シリコン膜を用いることが望ましい。勿論、その他に窒化シリコン膜や酸化シリコン膜などを用いることも可能である。しかしながら、最も好ましい材料として、第 1 の絶縁膜 3 または第 2 の絶縁膜 4 を、プラズマ CVD 法で SiH<sub>4</sub>、N<sub>2</sub>O から作製する酸化窒化シリコン膜で形成し、その組成を含有酸素濃度が 5.5 atomic% 以上 7.0 atomic% 以下であり、かつ含有窒素濃度が 1 atomic% 以上 2.0 atomic% 以下とすると良い。 40

#### 【 0 0 1 9 】

第 1 の絶縁層 3 は、ガラス基板上において TFT の活性層 (チャネル形成領域、ソース領域、ドレイン領域、および LDD 領域が形成される半導体膜) の配置に合わせて、同様に島状またはストライプ状に分割して形成する。その大きさは、例えば TFT の大きさに合わせて  $0.35 \times 0.35 \mu\text{m}^2$  (チャネル長 × チャネル幅) としたサブミクロンサイズとしても良いし、 $8 \times 8 \mu\text{m}^2$ 、 $8 \times 200 \mu\text{m}^2$  または  $12 \times 400 \mu\text{m}^2$  などとすることができる。少なくとも TFT のチャネル形成領域の位置と大きさに合わせて第 1 の絶縁層 3 を 50

形成することにより、この上に形成される結晶質半導体膜の一つの結晶粒でチャネル形成領域を形成することが可能となる。即ち、実質的に単結晶膜でチャネル形成領域を形成したものと同等な構造とすることができます。このとき、第1の絶縁膜の端面における側壁の角度が、ガラス基板の主表面に対して、10度以上40度未満で形成することが望ましい。

#### 【0020】

このような現象を利用することにより、結晶質半導体膜に存在する結晶粒の大粒形化を図ることができる。さらに、その結晶粒の位置をTFTの活性層を形成する位置に配置させることができる。

#### 【0021】

10

#### 【発明の実施の形態】

##### 【実施形態1】

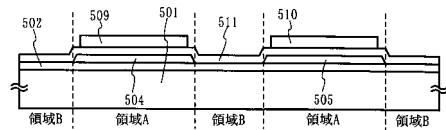

本発明の実施形態を図2を用いて説明する。図2(A)において、基板501にはバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどの無アルカリガラス基板を用いる。例えば、コーニング社の#7059ガラスや#1737ガラス基などを好適に用いることができる。このようなガラス基板は、ガラス歪み点よりも10~20程度低い温度であらかじめ熱処理しておくと後の工程において基板の収縮による変形を低減できる。

#### 【0022】

この基板501のTFTを形成する表面に、透光性でかつ絶縁性を有し、熱伝導性の優れる熱伝導層502を形成する。熱伝導層502の厚さは50~500nmとし、熱伝導率は $10\text{ Wm}^{-1}\text{K}^{-1}$ 以上であることが必要である。このような材料として、アルミニウムの酸化物(酸化アルミニウム( $\text{Al}_2\text{O}_3$ ))は可視光において透光性を有し、熱伝導率が $20\text{ Wm}^{-1}\text{K}^{-1}$ であり適している。また、酸化アルミニウムは化学量論比に限定されるものではなく、熱伝導率特性と内部応力などの特性を制御するために、他の元素を添加しても良い。例えば、酸化アルミニウムに窒素を含ませて、酸化窒化アルミニウム( $\text{AlN}_x\text{O}_{1-x}$ : $0.02 \times 0.5$ )を用いても良いし、アルミニウムの窒化物( $\text{AlN}_x$ )を用いることも可能である。また、シリコン(Si)、酸素(O)、窒素(N)とM(Mはアルミニウム(Al)または希土類元素から選ばれた少なくとも一種)を含む化合物を用いることができる。例えば、 $\text{AlSiON}$ や $\text{LaSiON}$ などを好適に用いることができる。その他に、窒化ホウ素なども適用することができる。

20

#### 【0023】

上記の酸化物、窒化物、および化合物はいずれもスパッタ法で形成することができる。これは所定の組成のターゲットを用い、アルゴン(Ar)や窒素などの不活性ガスを用いてスパッタすることにより形成する。また、熱伝導度が $100\text{ Wm}^{-1}\text{K}^{-1}$ に達する薄膜ダイアモンド層やDLC(Diamond Like Carbon)層を設けても良い。

30

#### 【0024】

この上に第1の絶縁層503を形成する。第1の絶縁層の熱伝導率は $10\text{ Wm}^{-1}\text{K}^{-1}$ 未満である材料を用いる。このような材料として、酸化シリコン膜や窒化シリコン膜などを選択することができるが、好ましくは酸化窒化シリコン膜で形成すると良い。酸化窒化シリコン膜は、プラズマCVD法で $\text{SiH}_4$ 、 $\text{N}_2\text{O}$ を原料ガスとして作製する。この原料ガスに $\text{O}_2$ を添加しても良い。作製条件は限定されないが、この第1の絶縁膜としての酸化窒化シリコン膜は膜厚を50~500nmとし、含有酸素濃度を5.5atomic%以上7.0atomic%以下とし、かつ、含有窒素濃度を1atomic%以上2.0atomic%以下となるようにする。このような組成として酸化窒化シリコン膜の内部応力が低減すると共に固定電荷密度が減少する。

40

#### 【0025】

第1の絶縁膜503は、図2(B)に示すようにエッチングして島状またはストライプ状に形成する。エッチングはフッ化水素(HF)やフッ化水素アンモニウム( $\text{NH}_4\text{HF}_2$ )を含む溶液で行う。島状に形成した第1の絶縁膜504、505の大きさは適宜決定されるものである。その大きさは用途によるものであるが、例えばTFTの大きさに合わせて

50

$0.35 \times 0.35 \mu\text{m}^2$  (チャネル長×チャネル幅)としたサブミクロンサイズとしても良いし、 $8 \times 8 \mu\text{m}^2$ 、 $8 \times 200 \mu\text{m}^2$ または $12 \times 400 \mu\text{m}^2$ などとすることができる。少なくとも TFT のチャネル形成領域の位置と大きさに合わせて第 1 の絶縁層 504、505 を形成することにより、この上に形成される結晶質半導体膜の一つの結晶粒でチャネル形成領域を形成することが可能となる。また、第 1 の絶縁層 504、505 の端面における側壁の角度は、ガラス基板 501 の主表面に対して、 $10^\circ$ 以上 $40^\circ$ 未満となるようにテーパー状にエッチングしてこの上に積層させる膜のステップカバレージを確保する。このように作製した熱伝導層 502 と第 1 の絶縁膜 503、504 を、本明細書では下地層と呼ぶ。

## 【0026】

10

次に、 $25 \sim 80 \text{ nm}$  (好ましくは $30 \sim 60 \text{ nm}$ ) の厚さで非晶質構造を有する半導体膜 506 を、プラズマ CVD 法やスパッタ法などの公知の方法で形成する。本実施形態では、プラズマ CVD 法で非晶質シリコン膜を $55 \text{ nm}$ の厚さに形成した。非晶質構造を有する半導体膜としては、非晶質半導体膜や微結晶半導体膜があり、非晶質シリコンゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。

## 【0027】

そして、レーザーアニール法を使用して非晶質半導体膜 506 を結晶化させる。結晶化の方法は、その他にラピットサーマルアニール法 (RTA 法) を適用することもできる。RTA 法では、赤外線ランプ、ハロゲンランプ、メタルハライドランプ、キセノンランプなどを光源に用いる。結晶化の工程ではまず、非晶質半導体膜が含有する水素を放出させておくことが望ましく、 $400 \sim 500$  度 1 時間程度の熱処理を行い含有する水素量を 5 atomic% 以下にしておく。

20

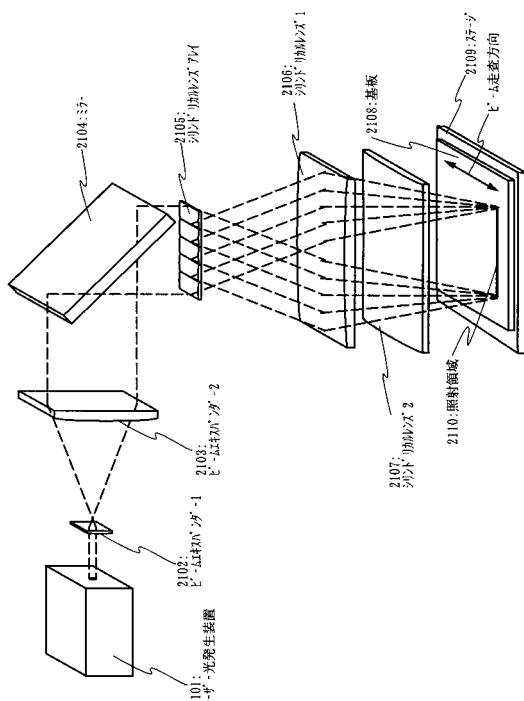

## 【0028】

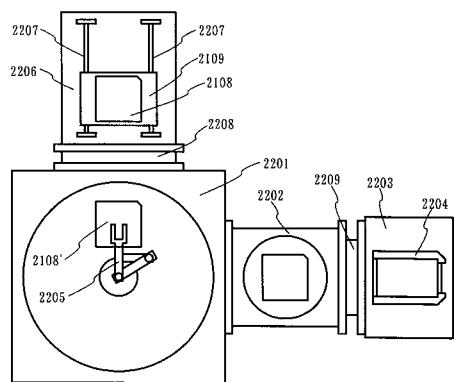

結晶化をレーザーアニール法にて行う場合には、パルス発振型または連続発光型のエキシマレーザーやアルゴンレーザー、または YAG レーザーなどの固体レーザーをその光源とする。図 22 はこのようなレーザーアニール装置の構成を示す図である。レーザー光発生装置 2101 にはエキシマレーザーやアルゴンレーザーなどを適用する。レーザー光発生装置 2101 から発せられたレーザービームはビームエキスパンダー 2102、2103 によりレーザービームを一方向に広げ、ミラー 2104 によって反射したレーザービームは、シリンドリカルレンズアレイ 2105 で分割され、シリンドリカルレンズ 2106、2107 によって、線幅 $100 \sim 1000 \mu\text{m}$ の線状ビームにして、試料面に照射領域 2110 を形成するように照射する。基板 2108 は X 方向、Y 方向、Z 方向に動作可能なステージ 2109 に保持される。そして、照射領域 2110 に対し、ステージ 2109 を動かすことにより、基板 2108 の全面に渡ってレーザーアニールを施すことができる。このとき、基板 2108 は大気雰囲気中に保持しても良いし、図 23 で示すような反応室を設け、減圧下または不活性ガス雰囲気中に保持して結晶化を行っても良い。

30

## 【0029】

図 23 は図 22 で説明したレーザーアニール装置の基板保持方法に関する一実施形態を説明する図である。ステージ 2109 に保持された基板 2108 は反応室 2206 に設置される。反応室内は図示されていない排気系またはガス系により減圧状態または不活性ガス雰囲気とすることが出来、ステージ 2109 はガイドレール 2207 に沿って反応室内を移動することができる。レーザー光は基板 2108 の上面に設けられた図示されていない石英製の窓から入射する。このような構成にすると、ステージ 2109 に設けた加熱手段 (図示せず) によって基板 2108 を $300 \sim 500$  度まで加熱することができる。また、図 23 ではこの反応室 2206 にトランスファー室 2201、中間室 2202、ロード・アンロード室 2203 が接続し、仕切弁 2208、2209 で分離されている。ロード・アンロード室 2203 には複数の基板を保持することが可能なカセット 2204 が設置され、トランスファー室 2201 に設けられた搬送口ボット 2205 により基板が搬送される。基板 2108' は搬送中の基板を表す。こうのうのような構成とすることによりレーザーアニールを減圧下または不活性ガス雰囲気中で連続して処理することができる

40

50

。

### 【0030】

レーザーアニール条件は実施者が適宜選択するものであるが、例えば、エキシマレーザーのパルス発振周波数30Hzとし、レーザーエネルギー密度を100～500mJ/cm<sup>2</sup>(代表的には300～400mJ/cm<sup>2</sup>)とする。そして線幅100～1000μm、例えば線幅400μmの線状ビームを基板全面に渡って照射する。この線幅は島状に形成した第1の絶縁膜よりも大きいので、1パルスの線状ビームの照射で第1の絶縁膜上の非晶質シリコン層を結晶化させることもできる。または、線状ビームを走査しながら複数回照射しても良い。この時の線状ビームの重ね合わせ率(オーバーラップ率)を50～98%として行うと良い。レーザービームの形状は面状としても同様に処理することができる。

10

### 【0031】

エキシマレーザーのパルス発振周波数を30Hzとすると、そのパルス幅は数nsec(ナノ秒)～数十nsec、例えば30nsec程度であるので、非晶質シリコン膜にパルス状の線状レーザービームを照射すると、瞬時に加熱され、加熱時間よりも遙かに長い時間冷却されることになる。この時、図2(D)に示すように第1の絶縁膜が形成されている領域を領域A、それ以外の領域を領域Bとすると、領域Aは第1の絶縁膜が形成されている分体積が増えるため、領域Bと比べレーザービームの照射による温度上昇が低くなる。一方、レーザービームの照射が終わった直後からは、熱伝導層502を通して熱が拡散するので、領域Bの方が急激に冷却される。

### 【0032】

連続発光型のエキシマレーザーをレーザー発生装置2101に使用する場合には、同様の光学系を使用する。例えば、出力1000Wの連続発光エキシマレーザーを使用すると、光学系にて400μm×125mmの線状ビームにして0.1～10m/secの走査速度で基板全面をスキャンすれば良い。

20

### 【0033】

レーザーアニール法では、照射するレーザービームの条件を最適なものとすることにより、結晶核の発生密度と、その結晶核からの結晶成長を制御している。

領域Aは加熱と冷却の温度変化が比較的おだやかなものとなるため、領域Aにある半導体膜508はその中心から結晶粒が成長し、第1の絶縁層504、505上のほぼ全面に渡って単一の結晶粒を成長させることができる。一方、領域Bは急激に冷却されることにより、領域Bにある半導体膜507は小さな結晶粒しか成長しないので、複数の結晶粒が集合した構造となる。このようにして、結晶粒の位置を制御した結晶質半導体膜を形成することができる。

30

### 【0034】

その後、形成された結晶質半導体膜の領域A上にフォトレジストパターンを形成し、ドライエッチングによって領域Bの結晶質シリコン膜を選択的に除去して、島状半導体層509、510を形成しても良い。ドライエッチングにはCF<sub>4</sub>とO<sub>2</sub>の混合ガスを用いる。このようにして作製された島状半導体層509、510には10<sup>16</sup>～10<sup>18</sup>/cm<sup>3</sup>の欠陥準位が残留するため、水素雰囲気中、または1～3%の水素を含む窒素雰囲気中、または、プラズマ化して生成された水素を含む雰囲気中で300～450°の温度で加熱処理して水素化の工程を実施すると良い。この水素化の工程によって、0.01～0.1 atomic%程度の水素が島状半導体層509、510に添加される。このようにして、島状半導体層509、510は単一の結晶粒で形成され、実質的に単結晶と同等であるため、この部分にTFTなどの素子を形成すると単結晶シリコン基板に形成されるMOSトランジスタに匹敵する特性を得ることができる。

40

### 【0035】

#### [実施形態2]

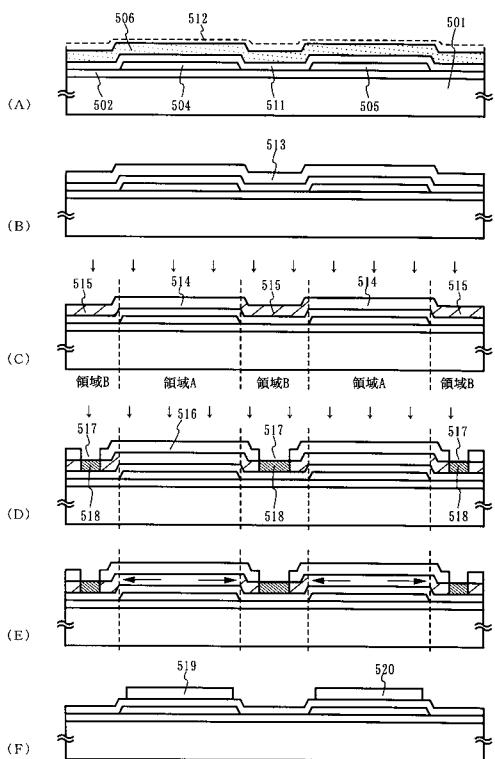

図3に示す実施形態は、実施形態1と同様に基板501上に熱伝導層502を形成し、第1の絶縁層504、505を形成する。その後、熱伝導層および第1の絶縁層上に第2の絶縁層511を形成する。第2の絶縁層は第1の絶縁層と同様に酸化窒化シリコン膜で形

50

成すると良い。第2の絶縁層511上には実施形態1と同様な手順により、島状半導体層509、510を形成する。

#### 【0036】

第2の絶縁層511はその膜厚を変化させることで、半導体膜から基板への熱が拡散する速度を制御することができる。また、熱伝導層として用いる材料の種類やその作製条件にもよるが、窒化アルミニウムなどは内部応力が比較的大きいので、その影響で半導体膜との界面で歪みが発生し、これが結晶化に悪影響を及ぼす場合もあるが、図3に示すように内部応力が小さい酸化窒化シリコン膜を形成しておくと、そのような悪影響を緩和させることができる。この場合、第2の絶縁層の厚さは5～100nmとすれば良い。

#### 【0037】

10

#### [実施形態3]

TFTの活性層とする結晶質半導体膜の作製方法は、レーザーアニール法のみに限定されるものではなく、レーザーアニール法と熱アニール法を併用しても良い。例えば、図2(C)の状態の非晶質構造を有する半導体膜506(非晶質シリコン膜)が形成された基板をファーネスアニール炉を用い600～670で4～12時間程度加熱して結晶化させ、その後実施形態1で説明したレーザーアニール法で処理しても同様な効果が得られる。その他に熱アニール法による結晶化は、特開平7-130652号公報で開示される触媒元素を用いる結晶化法にも応用することができる。

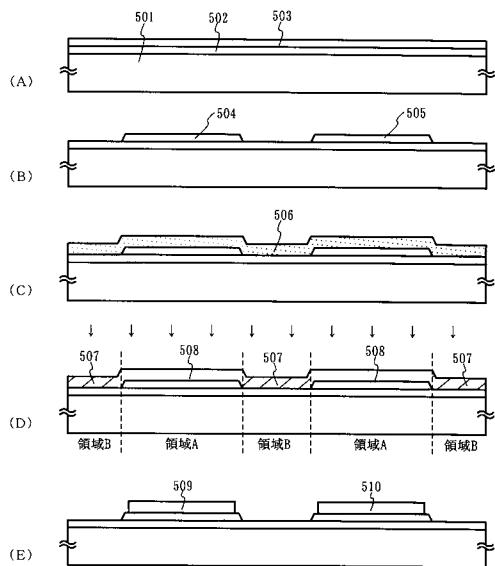

#### 【0038】

図4(A)で示すように、実施形態1と同様にして、ガラス基板501上に熱伝導層502、第1の絶縁層504、505を形成する。さらに、実施形態2と同様に第2の絶縁層511を形成しても良いし、この層は省略しても良い。そしてプラズマCVD法やスパッタ法などで非晶質半導体膜506を25～80nmの厚さで形成する。例えば、非晶質シリコン膜を55nmの厚さで形成する。そして、重量換算で10ppmの触媒元素を含む水溶液をスピンドル法で塗布して触媒元素を含有する層512を形成する。触媒元素にはニッケル(Ni)、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Plt)、銅(Cu)、金(Au)などである。この触媒元素を含有する層511は、スピンドル法の他にスパッタ法や真空蒸着法によって上記触媒元素の層を1～5nmの厚さに形成しても良い。

#### 【0039】

20

第1の絶縁層504、505が選択的に形成されることによって非晶質半導体膜506の表面に凹凸が形成される。触媒元素を含む水溶液をスピンドル法で塗布して触媒元素を含有する層512を形成した場合、触媒元素を含有する層512の厚さは一様ではなく、相対的に第1の絶縁層が形成されない凹の領域が厚くなる。その結果、次の熱アニールの工程で半導体膜中に拡散する触媒元素の濃度も多くなる。

#### 【0040】

そして、図4(B)に示す結晶化の工程では、まず400～500で1時間程度の熱処理を行い、非晶質シリコン膜の含有水素量を5atomic%以下にする。

そして、ファーネスアニール炉を用い、窒素雰囲気中において550～600で1～8時間の熱アニールを行う。以上の工程により結晶質シリコン膜を得ることができる。しかし、ここまでこの工程で熱アニールによって作製された結晶質半導体膜513は、透過型電子顕微鏡などで微視的に観察すると複数の結晶粒から成り、その結晶粒の大きさとその配置は一様ではなくランダムなものである。また、ラマン分光法で観測すると局所的に非晶質領域が残存していることが観察されることがある。

#### 【0041】

このような結晶質半導体膜513の結晶粒を所定の位置に形成できるように制御し、また大粒形化を目的として、レーザーアニール法をこの段階で実施すると有効である。レーザーアニール法では結晶質半導体膜513を一旦溶融状態にしてから再結晶化させるため、上記目的を達成することができる。例えば、XeClエキシマレーザー(波長308nm)を用い、光学系で線状ビームを形成して、発振周波数5～50Hz、エネルギー密度100

40

50

～500mJ/cm<sup>2</sup>として線状ビームのオーバーラップ率を80～98%として照射する。この時、図4(C)に示すように、第1の絶縁層504、505が形成されている領域Aとそれ以外の領域Bとでは、前述のようにレーザービームの照射により加熱される最高温度と、照射後の冷却速度がことなることにより、領域Aでは大きな結晶粒が成長しやすくなる一方で、領域Bは急激に冷却されることにより、小さな結晶粒しか成長しない。このようにして、大粒形の位置を制御した結晶質半導体膜を形成することができる。

#### 【0042】

このようにして、第1の絶縁層上に形成された作製された結晶質半導体膜514は、その領域上でほぼ単一の結晶粒を形成させることができる。それ以外の結晶質半導体膜515は相対的に小さく、大きさもランダム結晶粒が形成される領域である。しかし、この状態で結晶質半導体膜514、515の表面に残存する触媒元素の濃度は $3 \times 10^{10} \sim 2 \times 10^{11}$ atoms/cm<sup>2</sup>である。

#### 【0043】

そこで、特開平10-247735号公報で開示されているゲッタリングの工程を行っても良い。このゲッタリングの工程により結晶質シリコン膜中の触媒元素の濃度を $1 \times 10^{17}$ atoms/cm<sup>3</sup>以下、好ましくは $1 \times 10^{16}$ atoms/cm<sup>3</sup>にまで低減させることができる。まず、図4(D)に示すように、結晶質半導体膜514、515の表面にマスク絶縁膜膜516を150nmの厚さに形成し、パターニングにより開口部517を形成し、結晶質シリコン膜を露出させる。そして、リンを添加する工程を実施して、結晶質シリコン膜にリン含有領域518を設ける。

この状態で、図4(E)に示すように、窒素雰囲気中で500～800(好ましくは500～550)、5～24時間、例えば525、12時間の熱処理を行うと、リン含有領域518がゲッタリングサイトとして働き、結晶質シリコン膜514、515に残存している触媒元素をリン含有領域518に偏析させることができる。そして、マスク絶縁膜膜516とリン含有領域518を除去し、図4(F)に示すように島状半導体層519、520を形成することにより、結晶化の工程で使用した触媒元素の濃度を $1 \times 10^{17}$ atoms/cm<sup>3</sup>以下にまで低減された結晶質シリコン膜を得ることができる。

#### 【0044】

このようにして、触媒元素を添加して熱アニール法により作製した結晶質シリコン膜に対し、本発明のレーザーアニール法による結晶化の工程を実施すると、実施形態1において示したレーザーアニール法のみの結晶化の工程と比較して、さらに結晶粒の大きな結晶質半導体膜を得ることができる。しかし、作製された島状半導体層519、520には $10^{16} \sim 10^{18}$ /cm<sup>3</sup>の欠陥準位が残留するため、水素雰囲気中、または1～3%の水素を含む窒素雰囲気中、または、プラズマ化して生成された水素を含む雰囲気中で300～450の温度で加熱処理して水素化の工程を実施することによって欠陥密度を $10^{16}/cm^3$ 以下にすることができる。この水素化の工程によって、0.01～0.1 atomic%程度の水素が島状半導体層519、520に添加される。

#### 【0045】

##### 【実施例】

###### 【実施例1】

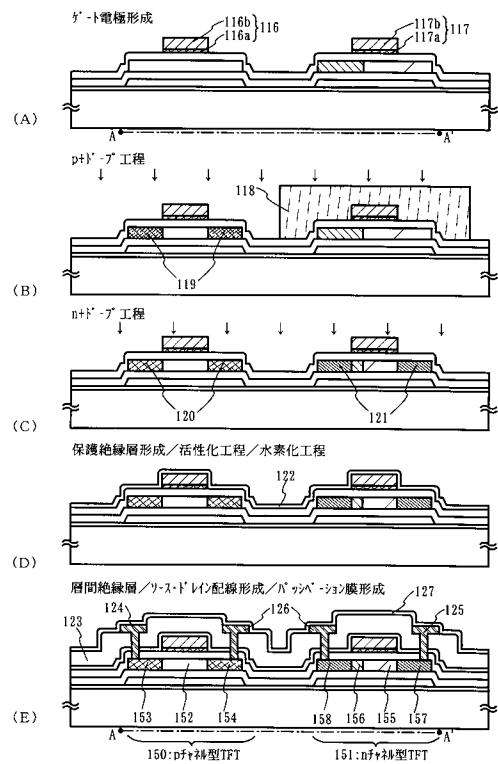

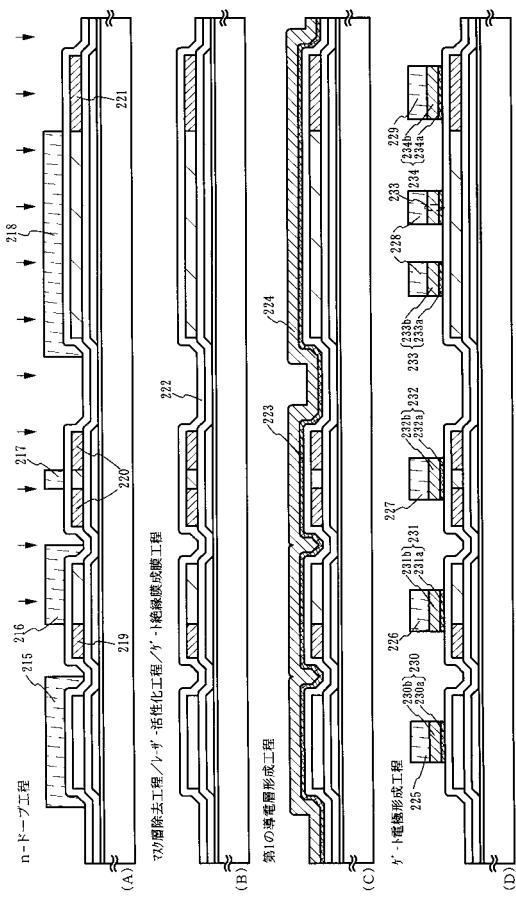

本実施例では、nチャネル型TFTとpチャネル型TFTでなるCMOS回路の作製工程を図5と図6を用いて説明する。

#### 【0046】

図5(A)において、基板101にはコーニング社の#7059ガラスや#1737ガラス基板などに代表されるバリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどを用いる。そして、ガラス歪み点よりも10～20程度低い温度であらかじめ熱処理しておくと後の工程において基板の収縮による変形を低減できる。この基板101のTFTを形成する表面に、透光性と絶縁性を有する熱伝導層102を少なくとも1層形成する。ここでは、酸化窒化アルミニウム(AlN<sub>x</sub>O<sub>1-x</sub>: 0.02 × 0.5)を50～500nmの厚さで形成する。その他にSi、N、O、M(MはAl、Y、La、Gd、Dy、Nd、

10

20

30

40

50

S m、E r から選ばれた少なくとも 1 つの元素)、例えば AlSiON、LaSiONなどで形成しても良い。このような熱伝導層はスパッタ法で形成することができる。所望の組成のターゲットを用い、アルゴン (Ar) や窒素などの不活性ガスを用いてスパッタすることにより形成できる。また、熱伝導度が  $1000 \text{ Wm}^{-1}\text{K}^{-1}$  に達する薄膜ダイアモンド層や DLC (Diamond Like Carbon) 層を設けても良い。

#### 【0047】

そして、この上にプラズマ CVD 法で SiH<sub>4</sub>、N<sub>2</sub>O から作製する酸化窒化シリコン膜を 50 ~ 500 nm の厚さで形成し、フッ化水素 (HF) やフッ化水素アンモニウム (NH<sub>4</sub>HF<sub>2</sub>) を含む溶液で部分的にエッチングして、島状に第 1 の絶縁膜 103、104 を形成する。この第 1 の絶縁膜の含有酸素濃度は 55 atomic% 以上 70 atomic% 以下とし、かつ、含有窒素濃度 1 atomic% 以上 20 atomic% 以下となるようにする。このような組成とすることにより、膜中の固定電荷密度を低減させ、さらに膜を緻密化できる。

10

#### 【0048】

島状に形成した第 1 の絶縁膜 103、104 の大きさは、後の工程で活性層とすべく形成する島状半導体層の大きさと同じかそれよりも若干大きく形成する。

もしくは、TFT のチャネル形成領域の大きさと同じか若干大きくする。島状半導体層の大きさは要求される TFT の特性に応じて適宜決められるものであるが、例えば、20 μm × 8 μm (チャネル長方向の長さ × チャネル幅方向の長さ) としても良いし、28 μm × 30 μm、45 μm × 63 μm など様々な大きさで形成される。従って、第 1 の絶縁膜 103、104 の外寸は、それぞれの島状半導体層の大きさに合わせて、同じ大きさかそれよりも 1 ~ 20 % 程度大きくする。また、第 1 の絶縁膜 103、104 の端面における側壁の角度は、ガラス基板の主表面に対して、10 度以上 40 度未満となるようにテーパーエッチングしてこの上に積層させる膜のステップかバレージを確保する。

20

#### 【0049】

さらに、プラズマ CVD 法で SiH<sub>4</sub>、N<sub>2</sub>O から作製する酸化窒化シリコン膜から成る第 2 の絶縁層 105 を形成する。酸化窒化シリコン膜の組成は、含有酸素濃度が 55 atomic% 以上 65 atomic% 以下であり、かつ、含有窒素濃度が 1 atomic% 以上 20 atomic% 以下として、内部応力を低減させておき、この上に形成する半導体層に直接ストレスが及ばないようにする。第 2 の絶縁膜は 10 ~ 200 nm (好ましくは 20 ~ 100 nm) の厚さで形成する。第 2 の絶縁層は実施形態 1 で示すように省略することもできる。

30

#### 【0050】

次に、25 ~ 80 nm (好ましくは 30 ~ 60 nm) の厚さで非晶質構造を有する半導体層を、プラズマ CVD 法やスパッタ法などの公知の方法で形成する。例えば、プラズマ CVD 法で非晶質シリコン膜を 55 nm の厚さに形成する。非晶質構造を有する半導体膜としては、非晶質半導体膜や微結晶半導体膜があり、非晶質シリコングルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。また、下地層のうち第 2 の絶縁層と非晶質半導体層とは両者を連続形成しても良い。

30

#### 【0051】

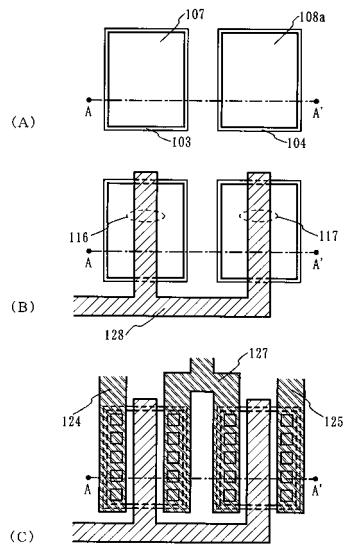

そして、実施形態 1 ~ 3 に記載したいずれかの方法を選択し、結晶質半導体膜 (ここでは結晶質シリコン膜) を形成し、エッチング処理をして島状半導体層 107、108a を形成する。エッチング処理はドライエッチング法で行い、CF<sub>4</sub> と O<sub>2</sub> の混合ガスを用いた。島状半導体層 107、108a はそれぞれ単一の結晶粒から成るものであり、エッチングによりパターン形成したものは実質的に単結晶とみなすことができた。その後、プラズマ CVD 法や減圧 CVD 法、またはスパッタ法により 50 ~ 100 nm の厚さの酸化シリコン膜によるマスク層 109 を形成する。例えば、プラズマ CVD 法による場合、オルトケイ酸テトラエチル (Tetraethyl Ortho silicate: TEOS) と O<sub>2</sub> とを混合し、反応圧力 40 Pa、基板温度 300 ~ 400 とし、高周波 (13.56 MHz) 電力密度 0.5 ~ 0.8 W/cm<sup>2</sup> で放電させ、100 ~ 150 nm 代表的には 130 nm の厚さに形成する。

40

#### 【0052】

図 7 (A) は図 5 (A) における上面図を示している。図 7 (A) では、マスク層と第 1

50

および第2の絶縁膜は省略して表している。島状半導体層107、108bは、島状にパターン形成された第1の絶縁膜103、104にそれぞれ重なるようにして設けられている。図7(A)において、A-A'断面が図5(A)における断面構造に対応している。

#### 【0053】

そして図5(B)に示すように、フォトレジストマスク110を設け、nチャネル型TFTを形成する島状半導体層108aにしきい値電圧を制御する目的で $1 \times 10^{16} \sim 5 \times 10^{17}$ atoms/cm<sup>3</sup>程度の濃度でp型を付与する不純物元素を添加する。半導体に対してp型を付与する不純物元素には、ホウ素(B)、アルミニウム(Al)、ガリウム(Ga)など周期律表第13族の元素が知られている。ここではイオンドープ法でジボラン(B<sub>2</sub>H<sub>6</sub>)を用いホウ素(B)を添加した。ホウ素(B)添加は必ずしも必要でなく省略しても差し支えないが、ホウ素(B)を添加した半導体層108bはnチャネル型TFTのしきい値電圧を所定の範囲内に収めるために形成することができる。10

#### 【0054】

nチャネル型TFTのLDD領域を形成するために、n型を付与する不純物元素を島状半導体層108bに選択的に添加する。半導体に対してn型を付与する不純物元素には、リン(P)、砒素(As)、アンチモン(Sb)など周期律表第15族の元素が知られている。フォトレジストマスク111を形成し、ここではリン(P)を添加すべく、fosfain(PH<sub>3</sub>)を用いたイオンドープ法を適用した。形成される不純物領域112におけるリン(P)濃度は $2 \times 10^{16} \sim 5 \times 10^{19}$ atoms/cm<sup>3</sup>の範囲とする(図5(C))。本明細書中では、不純物領域112に含まれるn型を付与する不純物元素の濃度を(n<sup>-</sup>)と表す。20

#### 【0055】

次に、マスク層109を純水で希釈したフッ酸などのエッチング液により除去した。そして、図5(B)と(C)で島状半導体層108bに添加した不純物元素を活性化させる工程を行う。活性化は窒素雰囲気中において500~600で1~4時間の熱アニールや、他の手法としてレーザーハニールなどの方法により行うことができる。また、両方の方法を併用しても良い。本実施例では、レーザー活性化の方法を用い、エキシマレーザー光を用い、線状ビームを形成して、発振周波数5~50Hz、エネルギー密度100~500mJ/cm<sup>2</sup>として線状ビームのオーバーラップ率を80~98%として、島状半導体層が形成された基板全面を処理した。尚、レーザー光の照射条件には何ら限定される事項はなく、実施者が適宜決定すれば良い。30

#### 【0056】

ゲート絶縁膜113はプラズマCVD法またはスパッタ法を用い、膜厚を40~150nmとしてシリコンを含む絶縁膜で形成する。例えば、120nmの厚さで、第1の絶縁膜と同じ酸化窒化シリコン膜で形成すると良い。また、SiH<sub>4</sub>とN<sub>2</sub>OにO<sub>2</sub>を添加させて作製された酸化窒化シリコン膜は、膜中の固定電荷密度が低減されているのでさらに良い。ゲート絶縁膜は、このような酸化窒化シリコン膜に限定されるものではなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い(図5(D))。

#### 【0057】

図5(E)に示すように、ゲート絶縁膜上にゲート電極を形成するために導電層を成膜する。この導電層は単層で形成しても良いが、必要に応じて二層あるいは三層といった積層構造とすることもできる。本実施形態では、導電性の窒化物金属膜から成る導電層(A)114と金属膜から成る導電層(B)115とを積層した構造とした。導電層(B)115はタンタル(Ta)、チタン(Ti)、モリブデン(Mo)、タンクステン(W)から選ばれた元素、または前記元素を主成分とする合金か、前記元素を組み合わせた合金膜(代表的にはMo-W合金膜、Mo-Ta合金膜)で形成すれば良く、導電層(A)114は窒化タンタル(TaN)、窒化タンクステン(WN)、窒化チタン(TiN)膜、窒化モリブデン(MoN)などで形成する。また、導電層(A)114はタンクステンシリサイド、チタンシリサイド、モリブデンシリサイドを適用しても良い。導電層(B)115は低抵抗化を図るために含有する不純物濃度を低減させると良く、特に酸素濃度に関して40

は 30 ppm 以下とすると良かった。例えば、タンゲステン (W) は酸素濃度を 30 ppm 以下とすることで 20  $\mu$  cm 以下の比抵抗値を実現することができる。

#### 【0058】

導電層 (A) 114 は 10 ~ 50 nm (好ましくは 20 ~ 30 nm) とし、導電層 (B) 115 は 200 ~ 400 nm (好ましくは 250 ~ 350 nm) とすれば良い。本実施例では、導電層 (A) 114 に 30 nm の厚さの TaN 膜を、導電層 (B) 115 には 350 nm の Ta 膜を用い、いずれもスパッタ法で形成した。TaN 膜は Ta をターゲットとしてスパッタガスに Ar と窒素との混合ガスを用いて成膜した。Ta はスパッタガスに Ar を用いた。また、これらのスパッタガス中に適量の Xe や Kr を加えておくと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。10 相の Ta 膜の抵抗率は 20  $\mu$  cm 程度でありゲート電極に使用することができるが、相の Ta 膜の抵抗率は 180  $\mu$  cm 程度でありゲート電極とするには不向きであった。TaN 膜は相に近い結晶構造を持つので、この上に Ta 膜を形成すれば相の Ta 膜が容易に得られた。尚、図示しないが、導電層 (A) 114 の下に 2 ~ 20 nm 程度の厚さでリン (P) をドープしたシリコン膜を形成しておくことは有効である。これにより、その上に形成される導電膜の密着性向上と酸化防止を図ると同時に、導電層 (A) または導電層 (B) が微量に含有するアルカリ金属元素がゲート絶縁膜 113 に拡散するのを防ぐことができる。いずれにしても、導電層 (B) は抵抗率を 10 ~ 500  $\mu$  cm の範囲ですることが好ましい。

#### 【0059】

次に、所定のパターンのフォトレジストマスクを形成し、導電層 (A) 114 と導電層 (B) 115 とを一括でエッチングしてゲート電極 116、117 を形成する。例えば、ドライエッチング法により CF<sub>4</sub> と O<sub>2</sub> の混合ガス、または Cl<sub>2</sub> を用いて 1 ~ 20 Pa の反応圧力で行うことができる。ゲート電極 116、117 は、導電層 (A) から成る 116a、117a と、導電層 (B) から成る 116b、117b とが一体として形成されている。この時、n チャネル型 TFT に設けるゲート電極 117 は不純物領域 112 の一部と、ゲート絶縁膜 113 を介して重なるように形成する。また、ゲート電極は導電層 (B) のみで形成することも可能である (図 6 (A))。20

#### 【0060】

図 7 (B) は図 6 (A) における上面図を示している。図 7 (B) では、ゲート絶縁膜と第 1 および第 2 の絶縁膜とは省略して表している。島状半導体層 107、108b 上にゲート絶縁膜を介して設けられるゲート電極 116、117 は、ゲート配線 128 に接続する。30 図 7 (B) において、A - A' 断面が図 6 (A) における断面構造に対応している。

#### 【0061】

次いで、p チャネル型 TFT を形成する島状半導体層 107 にソース領域およびドレイン領域とする不純物領域 119 を形成する。ここでは、ゲート電極 116 をマスクとして p 型を付与する不純物元素を添加し、自己整合的に不純物領域を形成する。このとき、n チャネル型 TFT を形成する島状半導体層 108b はフォトレジストマスク 118 で被覆しておく。そして、不純物領域 119 はジボラン (B<sub>2</sub>H<sub>6</sub>) を用いたイオンドープ法で形成する。この領域のボロン (B) 濃度は  $3 \times 10^{20} \sim 3 \times 10^{21}$  atoms/cm<sup>3</sup> となるようになる (図 6 (B))。40 本明細書中では、ここで形成された不純物領域 134 に含まれる p 型を付与する不純物元素の濃度を (p<sup>+</sup>) と表す。

#### 【0062】

次に、n チャネル型 TFT を形成する島状半導体層 108b にソース領域またはドレイン領域を形成する不純物領域 121 の形成を行った。ここでは、fosfphin (PH<sub>3</sub>) を用いたイオンドープ法で行い、この領域のリン (P) 濃度を  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms/cm<sup>3</sup> とした (図 6 (C))。50 本明細書中では、ここで形成された不純物領域 121 に含まれる n 型を付与する不純物元素の濃度を (n<sup>+</sup>) と表す。不純物領域 119 にも同時にリン (P) が添加されるが、既に前の工程で添加されたボロン (B) 濃度と比較して不純物領域 117 に添加されたリン (P) 濃度はその 1/2 ~ 1/3 程度なので p 型の導電性が確保され、TFT の特性に何ら影響を与えることはない。

## 【0063】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化する工程を熱アニール法で行う。この工程はファーネスアニール炉を用いれば良い。その他に、レーザーアニール法、またはラピッドサーマルアニール法（RTA法）で行うことができる。アニール処理は酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400～700、代表的には500～600で行うものであり、本実施例では550で4時間の熱処理を行った。

また、アニール処理の前に、50～200nmの厚さの保護絶縁層122を酸化窒化シリコン膜や酸化シリコン膜などで形成すると良い。酸化窒化シリコン膜は表1のいずれの条件でも形成できるが、その他にも、SiH<sub>4</sub>を27SCCM、N<sub>2</sub>Oを900SCCMとして反応圧力160Pa、基板温度325、放電電力密度0.1W/cm<sup>2</sup>で形成すると良い（図6（D））。

10

## 【0064】

活性化の工程の後、さらに、3～100%の水素を含む雰囲気中で、300～450で1～12時間の熱処理を行い、島状半導体層を水素化する工程を行った。この工程は熱的に励起された水素により島状半導体層にある10<sup>16</sup>～10<sup>18</sup>/cm<sup>3</sup>のダンギングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）行っても良い。

## 【0065】

活性化および水素化の工程が終了したら、保護絶縁層上にさらに酸化窒化シリコン膜または酸化シリコン膜を積層させ、層間絶縁層123を形成する。酸化窒化シリコン膜は保護絶縁層119と同様にしてSiH<sub>4</sub>を27SCCM、N<sub>2</sub>Oを900SCCMとして反応圧力160Pa、基板温度325とし、放電電力密度を0.15W/cm<sup>2</sup>として、500～1500nm（好ましくは600～800nm）の厚さで形成する。そして、層間絶縁層123および保護絶縁層122 TFTのソース領域またはドレイン領域に達するコントラクトホールを形成し、ソース配線124、125と、ドレイン配線126を形成する。図示していないが、本実施例ではこの電極を、Ti膜を100nm、Tiを含むアルミニウム膜300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とした。

20

## 【0066】

次に、パッシベーション膜127として、窒化シリコン膜または酸化窒化シリコン膜を50～500nm（代表的には100～300nm）の厚さで形成する。さらに、この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られた。例えば、3～100%の水素を含む雰囲気中で、300～450で1～12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。また、このような熱処理により層間絶縁層123および保護絶縁層122に存在する水素を島状半導体層107、108bに拡散させ水素化することもできる。いずれにしても、島状半導体層107、108b中の欠陥密度を10<sup>16</sup>/cm<sup>3</sup>以下とすることが望ましく、そのために水素を0.01～0.1atomic%程度付与すれば良かった。

30

## 【0067】

こうして図6（E）に示すように、基板101上に、nチャネル型TFT151とpチャネル型TFT150とを完成させることができた。pチャネル型TFT150には、島状半導体層107にチャネル形成領域152、ソース領域153、ドレイン領域154を有している。nチャネル型TFT151には、島状半導体層108にチャネル形成領域155、ゲート電極117と重なるLDD領域156（以降、このようなLDD領域をLovと記す）、ソース領域157、ドレイン領域158を有している。このLov領域のチャネル長方向の長さは、チャネル長3～8μmに対して、0.5～3.0μm（好ましくは1.0～1.5μm）とした。図2ではそれぞれのTFTをシングルゲート構造としたが、ダブルゲート構造でも良いし、複数のゲート電極を設けたマルチゲート構造としても差し支えない。

40

## 【0068】

50

図7(C)は図6(E)における上面図を示している。ソース配線124、125は、図示していない層間絶縁層123、保護絶縁層122に設けられたコンタクトホールによって島状半導体層107、108bと接触している。図7(C)において、A-A'断面が図6(E)における断面構造に対応している。

#### 【0069】

このようにして作製されたpチャネル型TFT150とnチャネル型TFT151とは、チャネル形成領域が単一の結晶粒、即ち単結晶で形成されている。その結果、TFTの動作時における電流輸送特性は、粒界のポテンシャルやトラップの影響を受けることがないので、単結晶シリコン基板に作製したMOSトランジスタに匹敵する特性を得ることができる。また、このようなTFTを用いてシフトレジスタ回路、バッファ回路、D/Aコンバータ回路、レベルシフタ回路、マルチブレクサ回路などを形成することができる。これらの回路を適宜組み合わせることにより、液晶表示装置やEL表示装置、および密着型イメージセンサなどガラス基板上に作製される半導体装置を形成することができる。10

#### 【0070】

##### [実施例2]

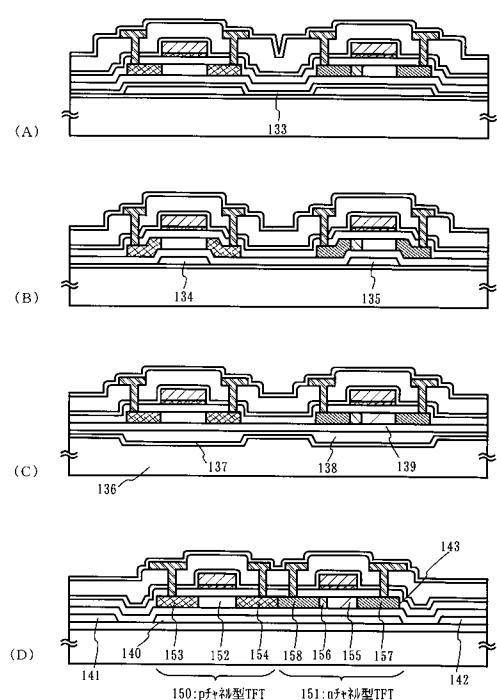

本実施例は図8を用い、実施例1で作製したTFTに対し、下地層を異なる形態で作製するものについて説明する。図8で示すTFT断面構造は、実施例1の作製手順に従って形成されるものであり、ここでは、実施例1との差異について示す。

#### 【0071】

図8(A)は、熱伝導層102、選択的に形成された第1の絶縁層103、104上に、SiH<sub>4</sub>、N<sub>2</sub>O、NH<sub>3</sub>からプラズマCVD法で作製した酸化窒化シリコン膜から成る絶縁層133を設ける。この酸化窒化シリコン膜は、含有酸素濃度が20 atomic%以上30 atomic%以下であり、かつ、含有窒素濃度が20 atomic%以上30 atomic%以下である酸化窒化シリコン膜であり、酸素の含有量と窒素の含有量をほぼ同等として形成する。その結果、窒化シリコン膜よりも内部応力を低減させ、かつ、アルカリ金属元素のプロッキング性をもたせることができる。さらにこの上に第2の絶縁層511を形成する。第1の絶縁層103、104の厚さ50~500nmに対し、絶縁層133は50~200nmの厚さで形成する。第3の絶縁層は応力を緩和する作用があり、その結果、TFTのしきい値電圧やS値の変動を抑える効果がある。20

#### 【0072】

図8(B)は第1の絶縁層134、135の大きさが島状半導体層107、108よりも相対的に小さくしたものである。第1の絶縁層上における結晶粒は大粒形化するが、このときチャネル形成領域152、155をこの部分に位置させると、チャネル形成領域内に結晶粒界を無くすことも可能である。30

#### 【0073】

図8(C)において、ガラス基板136のTFTを形成する表面に溝が形成されている。溝の深さは50~500nmとし、このような溝加工は所定のパターンでフォトレジストマスクをガラス基板表面に形成しておき、フッ化水素(HF)を含む水溶液でエッチングすることにより容易に形成できる。そして、溝が形成された表面に熱伝導層を形成する。熱伝導層137の厚さは50~500nmとする。その上に第1の絶縁層を500~2000nmの厚さで形成する。その後、CMP(Chemical-Mechanical Polishing: 化学的・機械的ポリッシング)法を用いて表面を平坦化する。例えば、深さ200nmの溝が形成されている表面に、熱伝導層137を100nmの厚さで形成し、第1の絶縁層を1000nmの厚さで形成する。その後、CMP法を用いて平坦化することにより、第1の絶縁層138の厚さは溝が形成されている部分で500nm、溝が形成されていない部分で300nmとすることができる。第2の絶縁膜に用いる酸化窒化シリコン膜に対するCMPの研磨剤には、例えば、塩化シリコンガスを熱分解して得られるフュームドシリカ粒子をKOH添加水溶液に分散したものを使う。このようにして平坦化された表面上に、実施形態1と同様にしてTFTを作製する。40

#### 【0074】

図8(D)は、nチャネル型TFT151とpチャネル型TFT150とを、第1の絶縁層140上に形成した一つの島状半導体層143に形成した例を示す。それぞれのTFTを作製する工程は同一であり、使用するフォトマスクのレイアウトパターンを変更することで、図8(D)の構造を完成させることができる。実施例1における図6(D)と同様に、pチャネル型TFT150には、チャネル形成領域152、ソース領域153、ドレイン領域154を有している。nチャネル型TFT151には、チャネル形成領域155、ゲート電極157と重なるLDD領域156、ソース領域157、ドレイン領域158を有している。

図6～図8ではそれぞれのTFTをシングルゲート構造とする例を示したが、ゲート電極の構造はこの他にダブルゲート構造でも良いし、複数のゲート電極を設けたマルチゲート構造としても差し支えない。このように2つのTFTを近接させることにより、TFTの特性バラツキを低減させることができ、また、集積度を向上させることができる。

10

#### 【0075】

##### [実施例3]

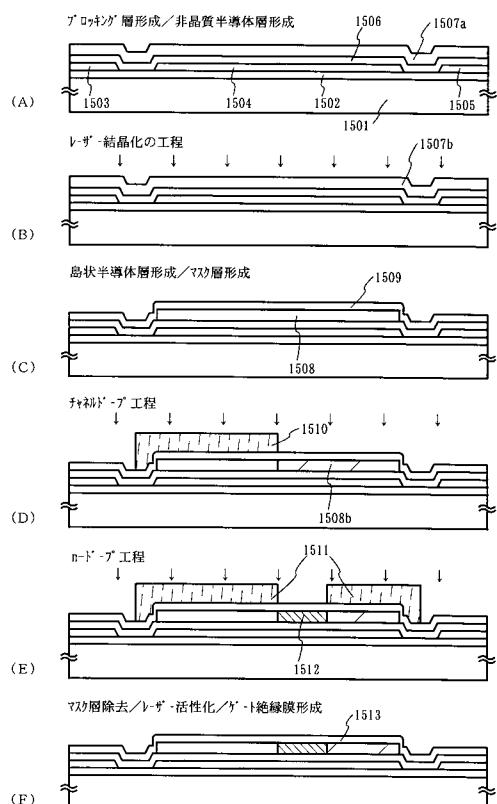

本実施形態を図27と図28を用い、実施例1とは異なる構造のnチャネル型TFTとpチャネル型TFTでなるCMOS回路の作製工程を示す。ここでの工程順および作製条件の許容される範囲は実施例1に従う。

#### 【0076】

図27(A)に示すように、実施例1と同様に、ガラス基板1501上に第1の絶縁膜1502、第2の絶縁膜1503～1505、第3の絶縁膜1506を形成する。パターン形成されている第2の絶縁膜のサイズに限定はないが、後の工程で $45\mu\text{m} \times 65\mu\text{m}$ (チャネル長方向の長さ×チャネル幅方向の長さ)の島状半導体層を形成するために、例えば、第2の絶縁膜1504のサイズは $50\mu\text{m} \times 70\mu\text{m}$ で形成する。そしてこの上に非晶質シリコン膜1507aを形成する。

20

#### 【0077】

次に、図27(B)に示すように実施形態1で説明したレーザーアニール法を用いて結晶質シリコン膜1507bを形成する。第2の絶縁膜上において、結晶粒径は数μmのサイズで成長するが、必ずしも単一の結晶粒である必要はなく、複数の結晶粒が存在しても構わない。

#### 【0078】

そして、図27(C)に示すように、第2の絶縁膜1504上に第3の絶縁膜1506を介して $45\mu\text{m} \times 65\mu\text{m}$ の島状半導体層1508を形成する。そしてマスク層1509を形成する。図6(D)から図7(F)で示す工程は、この島状半導体層1508を活性層としてnチャネル型TFTとpチャネル型TFTを形成し、CMOS回路を形成する工程を説明するものである。

30

#### 【0079】

図27(D)はチャネルドープの工程であり、レジストマスク1510を設け、nチャネル型TFTを形成する領域にイオンドープ法でボロン(B)を添加する。図27(E)では、レジストマスク1511を設け、nチャネル型TFTのLDD領域とするn<sup>-</sup>不純物領域1512を形成する。そして、図27(F)で示すように、マスク層1509を除去してレーザー活性化の処理を行い、ゲート絶縁膜1513を形成する。

40

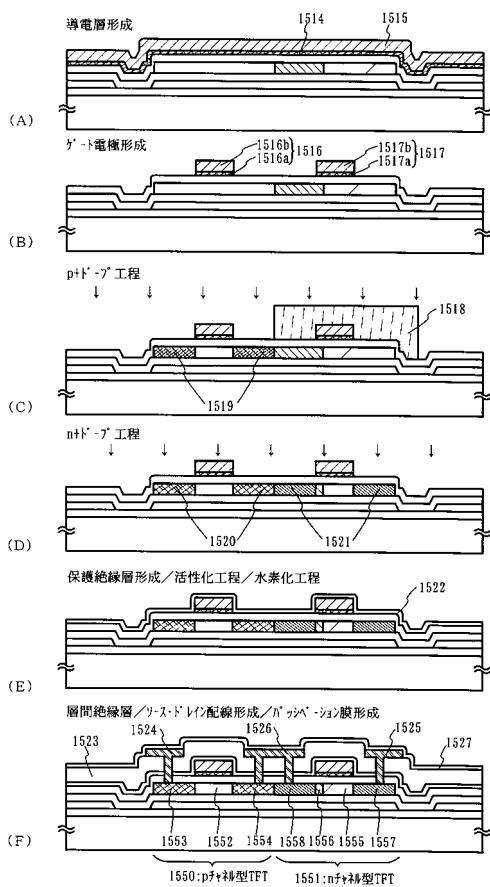

#### 【0080】

図28(A)において、ゲート絶縁膜上に導電層(A)1514、導電層(B)1515をスパッタ法で形成する。これらの導電層の好ましい組み合わせは、導電層(A)をTaNとし、導電層(B)をTaとする組み合わせ、または導電層(A)をWNとし、導電層(B)をWで形成する組み合わせである。そして、図28(B)に示すようにゲート電極1516、1517を形成する。ゲート電極1516、1517は、導電層(A)から成る1516a、1517aと導電層(B)から成る1516b、1517bで構成される。

50

#### 【0081】

そして、これらのゲート電極をマスクとして、イオンドープ法により不純物元素を添加して自己整合的にソース領域およびドレイン領域を形成する。図28(C)はpチャネル型TFTのソース領域およびドレイン領域を形成する工程であり、p型を付与する不純物元素をイオンドープ法で添加して、p<sup>+</sup>不純物領域1519を形成する。このとき、nチャネル型TFTが形成される領域はレジストマスク1518で覆っておく。図28(D)はnチャネル型TFTのソース領域およびドレイン領域を形成する工程であり、n型を付与する不純物元素をイオンドープ法で添加して、n<sup>+</sup>不純物領域1521を形成する。不純物領域1519にも同時にリン(P)が添加されるが、既に前の工程で添加されたボロン(B)濃度と比較して不純物領域1520に添加されたリン(P)濃度はその1/2~1/3程度なのでp型の導電性が確保され、TFTの特性に何ら影響を与えることはない。

10

#### 【0082】

その後、図28(E)に示すように保護絶縁層1522を形成し、活性化工程および水素化工程を実施する。活性化および水素化の工程が終了したら、保護絶縁層上にさらに酸化窒化シリコン膜または酸化シリコン膜を積層させ、層間絶縁層1523を形成する。そして、層間絶縁層1523および保護絶縁層1522TFTのソース領域またはドレイン領域に達するコンタクトホールを形成し、ソース配線1524、1525と、ドレイン配線1526を形成する。次に、パッシベーション膜1527として、窒化シリコン膜または酸化窒化シリコン膜を50~500nm(代表的には100~300nm)の厚さで形成する。さらに、この状態で水素化処理を行うとTFTの特性向上に対して好ましい結果が得られる。

20

#### 【0083】

こうして基板1501上に、nチャネル型TFT1551とpチャネル型TFT1550とを完成させることができる。pチャネル型TFT1550にはチャネル形成領域1552、ソース領域1553、ドレイン領域1554を有している。nチャネル型TFT1551はチャネル形成領域1555、ゲート電極1517と重なるLDD領域1556、ソース領域1557、ドレイン領域1558を有している。図28ではそれぞれのTFTをシングルゲート構造としたが、ダブルゲート構造でも良いし、複数のゲート電極を設けたマルチゲート構造としても差し支えない。

#### 【0084】

このようにして、一つの島状に形成された第2の絶縁層1504上に島状半導体層1508を形成し、その島状半導体層1508を用いて2つのTFTを形成することもできる。このように2つのTFTを近接させることにより、TFTの特性バラツキを低減させることができ、また、集積度を向上させることができる。

30

#### 【0085】

##### [実施例4]

図9~図13を用い、画素部の画素TFTと、画素部の周辺に設けられる駆動回路のTFTを同一基板上に作製する方法について工程に従って詳細に説明する。但し、説明を簡単にするために、制御回路ではシフトレジスタ回路、バッファ回路などの基本回路であるCMOS回路と、サンプリング回路を形成するnチャネル型TFTとを図示することにする。

40

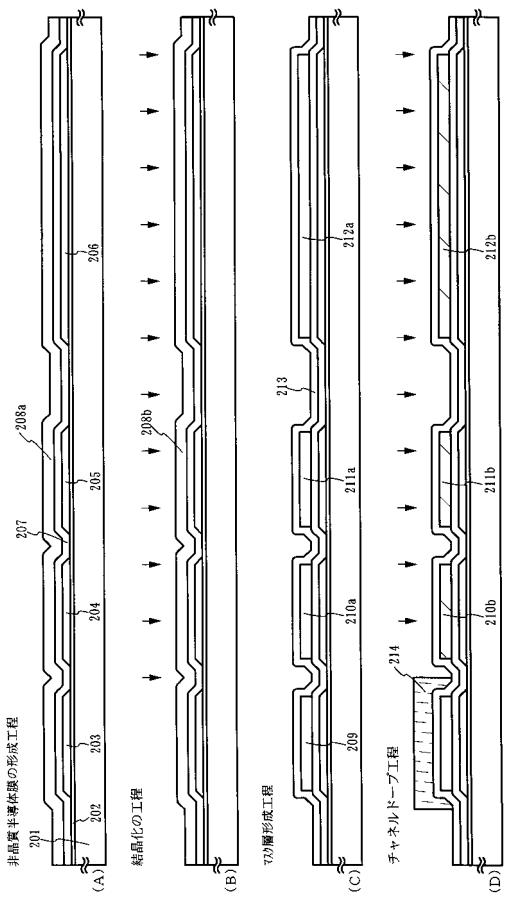

#### 【0086】

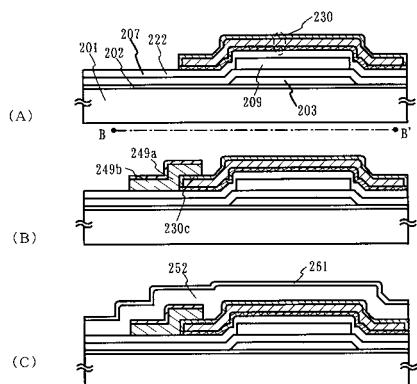

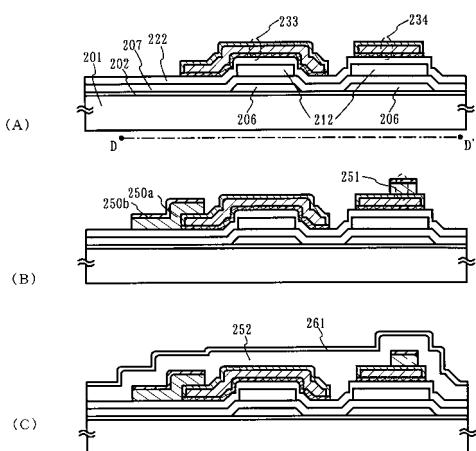

図9(A)において、基板201にはバリウムホウケイ酸ガラス基板やアルミノホウケイ酸ガラス基板を用いる。本実施例ではアルミノホウケイ酸ガラス基板を用いた。この基板201のTFTを形成する表面に、熱伝導層202として、窒化アルミニウム(AlN)を50nmの厚さで形成する。その上に島状に加工した酸化窒化シリコン膜から成る第1の絶縁層203~206を200nmの厚さで形成する。さらにその上に酸化窒化シリコン膜から成る第2の絶縁層207を100nmの厚さで形成した。このように、熱伝導層202と第1の絶縁層203~206、および第2の絶縁層207を積層して下地層とした。

#### 【0087】

次に、25~80nm(好ましくは30~60nm)の厚さで非晶質構造を有する半導体層2

50

0 8 aを、プラズマCVD法やスパッタ法などの公知の方法で形成する。本実施例では、

プラズマCVD法で非晶質シリコン膜を55nmの厚さに形成した。非晶質構造を有する半

導体膜としては、非晶質半導体膜や微結晶半導体膜があり、非晶質シリコンゲルマニウム

膜などの非晶質構造を有する化合物半導体膜を適用しても良い。また、第2の絶縁膜20

7と非晶質シリコン層208aとは同じ成膜法で形成することが可能であるので、両者を

連続形成しても良い。第2の絶縁膜を形成した後、一旦大気雰囲気に晒さないことでその

表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツキやしきい値電圧の変

動を低減させることができる。

#### 【0088】

そして、非晶質シリコン層208aから結晶質シリコン膜208bを形成する。これは実 10

施形態1で示したように、本発明のレーザーアニール法を適用する。

また、実施形態3で示した特開平7-130652号公報で開示された技術に従って、熱

アニール法とレーザーアニール法を組み合わせて結晶性シリコン膜208bを形成しても

良い。レーザーアニール法を用いる場合には、例えば、XeClエキシマレーザー(波長

308nm)をレーザー光発生装置として、図21で示したレーザーアニール装置を用い、

光学系で線状ビームを形成して、発振周波数5~50Hz、エネルギー密度100~500

mJ/cm<sup>2</sup>として線状ビームのオーバーラップ割合を80~98%として照射する。このよう

にして、結晶性シリコン膜208bを得る(図9(B))。

#### 【0089】

そして、結晶質シリコン膜208bをエッチング処理して島状に分割し、島状半導体層2 20

0 9、210a~212aを形成し活性層とする。その後、プラズマCVD法や減圧CV

D法、またはスパッタ法により50~100nmの厚さの酸化シリコン膜によるマスク層2

13を形成する。例えば、減圧CVD法でSiH<sub>4</sub>とO<sub>2</sub>との混合ガスを用い、266Paに

おいて400℃に加熱して酸化シリコン膜を形成する(図9(C))。

#### 【0090】

チャネルドープ工程は、フォトレジストマスク214を設け、nチャネル型TFTを形成

する島状半導体層210a~212aの全面にしきい値電圧を制御する目的で1×10<sup>16</sup>

~5×10<sup>17</sup>atoms/cm<sup>3</sup>程度の濃度でp型を付与する不純物元素としてボロン(B)を添

加した。ボロン(B)の添加はイオンドープ法で実施しても良いし、非晶質シリコン膜を

成膜するときに同時に添加しておくこともできる。ここでボロン(B)添加は必ずしも

必要でないが、ボロン(B)を添加した半導体層210b~212bはnチャネル型TFTのしきい

値電圧を所定の範囲内に収めるために形成することが好ましかった(図9(D))。

#### 【0091】

駆動回路のnチャネル型TFTのLDD領域を形成するために、n型を付与する不純物元

素を島状半導体層210b、211bに選択的に添加する。あらかじめフォトレジストマ

スク215~218を形成した。ここではリン(P)を添加するために、フォスフィン(PH<sub>3</sub>)を用いたイオンドープ法を適用した。形成された不純物領域(n<sup>-</sup>)219、22

0のリン(P)濃度は1×10<sup>17</sup>~5×10<sup>19</sup>atoms/cm<sup>3</sup>とする(図10(A))。また、不純物領域221は、画素部の保持容量を形成するための半導体層であり、この領域

にも同じ濃度でリン(P)を添加した。

#### 【0092】

次に、マスク層213をフッ酸などにより除去して、図9(D)と図10(A)で添加し

た不純物元素を活性化させる工程を行う。活性化は、窒素雰囲気中において500~60

0℃で1~4時間の熱アニールや、他の方法としてレーザーアニールの方法により行うこ

とができる。また、両者を併用して行っても良い。

本実施例では、レーザー活性化の方法を用い、KrFエキシマレーザー光(波長248nm)

を用い、線状ビームを形成して、発振周波数5~50Hz、エネルギー密度100~

500mJ/cm<sup>2</sup>として線状ビームのオーバーラップ割合を80~98%として走査し

て、島状半導体層が形成された基板全面を処理した。

10

20

30

40

50

尚、レーザー光の照射条件には何ら限定される事項はなく、実施者が適宜決定すれば良い。

#### 【0093】

そして、ゲート絶縁膜222をプラズマCVD法またはスパッタ法を用いて40～150 nmの厚さでシリコンを含む絶縁膜で形成する。例えば、SiH<sub>4</sub>、N<sub>2</sub>O、O<sub>2</sub>を原料としてプラズマCVD法で作製される酸化窒化シリコン膜で形成する。(図10(B))

#### 【0094】

次に、ゲート電極を形成するために第1の導電層を成膜する。本実施例では導電性の窒化物金属膜から成る導電層(A)223と金属膜から成る導電層(B)224とを積層させた。ここでは、Taをターゲットとしたスパッタ法で導電層(B)224をタンタル(Ta)で250 nmの厚さに形成し、導電層(A)223は窒化タンタル(TaN)で50 nmの厚さに形成した(図10(C))。

#### 【0095】

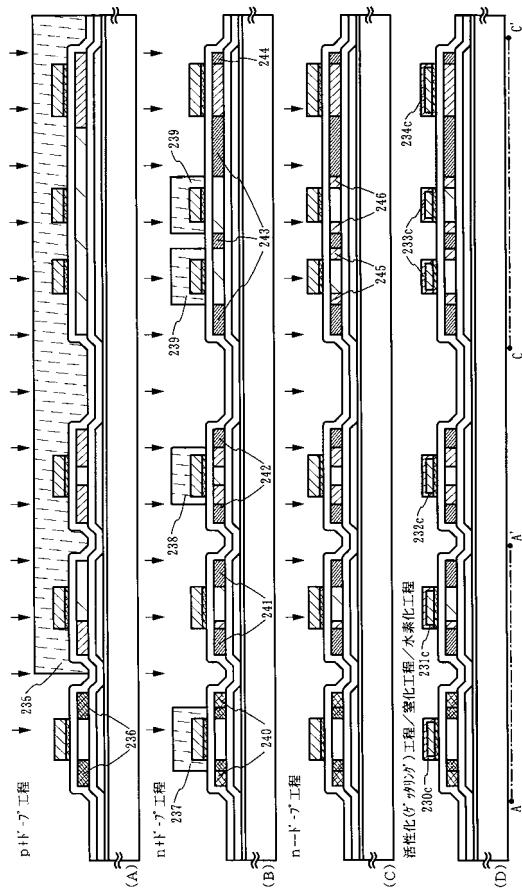

次に、フォトトレジストマスク225～229を形成し、導電層(A)223と導電層(B)224とを一括でエッチングしてゲート電極230～233と容量配線234を形成する。ゲート電極230～233と容量配線234は、導電層(A)から成る230a～234aと、導電層(B)から成る230b～234bとが一体として形成されている。この時、駆動回路に形成するゲート電極231、232は不純物領域219、220の一部と、ゲート絶縁膜222を介して重なるように形成する(図10(D))。

#### 【0096】

次いで、駆動回路のpチャネル型TFTのソース領域およびドレイン領域を形成するために、p型を付与する不純物元素を添加する工程を行う。ここでは、ゲート電極230をマスクとして、自己整合的に不純物領域を形成する。nチャネル型TFTが形成される領域はフォトトレジストマスク235で被覆しておく。そして、ジボラン(B<sub>2</sub>H<sub>6</sub>)を用いたイオンドープ法で不純物領域(p<sup>+</sup>)234を1×10<sup>21</sup>atoms/cm<sup>3</sup>の濃度で形成した(図11(A))。

#### 【0097】

次に、nチャネル型TFTにおいて、ソース領域またはドレイン領域として機能する不純物領域の形成を行った。レジストのマスク237～239を形成し、n型を付与する不純物元素を添加して不純物領域241～244を形成した。これは、フォスフィン(PH<sub>3</sub>)を用いたイオンドープ法で行い、不純物領域(n<sup>+</sup>)241～244の(P)濃度を5×10<sup>20</sup>atoms/cm<sup>3</sup>とした(図11(B))。不純物領域240には、既に前工程で添加されたボロン(B)が含まれているが、それに比して1/2～1/3の濃度でリン(P)が添加されるので、添加されたリン(P)の影響は考えなくても良く、TFTの特性に何ら影響を与えることはなかった。

#### 【0098】

そして、画素部のnチャネル型TFTのLDD領域を形成するために、n型を付与する不純物添加の工程を行った。ここではゲート電極233をマスクとして自己整合的にn型を付与する不純物元素をイオンドープ法で添加した。添加するリン(P)の濃度は5×10<sup>16</sup>atoms/cm<sup>3</sup>とし、図9(A)および図10(A)と図10(B)で添加する不純物元素の濃度よりも低濃度で添加することで、実質的には不純物領域(n<sup>-</sup>)245、246のみが形成される(図11(C))。

#### 【0099】

その後、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化するために熱処理工程を行う。この工程はファーネスアニール炉を用いた熱アニール法、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)で行うことができる。ここではファーネスアニール法で活性化工程を行った。熱処理は酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400～700℃、代表的には500～600℃で行うものであり、本実施例では550℃で4時間の熱処理を行った。

#### 【0100】

10

20

30

40

50

この熱アニールにおいて、ゲート電極 230～233 と容量配線 234 形成する Ta 膜 230b～234b は、表面から 5～80 nm の厚さで TaN から成る導電層 (C) 230c～234c が形成される。また、その他に導電層 (B) 230b～234b がタンゲステン (W) の場合には窒化タンゲステン (WN) が形成され、チタン (Ti) の場合には窒化チタン (TiN) を形成することができる。また、窒素またはアンモニアなどを用いた窒素を含むプラズマ雰囲気にゲート電極 230～234 を晒しても同様に形成することができる。さらに、3～100 % の水素を含む雰囲気中で、300～450 で 1～12 時間の熱アニールを行い、島状半導体層を水素化する工程を行った。この工程は熱的に励起された水素により島状半導体層にある  $10^{16} \sim 10^{18}/\text{cm}^3$  のダンギングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化（プラズマにより励起された水素を用いる）を行っても良い。

#### 【0101】

結晶化の工程においてシリコンの結晶化を助長する触媒元素を使用し、その後実施形態 3 で説明したゲッタリングの工程を行わない場合、島状半導体層中には微量 ( $1 \times 10^{17} \sim 1 \times 10^{19} \text{ atoms/cm}^3$  程度) の触媒元素が残留する。勿論、そのような状態でも TFT を完成させることができるとともに、触媒元素を少なくともチャネル形成領域から除去する方がより好ましかった。この触媒元素を除去する手段の一つにリン (P) によるゲッタリング作用を利用する手段があった。ゲッタリングに必要なリン (P) の濃度は図 10 (B) で形成した不純物領域 ( $n^+$ ) と同程度であれば良く、ここで実施される活性化工程の熱アニールにより、n チャネル型 TFT および p チャネル型 TFT のチャネル形成領域から触媒元素を不純物領域 240～244 に偏析させゲッタリングをすることができた。その結果不純物領域 240～244 には  $1 \times 10^{17} \sim 1 \times 10^{19} \text{ atoms/cm}^3$  程度の触媒元素が偏析する（図 11 (D)）。

#### 【0102】

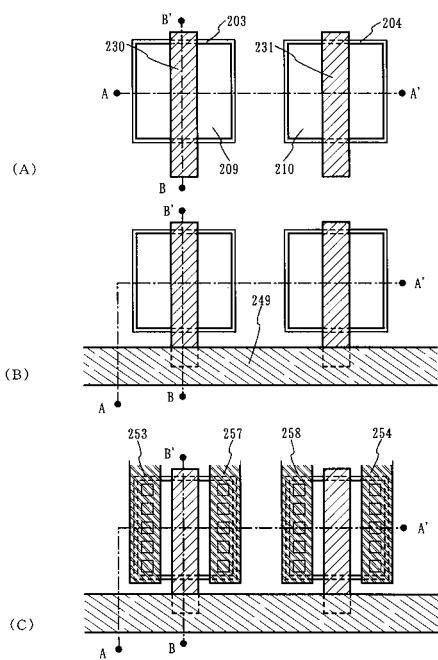

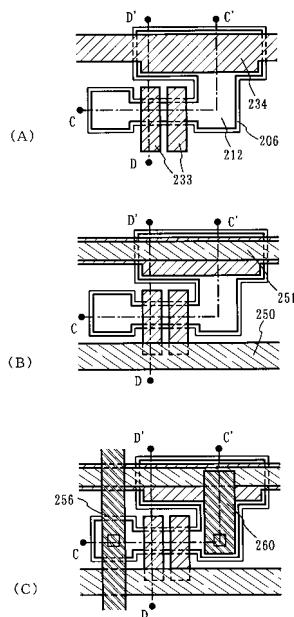

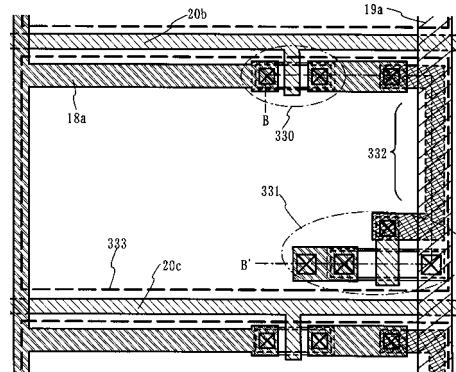

図 14 (A) および図 15 (A) は、図 11 (D) における TFT の上面図であり、A-A' 断面および C-C' 断面は図 11 (D) の A-A' および C-C' に対応している。また、B-B' 断面および D-D' 断面は図 16 (A) および図 17 (A) の断面図に対応している。図 14 および図 15 の上面図はゲート絶縁膜を省略しているが、ここまで工程で、第 2 の絶縁層 203、204、206 上に形成された島状半導体層 209、210、212 上にゲート電極 230、231、233 と容量配線 234 が図に示すように形成される。

#### 【0103】

活性化および水素化の工程が終了したら、ゲート配線とする第 2 の導電層を形成する。この第 2 の導電層は低抵抗材料であるアルミニウム (Al) や銅 (Cu) を主成分とする導電層 (D) で形成する。いずれにしても、第 2 の導電層の抵抗率は  $0.1 \sim 10 \mu \Omega \text{ cm}$  程度とする。さらに、チタン (Ti) やタンタル (Ta)、タンゲステン (W)、モリブデン (Mo) から成る導電層 (E) を積層形成すると良い。本実施例では、チタン (Ti) を  $0.1 \sim 2$  重量 % 含むアルミニウム (Al) 膜を導電層 (D) 247 とし、チタン (Ti) 膜を導電層 (E) 248 として形成した。導電層 (D) 247 は  $200 \sim 400 \text{ nm}$  (好ましくは  $250 \sim 350 \text{ nm}$ ) とすれば良く、導電層 (E) 248 は  $50 \sim 200$  (好ましくは  $100 \sim 150 \text{ nm}$ ) で形成すれば良い（図 12 (A)）。

#### 【0104】

そして、ゲート電極に接続するゲート配線を形成するために導電層 (E) 248 と導電層 (D) 247 をエッチング処理して、ゲート配線 249、250 と容量配線 251 を形成した。エッチング処理は最初に SiCl<sub>4</sub> と Cl<sub>2</sub> と BC<sub>1.3</sub> の混合ガスを用いたドライエッチング法で導電層 (E) の表面から導電層 (D) の途中まで除去し、その後リン酸系のエッチング溶液によるウェットエッチングで導電層 (D) を除去することにより、下地との選択加工性を保ってゲート配線を形成することができる。

#### 【0105】

図 14 (B) および図 15 (B) はこの状態の上面図を示し、A-A' 断面および C-C'

10

20

30

40

50

断面は図12( B )のA - A'およびC - C'に対応している。また、B - B'断面およびD - D'断面は図16( B )および図17( B )のB - B'およびD - D'に対応している。図14( B )および図15( B )において、ゲート配線249、250の一部は、ゲート電極230、231、233の一部と重なり電気的に接触している。この様子はB - B'断面およびD - D'断面に対応した図16( B )および図17( B )の断面構造図からも明らかで、第1の導電層を形成する導電層( C )と第2の導電層を形成する導電層( D )とが電気的に接触している。

#### 【 0 1 0 6 】

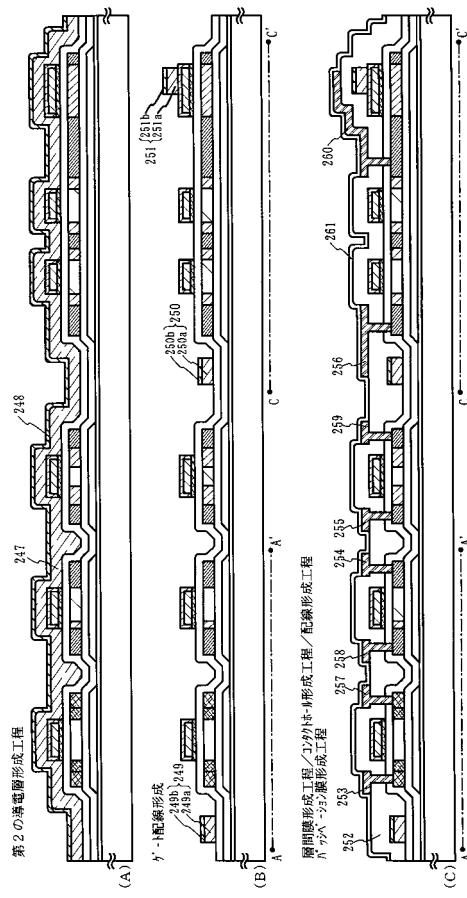

第1の層間絶縁膜252は500～1500nmの厚さで酸化シリコン膜または酸化窒化シリコン膜で形成する。本実施例では、SiH<sub>4</sub>を27SCCM、N<sub>2</sub>Oを900SCCM、として反応圧力160Pa、基板温度325で放電電力密度0.15W/cm<sup>2</sup>で形成する。その後、それぞれの島状半導体層に形成されたソース領域またはドレイン領域に達するコンタクトホールを形成し、ソース配線253～256と、ドレイン配線257～260を形成する。図示していないが、本実施例ではこの電極を、Ti膜を100nm、Tiを含むアルミニウム膜300nm、Ti膜150nmをスパッタ法で連続して形成した3層構造の積層膜とした。

#### 【 0 1 0 7 】

次に、パッシベーション膜261として、窒化シリコン膜、酸化シリコン膜、または酸化窒化シリコン膜を50～500nm(代表的には100～300nm)の厚さで形成する。この状態で水素化処理を行うと TFT の特性向上に対して好ましい結果が得られた。例えば、3～100%の水素を含む雰囲気中で、300～450で1～12時間の熱処理を行うと良く、あるいはプラズマ水素化法を用いても同様の効果が得られた。また、このような熱処理により第1の層間絶縁膜252に存在する水素を島状半導体層209、210b～212bに拡散させ水素化することもできる。いずれにしても、島状半導体層107、108b中の欠陥密度を10<sup>16</sup>/cm<sup>3</sup>以下とすることが望ましく、そのために水素を0.01～0.1 atomic%程度付与すれば良かった(図12( C ))。なお、ここで後に画素電極とドレイン配線を接続するためのコンタクトホールを形成する位置において、パッシベーション膜261に開口部を形成しておいても良い。

#### 【 0 1 0 8 】

図14( C )および図15( C )のはこの状態の上面図を示し、A - A'断面およびC - C'断面は図12( C )のA - A'およびC - C'に対応している。また、B - B'断面およびD - D'断面は図16( C )および図17( C )のB - B'およびD - D'に対応している。図14( C )と図15( C )では第1の層間絶縁膜を省略して示すが、島状半導体層209、210、212の図示されていないソースおよびドレイン領域にソース配線253、254、256とドレイン配線257、258、260が第1の層間絶縁膜に形成されたコンタクトホールを介して接続している。

#### 【 0 1 0 9 】

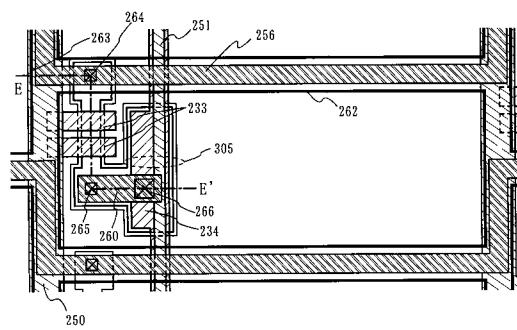

その後、有機樹脂からなる第2の層間絶縁膜262を1.0～1.5μmの厚さに形成する。有機樹脂としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。ここでは、基板に塗布後、熱重合するタイプのポリイミドを用い、300で焼成して形成する。そして、第2の層間絶縁膜262にドレイン配線260に達するコンタクトホールを形成し、画素電極263、264を形成する。画素電極は、透過型液晶表示装置とする場合には透明導電膜を用いれば良く、反射型の液晶表示装置とする場合には金属膜を用いれば良い。本実施例では透過型の液晶表示装置とするために、酸化インジウム・スズ(ITO)膜を100nmの厚さにスパッタ法で形成する(図13)。

#### 【 0 1 1 0 】

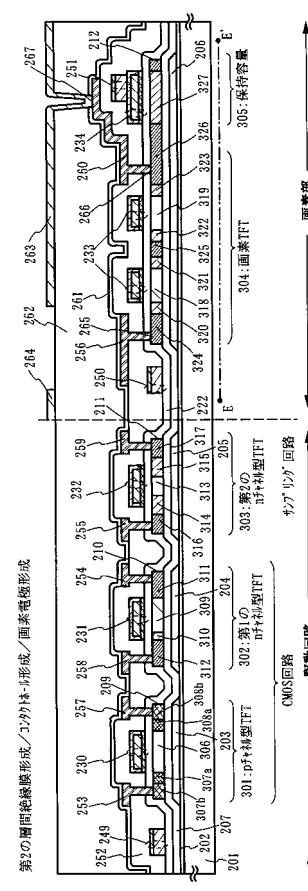

こうして同一基板上に、駆動回路のTFTと画素部の画素TFTとを有した基板を完成させることができた。駆動回路にはpチャネル型TFT301、第1のnチャネル型TFT302、第2のnチャネル型TFT303、画素部には画素TFT304、保持容量30

10

20

30

40

50

5が形成した。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

#### 【0111】

駆動回路のpチャネル型TFT301には、島状半導体層209にチャネル形成領域306、ソース領域307a、307b、ドレイン領域308a、308bを有している。第1のnチャネル型TFT302には、島状半導体層210にチャネル形成領域309、ゲート電極231と重なるLDD領域(Lov)310、ソース領域311、ドレイン領域312を有している。このLov領域のチャネル長方向の長さは0.5~3.0μm、好ましくは1.0~1.5μmとした。第2のnチャネル型TFT303には、島状半導体層211にチャネル形成領域313、Lov領域とLoff領域(ゲート電極と重ならないLDD領域であり、以降Loff領域と記す)とが形成され、このLoff領域のチャネル長方向の長さは0.3~2.0μm、好ましくは0.5~1.5μmである。画素TFT304には、島状半導体層212にチャネル形成領域318、319、Loff領域320~323、ソースまたはドレイン領域324~326を有している。Loff領域のチャネル長方向の長さは0.5~3.0μm、好ましくは1.5~2.5μmである。さらに、容量配線234、251と、ゲート絶縁膜と同じ材料から成る絶縁膜と、画素TFT304のドレイン領域326に接続し、n型を付与する不純物元素が添加された半導体層327とから保持容量305が形成されている。図12では画素TFT304をダブルゲート構造としたが、シングルゲート構造でも良いし、複数のゲート電極を設けたマルチゲート構造としても差し支えない。

#### 【0112】

以上の様な構成は、画素TFTおよび駆動回路が要求する仕様に応じて各回路を構成するTFTの構造を最適化し、半導体装置の動作性能と信頼性を向上させることを可能としている。さらにゲート電極を耐熱性を有する導電性材料で形成することによりLDD領域やソース領域およびドレイン領域の活性化を容易とし、ゲート配線低抵抗材料で形成することにより、配線抵抗を十分低減できる。従って、表示領域(画面サイズ)が4インチクラス以上の表示装置に適用することができる。そして、下地層を形成する第1の絶縁層203~206上で選択的に形成された単結晶構造を有する結晶質シリコン膜を用いることにより、完成したTFTにおいてnチャネル型TFTでは、S値を0.10V/dec以上0.30V/dec以下、Vthを0.5V以上2.5V以下、電界効果移動度は300cm<sup>2</sup>/V·sec以上を実現することもできる。また、pチャネル型TFTでは、S値を0.10V/dec以上0.30V/dec以下、Vthを-0.5V以上-2.5V以下、電界効果移動度は200cm<sup>2</sup>/V·sec以上を実現することもできる。

#### 【0113】

##### [実施例5]

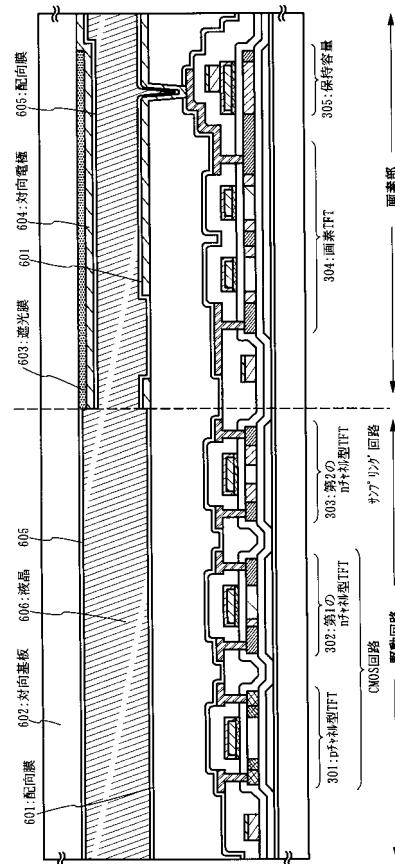

本実施例では、実施例4で作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。図19に示すように、図13の状態のアクティブマトリクス基板に対し、配向膜601を形成する。通常液晶表示素子の配向膜にはポリイミド樹脂が多く用いられている。対向側の対向基板602には、遮光膜603、透明導電膜604および配向膜605を形成した。配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにした。そして、画素部と、CMOS回路が形成されたアクティブマトリクス基板と対向基板とを、公知のセル組み工程によってシール材やスペーサ(共に図示せず)などを介して貼りあわせる。その後、両基板の間に液晶材料606を注入し、封止剤(図示せず)によって完全に封止した。液晶材料には公知の液晶材料を用いれば良い。このようにして図19に示すアクティブマトリクス型液晶表示装置が完成した。

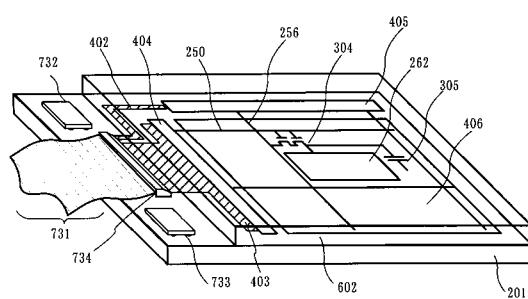

#### 【0114】

次に、このアクティブマトリクス型液晶表示装置の構成を、図20の斜視図および図21の上面図を用いて説明する。尚、図20と図21は、図9~図13と図19の断面構造図と対応付けるため、共通の符号を用いている。また、図21で示すE-E'に沿った断面構造は、図13に示す画素マトリクス回路の断面図に対応している。

**【 0 1 1 5 】**

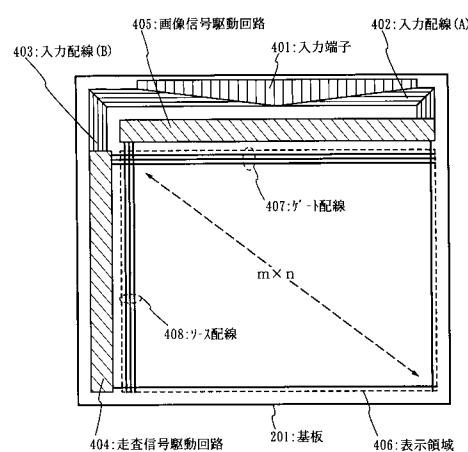

図20においてアクティブマトリクス基板は、ガラス基板201上に形成された、画素部406と、走査信号駆動回路404と、画像信号駆動回路405で構成される。表示領域には画素TFT304が設けられ、周辺に設けられる駆動回路はCMOS回路を基本として構成されている。走査信号駆動回路404と、画像信号駆動回路405はそれぞれゲート配線250とソース配線256で画素TFT304に接続している。また、FPC(Flexible Print Circuit)731が外部入出力端子734に接続され、入力配線402、403でそれぞれの駆動回路に接続している。

**【 0 1 1 6 】**

図21は表示領域406のほぼ一画素分を示す上面図である。ゲート配線250は、図示されていないゲート絶縁膜を介してその下の半導体層212と交差している。図示はしていないが、半導体層には、ソース領域、ドレイン領域、n<sup>-</sup>領域でなるL<sub>off</sub>領域が形成されている。また、265はソース配線256とソース領域324とのコンタクト部、266はドレイン配線260とドレイン領域326とのコンタクト部、267はドレイン配線260と画素電極263のコンタクト部である。保持容量305は、画素TFT304のドレイン領域326から延在する半導体層327とゲート絶縁膜を介して容量配線234、251が重なる領域で形成されている。

**【 0 1 1 7 】**

なお、本実施例のアクティブマトリクス型液晶表示装置は、実施例4で説明した構造と照らし合わせて説明したが、実施例4の構成に限定されるものでなく、実施形態1～3で示した構成を実施例4に応用して完成させたアクティブマトリクス基板を用いても良い。いずれにしても、実施形態1で示した下地層を設けたアクティブマトリクス基板であれば自由に組み合わせてアクティブマトリクス型液晶表示装置を作製することができる。

**【 0 1 1 8 】****[実施例6]**

図18は液晶表示装置の入出力端子、表示領域、駆動回路の配置の一例を示す図である。画素部406にはm本のゲート配線とn本のソース配線がマトリクス状に交差している。例えば、画素密度がVGAの場合、480本のゲート配線と640本のソース配線が形成され、XGAの場合には768本のゲート配線と1024本のソース配線が形成される。表示領域の画面サイズは、13インチクラスの場合対角線の長さは340mmとなり、18インチクラスの場合には460mmとなる。このような液晶表示装置を実現するには、ゲート配線を実施例3で示したような低抵抗材料で形成する必要がある。ゲート配線の時定数(抵抗×容量)が大きくなると走査信号の応答速度が遅くなり、液晶を高速で駆動できなくなる。例えば、ゲート配線を形成する材料の比抵抗が100μcmである場合には6インチクラスの画面サイズがほぼ限界となるが、3μcmである場合には27インチクラスの画面サイズまで対応できる。

**【 0 1 1 9 】**

表示領域406の周辺には走査信号駆動回路404と画像信号駆動回路405が設けられている。これらの駆動回路のゲート配線の長さも表示領域の画面サイズの大型化と共に必然的に長くなるので、大画面を実現するためには実施例4で示したようなアルミニウム(A1)や銅(Cu)などの低抵抗材料でゲート配線を形成することが好ましい。また、本発明は入力端子401から各駆動回路までを接続する入力配線402、403をゲート配線と同じ材料で形成することができ、配線抵抗の低抵抗化に寄与することができる。

**【 0 1 2 0 】**

一方、表示領域の画面サイズが0.9インチクラスの場合には、対角線の長さが24mm程度となり、TFTをサブミクロルールで作製すると周辺に設ける駆動回路を含めても30×30mm<sup>2</sup>以内に収まる。このような場合には、実施例4で示したような低抵抗材料でゲート配線を形成することは必ずしも必要でなく、TaやWなどのゲート電極を形成する材料と同じ材料でゲート配線を形成することも可能である。

**【 0 1 2 1 】**

10

20

30

40

50

このような構成の液晶表示装置は、実施形態1～3で示した結晶化の方法を実施例4に応用して完成させたアクティブマトリクス基板を用いて完成させることができる。いずれにしても、実施形態1～3で示した結晶化技術により完成したアクティブマトリクス基板であれば自由に組み合わせてアクティブマトリクス型液晶表示装置を作製することができる。

#### 【0122】

##### [実施例7]

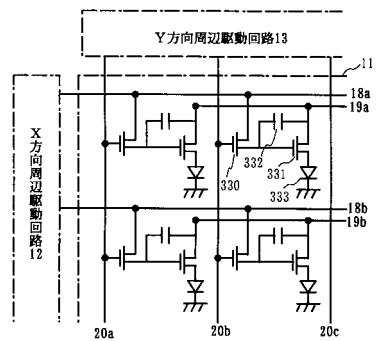

本実施例では、本発明をアクティブマトリクス型有機EL表示装置（有機EL）材料を用いた表示装置（有機EL表示装置）に適用した例を図24で説明する。図24（A）はアクティブマトリクス型有機EL表示装置の回路図を示す。この有機EL表示装置は、基板上に設けられた表示領域11、X方向周辺駆動回路12、Y方向周辺駆動回路13から成る。この表示領域11は、スイッチ用TFT330、保持容量332、電流制御用TFT331、有機EL素子333、X方向信号線18a、18b、電源線19a、19b、Y方向信号線20a、20b、20cなどにより構成される。

10

#### 【0123】

図24（B）はほぼ一画素分の上面図を示している。スイッチ用TFT330は図13に示すpチャネル型TFT301と同様にして形成し、電流制御用TFT331はnチャネル型TFT303と同様にして形成すると良い。

#### 【0124】

ところで、TFTの上方に向かって光を発光させる動作モードの有機EL表示装置の場合、画素電極をA1などの反射性の電極で形成することになる。ここでは、有機EL表示装置の画素領域の構成について示したが、実施例1と同様に画素領域の周辺に駆動回路を設けた周辺回路一体型のアクティブマトリクス型表示装置とすることもできる。そして、図示しないがカラーフィルターを設ければカラー表示をすることも可能である。いずれにしても、実施形態1で示した下地層を設けたアクティブマトリクス基板であれば自由に組み合わせてアクティブマトリクス型有機EL表示装置を作製することができる。

20

#### 【0125】

##### [実施例8]

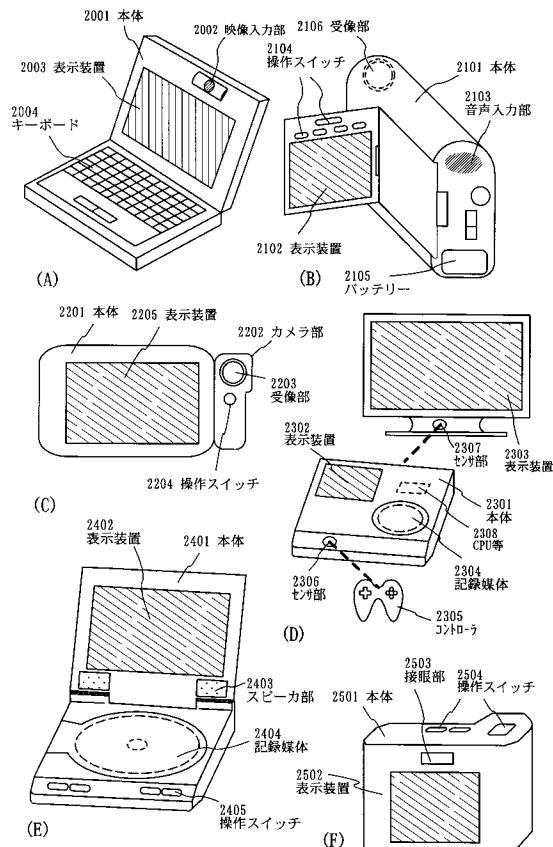

本発明を実施して作製されたアクティブマトリクス基板および液晶表示装置並びにEL型表示装置は様々な電気光学装置に用いることができる。そして、そのような電気光学装置を表示媒体として組み込んだ電子機器全てに本発明を適用することができる。電子機器としては、パーソナルコンピュータ、デジタルカメラ、ビデオカメラ、携帯情報端末（モバイルコンピュータ、携帯電話、電子書籍など）、ナビゲーションシステムなどが上げられる。それらの一例を図25に示す。

30

#### 【0126】

図25（A）はパーソナルコンピュータであり、マイクロプロセッサやメモリーなどを備えた本体2001、画像入力部2002、表示装置2003、キーボード2004で構成される。本発明のレーザーアニール法で作製される結晶質半導体膜を用いて作製されるTFTは、表示装置2003やその他の信号処理回路を形成することができる。

#### 【0127】

40

図25（B）はビデオカメラであり、本体2101、表示装置2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本発明のレーザーアニール法で作製される結晶質半導体膜を用いて作製されるTFTは、表示装置2102やその他の信号制御回路に適用することができる。

#### 【0128】

図25（C）は携帯情報端末であり、本体2201、画像入力部2202、受像部2203、操作スイッチ2204、表示装置2205で構成される。本発明のレーザーアニール法で作製される結晶質半導体膜を用いて作製されるTFTは、表示装置2205やその他の信号制御回路に適用することができる。

#### 【0129】

50

図25(D)はテレビゲームまたはビデオゲームなどの電子遊技機器であり、CPU等の電子回路2308、記録媒体2304などが搭載された本体2301、コントローラ2305、表示装置2303、本体2301に組み込まれた表示装置2302で構成される。表示装置2303と本体2301に組み込まれた表示装置2302とは、同じ情報を表示しても良いし、前者を主表示装置とし、後者を副表示装置として記録媒体2304の情報を表示したり、機器の動作状態を表示したり、或いはタッチセンサーの機能を付加して操作盤とすることもできる。また、本体2301とコントローラ2305と表示装置2303とは、相互に信号を伝達するために有線通信としても良いし、センサ部2306、2307を設けて無線通信または光通信としても良い。本発明のレーザーアニール法で作製される結晶質半導体膜を用いて作製されるTFTは、表示装置2302、2303に適用することができる。表示装置2303は従来のCRTを用いることもできる。10

#### 【0130】

図25(E)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体2401、表示装置2402、スピーカー部2403、記録媒体2404、操作スイッチ2405で構成される。尚、記録媒体にはDVD(Digital Versatile Disc)やコンパクトディスク(CD)などを用い、音楽プログラムの再生や映像表示、ビデオゲーム(またはテレビゲーム)やインターネットを介した情報表示などを行なうことができる。本発明のレーザーアニール法で作製される結晶質半導体膜を用いて作製されるTFTは、表示装置2402やその他の信号制御回路に好適に利用することができる。20

#### 【0131】

図25(F)はデジタルカメラであり、本体2501、表示装置2502、接眼部2503、操作スイッチ2504、受像部(図示しない)で構成される。本発明のレーザーアニール法で作製される結晶質半導体膜を用いて作製されるTFTは、表示装置2502やその他の信号制御回路に適用することができる。

#### 【0132】

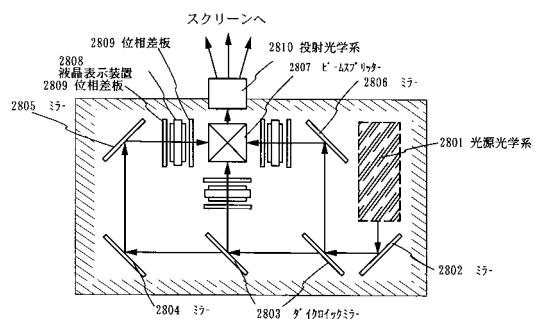

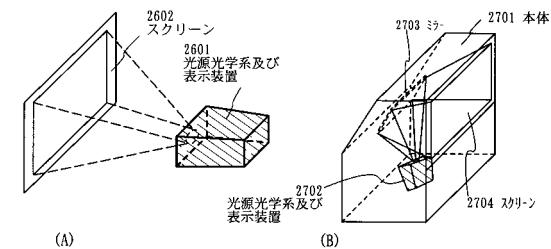

図26(A)はフロント型プロジェクターであり、光源光学系および表示装置2601、スクリーン2602で構成される。本発明は表示装置やその他の信号制御回路に適用することができる。図26(B)はリア型プロジェクターであり、本体2701、光源光学系および表示装置2702、ミラー2703、スクリーン2704で構成される。本発明のレーザーアニール法で作製される結晶質半導体膜を用いて作製されるTFTは、表示装置やその他の信号制御回路に適用することができる。30

#### 【0133】

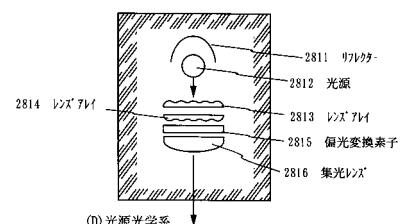

なお、図26(C)に、図26(A)および図26(B)における光源光学系および表示装置2601、2702の構造の一例を示す。光源光学系および表示装置2601、2702は光源光学系2801、ミラー2802、2804~2806、ダイクロイックミラー2803、ビームスプリッター2807、液晶表示装置2808、位相差板2809、投射光学系2810で構成される。投射光学系2810は複数の光学レンズで構成される。図26(C)では液晶表示装置2808を三つ使用する三板式の例を示したが、このような方式に限定されず、単板式の光学系で構成しても良い。また、図26(C)中で矢印で示した光路には適宣光学レンズや偏光機能を有するフィルムや位相を調節するためのフィルムや、IRフィルムなどを設けても良い。また、図26(D)は図26(C)における光源光学系2801の構造の一例を示した図である。本実施例では、光源光学系2801はリフレクター2811、光源2812、レンズアレイ2813、2814、偏光変換素子2815、集光レンズ2816で構成される。尚、図26(D)に示した光源光学系は一例であって図示した構成に限定されるものではない。40

#### 【0134】

また、ここでは図示しなかったが、本発明はその他にも、ナビゲーションシステムやイメージセンサの読み取り回路などに適用することも可能である。このように本願発明の適用範囲はきわめて広く、あらゆる分野の電子機器に適用することが可能である。また、本実施例の電子機器は実施形態1~3の結晶化技術を用い、実施例1~7のどのような組み合50

わせから成る構成を用いても実現することができる。

【0135】

【発明の効果】

本発明の結晶化の技術を用いることにより、結晶粒の位置とその大きさを制御した結晶質半導体膜を作製することができる。このような結晶質半導体膜の結晶粒の位置をTFTのチャネル形成領域に合わせて形成することにより、単一の結晶粒で少なくとも該チャネル形成領域を形成することが可能となり、実質的に単結晶半導体膜で作製したTFTと同等の特性を得ることができる。

【0136】

また、熱伝導層を透光性と絶縁性を有する材料で形成することにより、トップゲート型の TFTにおいてバックチャネル側の寄生容量を無くすことが可能となり、透過型の液晶表示装置をはじめとして、EL型表示装置やイメージセンサなどのさまざまな半導体装置に適用することにより、該半導体装置の高性能化を図ることができる。 10

【図面の簡単な説明】

【図1】本発明の構成を説明する図。

【図2】本発明による結晶質半導体膜の作製工程を示す断面図。

【図3】本発明による結晶質半導体膜を示す断面図。

【図4】本発明による結晶質半導体膜の作製工程を示す断面図。

【図5】TFTの作製工程を示す断面図。

【図6】TFTの作製工程を示す断面図。

【図7】TFTの作製工程を示す上面図。

【図8】下地層の構成を説明する断面図。

【図9】画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図10】画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図11】画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図12】画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図13】画素TFT、駆動回路のTFTの断面図。

【図14】駆動回路のTFTの作製工程を示す上面図。

【図15】画素TFTの作製工程を示す上面図。

【図16】駆動回路のTFTの作製工程を示す断面図。

【図17】画素TFTの作製工程を示す断面図。

【図18】液晶表示装置の入出力端子、配線、回路配置を説明する上面図。

【図19】液晶表示装置の構造を示す断面図。

【図20】液晶表示装置の構造を示す斜視図。

【図21】画素部の画素を示す上面図。

【図22】レーザーラニール装置の構成を示す図。

【図23】レーザーラニール装置の反応室の構成を示す図。

【図24】アクティブマトリクス型EL表示装置の構成を示す図。

【図25】半導体装置の一例を示す図。

【図26】投影型液晶表示装置の構成を示す図。

【図27】TFTの作製工程を示す断面図。

【図28】TFTの作製工程を示す断面図。

10

20

30

40

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

201 : 基板

402 : 画素部

403 : 入力配線

404 : 走査信号駆動回路

405 : 画像信号駆動回路

731 : FPC

732, 733 : ICチップ

734 : 外部入出力端子

304 : 画素TFT

250 : Y'-配線

256 : Y-X配線

262 : 画素電極

305 : 保持容量

602 : 対向基板

【図22】

【図21】

【図23】

【図24】

(A) ELパネル回路図

11:表示領域 12:X方向周辺駆動回路 13:Y方向周辺駆動回路

330:メモリ用IFT 331:電流制御用IFT 332:保持容量 333:有機EL素子

18a,18b:X方向信号線 19a,19b,19c:電源線 20a,20b,20c:Y方向信号線

(B) ELパネル画素部上面図

【図25】

【図26】

(C)光源光学系及び表示装置(三板式)

(D)光源光学系

【図27】

【図28】

---

フロントページの続き

(56)参考文献 特開昭63-031108(JP,A)

特開平07-249779(JP,A)

特開平09-162410(JP,A)

特開平05-206468(JP,A)

特開平03-050720(JP,A)

特開昭62-181419(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/20

H01L 21/336

H01L 29/786