(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4034137号

(P4034137)

(45) 発行日 平成20年1月16日(2008.1.16)

(24) 登録日 平成19年11月2日(2007.11.2)

(51) Int.C1.

F 1

|                |              |                  |         |       |         |

|----------------|--------------|------------------|---------|-------|---------|

| <b>G 1 1 C</b> | <b>19/00</b> | <b>(2006.01)</b> | G 1 1 C | 19/00 | J       |

| <b>G 1 1 C</b> | <b>19/28</b> | <b>(2006.01)</b> | G 1 1 C | 19/28 | B       |

| <b>G 0 2 F</b> | <b>1/133</b> | <b>(2006.01)</b> | G 0 2 F | 1/133 | 5 5 O   |

| <b>G 0 9 G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G 0 9 G | 3/20  | 6 2 2 E |

| <b>G 0 9 G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G 0 9 G | 3/20  | 6 2 3 H |

請求項の数 5 (全 34 頁) 最終頁に続く

(21) 出願番号

特願2002-205961 (P2002-205961)

(22) 出願日

平成14年7月15日 (2002.7.15)

(65) 公開番号

特開2003-141893 (P2003-141893A)

(43) 公開日

平成15年5月16日 (2003.5.16)

審査請求日 平成16年9月30日 (2004.9.30)

(31) 優先権主張番号

特願2001-216040 (P2001-216040)

(32) 優先日

平成13年7月16日 (2001.7.16)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 納 光明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 堀江 義隆

(56) 参考文献 特開平11-134893 (JP, A)

特開平05-216441 (JP, A)

最終頁に続く

(54) 【発明の名称】シフトレジスタ及び表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

r (r は 3 以上の自然数) 個の段を有し、

前記 r 個の段はそれぞれ、クロックパルス及び前記クロックパルスの極性が反転した反転クロックパルスに同期して信号を出力する第 1 のクロックドインバータと第 2 のクロックドインバータとを有し、

前記第 1 のクロックドインバータ及び前記第 2 のクロックドインバータは高電源電位または低電源電位を出力し、

前記第 1 のクロックドインバータの出力端子と前記第 2 のクロックドインバータの出力端子とは接続され、

前記第 1 のクロックドインバータの出力信号の極性を反転させて前記第 2 のクロックドインバータに入力する手段を有し、

第 k (k は 3 以上の自然数) 段の前記第 1 のクロックドインバータにおいて、前記低電源電位に保たれた配線と出力端子とは、第 1 の n チャネル型 TFT 及び前記第 1 の n チャネル型 TFT と直列に接続された第 2 の n チャネル型 TFT を介して接続され、

前記第 1 の n チャネル型 TFT のゲート電極には、第 (k - 1) 段の前記第 1 のクロックドインバータの出力信号の極性を反転させた信号が入力され、

前記第 2 の n チャネル型 TFT のゲート電極は、第 (k - 2) 段の第 1 のクロックドインバータの出力信号が入力されることを特徴とするシフトレジスタ。

## 【請求項 2】

請求項 1 において、

前記クロックパルスの振幅電圧は前記高電源電位と前記低電源電位との電位差よりも小さいことを特徴とするシフトレジスタ。

**【請求項 3】**

請求項 1 または請求項 2 において、

前記シフトレジスタを用いた駆動回路を有することを特徴とする表示装置。

**【請求項 4】**

請求項 1 または請求項 2 において、

前記シフトレジスタを用いた駆動回路と、

単結晶 I C 基板上に形成されたパルス信号制御回路を有し、

10

前記シフトレジスタは絶縁面を有する基板上に形成され、

前記パルス信号制御回路は前記クロックパルスを前記シフトレジスタへ出力することを特徴とする表示装置。

**【請求項 5】**

請求項 1 または請求項 2 において、

前記シフトレジスタを用いた駆動回路を有することを特徴とする携帯情報端末、パーソナルコンピュータ、画像再生装置、テレビ、ヘッドマウントディスプレイまたはカメラ。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

20

本発明は、シフトレジスタに関する。特に、薄膜トランジスタ（以下、TFTと表記する）を用いて構成されたシフトレジスタ及びその駆動方法に関する。

**【0002】**

**【従来の技術】**

クロックパルス及びスタートパルスを入力することで、順次、パルス（サンプリングパルス）を出力するシフトレジスタは、様々な回路に用いられている。中でも、マトリクス状に配置された複数の画素を有する表示装置において、シフトレジスタは、各画素を選択し、また選択された画素に信号を入力する、ソース信号線駆動回路やゲート信号線駆動回路として用いられている。

**【0003】**

30

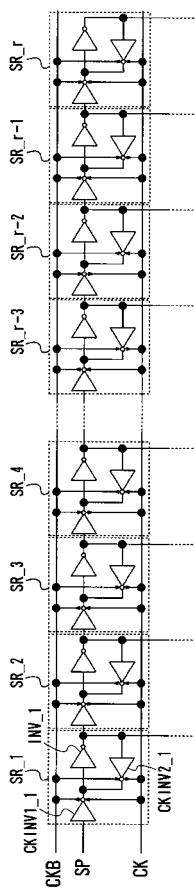

ここで、一般のシフトレジスタの構造の例を、図5に示す。シフトレジスタは、第1段～第r（rは、3以上の自然数）段を有している。それぞれの段は、第1のクロックドインバータCKINV1と、第2のクロックドインバータCKINV2と、インバータINVとによって構成されてる。

**【0004】**

一般に、第i（iは、r以下の自然数）段をSR\_iと表記する。第i段を構成する第1のクロックドインバータ、第2のクロックドインバータ及びインバータをCKINV1\_i、CKINV2\_i、INV\_iと表記する。

**【0005】**

第1段SR\_1において、第1のクロックドインバータCKINV1\_1の入力端子には、外部からスタートパルスSPが入力されており、第1のクロックドインバータCKINV1\_1の出力端子は、インバータINV\_1の入力端子、及び第2のクロックドインバータCKINV2\_1の出力端子に接続されている。第2のクロックドインバータCKINV2\_1の入力端子は、インバータINV\_1の出力端子に接続されている。インバータINV\_1の出力端子が第1段SR\_1の出力端子に相当する。

**【0006】**

第2段SR\_2において、第1のクロックドインバータCKINV1\_2の入力端子は、第1段SR\_1のインバータINV\_1の出力端子に接続され、第1のクロックドインバータCKINV1\_2の出力端子は、インバータINV\_2の入力端子、及び第2のクロックドインバータCKINV2\_2の出力端子に接続されている。第2のクロックドイン

40

50

バーチカルインバータの入力端子は、インバータの出力端子に接続されている。インバータの出力端子が、第2段の出力端子に相当する。

【0007】

一般に、第j (jは、2以上r以下の自然数)段において、第1のクロックドインバータCKINV1\_jの入力端子は、第j-1段SR\_j-1のインバータINV\_j-1の出力端子に接続されている。第1のクロックドインバータCKINV1\_jの出力端子は、インバータINV\_jの入力端子、及び第2のクロックドインバータCKINV2\_jの出力端子に接続されている。第2のクロックドインバータCKINV2\_jの入力端子は、インバータINV\_jの出力端子に接続されている。インバータINV\_jの出力端子が、第j段の出力端子に相当する。

10

【0008】

上記接続の第1段の回路SR\_1～第r段の回路SR\_rによって構成されるシフトレジスタは、第1段にスタートパルスSPが入力されると、それぞれの段が有する第1のクロックドインバータCKINV1及び第2のクロックドインバータCKINV2それぞれに入力される、クロックパルスCK及びその極性が反転した反転クロックパルスCKBに同期して、第1段SR\_1～第r段の回路SR\_rそれぞれの出力端子から、順にシフトしたパルスS\_1～S\_rが出力される。

【0009】

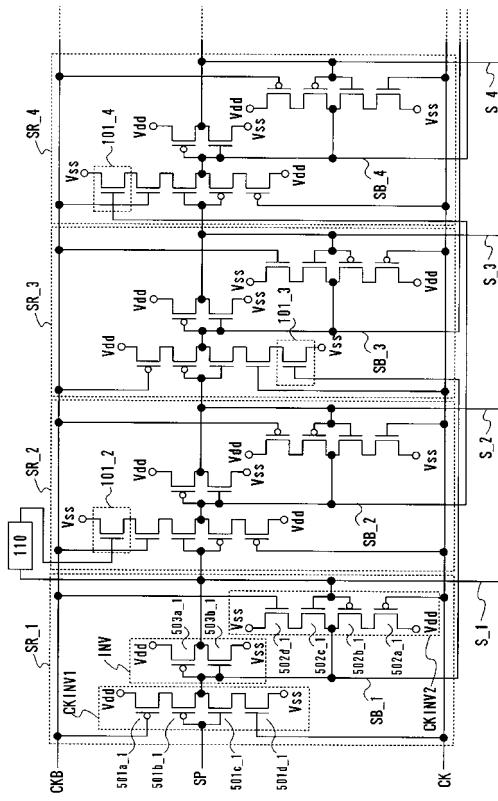

図5で示した構成のシフトレジスタにおいて、各段を構成する第1のクロックドインバータCKINV1、第2のクロックドインバータCKINV2及びインバータINVの詳細な回路図の例を図4に示す。

20

【0010】

Vddは高電源電位であり、Vssは低電源電位であるとする。ここで、高電源電位Vddの電位は、低電源電位Vssの電位より高いとする。高電源電位Vddと低電源電位Vssの電位差が、シフトレジスタの電源電圧に相当する。

【0011】

第1のクロックドインバータCKINV1は、pチャネル型TFT501a及び501bと、nチャネル型TFT501d及び501cによって構成されている。本明細書中では、第1のクロックドインバータCKINV1において、そのゲート電極に、クロックパルスCKもしくは反転クロックパルスCKBが入力されるpチャネル型TFT、nチャネル型TFTをそれぞれ、501a、501dとする。また、pチャネル型TFT501b及びnチャネル型TFT501cのゲート電極は、第1のクロックドインバータCKINV1の入力端子に接続されているものとする。

30

【0012】

ここで、pチャネル型TFT501aのゲート電極にクロックパルスCKが入力される場合、nチャネル型TFT501dのゲート電極に、反転クロックパルスCKBが入力される。一方、pチャネル型TFT501aのゲート電極に、反転クロックパルスCKBが入力される場合、nチャネル型TFT501dのゲート電極に、クロックパルスCKが入力される。

【0013】

pチャネル型TFT501aのソース電極は、高電源電位Vddに保たれ、ドレイン電極は、pチャネル型TFT501bのソース電極に接続されている。pチャネル型TFT501bのドレイン電極は、nチャネル型TFT501cのドレイン電極に接続され、nチャネル型TFT501cのソース電極は、nチャネル型TFT501dのドレイン電極に接続されている。nチャネル型TFT501dのソース電極は、低電源電位Vssに保たれている。pチャネル型TFT501b及びnチャネル型TFT501cのゲート電極が、第1のクロックドインバータCKINV1の入力端子となり、pチャネル型TFT501b及びnチャネル型TFT501cのドレイン電極が、第1のクロックドインバータCKINV1の出力端子となっている。

40

【0014】

50

第2のクロックドインバータCKINV2は、pチャネル型TFT502a及び502bと、nチャネル型TFT502d及び502cとによって構成されている。本明細書中では、第2のクロックドインバータCKINV2において、そのゲート電極に、クロックパルスCKもしくは反転クロックパルスCKBが入力されているpチャネル型TFT、nチャネル型TFTをそれぞれ、502a、502dとする。また、pチャネル型TFT502b及びnチャネル型TFT502cのゲート電極が、インバータINVの出力端子に接続されているものとする。

【0015】

ここで、各段において、第1のクロックドインバータCKINV1を構成するpチャネル型TFT501aのゲート電極に、クロックパルスCKが入力される場合、第2のクロックドインバータCKINV2を構成するpチャネル型TFT502aのゲート電極に、反転クロックパルスCKBが入力され、nチャネル型TFT502dのゲート電極に、クロックパルスCKが入力される。一方、各段において、第1のクロックドインバータCKINV1を構成するpチャネル型TFT501aのゲート電極に、反転クロックパルスCKBが入力される場合、第2のクロックドインバータCKINV2を構成するpチャネル型TFT502aのゲート電極に、クロックパルスCKが入力され、nチャネル型TFT502dのゲート電極に、反転クロックパルスCKBが入力される。

10

【0016】

pチャネル型TFT502aのソース電極は、高電源電位Vddに保たれており、ドレン電極は、pチャネル型TFT502bのソース電極に接続されている。pチャネル型TFT502bのドレン電極は、nチャネル型TFT502cのドレン電極に接続され、nチャネル型TFT502cのソース電極は、nチャネル型TFT502dのドレン電極に接続されている。nチャネル型TFT502dのソース電極は、低電源電位Vssに保たれている。pチャネル型TFT502b及びnチャネル型TFT502cのドレン電極が、第2のクロックドインバータCKINV2の出力端子となっている。

20

【0017】

インバータINVは、pチャネル型TFT503aとnチャネル型TFT503bによって構成されている。pチャネル型TFT503aのソース電極は、高電源電位Vddに保たれ、pチャネル型TFT503aのドレン電極は、nチャネル型TFT503bのドレン電極に接続されている。nチャネル型TFT503bのソース電極は、低電源電位Vssに保たれている。pチャネル型TFT503a及びnチャネル型TFT503bのゲート電極が、インバータINVの入力端子となり、pチャネル型TFT503a及びnチャネル型TFT503bのドレン電極が、インバータINVの出力端子となる。

30

【0018】

第i(iは、自然数)段の第1のクロックドインバータCKINV1\_iが有するpチャネル型TFT501a\_iのゲート電極に、クロックパルスCKが入力されている場合、第(i-1)段の第1のクロックドインバータCKINV1\_i-1が有するpチャネル型TFT501a\_i-1のゲート電極には、反転クロックパルスCKBが入力されている。

40

【0019】

一般に、第i(iは、自然数)段の第1のクロックドインバータCKINV1\_iを構成するpチャネル型TFT501a、501bをそれぞれ、501a\_i、501b\_iと表記し、nチャネル型TFT501c、501dをそれぞれ501c\_i、501d\_iと表記する。同様に、第i段の第2のクロックドインバータCKINV2\_iを構成するpチャネル型TFT502a、502bをそれぞれ、502a\_i、502b\_iと表記し、nチャネル型TFT502c、502dをそれぞれ、502c\_i、502d\_iと表記する。また、第i段のインバータINV\_iを構成するnチャネル型TFT503a、pチャネル型TFT503bをそれぞれ、503a\_i、503b\_iと表記する。

【0020】

図7に、図4及び図5に示した構成のシフトレジスタの理想的な駆動方法を示すタイミン

50

グチャートを示し、その具体的な動作について以下に説明する。

【0021】

シフトレジスタには、クロックパルスCK及びクロックパルスの極性が反転した反転クロックパルスCKB、スタートパルスSPが入力される。第1段SR\_1の第1のクロックドインバータCKINV1\_1において、pチャネル型TFT501a\_1のゲート電極には、反転クロックパルスCKBが入力され、nチャネル型TFT501d\_1のゲート電極には、クロックパルスCKが入力されている。第1のクロックドインバータCKINV1\_1のpチャネル型TFT501b\_1及びnチャネル型TFT501c\_1のゲート電極に、スタートパルスSPが入力される。

【0022】

スタートパルスSPと、クロックパルスCK及び、反転クロックパルスCKBの関係は、図7のタイミングチャートに示した通りである。

【0023】

その入力端子にスタートパルスSPが入力された、つまりスタートパルスSPによって「Hi」の電位が入力され、クロックパルスCK及び反転クロックパルスCKBが入力された第1段SR\_1の第1のクロックドインバータCKINV1\_1において、nチャネル型TFT501c\_1及び501d\_1がオンの状態となる。こうして、第1のクロックドインバータCKINV1の出力端子は、低電源電位Vssの電位となる。すなわち、第1段の第1のクロックドインバータCKINV1\_1の出力SB\_1は、「Lo」の電位となる。このとき、同じ段の第2のクロックドインバータCKINV2\_1のpチャネル型TFT502a\_1及びnチャネル型TFT502d\_1は、そのゲート電極に入力されたクロックパルスCK及び反転クロックパルスCKBによって、オフの状態にある。

【0024】

一方、第2段の第1のクロックドインバータCKINV1\_2のpチャネル型TFT501a\_2及びnチャネル型TFT501d\_2は、それらのゲート電極に入力されているクロックパルスCK及び反転クロックパルスCKBによって、どちらもオフの状態となっている。

【0025】

また、第2のクロックドインバータCKINV2\_2のpチャネル型TFT502a\_2及びnチャネル型TFT502d\_2は、それらのゲート電極に入力されているクロックパルスCK及び反転クロックパルスCKBによって、どちらもオンの状態であり、且つ、第2のクロックドインバータCKINV2\_2の入力端子に、「Lo」の電位が入力されているため、第2のクロックドインバータCKINV2\_2の出力端子は、高電源電位Vddが出力される。すなわち、「Hi」の電位が出力される。

【0026】

次に、クロックパルスCK及び反転クロックパルスCKBによって、第1段SR\_1の第1のクロックドインバータCKINV1\_1において、nチャネル型TFT501d\_1がオフの状態に変化する。一方、第2のクロックドインバータCKINV2\_1において、nチャネル型TFT502d\_1がオンの状態となる。

【0027】

また、第2のクロックドインバータCKINV2\_1の入力端子には、第1のクロックドインバータCKINV1\_1の出力SB\_1が、インバータINV\_1を介して入力されている。すなわち、第2のクロックドインバータCKINV2\_1の入力端子には、第1のクロックドインバータCKINV1\_1の出力SB\_1の極性が反転した信号が入力されている。この入力信号により、第2のクロックドインバータCKINV2\_1のnチャネル型TFT502c\_1がオンの状態となる。こうして、第2のクロックドインバータCKINV2\_1の出力端子は、低電源電位Vssとなる。すなわち、第2のクロックドインバータCKINV2\_1の出力SB\_1は、「Lo」の電位となる。

【0028】

一方、第2段の第1のクロックドインバータCKINV1\_2の入力端子に、第1段SR

10

20

30

40

50

—1から「H i」の電位が入力されている。また、クロックパルスCK及び反転クロックパルスCKBにより、nチャネル型TFT501d\_2がオンの状態にある。こうして、第2段の第1のクロックドインバータCKINV1\_2の出力端子は、低電源電位Vssの電位となり、第2段の第1のクロックドインバータの出力SB\_2は、「Lo」の電位となる。

#### 【0029】

再び、クロックパルスCK及び反転クロックパルスCKBによって、第1段の第1のクロックドインバータのpチャネル型TFT501a\_1がオンの状態となる。このとき、スタートパルスSPは入力されていないので、第1のクロックドインバータのpチャネル型TFT501b\_1もオンの状態である。こうして、第1段の第1のクロックドインバータCKINV1\_1の出力端子は、高電源電位Vddの電位となり、第1のクロックドインバータの出力SB\_1は、「Hi」となる。

#### 【0030】

上記の様に、第1のクロックドインバータCKINV1および第2のクロックドインバータCKINV2の出力が変化する。こうして各段の出力Sが、クロックパルスCKの半周期分ずつ順に、入力されたスタートパルスSPからシフトして出力される。こうして、図4で示したシフトレジスタはパルスを出力する。

#### 【0031】

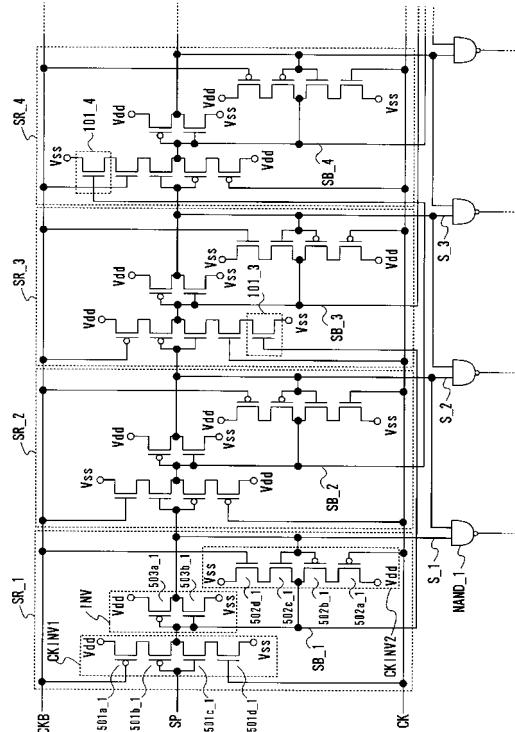

また、図4で示した構成のシフトレジスタに対して、隣り合う段の出力信号SをNAND演算したものを出力パルスとするシフトレジスタの例を図10に示す。図10において、図4と同じ部分は同じ符号を用いて示し、説明は省略する。

#### 【0032】

第(*i*+1)(*i*+1は、r以下の自然数)段の回路SR\_1+iと、第*i*段の回路SR\_1+i、それぞれの出力S\_1+i、S\_1+i+1が、第*i*のNAND回路NAND\_1+iに入力される。この第*i*のNAND回路NAND\_1+iから、第*i*のパルスSMP\_1+iが出力される。このパルスSMP\_1+iが、シフトレジスタの出力パルスとなる。

#### 【0033】

図10で示したシフトレジスタの駆動方法を示すタイミングチャートを、図11に示す。第1段の回路SR\_1から第*r*段の回路SR\_1+rの出力端子から、順にシフトしたパルスS\_1~S\_1+rが出力されるまでの動作は、図7において示した動作と同様である。隣り合う段の出力がそれぞれNAND回路NAND\_1~NAND\_1+r-1に入力され、パルスSMP\_1~SMP\_1+r-1が順に出力される。こうして、図10で示したシフトレジスタはパルスを出力する。

#### 【0034】

図4、図5及び図10で示した構成のシフトレジスタは、回路を構成する素子が少なくてすむので、負荷容量が小さくてすみ、高周波数での動作が比較的容易である。

#### 【0035】

##### 【発明が解決しようとする課題】

シフトレジスタは一般に、電源電圧と、クロックパルス及びスタートパルスの信号の振幅電圧とが、ほぼ等しい状態で動作させる。通常、シフトレジスタの電源電圧は、10V程度に設定されることが多い。

#### 【0036】

ここで、シフトレジスタに入力するクロックパルスやスタートパルス等のパルス信号は、通常、単結晶IC基板上に形成された、パルス信号制御回路によって出力されている。パルス信号制御回路は、通常、振幅電圧が3.3V程度のコントロール信号を出力する。よって、パルス信号発生回路の出力するパルス信号の振幅電圧は、通常は、レベルシフタ等によって、シフトレジスタの電源電圧程度まで大きくして、シフトレジスタに入力される。

#### 【0037】

ここで、仮にレベルシフタ等によって、シフトレジスタに入力されるパルス信号の信号電

10

20

30

40

50

圧を大きくしなかった場合について考える。つまりこれは、図4において、シフトレジスタを構成する素子の電源電圧（高電源電位V<sub>dd</sub>と低電源電位V<sub>ss</sub>の電位差に相当する）、つまりシフトレジスタの電源電位が、スタートパルスSPや、クロックパルスCKの振幅電圧より大きい場合に該当する。

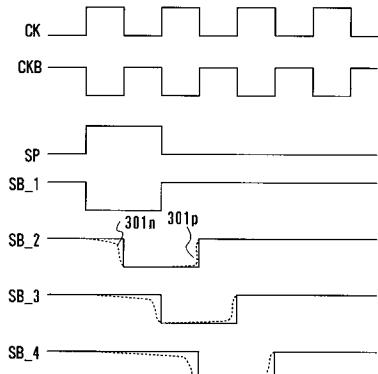

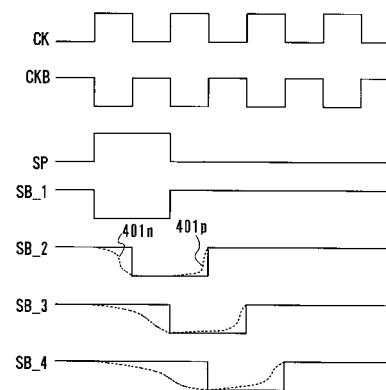

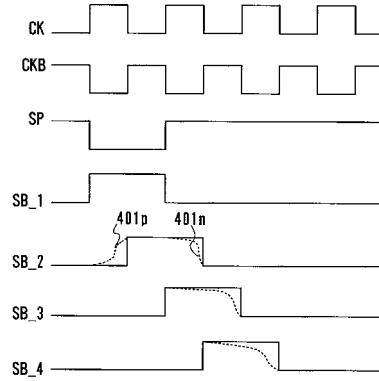

#### 【0038】

このときのシフトレジスタの動作について、図6のタイミングチャートを用いて説明する。また、シフトレジスタの回路構成は、図4を参照する。ここで、説明のため、シフトレジスタの電源電圧を10V（高電源電位V<sub>dd</sub>を10V、低電源電位V<sub>ss</sub>を0V）とし、クロックパルスやスタートパルス等のパルス信号の振幅電圧を3.0Vとする。このとき、パルス信号の「Lo」に対応する電位（最低電位）を3.5V、「Hi」に対応する電位（最高電位）を6.5Vとする。

10

#### 【0039】

第1のクロックドインバータCKINV1に注目する。クロックパルスCK、反転クロックパルスCKBが入力され、pチャネル型TFT501aのゲート電極には、「Hi」に対応する電位、この場合は、6.5Vが入力され、同時に、nチャネル型TFT501dのゲート電極には、「Lo」に対応する電位、この場合は3.5Vが入力されている場合を考える。このとき、理想的には、pチャネル型TFT501a及び、nチャネル型TFT501dは、どちらもオフの状態であることが望まれる。しかし、電源電圧より、クロックパルスCK及び反転クロックパルスCKBの振幅電圧が小さいため次のような問題が生じる。

20

#### 【0040】

pチャネル型TFT501aにおいて、そのソース電極の電位が、そのゲート電極の電位より大きくなる。この例では、pチャネル型TFT501aのソース電極の電位は、高電源電位V<sub>dd</sub>の10Vであり、ゲート電極の電位は、クロックパルスCKまたは反転クロックパルスCKBの「Hi」の電位、6.5Vが入力されており、その電位差は3.5Vである。もし、pチャネル型TFT501aの閾値電圧（pチャネル型TFTにおいて、ソース電極の電位に対するゲート電極の電位を示すものとする）が-3.5V以上であつたら、つまり、pチャネル型TFT501aの閾値電圧の絶対値が、3.5Vより小さい場合、pチャネル型TFT501aはオンの状態となって、そのソース・ドレイン間が導通状態となってしまう。

30

#### 【0041】

同様に、nチャネル型TFT501dにおいて、そのソース電極の電位が、そのゲート電極の電位より小さくなる。この例では、nチャネル型TFT501dのソース電極の電位は、低電源電位V<sub>ss</sub>の0Vであり、ゲート電極の電位は、クロックパルスCKもしくは、反転クロックパルスCKBの「Lo」の電位、3.5Vが入力されており、その電位差は3.5Vである。もし、nチャネル型TFT501dの閾値電圧（nチャネル型TFTにおいて、ソース電極の電位に対するゲート電極の電位を示すものとする）が3.5V以下であつたら、nチャネル型TFT501dはオンの状態となってしまう。

30

#### 【0042】

タイミングチャートにおいて、破線で示した部分は、上記した問題によってオフとなるべきTFTがオンの状態となった場合の動作を示す。

40

#### 【0043】

ここで、第1段SR\_1の第1のクロックドインバータCKINV1\_1においては、その入力端子に、タイミングチャートに示すようにスタートパルスSPが入力されている場合、クロックパルスCK及び反転クロックパルスCKBに同期して、信号SB\_1を出力する。

#### 【0044】

一方、第2段SR\_2の第1のクロックドインバータCKINV1\_2においては、第1段目SR\_1のインバータINV\_1からの出力（図中、S\_1と表記）が入力されている。

50

## 【0045】

第1段 S R \_ 1 から出力されたパルス信号 S \_ 1 が、第2段 S R \_ 2 の第1のクロックドインバータ C K I N V 1 \_ 2 の入力端子に入力されている場合、前述した問題によって、本来オフの状態にあるはずの n チャネル型 T F T 5 0 1 d \_ 2 がオンの状態となると、n チャネル型 T F T 5 0 1 c \_ 2 及び n チャネル型 T F T 5 0 1 d \_ 2 を介して漏れ電流が流れる。この漏れ電流が流れ続ける間に、第1のクロックドインバータ C K I N V 1 \_ 2 の出力電位 S B \_ 2 が、高電源電位 V d d に対して低くなっていく。（図6中、破線 4 0 1 n で示す。）

## 【0046】

一方、第1段 S R \_ 1 から出力されたパルス信号 S \_ 1 が、第2段 S R \_ 2 の第1のクロックドインバータ C K I N V 1 \_ 2 の入力端子に入力されていない場合、前述した問題によって、本来オフの状態にあるはずの p チャネル型 T F T 5 0 1 a \_ 2 がオンの状態となると、p チャネル型 T F T 5 0 1 a \_ 2 及び p チャネル型 T F T 5 0 1 b \_ 2 を介して漏れ電流が流れる。この漏れ電流が流れ続ける間に、第1のクロックドインバータ C K I N V 1 \_ 2 の出力電位 S B \_ 2 が、低電源電位 V s s に対して高くなっていく。（図6中、破線 4 0 1 p で示す。）

## 【0047】

同様に、第3段 S R \_ 3 以降も、その段の有する第1のクロックドインバータ C K I N V 1 の出力電位 S B は、漏れ電流のために、図7のタイミングチャートに示したような理想的な動作をする場合と比較して、変動する。

## 【0048】

上記の様に、本来オフの状態であるはずの p チャネル型 T F T 5 0 1 a 及び n チャネル型 T F T 5 0 1 d が、オンの状態となった場合に、第1のクロックドインバータ C K I N V 1 の入力端子に、パルスが入力されると、n チャネル型 T F T 5 0 1 c 及び 5 0 1 d を介して電流（以下、これを n チャネル型 T F T の漏れ電流と呼ぶ）が流れ、本来出力されるべき出力電位 V d d より低い電位が出力される。

## 【0049】

また、本来オフの状態であるはずの T F T 5 0 1 a 及び T F T 5 0 1 d が、オンの状態となつた場合に、第1のクロックドインバータ C K I N V 1 の入力端子に、パルスが入力されていない場合、5 0 1 a 及び 5 0 1 b を介して電流（以下、これを p チャネル型 T F T の漏れ電流と呼ぶ）が流れ、本来出力されるべき出力電位 V s s より高い電位が出力される。

## 【0050】

上記漏れ電流が大きくなると、出力 S B のパルスがシフトしなくなる。

## 【0051】

このように、本来オフの状態であることを求められる T F T がオンの状態となつてしまつたためにシフトレジスタ内の出力が、正常に行われず、誤作動を起す可能性が高い。

## 【0052】

上記理由による誤作動を配慮して、従来のシフトレジスタでは、クロックパルス C K 、スタートパルス S P 等のパルス信号は、レベルシフタを介して、その振幅電圧をシフトレジスタの電源電圧程度に大きくした後、入力されている。

## 【0053】

ここで、レベルシフタを有するシフトレジスタを用いた駆動回路を備えた表示装置を例に挙げる。この際のレベルシフタは、シフトレジスタを用いた駆動回路と、この駆動回路から出力される信号によって表示を行う画素部とが形成された基板（パネル基板）上や、パネル基板とは別の単結晶 I C 基板上に形成される。

## 【0054】

パネル基板とは別の基板上に、レベルシフタを形成する場合、表示装置内で画素部以外の周辺回路が占める面積が増大する。また、レベルシフタとパネル上の回路の接続部分の配線容量及び配線抵抗が大きくなるため、消費電力が増大する。

10

20

30

40

50

## 【0055】

また、パネル基板上にレベルシフタを形成する場合、次のような問題点がある。クロックパルスCKやスタートパルスSPなどが入力される信号線は、負荷容量が大きい。そのため、レベルシフト後のバッファ出力は、クロックパルスCKやスタートパルスSPなどのパルス信号がなまつて出力され、信号遅延によるタイミングずれを引き起す。また、パルス信号のなまりを防ぐために、バッファの電流供給能力を大きくする必要が生じる。

## 【0056】

このように、パネル基板上にレベルシフタを有するシフトレジスタでは、高周波数で動作が困難、電源線のノイズ、レイアウト面積の増大等の問題が生じる。

## 【0057】

このように、パネル基板上やパネル基板とは別の基板上のレベルシフタ等を用いて、入力するパルス信号の振幅電圧を大きくするシフトレジスタの場合、消費電力の増大、高周波数で動作が困難、電源線のノイズ、レイアウト面積の増大等の問題が生じる。そこで、上記問題を解決するシフトレジスタ及びその駆動方法を提供することを課題とする。

## 【0058】

## 【課題を解決するための手段】

シフトレジスタの電源電圧より小さな振幅電圧を有する、クロックパルス、スタートパルスをシフトレジスタに入力する。これによって、パネル基板外にクロックパルスやスタートパルスの振幅電圧を昇圧するためのレベルシフタを形成し電源電圧程度の振幅電圧を有する様にレベルシフトしたクロックパルスやスタートパルスをパネルに入力する必要がないので、パネル上の回路とレベルシフタの間の配線容量及び配線抵抗による、消費電力の増大の問題を解決することができる。

## 【0059】

また、パネル基板上にクロックパルスやスタートパルスの振幅電圧を昇圧するためのレベルシフタを形成しレベルシフトしたクロックパルスやスタートパルスを信号線に入力する必要がないので、信号線の負荷によるなまりの影響を抑え、シフトレジスタを高周波数で動作させることができるとなる。また、電源線のノイズの影響を抑えることができる。

## 【0060】

加えて、レベルシフタが必要ない分、シフトレジスタのレイアウト面積を縮小することができる。

## 【0061】

こうして、低消費電力・高周波数で動作し、電源線のノイズ、レイアウト面積の増大等の問題を解決するシフトレジスタの駆動方法が提供される。

## 【0062】

上記駆動方法を用いる場合に、シフトレジスタを構成する第2のクロックドインバータの電流能力が高ければ、第1のクロックドインバータにおいて、オフになるべきTFTがオンになってしまふために流れる電流（漏れ電流）によって起こる、第1のクロックドインバータの出力電位の変化を低減することができる。そこで、第2のクロックドインバータを構成するTFTのゲート幅を、大きく設定する。

## 【0063】

ここで従来のシフトレジスタでは、各段において、第2のクロックドインバータCKINV2は、第1のクロックドインバータCKINV1より出力された信号を保持するだけの役割を有する。そのため、第2のクロックドインバータによる負荷を小さくするために、第1のクロックドインバータCKINV1を構成するpチャネル型TFT501a及び501bと、nチャネル型TFT501c及び501dとに対して、第2のクロックドインバータCKINV2を構成するpチャネル型TFT502a及び502bと、nチャネル型TFT502c及び502dとは、それぞれの極性のTFTに関してそのゲート幅を十分に小さくしている多かった。例えば、第1のクロックドインバータを構成するTFTのゲート幅に対して、第2のクロックドインバータを構成するTFTのゲート幅が、1/10程に設定されていた。なお、これらのTFTのゲート長は、すべて同じであると

10

20

30

40

50

する。

【0064】

一方本発明では、シフトレジスタの電源電圧より小さな振幅電圧を有する、クロックパルス、スタートパルスをシフトレジスタに入力するため、漏れ電流が問題となる。そこで、第2のクロックドインバータを構成するTFTのゲート幅を、従来と比較して大きく設定することで漏れ電流を低減する。

【0065】

例えば、シフトレジスタが有する第1のクロックドインバータを構成するnチャネル型TFTのソース電極の電位と、そのゲート電極に入力されるクロックパルスまたは反転クロックパルスの最低電位（「Lo」に対応する電位）の電位差の絶対値が、nチャネル型TFTの閾値電圧の絶対値より大きな場合を考える。本来オフの状態になるはずのnチャネル用TFTがオンになってしまるために流れる電流（漏れ電流）によって起こる、第1のクロックドインバータの出力電位の変化を、第2のクロックドインバータを構成するpチャネル型TFTのゲート幅を大きく設定することによって抑制することができる。

10

【0066】

また、シフトレジスタが有する第1のクロックドインバータを構成するpチャネル型TFTのソース電極の電位と、そのゲート電極に入力されるクロックパルスまたは反転クロックパルスの最高電位（「Hi」に対応する電位）の電位差の絶対値が、pチャネル型TFTの閾値電圧の絶対値より大きな場合を考える。本来オフの状態になるはずのpチャネル用TFTがオンになってしまるために流れる電流（漏れ電流）によって起こる、第1のクロックドインバータの出力電位の変化を、第2のクロックドインバータを構成するnチャネル型TFTのゲート幅を大きく設定することによって抑制することができる。

20

【0067】

また、第1のクロックドインバータに、新たにTFTを追加する。この追加したTFTのソース・ドレイン間を介して、電源電位を第1のクロックドインバータの出力端子に出力する構成とする。追加したTFTのゲート電極には、シフトレジスタの電源電圧程度の振幅電圧を有する信号が入力される。漏れ電流が問題となる場合に、追加したTFTをオフする構成とする。これによって、第1のクロックドインバータを流れる電流（漏れ電流）を遮断する。

【0068】

30

こうして、誤作動を起さないシフトレジスタが提供される。

【0069】

上記構成によって、誤作動を起さず、高周波数で、また、低電源電圧での動作が可能なシフトレジスタ及びその駆動方法が提供される。

【0070】

【発明の実施の形態】

（第1の実施の形態）

第1の実施の形態で説明する、本発明のシフトレジスタは、従来例において図4で示した回路図と同等の回路図によって示すことができる。以下、図4と同じ部分は同じ符号を用い、説明は省略する。

40

【0071】

本発明のシフトレジスタでは、その電源電圧（高電源電位Vddと低電源電位Vssの電位差に相当する）より小さな振幅電圧の、スタートパルスSPや、クロックパルスCKを入力する。

【0072】

このとき、シフトレジスタの各段を構成する第2のクロックドインバータCKINV2が有するpチャネル型TFT502a及び502bのゲート幅は、第1のクロックドインバータが有するpチャネル型TFT501a及び501bのゲート幅の1/2以上に設定する。

【0073】

50

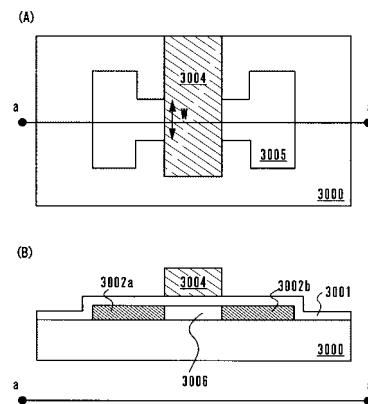

ここで、TFTのゲート幅は、TFTの半導体活性層と重なるゲート電極部分の、キャリアの移動方向に垂直な方向の長さを示すものとする。図26を用いて、ゲート幅Wについて説明する。ここで、図26(A)のa-a'の断面が図26(B)に相当する。3000は絶縁表面を有する基板、3005は半導体活性層、3004はゲート電極、3001はゲート絶縁膜である。半導体活性層3005は、ソース領域及びドレイン領域として機能する領域3002a、3002b、チャネル領域3006を有する。図中ゲート幅をWで示す。

#### 【0074】

また、シフトレジスタの各段を構成する第2のクロックドインバータが有するnチャネル型TFT502c及び502dのゲート幅は、第1のクロックドインバータが有するnチャネル型TFT501c及び501dのゲート幅の1/2以上に設定する。10

#### 【0075】

こうして、各段の回路の有する、第2のクロックドインバータCKINV2の電流能力を高める。これによって、シフトレジスタの電源電圧より小さな振幅電圧の、スタートパルスSPや、クロックパルスCKを入力するシフトレジスタにおいて、第2のクロックドインバータCKINV2の「Hi」の電位(高電源電位Vdd)の出力によって、第1のクロックドインバータCKINV1のnチャネル型TFTの漏れ電流による出力電位SBの変動を抑制することができる。

#### 【0076】

同様に、第2のクロックドインバータCKINV2の「Lo」の電位(低電源電位Vss)の出力によって、第1のクロックドインバータCKINV1のpチャネル型TFTの漏れ電流による出力電位SBの変動を抑制することができる。20

#### 【0077】

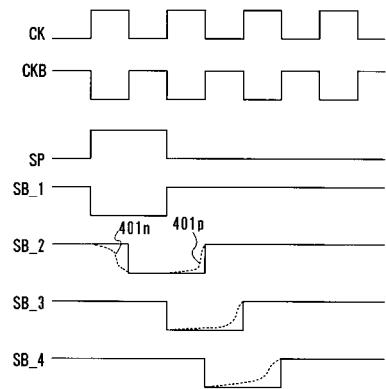

上記構成のシフトレジスタの動作について、図3のタイミングチャートを用いて説明する。破線は、漏れ電流による出力電位SBの変化を示す。図3中破線301nは、第2段の第1のクロックドインバータCKINV1\_2のnチャネル型TFT501c及び501dを介して流れる漏れ電流による出力電位SB\_2の変化を示す。また、破線301pは、第2段の第1のクロックドインバータCKINV1\_2のpチャネル型TFT501a及び501bを介して流れる漏れ電流による出力電位SB\_2の変化を示す。30

#### 【0078】

第2のクロックドインバータCKINV2のpチャネル型TFTのゲート幅を大きくすることによって、従来例において、図6において示した漏れ電流による出力電位SB\_2の変化401nに対して、301nを小さく抑えることができる。

#### 【0079】

また、第2のクロックドインバータCKINV2のnチャネル型TFTのゲート幅を大きくすることによって、従来例において、図6において示した漏れ電流による出力電位SB\_2の変化401pに対して、301pを小さく抑えることができる。

#### 【0080】

上記構成によって、第1のクロックドインバータの漏れ電流による、出力電圧の変動を抑えることができる。40

#### 【0081】

なお、図4において従来例において示したように、シフトレジスタの各段が有する第1のクロックドインバータの、クロックパルスCKまたは反転クロックパルスCKBがゲート電極に入力されているpチャネル型TFT501aと、ゲート電極が第1のクロックドインバータの入力端子に相当するpチャネル型TFT501bとは、その配置を入れ替えることができる。

#### 【0082】

ここで、上記のTFTの配置の入れ替えについてその意味を定義する。例えば、TFT1とTFT2を有する第1の構成において、TFT1とTFT2の配置を入れ替えて得られる第2の構成について説明する。第2の構成は、TFT1とTFT2それぞれのゲート電

極に入力される信号は第1の構成と同じであって、TFT1のソース電極の電気的接続関係を第1の構成のTFT2のソース電極の電気的接続関係となるように配線し、TFT2のソース電極の電気的接続関係を第1の構成のTFT1のソース電極の電気的接続関係となるように配線し、TFT1のドレイン電極の電気的接続関係を第1の構成のTFT2のドレイン電極の電気的接続関係となるように配線し、TFT2のドレイン電極の電気的接続関係を第1の構成のTFT1のドレイン電極の電気的接続関係となるように配線した構成を示すものとする。

#### 【0083】

また、第1のクロックドインバータの、クロックパルスCKまたは反転クロックパルスCKBがゲート電極に入力されているnチャネル型TFT501dと、ゲート電極が第1のクロックドインバータの入力端子に相当するnチャネル型TFT501cとは、その配置を入れ替えることができる。10

#### 【0084】

同様に、シフトレジスタの各段が有する第2のクロックドインバータの、クロックパルスCKまたは反転クロックパルスCKBがゲート電極に入力されているpチャネル型TFT501aと、ゲート電極が第2のクロックドインバータの入力端子に相当するpチャネル型TFT501bとは、その配置を入れ替えることができる。また、第2のクロックドインバータの、クロックパルスCKまたは反転クロックパルスCKBがゲート電極に入力されているnチャネル型TFT501dと、ゲート電極が第2のクロックドインバータの入力端子に相当するnチャネル型TFT501cとは、その配置を入れ替えることができる。20

#### 【0085】

また、図4において、シフトレジスタの各段が有する、第1のクロックドインバータCKINV1、第2のクロックドインバータCKINV2及びインバータINVを構成するTFTは、シングルゲート構造としたが、これに限定されない。ダブルゲート構造や、更に多くのゲート電極を有するマルチゲート構造であっても良い。

#### 【0086】

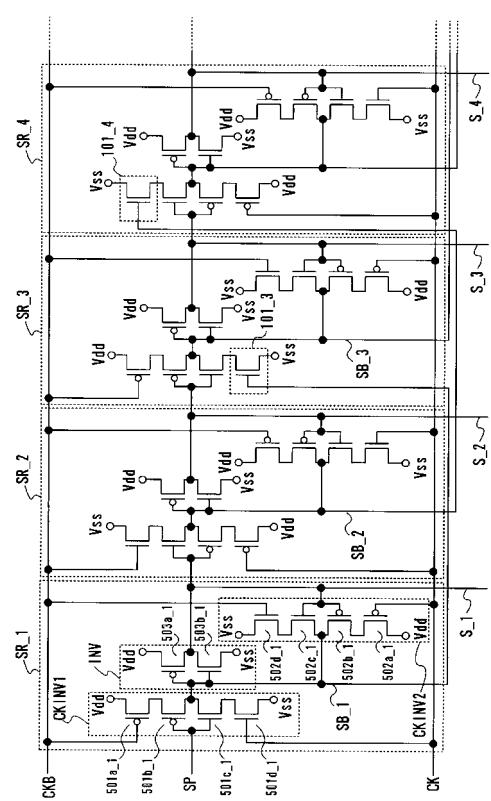

##### (第2の実施の形態)

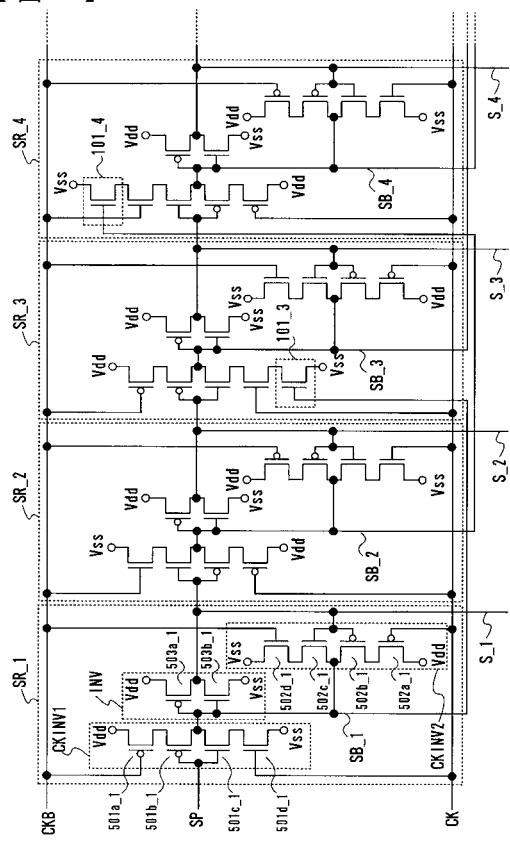

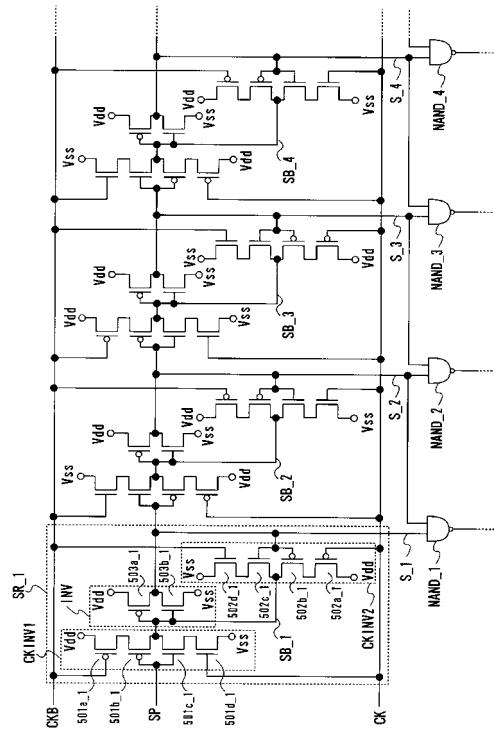

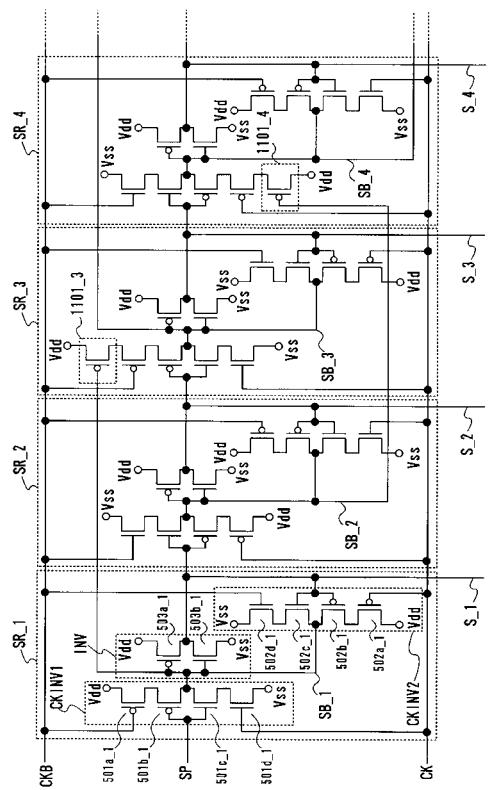

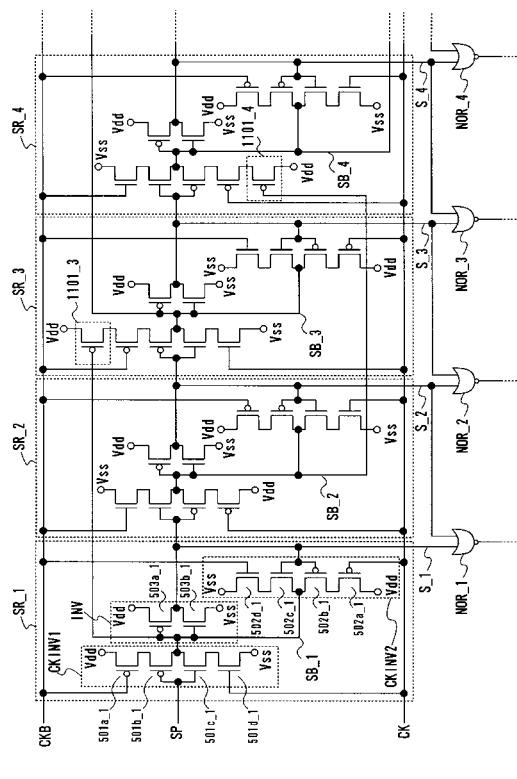

第2の実施の形態におけるシフトレジスタの構成を示す回路図を図1に示す。なお、図4と同じ部分は同じ符号を用いて表現し、説明は省略する。30

#### 【0087】

本発明のシフトレジスタでは、その電源電圧（高電源電位Vddと低電源電位Vssの電位差に相当する）より小さな振幅電圧の、スタートパルスSPや、クロックパルスCKを入力する。この際問題となる、第1のクロックドインバータの漏れ電流を以下の構成によって低減する。

#### 【0088】

図1において、シフトレジスタを構成する第3段以降の各段の第1のクロックドインバータCKINV1に、新たに、nチャネル型TFT101を追加する。ここで、第k（kは、3以上r以下の自然数）段のnチャネル型TFT101を101\_kと表記する。

#### 【0089】

nチャネル型TFT101\_kのゲート電極は、第k-2段の第1のクロックドインバータCKINV1\_k-2の出力端子に接続されている。また、nチャネル型TFT101\_kのソース電極は、低電源電位Vssに接続され、ドレイン電極は、クロックドインバータCKINV1\_kの有するnチャネル型TFT501d\_kのソース電極に接続されている。40

#### 【0090】

上記構成によって、第k段の第1のクロックドインバータCKINV1\_kにおいて、nチャネル型TFT101\_kのゲート電極には、SB\_k-2の信号が入力される。nチャネル型TFT501d\_kがオフの状態になることを望まれる際に、SB\_k-2の信号は、「Lo」の電位となる。この信号SB\_k-2の「Lo」の電位は、低電源電位V

s s 程度の電位である。そのため、信号 S B \_ k - 2 の「L o」の電位がゲート電極に入力されたnチャネル型TFT501d - k は、ゲート電圧（ゲート・ソース間電圧  $V_{gs}$ ）を0V程度にすることができ、確実にオフすることができる。こうして、第k段の回路の第1のクロックドインバータCKINV1\_kにおいて、nチャネル型TFTの漏れ電流が流れるのを防ぐことができる。

## 【0091】

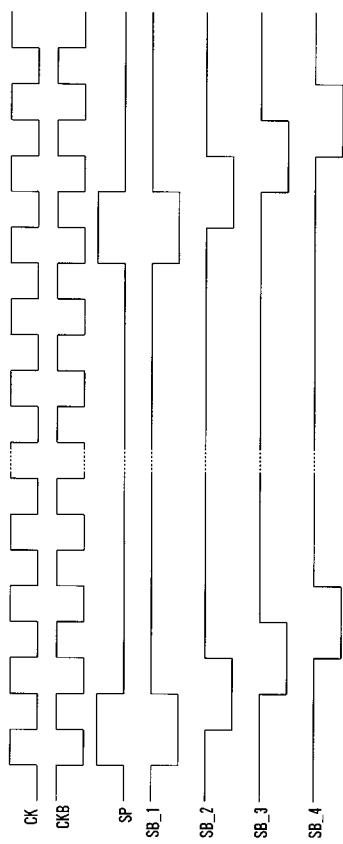

図1のシフトレジスタを駆動させた場合のタイミングチャートを、図2に示す。

## 【0092】

ここで、タイミングチャートに示すようにスタートパルスを入力すれば、漏れ電流による第1段の第1のクロックドインバータの出力 S B \_ 1 の変動は問題とならない。つまり、第1段の第1のクロックドインバータにおいて、入力されたスタートパルス S P の極性が反転した信号が、第1段の第1のクロックドインバータCKINV1\_1 の出力 S B \_ 1 となるような場合、漏れ電流による第1段の第1のクロックドインバータの出力 S B \_ 1 の変動は問題とならない。

## 【0093】

なお、第2段の第1のクロックドインバータの出力 S B \_ 2 は、漏れ電流によって変動する。一方、本実施の形態の構成によって、第3段以降の第1のクロックドインバータの出力 S B の、nチャネル型TFTの漏れ電流による変動を防ぐことができる。この際、第3段以降の出力を正規出力とするシフトレジスタとすればよい。

## 【0094】

この様に、第3段以降の第1のクロックドインバータCKINV1 に、新たに、nチャネル型TFT101を設けることによって、漏れ電流を防ぎ、シフトレジスタを正常に動作させることができる。

## 【0095】

ここで、図1に示した部分の電位に対応する各段の出力 S において、その隣り合う段の出力 S のNANDをとった信号を出力信号とするタイプのシフトレジスタを、図12に示す。図1と同じ部分は同じ符号を用いて示し、説明は省略する。

## 【0096】

タイミングチャートに示すようにスタートパルス S P を入力すれば、漏れ電流による第1段の第1のクロックドインバータCKINV1\_1 の出力 S B \_ 1 の変動は問題とならない。また、第2段の第1のクロックドインバータの出力 S B \_ 2 は、漏れ電流によって変動するが、第1段及び第2段の出力 S \_ 1 と S \_ 2 のNANDをとったものが、サンプリングパルス S MP \_ 1 として出力されるため、シフトレジスタの動作上、問題ない。第3段以降の第1のクロックドインバータCKINV1 に、新たに、nチャネル型TFT101を設けることによって、漏れ電流を防ぎ、シフトレジスタを正常に動作させることができる。

## 【0097】

なお、本実施の形態において、pチャネル型TFTの漏れ電流を確実に防ぐために、新たなpチャネル型TFT等は設けなかった。一般に、nチャネル型TFTは、pチャネル型TFTより特性が良いため、特にnチャネル型TFTの漏れ電流を確実に防止することが重要である。そのため、上記構成による漏れ電流防止の構造は有効である。

## 【0098】

なお、本実施の形態のシフトレジスタの第1段及び第2段において、それぞれ有する第1のクロックドインバータCKINV1のpチャネル型TFT501aと、pチャネル型TFT501bとは、その配置を入れ替えることができる。つまり、図1及び図12に示すように、高電源電位 Vdd にそのソース電極が接続されたpチャネル型TFTを501aとして、pチャネル型TFT501a、501bの順に直列に接続し、pチャネル型TFT501bのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、高電源電位 Vdd にそのソース電極が接続されたpチャネル型TFTを501bとして、pチャネル型TFT501b、501aの順に直列に接続し、p

10

20

30

40

50

チャネル型TFT501aのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良い。

【0099】

また、また上記の様に、第1のクロックドインバータCKINV1内において、pチャネル型TFT501a及び501bの配置が2とおり存在するが、このそれぞれにおいて、nチャネル型TFT501dと、501cとは、その配置を入れ替えることができる。つまり、図1及び図12に示すように、低電源電位Vssにそのソース電極が接続されたnチャネル型TFTを501dとして、nチャネル型TFT501d、501cの順に直列に接続し、nチャネル型TFT501cのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたnチャネル型TFTを501cとして、nチャネル型TFT501c、501dの順に直列に接続し、nチャネル型TFT501dのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良い。

【0100】

第1段及び第2段の回路において、第1のクロックドインバータCKINV1と同様に、第2のクロックドインバータCKINV2のpチャネル型TFT501aと、501bとは、その配置を入れ替えることができる。また、第2のクロックドインバータCKINV2のnチャネル型TFT501dと、501cとは、その配置を入れ替えることができる。

【0101】

なお、本実施の形態のシフトレジスタの第3段以降の回路において、それぞれ有する第1のクロックドインバータCKINV1のpチャネル型TFT501aと、pチャネル型TFT501bとは、その配置を入れ替えることができる。つまり、図1及び図12に示すように、高電源電位Vddにそのソース電極が接続されたTFTをpチャネル型TFT501aとして、pチャネル型TFT501a、501bの順に直列に接続し、pチャネル型TFT501bのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、高電源電位Vddにそのソース電極が接続されたTFTをpチャネル型TFT501bとし、pチャネル型TFT501b、501aの順に直列に接続し、pチャネル型TFT501aのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良い。

【0102】

また、また上記の様に、第1のクロックドインバータCKINV1内において、pチャネル型TFT501a及び501bの配置が2とおり存在するが、このそれぞれにおいて、nチャネル型TFT101と、501dと、501cとは、その配置を入れ替えることができる。つまり、図1及び図12に示すように、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT101とし、nチャネル型TFT101、501d、501cの順に直列に接続し、nチャネル型TFT501cのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いがその他に、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT101とし、nチャネル型TFT101、501c、501dの順に直列に接続し、nチャネル型TFT501dのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT501dとし、nチャネル型TFT501d、101、501cの順に直列に接続し、nチャネル型TFT501cのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT501cとし、nチャネル型TFT501c、101、501dの順に直列に接続し、nチャネル型TFT501dのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT501dとし、nチャネル型TFT501d、501c、101の順に直列に接続し、nチャネル型TFT101

10

20

30

40

50

01のドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT501cとし、nチャネル型TFT501c、501d、101の順に直列に接続し、nチャネル型TFT101のドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良い。

【0103】

第1段及び第2段における第2のクロックドインバータCKINV2と同様に、第3段以降の第2のクロックドインバータCKINV2のpチャネル型TFT501aと、501bとは、その配置を入れ替えることができる。また、第2のクロックドインバータCKINV2のnチャネル型TFT501dと、501cとは、その配置を入れ替えることができる。

10

【0104】

なお、図1及び図12において、シフトレジスタの各段が有する、第1のクロックドインバータCKINV1、第2のクロックドインバータCKINV2及びインバータINVを構成するTFTは、シングルゲート構造としたが、これに限定されない。ダブルゲート構造や、更に多くのゲート電極を有するマルチゲート構造であっても良い。

【0105】

本実施の形態は、第1の実施の形態と自由に組み合わせて実施することが可能である。

【0106】

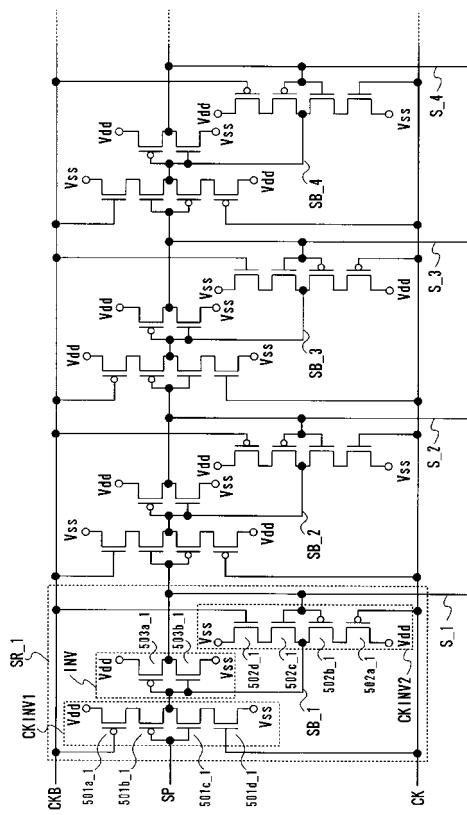

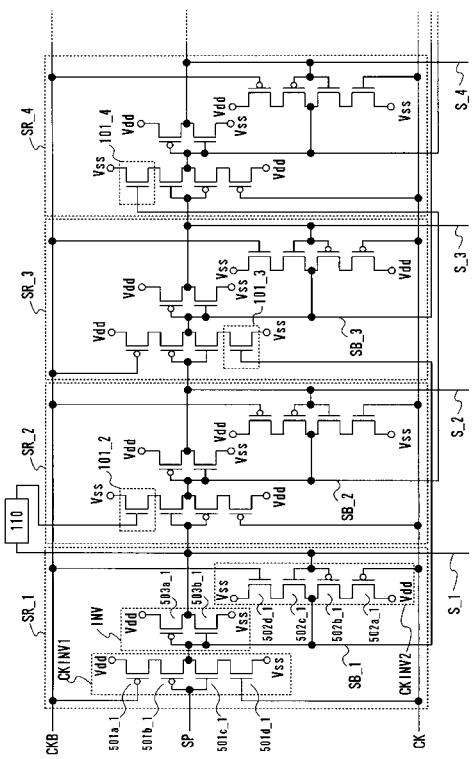

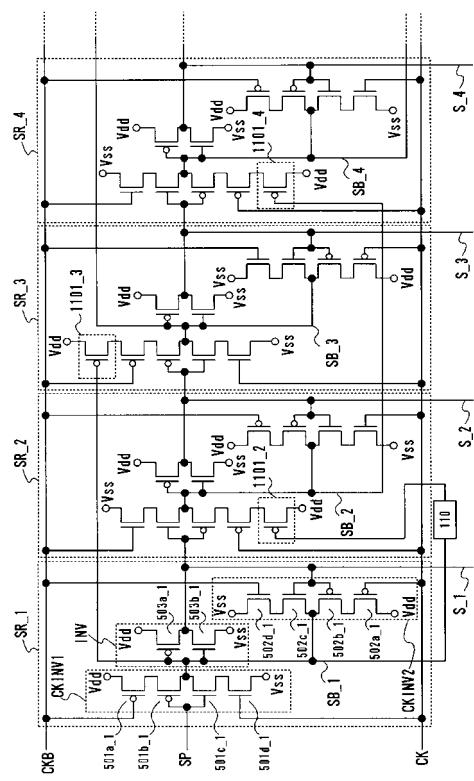

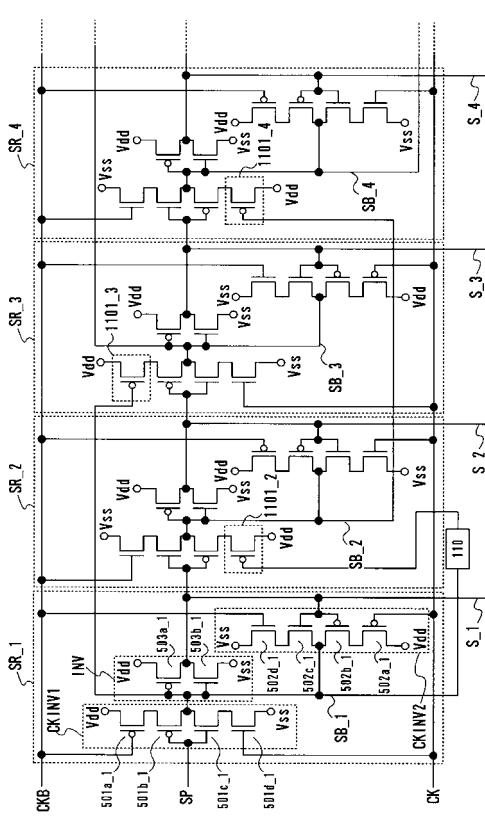

(第3の実施の形態)

20

本実施の形態では、第2の実施の形態において、図1で示した構成とは異なる構成のシフトレジスタについて図8を用いて説明する。図8において、図1と同じ部分は同じ符号を用いて表現し、説明は省略する。

【0107】

本発明のシフトレジスタでは、その電源電圧（高電源電位Vddと低電源電位Vssの電位差に相当する）より小さな振幅電圧の、スタートパルスSPや、クロックパルスCKを入力する。この際問題となる、第1のクロックドインバータの漏れ電流を以下の構成によって低減する。

【0108】

図8において、シフトレジスタを構成する第2段以降の各段の第1のクロックドインバータCKINV1に、新たに、nチャネル型TFT101を追加する。ここで、第k（kは、2以上r以下の自然数）段目のnチャネル型TFT101を101\_kと表記する。

30

【0109】

nチャネル型TFT101\_kのゲート電極は、第k-2段目の第1のクロックドインバータCKINV1\_k-2の出力端子に接続されている。また、nチャネル型TFT101\_kのソース電極は、低電源電位Vssに接続され、ドレイン電極は、クロックドインバータCKINV1\_kの有するnチャネル型TFT501d\_kのソース電極に接続されている。

【0110】

また、第2段に追加したnチャネル型TFT101\_2のソース電極は、低電源電位Vssに接続され、ドレイン電極は、第1のクロックドインバータCKINV1\_2が有する第1のnチャネル型TFT501d\_2のソース電極に接続されている。

40

【0111】

図8においては、第2段のnチャネル型TFT101\_2のゲート電極には、遅延回路110を介して、第1段のインバータINV\_1の出力が入力されている。遅延回路110としては、複数の縦列接続されたインバタ回路によって構成することができる。しかしこれに限定されず、遅延回路110として、公知の構成の回路を自由に用いることができる。

【0112】

上記構成によって、第2段の第1のクロックドインバータCKINV1\_2において、n

50

チャネル型 TFT がオフの状態になることを望まれる際に、n チャネル型 TFT 101\_2 のゲート電極には、第 1 段の出力（第 1 段のインバータ INV\_1 の出力）S\_1 を遅延させた信号が入力される。この遅延の度合いは、クロックパルスの半周期程度に設定する。これによって、第 2 段の回路の第 1 のクロックドインバータ CKINV1\_2 において、n チャネル型 TFT の漏れ電流が流れるのを防ぐことができる。

#### 【0113】

ここで、n チャネル型 TFT 101\_2 のゲート電極に入力される信号は、第 1 段のインバータ INV\_1 の出力 S\_1 を、クロックパルスの半周期程度遅延させた信号に限定されない。例えば、第 1 段の第 1 のクロックドインバータ CKINV1\_1 の出力 SB\_1 の極性を反転させ、遅延させた信号であっても構わない。

10

#### 【0114】

なお、n チャネル型 TFT の漏れ電流が問題となる際に、n チャネル型 TFT 101\_2 をオフの状態とし、第 2 段の n チャネル型 TFT 501c 及び 501d が共にオンの状態を選択される場合に、n チャネル型 TFT 101\_2 をオンの状態にする信号であれば、上記に限定されない。

#### 【0115】

また、第 3 段以降の回路において、第 k 段の第 1 のクロックドインバータにおいて、n チャネル型 TFT 501d\_k がオフの状態になることを望まれる際に、n チャネル型 TFT 101\_k のゲート電極に入力された SB\_k - 2 の信号によって、n チャネル型 TFT 101\_k をオフにする。こうして、第 k 段の回路の第 1 のクロックドインバータ CK 20 INV1\_k において、n チャネル型 TFT の漏れ電流が流れるのを防ぐことができる。

20

#### 【0116】

ここで、タイミングチャートに示すようにスタートパルスを入力すれば、漏れ電流による第 1 段の第 1 のクロックドインバータの出力 SB\_1 の変動は問題とならない。つまり、第 1 段の第 1 のクロックドインバータにおいて、入力されたスタートパルス SP の極性が反転した信号が、第 1 段の第 1 のクロックドインバータ CKINV1\_1 の出力 SB\_1 となるような場合、漏れ電流による第 1 段の第 1 のクロックドインバータの出力 SB\_1 の変動は問題とならない。

#### 【0117】

こうして、第 2 段以降の第 1 のクロックドインバータ CKINV1 に、新たに、n チャネル型 TFT 101 を設けることによって、漏れ電流を防ぎ、シフトレジスタを正常に動作させることができる。

30

#### 【0118】

本実施の形態のシフトレジスタの駆動方法について、図 9 のタイミングチャートを用いて説明する。図 9 において、遅延回路 110 を介して TFT 101\_2 のゲート電極に入力される信号 S\_1R を示す。この信号 S\_1R によって、TFT 101\_2 をオフにし、第 2 段の第 1 のクロックドインバータ CKINV1\_2 の漏れ電流を防ぐことができる。

#### 【0119】

なお、p チャネル型 TFT の漏れ電流を確実に防ぐために、新たな p チャネル型 TFT 等は設けなかった。一般に、n チャネル型 TFT は、p チャネル型 TFT より特性が良いため、特に n チャネル型 TFT の漏れ電流を確実に防止することが重要である。そのため、上記構成による漏れ電流防止の構造は有効である。

40

#### 【0120】

なお、本実施の形態のシフトレジスタの第 1 段において、第 1 のクロックドインバータ CKINV1\_1 の p チャネル型 TFT 501a と、p チャネル型 TFT 501b とは、その配置を入れ替えることができる。つまり、図 8 のように、高電源電位 Vdd にそのソース電極が接続された p チャネル型 TFT を 501a として、p チャネル型 TFT 501a 、501b の順に直列に接続し、p チャネル型 TFT 501b のドレイン電極を第 1 のクロックドインバータ CKINV1\_1 の出力端子とした構成であっても良いし、高電源電位 Vdd にそのソース電極が接続された p チャネル型 TFT を 501b として、p チャネル型 TFT 501b 、501a の順に直列に接続し、p チャネル型 TFT 501a のドレイン電極を第 1 のクロックドインバータ CKINV1\_1 の出力端子とした構成であっても良い。

50

ル型TFT501b、501aの順に直列に接続し、pチャネル型TFT501aのドレイン電極を第1のクロックドインバータCKINV1\_1の出力端子とした構成であっても良い。

#### 【0121】

また、また上記の様に、第1のクロックドインバータCKINV1\_1内において、pチャネル型TFT501a及び501bの配置が2とおり存在するが、このそれれにおいて、nチャネル型TFT501dと、501cとは、その配置を入れ替えることができる。つまり、図8のように低電源電位Vssにそのソース電極が接続されたnチャネル型TFTを501dとして、nチャネル型TFT501d、501cの順に直列に接続し、nチャネル型TFT501cのドレイン電極を第1のクロックドインバータCKINV1\_1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたnチャネル型TFTを501cとして、nチャネル型TFT501c、501dの順に直列に接続し、nチャネル型TFT501dのドレイン電極を第1のクロックドインバータCKINV1\_1の出力端子とした構成であっても良い。

#### 【0122】

第1段の回路において、第1のクロックドインバータCKINV1\_1と同様に、第2のクロックドインバータCKINV2\_1のpチャネル型TFT501aと、501bとは、その配置を入れ替えることができる。また、第2のクロックドインバータCKINV2\_1のnチャネル型TFT501dと、501cとは、その配置を入れ替えることができる。

#### 【0123】

なお、本実施の形態のシフトレジスタの第2段以降の回路において、それぞれ有する第1のクロックドインバータCKINV1のpチャネル型TFT501aと、pチャネル型TFT501bとは、その配置を入れ替えることができる。つまり、図8のように高電源電位Vddにそのソース電極が接続されたTFTをpチャネル型TFT501aとして、pチャネル型TFT501a、501bの順に直列に接続し、pチャネル型TFT501bのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、高電源電位Vddにそのソース電極が接続されたTFTをpチャネル型TFT501bとし、pチャネル型TFT501b、501aの順に直列に接続し、pチャネル型TFT501aのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良い。

#### 【0124】

また、また上記の様に、第1のクロックドインバータCKINV1内において、pチャネル型TFT501a及び501bの配置が2とおり存在するが、このそれれにおいて、nチャネル型TFT101と、501dと、501cとは、その配置を入れ替えることができる。つまり、図8のように低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT101とし、nチャネル型TFT101、501d、501cの順に直列に接続し、nチャネル型TFT501cのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いがその他に、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT101とし、nチャネル型TFT101、501c、501dの順に直列に接続し、nチャネル型TFT501dのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT501dとし、nチャネル型TFT501d、101、501cの順に直列に接続し、nチャネル型TFT501cのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT501cとし、nチャネル型TFT501c、101、501dの順に直列に接続し、nチャネル型TFT501dのドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT501dとし、nチャネル型TFT5

10

20

30

40

50

01d、501c、101の順に直列に接続し、nチャネル型TFT101のドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良いし、低電源電位Vssにそのソース電極が接続されたTFTをnチャネル型TFT501cとし、nチャネル型TFT501c、501d、101の順に直列に接続し、nチャネル型TFT101のドレイン電極を第1のクロックドインバータCKINV1の出力端子とした構成であっても良い。

#### 【0125】

第1段の回路における第2のクロックドインバータCKINV2\_1と同様に、第2段以降の第2のクロックドインバータCKINV2のpチャネル型TFT501aと、501bとは、その配置を入れ替えることができる。また、第2のクロックドインバータCKINV2のnチャネル型TFT501dと、501cとは、その配置を入れ替えることができる。

#### 【0126】

なお、図8において、シフトレジスタの各段が有する、第1のクロックドインバータCKINV1、第2のクロックドインバータCKINV2及びインバータINVを構成するTFTは、シングルゲート構造としたが、これに限定されない。ダブルゲート構造や、更に多くのゲート電極を有するマルチゲート構造であっても良い。

#### 【0127】

本実施の形態は、第1の実施の形態と自由に組み合わせて実施することが可能である。

#### 【0128】

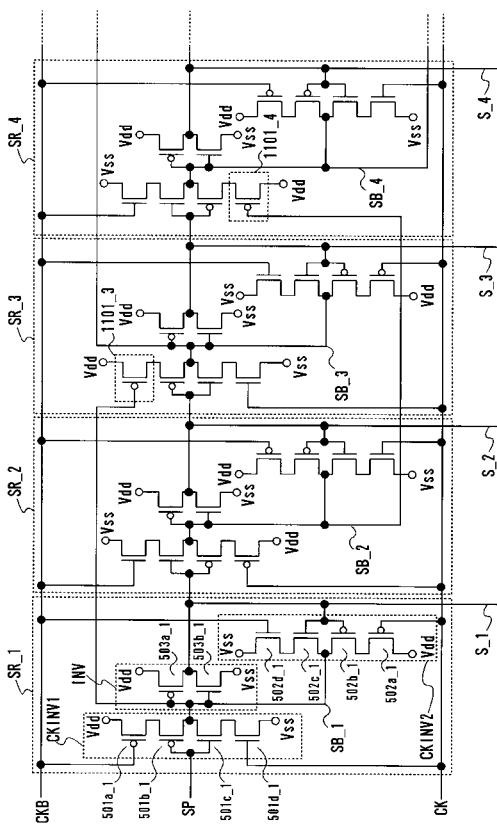

(第4の実施の形態)

本実施の形態では、実施の形態2や実施の形態3とは異なる構成のシフトレジスタについて説明する。

#### 【0129】

本実施の形態のシフトレジスタは、図1に示した構成のシフトレジスタにおいて、第1のクロックドインバータCKINV1にnチャネル型TFT101を有する第3段以降の段では、クロックパルスCKまたは反転クロックパルスCKBが入力されるnチャネル型TFT501dを省略した構成である。この構成を図18に示す。なお、図1と同じ部分は同じ符号を用いて示し説明は省略する。例えば、図18における第3段の第1のクロックドインバータCKINV1では、図1に対してnチャネル型TFT501d\_3が省略されている。図18に示す構成のシフトレジスタは、図1と同様のタイミングでパルスを出力することができる。

#### 【0130】

図18に示すような構成では、シフトレジスタを構成するTFTの数は従来のシフトレジスタに対して増加しない。しかし、その電源電圧より小さな振幅電圧を有するクロックパルス、スタートパルスを入力する場合にも、漏れ電流による第1のクロックドインバータの出力電位の変化を低減することができる。こうして、低消費電力・高周波数で動作し、電源線のノイズ、レイアウト面積の増大等の問題を解決するシフトレジスタが提供される。

#### 【0131】

また同様に、図8に示した構成のシフトレジスタにおいて、第1のクロックドインバータCKINV1にnチャネル型TFT101を有する第2段以降の段では、クロックパルスCKまたは反転クロックパルスCKBが入力されるnチャネル型TFT501dを省略した構成である。この構成を図19に示す。なお、図8と同じ部分は同じ符号を用いて示し説明は省略する。例えば、図19における第2段の第1のクロックドインバータCKINV1では、図8に対してnチャネル型TFT501d\_2が省略されている。図19に示す構成のシフトレジスタは、図8と同様のタイミングでパルスを出力することができる。

#### 【0132】

図19に示すような構成でも、シフトレジスタを構成するTFTの数は従来のシフトレジスタに対して増加しない。しかし、その電源電圧より小さな振幅電圧を有するクロックパ

10

20

30

40

50

ルス、スタートパルスを入力する場合にも、漏れ電流による第1のクロックドインバータの出力電位の変化を低減することができる。こうして、低消費電力・高周波数で動作し、電源線のノイズ、レイアウト面積の増大等の問題を解決するシフトレジスタが提供される。

【0133】

本実施の形態は、実施の形態1～実施の形態3と自由に組み合わせて実施することができる。

【0134】

(第5の実施の形態)

本実施の形態では、その電源電圧(高電源電位Vddと低電源電位Vssの電位差に相当する)より小さな振幅電圧の、スタートパルスSPや、クロックパルスCKを入力するシフトレジスタであって、この際問題となる、第1のクロックドインバータの漏れ電流を以下の構成によって低減したシフトレジスタの例を示す。

【0135】

なお、本実施の形態に示すシフトレジスタでは、第1のクロックドインバータのpチャネル型TFT501aや501bを介して流れる漏れ電流を低減する構成である。

【0136】

本実施の形態のシフトレジスタの構成を図21に示す。また、図21のシフトレジスタのタイミングチャートを図20に示す。ここで、スタートパルスSP、クロックパルスCKの入力のタイミングは実施の形態1において図1で示した構成と同様であるので詳細な説明は省略する。

【0137】

但し、実施の形態1において図1で示した構成のシフトレジスタに入力されるスタートパルスに対して、本実施の形態の図21で示した構成のシフトレジスタに入力されるスタートパルスの極性は反転している。入力されるクロックパルスCK、反転クロックパルスCKBについては、図1の構成のシフトレジスタ、図21の構成のシフトレジスタ共に同じである。

【0138】

図21に示すシフトレジスタでは、第3段以降の各段の第1のクロックドインバータCKINV1は、pチャネル型TFT1101を有する。ここで、第k(kは、3以上n以下の自然数)段のpチャネル型TFT1101を1101\_kと表記する。なお、pチャネル型TFT1101のゲート電極の電気的接続については、図21に示した通りである。つまり、ある段におけるpチャネル型TFT1101のゲート電極には、2つ前の段の第1のクロックドインバータCKINV1の出力が入力されている。

【0139】

図21に示した構成のシフトレジスタによって、第1のクロックドインバータのpチャネル型TFT501aや501bを介して流れる漏れ電流を低減することができる。こうして、低消費電力・高周波数で動作し、電源線のノイズ、レイアウト面積の増大等の問題を解決するシフトレジスタが提供される。

【0140】

なお、図21に示した構成において、さらに第2段の第1のクロックドインバータCKINV1に、新たにpチャネル型TFT1101を追加する構成としてもよい。この構成を、図22に示す。なお、図22に示した構成において、図21と同じ部分は同じ符号を用いて示し説明は省略する。ここで、110は遅延回路である。第2段の第1のクロックドインバータCKINV1に追加されたpチャネル型TFT1101\_2のゲート電極には、第1段の第1のクロックドインバータCKINV1の出力が遅延回路110を介して入力される。遅延回路110により信号を遅延させる度合いは、クロックパルスの半周期程度に設定する。

【0141】

図22に示した構成のシフトレジスタによって、第1のクロックドインバータのpチャネル型TFT501aや501bを介して流れる漏れ電流を低減することができる。

10

20

30

40

50

ル型TFT501aや501bを介して流れる漏れ電流を低減することができる。こうして、低消費電力・高周波数で動作し、電源線のノイズ、レイアウト面積の増大等の問題を解決するシフトレジスタが提供される。

【0142】

また、図21や図22に示した構成のシフトレジスタにおいて、新たにpチャネル型TFT1101が追加された第1のクロックドインバータCKINV1では、クロックパルスCKまたは反転クロックパルスCKBが入力されるpチャネル型TFT501aを省略した構成とすることができる。

【0143】

つまり、図21において、新たにpチャネル型TFT1101が追加された第3段以降の第1のクロックドインバータCKINV1では、クロックパルスCKまたは反転クロックパルスCKBが入力されるpチャネル型TFT501aを省略することができる。この構成を図23に示す。例えば、図23における第3段の第1のクロックドインバータCKINV1では、図21に対してpチャネル型TFT501a\_3が省略されている。

【0144】

また図22において、新たにpチャネル型TFT1101が追加された第2段以降の第1のクロックドインバータCKINV1では、クロックパルスCKまたは反転クロックパルスCKBが入力されるpチャネル型TFT501aを省略することができる。この構成を図24に示す。例えば、図24における第2段の第1のクロックドインバータCKINV1では、図22に対してpチャネル型TFT501a\_2が省略されている。

【0145】

図23や図24において、シフトレジスタを構成するTFTの数は従来のシフトレジスタに対して増加しない。しかし、その電源電圧より小さな振幅電圧を有するクロックパルス、スタートパルスを入力する場合にも、漏れ電流による第1のクロックドインバータの出力電位の変化を低減することができる。こうして、低消費電力・高周波数で動作し、電源線のノイズ、レイアウト面積の増大等の問題を解決するシフトレジスタが提供される。

【0146】

また、図21～図24に示したようなシフトレジスタの各段の出力Sにおいて、その隣り合う段の出力のNORをとった信号を出力信号とするタイプのシフトレジスタでもよい。図21に示したようなシフトレジスタにおいて、その隣り合う段の出力のNORをとった信号を出力信号とするタイプのシフトレジスタを図25に示す。

【0147】

なお図25において、図21に示したタイミングチャートに示すようにスタートパルスSPを入力すれば、漏れ電流による第1段の第1のクロックドインバータCKINV1\_1の出力SB\_1の変動は問題とならない。また、第2段の第1のクロックドインバータの出力SB\_2は、漏れ電流によって変動するが、第1段及び第2段の出力S\_1とS\_2のNORをとったものが、サンプリングパルスSMP\_1として出力されるため、シフトレジスタの動作上、問題ない。第3段以降の第1のクロックドインバータCKINV1に、新たに、pチャネル型TFT1101を設けることによって、漏れ電流を防ぎ、シフトレジスタを正常に動作させることができる。

【0148】

本実施の形態は、実施の形態1～実施の形態4と自由に組み合わせて実施することができる。

【0149】

(第6の実施の形態)

本発明のシフトレジスタ及びその駆動方法は、表示装置の駆動回路に用いることができる。

【0150】

例えば、エレクトロルミネッセンス(EL)素子を用いたEL表示装置や、液晶素子を用いた液晶表示装置等の駆動回路に、本発明のシフトレジスタ及びその駆動方法を用いるこ

10

20

30

40

50

とができる。これにより、消費電力が少なく、また、小型化可能で、信頼性の高い表示装置が提供される。

【0151】

なおEL素子とは、一対の電極（陽極と陰極）間にEL層を挟んだ構成の素子で、一対の電極間に電圧を印加することによって発光する素子を示すものとする。なお、EL層は、有機化合物によって形成されていてもよいし、無機物によって構成されていてもよいし、有機化合物と無機物の混合物によって形成されていてもよい。ここで、EL層が有機化合物を主成分として形成される素子を特にOLED（Organic Light Emitting Diode）と呼ぶことにする。OLEDを用いた表示装置をOLED表示装置と呼ぶ。

【0152】

OLEDのEL層を有機化合物層と呼ぶことにする。有機化合物層は通常、積層構造となっている。代表的には、コダック・イーストマン・カンパニーのTangらが提案した「正孔輸送層／発光層／電子輸送層」という積層構造が挙げられる。また他にも、陽極上に正孔注入層／正孔輸送層／発光層／電子輸送層、または正孔注入層／正孔輸送層／発光層／電子輸送層／電子注入層の順に積層する構造でも良い。発光層に対して蛍光性色素等をドーピングしても良い。上述した正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層等は、全て有機化合物層に含まれる。そして、上記構造でなる有機化合物層に一対の電極（陽極と陰極）から所定の電圧をかけ、それにより発光層においてキャリアの再結合が起こって発光する。

【0153】

なお、有機化合物層は、明確な積層構造を有している必要は無い。各層を構成する物質が混合した構造を有していてもよい。

【0154】

また本明細書中において、OLEDとは、1重項励起子からの発光（蛍光）と、3重項励起子からの発光（燐光）の一方または両方を用いるものを示すものとする。

【0155】

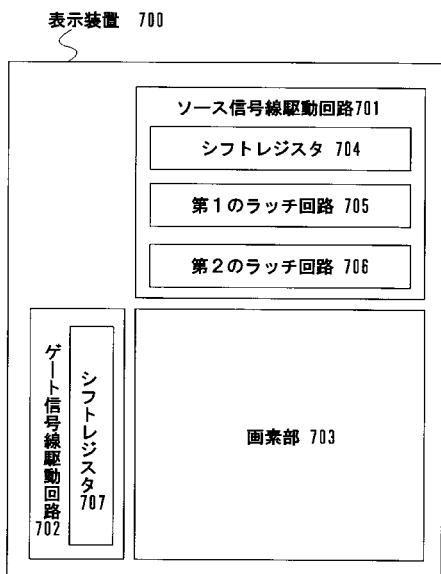

図13に、表示装置の構成の例を示すブロック図を示す。図13において、表示装置700は、ソース信号線駆動回路701、ゲート信号線駆動回路702、画素部703によって構成されている。ソース信号線駆動回路701は、シフトレジスタ704、第1のラッチ回路705、第2のラッチ回路706によって構成されている。また、ゲート信号線駆動回路702は、シフトレジスタ707によって構成されている。

【0156】

画素部703には、ソース信号線駆動回路701からの信号が入力される複数のソース信号線が列方向に配置され、ゲート信号線駆動回路702からの信号が入力される複数のゲート信号線が行方向に配置されている。これらのソース信号線及びゲート信号線の交点毎に、画素が配置されている。

【0157】

表示装置がOLED表示装置では、画素はそれぞれOLEDを有し、表示装置が液晶表示装置では液晶素子を有する。

【0158】

ゲート信号線駆動回路702は、シフトレジスタ707からの信号によって、ゲート信号線に順に信号を出力し、画素部703が有する画素行を選択する。ソース信号線駆動回路701は、シフトレジスタ704からの信号によって、第1のラッチ回路705が順にビデオ信号を保持し、第1のラッチ回路705において保持されたビデオ信号は、第2のラッチ回路706に転送されて、ソース信号線に入力される。こうして、1行の画素に信号を入力する。これを全ての画素行について繰り返し、1つの画像が表示される。

【0159】

例えば、OLED表示装置の画素の構成としては、ゲート信号線の信号によって、画素にソース信号線の信号を入力するかどうかを選択するスイッチとして働く、スイッチング用TFT及び、スイッチング用TFTがオンの状態となり、ソース信号線から入力された信

10

20

30

40

50

号に応じて、画素のOLEDを流れる電流を制御するOLED駆動用TFTを配置する構成の画素を用いることができる。

【0160】

なお、画素の構成としては公知のものを自由に用いることができる。

【0161】

本発明のシフトレジスタ及びその駆動方法は、ソース信号線駆動回路701が有するシフトレジスタ704及び、ゲート信号線駆動回路702が有するシフトレジスタ707に用いることができる。

【0162】

本実施の形態は、本発明の実施の形態1～実施の形態5と自由に組み合わせて実施するこ

とが可能である。 10

【0163】

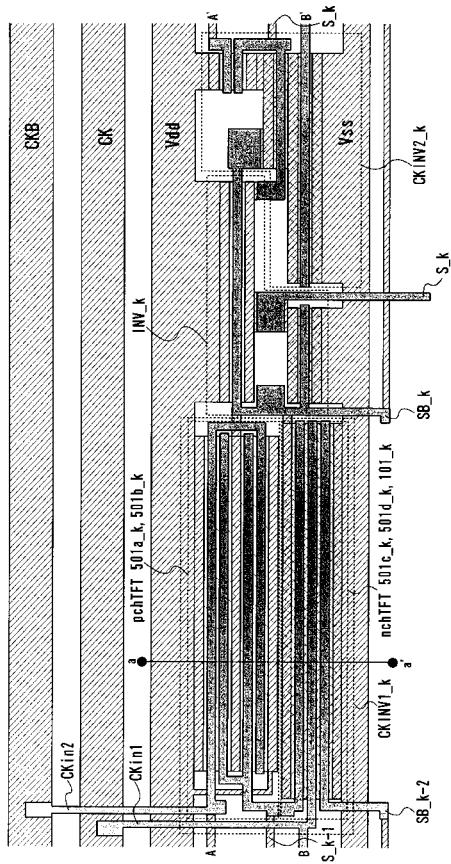

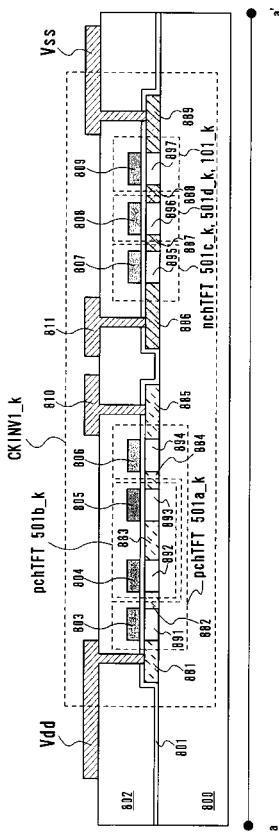

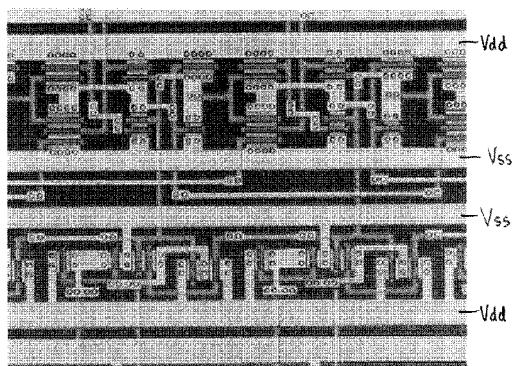

(第7の実施の形態)

本実施の形態では、本発明のシフトレジスタを実際に作製した際の上面図を示す。図15

において、図1におけるシフトレジスタの第3段以降のある1段に相当する部分の上面図

を示す。ここで、第k(kは3以上の自然数)段SR\_kの上面図を示す。

【0164】

第1のクロックドインバータCKINV1\_k、第2のクロックドインバータCKINV

2\_k及びインバータINV\_kが配置されている。なお、図1において示した部分と同じ部分は、同じ符号を用いて示す。 20

【0165】

第1のクロックドインバータCKINV1\_kを構成するpチャネル型TFT501a\_k

及び501b\_kを、図中pchTFT501a\_k, 501b\_kで示す。また、

第1のクロックドインバータCKINV1\_kを構成するnチャネル型TFT501c\_k

、501d\_k及び漏れ電流対策として配置したTFT101\_kを、図中nchTFT

501c\_k, 501b\_k, 101\_kで示す。

【0166】

CK、CKBは、それぞれクロックパルス及びクロックパルスの極性が反転した反転クロ

ックパルスが入力される配線である。また、Vddは、高電源電位が入力される電源線で

あり、Vssは、低電源電位が入力される電源線である。 30

【0167】

図中、A、Bで示した配線は、前段(第k-1段)のA'、B'にそれぞれ接続される。但

し、前後の段(第k-1段及び第k+1段)の回路では、TFT501dのゲート電極に

信号を入力する配線CKin1が配線CKBに接続され、TFT501aのゲート電極に

信号を入力する配線CKin2が配線CKに接続されている。

【0168】

第k段の第1のクロックドインバータCKINV1\_kに追加した、nチャネル型TFT

101\_kのゲート電極には、前々段(第k-2段)の第1のクロックドインバータCK

INV1\_k-2の出力に相当する、SB\_k-2で示す信号が入力されている。(なお

、出力される信号と同じ符号をもって、その信号が出力される端子や配線を示すこととす

る)。図15中SB\_k-2は、第k-2段の第1のクロックドインバータの出力端子及

び第k-2段の第2のクロックドインバータの出力端子に相当する。 40

【0169】

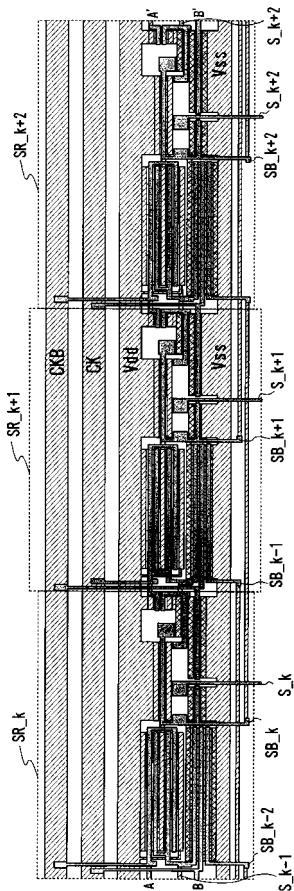

図16に、シフトレジスタの3段分の構成を示す上面図を示す。なお、図15と同じ部分

は同じ符号を用いて示し説明は省略する。

【0170】

図16において、シフトレジスタの第k段～第k+2段、SR\_k～SR\_k+2を示す

。第k+2段SR\_k+2の第1のクロックドインバータCKINV1\_k+2のnチャ

ネル型TFT101\_k+2のゲート電極に入力される信号は、第k段SR\_kの第1の

クロックドインバータCKINV1\_kの出力端子から出力される信号SB\_kである。 50

図15中S B \_ kは、第k段の第1のクロックドインバータの出力端子及び第k段の第2のクロックドインバータの出力端子に相当する。

【0171】

図15及び図16において示した構成のシフトレジスタでは、電源電圧より小さな振幅電圧を有するパルス信号（クロックパルス、反転クロックパルス及びスタートパルス）を入力しても、nチャネル型TFT101によって、漏れ電流による出力電位の変動を抑えることができる。

【0172】

本実施の形態は、実施の形態1～実施の形態6と自由に組み合わせて実施することが可能である。

10

【0173】

（第8の実施の形態）

本実施の形態では、本発明のシフトレジスタを実際に作製した際の断面図を示す。

【0174】

ここでは、図15のa～a'の部分の断面図を図17に示す。なお、図15と同じ部分は同じ符号を用いて示し、説明は省略する。

【0175】

絶縁表面を有する基板800上に、pチャネル型TFT（図中、p c h T F Tと表記）501a\_k、501b\_k、nチャネル型TFT（図中、n c h T F Tと表記）501c\_k、501d\_k、101\_kが形成されている。なお、801はゲート絶縁膜、802は層間絶縁膜である。

20

【0176】

pチャネル型TFT501a\_kは活性層中に、ソース領域として機能する不純物領域881及び885、チャネル領域として機能する891及び894を有する。なお、不純物領域882及び884はドレイン領域として機能する。なお、不純物領域885は、配線810によって、電源線Vddと電気的に接続されている。pチャネル型TFT501a\_kは、活性層と重ならない部分で電気的に接続されたゲート電極803と806を有するダブルゲート型のTFTである。ゲート電極803は、配線CKin2によって配線CKBと接続されている。

【0177】

30

pチャネル型TFT501b\_kは活性層中に、ソース領域として機能する不純物領域882及び884、ドレイン領域として機能する不純物領域883、チャネル領域として機能する892及び893を有する。pチャネル型TFT501b\_kは、活性層と重ならない部分で電気的に接続されたゲート電極804と805を有するダブルゲート型のTFTである。ゲート電極804は、端子S\_k\_1と電気的に接続されている。また、ドレイン領域として機能する不純物領域883は、端子S B \_ kに接続されている。

【0178】

pチャネル型TFT501a\_kのドレイン領域とpチャネル型TFT501b\_kのソース領域とは、活性層によって直接接続されている。

【0179】

40

nチャネル型TFT501c\_kは活性層中に、ドレイン領域として機能する不純物領域886、ソース領域として機能する不純物領域887、チャネル領域として機能する895を有する。なお、ドレイン領域として機能する不純物領域886は、配線811によって、端子S B \_ kと接続されている。ゲート電極807は、端子S\_k\_1と接続されている。

【0180】

nチャネル型TFT501d\_kは活性層中に、ドレイン領域として機能する不純物領域887、ソース領域として機能する不純物領域888、チャネル領域として機能する896を有する。ゲート電極808は、配線CKin1によって配線CKと接続されている。

【0181】

50

nチャネル型TFT101\_kは活性層中に、ドレイン領域として機能する不純物領域888、ソース領域として機能する不純物領域889、チャネル領域として機能する897を有する。ゲート電極809は、端子SB\_k-2と接続されている。ソース領域として機能する不純物領域889は、電源線Vssと電気的に接続されている。

【0182】

nチャネル型TFT501c\_kのソース領域とnチャネル型TFT501d\_kのドレイン領域は、活性層によって直接接続されている。また、nチャネル型TFT501d\_kのソース領域とnチャネル型TFT101\_kのドレイン領域は、活性層によって直接接続されている。

【0183】

以上が、本発明のシフトレジスタを実際に作製した際の断面図についての説明であった。本発明のシフトレジスタでは、電源電圧より小さな振幅電圧を有するパルス信号（クロックパルス、反転クロックパルス及びスタートパルス）を入力しても、nチャネル型TFT101によって、漏れ電流による出力電位の変動を抑えることができる。

【0184】

本実施の形態は、実施の形態1～実施の形態7と自由に組み合わせて実施することが可能である。

【0185】

（第9の実施の形態）

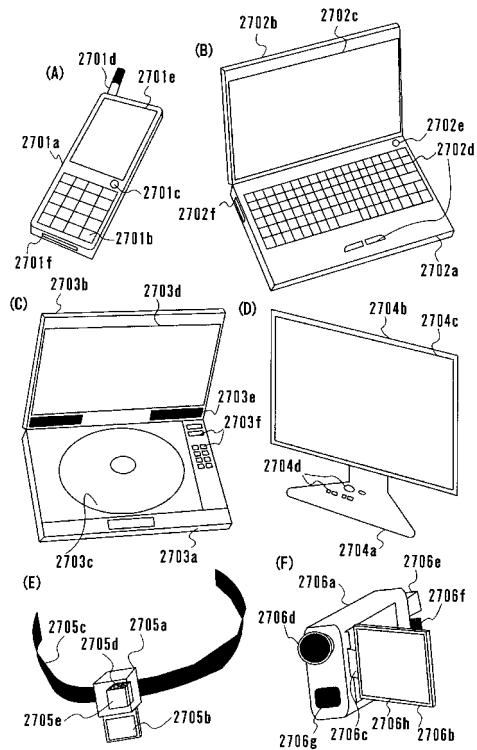

本実施の形態では、本発明のシフトレジスタ用いた駆動回路を有する表示装置を利用した電子機器について図11を用いて説明する。

【0186】

図11(A)に本発明の表示装置を用いた携帯情報端末の模式図を示す。携帯情報端末は、本体2701a、操作スイッチ2701b、電源スイッチ2701c、アンテナ2701d、表示部2701e、外部入力ポート2701fによって構成されている。本発明の表示装置は、表示部2701eに用いることができる。

【0187】

図11(B)に本発明の表示装置を用いたパーソナルコンピュータの模式図を示す。パーソナルコンピュータは、本体2702a、筐体2702b、表示部2702c、操作スイッチ2702d、電源スイッチ2702e、外部入力ポート2702fによって構成されている。本発明の表示装置は、表示部2702cに用いることができる。

【0188】

図11(C)に本発明の表示装置を用いた画像再生装置の模式図を示す。画像再生装置は、本体2703a、筐体2703b、記録媒体2703c、表示部2703d、音声出力部2703e、操作スイッチ2703fによって構成されている。本発明の表示装置は、表示部2703dに用いることができる。

【0189】

図11(D)に本発明の表示装置を用いたテレビの模式図を示す。テレビは、本体2704a、筐体2704b、表示部2704c、操作スイッチ2704dによって構成されている。本発明の表示装置は、表示部2704cに用いることができる。

【0190】

図11(E)に本発明の表示装置を用いたヘッドマウントディスプレイの模式図を示す。ヘッドマウントディスプレイは、本体2705a、モニター部2705b、頭部固定バンド2705c、表示部2705d、光学系2705eによって構成されている。本発明の表示装置は、表示部2705dに用いることができる。

【0191】

図11(F)に本発明の表示装置を用いたビデオカメラの模式図を示す。ビデオカメラは、本体2706a、筐体2706b、接続部2706c、受像部2006d、接眼部2706e、バッテリー2706f、音声入力部2706g、表示部2706hによって構成されている。本発明の表示装置は、表示部2706hに用いることができる。

10

20

30

40

50

**【0192】**

本発明は、上記応用電子機器に限定されず、様々な電子機器に応用することができる。

**【0193】**

本実施の形態は、実施の形態1～実施の形態8と自由に組み合わせて実施することができる。

**【0194】****(第10の実施の形態)**

本実施の形態では、同一基板上に従来型及び本発明のシフトレジスタの各々を搭載したパネルを作製し、動作させたときの測定結果について述べる。より詳しくは、入力する信号電圧を0～3Vとして、電源電圧の振幅を増加していき、何Vまで正常に動作するのかを測定した結果について述べる。なおこのときの周波数は5MHzとした。

10

**【0195】**

従来型のシフトレジスタは、電源電圧が-1.5V～5.5Vの範囲において正常に動作し、その振幅は7.0Vであった。一方、本発明のシフトレジスタでは、電源電圧が-5.0～7.5Vの範囲において正常に動作し、その振幅は12.5Vであった。

**【0196】**

以上の結果より、本発明のシフトレジスタを用いると、従来型のシフトレジスタよりも電源電圧にマージンが生じるため、TFTの特性バラツキの影響を抑制することができる。さらに、シフトレジスタから他の回路に対して正確に信号を供給することができる。

**【0197】**

20

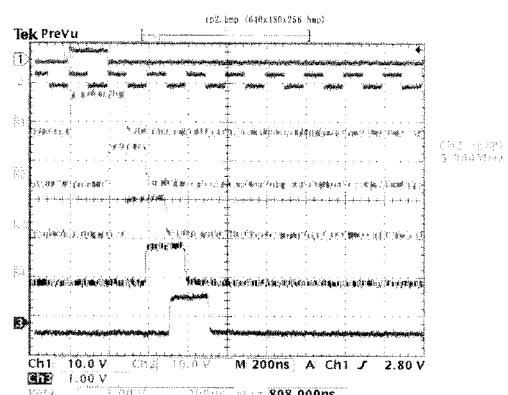

**(第11の実施の形態)**

本発明のシフトレジスタについて、上面から撮影した写真を図27に示す。具体的な仕様としては、入力信号の振幅電圧電圧は3.0V、電源電圧は8.0Vとした。

**【0198】**

また、本発明のシフトレジスタを周波数5MHzで動作させたときの波形を図28に示す。図28において、上から順にスタートパルス、クロック信号、シフトレジスタが出力する信号の波形を示す。なお、シフトレジスタが出力する信号において、1段目の波形が半パルス分大きくなっているが、これは2段目のNANDをとるためであるので、特に問題はない。

**【0199】**

30

**【発明の効果】**

シフトレジスタの電源電圧より小さな振幅電圧を有する、クロックパルス、スタートパルスをシフトレジスタに入力する。こうして、低消費電力・高周波数で動作し、電源線のノイズ、レイアウト面積の増大等の問題を解決するシフトレジスタの駆動方法が提供される。

**【0200】**

また上記駆動方法を用いる場合に、第2のクロックドインバータを構成するTFTのゲート幅を、従来と比較して大きく設定することで漏れ電流を低減する。

**【0201】**

さらに、第1のクロックドインバータに、新たにTFTを追加する。この追加したTFTのソース・ドレイン間を介して、電源電位を第1のクロックドインバータの出力端子に出力する構成とする。追加したTFTのゲート電極には、シフトレジスタの電源電圧程度の振幅電圧を有する信号が入力される。漏れ電流が問題となる場合に、追加したTFTをオフする構成とする。これによって、第1のクロックドインバータを流れる電流（漏れ電流）を遮断する。

40

**【0202】**

上記構成によって、シフトレジスタにおいて高周波数・低電源電圧動作、また、小型化を実現することができる。

**【0203】****【図面の簡単な説明】**

50

【図 1】 本発明のシフトレジスタの構成を示す回路図。

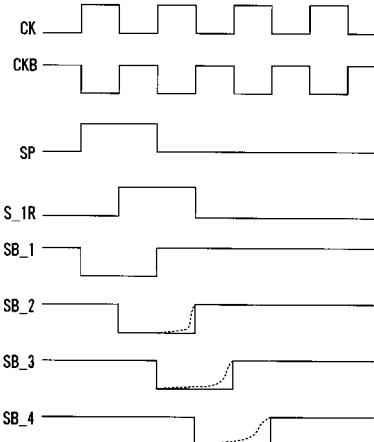

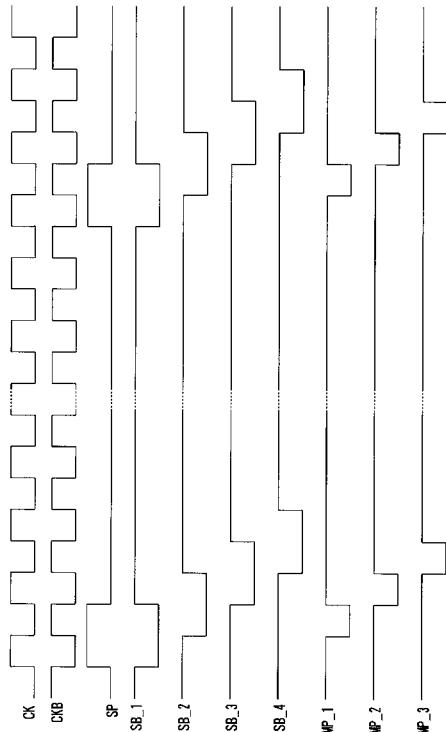

【図 2】 本発明のシフトレジスタの駆動方法を示すタイミングチャートを示す図。

【図 3】 本発明のシフトレジスタの駆動方法を示すタイミングチャートを示す図。

【図 4】 シフトレジスタの構成を示す図。

【図 5】 シフトレジスタの構成を示す図。

【図 6】 従来のシフトレジスタの駆動方法を示すタイミングチャートを示す図。

【図 7】 理想的なシフトレジスタの駆動方法を示すタイミングチャートを示す図。

【図 8】 本発明のシフトレジスタの構成を示す回路図。

【図 9】 本発明のシフトレジスタの駆動方法を示すタイミングチャートを示す図。

【図 10】 シフトレジスタの構成を示す回路図。 10

【図 11】 本発明のシフトレジスタの駆動方法を示すタイミングチャートを示す図。

【図 12】 本発明のシフトレジスタの構成を示す回路図。

【図 13】 本発明のシフトレジスタを用いた駆動回路を有する表示装置のブロック図。

【図 14】 本発明のシフトレジスタを用いた駆動回路を有する表示装置を応用した電子機器を示す図。

【図 15】 本発明のシフトレジスタの作製例を示す上面図。

【図 16】 本発明のシフトレジスタの作製例を示す上面図。

【図 17】 本発明のシフトレジスタの作製例を示す断面図。

【図 18】 本発明のシフトレジスタの構成を示す回路図。 20

【図 19】 本発明のシフトレジスタの構成を示す回路図。

【図 20】 本発明のシフトレジスタの駆動方法を示すタイミングチャートを示す図。

【図 21】 本発明のシフトレジスタの構成を示す回路図。

【図 22】 本発明のシフトレジスタの構成を示す回路図。

【図 23】 本発明のシフトレジスタの構成を示す回路図。

【図 24】 本発明のシフトレジスタの構成を示す回路図。

【図 25】 本発明のシフトレジスタの構成を示す回路図。

【図 26】 T F T のゲート幅を示す図。

【図 27】 本発明のシフトレジスタの上面写真。

【図 28】 本発明のシフトレジスタを周波数 5 MHz で動作させたときの波形を示す図。 30

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【図7】

【 図 8 】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 7 0 E

G 0 9 G 3/36

(58)調査した分野(Int.Cl. , DB名)

G11C 19/00

G11C 19/28

G02F 1/133

G09G 3/20

G09G 3/36