(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6782431号

(P6782431)

(45) 発行日 令和2年11月11日(2020.11.11)

(24) 登録日 令和2年10月22日(2020.10.22)

(51) Int.Cl.

F 1

H04N 5/355 (2011.01)

H04N 5/3745 (2011.01)H04N 5/355 630

H04N 5/3745

請求項の数 22 (全 57 頁)

(21) 出願番号 特願2016-210311 (P2016-210311)

(22) 出願日 平成28年10月27日 (2016.10.27)

(65) 公開番号 特開2017-135696 (P2017-135696A)

(43) 公開日 平成29年8月3日 (2017.8.3)

審査請求日 令和1年5月15日 (2019.5.15)

(31) 優先権主張番号 特願2016-10727 (P2016-10727)

(32) 優先日 平成28年1月22日 (2016.1.22)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 314012076

パナソニックIPマネジメント株式会社

大阪府大阪市中央区城見2丁目1番61号

(74) 代理人 100101683

弁理士 奥田 誠司

(74) 代理人 100155000

弁理士 喜多 修市

(74) 代理人 100180529

弁理士 梶谷 美道

(74) 代理人 100125922

弁理士 三宅 章子

(74) 代理人 100135703

弁理士 岡部 英隆

(74) 代理人 100188813

弁理士 川喜田 徹

最終頁に続く

(54) 【発明の名称】撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路

と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路

と、

を含む第2撮像セルと、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1信号検出回路は、前記第2信号検出回路と異なる回路構成を有する、撮像装置

。

## 【請求項 2】

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路

と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

10

20

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

を含む第2撮像セルと、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1信号検出回路は、前記第2信号検出回路と異なる回路構成を有し、

前記第1信号検出回路は、前記第2信号検出回路よりもランダムノイズを低減するよう構成されている、撮像装置。

【請求項3】

光電変換により第1の信号を生成する第1光電変換部と、

10

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

を含む第2撮像セルと、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1信号検出回路が含むトランジスタの数は、前記第2信号検出回路が含むトランジスタの数よりも多い、撮像装置。

20

【請求項4】

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

を含む第2撮像セルと、

30

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1信号検出回路が含む容量素子の数は、前記第2信号検出回路が含む容量素子の数よりも多い、撮像装置。

【請求項5】

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

40

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

を含む第2撮像セルと、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを含み、

前記第2光電変換部は、第2画素電極と、前記第2画素電極に接する第2光電変換領域とを含み、

前記第1信号検出回路は、前記第1画素電極にゲートが電気的に接続され、前記第1の

50

信号を検出する第1増幅トランジスタを含み、

前記第2信号検出回路は、前記第2画素電極にゲートが電気的に接続され、前記第2の信号を検出する第2増幅トランジスタを含み、

前記第1増幅トランジスタのゲート幅は、前記第2増幅トランジスタのゲート幅よりも大きい、撮像装置。

【請求項6】

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

を含む第2撮像セルと、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを含み、

前記第2光電変換部は、第2画素電極と、前記第2画素電極に接する第2光電変換領域とを含み、

前記第1信号検出回路は、前記第1画素電極にソースおよびドレインの一方が電気的に接続され、前記第1の信号をリセットする第1リセットトランジスタを含み、

前記第2信号検出回路は、前記第2画素電極にソースおよびドレインの一方が電気的に接続され、前記第2の信号をリセットする第2リセットトランジスタを含み、

第1リセットトランジスタのゲート長は、第2リセットトランジスタのゲート長よりも大きい、撮像装置。

【請求項7】

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

を含む第2撮像セルと、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1信号検出回路は、前記第2信号検出回路と異なる回路構成を有し、

前記第2光電変換部は、第2画素電極と、前記第2画素電極に接する第2光電変換領域とを含み、

前記第2信号検出回路は、前記第2画素電極に電気的に接続され前記第2の信号を蓄積する第1容量素子を含む、撮像装置。

【請求項8】

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

10

20

30

40

50

を含む第2撮像セルと、

反転増幅器を含む第1フィードバック回路と、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1信号検出回路は、前記第2信号検出回路と異なる回路構成を有し、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、

前記第1信号検出回路は、前記第1画素電極にゲートが電気的に接続され、前記第1の信号を検出する第1増幅トランジスタと、前記第1画素電極にソースおよびドレインの一方が電気的に接続され、前記第1の信号をリセットする第1リセットトランジスタと、を含み、

前記第1フィードバック回路は、前記第1増幅トランジスタ、前記反転増幅器、および前記第1リセットトランジスタを介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、撮像装置。

**【請求項9】**

前記第1信号検出回路は、一端が前記第1画素電極に電気的に接続された第1容量素子と、前記第1容量素子よりも容量値が大きく、一端が前記第1容量素子の他端に電気的に接続され、他端が基準電位に設定された第2容量素子と、ソースおよびドレインの一方が前記第1容量素子の前記他端に接続された第1帯域制御トランジスタと、をさらに含み、

前記第1フィードバック回路は、前記第1増幅トランジスタ、前記反転増幅器、前記第1帯域制御トランジスタ、および前記第1容量素子を介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、請求項8に記載の撮像装置。

**【請求項10】**

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの前記一方に電気的に接続されている、請求項9に記載の撮像装置。

**【請求項11】**

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されている、請求項9に記載の撮像装置。

**【請求項12】**

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

を含む第2撮像セルと、

第1フィードバック回路と、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1信号検出回路は、前記第2信号検出回路と異なる回路構成を有し、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、

前記第1信号検出回路は、前記第1画素電極にゲートが電気的に接続され、前記第1の信号を検出する第1増幅トランジスタと、前記第1画素電極にソースおよびドレインの一方が電気的に接続され、前記第1の信号をリセットする第1リセットトランジスタと、一端が前記第1画素電極に電気的に接続された第1容量素子と、前記第1容量素子よりも容量値が大きく、一端が前記第1容量素子の他端に電気的に接続され、他端が基準電位に設

10

20

30

40

50

定された第2容量素子と、ソースおよびドレインの一方が前記第1容量素子の前記他端に接続された第1帯域制御トランジスタと、を含み、

前記第1増幅トランジスタのソースおよびドレインの一方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されており、

前記第1フィードバック回路は、前記第1増幅トランジスタ、前記第1帯域制御トランジスタ、および前記第1容量素子を介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、撮像装置。

【請求項13】

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの前記一方電気的に接続されている、請求項12に記載の撮像装置。 10

【請求項14】

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されている、請求項12に記載の撮像装置。

【請求項15】

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

前記第2光電変換部に電気的に接続され、前記第2の信号を検出する第2信号検出回路と、

を含む第2撮像セルと、

第1フィードバック回路と、

を備え、

前記第1撮像セルの感度は、前記第2撮像セルの感度よりも高く、

前記第1信号検出回路は、前記第2信号検出回路と異なる回路構成を有し、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し。 30

前記第1信号検出回路は、前記第1画素電極にゲートが電気的に接続され、前記第1の信号を検出する第1増幅トランジスタと、前記第1画素電極にソースおよびドレインの一方が電気的に接続され、前記第1の信号をリセットする第1リセットトランジスタと、一端が前記第1画素電極に電気的に接続された第1容量素子と、前記第1容量素子よりも容量値が大きく、一端が前記第1容量素子の他端に電気的に接続され、他端が基準電位に設定された第2容量素子と、ソースおよびドレインの一方が前記第1容量素子の前記他端に接続された第1帯域制御トランジスタと、ソースおよびドレインの一方が前記第1増幅トランジスタのソースおよびドレインの一方に電気的に接続された第1選択トランジスタと、を含み、

前記第1選択トランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されており。 40

前記第1フィードバック回路は、前記第1増幅トランジスタ、前記第1選択トランジスタ、前記第1帯域制御トランジスタ、および前記第1容量素子を介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、撮像装置。

【請求項16】

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの前記一方電気的に接続されている、請求項15に記載の撮像装置。

【請求項17】

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御ト 50

ランジスタのソースおよびドレインの他方に電気的に接続されている、請求項 15 に記載の撮像装置。

【請求項 18】

光電変換により第 1 の信号を生成する第 1 光電変換部と、

前記第 1 光電変換部に電気的に接続され、前記第 1 の信号を検出する第 1 信号検出回路と、

を含む第 1 撮像セルと、

光電変換により第 2 の信号を生成する第 2 光電変換部と、

前記第 2 光電変換部に電気的に接続され、前記第 2 の信号を検出する第 2 信号検出回路と、

を含む第 2 撮像セルと、

を備え、

前記第 1 撮像セルの感度は、前記第 2 撮像セルの感度よりも高く、

前記第 1 信号検出回路は、前記第 2 信号検出回路と異なる回路構成を有し、

前記第 1 光電変換部は、第 1 画素電極と、前記第 1 画素電極に接する第 1 光電変換領域とを有し、

前記第 1 信号検出回路は、前記第 1 画素電極にゲートが電気的に接続され、前記第 1 の信号を検出する第 1 増幅トランジスタと、前記第 1 画素電極にソースおよびドレインの一方が電気的に接続され、前記第 1 の信号をリセットする第 1 リセットトランジスタと、一端が前記第 1 画素電極に電気的に接続された第 1 容量素子と、前記第 1 容量素子よりも容量値が大きく、一端が前記第 1 容量素子の他端に電気的に接続され、他端が基準電位に設定された第 2 容量素子と、ソースおよびドレインの一方が前記第 1 容量素子の前記他端に接続された第 1 帯域制御トランジスタと、第 1 フィードバック回路と、を含み、

前記第 1 帯域制御トランジスタのゲートは、前記第 1 画素電極に電気的に接続されており、

前記第 1 フィードバック回路は、前記第 1 帯域制御トランジスタ、および前記第 1 容量素子を介して、前記第 1 画素電極の電位を負帰還させる帰還経路を形成する、撮像装置。

【請求項 19】

前記第 1 リセットトランジスタのソースおよびドレインの他方は、前記第 1 帯域制御トランジスタのソースおよびドレインの前記一方に電気的に接続されている、請求項 18 に記載の撮像装置。

【請求項 20】

前記第 1 リセットトランジスタのソースおよびドレインの他方は、前記第 1 帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されている、請求項 18 に記載の撮像装置。

【請求項 21】

光電変換により第 1 の信号を生成する第 1 光電変換部と、

前記第 1 光電変換部に電気的に接続され、前記第 1 の信号を検出する第 1 信号検出回路と、

を含む第 1 撮像セルと、

光電変換により第 2 の信号を生成する第 2 光電変換部と、

ソースおよびドレインの一方が前記第 2 光電変換部に電気的に接続され、ソースおよびドレインの他方が前記第 1 光電変換部に電気的に接続される第 2 リセットトランジスタと、

一端が前記第 2 光電変換部に電気的に接続され、他端が基準電位に設定された第 1 容量素子と、

を含む第 2 撮像セルと、

を備える、撮像装置。

【請求項 22】

前記第 1 信号検出回路および第 2 信号検出回路は、それぞれが含むトランジスタの数が

10

20

30

40

50

互いに異なるか、あるいは、それが含む容量素子の数が互いに異なるかの少なくとも

いずれか一方である、請求項 1 に記載の撮像装置。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は撮像装置に関する。

【背景技術】

【0002】

自然界に存在する被写体のダイナミックレンジは広い。例えば車載用の撮像装置には、被写体の明るさが刻々と変化するので、明るい被写体と暗い被写体とを同時に撮像すること（広ダイナミックレンジ）が求められる。広ダイナミックレンジを実現するために、例えば、以下のような方法が提案されている。 10

【0003】

特許文献 1 および 2 に開示された撮像装置では、シリコンフォトダイオードが用いられる。特許文献 1 では、露光時間（以下、「蓄積時間」と称する場合がある。）が互いに異なる画像を合成することによって広いダイナミックレンジを得ることができる。その手法はすでに実用化に至っている。また、特許文献 2 では、1 画素内に配置された感度の異なる複数の撮像セルから得られる画像を合成してダイナミックレンジを拡大する。

【0004】

特許文献 3 は、広ダイナミックレンジを阻害するシリコンフォトダイオードの代わりに、光電変換膜を有する積層型センサを提案している。 20

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開昭 62-108678 号公報

【特許文献 2】特開 2008-99073 号公報

【特許文献 3】特開 2007-59465 号公報

【特許文献 4】特開 2012-19167 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した従来の撮像装置では、さらなる広ダイナミックレンジ撮影の向上が求められていた。本願の限定的ではないある例示的な一実施の形態は、広ダイナミックレンジ撮影を行うことが可能な撮像装置およびカメラシステムを提供する。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本開示の一態様による撮像装置は、光電変換により第 1 の信号を生成する第 1 光電変換部と、前記第 1 光電変換部に電気的に接続され、前記第 1 の信号を検出する第 1 信号検出回路と、を含む第 1 撮像セルと、光電変換により第 2 の信号を生成する第 2 光電変換部と、前記第 2 光電変換部に電気的に接続され、前記第 2 の信号を検出する第 2 信号検出回路と、を含む第 2 撮像セルと、を備え、前記第 1 撮像セルの感度は、前記第 2 撮像セルの感度よりも高く、前記前記第 1 信号検出回路は、前記第 2 信号検出回路と異なる回路構成を有する、撮像装置。 40

【0008】

包括的または具体的な態様は、素子、デバイス、装置、システム、集積回路または方法で実現されてもよい。また、包括的または具体的な態様は、素子、デバイス、装置、システム、集積回路および方法の任意の組み合わせによって実現されてもよい。

【0009】

開示された実施形態の追加的な効果および利点は、明細書および図面から明らかになる。効果および / または利点は、明細書および図面に開示の様々な実施形態または特徴によ 50

って個々に提供され、これらの1つ以上を得るために全てを必要とはしない。

【発明の効果】

【0010】

本開示の一態様によれば、広ダイナミックレンジ撮影を行うことが可能な撮像装置およびカメラシステムを提供できる。

【図面の簡単な説明】

【0011】

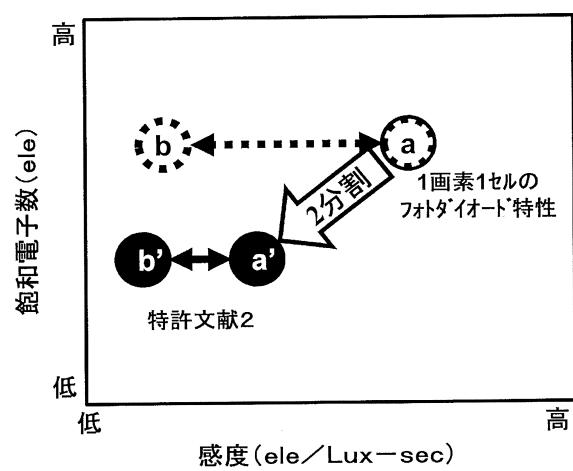

【図1】図1は、従来の撮像セル特性と、望ましい撮像セル特性とを示す図である。

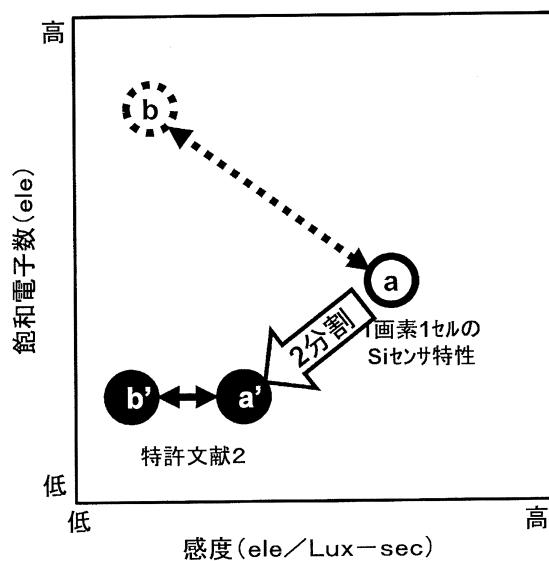

【図2】図2は、従来の撮像セル特性と、さらに望ましい撮像セル特性とを示す図である。

10

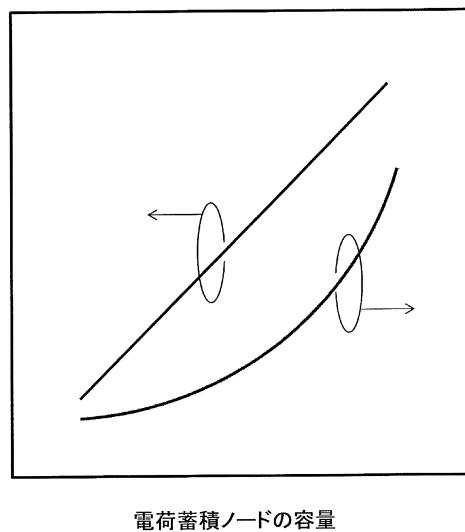

【図3】図3は、電荷蓄積ノードの容量と、飽和電子数(  $e_{1e}$  )およびランダムノイズ(  $e_{1e}$  )との関係を模式的に示す図である。

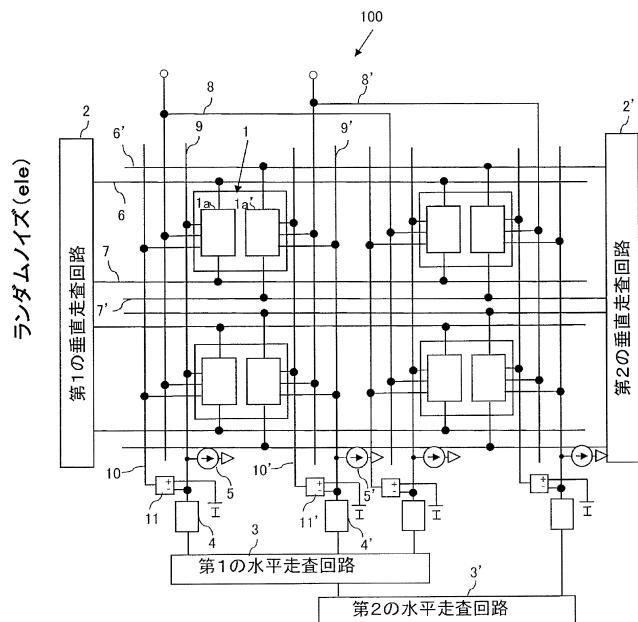

【図4】図4は、撮像装置100の構造の一例を模式的に示しているブロック図である。

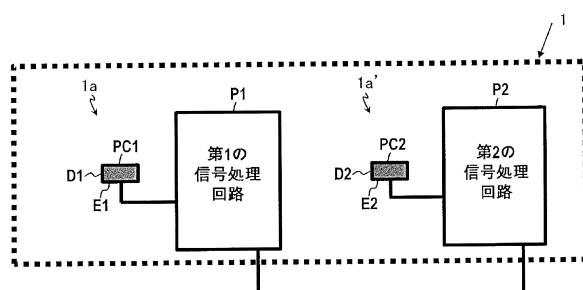

【図5】図5は、単位画素1における第1信号処理回路P1および第2信号処理回路P2を示す模式図である。

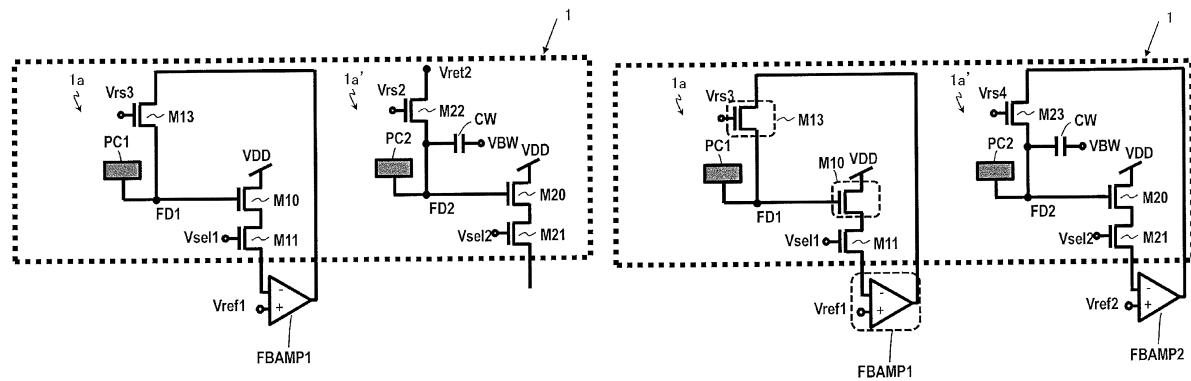

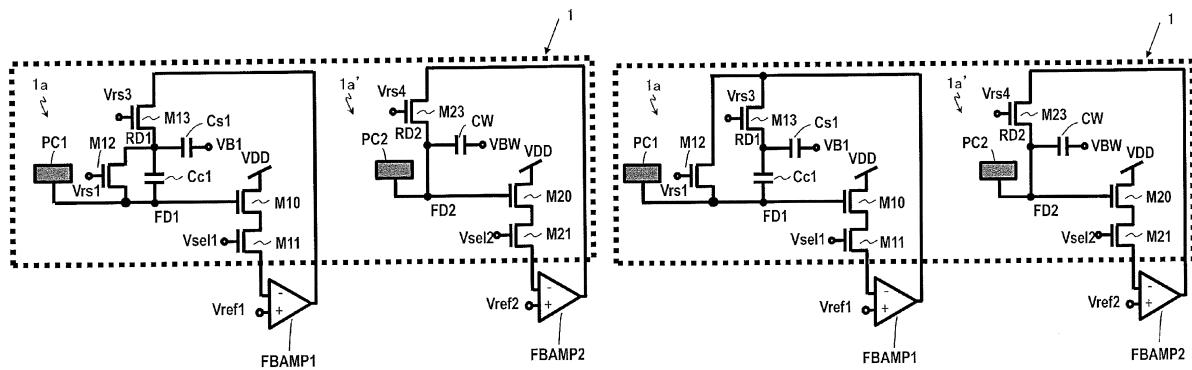

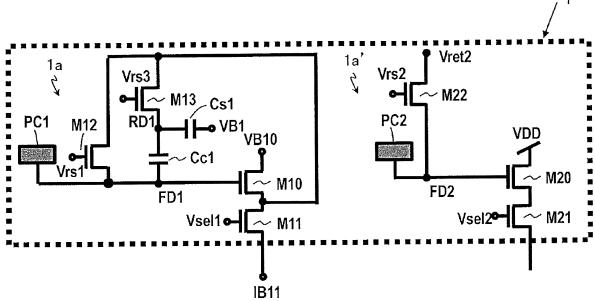

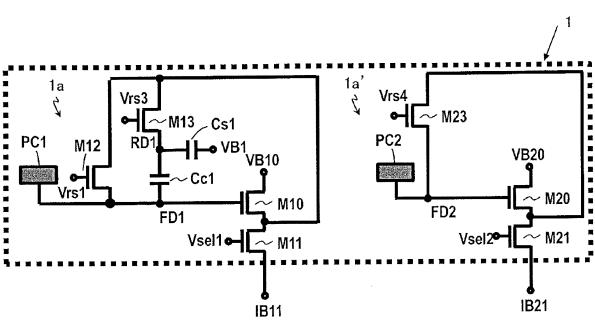

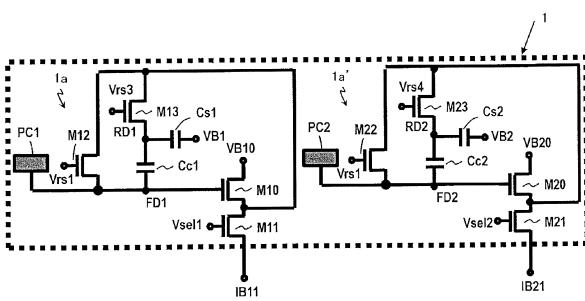

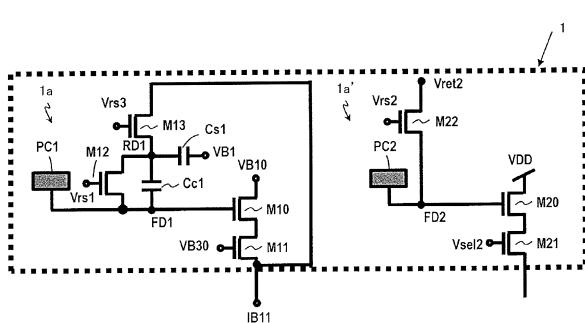

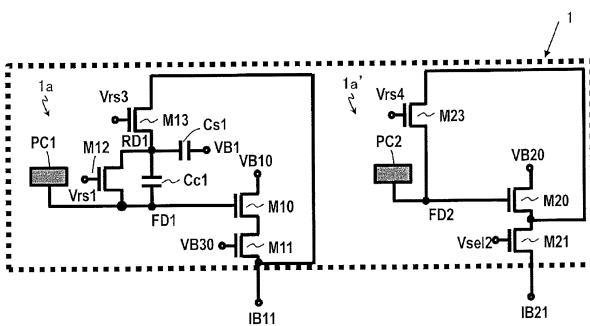

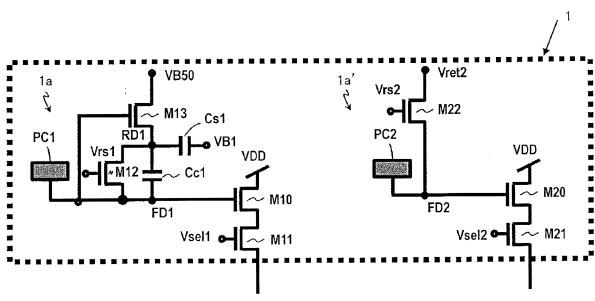

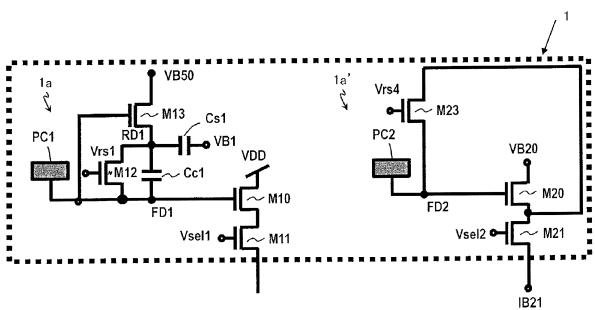

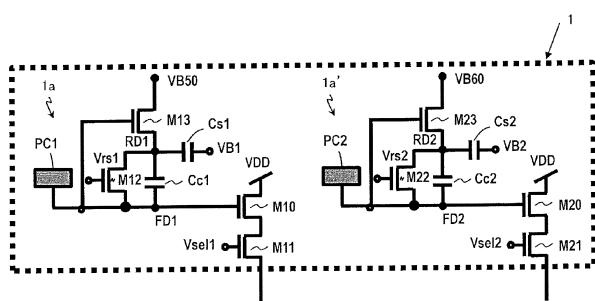

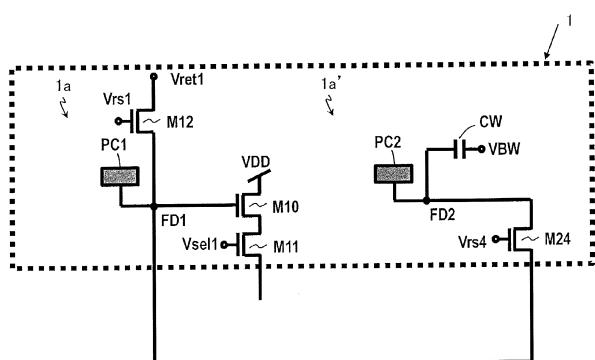

【図6A】図6Aは、例示的な第1の実施形態による単位画素1の回路構成を示す模式図である。

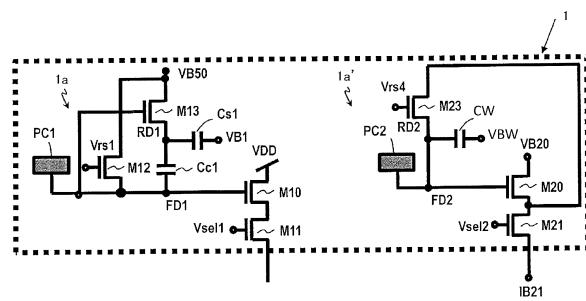

【図6B】図6Bは、例示的な第1の実施形態による単位画素1の他の回路構成を示す模式図である。

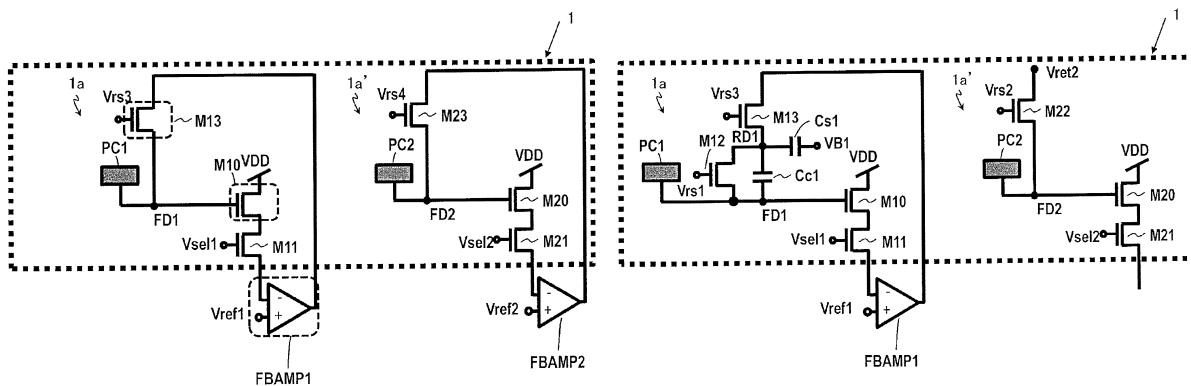

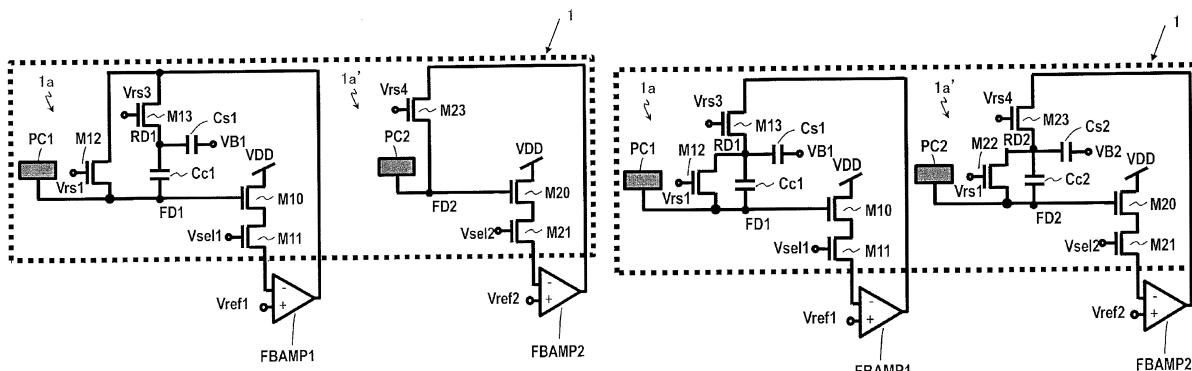

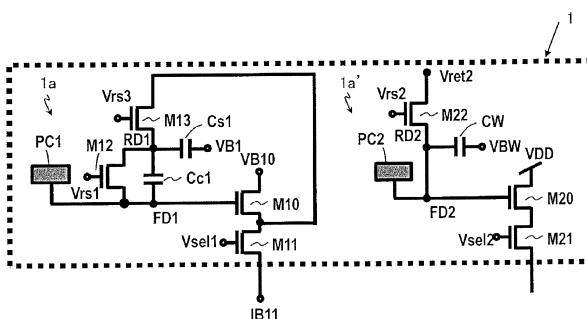

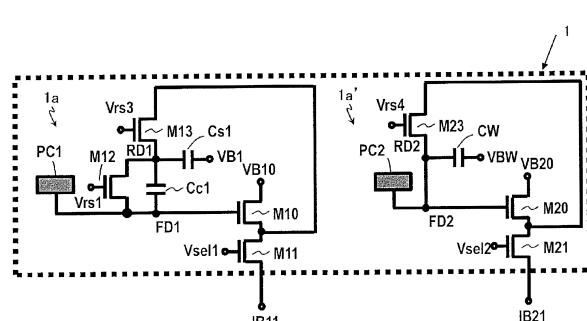

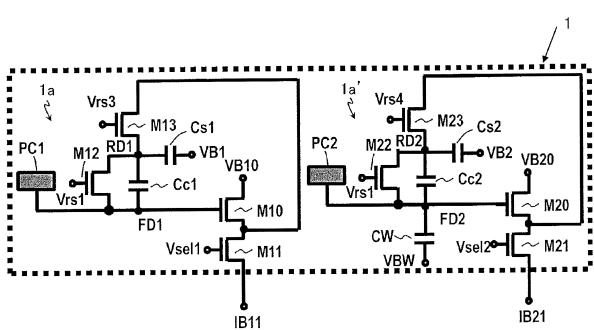

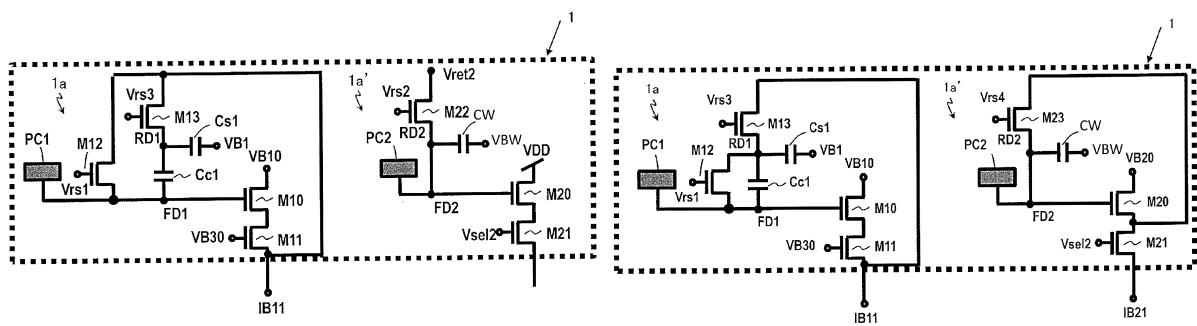

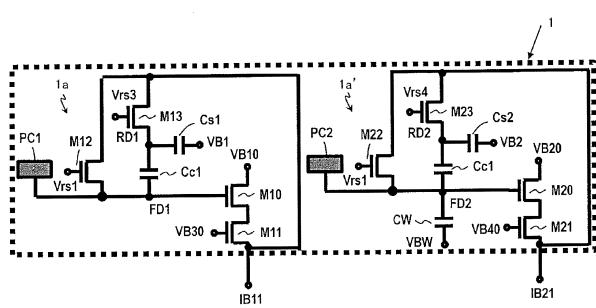

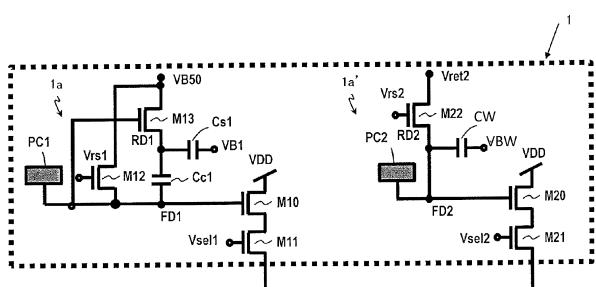

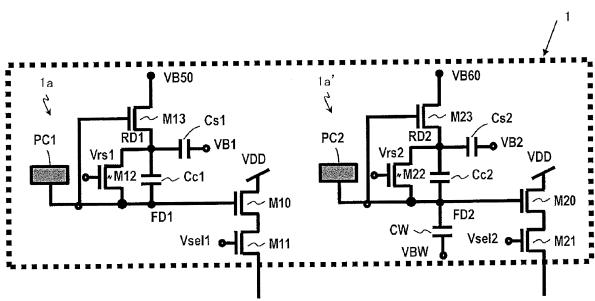

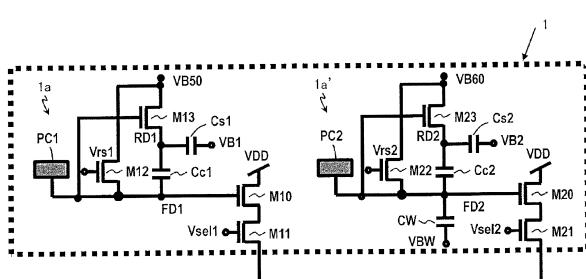

【図7】図7は、例示的な第2の実施形態による単位画素1の回路構成を示す模式図である。

20

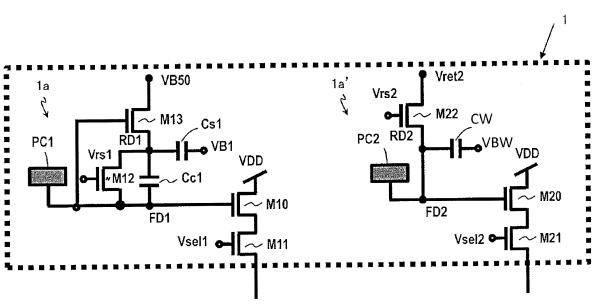

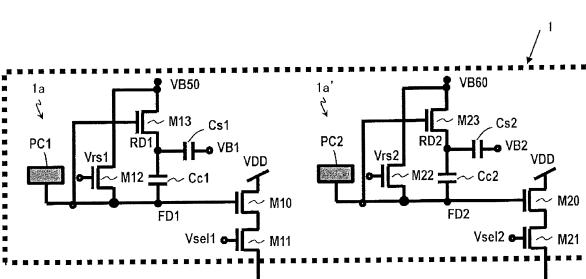

【図8】図8は、例示的な第2の実施形態による単位画素1の他の回路構成を示す模式図である。

【図9A】図9Aは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9B】図9Bは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9C】図9Cは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9D】図9Dは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

30

【図9E】図9Eは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9F】図9Fは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9G】図9Gは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9H】図9Hは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9I】図9Iは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

40

【図9J】図9Jは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9K】図9Kは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9L】図9Lは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9M】図9Mは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図9N】図9Nは、例示的な第2の実施形態による単位画素1のさらなる他の回路構成

50

を示す模式図である。

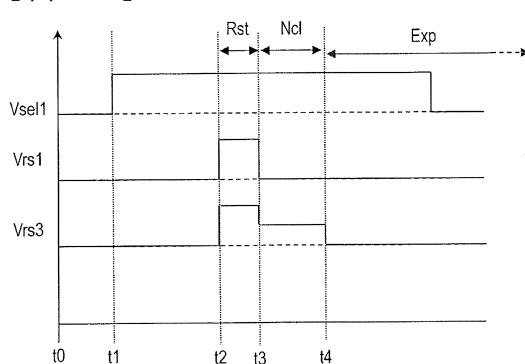

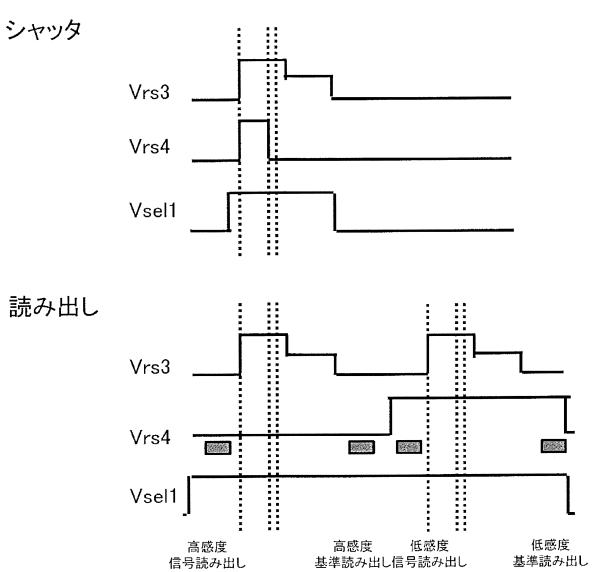

【図10】図10は、例示的な第2の実施の形態による第1撮像セル1aの動作タイミングの一例を示すタイミングチャートである。

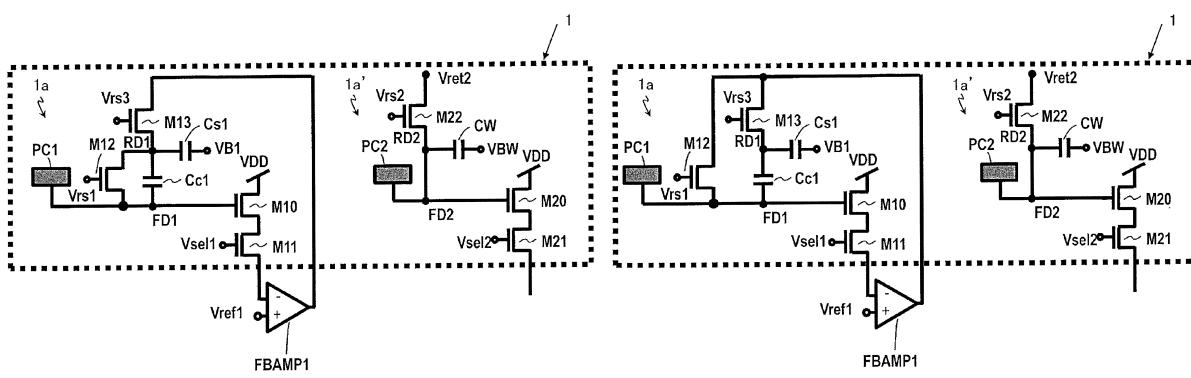

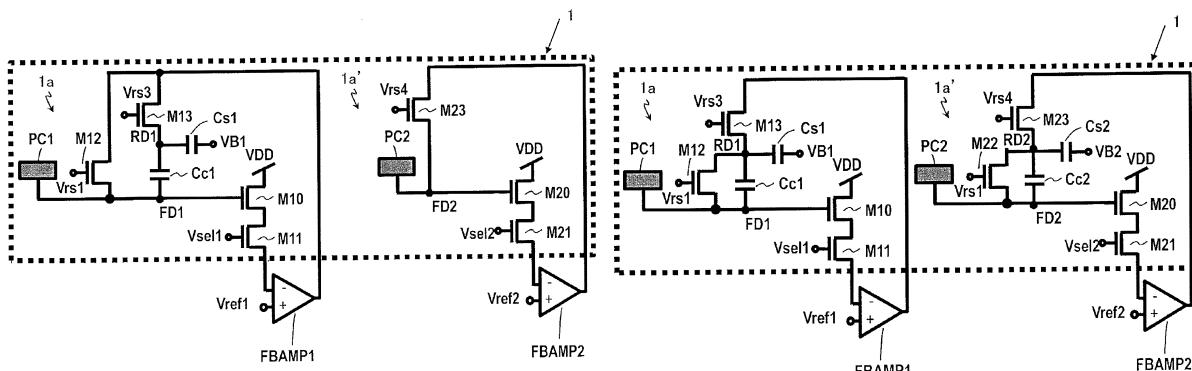

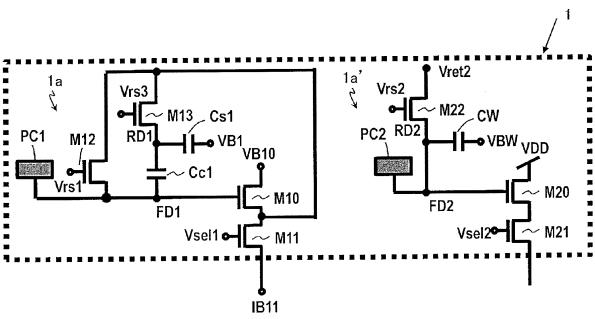

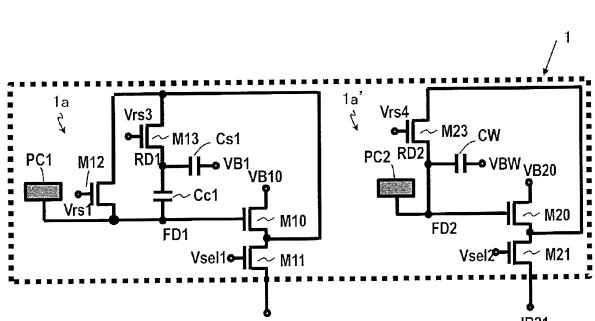

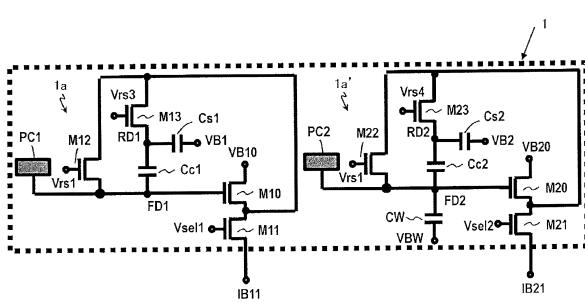

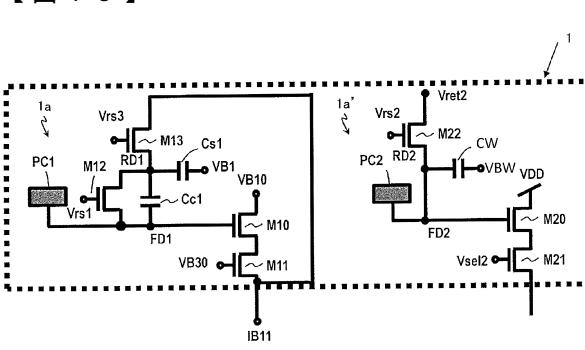

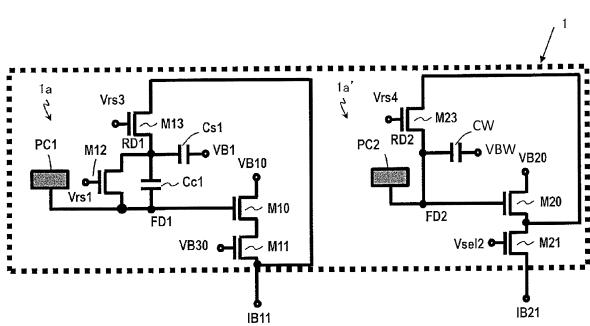

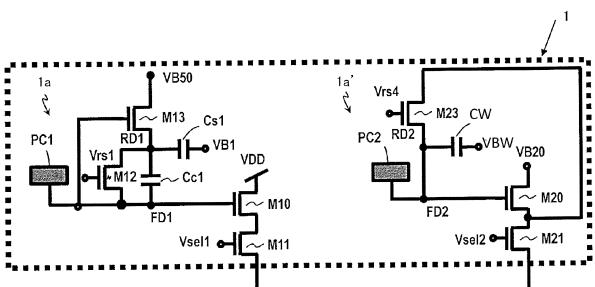

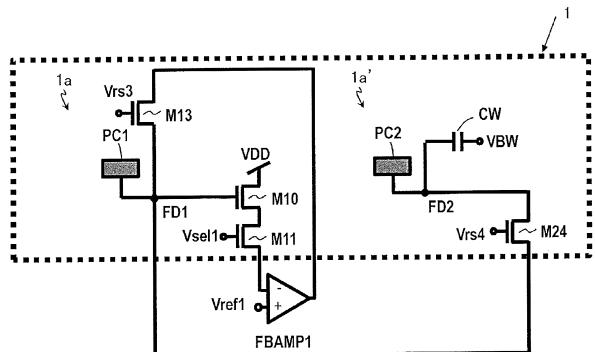

【図11】図11は、例示的な第3の実施の形態による単位画素1の回路構成を示している。

【図12】図12は、例示的な第3の実施の形態による単位画素1の他の回路構成を示している。

【図13】図13は、例示的な第3の実施の形態による単位画素1の他の回路構成を示している。

【図14A】図14Aは、例示的な第3の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。 10

【図14B】図14Bは、例示的な第3の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図14C】図14Cは、例示的な第3の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図14D】図14Dは、例示的な第3の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図14E】図14Eは、例示的な第3の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図14F】図14Fは、例示的な第3の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。 20

【図14G】図14Gは、例示的な第3の実施形態による回路構成のさらなる他の回路構成を示す模式図である。

【図14H】図14Hは、例示的な第3の実施形態による回路構成のさらなる他の回路構成を示す模式図である。

【図14I】図14Iは、例示的な第3の実施形態による回路構成のさらなる他の回路構成を示す模式図である。

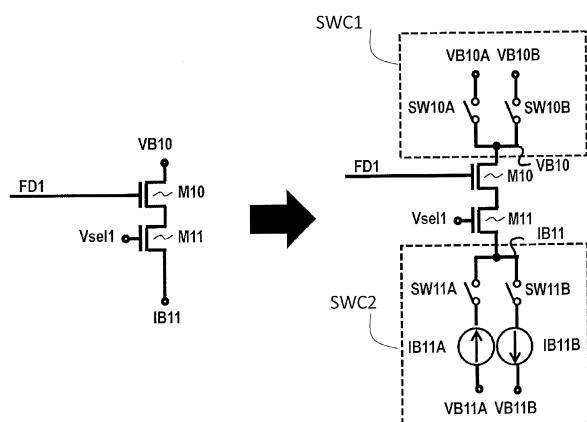

【図15】図15は、第1撮像セル1aの第1信号処理回路P1の一部を示す模式図である。

【図16】図16は、例示的な第3の実施の形態による第1撮像セル1aの動作タイミングの一例を示すタイミングチャートである。 30

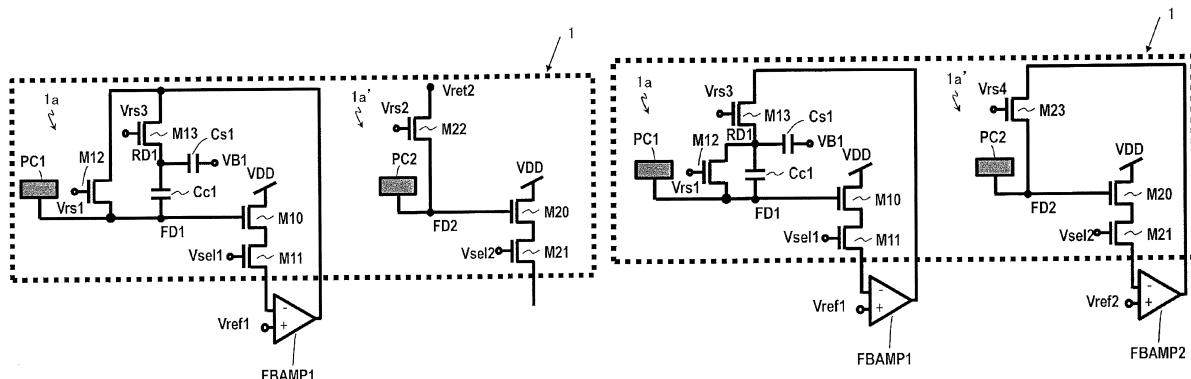

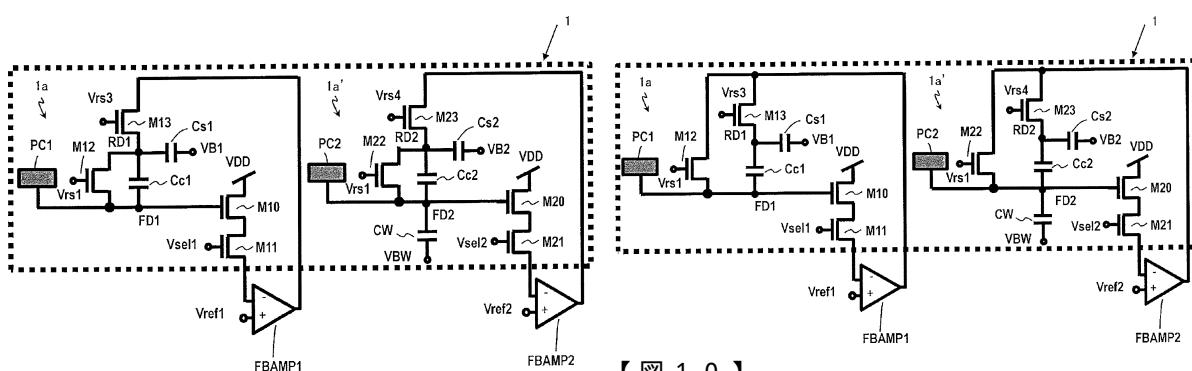

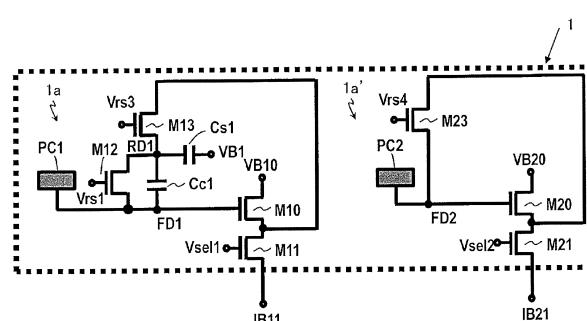

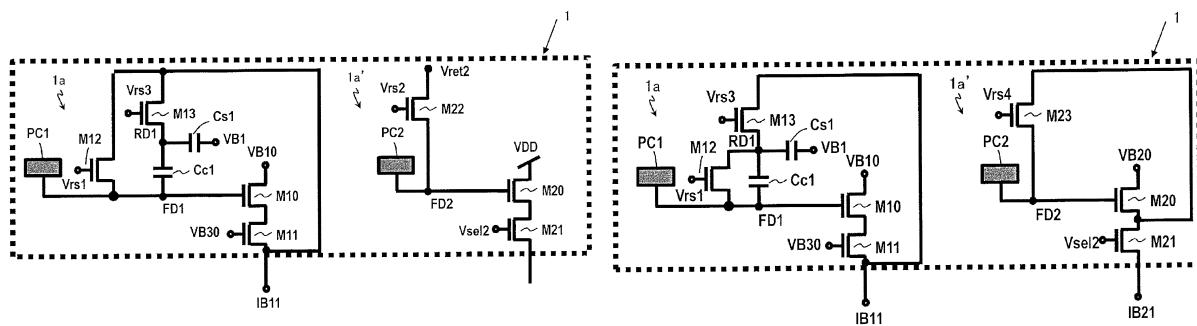

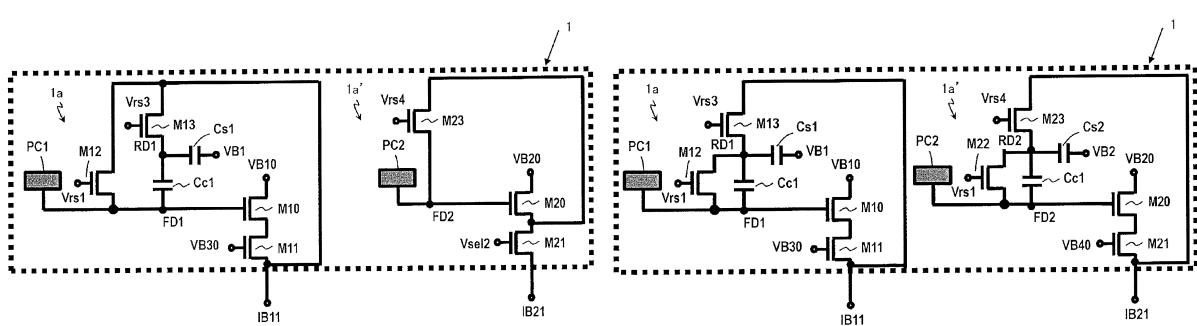

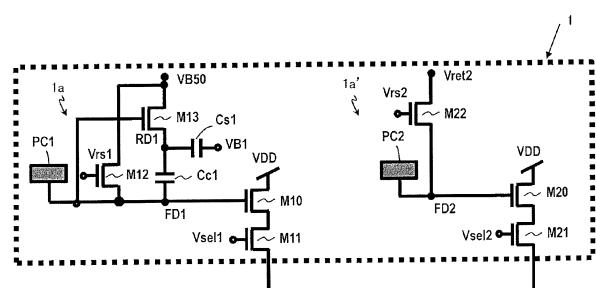

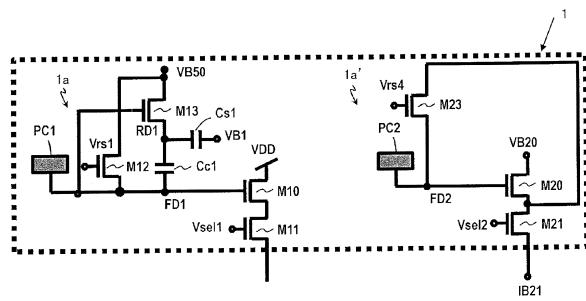

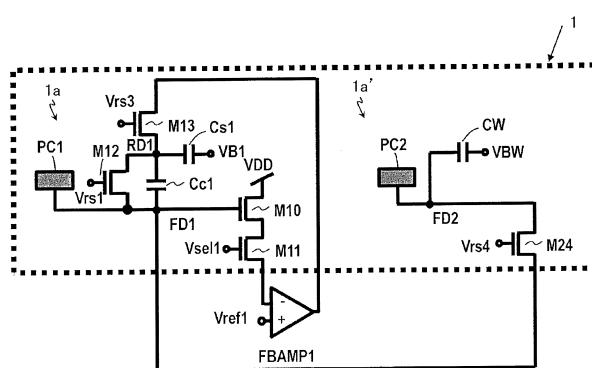

【図17】図17は、例示的な第4の実施形態による単位画素1の回路構成を示す模式図である。

【図18】図18は、例示的な第4の実施形態による単位画素1の他の回路構成を示す模式図である。

【図19】図19は、例示的な第4の実施形態による単位画素1の他の回路構成を示す模式図である。

【図20A】図20Aは、例示的な第4の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図20B】図20Bは、例示的な第4の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。 40

【図20C】図20Cは、例示的な第4の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図20D】図20Dは、例示的な第4の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図20E】図20Eは、例示的な第4の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図20F】図20Fは、例示的な第4の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図20G】図20Gは、例示的な第4の実施形態による回路構成のさらなる他の回路構

50

成を示す模式図である。

【図20H】図20Hは、例示的な第4の実施形態による回路構成のさらなる他の回路構成を示す模式図である。

【図20I】図20Iは、例示的な第4の実施形態による回路構成のさらなる他の回路構成を示す模式図である。

【図21】図21は、例示的な第5の実施形態による単位画素1の回路構成を示す模式図である。

【図22】図22は、例示的な第5の実施形態による単位画素1の他の回路構成を示す模式図である。

【図23】図23は、例示的な第5の実施形態による単位画素1の他の回路構成を示す模式図である。 10

【図24A】図24Aは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図24B】図24Bは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図24C】図24Cは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図24D】図24Dは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図24E】図24Eは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。 20

【図24F】図24Fは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図24G】図24Gは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図24H】図24Hは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図24I】図24Iは、例示的な第5の実施形態による単位画素1のさらなる他の回路構成を示す模式図である。

【図25】図25は、例示的な第6の実施形態による回路構成を示す模式図である。 30

【図26A】図26Aは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。

【図26B】図26Bは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。

【図26C】図26Cは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。

【図26D】図26Dは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。

【図26E】図26Eは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。 40

【図26F】図26Fは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。

【図26G】図26Gは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。

【図26H】図26Hは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。

【図26I】図26Iは、例示的な第6の実施形態による回路構成のさらなるバリエーションを示す模式図である。

【図27】図27は、例示的な第6の実施形態による、第1帯域制御トランジスタM13がある場合の駆動のタイミング例を示すタイミングチャートである。 50

【図28】図28は、例示的な第6の実施形態による、第1帯域制御トランジスタM13がない場合の駆動のタイミング例を示すタイミングチャートである。

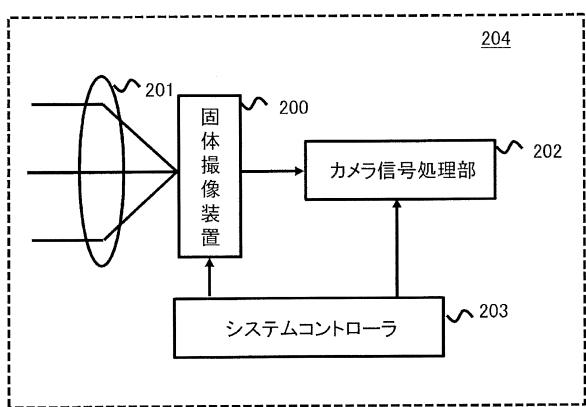

【図29】図29は、例示的な第7の実施形態によるカメラシステム204のシステム構成を示すシステム構成図である。

【発明を実施するための形態】

【0012】

まず、本願発明者が考察した従来技術の問題点を説明する。

【0013】

特許文献1に開示された画像合成では、複数の画像データが時系列に取得される。そのため、一枚の合成画像を得るには通常の撮像時間の数倍の時間が必要となる。また、時間差のある画像を合成するので画像の同時性が損なわれ、動きのある被写体の画像に乱れが生じてしまう。

【0014】

特許文献2では、感度および飽和電子数が同一である、同じ大きさの複数のフォトダイオードを用いている。それぞれのフォトダイオードに入射する光量を大小に分けるオンチップトップレンズを有するオンチップ構造が採用されている。この構成によれば、複数の撮像セルの間では実効的に感度が異なるように見せかけられる。1画素内に2つのセルが搭載されているので、同時に撮像が可能となり、画像の同時性は確保される。

【0015】

一方、1画素内に2つのセルを配置する必要があるので、フォトダイオードの面積は従来と比べて1/2以下にならざるを得なくなる。フォトダイオードの面積と、感度または飽和電子数とは、比例関係にある。その結果、フォトダイオードの面積が1/2以下になれば、感度および飽和電子数も従来の1/2以下となる。

【0016】

図1は、従来の撮像セル特性と、望ましい撮像セル特性とを模式的に示している。横軸は感度を示し、縦軸は飽和電子数を示している。ここでいう、感度とは、撮像装置（具体的にはイメージセンサ）の特性を示す指標の1つであり、入射光に対して撮像セルに発生する電荷（電子正孔対）の数を意味する。感度は一般的に単位（e1e/Lux-sec）で表される。また、飽和電子数とは、撮像セルに蓄積される電子数の許容量を意味し、単位（e1e）で表される。感度および飽和電子数は原則、光電変換素子の有効面積に比例する。ただし、感度は、マイクロレンズの設計にも依存する。

【0017】

以下、単一の画素内に1つの撮像セルを有するセルを「通常セル」と称する。広ダイナミックレンジ撮影では、単一の画素内の2つの撮像セルは、（a）通常セルと同程度の感度および飽和電子数である撮像セル特性と、（b）飽和電子数は通常セルと同程度であり、感度は通常セルと比べて低い撮像セル特性とを備えていることが望ましい。図中の「a」および「b」はその望ましい組み合わせを示している。

【0018】

図1中の「a」および「b」は、特許文献2における2つの撮像セルの組み合わせを示している。上述したとおり、各撮像セル（フォトダイオード）の面積は、通常セルと比べて1/2以下になる。そのため、各撮像セルの感度は低下し、飽和電子数も減少する。これは、望ましい特性から乖離してしまうことを意味している。このように、特許文献2における撮像セルの特性は、要求される特性と比べると著しく劣る。

【0019】

図2は、従来の撮像セル特性と、さらに望ましい撮像セル特性とを模式的に示している。感度を低下させることにより、入射光の光量が高いときに発生し得る飽和が緩和される。加えて、飽和電子数そのものを増大できれば、ダイナミックレンジはさらに拡大される。

【0020】

表1は、フォトダイオードを有する従来のSiセンサと特許文献3に開示された光電変

10

20

30

40

50

換膜を有する積層型センサとを比較して素子機能およびセンサ性能を決定するそれぞれの要因を表している。表1から分かるように、従来のSiセンサでは、感度・飽和電子数はいずれもフォトダイオードの性能によって決定される。これに対して、光電変換膜を有する積層型センサでは、感度は光電変換膜の面積とその量子効率に依存し、飽和電子数は電荷蓄積ノードの容量に依存する。これによると、電荷蓄積ノードの容量を増大すればする程、飽和電子数はますます増加する。しかしながら、電荷蓄積ノードの容量の増大には大きな副作用がある。

## 【0021】

【表1】

|       |                        | 従来Siセンサ              | 光電変換膜センサ          |

|-------|------------------------|----------------------|-------------------|

| 素子機能  | 光電変換                   | フォトダイオード             | 光電変換膜             |

|       | 電荷蓄積                   | フォトダイオード             | 電荷蓄積ノード           |

|       | 信号読み出し<br>(増幅Trのゲート電圧) | フローティングディフィージョン      | 電荷蓄積ノード           |

| センサ性能 | 感度                     | フォトダイオードの<br>量子効率に依存 | 光電変換膜の<br>量子効率に依存 |

|       | 飽和電子数                  | フォトダイオードの<br>容量に依存   | 電荷蓄積ノードの<br>容量に依存 |

10

20

30

## 【0022】

図3は、電荷蓄積ノードの容量と、飽和電子数( $e_{1e}$ )およびランダムノイズ( $e_{1e}$ )との関係を模式的に示している。横軸は電荷蓄積ノードの容量を示し、縦軸は飽和電子数およびランダムノイズを示している。電荷蓄積ノードの容量を大きくすることにより、飽和電子数を増大させることは可能であるが、それと同時にランダムノイズが増大してしまうという課題が発生する。

## 【0023】

ランダムノイズには、電荷検出回路が電荷蓄積ノードに蓄積された電荷を読み出すとき、つまり転送するときに発生するノイズ、および電荷検出回路が電荷蓄積ノードに蓄積された電荷をリセットするときに発生するノイズ(以下、「kTCノイズ」と呼ぶ。)が含まれる。電荷蓄積ノードを大容量化すると、飽和電子数は増大できるが、単位体積当たりの蓄積電荷数の変化量に対する電荷蓄積ノード電圧の変化量の割合は小さくなる。電荷検出回路で発生するノイズは電圧ノイズであり、その結果として電荷数に換算されたノイズは大きくなってしまう。

## 【0024】

また、シリコンフォトダイオードを光電変換に用いるセンサでは、電荷の完全転送がなされるので、CDS(相関2重サンプリング)がkTCノイズの抑制に効果的である。これに対し、光電変換膜を用いる積層型センサでは、電荷の完全転送はできないので、CDSを用いてkTCノイズをキャンセルできない。そのため、例えば特許文献4で提案されているようなフィードバックを用いたノイズキャンセルが必要である。しかし、上述したように、電荷蓄積ノードを大容量化すると、単位体積当たりの蓄積電荷数の変化量に対する電荷蓄積ノード電圧の変化量の割合は小さくなるので、フィードバックによってkTCノイズが十分に抑制される効果が得られなくなる。

## 【0025】

このような課題に鑑み、本願発明者は、新規な構造を備えた撮像装置に想到した。本開示の一態様の概要は以下の項目に記載のとおりである。

40

50

## 【0026】

## 〔項目1〕

第1光電変換部と、

前記第1光電変換部に電気的に接続された第1信号処理回路と、

を有する第1撮像セルと、

第2光電変換部と、

前記第2光電変換部に電気的に接続された第2信号処理回路と、

を有する第2撮像セルと、

を備え、

前記第1信号処理回路は、前記第1光電変換部で発生した電気信号を検出する第1信号検出回路と、第1容量素子と前記第1容量素子よりも容量値が大きい第2容量素子とが直列に接続された容量回路と、前記第1光電変換部で発生した前記電気信号を負帰還させる第1帰還経路を形成する第1フィードバック回路と、を含み、 10

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、

前記第1信号検出回路は、前記第1画素電極にゲートが接続され、前記第1画素電極の電位に応じた信号電圧を增幅して出力する第1トランジスタと、前記第1画素電極にソースおよびドレインの一方が接続された第2トランジスタと、を含み、

前記第1フィードバック回路は、前記第1光電変換部で発生した前記電気信号を前記第2トランジスタの前記ソースおよび前記ドレインの他方に負帰還させ、 20

前記容量回路は、前記第1画素電極と基準電位との間に設けられており、

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路と、一端が前記第2光電変換部に電気的に接続された第3容量素子と、前記電気信号を負帰還させる第2帰還経路を形成する第2フィードバック回路と、を含み、

前記第2光電変換部は、第2画素電極と、前記第2画素電極に接する第2光電変換領域とを有し、

前記第2信号検出回路は、前記第2画素電極にゲートが接続され、前記第2画素電極の電位に応じた信号電圧を增幅して出力する第3トランジスタと、前記第2画素電極にソースおよびドレインの一方が接続された第4トランジスタとを含み、

前記第2フィードバック回路は、前記第2光電変換部で発生した前記電気信号を前記第4トランジスタの前記ソースおよび前記ドレインの他方に負帰還させている、撮像装置。 30

## 【0027】

項目1に記載の撮像装置によると、同一画素内の2つの撮像セルを用いて高飽和および低感度の撮像が可能になる。

## 【0028】

## 〔項目2〕

第1光電変換部と、

前記第1光電変換部に電気的に接続された第1信号処理回路と、

を有する第1撮像セルと、

第2光電変換部と、

前記第2光電変換部に電気的に接続された第2信号処理回路と、

を有する第2撮像セルと、

を備え、

前記第1信号処理回路は、前記第1光電変換部で発生した電気信号を検出する第1信号検出回路と、第1容量素子と前記第1容量素子よりも容量値が大きい第2容量素子とが直列に接続された容量回路と、前記第1光電変換部で発生した前記電気信号を負帰還させる第1帰還経路を形成する第1フィードバック回路と、を含み、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、

前記第1信号検出回路は、前記第1画素電極にゲートが接続され、前記第1画素電極の 40

50

電位に応じた信号電圧を増幅して出力する第1トランジスタと、前記第1画素電極にソースおよびドレインの一方が接続された第2トランジスタと、前記第2トランジスタのドレインおよびソースの他方にソースおよびドレインの一方が接続された第5トランジスタと、を含み、

前記第1フィードバック回路は、前記第1光電変換部で発生した前記電気信号を前記第5トランジスタの前記ソースおよび前記ドレインの他方に負帰還させ、

前記容量回路は、前記第1画素電極と基準電位との間に設けられており、

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路と、一端が前記第2光電変換部に電気的に接続された第3容量素子と、前記電気信号を負帰還させる第2帰還経路を形成する第2フィードバック回路と、を含み、

前記第2光電変換部は、第2画素電極と、前記第2画素電極に接する第2光電変換領域とを有し、

前記第2信号検出回路は、前記第2画素電極にゲートが接続され、前記第2画素電極の電位に応じた信号電圧を増幅して出力する第3トランジスタと、前記第2画素電極にソースおよびドレインの一方が接続された第4トランジスタとを含み、

前記第2フィードバック回路は、前記第2光電変換部で発生した前記電気信号を前記第4トランジスタの前記ソースおよび前記ドレインの他方に負帰還させている、撮像装置。

#### 【0029】

項目2に記載の撮像装置によると、同一画素内の2つの撮像セルを用いて高飽和および低感度の撮像が可能になる。

#### 【0030】

##### 〔項目3〕

前記第1容量素子は、前記第2トランジスタの前記ソースと前記ドレインとの間に接続されている、項目1または2に記載の撮像装置。

#### 【0031】

項目3に記載の撮像装置によると、第1撮像セルがノイズを抑制する能力を向上させることができる。

#### 【0032】

##### 〔項目4〕

前記第1フィードバック回路は、前記第1トランジスタおよび第1反転増幅器を前記第1帰還経路の一部に含み、前記第1光電変換部で発生した前記電気信号を、前記第1トランジスタおよび前記第2反転増幅器を介して、前記第2トランジスタの前記ソースおよび前記ドレインの他方に負帰還させ、

前記第2フィードバック回路は、前記第3トランジスタおよび第2反転増幅器を前記第2帰還経路の一部に含み、前記第2光電変換部で発生した前記電気信号を、前記第3トランジスタおよび前記第2反転増幅器を介して、前記第4トランジスタの前記ソースおよび前記ドレインの他方に負帰還させる、項目1から3のいずれかに記載の撮像装置。

#### 【0033】

項目4に記載の撮像装置によると、各撮像セルでランダムノイズを抑制することができる。

#### 【0034】

##### 〔項目5〕

前記第2容量素子は、前記第2トランジスタの前記ソースまたは前記ドレインに接続されている、項目1から4のいずれかに記載の撮像装置。

#### 【0035】

項目5に記載の撮像装置によると、第1撮像セルがノイズを抑制する能力を向上させることができる。

#### 【0036】

##### 〔項目6〕

前記第1および第2撮像セルを複数備え、複数の第1および第2撮像セルは1次元また

10

20

30

40

50

は2次元に配列されている、項目1から5のいずれかに記載の撮像装置。

【0037】

項目6に記載の撮像装置によると、時間ずれなく、かつ、ダイナミックレンジの広い被写体を、白飛びおよび黒潰れなく撮像できる撮像装置が提供される。

【0038】

〔項目7〕

前記複数の第1撮像セルの各々と前記複数の第2撮像セルの各々とは、互いに隣接して配置される、項目6に記載の撮像装置。

【0039】

項目7に記載の撮像装置によると、高飽和撮像および低ノイズ撮像を同一の分解能で実現できる。

【0040】

〔項目8〕

複数の画素を有する撮像装置であり、

各画素は、

第1光電変換部と、接続部分を介して、前記第1光電変換部に電気的に接続された第1信号処理回路とを有する第1撮像セルと、

第2光電変換部と、接続部分を介して、前記第2光電変換部に電気的に接続された第2信号処理回路とを有する第2撮像セルと、

を備え、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、前記第2光電変換部は、第2画素電極と、前記第2画素電極に接する第2光電変換領域とを有し、

前記第1信号処理回路と前記第2信号処理回路は、異なる回路構成を備え、前記第1信号処理回路はノイズを低減する構成を含む、撮像装置。

【0041】

〔項目9〕

前記第1信号処理回路は、前記第1光電変換部で発生した電気信号を検出する第1信号検出回路、を含み、

前記第1信号検出回路は、前記第1画素電極にゲートが接続され、前記第1画素電極の電位に応じた信号電圧を增幅して出力する第1トランジスタと、前記の第1画素電極にソースまたはドレインの一方が接続された第2トランジスタとを含み、

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路、を含み、

前記第2信号検出回路は、前記第2画素電極にゲートが接続され、前記第2画素電極の電位に応じた信号電圧を增幅して出力する第3トランジスタと、前記第2画素電極にソースまたはドレインの一方が接続された第4トランジスタとを含み、

前記第1トランジスタと前記第3トランジスタ、または、前記第2トランジスタと前記第4トランジスタのトランジスタサイズは異なる、項目8に記載の撮像装置。

【0042】

〔項目10〕

前記第1信号処理回路は、前記第1光電変換部で発生した電気信号を検出する第1信号検出回路と、前記第1光電変換部で発生した前記電気信号を負帰還させる第1の帰還経路を形成する第1フィードバック回路と、を含み、

前記第1信号検出回路は、前記第1画素電極にゲートが接続され、前記第1画素電極の電位に応じた信号電圧を增幅して出力する第1トランジスタと、前記第1画素電極にソースまたはドレインの一方が接続された第2トランジスタとを含み、

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路、を含み、

前記第2信号検出回路は、前記第2画素電極にゲートが接続され、前記第2画素電極の

10

20

30

40

50

電位に応じた信号電圧を増幅して出力する第3トランジスタと、前記第2画素電極にソースまたはドレインの一方が接続された第4トランジスタとを含む、項目8に記載の撮像装置。

#### 【0043】

##### 〔項目11〕

前記第1信号処理回路は、前記第1光電変換部で発生した電気信号を検出する第1信号検出回路と、前記第1光電変換部で発生した前記電気信号を負帰還させる第1の帰還経路を形成する第1フィードバック回路と、を含み、

前記第1信号検出回路は、前記第1画素電極にゲートが接続され、前記第1画素電極の電位に応じた信号電圧を増幅して出力する第1トランジスタと、前記第1画素電極にソースまたはドレインの一方が接続された第2トランジスタとを含み、

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路と、前記第2光電変換部で発生した前記電気信号を負帰還させる第2の帰還経路を形成する第2フィードバック回路と、を含み、

前記第2信号検出回路は、前記第2画素電極にゲートが接続され、前記第2画素電極の電位に応じた信号電圧を増幅して出力する第3トランジスタと、前記第2画素電極にソースまたはドレインの一方が接続された第4トランジスタとを含み、

前記第1トランジスタと前記第3のトランジスタ、または、前記第2トランジスタと前記第4トランジスタ2のトランジスタサイズ、または、前記第1フィードバック回路と前記第2フィードバック回路は異なる、項目8に記載の撮像装置。

#### 【0044】

##### 〔項目12〕

前記第1信号処理回路は、前記第1光電変換部で発生した電気信号を検出する第1信号検出回路と、一端が前記接続部分に電気的に接続された第1容量素子と前記第1容量素子よりも容量値が大きい第2容量素子とが直列に接続された容量回路と、前記第1光電変換部で発生した前記電気信号を負帰還させる第1の帰還経路を形成する第1フィードバック回路と、を含み、

前記第1信号検出回路は、前記第1画素電極にゲートが接続され、前記第1画素電極の電位に応じた信号電圧を増幅して出力する第1トランジスタと、前記第1画素電極にソースまたはドレインの一方が接続された第2トランジスタとを含み、

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路、を含み、

前記第2信号検出回路は、前記第2画素電極にゲートが接続され、前記第2画素電極の電位に応じた信号電圧を増幅して出力する第3トランジスタと、前記第2画素電極にソースまたはドレインの一方が接続された第4トランジスタとを含む、項目8に記載の撮像装置。

#### 【0045】

##### 〔項目13〕

前記第1信号処理回路は、前記第1光電変換部で発生した電気信号を検出する第1信号検出回路と、一端が前記接続部分に電気的に接続された第1容量素子と前記第1容量素子よりも容量値が大きい第2容量素子とが直列に接続された容量回路と、前記第1光電変換部で発生した前記電気信号を負帰還させる第1の帰還経路を形成する第1フィードバック回路と、を含み、

前記第1信号検出回路は、前記第1画素電極にゲートが接続され、前記第1画素電極の電位に応じた信号電圧を増幅して出力する第1トランジスタと、前記第1画素電極にソースまたはドレインの一方が接続された第2トランジスタとを含み、

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路と、前記第2光電変換部で発生した前記電気信号を負帰還させる第2の帰還経路を形成する第2フィードバック回路と、を含み、

前記第2信号検出回路は、前記第2画素電極にゲートが接続され、前記第2画素電極の

10

20

30

40

50

電位に応じた信号電圧を増幅して出力する第3トランジスタと、前記第2画素電極にソースまたはドレインの一方が接続された第4トランジスタとを含む、項目8に記載の撮像装置。

【0046】

〔項目14〕

前記第1信号処理回路は、前記第1光電変換部で発生した電気信号を検出する第1信号検出回路と、一端が前記接続部分に電気的に接続された第1容量素子と前記第1容量素子よりも容量値が大きい第2容量素子とが直列に接続された容量回路と、前記第1光電変換部で発生した前記電気信号を負帰還させる第1の帰還経路を形成する第1フィードバック回路と、を含み、

10

前記第1信号検出回路は、前記第1画素電極にゲートが接続され、前記第1画素電極の電位に応じた信号電圧を増幅して出力する第1トランジスタと、前記第1画素電極にソースまたはドレインの一方が接続された第2トランジスタとを含み、

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路と、一端が前記接続部分に電気的に接続された第3容量素子と前記第3容量素子よりも容量値が大きい第4容量素子とが直列に接続された容量回路と、前記第2光電変換部で発生した前記電気信号を負帰還させる第2の帰還経路を形成する第2フィードバック回路と、を含み、

20

前記第2信号検出回路は、前記第2画素電極にゲートが接続され、前記第2画素電極の電位に応じた信号電圧を増幅して出力する第3トランジスタと、前記第2画素電極にソースまたはドレインの一方が接続された第4トランジスタとを含み、

前記第1トランジスタと前記第3のトランジスタ、または、前記第2トランジスタと前記第4トランジスタのトランジスタサイズ、または、前記第1のフィードバック回路と前記第2フィードバック回路、または、第1容量素子と第3容量素子、または、第2容量素子と第4容量素子は異なる、項目8に記載の撮像装置。

【0047】

〔項目15〕

前記第2信号処理回路は、一端が前記第2光電変換部に電気的に接続された第5容量素子、を備える、項目8から14のいずれかに記載の撮像装置。

【0048】

30

〔項目16〕

前記第1容量素子は、前記第2トランジスタのソースとドレインとの間に接続されている、項目12から15のいずれかに記載の撮像装置。

【0049】

〔項目17〕

前記第2容量素子は、前記第2トランジスタのソースまたはドレインの一方と、基準電圧の間に接続されている、項目12から16のいずれかに記載の撮像装置。

【0050】

〔項目18〕

前記第3容量素子は、前記第4トランジスタのソースとドレインとの間に接続されている、項目14に記載の撮像装置。

40

【0051】

〔項目19〕

前記第4容量素子は、前記第4トランジスタのソースまたはドレインの一方と、基準電圧の間に接続されている、項目14または16から18のいずれかに記載の撮像装置。

【0052】

〔項目20〕

前記第1フィードバック回路は、前記第1トランジスタおよび第1の反転増幅器を前記第1の帰還経路の一部に含み、前記第1光電変換部で発生した前記電気信号を、前記第1トランジスタおよび前記第1反転増幅器を介して、前記第2トランジスタの前記ソース

50

またはドレインの他方に負帰還させ、

前記第2フィードバック回路は、前記第3トランジスタおよび第2反転増幅器を前記第2の帰還経路の一部に含み、前記第2光電変換部で発生した前記電気信号を、前記第3トランジスタおよび前記第2の反転増幅器を介して、前記第4トランジスタの前記ソースまたはドレインの他方に負帰還させる、項目8から19のいずれかに記載の撮像装置。

【0053】

〔項目21〕

前記第1フィードバック回路は、前記第1トランジスタを前記第1の帰還経路の一部に含み、前記第1光電変換部で発生した前記電気信号を、前記第1トランジスタを介して、第5トランジスタのソースまたはドレインの他方に負帰還させ、

10

前記第2フィードバック回路は、前記第3トランジスタを前記第2の帰還経路の一部に含み、前記第2光電変換部で発生した前記電気信号を、前記第3トランジスタを介して、第6トランジスタの前記ソースまたはドレインの他方に負帰還させる、項目8から20のいずれかに記載の撮像装置。

【0054】

〔項目22〕

前記第1フィードバック回路は、前記第1トランジスタに加え、前記第1トランジスタの出力の選択、非選択を決定する第7トランジスタを前記第1の帰還経路の一部に含み、前記第1光電変換部で発生した前記電気信号を、前記第1トランジスタ、第7トランジスタを介して、前記第1フィードバック回路の帯域制限を行う第5トランジスタのソースまたはドレインの他方に負帰還させ、

20

前記第2トランジスタに加え、前記第2トランジスタの出力の選択、非選択を決定する第8トランジスタを前記第2の帰還経路の一部に含み、前記第2光電変換部で発生した前記電気信号を、前記第2トランジスタ、第8のトランジスタを介して、前記第2フィードバック回路の帯域制限を行う第6トランジスタのソースまたはドレインの他方に負帰還させる、項目8から19のいずれかに記載の撮像装置。

【0055】

〔項目23〕

前記第1フィードバック回路は、前記第1トランジスタは前記第1の帰還経路の一部に含みます、前記第1光電変換部で発生した前記電気信号を、前記第1トランジスタのソースまたはドレインとゲインを介して、負帰還させ、

30

前記第2フィードバック回路は、前記第3トランジスタを前記第2の帰還経路の一部に含み、前記第2光電変換部で発生した前記電気信号を、前記第3トランジスタを介して、第6トランジスタの前記ソースまたはドレインの他方に負帰還させる、項目8から19のいずれかに記載の撮像装置。

【0056】

〔項目24〕

前記第2信号処理回路は、前記第2光電変換部で発生した電気信号を検出する第2信号検出回路、を含み、

前記第2信号検出回路は、前記第2画素電極にソースまたはドレインの一方と、前記第1光電変換部の出力部の間に接続された第14トランジスタを含む、項目8に記載の撮像装置。

40

【0057】

〔項目25〕

前記第2信号処理回路は、前記第2画素電極に接続された第5容量素子を備える、項目8から24のいずれかに記載の撮像装置。

【0058】

〔項目26〕

前記第1トランジスタのゲート幅は、前記第3トランジスタのゲート幅よりも大きく、または、前記第2トランジスタのゲート長は、前記第4トランジスタのゲート長よりも大

50

きい、項目 8 から 25 のいずれかに記載の撮像装置。

【0059】

〔項目27〕

前記第1および第2の撮像セルを複数備え、複数の第1および第2撮像セルは1次元または2次元に配列されている、項目8から26のいずれかに記載の撮像装置。

【0060】

〔項目28〕

前記第1の撮像セルと前記第2の撮像セルとは、互いに隣接して配置される、項目27に記載の撮像装置。

【0061】

〔項目29〕

前記第1の撮像セルは、前記第1光電変換部が生成する第1の電荷を蓄積し、

前記第2の撮像セルは、前記第2光電変換部が生成する第2の電荷を蓄積し、

前記第2の撮像セルにおける前記第2の電荷の蓄積時間は、前記第1の撮像セルにおける前記第1の電荷の蓄積時間よりも長い、項目8から28のいずれかに記載の撮像装置。

【0062】

〔項目30〕

項目1から29のいずれかに記載の撮像装置と、

前記撮像装置に被写体像を結像する光学系と、

信号処理を行う信号処理部と、を備えるカメラシステム。

【0063】

〔項目31〕

光電変換により第1の信号を生成する第1光電変換部と、

前記第1光電変換部に電気的に接続され、前記第1の信号を検出する第1信号検出回路と、

を含む第1撮像セルと、

光電変換により第2の信号を生成する第2光電変換部と、

ソースおよびドレインの一方が前記第2光電変換部に電気的に接続され、ソースおよびドレインの他方が前記第1光電変換部に電気的に接続される第2リセットトランジスタと、

一端が前記第2光電変換部に電気的に接続され、他端が基準電位に設定された第1容量素子と、

を含む第2撮像セルと、

を備える、撮像装置。

【0064】

〔項目32〕

反転増幅器を含む第1フィードバック回路をさらに備え、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、

前記第1信号検出回路は、前記第1画素電極にゲートが電気的に接続され、前記第1の信号を検出する第1增幅トランジスタと、前記第1画素電極にソースおよびドレインの一方が電気的に接続され、前記第1の信号をリセットする第1リセットトランジスタと、を含み、

前記第1フィードバック回路は、前記第1增幅トランジスタ、前記反転増幅器、および前記第1リセットトランジスタを介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、項目31に記載の撮像装置。

【0065】

〔項目33〕

前記第1信号検出回路は、一端が前記第1画素電極に電気的に接続された第1容量素子と、前記第1容量素子よりも容量値が大きく、一端が前記第1容量素子の他端に電気的に

10

20

30

40

50

接続され、他端が基準電位に設定された第2容量素子と、ソースおよびドレインの一方が前記第1容量素子の前記他端に接続された第1帯域制御トランジスタと、をさらに含み、

前記第1フィードバック回路は、前記第1増幅トランジスタ、前記反転増幅器、前記第1帯域制御トランジスタ、および前記第1容量素子を介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、項目31に記載の撮像装置。

【0066】

〔項目34〕

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの前記一方に電気的に接続されている、項目33に記載の撮像装置。

10

【0067】

〔項目35〕

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されている、項目33に記載の撮像装置。

【0068】

〔項目36〕

第1フィードバック回路をさらに備え、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、

20

前記第1信号検出回路は、前記第1画素電極にゲートが電気的に接続され、前記第1の信号を検出する第1増幅トランジスタと、前記第1画素電極にソースおよびドレインの一方が電気的に接続され、前記第1の信号をリセットする第1リセットトランジスタと、一端が前記第1画素電極に電気的に接続された第1容量素子と、前記第1容量素子よりも容量値が大きく、一端が前記第1容量素子の他端に電気的に接続され、他端が基準電位に設定された第2容量素子と、ソースおよびドレインの一方が前記第1容量素子の前記他端に接続された第1帯域制御トランジスタと、を含み、

前記第1増幅トランジスタのソースおよびドレインの一方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されており、

前記第1フィードバック回路は、前記第1増幅トランジスタ、前記第1帯域制御トランジスタ、および前記第1容量素子を介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、項目31に記載の撮像装置。

30

【0069】

〔項目37〕

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの前記一方に電気的に接続されている、項目36に記載の撮像装置。

【0070】

〔項目38〕

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されている、項目36に記載の撮像装置。

40

【0071】

〔項目39〕

第1フィードバック回路をさらに備え、

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、

前記第1信号検出回路は、前記第1画素電極にゲートが電気的に接続され、前記第1の信号を検出する第1増幅トランジスタと、前記第1画素電極にソースおよびドレインの一方が電気的に接続され、前記第1の信号をリセットする第1リセットトランジスタと、一

50

端が前記第1画素電極に電気的に接続された第1容量素子と、前記第1容量素子よりも容量値が大きく、一端が前記第1容量素子の他端に電気的に接続され、他端が基準電位に設定された第2容量素子と、ソースおよびドレインの一方が前記第1容量素子の前記他端に接続された第1帯域制御トランジスタと、ソースおよびドレインの一方が前記第1増幅トランジスタのソースおよびドレインの一方に電気的に接続された第1選択トランジスタと、を含み、

前記第1選択トランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されており、

前記第1フィードバック回路は、前記第1増幅トランジスタ、前記第1選択トランジスタ、前記第1帯域制御トランジスタ、および前記第1容量素子を介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、項目31に記載の撮像装置。 10

【0072】

〔項目40〕

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの前記一方に電気的に接続されている、請求項30に記載の撮像装置。

【0073】

〔項目41〕

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されている、項目39に記載の撮像装置。 20

【0074】

〔項目42〕

前記第1光電変換部は、第1画素電極と、前記第1画素電極に接する第1光電変換領域とを有し、

前記第1信号検出回路は、前記第1画素電極にゲートが電気的に接続され、前記第1の信号を検出する第1増幅トランジスタと、前記第1画素電極にソースおよびドレインの一方が電気的に接続され、前記第1の信号をリセットする第1リセットトランジスタと、一端が前記第1画素電極に電気的に接続された第1容量素子と、前記第1容量素子よりも容量値が大きく、一端が前記第1容量素子の他端に電気的に接続され、他端が基準電位に設定された第2容量素子と、ソースおよびドレインの一方が前記第1容量素子の前記他端に接続された第1帯域制御トランジスタと、第1フィードバック回路と、を含み、 30

前記第1帯域制御トランジスタのゲートは、前記第1画素電極に電気的に接続されており、

前記第1フィードバック回路は、前記第1帯域制御トランジスタ、および前記第1容量素子を介して、前記第1画素電極の電位を負帰還させる帰還経路を形成する、項目31に記載の撮像装置。

【0075】

〔項目43〕

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの前記一方に電気的に接続されている、項目42に記載の撮像装置。 40

【0076】

〔項目44〕

前記第1リセットトランジスタのソースおよびドレインの他方は、前記第1帯域制御トランジスタのソースおよびドレインの他方に電気的に接続されている、項目42に記載の撮像装置。

【0077】

本開示の一態様によれば、構成の異なる2つの撮像セルを各画素内に設けることができる。第1撮像セルは低ノイズ特性を必要とするが、高飽和特性を特に必要としない。第1 50

撮像セルによって「低ノイズ高感度撮像」を行うことができる。第2撮像セルは、高飽和特性を必要するが、光量が多く、ショットノイズの影響の大きい明るいシーンの撮像を担うので、低ノイズ特性を特に必要としない。第2撮像セルによって「高飽和低感度撮像」を行うことができる。従って、従来に比べて明暗差の大きな被写体まで、白飛びおよび黒潰れなく撮像できる。つまり、図2に示すような、さらに望ましい撮像セル特性を実現できる。さらに、本構成では、2つの撮像セルによって、高感度撮像と低感度撮像とを同時にを行うことができるので、これらの撮像間の時間ずれが抑制される。

#### 【0078】

以下、図面を参照しながら、本開示の実施形態を詳細に説明する。なお、以下で説明する実施形態は、いずれも包括的または具体的な例を示す。以下の実施形態で示される数値、形状、材料、構成要素、構成要素の配置および接続形態、ステップ、ステップの順序などは、一例であり、本開示を限定する主旨ではない。本明細書において説明される種々の態様は、矛盾が生じない限り互いに組み合わせることが可能である。また、以下の実施形態における構成要素のうち、最上位概念を示す独立請求項に記載されていない構成要素については、任意の構成要素として説明される。以下の説明において、実質的に同じ機能を有する構成要素は共通の参照符号で示し、説明を省略することがある。

10

#### 【0079】

##### (第1の実施の形態)

図4から図6Bを参照しながら、本実施の形態による撮像装置100の構造を説明する。以下、半導体基板としてp型シリコンの基板を用いた構造例を説明する。また、信号電荷として正孔を利用する例を示す。なお、信号電荷として電子を用いても構わない。

20

#### 【0080】

##### (撮像装置100の構造)

図4は、撮像装置100の構造の一例を模式的に示している。撮像装置100は、2次元に配列された複数の単位画素1を備えている。なお、実際には、数百万個の単位画素1が2次元に配列され得るが、図4は、そのうちの2×2の行列状に配置された単位画素1に着目してその様子を示している。なお、撮像装置100は、ラインセンサであっても構わない。その場合、複数の単位画素1は、1次元(行方向または列方向)に配列され得る。

#### 【0081】

30

単位画素1は、第1撮像セル1aおよび第2撮像セル1a'を含んでいる。第1撮像セル1aは低ノイズに対応した撮像セルであり、第2撮像セル1a'は高飽和に対応した撮像セルである。典型的には、第1撮像セル1aは高感度用の撮像セルとして機能し、第2撮像セル1a'は低感度用の撮像セルとして機能する。撮像装置100は、第1撮像セル1a用に、行毎に配置された複数のリセット信号線6および複数のアドレス信号線7と、列毎に配置された複数の垂直信号線9、電源配線8および複数のフィードバック信号線10と、を備えている。また、撮像装置100は、第2撮像セル1a'用に、行毎に配置された複数のリセット信号線6'および複数のアドレス信号線7'、と、列毎に配置された複数の垂直信号線9'、電源配線8'および複数のフィードバック信号線10'、を備えている。

40

#### 【0082】

撮像装置100には、第1撮像セル1aからの信号を処理する第1の周辺回路と、第2撮像セル1a'からの信号を処理する第2の周辺回路とがそれぞれ個別に設けられている。第1の周辺回路は、第1の垂直走査回路2、第1の水平走査回路3、第1反転増幅器11、第1の列A/D変換回路4および電流源5を有し、第2の周辺回路は、第2の垂直走査回路2'、第2の水平走査回路3'、第2反転増幅器11'、第2の列A/D変換回路4'、および第2の電流源5'を有している。

#### 【0083】

第1撮像セル1aに着目すると、第1の垂直走査回路は、複数のリセット信号線6および複数のアドレス信号線7を制御する。垂直信号線9は第1の水平走査回路3に接続され

50

、画素信号を第1の水平走査回路3に伝達する。電源配線8は、すべての単位画素1aに電源電圧(例えばVDD)を供給する。フィードバック信号線10は、後述する反転増幅器11からのフィードバック信号を単位画素1の第1撮像セル1aに伝達する。第2撮像セル1a'においても、第1撮像セル1aと同様に各種の信号線が配線されており、それぞれの回路が各信号線を制御する。ただし、第1撮像セル1aと第2撮像セル1a'のリセット信号線6、6'、アドレス信号線7、7'は画素の構成次第で共通化することが可能である。また、フィードバック信号線10、10'、第1反転増幅器11、第2反転増幅器11'は画素の構成次第で共通化および省略することが可能である。またそれに伴い、第1の垂直走査回路2、第2の垂直走査回路2'、第1の水平走査回路3、および第2の水平走査回路3'も画素の構成次第で共通化することが可能である。

10

#### 【0084】

(第1および第2撮像セル1a、1a'の回路構成)

次に、図5、図6Aを参照しながら、第1および第2撮像セル1a、1a'(単位画素1)の回路構成例を説明する。

#### 【0085】

図5は、単位画素1における第1および第2信号処理回路P1、P2を示している。図6Aは、本実施の形態による単位画素1の回路構成の一例を示している。

#### 【0086】

単位画素1は、同一画素内に、第1撮像セル1aと第2撮像セル1a'を有する。第1撮像セル1aは、低ノイズセルとして機能する。第1撮像セル1aは、光を電気信号に変換する第1光電変換部PC1と、第1光電変換部PC1に電気的に接続され、第1光電変換部PC1で生成した電気信号を読み出す第1信号処理回路P1とを有する。第1光電変換部PC1は、第1画素電極E1と、第1画素電極E1に接する第1光電変換領域D1とを有する。

20

#### 【0087】

第1信号処理回路P1は、第1光電変換部PC1で生成した電気信号を検出する第1信号検出回路を含む。第1信号検出回路は、第1増幅トランジスタM10と、第1選択トランジスタM11と、第1リセットトランジスタM12とを有する。第1増幅トランジスタM10のゲートは、第1光電変換部PC1に接続されている。第1増幅トランジスタM10は、第1光電変換部PC1で生成した電気信号を増幅する。第1選択トランジスタM11のソースおよびドレインの一方は、第1増幅トランジスタM10のソースおよびドレインの一方に接続される。第1選択トランジスタM11は、第1増幅トランジスタM10で増幅された信号を選択的に出力する。第1リセットトランジスタM12のソースおよびドレインの一方は、読み出しノードFD1に接続される。第1リセットトランジスタM12は、第1光電変換部PC1の第1画素電極に接続された読み出しノードFD1をリセット(初期化)する。

30

#### 【0088】

第2撮像セル1a'は、高飽和セルとして機能する。第2撮像セル1a'は、光を電気信号に変換する第2光電変換部PC2と、第2光電変換部PC2に電気的に接続され、第2光電変換部PC2で生成した電気信号を読み出す第2信号処理回路P2とを有する。第2光電変換部PC2は、第2画素電極E2と、第2画素電極E2に接する第2光電変換領域D2とを有する。

40

#### 【0089】

第2信号処理回路P2は、第2光電変換部PC2で生成した電気信号を検出する第2信号検出回路を含む。第2信号検出回路は、第2増幅トランジスタM20と、第2選択トランジスタM21と、第2リセットトランジスタM22とを有する。第2増幅トランジスタM20のゲートは、第2光電変換部PC2に接続される。第2増幅トランジスタM20は、第2光電変換部PC2で生成した電気信号を増幅する。第2選択トランジスタM21のソースおよびドレインの一方は、第2増幅トランジスタM20のソースおよびドレインの一方に接続される。第2選択トランジスタM20は、第2増幅トランジスタM20で増幅

50

された信号を選択的に出力する。第2リセットトランジスタM22のソースおよびドレインの一方は、読み出しノードFD2に接続される。第2リセットトランジスタM22は、第2光電変換部PC2の第2画素電極に接続された読み出しノードFD2をリセット(初期化)する。

【0090】

第1撮像セル1aは、暗いシーンの撮像を担うので、低ノイズ特性を必要とするが、高飽和特性を特に必要としない。一方、第2撮像セル1a'は、明るいシーンの撮像を担うので、高飽和特性を必要とする。しかし、明るいシーンの撮像では、光の量が多く、ショットノイズで特性が決定されるので、第2撮像セル1a'は低ノイズ特性を特に必要としない。

10

【0091】

本実施の形態においては、第1增幅トランジスタM10のゲート幅が、第2增幅トランジスタM20のゲート幅よりも大きい。これにより、第1增幅トランジスタM10のgmを大きく設定することができ、その結果、第1撮像セル1aの読み出しノイズを低減することができる。一方、第2撮像セル1a'の低ノイズ特性は従来相当であっても問題とはならない。また、第1リセットトランジスタM12のゲート長が、第2リセットトランジスタM22のゲート長よりも大きい。これにより、第1撮像セル1aのノイズ低減効果が向上する。一方、第2撮像セル1a'の低ノイズ特性は従来相当であっても問題とはならない。

【0092】

20

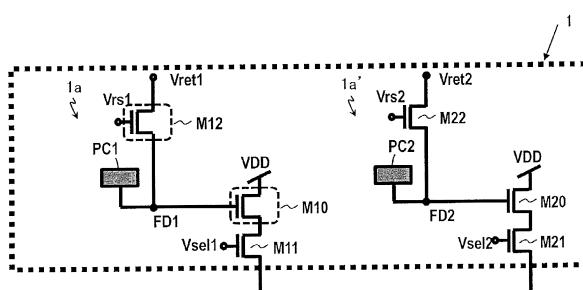

図6Bは、本実施の形態による単位画素1の他の回路構成例を示している。図6Bに示すように、第2光電変換部PC2と基準電圧VBWとの間に電気的に接続された第5容量素子CWを設けている。これにより、第2撮像セル1a'の高飽和特性を容量比分だけ向上させることができる。その結果、さらなるダイナミックレンジの拡大を図ることも可能である。なお、図6B以降の図面においては、第1信号処理回路および第2信号処理回路のそれぞれの参照符号「P1」および「P2」は省略して明細書中のみで使用する。

【0093】

本実施の形態によれば、無駄な画素のサイズの増加を抑制することができる。また、本実施の形態によれば、第1撮像セル1aで低ノイズ高感度撮像を行うと同時に、第2撮像セル1a'で高飽和低感度撮像を行うことが可能な、小型の撮像装置を提供できる。また、本実施の形態によれば、明暗差が大きな被写体を、時間ずれなく、かつ、白飛びおよび黒潰れなく撮像できる。

30

【0094】

(第2の実施の形態)

図7から図10を参照しながら、第2の実施の形態による単位画素1の回路構成例を説明する。

【0095】

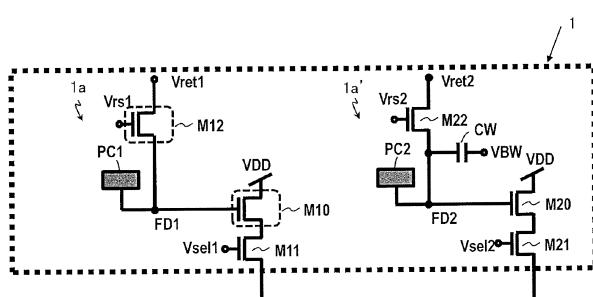

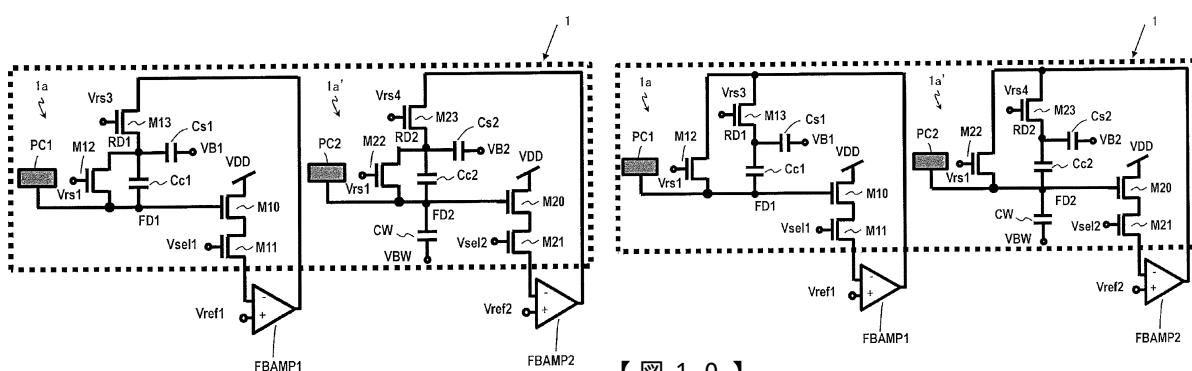

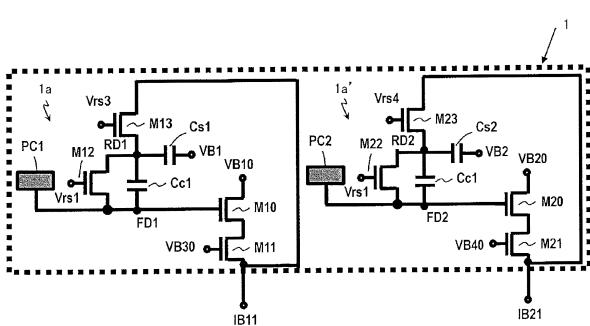

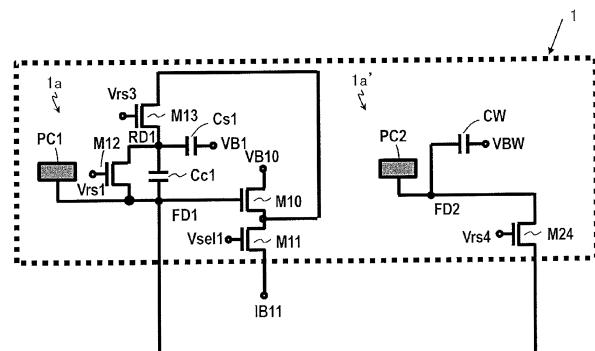

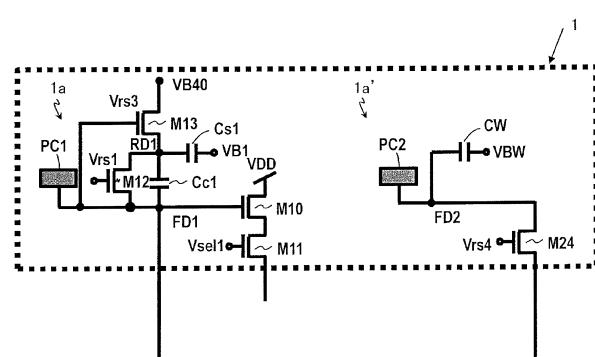

図7は、本実施の形態による単位画素1の回路構成例を示している。単位画素1は、同一画素内に、第1撮像セル1aと第2撮像セル1a'を有する。第1撮像セル1aは、低ノイズセルとして機能する。第1撮像セル1aは、光を電気信号に変換する第1光電変換部PC1と、第1光電変換部PC1に電気的に接続され、第1光電変換部PC1で生成した電気信号を読み出す第1信号処理回路P1とを有する。

40

【0096】

第1信号処理回路P1は、第1光電変換部PC1で生成した電気信号を検出する第1信号検出回路を含む。第1信号検出回路は、第1増幅トランジスタM10と、第1選択トランジスタM11と、第1リセットトランジスタM13と、第1フィードバック回路とを有する。第1増幅トランジスタM10のゲートは、第1光電変換部PC1に接続されている。第1増幅トランジスタM10は、第1光電変換部PC1で生成した電気信号を増幅する。第1選択トランジスタM11のソースおよびドレインの一方は、第1増幅トランジスタM10のソースおよびドレインの一方に接続される。第1増幅トランジスタM10は、第

50

1 増幅トランジスタM 1 0で増幅された信号を選択的に出力する。第1リセットトランジスタM 1 3のソースおよびドレインの一方は、読み出しノードF D 1に接続される。第1リセットトランジスタM 1 3は、第1光電変換部P C 1第1画素電極に接続された読み出しノードF D 1をリセット(初期化)する。

【0097】

第1フィードバック回路は、第1反転増幅器F B A M P 1を有し、第1リセットトランジスタM 1 3をオフする時に発生するk T C ノイズを負帰還させる第1の帰還経路を形成する。第1反転増幅器F B A M P 1によって、第1の帰還経路の利得を上げ、かつ、ノイズ抑制効果を向上させることができる。第1反転増幅器F B A M P 1は、図4における第1反転増幅器1 1に対応する。

10

【0098】

第2撮像セル1 a'は、高飽和セルとして機能する。第2撮像セル1 a'は、光を電気信号に変換する第2光電変換部P C 2と、第2光電変換部P C 2に電気的に接続され、第2光電変換部P C 2で生成した電気信号を読み出す第2信号処理回路P 2とを有する。

【0099】

第2信号処理回路P 2は、第2光電変換部P C 2で発生した電気信号を検出する第2信号検出回路を含む。第2信号検出回路は、第2増幅トランジスタM 2 0と、第2選択トランジスタM 2 1と、第2リセットトランジスタM 2 2とを有する。第2増幅トランジスタM 2 0のゲートは、第2光電変換部P C 2に接続される。第2増幅トランジスタM 2 0は、第2光電変換部P C 2で生成した電気信号を増幅する。第2選択トランジスタM 2 1のソースおよびドレインの一方は、第2増幅トランジスタM 2 0のソースおよびドレインの一方に接続される。第2選択トランジスタM 2 1は、第2増幅トランジスタM 2 0で増幅された信号を選択的に出力する。第2リセットトランジスタM 2 2は読み出しノードF D 2に接続され、第2光電変換部P C 2の第2画素電極に接続された読み出しノードF D 2をリセット(初期化)する。

20

【0100】

第1撮像セル1 aは、暗いシーンの撮像を担うので、低ノイズ特性を必要とするが、高飽和特性を特に必要としない。一方、第2撮像セル1 a'は、明るいシーンの撮像を担うので、高飽和特性を必要とする。しかし、明るいシーンの撮像では、光の量が多く、ショットノイズで特性が決定されるので、第2撮像セル1 a'は低ノイズ特性を特に必要としない。

30

【0101】

第1撮像セル1 aは、第1フィードバック回路を備えるので、第1リセットトランジスタM 1 3オフ時に発生する雑音を大幅に抑制できる。一方、第2撮像セル1 a'のノイズ特性は従来相当であっても問題とはならない。なお、ノイズ抑制手法については後述する。さらに、第1増幅トランジスタM 1 0のゲート幅を、第2増幅トランジスタM 2 0のゲート幅よりも大きくしてもよい。これにより、第1増幅トランジスタM 1 0のg mを大きく設定することができる。その結果、第1撮像セル1 aの読み出しノイズを低減することができる。一方、第2撮像セル1 a'のノイズ特性は従来相当であっても問題とはならない。また、第1リセットトランジスタM 1 3のゲート長を、第2リセットトランジスタM 2 2のゲート長よりも大きくしてもよい。これにより、第1撮像セル1 aのノイズ低減効果がさらに向上する。第2撮像セル1 a'のノイズ特性は従来相当であっても問題とはならない。

40

【0102】

図8は、本実施の形態による単位画素1の他の回路構成例を示している。図示するように、第2光電変換部P C 2と基準電圧V B Wとの間に電気的に接続された第5容量素子C Wを設けている。これにより、第2撮像セル1 a'の高飽和特性を容量比分だけ向上させることができる。その結果、さらなるダイナミックレンジの拡大を図ることも可能である。

【0103】

50

本実施の形態によれば、無駄な画素のサイズの増加を抑制することができる。また、本実施の形態によれば、第1撮像セル1aで低ノイズ高感度撮像を行うと同時に、第2撮像セル1a'で高飽和低感度撮像を行うことが可能な、小型の撮像装置を提供できる。また、本実施の形態によれば、明暗差が大きな被写体を、時間ずれなく、かつ、白飛びおよび黒潰れなく撮像できる。

#### 【0104】

図9Aから図9Nを参照して、本実施の形態による単位画素1のさらなる他の回路構成例を説明する。それぞれの回路構成を用いても、上述した効果と同じ効果が得られる。

#### 【0105】

図9Aから図9Nは、本実施の形態による単位画素1のさらなる他の回路構成例を示している。以下、複数の回路構成例のうち、代表的な回路構成例を主として説明する。

10

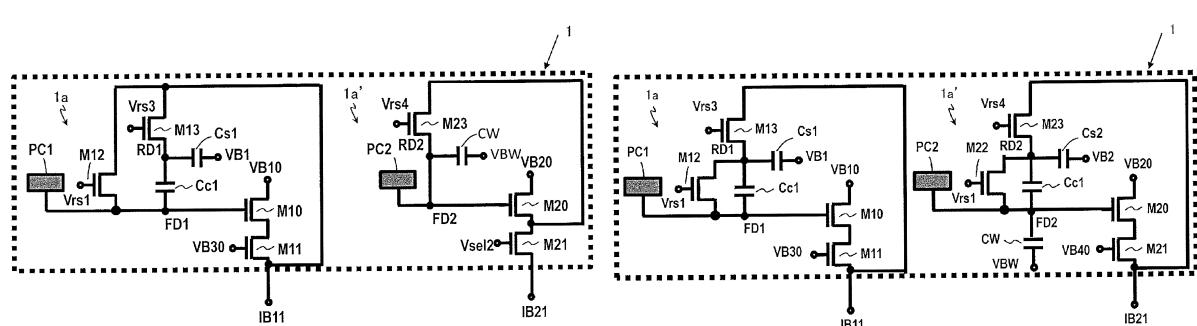

#### 【0106】

図9Aに示される単位画素1は、第2リセットトランジスタM23をオフする時に発生するKTCノイズを負帰還させる第2の帰還経路を形成する第2フィードバック回路を、図7に示される単位画素1の第2撮像セル1a'に付加した構成を備える。第2フィードバック回路は、第2反転増幅器FBAMP2を含む。この構成によると、第1撮像セル1aを用いて低ノイズ撮像が可能であり、第2撮像セル1a'を用いて、低ノイズかつ高飽和な撮像が可能である。その結果、撮像データ全域のノイズを抑制することができる。特に中間光量での撮像においてノイズを効果的に抑制でき、より高精彩な画像の取得が可能となる。第2反転増幅器FBAMP2は、図4における第1反転増幅器11'に対応する。

20

#### 【0107】

上述したように、第1増幅トランジスタM10のゲート幅を、第2増幅トランジスタM20のゲート幅よりも大きくしてもよい。これにより、第1増幅トランジスタM10のgmを大きく設定することができる。その結果、第1撮像セル1aの読み出しノイズを低減することができる。一方、第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。また、第1リセットトランジスタM13のゲート長を、第2リセットトランジスタM23のゲート長よりも大きくしてもよい。これにより、第1撮像セル1aのノイズ低減効果が一層向上する。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。さらに、第1フィードバック回路の利得を、第2フィードバック回路の利得よりも大きく設定してもよい。これにより、第1撮像セル1aのノイズ低減効果がなお一層向上する。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。

30

#### 【0108】

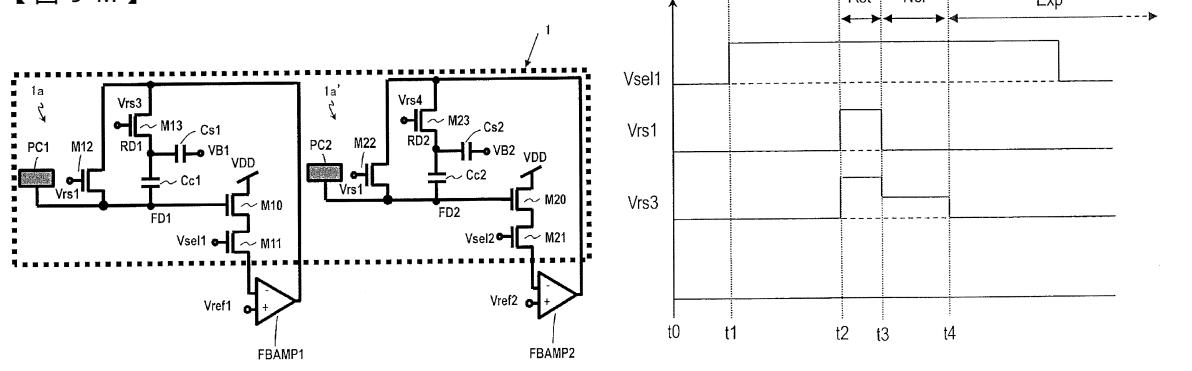

図9Cに示される単位画素1は、第1帯域制御トランジスタM13、第1容量素子Cc1および第2容量素子Cs1を、図7に示される単位画素1の第1撮像セル1aに付加した構成を備える。第1帯域制御トランジスタM13は、第1フィードバック回路の帯域制御を行う。第1帯域制御トランジスタM13は帰還経路上に配置され、第1反転増幅器FBAMP1の出力に接続されている。第1容量素子Cc1は、読み出しノードFD1と第1帯域制御トランジスタM13のソースまたはドレンとの間に電気的に接続されている。第2容量素子Cs1は、第1容量素子Cc1よりも大きい容量値を有し、第1容量素子Cc1と基準電圧VB1との間に接続されている。この構成によると、第1撮像セル1aがノイズを抑制する能力を、向上させることができる。

40

#### 【0109】

上述したように、第1増幅トランジスタM10のゲート幅を、第2増幅トランジスタM20のゲート幅よりも大きくしてもよい。これにより、第1増幅トランジスタM10のgmを大きく設定することができる。その結果、第1撮像セル1aの読み出しノイズを低減することができる。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。また、第1リセットトランジスタM12のゲート長を、第2リセットトランジスタM22のゲート長よりも大きくしてもよい。これにより、第1撮像セル1aのノイズ低減効果が一層向上する。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはな

50

らない。

【0110】

図9Cに示されるように、第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1と、第1容量素子Cc1と第2容量素子Cs1との間の接続ノード（「接続部」と呼ぶ場合がある。）RD1との間に接続されていることが望ましい。または、図9Eに示されるように、第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1と、第1帯域制御トランジスタM13のソースおよびドレインのうち接続ノードRD1と接続されていない方との間に接続されることが望ましい。このような構成によれば、リセット電圧Vreset（＝VRST）を別途設けなくてもよい。また、帰還をかけてリセット値近傍に収束させることができるので、ノイズキャンセルの高速化が図れる。10

【0111】

図9Gに示される単位画素1は、第2リセットトランジスタM23をオフする時に発生するKTCノイズを負帰還させる第2の帰還経路を形成する第2フィードバック回路を、図9Cに示される単位画素1の第2撮像セル1a'に付加した構成を備える。この構成によると、第1撮像セル1aを用いて低ノイズ撮像が可能であり、第2撮像セル1a'を用いて、低ノイズかつ高飽和な撮像が可能である。その結果、撮像データ全域のノイズを抑制することができる。特に中間光量での撮像においてノイズを効果的に抑制でき、より高精細な画像の取得が可能となる。

【0112】

上述したように、第1増幅トランジスタM10のゲート幅を、第2増幅トランジスタM20のゲート幅よりも大きくしてもよい。これにより、第1増幅トランジスタM10のgmを大きく設定することができる。その結果、第1撮像セル1aの読み出しノイズを低減することができる。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。また、第1リセットトランジスタM12のゲート長を、第2リセットトランジスタM23のゲート長よりも大きくしてもよい。これにより、第1撮像セル1aのノイズ低減効果が一層向上する。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。さらに、第1フィードバック回路の利得を、第2フィードバック回路の利得よりも大きく設定してもよい。これにより、第1撮像セル1aのノイズ低減効果がなお一層向上する。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。30

【0113】

図9Gに示されるように、第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1と、第1容量素子Cc1と第2容量素子Cs1との間の接続ノードRD1との間に接続されていることが望ましい。または、図9Iに示されるように、第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1と、第1帯域制御トランジスタM13のソースおよびドレインのうち接続ノードRD1と接続されていない方との間に接続されることが望ましい。このような構成によれば、リセット電圧Vreset（＝VRST）を別途設けなくてもよい。また、帰還をかけてリセット値近傍に収束させることができるので、ノイズキャンセルの高速化が図れる。40

【0114】

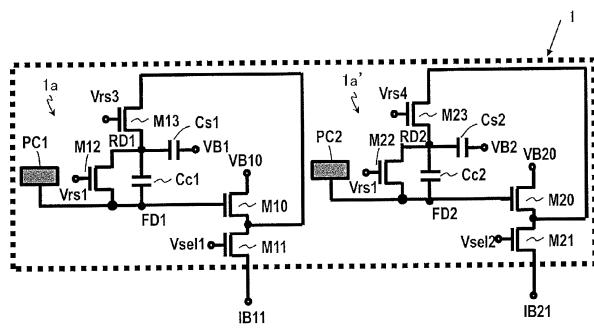

図9K、図9Mに示される単位画素1は、第2帯域制御トランジスタM23と、第3容量素子Cc2および第4容量素子Cs2を有する容量回路とを、図9Gに示される単位画素1の第2撮像セル1a'に付加した構成を備える。第2帯域制御トランジスタM23は、第2フィードバック回路の帯域制御を行う。第2帯域制御トランジスタM23は帰還経路上に配置され、第2反転増幅器FBAMP2の出力と、第3容量素子Cc2および第4容量素子Cs2の接続ノードRD2との間に接続されている。第3容量素子Cc2は、読み出しノードFD2と第2帯域制御トランジスタM23のソースまたはドレインとの間に電気的に接続されている。第4容量素子Cs2は、第3容量素子Cc2よりも大きい容量値を有し、第3容量素子Cc2と基準電圧VB2との間に接続されている。第3容量素子50

C c 2 は第 4 容量素子 C s 2 に直列に接続されている。この構成によると、第 1 撮像セル 1 a を用いて低ノイズ撮像が可能であり、第 2 撮像セル 1 a ' を用いて、低ノイズかつ高飽和な撮像が可能である。その結果、撮像データ全域のノイズを抑制することができる。特に中間光量での撮像においてノイズを効果的に抑制でき、より高精彩な画像の取得が可能となる。

#### 【 0 1 1 5 】

上述したように、第 1 増幅トランジスタ M 1 0 のゲート幅を、第 2 増幅トランジスタ M 2 0 のゲート幅よりも大きくしてもよい。これにより、第 1 増幅トランジスタ M 1 0 の g<sub>m</sub> を大きく設定することができる。その結果、第 1 撮像セル 1 a の読み出しノイズを低減することができる。第 2 撮像セル 1 a ' のノイズ特性は従来相当であっても問題とはならない。また、第 1 リセットトランジスタ M 1 2 のゲート長を、第 2 リセットトランジスタ M 2 2 のゲート長よりも大きくしてもよい。これにより、第 1 撮像セル 1 a のノイズ低減効果が一層向上する。第 2 撮像セル 1 a ' のノイズ特性は従来相当であっても問題とはならない。さらに、第 1 フィードバック回路の利得を、第 2 フィードバック回路の利得よりも大きく設定してもよい。これにより、第 1 撮像セル 1 a のノイズ低減効果がなお一層向上する。第 2 撮像セル 1 a ' のノイズ特性は従来相当であっても問題とはならない。

#### 【 0 1 1 6 】

図 9 K に示されるように、第 1 リセットトランジスタ M 1 2 は、第 1 光電変換部 P C 1 に接続された読み出しノード F D 1 と、第 1 容量素子 C c 1 と第 2 容量素子 C s 1 との間の接続ノード R D 1 と、の間に接続されていることが望ましい。または、図 9 M に示されるように、第 1 リセットトランジスタ M 1 2 は、第 1 光電変換部 P C 1 に接続された読み出しノード F D 1 と、第 1 帯域制御トランジスタ M 1 3 のソースおよびドレインのうち接続ノード R D 1 と接続されていない方との間に接続されることが望ましい。このような構成によれば、リセット電圧 V<sub>ret</sub> (= V<sub>RST</sub>) を別途設けなくてもよい。また、帰還をかけてリセット値近傍に収束させることができるので、ノイズキャンセルの高速化が図れる。

#### 【 0 1 1 7 】

図 9 A から図 9 N に示される回路構成によれば、無駄な画素のサイズの増加を抑制することができる。また、第 1 撮像セル 1 a で低ノイズ高感度撮像を行うと同時に、第 2 撮像セル 1 a ' で高飽和低感度撮像を行うことが可能な、小型の撮像装置を提供できる。さらに、明暗差が大きな被写体を、時間ずれなく、かつ、白飛びおよび黒潰れなく撮像できる。

#### 【 0 1 1 8 】

図 8 に示される単位画素 1 と同様に、図 9 B、図 9 D、図 9 F、図 9 H、図 9 J、図 9 L および図 9 N に示されるように、第 2 光電変換部 P C 2 と基準電圧 V<sub>BW</sub>との間に電気的に接続された第 5 容量素子 C<sub>W</sub>を設けてもよい。これにより、第 2 撮像セル 1 a ' の高飽和特性を容量比分だけ向上させることができる。その結果、さらなるダイナミックレンジの拡大を図ることも可能である。

#### 【 0 1 1 9 】

以下、フィードバック回路を用いたノイズ抑制、および、データの読み出し動作の具体例を示す。

#### 【 0 1 2 0 】

(読み出しおよびノイズ抑制)

図 9 C に示される単位画素 1 の第 1 撮像セル 1 a を用いた、ノイズ抑制およびデータの読み出し動作を具体例として説明する。

#### 【 0 1 2 1 】

第 1 信号処理回路 P 1 において、第 1 帯域制御トランジスタ M 1 3 のソースおよびドレインの一方には、第 2 容量素子 C s 1 の一端が接続される。第 1 帯域制御トランジスタ M 1 3 と第 2 容量素子 C s 1 により、R C フィルタ回路が形成される。さらに、第 1 帯域制御トランジスタ M 1 3 のソースおよびドレインの一方には第 1 容量素子 C c 1 の一端も接

10

20

30

40

50

続される。第1容量素子Cc1の他端は、第1の読み出しノードFD1に接続される。

【0122】

第1帯域制御トランジスタM13のゲートには第1の帯域制御信号Vrs3が入力され、第1の帯域制御信号Vrs3の電位により第1帯域制御トランジスタM13の状態が決定される。例えば、第1の帯域制御信号Vrs3がハイレベルの場合、第1帯域制御トランジスタM13はオンし、読み出しノードFD1と、第1増幅トランジスタM10と、第1選択トランジスタM11と、第1反転増幅器FBAMP1と、第1帯域制御トランジスタM13と、第1容量素子Cc1とで帰還経路が形成される。第1の帯域制御信号Vrs3の電位が低くなると第1帯域制御トランジスタM13の抵抗成分が大きくなるので、第1帯域制御トランジスタM13の帯域は狭くなり、帰還する信号の周波数領域が狭くなる。帰還が形成されている時、第1帯域制御トランジスタM13が出力する信号は、第1容量素子Cc1と読み出しFD1の寄生容量とによって形成される減衰回路で減衰されて、読み出しノードFD1に帰還される。第1容量素子Cc1の容量値をCc、読み出しノードFD1の寄生容量をCFDとすると、減衰率Bは、 $B = Cc / (Cc + CFD)$ となる。更に第1の帯域制御信号Vrs3の電位が低くなり、ローレベルになると、第1帯域制御トランジスタM13はオフし、帰還は形成されない。読み出しノードFD1は更に第1リセットトランジスタM12のソースおよびドレインの一方に接続される。第1リセットトランジスタM12のソースおよびドレインの他方は、接続ノードRD1に接続される。

【0123】

第1リセットトランジスタM12のゲートには、第1のリセット制御信号Vrs1が入力され、第1のリセット制御信号Vrs1の電位により、第1リセットトランジスタM12の状態が決定される。例えば、第1のリセット制御信号Vrs1がハイレベルの場合、第1リセットトランジスタM12はオンし、読み出しノードFD1は接続ノードRD1と同一の電圧となる。このとき、第1の帯域制御信号Vrs3もハイレベルの場合、第1リセットトランジスタM12、および、第1帯域制御トランジスタM13は共にオンし、読み出しノードFD1と接続ノードRD1は共に、所望のリセット電圧VRSTになる。ここでリセット電圧VRSTは、第1反転増幅器FBAMP1の基準電圧Vref1から第1増幅トランジスタM10のゲートと、ソースおよびドレインのうちVDDに接続されていない方との間の電圧を引いた値となる。第1選択トランジスタM11のソースおよびドレインの一方は、垂直信号線9に接続される。第1選択トランジスタM11のゲートには第1の選択制御信号Vsel1が入力され、第1の選択制御信号Vsel1の電位により第1選択トランジスタM11の状態が決定される。例えば、第1の選択制御信号Vsel1がハイレベルの場合、第1選択トランジスタM11はオンし、第1増幅トランジスタM10と垂直信号線9は電気的に接続された状態となる。第1の選択制御信号Vsel1がローレベルの場合、第1選択トランジスタM11はオフし、第1増幅トランジスタM10と垂直信号線9とは電気的に分離された状態となる。

【0124】

(第1撮像セル1aの動作)

図10は、本実施の形態による第1撮像セル1aの動作タイミングの一例を示している。

【0125】

(リセット期間)

まず、第1の選択制御信号Vsel1をハイレベルにする(時刻t1)。次に、第1の帯域制御信号Vrs3の電位をハイレベルにして第1帯域制御トランジスタM13をオン状態に設定する。同時に、第1のリセット制御信号Vrs1をハイレベルにし、第1リセットトランジスタM12をオン状態に設定する(時刻t2)。これにより、読み出しノードFD1の電圧は、リセット電圧VRSTに等しくなる。

【0126】

(ノイズ抑制期間)

次に、第1のリセット制御信号Vrs1をローレベルにし、第1リセットトランジスタ

10

20

30

40

50

M12をオフ状態に設定する(時刻t3)。このとき、第1フィードバック回路は、増幅率(= -A × B)で帰還を形成しているので、第1リセットトランジスタM12をオフした時の読み出しノードFD1のkTCノイズは、 $1 / (1 + A \times B)$ に抑制される。また、このとき、第1帯域制御トランジスタM13の動作帯域が広帯域である第1の帯域となるように、第1の帯域制御信号Vrs3の電位が設定されることにより、高速にノイズが抑制される。

#### 【0127】

同時に、第1の帯域制御信号Vrs3をハイレベルとローレベルとの中間の電位に設定する(時刻t3)なお、このタイミングは、時刻t3よりも若干遅れたタイミングであってもよい。このとき、第1帯域制御トランジスタM13の動作帯域は、第1の帯域よりも低い第2の帯域となる。なお、第2の帯域を、第1増幅トランジスタM10の動作帯域よりも十分に低くすることで、ノイズ抑制効果は大きくなる。ただし、これとトレードオフに、ノイズ抑制に必要な時間は長くなる。第2の帯域が第1増幅トランジスタM10の動作帯域より高くてもノイズ抑制効果は得られる。ノイズ抑制に掛ける時間に応じて、設計者は第2の帯域を任意に設計することは可能である。本実施の形態では、第2の帯域が、第1増幅トランジスタM10の動作帯域よりも十分に低い状態にあるとする。

#### 【0128】

第2の帯域が、第1増幅トランジスタM10の動作帯域よりも低い状態においては、第1帯域制御トランジスタM13で発生する熱ノイズは、第1フィードバック回路により、 $1 / (1 + A \times B)^{1/2}$ 倍に抑制される。この状態で、第1の帯域制御信号Vrs3をローレベルに設定し、帯域制御トランジスタをオフにする(時刻t4)。そのときに読み出しノードFD1に残存するkTCノイズは、第1リセットトランジスタM12に起因したkTCノイズと、第1帯域制御トランジスタM13に起因したkTCノイズとを二乗和した値となる。第2容量素子Cs1の容量値をCsとするとき、帰還による抑制がない状態で発生する第1帯域制御トランジスタM13のkTCノイズは、帰還による抑制がない状態で発生する第1リセットトランジスタM12のkTCノイズに比べて( $CFD / Cs$ ) $^{1/2}$ 倍になる。この点を考慮して、帰還がない場合と比較すると、kTCノイズは、 $[1 + (1 + A \times B) \times CFD / Cs]^{1/2} / (1 + A \times B)$ 倍に抑制される。

#### 【0129】

なお、第1帯域制御トランジスタM13がオン状態からオフ状態に徐々に変化するよう、第1帯域制御トランジスタM13のしきい値電圧を跨いで変化するような電位に第1の帯域制御信号Vrs3を制御してもよい。これにより、撮像装置100を構成する複数の単位画素1の間で第1帯域制御トランジスタM13のしきい値電圧にはらつきがあっても、全ての単位画素1のノイズを抑制することが可能となる。更に、変化させる第1の帯域制御信号Vrs3の電圧範囲を、単位画素1のはらつきの範囲に制限してもよい。これにより、変化させるのに必要な時間を短縮でき、かつ、高速なノイズ抑制が可能となる。

#### 【0130】

##### 〔露光/読み出し期間〕

次に、垂直信号線9の電位は、読み出しノードFD1の電位に応じたレベルとなるが、第1増幅トランジスタM10と、第1選択トランジスタM11と、電流源5(図4を参照)とによって形成されるソースフォロア回路の増幅率は1倍程度である。このとき、読み出しノードFD1には、ノイズ抑制完了時(時刻t4)から読み出し時までに第1光電変換部PC1で変換された電気信号に応じた分だけ変化した電圧信号が蓄積されている。読み出しノードFD1の電圧信号は、ソースフォロア回路により1倍程度の増幅率で垂直信号線9に出力される。ここで、ランダムノイズは第1光電変換部PC1で変換される電気信号が0の時の出力の揺らぎ、すなわち、kTCノイズである。kTCノイズは、リセット抑制期間において $[1 + (1 + A \times B) \times CFD / Cs]^{1/2} / (1 + A \times B)$ 倍に抑制される。更に、露光/読み出し期間において、1倍程度の増幅率で垂直信号線9に出力されるので、本実施の形態によれば、ランダムノイズが抑制された良好な画像データを取得することができる。

10

20

30

40

50

## 【0131】

面積が許す限り第2容量素子C<sub>s</sub>1を大きくすることにより、ランダムノイズは抑制される。通常、容量を大きくすると、ランダムノイズは低減される。しかし、読み出しノードF D 1で電荷信号を電圧信号に変換する際、信号自体が小さくなってしまう。その結果としてS/Nは改善されない。

## 【0132】

本実施の形態においては、読み出しノードF D 1と接続部ノードR D 1とが第1容量素子C<sub>c</sub>1によって分離されているので、第2容量素子C<sub>s</sub>1の容量を大きくしても信号低下は起こらない。ランダムノイズだけが抑制されるので、S/N比が改善されるという利点がある。従って、本実施の形態は、単位画素1の面積を広くとれるような用途の撮像装置において有効である。

10

## 【0133】

例えば図4に示されるような、垂直信号線9の信号を検出するための後段回路を接続することができる。後段回路は、例えば第1の垂直走査回路2、第2の垂直走査回路2'、第1の列A/D変換回路4および第2の列A/D変換回路4'から構成される。ただし、本開示はこのような回路構成に限られない。

## 【0134】

撮像装置100において、後段回路のばらつきをキャンセルするためにCDSを実施してもよい。具体的には、信号電圧を読み出した後、再度上述したリセット動作を行う。リセット動作完了後、第1光電変換部P C 1で光検出を行う前に、露光/読み出し期間で述べた読み出し動作を行うことにより、基準電圧を読み出すことが可能となる。信号電圧と基準電圧との差分を取ることで固定ノイズを除く信号が得られる。

20

## 【0135】

本実施の形態では、露光/読み出し期間において、読み出しノードF D 1の信号は、1倍程度の増幅率でソースフォロア回路によって読み出される。ただし、本開示はこれに限定されるものではなく、システムに必要なS/N比および回路レンジに応じて設計者は増幅率を当然に変更してもよい。

## 【0136】

本実施の形態では、更に、第1撮像セルaに配置する容量素子の容量値を大きくすることでノイズ抑制効果を大きくすることが可能である。

30

## 【0137】

また、リセット期間における読み出しノードF D 1のリセット電圧は、図9Cに示されるように接続ノードR D 1を介して供給されてもよいし、図9Fに示されるように第1反転増幅器F B A M P 1から直接供給されても構わない。また、所望の電圧値を、外部から供給する構成を採用してもよい。これらの構成の展開例により、狭面積の画素レイアウトにおいて、各ノードを接続する配線を最適化することができ、画素面積を縮小することができる。

## 【0138】

上記においては、第1撮像セル1aの動作例を説明したが、第2撮像セル1a'も第1撮像セル1aと同様に動作させることができる。また、上記においては、図9Cに示される、最も高いノイズ抑制能力を備える第1の撮像素子1aを用いたときの動作例を説明した。ただし、必要とされるノイズレベルおよび画素面積に応じて、図7に示される第1撮像セルaのように、第1帯域制御トランジスタM13がない構成を選択してもよい。この場合、第1リセットトランジスタM13には、図10のV<sub>rs</sub>3のように中間の電位を入力し、リセットをしながら帯域制限をかけても良いし、中間電位を入力せず、ローレベルとハイレベルのみを入力し、リセット動作のみを実施しても良い。他のトランジスタの動作は、上記の説明と同様の動作となる。また、図7の第2撮像セル1a'のように第1帯域制御トランジスタM23および第2フィードバック回路がない構成を選択することもできる。他のトランジスタの動作は、上記の説明と同様の動作となる。

40

## 【0139】

50

(第3の実施の形態)

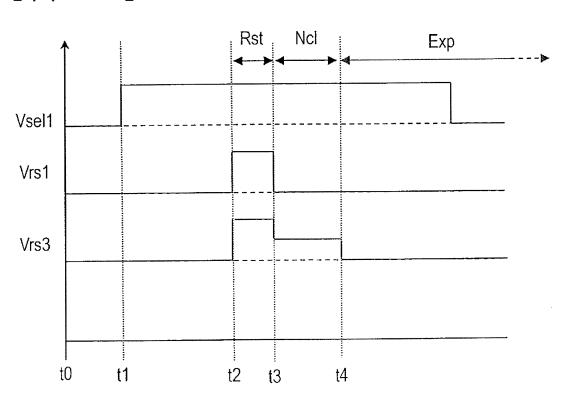

図11から図14Iを参照しながら、第3の実施の形態による単位画素1の回路構成例を説明する。

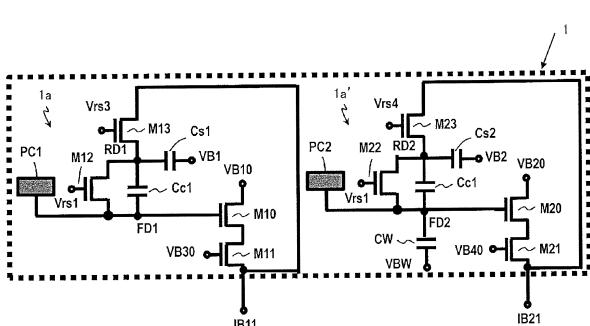

【0140】

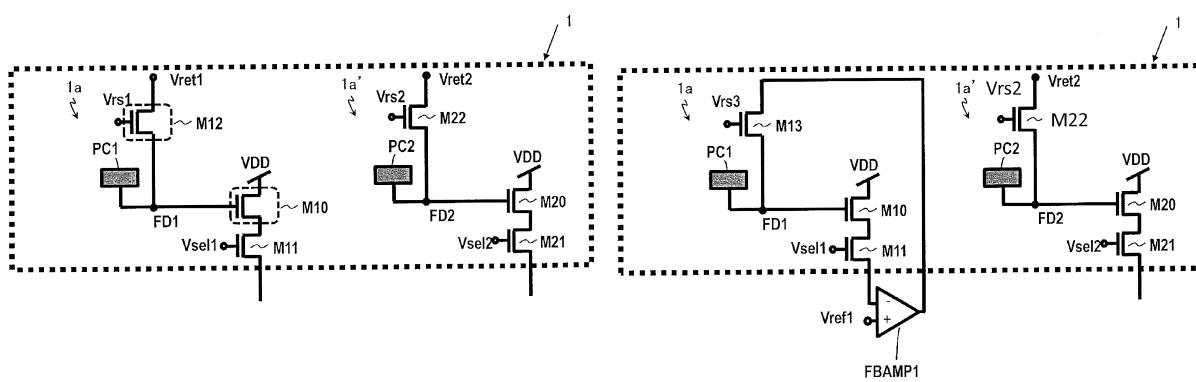

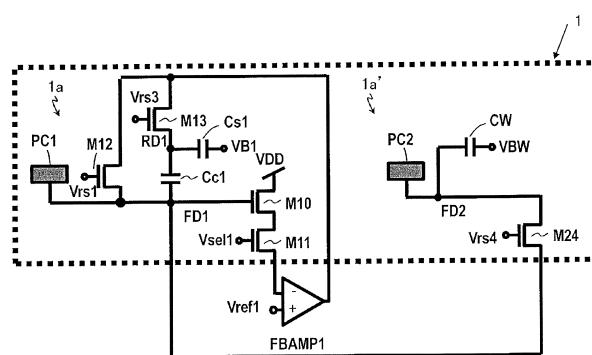

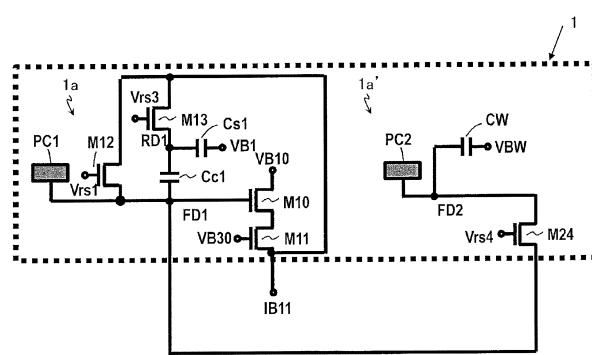

図11は、本実施の形態による単位画素1の回路構成例を示している。単位画素1は、同一画素内に、第1撮像セル1aと第2撮像セル1a'を有する。第1撮像セル1aは、低ノイズセルとして機能する。第1撮像セル1aは、光を電気信号に変換する第1光電変換部PC1と、第1光電変換部PC1に電気的に接続され、第1光電変換部PC1で生成された電気信号を読み出す第1信号処理回路P1を有する。

【0141】

第1信号処理回路P1は、第1光電変換部PC1で生成した電気信号を検出する第1信号検出回路を含む。第1信号検出回路は、第1増幅トランジスタM10と、第1選択トランジスタM11と、第1リセットトランジスタM12と、容量回路と、第1帯域制御トランジスタM13を有する。第1増幅トランジスタM10のゲートは、第1光電変換部PC1に接続されている。第1増幅トランジスタM10は、第1光電変換部PC1で生成された電気信号を増幅する。第1選択トランジスタM11のソースおよびドレインの一方は、第1増幅トランジスタM10のソースおよびドレインの一方に接続される。第1選択トランジスタM11は、第1増幅トランジスタM10で増幅された信号を選択的に出力する。第1リセットトランジスタM12のソースおよびドレインの一方は、読み出しノードFD1に接続される。第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1をリセット(初期化)する。容量回路は、一端が読み出しノードFD1に電気的に接続された第1容量素子Cc1および第1容量素子Cc1よりも大きい容量値を有する第2容量素子Cs1を備える。第1容量素子Cc1は、第2容量素子Cs1に直列に接続されている。第1帯域制御トランジスタM13のソースおよびドレインの一方は、第1容量素子Cc1と第2容量素子Cs1との間の接続ノードRD1に接続され、第1フィードバック回路の帯域制御を行う。

【0142】

第1信号処理回路はさらに、第1リセットトランジスタM12をオフする時に発生する雑音を負帰還させて抑制させる第1の帰還経路を形成する第1フィードバック回路を有する。第1フィードバック回路は、第1増幅トランジスタM10、第1帯域制御トランジスタM13および第1容量素子Cc1を介して負帰還を行う。

【0143】

第2撮像セル1a'は、高飽和セルとして機能する。第2撮像セル1a'は、光を電気信号に変換する第2光電変換部PC2と、第2光電変換部PC2に電気的に接続され、第2光電変換部PC2で生成した電気信号を読み出す第2信号処理回路P2を有する。

【0144】

第2信号処理回路P2は、第2光電変換部PC2で生成した電気信号を検出する第2信号検出回路を含む。第2信号検出回路は、第2増幅トランジスタM20と、第2選択トランジスタM21と、第2リセットトランジスタM22を有する。第2増幅トランジスタM20のゲートは、第2光電変換部PC2に接続される。第2増幅トランジスタM20は、第2光電変換部PC2で生成した電気信号を増幅する。第2選択トランジスタM21のソースおよびドレインの一方は、第2増幅トランジスタM20のソースおよびドレインの一方に接続される。第2選択トランジスタM21は、第2増幅トランジスタM20で増幅された信号を選択的に出力する。第2リセットトランジスタM22は読み出しノードFD2に接続され、第2光電変換部PC2の接続された読み出しノードFD2をリセット(初期化)する。

【0145】

第1撮像セル1aは、暗いシーンの撮像を担うので、低ノイズ特性を必要とするが、高飽和特性を特に必要としない。一方、第2撮像セル1a'は、明るいシーンの撮像を担うので、高飽和特性を必要とする。しかし、明るいシーンの撮像では、光の量が多く、ショ

10

20

30

40

50

ットノイズで特性が決定されるので、第2撮像セル1a'は低ノイズ特性を特に必要としない。

【0146】

第1撮像セル1aは、第1フィードバック回路を備えるので、第1リセットトランジスタM12オフ時に発生する雑音を大幅に抑制できる。一方、第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。さらに、第1増幅トランジスタM10のゲート幅を、第2増幅トランジスタM20のゲート幅よりも大きくしてもよい。これにより、第1増幅トランジスタM10のgmを大きく設定することができる。その結果、第1撮像セル1aの読み出しノイズを低減することができる。一方、第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。また、第1リセットトランジスタM12のゲート長を、第2リセットトランジスタM22のゲート長よりも大きくしてもよい。これにより、第1撮像セル1aのノイズ低減効果がさらに向上する。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。

【0147】

図12および図13は、本実施形態による単位画素1の他の回路構成例を示している。図12に示すように、第2光電変換部PC2と基準電圧VBWとの間に電気的に接続された第5容量素子CWを設けている。これにより、第2撮像セル1a'の高飽和特性を容量比分だけ向上させることができる。その結果、さらなるダイナミックレンジの拡大を図ることも可能である。また、第1リセットトランジスタM12の接続方法を変えることで、リセット電圧の設定方法を変えることも可能である。その結果、リセット電圧への収束時間の短縮が図れる。

【0148】

本実施の形態によれば、無駄な画素のサイズの増加を抑制することができる。また、本実施の形態によれば、第1撮像セル1aで低ノイズ高感度撮像を行うと同時に、第2撮像セル1a'で高飽和低感度撮像を行うことが可能な、小型の撮像装置を提供できる。また、本実施の形態によれば、明暗差が大きな被写体を、時間ずれなく、かつ、白飛びおよび黒潰れなく撮像できる。

【0149】

図11に示されるように、第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1と、第1容量素子Cc1と第2容量素子Cs1との間の接続ノードRD1と、の間に接続されていることが望ましい。または、図13に示されるように、第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1と、第1帯域制御トランジスタM13のソースおよびドレインのうち接続ノードRD1と接続されていない方との間に接続されることが望ましい。このような構成によれば、リセット電圧Vreset(=VRST)を別途設けなくてもよい。また、帰還をかけてリセット値近傍に収束させることができるので、ノイズキャンセルの高速化が図れる。

【0150】

本実施の形態による第1および第2撮像セル1a、1a'のさらなる他の回路構成例を説明する。

【0151】

図14Aから図14Iは、本実施の形態による単位画素1のさらなる他の回路構成例を示している。図11、図12、図13、および、図14A～図14Iに示される構成は、第2の実施の形態の図9Cから図9Nに示される構成に対応する。これらの間では、第1撮像セル1aにおけるノイズ抑制を行う第1フィードバック回路の構成と、第1フィードバック回路の動作とが異なっており、その他の構成および動作は共通している。

【0152】

以下、本実施の形態による第1撮像セル1aの動作を説明する。

【0153】

(読み出しおよびノイズ抑制)

10

20

30

40

50

図11に示される第1撮像セル1aを用いた、ノイズ抑制およびデータの読み出し動作を具体例として説明する。

【0154】

第1信号処理回路P1において、第1帯域制御トランジスタM13のソースおよびドレインの一方には、第2容量素子Cs1の一端が接続される。第1帯域制御トランジスタM13と第2容量素子Cs1により、RCフィルタ回路が形成される。さらに、第1帯域制御トランジスタM13のソースおよびドレインの一方には第1容量素子Cc1の一端も接続される。第1容量素子Cc1の他端は、第1の読み出しノードFD1に接続される。

【0155】

第1帯域制御トランジスタM13のゲートには第1の帯域制御信号Vrs3が入力され、第1の帯域制御信号Vrs3の電位により第1帯域制御トランジスタM13の状態が決定される。例えば、第1の帯域制御信号Vrs3がハイレベルの場合、第1帯域制御トランジスタM13はオンし、読み出しノードFD1と、第1増幅トランジスタM10と、第1帯域制御トランジスタM13と、第1容量素子Cc1とで帰還経路が形成される。第1の帯域制御信号Vrs3の電位が低くなると第1帯域制御トランジスタM13の抵抗成分が大きくなるので、第1帯域制御トランジスタM13の帯域は狭くなり、帰還する信号の周波数領域が狭くなる。帰還が形成されている時、第1帯域制御トランジスタM13が 출력する信号は、第1容量素子Cc1と読み出しノードFD1の寄生容量とによって形成される減衰回路で減衰されて、読み出しノードFD1に帰還される。第1容量素子Cc1の容量値をCc、読み出しノードFD1の寄生容量をCFDとすると、減衰率Bは、 $B = Cc / (Cc + CF D)$ となる。更に第1の帯域制御信号Vrs3の電位が低くなり、ローレベルになると、第1帯域制御トランジスタM13はオフし、帰還は形成されない。読み出しノードFD1は更に第1リセットトランジスタM12のソースおよびドレインの一方に接続される。第1リセットトランジスタM12のソースおよびドレインの他方は、接続ノードRD1に接続される。

【0156】

第1リセットトランジスタM12のゲートには、第1のリセット制御信号Vrs1が入力され、第1のリセット制御信号Vrs1の電位により、第1リセットトランジスタM12の状態が決定される。例えば、第1のリセット制御信号Vrs1がハイレベルの場合、第1リセットトランジスタM12はオンし、読み出しノードFD1は接続ノードRD1と同一の電圧となる。このとき、第1の帯域制御信号Vrs3もハイレベルの場合、第1リセットトランジスタM12、および、第1帯域制御トランジスタM13は共にオンし、読み出しノードFD1と接続ノードRD1は共に、所望のリセット電圧V\_RSTになる。第1選択トランジスタM11のソースおよびドレインの一方は、垂直信号線9に接続される。第1選択トランジスタM11のゲートには、第1の選択制御信号Vsel1が入力され、第1の選択制御信号Vsel1の電位により第1選択トランジスタM11の状態が決定される。例えば、第1の選択制御信号Vsel1がハイレベルの場合、第1選択トランジスタM11はオンし、第1増幅トランジスタM10と垂直信号線9は電気的に接続された状態となる。第1の選択制御信号Vsel1がローレベルの場合、第1選択トランジスタM11はオフし、第1増幅トランジスタM10と垂直信号線9とは電気的に分離された状態となる。

【0157】

図15は、第1撮像セル1aの第1信号処理回路P1の一部を示している。第1増幅トランジスタM10のソースおよびドレインの一方には、第1の切り替え回路SWC1が接続される。第1の切り替え回路SWC1は、スイッチ素子SW10A、SW10Bを含む。スイッチ素子SW10A、SW10Bはそれぞれ、基準電圧VB10A、VB10Bに接続される。第1増幅トランジスタM10のソースおよびドレインの一方には、スイッチ素子SW10Aを介して基準電圧VB10Aが入力可能であり、スイッチ素子SW10Bを介して基準電圧VB10Bが入力可能である。制御信号により、第1増幅トランジスタM10のソースおよびドレインの一方の電圧を切り替えることができる。基準電圧VB1

10

20

30

40

50

0 A は例えば GND であり、基準電圧 V<sub>B10B</sub> は例えば VDD である。なお、第 1 の切り替え回路 SWC1 は、単位画素毎に設けても良く、単位画素あたりの素子数を削減するために複数の単位画素で共有しても良い。

【0158】

垂直信号線 9 には、第 2 の切り替え回路 SWC2 が接続されている。第 2 の切り替え回路 SWC2 は、スイッチ素子 SW11A、SW11B を含む。スイッチ素子 SW11A、SW11B はそれぞれ、定電流源 IB11A、IB11B を介して、基準電圧 V<sub>B11A</sub>、V<sub>B11B</sub> に接続される。基準電圧 V<sub>B11A</sub> は、例えば VDD であり、基準電圧 V<sub>B11B</sub> は、例えば GND である。

【0159】

スイッチ素子 SW10A、SW11A が選択的にオンされているとする。その場合、第 1 の選択制御信号 V<sub>sel1</sub> の電位がハイレベルであると、第 1 選択トランジスタ M11 はオンされ、定電流源 IB11A と第 1 増幅トランジスタ M10 とは反転増幅回路を形成する。これにより、読み出しノード FD1 と、第 1 増幅トランジスタ M10 と、第 1 帯域制御トランジスタ M13 と、第 1 容量素子 Cc1 とで帰還経路が形成される。

【0160】

スイッチ素子 SW10B、SW11B が選択的にオンされているとする。その場合、第 1 の選択制御信号 V<sub>sel1</sub> の電位がハイレベルであると、第 1 選択トランジスタ M11 はオンされ、第 1 増幅トランジスタ M10 と定電流源 IB11B はソースフォロア回路を形成する。これにより、読み出しノード FD1 の信号が、垂直信号線 9 に出力されることとなる。

【0161】

(第 1 撮像セル 1a の動作)

図 16 は、本実施の形態による第 1 撮像セル 1a の動作タイミングの一例を示している。

【0162】

[リセット期間]

まず、第 1 の選択制御信号 V<sub>sel1</sub> をハイレベルにする。さらに、第 1 および第 2 の切り替え回路 SWC1、SWC2 のそれぞれを制御して、垂直信号線 9 に定電流源 IB11A を接続し、かつ、第 1 増幅トランジスタ M10 のソースおよびドレインの一方を基準電圧 V<sub>B10A</sub> にする (時刻 t1)。次に、第 1 の帯域制御信号 V<sub>rs3</sub> の電位をハイレベルにして第 1 帯域制御トランジスタ M13 をオン状態に設定する。さらに、第 1 のリセット信号 V<sub>rs1</sub> をハイレベルにして、第 1 リセットトランジスタ M12 をオン状態に設定する (時刻 t2)。これにより、読み出しノード FD1 の電圧は、リセット電圧 V<sub>RS</sub> T に等しくなる。

【0163】

[ノイズ抑制期間]

次に、第 1 のリセット制御信号 V<sub>rs1</sub> をローレベルにし、第 1 リセットトランジスタ M12 をオフ状態に設定する (時刻 t3)。このとき、第 1 信号検出回路は、増幅率 (= -A × B) で帰還を形成しているので、第 1 リセットトランジスタ M12 をオフした時の読み出しノード FD1 の kTC ノイズは、1 / (1 + A × B) に抑制される。また、このとき、第 1 帯域制御トランジスタ M13 の動作帯域が広帯域である第 1 の帯域となるよう、第 1 の帯域制御信号 V<sub>rs3</sub> の電位が設定されることにより、高速にノイズが抑制される。

【0164】

同時に、第 1 の帯域制御信号 V<sub>rs3</sub> をハイレベルとローレベルとの中間の電位に設定する (時刻 t3)。なお、このタイミングは、時刻 t3 よりも若干遅れたタイミングであってもよい。このとき、第 1 帯域制御トランジスタ M13 の動作帯域は、第 1 の帯域よりも低い第 2 の帯域となる。なお、第 2 の帯域を、第 1 増幅トランジスタ M10 の動作帯域よりも十分に低くすることで、ノイズ抑制効果は大きくなる。ただし、これとトレードオ

10

20

30

40

50

フに、ノイズ抑制に必要な時間は長くなる。第2の帯域が第1增幅トランジスタM10の動作帯域よりも高くてもノイズ抑制効果は得られる。ノイズ抑制に掛ける時間に応じて、設計者は第2の帯域を任意に設計することは可能である。本実施の形態では、第2の帯域が、第1增幅トランジスタM10の動作帯域よりも十分に低い状態にあるとする。

#### 【0165】

第2の帯域が、第1增幅トランジスタM10の動作帯域よりも低い状態においては、第1帯域制御トランジスタM13で発生する熱ノイズは、フィードバック回路により、 $1/(1 + A \times B)^{1/2}$ 倍に抑制される。この状態で、第1の帯域制御信号V<sub>rs3</sub>をローレベルに設定し、帯域制御トランジスタをオフにする（時刻t4）。そのときに読み出しノードFD1に残存するk<sub>TC</sub>ノイズは、第1リセットトランジスタM12に起因したk<sub>TC</sub>ノイズと、第1帯域制御トランジスタM13に起因したk<sub>TC</sub>ノイズとを二乗和した値となる。第2容量素子C<sub>s1</sub>の容量値をC<sub>s</sub>とすると、帰還による抑制がない状態で発生する第1帯域制御トランジスタM13のk<sub>TC</sub>ノイズは、帰還による抑制がない状態で発生する第1リセットトランジスタM12のk<sub>TC</sub>ノイズに比べて(CFD/C<sub>s</sub>)<sup>1/2</sup>倍になる。この点を考慮して、帰還がない場合と比較すると、k<sub>TC</sub>ノイズは、 $[1 + (1 + A \times B) \times CFD/C_s]^{1/2} / (1 + A \times B)$ 倍に抑制される。

10

#### 【0166】

なお、第1帯域制御トランジスタM13がオン状態からオフ状態に徐々に変化するよう、第1帯域制御トランジスタM13のしきい値電圧を跨いで変化するような電位に第1の帯域制御信号V<sub>rs3</sub>を制御してもよい。これにより、撮像装置100を構成する複数の単位画素1の間で第1帯域制御トランジスタM13のしきい値電圧にばらつきがあっても、全ての単位画素1のノイズを抑制することが可能となる。更に、変化させる第1の帯域制御信号V<sub>rs3</sub>の電圧範囲を、単位画素1のばらつきの範囲に制限してもよい。これにより、変化させるのに必要な時間を短縮でき、かつ、高速なノイズ抑制が可能となる。

20

#### 【0167】

##### 〔露光／読み出し期間〕

次に、第1および第2の切り替え回路SWC1、SWC2のそれぞれを制御することで、垂直信号線9に定電流源IB11Bを接続し、かつ、第1增幅トランジスタM10のソースおよびドレインの一方の電位を基準電圧VB10Bにする。この状態においては、第1增幅トランジスタM10と定電流源IB11Bとがソースフォロア回路を構成し、垂直信号線9の電位は、読み出しノードFD1の電位に応じたレベルとなる。ただし、ソースフォロア回路の増幅率は1倍程度である。このとき、読み出しノードFD1には、ノイズ抑制完了時（時刻t4）から読み出し時までに第1光電変換部PC1で変換された電気信号に応じた分だけ変化した電圧信号が蓄積されている。読み出しノードFD1の電圧信号は、ソースフォロア回路により1倍程度の増幅率で垂直信号線9に出力される。ここで、ランダムノイズは第1光電変換部PC1で変換される電気信号が0の時の出力の揺らぎ、すなわち、k<sub>TC</sub>ノイズである。k<sub>TC</sub>ノイズは、リセット抑制期間において $[1 + (1 + A \times B) \times CFD/C_s]^{1/2} / (1 + A \times B)$ 倍に抑制される。更に、露光／読み出し期間において、1倍程度の増幅率で垂直信号線9に出力されるので、本実施の形態によれば、ランダムノイズが抑制された良好な画像データを取得することができる。

30

#### 【0168】

面積が許す限り第2容量素子C<sub>s1</sub>を大きくすることにより、ランダムノイズは抑制される。通常、容量を大きくすると、ランダムノイズは低減される。しかし、読み出しノードFD1で電荷信号を電圧信号に変換する際、信号自体が小さくなってしまう。その結果としてS/Nは改善されない。

40

#### 【0169】

本実施の形態においては、読み出しノードFD1と接続ノードRD1とが第1容量素子C<sub>c1</sub>によって分離されているので、第2容量素子C<sub>s1</sub>の容量を大きくしても信号低下は起こらない。ランダムノイズだけが抑制されるので、S/N比が改善されるという利点がある。従って、本実施の形態は、単位画素1の面積を広くとれるような用途の撮像装置

50

において有効である。

【0170】

例えば図4に示されるような、垂直信号線9の信号を検出するための後段回路を接続することができる。後段回路は、例えば第1の垂直走査回路2、第2の垂直走査回路2'、第1の列A/D変換回路4および第2の列A/D変換回路4'から構成される。ただし、本開示はこのような回路構成に限られない。

【0171】

撮像装置100において、後段回路のばらつきをキャンセルするためにCDSを実施してもよい。具体的には、信号電圧を読み出した後、再度上述したリセット動作を行う。リセット動作完了後、第1光電変換部PC1で光検出を行う前に、露光/読み出し期間で述べた読み出し動作を行うことにより、基準電圧を読み出すことが可能となる。信号電圧と基準電圧との差分を取ることで固定ノイズを除く信号が得られる。

10

【0172】

本実施の形態では、露光/読み出し期間において、読み出しノードFD1の信号は、1倍程度の増幅率でソースフォロア回路によって読み出される。ただし、本開示はこれに限定されるものではなく、システムに必要なS/N比および回路レンジに応じて設計者は増幅率を当然に変更してもよい。また、リセット期間における読み出しノードFD1のリセット電圧は、図11に示されるような接続ノードRD1を介して供給されてもよいし、図13に示されるように第1増幅トランジスタM10から直接供給されても構わない。また、所望の電圧値を外部から供給する構成を採用してもよい。これらの構成の展開例により、狭面積の画素レイアウトにおいて、各ノードを接続する配線を最適化することができ、画素面積を縮小することが可能となる。

20

【0173】

本実施の形態によれば、電流源を除き、ノイズキャンセルのための帰還を画素内で行うことができる。これにより、垂直信号線9の時定数の影響を小さくでき、高速なノイズキャンセルが可能となる。更に、単位画素1に配置する容量素子の容量値を大きくすることによりノイズ抑制効果を大きくすることが可能である。

30

【0174】

(第4の実施の形態)

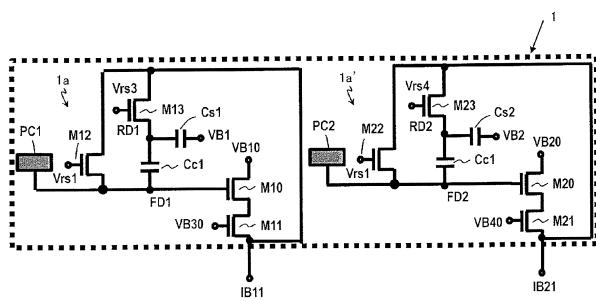

図17から図20Iを参照しながら、第4の実施の形態による単位画素1の回路構成例を説明する。

【0175】

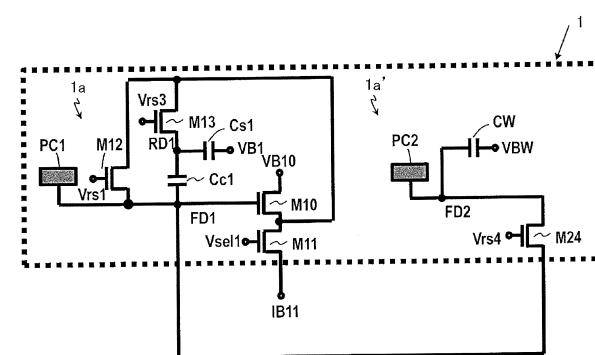

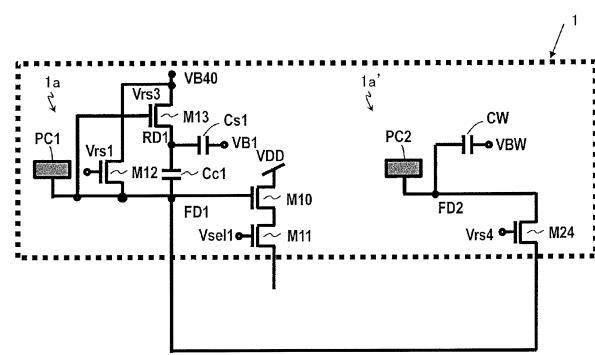

図17は、本実施の形態による単位画素1の回路構成例を示している。単位画素1は、同一画素内に、第1撮像セル1aと第2撮像セル1a'とを有する。第1撮像セル1aは、低ノイズセルとして機能する。第1撮像セル1aは、光を電気信号に変換する第1光電変換部PC1と、第1光電変換部PC1に電気的に接続され、第1光電変換部PC1で生成された電気信号を読み出す第1信号処理回路P1とを有する。

【0176】

第1信号処理回路P1は、第1光電変換部PC1で生成した電気信号を検出する第1信号検出回路を含む。第1信号検出回路は、第1増幅トランジスタM10と、第1選択トランジスタM11と、第1リセットトランジスタM12と、容量回路と、第1帯域制御トランジスタM13とを有する。第1増幅トランジスタM10のゲートは、第1光電変換部PC1に接続されている。第1増幅トランジスタM10は、第1光電変換部PC1で変換された電気信号を増幅する。第1選択トランジスタM11のソースおよびドレインの一方は、第1増幅トランジスタM10のソースおよびドレインの一方に接続される。第1選択トランジスタM11は、第1増幅トランジスタM10で増幅された信号を選択的に出力する。また、第1増幅トランジスタM10と第1選択トランジスタM11とは、フィードバック回路における帰還動作時に、カスコード接続を構成する。第1リセットトランジスタM12のソースおよびドレインの一方は、読み出しノードFD1に接続される。第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1をリ

40

50

セット（初期化）する。容量回路は、一端が読み出しノード F D 1 に電気的に接続された第 1 容量素子 C c 1 および第 1 容量素子 C c 1 よりも大きい容量値を有する第 2 容量素子 C s 1 を備える。第 1 容量素子 C c 1 は、第 2 容量素子 C s 1 に直列に接続されている。第 1 帯域制御トランジスタ M 1 3 のソースおよびドレインの一方は、第 1 容量素子 C c 1 と第 2 容量素子 C s 1 との間の接続ノード R D 1 に接続され、第 1 フィードバック回路の帯域制御を行う。

#### 【 0 1 7 7 】

第 1 信号処理回路はさらに、第 1 リセットトランジスタ M 1 2 をオフする時に発生する雑音を負帰還させて抑制させる第 1 の帰還経路を形成する第 1 フィードバック回路を有する。第 1 フィードバック回路は、第 1 増幅トランジスタ M 1 0 、第 1 選択トランジスタ M 1 1 、第 1 帯域制御トランジスタ M 1 3 および第 1 容量素子 C c 1 を介して負帰還を行う。

#### 【 0 1 7 8 】

第 2 撮像セル 1 a ' は、高飽和セルとして機能する。第 2 撮像セル 1 a ' は、光を電気信号に変換する第 2 光電変換部 P C 2 と、第 2 光電変換部 P C 2 に電気的に接続され、第 2 光電変換部 P C 2 で生成された電気信号を読み出す第 2 信号処理回路 P 2 とを有する。

#### 【 0 1 7 9 】

第 2 信号処理回路 P 2 は、第 2 光電変換部 P C 2 で生成した電気信号を検出する第 2 信号検出回路を含む。第 2 信号検出回路は、第 2 増幅トランジスタ M 2 0 と、第 2 選択トランジスタ M 2 1 と、第 2 リセットトランジスタ M 2 2 とを有する。第 2 増幅トランジスタ M 2 0 のゲートは、第 2 光電変換部 P C 2 に接続されている。第 2 増幅トランジスタ M 2 0 は、第 2 光電変換部 P C 2 で生成した電気信号を増幅する。第 2 選択トランジスタ M 2 1 ソースおよびドレインの一方は、第 2 増幅トランジスタ M 2 0 のソースおよびドレインの一方へ接続される。第 2 選択トランジスタ M 2 1 は、第 2 増幅トランジスタ M 2 0 で増幅された信号を選択的に出力する。第 2 リセットトランジスタ M 2 2 は読み出しノード F D 2 に接続され、第 2 光電変換部 P C 2 に接続された読み出しノード F D 2 をリセット（初期化）する。

#### 【 0 1 8 0 】

第 1 撮像セル 1 a は、暗いシーンの撮像を担うので、低ノイズ特性を必要とするが、高飽和特性を特に必要としない。一方、第 2 撮像セル 1 a ' は、明るいシーンの撮像を担うので、高飽和特性を必要とする。しかし、明るいシーンの撮像では、光の量が多く、ショットノイズで特性が決定されるので、第 2 撮像セル 1 a ' は低ノイズ特性を特に必要としない。

#### 【 0 1 8 1 】

第 1 撮像セル 1 a は、第 1 フィードバック回路を備えるので、第 1 リセットトランジスタ M 1 2 をオフする時に発生する雑音を大幅に抑制できる。一方、第 2 撮像セル 1 a ' のノイズ特性は従来相当であっても問題とはならない。さらに、第 1 増幅トランジスタ M 1 0 のゲート幅を、第 2 増幅トランジスタ M 2 0 のゲート幅よりも大きくしてもよい。これにより、第 1 増幅トランジスタ M 1 0 の g m を大きく設定することができる。その結果、第 1 撮像セル 1 a の読み出しノイズを低減することができる。一方、第 2 撮像セル 1 a ' のノイズ特性は従来相当であっても問題とはならない。また、第 1 リセットトランジスタ M 1 2 のゲート長を、第 2 リセットトランジスタ M 2 2 のゲート長よりも大きくしてもよい。これにより、第 1 撮像セル 1 a のノイズ低減効果がさらに向上する。第 2 撮像セル 1 a ' のノイズ特性は従来相当であっても問題とはならない。

#### 【 0 1 8 2 】

図 1 8 および図 1 9 は、本実施の形態による単位画素 1 の他の回路構成例を示している。図 1 8 に示すように、第 2 光電変換部 P C 2 と基準電圧 V B W との間に電気的に接続された第 5 容量素子 C W を設けている。これにより、第 2 撮像セル 1 a ' の高飽和特性を容量比で向上させることができる。その結果、さらなるダイナミックレンジの拡大を図ることも可能である。また、第 1 リセットトランジスタ M 1 2 の接続方法を変えることで

10

20

30

40

50

、リセット電圧の設定方法を変えることも可能である。その結果、リセット電圧への収束時間の短縮が図れる。

#### 【0183】

本実施の形態によれば、無駄な画素のサイズの増加を抑制することができる。また、本実施の形態によれば、第1撮像セル1aで低ノイズ高感度撮像を行うと同時に、第2撮像セル1a'で高飽和低感度撮像を行うことが可能な、小型の撮像装置を提供できる。また、本実施の形態によれば、明暗差が大きな被写体を、時間ずれなく、かつ、白飛びおよび黒潰れなく撮像できる。

#### 【0184】

図17に示されるように、第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1と、第1容量素子Cc1と第2容量素子Cs1との接続ノードRD1との間に接続されていることが望ましい。または、図19に示されるように、第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1と、第1帯域制御トランジスタM13のソースおよびドレインのうち接続ノードRD1と接続されていない方との間に接続されることが望ましい。このような構成によれば、リセット電圧Vret(=VRST)を別途設けなくてもよい。また、帰還をかけてリセット値近傍に収束させることができるので、ノイズキャンセルの高速化が図れる。

#### 【0185】

本実施の形態による第1および第2撮像セル1a、1a'のさらなる他の回路構成例を説明する。

#### 【0186】

図20Aから図20Iは、第1および第2撮像セル1a、1a'のさらなる他の回路構成例を示している。図17、図18、図19、図20A～図20Iに示される構成は、第3の実施の形態の図11、図12、図13、図14Aから図14Iに示される構成に対応する。これらの間では、第1撮像セル1aにおけるノイズ抑制を行う第1フィードバック回路の構成と、第1フィードバック回路の動作とが異なっており、その他の構成および動作は共通している。

#### 【0187】

以下、本実施の形態による第1撮像セル1aの動作を説明する。

#### 【0188】

(読み出しおよびノイズ抑制)

図17に示される第1撮像セル1aを用いた、ノイズ抑制およびデータの読み出し動作を具体例として説明する。

#### 【0189】

第3の実施の形態においては、第1增幅トランジスタM11のソースおよびドレインの一方が、第1帯域制御トランジスタM13のソースおよびドレインの一方に接続されことで帰還が形成される。第4の実施の形態においては、第1選択トランジスタM11のソースおよびドレインのうち第1增幅トランジスタに接続されていない方が、第1帯域制御トランジスタM13のソースおよびドレインの一方に接続されることで帰還が形成される。換言すると、第3の実施の形態においては、読み出しノードFD1、第1增幅トランジスタM10、第1帯域制御トランジスタM13、および第1容量素子Cc1を介して帰還が形成される。一方、第4の実施の形態においては、読み出しノードFD1、第1增幅トランジスタM10、第1選択トランジスタM11、第1帯域制御トランジスタM13、および第1容量素子Cc1を介して帰還が形成される。

#### 【0190】

第3の実施の形態では、第1選択トランジスタM11は、垂直信号線9との接続状態を切り替える機能のみを有する。一方、第4の実施の形態では、第1選択トランジスタM11は、上記の機能に加えて、帰還経路の形成にも関与する。具体的には、ノイズ抑制時に、第1選択トランジスタM11に入力されるバイアス制御信号VB30は、ハイレベルとローレベルの中間の電位に設定される。このとき、第1增幅トランジスタM10と、第1

10

20

30

40

50

選択トランジスタM11と、電流源IB11Aとで、カスコード接続となる反転増幅器を構成する。これにより、反転増幅器の利得を大幅に向上させることが可能となる。その結果、利得が向上した分だけ、第1撮像セル1aの低ノイズ化を実現できる。

#### 【0191】

(第5の実施の形態)

図21から図24Iを参照しながら、第5の実施の形態による単位画素1の回路構成例を説明する。

#### 【0192】

図21は、本実施の形態による単位画素1の回路構成例を示している。単位画素1は、同一画素内に、第1撮像セル1aと第2撮像セル1a'を有する。第1撮像セル1aは、低ノイズセルとして機能する。第1撮像セル1aは、光を電気信号に変換する第1光電変換部PC1と、第1光電変換部PC1に電気的に接続され、第1光電変換部PC1で生成した電気信号を読み出す第1信号処理回路P1を有する。

10

#### 【0193】

第1信号処理回路P1は、第1光電変換部PC1で生成した電気信号を検出する第1信号検出回路を含む。第1信号検出回路は、第1増幅トランジスタM10と、第1選択トランジスタM11と、第1リセットトランジスタM12と、容量回路と、第1帯域制御トランジスタM13を有する。第1増幅トランジスタM10のゲートは、第1光電変換部PC1に接続されている。第1増幅トランジスタM10は、第1光電変換部PC1で生成した電気信号を増幅する。第1選択トランジスタM11のソースおよびドレインの一方は、第1増幅トランジスタM10のソースおよびドレインの一方に接続される。第1選択トランジスタM11は、第1増幅トランジスタM10で増幅された信号を選択的に出力する。第1リセットトランジスタM12のソースおよびドレインの一方は、読み出しノードFD1に接続されている。第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1をリセット(初期化)する。容量回路は、一端が読み出しノードFD1に電気的に接続された第1容量素子Cc1および第1容量素子Cc1よりも大きい容量値を有する第2容量素子Cs1を備える。第1容量素子Cc1は、第2容量素子Cs1に直列に接続されている。第1帯域制御トランジスタM13のソースおよびドレインの一方は、第1容量素子Cc1と第2容量素子Cs1との間の接続ノードRD1に接続され、第1フィードバック回路の帯域制御を行う。

20

#### 【0194】

第1信号処理回路はさらに、第1リセットトランジスタM12をオフする時に発生する雑音を負帰還させて抑制させる第1の帰還経路を形成する第1フィードバック回路を有する。第1フィードバック回路は、第1帯域制御トランジスタM13および第1容量素子Cc1を介して負帰還を行う。第1帯域制御トランジスタM13のゲートを反転増幅器の入力端子とし、第1帯域制御トランジスタM13のソースおよびドレインの一方を反転増幅器の出力端子として、負帰還が行われる。

30

#### 【0195】

第2撮像セル1a'は、高飽和セルとして機能する。第2撮像セル1a'は、光を電気信号に変換する第2光電変換部PC2と、第2光電変換部PC2に電気的に接続され、第2光電変換部PC2で生成された電気信号を読み出す第2信号処理回路P2を有する。

40

#### 【0196】

第2信号処理回路P2は、第2光電変換部PC2で生成した電気信号を検出する第2信号検出回路を含む。第2信号検出回路は、第2増幅トランジスタM20と、第2選択トランジスタM21と、第2リセットトランジスタM22を有する。第2増幅トランジスタM20のゲートは、第2光電変換部PC2に接続されている。第2増幅トランジスタM20は、第2光電変換部PC2で生成された電気信号を増幅する。第2選択トランジスタM21のソースおよびドレインの一方は、第2増幅トランジスタM20のソースおよびドレインの一方接続される。第2選択トランジスタM21は、第2増幅トランジスタM20で増幅された信号を選択的に出力する。第2リセットトランジスタM22のソースおよび

50

ドレインの一方は、読み出しノードに接続されている。第2リセットトランジスタM22は、第2光電変換部P C 2に接続された読み出しノードをリセット(初期化)する。

【0197】

第1撮像セル1aは、暗いシーンの撮像を担うので、低ノイズ特性を必要とするが、高飽和特性を特に必要としない。一方、第2撮像セル1a'は、明るいシーンの撮像を担うので、高飽和特性を必要とする。しかし、明るいシーンの撮像では、光の量が多く、ショットノイズで特性が決定されるので、第2撮像セル1a'は低ノイズ特性を特に必要としない。

【0198】

第1撮像セル1aは、第1フィードバック回路を備えるので、第1リセットトランジスタM12をオフする時に発生する雑音を大幅に抑制できる。一方、第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。さらに、第1増幅トランジスタM10のゲート幅を、第2増幅トランジスタM20のゲート幅よりも大きくしてもよい。これにより、第1増幅トランジスタM10のg<sub>m</sub>を大きく設定することができる。その結果、第1撮像セル1aの読み出しノイズを低減することができる。一方、第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。また、第1リセットトランジスタM12のゲート長を、第2リセットトランジスタM22のゲート長よりも大きくしてもよい。これにより、第1撮像セル1aのノイズ低減効果がさらに向上する。第2撮像セル1a'のノイズ特性は従来相当であっても問題とはならない。

【0199】

図22および図23は、本実施の形態による単位画素1の他の回路構成例を示している。図22に示すように、第2光電変換部P C 2と基準電圧V B Wとの間に電気的に接続された第5容量素子C Wを設けている。これにより、第2撮像セル1a'の高飽和特性を容量比分だけ向上させることができる。その結果、さらなるダイナミックレンジの拡大を図ることも可能である。

【0200】

本実施の形態によれば、無駄な画素のサイズの増加を抑制することができる。また、本実施の形態によれば、第1撮像セル1aで低ノイズ高感度撮像を行うと同時に、第2撮像セル1a'で高飽和低感度撮像を行うことが可能な、小型の撮像装置を提供できる。また、本実施の形態によれば、明暗差が大きな被写体を、時間ずれなく、かつ、白飛びおよび黒潰れなく撮像できる。

【0201】

図21に示されるように、第1リセットトランジスタM12は、第1光電変換部P C 1に接続された読み出しノードF D 1と、第1容量素子C c 1と第2容量素子C s 1との間の接続ノードR D 1と、の間に接続されていることが望ましい。または、図23に示されるように、第1リセットトランジスタM12は、第1光電変換部P C 1に接続された読み出しノードF D 1と、第1帯域制御トランジスタM13のソースおよびドレインのうち接続ノードR D 1と接続されていない方との間に接続されることが望ましい。このような構成によれば、リセット電圧V r e t (=V R S T)を別途設けなくてもよい。また、帰還をかけてリセット値近傍に収束させることができるので、ノイズキャンセルの高速化が図れる。

【0202】

本実施の形態による第1および第2撮像セル1a、1a'のさらなる他の回路構成例を説明する。

【0203】

図24Aから図24Iは、第1および第2撮像セル1a、1a'のさらなる他の回路構成例を示している。図21、図22、図23、図24Aから図24Iに示される構成は、第3の実施の形態の図11、図12、図13、図14Aから図14Iに示される構成に対応する。これらの間では、第1撮像セル1aにおけるノイズ抑制を行う第1フィードバック回路の構成と、第1フィードバック回路の動作とが異なっており、その他の構成および

10

20

30

40

50

動作は共通している。

【0204】

以下、本実施の形態による第1撮像セル1aの動作を説明する。

【0205】

(読み出しおよびノイズ抑制動作)

図21に示される第1撮像セル1aを用いた、ノイズ抑制およびデータの読み出し動作を具体例として説明する。本構成において特筆すべき点は下記のとおりである。

【0206】

(A) 第1から第4の実施の形態とは異なり、第1帯域制御トランジスタM13が増幅機能と帯域制御機能とを同一回路で担う。第1帯域制御トランジスタM13のソースおよびドレインの一方を、第1帯域制御トランジスタM13のゲートに接続して自己バイアスさせる。これにより、自らが帯域制御を行いながら、自らの増幅機能(= -A)で負帰還をかけてkTCノイズを $1/(1+A)^{1/2}$ まで抑制する。

10

【0207】

(B) 読み出し時間以外に、第1の選択制御信号Vsel1をローレベルにして第1選択トランジスタM11をオフして、第1撮像セル1aを垂直信号線9から電気的に切り離した状態で、ノイズを抑制できる。このため、単位画素のサイズが大きい構成または単位画素数が多い構成のように、垂直信号線9の寄生成分が大きい場合であっても、その影響を受け難い。これは大きな利点である。

【0208】

20

(C) 垂直信号線9から電気的に切り離した状態でノイズ抑制ができるので、フィードバック線が不要となり、面積的な利点が得られる。さらに、垂直信号線9に対するカップリング容量が発生し難い。

【0209】

(D) 第1から第4の実施の形態では、第1の帯域制御信号Vrst3を用いて第1帯域制御トランジスタM13の帯域制御を行っていた。しかし、本実施の形態では、基準電圧VB50を用いて第1帯域制御トランジスタM13の帯域制御を行うことができる。

【0210】

第1から第5の実施の形態による第1撮像セル1aおよび第2撮像セル1a'の各構造および各動作は、本出願人による未公開の特許出願である特願2015-207381号および特願2015-207303号により詳細に記載されている。これらの開示内容の全てを参考のために本願明細書に援用する。

30

【0211】

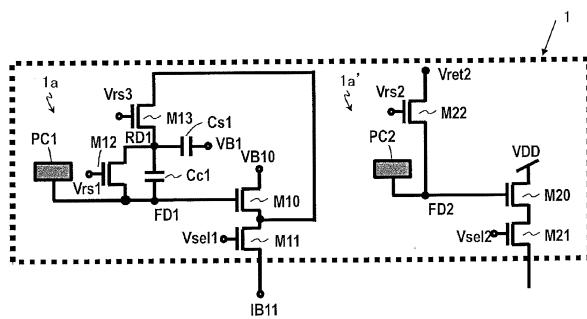

(第6の実施の形態)

図25から図26Iを参照しながら、第6の実施の形態による単位画素1の回路構成例を説明する。

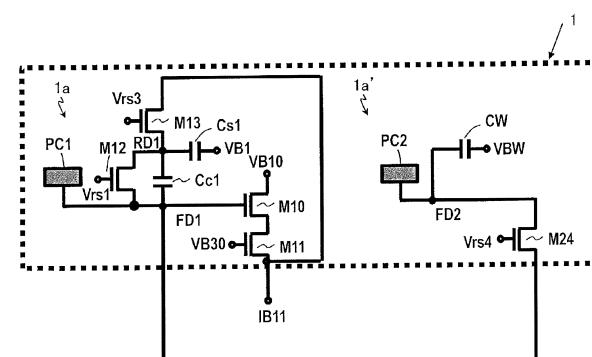

【0212】

図25は、本実施の形態による単位画素1の回路構成例を示している。単位画素1は、同一画素内に、第1撮像セル1aと第2撮像セル1a'とを有する。第1撮像セル1aは、低ノイズセルとして機能する。第1撮像セル1aは、光を電気信号に変換する第1光電変換部PC1と、第1光電変換部PC1に電気的に接続され、第1光電変換部PC1で生成した電気信号を読み出す第1信号処理回路P1とを有する。

40

【0213】

第1信号処理回路P1は、第1光電変換部PC1で生成した電気信号を検出する第1信号検出回路を含む。第1信号検出回路は、第1増幅トランジスタM10と、第1選択トランジスタM11と、第1リセットトランジスタM12とを有する。第1増幅トランジスタM10のゲートは、第1光電変換部PC1に接続されている。第1増幅トランジスタM10は、第1光電変換部PC1で生成した電気信号を増幅する。第1選択トランジスタM11のソースおよびドレインの一方は、第1増幅トランジスタM10のソースおよびドレインの一方に接続されている。第1選択トランジスタM11は、第1増幅トランジスタM1

50

0で増幅された信号を選択的に出力する。第1リセットトランジスタM12のソースおよびドレインの一方は読み出しノードFD1に接続される。第1リセットトランジスタM12は、第1光電変換部PC1に接続された読み出しノードFD1をリセット(初期化)する。

#### 【0214】

第2撮像セル1a'は、高飽和セルとして機能する。第2撮像セル1a'は、光を電気信号に変換する第2光電変換部PC2と、第2光電変換部PC2に電気的に接続され、第2光電変換部PC2で生成した電気信号を読み出す第2信号処理回路P2とを有する。

#### 【0215】

本実施の形態による第2信号処理回路P2は、他の実施の形態とは異なり、第3リセットトランジスタM24および第5容量素子CWのみを備える。第2光電変換部PC2で生成した電気信号は、第1増幅トランジスタM10から読み出される。

10

#### 【0216】

第1撮像セル1aは、暗いシーンの撮像を担うので、低ノイズ特性を必要とするが、高飽和特性を特に必要としない。一方、第2撮像セル1a'は、明るいシーンの撮像を担うので、高飽和特性を必要とする。しかし、明るいシーンの撮像では、光の量が多く、ショットノイズで特性が決定されるので、第2撮像セル1a'は低ノイズ特性を特に必要としない。そのため、本実施の形態においては、第3リセットトランジスタM24のKTCノイズ分の増加は問題ないとみなして、単位画素1の小型化を図っている。

#### 【0217】

20

図26Aから図26Iは、本実施の形態による単位画素1の回路構成の様々なバリエーションを示している。図示されるように、図25に示される構成を基礎として、第1から第5の実施の形態で説明した構成を適用してもよい。例えば、低ノイズセルとして機能する第1撮像セル1aが、反転増幅器FBAMP1、第1帯域制御トランジスタM13、および容量回路を備えていてもよい。いずれのバリエーションによっても、第2撮像セル1a'が高飽和低感度撮像を行うことが可能な、小型の撮像装置を提供できる。

#### 【0218】

次に、本実施の形態による第1撮像セル1aおよび第2撮像セル1a'の動作について説明する。

#### 【0219】

30

(小型化を実現するための読み出し駆動)

本実施の形態では、第1撮像セル1aは増幅トランジスタおよび選択トランジスタを備えているが、第2撮像セル1a'はそれらを備えていない。本実施形態は、この点で他の実施形態と異なる。図27を参照しながら、例えば図26Bに示される構成を備える単位画素1の駆動例を詳細に説明する。

#### 【0220】

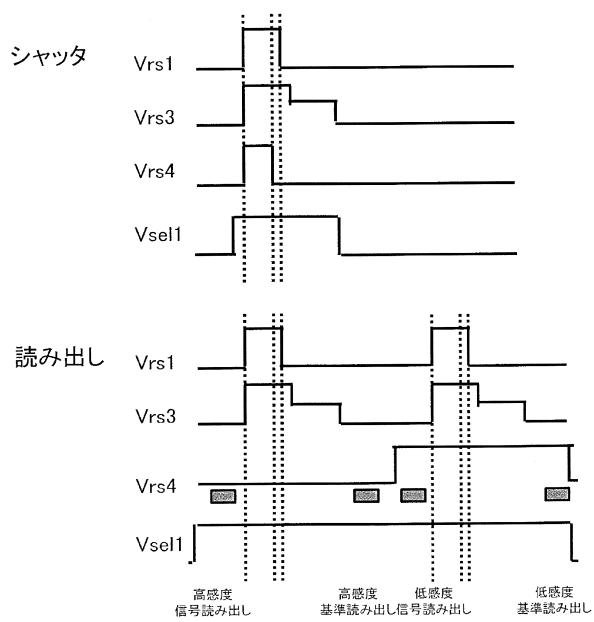

図27は、第1帯域制御トランジスタM13がある場合の駆動のタイミングの例を示す。

#### 【0221】

まず、信号蓄積(電荷蓄積)前のリセット時(電子シャッター)において、第1リセットトランジスタM12と、第1帯域制御トランジスタM13と、第3リセットトランジスタM24とを全てオンにし、第1撮像セル1aの第1光電変換部PC1に接続された読み出しノードFD1をリセットする。これと同時に、第2撮像セル1a'の第2光電変換部PC2に接続された読み出しノードFD2をリセットする。

40

#### 【0222】

次に、第1リセットトランジスタM12と、第1帯域制御トランジスタM13とをオフする前に、第3リセットトランジスタM24をオフして第2撮像セル1a'を切り離す。このとき、第2光電変換部PC2に接続された読み出しノードFD2には、第3リセットトランジスタM24のKTCノイズが重畠される。ただし、第2撮像セル1a'が対応する光量においてはショットノイズが支配的であるので、KTCノイズをそのまま残留させ

50

る。その後、第1リセットトランジスタM12、第1帯域制御トランジスタM13を順次オフする。

【0223】

第1撮像セル1aにおいては、ノイズ特性が重要であるので、第1フィードバック回路を用いて、第1リセットトランジスタM12、第1帯域制御トランジスタM13のkTCノイズをキャンセルする。このノイズ抑制動作は第3の実施の形態による第1撮像セル1aの動作と同様である。

【0224】

信号蓄積の後で、第1光電変換部PC1に接続された読み出しノードFD1の信号値を読み出す。このとき、第1撮像セル1aからの読み出しは信号のみが読みだされる。その後再度、第1リセットトランジスタM12および第1帯域制御トランジスタM13を両方オンして、第1撮像セル1aにおいて、第1光電変換部PC1に接続された読み出しノードFD1をリセットする。その後、第1撮像セル1a用の基準値を読み出す。

【0225】

次に、第3リセットトランジスタM24をオンし、第1光電変換部PC1と第2光電変換部PC2との合成ノードから信号値を読み出す。第2撮像セル1a'からの読み出した信号には第4のリセットトランジスタM24のkTCノイズが含まれている。その後再度、第1リセットトランジスタM12および第1帯域制御トランジスタM13を両方ONにして、第2撮像セル1a'において第1光電変換部PC1と第2光電変換部PC2との合成ノードからの読み出しノードをリセットし、その後基準値を読み出す。第2撮像セル1a'の信号値は、第3リセットトランジスタM24をオンすることで、第1光電変換部PC1と第2光電変換部PC2の両方のノードが接続されるので、両方のノードに蓄積された値として換算する必要がある。

【0226】

図28は、第1帯域制御トランジスタM13がない場合の駆動のタイミング例を示す。他のトランジスタの動作は図27と同等となる。図27および図28に、本実施の形態による単位画素1を駆動するタイミング例を示したが、上述したノイズ抑制および読み出しができる駆動方法であれば、駆動タイミングはこれらに限定されない。

【0227】

(第7の実施の形態)

図29を参照して、本実施の形態によるカメラシステム204を説明する。

【0228】

図29は、本実施の形態によるカメラシステム204のシステム構成を示している。カメラシステム204は、レンズ光学系201と、撮像装置200と、システムコントローラ203と、カメラ信号処理部202とを備えている。

【0229】

レンズ光学系201は、例えば、オートフォーカス用レンズ、ズーム用レンズおよび絞りを含んでいる。レンズ光学系201は、撮像装置200の撮像面に光を集光する。撮像装置200として、上述した第1から第6の実施形態およびそれらの変形例による撮像装置100を広く用いることができる。

【0230】

システムコントローラ203は、カメラシステム204全体を制御する。システムコントローラ203は、例えばマイクロコンピュータによって実現され得る。

【0231】

カメラ信号処理部202は、撮像装置200からの出力信号を処理する信号処理回路として機能する。カメラ信号処理部202は、例えばガンマ補正、色補間処理、空間補間処理、およびオートホワイトバランスなどの処理を行う。カメラ信号処理部202は、例えばDSP(Digital Signal Processor)などによって実現され得る。

【0232】

10

20

30

40

50

本実施形態によるカメラシステムによれば、第1から第6の実施形態による撮像装置100を利用することによって、読み出時のリセットノイズ(ktcノイズ)を適切に抑制することができる。その結果、電荷を正確に読み出すことができ、良好な画像を取得できる。

【産業上の利用可能性】

【0233】

本開示による撮像装置は、デジタルスチルカメラ、医療用カメラ、監視用カメラ、車載用カメラ、デジタル一眼レフカメラ、デジタルミラーレス一眼カメラ等、様々なカメラシステム及びセンサシステムへの利用が可能である。

【符号の説明】

【0234】

1 単位画素

1a, 1a' 撮像セル

2, 2' 垂直走査回路

3, 3' 水平走査回路

4, 4' 列AD変換回路

5, 5' 電流源

6, 6' リセット信号線

7, 7' アドレス信号線

8, 8' 電源配線

9, 9' 垂直信号線

10, 10' フィードバック信号線

100 撮像装置

PC1, PC2 光電変換部

M10, M20 増幅トランジスタ

M11, M21 選択トランジスタ

M24 リセットトランジスタ

Cc1 第1の容量

Cs1 第2の容量

Cc2 第3の容量

Cs2 第4の容量

CW 第5の容量

FBAMP1, FBAMP2 反転増幅器

Vref1, Vref2 反転増幅器の基準電圧

Vret1, Vret2 基準電圧

Vrs1, Vrs2 リセット制御信号

Vrs3, Vrs4 帯域制御信号

Vrs4 リセット制御信号

Vsel1, Vsel2 選択制御信号

VB1, VB2 基準電圧

VBW 容量信号

VB30, VB40 選択制御かつバイアス制御信号

VB50, VB60 帯域制御信号

VB10, VB20 制御電圧

IB11, IB21 制御電流

FD1, FD2 電荷蓄積ノード

RD1, RD2 帯域制御トランジスタと容量の接続ノード

200 撮像装置

201 レンズ/光学系

202 カメラ信号処理部

10

20

30

40

50

## 203 システムコントローラ

【図1】

【図2】

【図3】

飽和電子数( $e_{le}$ )

【図4】

【図5】

【図6 A】

【図6 B】

【図7】

【 図 8 】

【図 9 A】

【図9D】

【図9E】

【図9G】

【図9H】

【図9J】

【図9I】

【図9K】

【図9L】

【図9N】

【図9M】

【図10】

【図11】

【図13】

【図12】

【図14A】

【図14B】

【図14D】

【図14C】

【図14E】

【図14F】

【図14H】

【図14G】

【図14I】

【図15】

【図17】

【図16】

【図18】

【図19】

【図20B】

【図20A】

【図20C】

【図20D】

【図20F】

【図20E】

【図20G】

【図20H】

【図21】

【図20I】

【図22】

【図23】

【図24B】

【図24A】

【図24C】

【図24D】

【図24F】

【図24E】

【図24G】

【図24H】

【図25】

【図24I】

【図26A】

【図 2 6 B】

【図 2 6 D】

【図 2 6 C】

【図 2 6 E】

【図 2 6 F】

【図 2 6 H】

【図 2 6 G】

【図 2 6 I】

【図27】

【図28】

【図29】

---

フロントページの続き

(74)代理人 100184985

弁理士 田中 悠

(74)代理人 100202197

弁理士 村瀬 成康

(72)発明者 西村 佳壽子

大阪府門真市大字門真1006番地 パナソニック株式会社内

(72)発明者 玉置 徳彦

大阪府門真市大字門真1006番地 パナソニック株式会社内

(72)発明者 村上 雅史

大阪府門真市大字門真1006番地 パナソニック株式会社内

審査官 鈴木 明

(56)参考文献 特開2014-168112 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378