US00RE45731E

# (19) United States (12) Reissued Patent

## Li

## (54) PROGRAMMING MEMORY WITH SENSING-BASED BIT LINE COMPENSATION TO REDUCE CHANNEL-TO-FLOATING GATE COUPLING

- (71) Applicant: SanDisk Technologies Inc., Plano, TX (US)

- (72) Inventor: Yan Li, Milpitas, CA (US)

- (73)Assignee: SanDisk Technologies Inc., Plano, TX (US)

- Appl. No.: 14/285,813 (21)

#### (22) Filed: May 23, 2014 **Related U.S. Patent Documents**

Reissue of:

| reibt | ae 01.      |               |

|-------|-------------|---------------|

| (64)  | Patent No.: | 8,218,381     |

|       | Issued:     | Jul. 10, 2012 |

|       | Appl. No.:  | 12/624,595    |

|       | Filed:      | Nov. 24, 2009 |

|       |             |               |

| (51) | Int. Cl.   |           |  |

|------|------------|-----------|--|

|      | G11C 11/34 | (2006.01) |  |

|      | G11C 16/04 | (2006.01) |  |

|      | G11C 16/10 | (2006.01) |  |

|      | G11C 16/34 | (2006.01) |  |

|      | G11C 11/56 | (2006.01) |  |

| (50) |            |           |  |

- (52) U.S. Cl. G11C 16/0483 (2013.01); G11C 11/5628 CPC ..... (2013.01); G11C 16/10 (2013.01); G11C 16/3427 (2013.01); G11C 16/3418 (2013.01)

- (58) Field of Classification Search CPC ...... G11C 11/5628; G11C 16/0483; G11C 16/3427; G11C 16/10; G11C 16/3418 USPC ...... 700/94; 365/189.19 See application file for complete search history.

#### (56)**References** Cited

#### U.S. PATENT DOCUMENTS

6,956,770 B2 10/2005 Khalid

#### US RE45,731 E (10) Patent Number: (45) Date of Reissued Patent: Oct. 6, 2015

| 7,064,980 B2<br>7,206,235 B1<br>7,215,574 B2<br>7,242,616 B2 | 4/2007<br>5/2007 | Cernea<br>Lutze<br>Khalid<br>Takeuchi |

|--------------------------------------------------------------|------------------|---------------------------------------|

| 7,242,010 B2                                                 |                  |                                       |

(Continued)

#### FOREIGN PATENT DOCUMENTS

| CN | 1467747 A       | 1/2004  |

|----|-----------------|---------|

| CN | 101276638 A     | 10/2008 |

| WO | WO2011031302 A2 | 3/2011  |

#### OTHER PUBLICATIONS

English Abstract of Chinese Publication No. CN101276638 published on Oct. 1, 2008.

(Continued)

Primary Examiner - Ovidio Escalante

(74) Attorney, Agent, or Firm - Vierra Magen Marcus LLP

#### (57)ABSTRACT

During programming of storage elements, channel-to-floating gate coupling effects are compensated to avoid increased programming speed and threshold voltage distribution widening. In connection with a programming iteration, unselected bit lines voltages are stepped up to induce coupling to selected bit lines, and the amount of coupling which is experienced by the selected bit lines is sensed. When a program pulse is applied, voltages of the selected bit lines are set based on the amount of coupling. The bit line voltage is set higher when more coupling is sensed. The amount of coupling experience by a given selected bit line is a function of its proximity to unselected bit lines. One or more coupling thresholds can be used to indicate that a given selected bit line has one or two adjacent unselected bit lines, respectively.

#### 30 Claims, 21 Drawing Sheets

#### (56) **References** Cited

### U.S. PATENT DOCUMENTS

| 7,313,023<br>7,400,534<br>7,447,079<br>7,506,113<br>7,508,721<br>7,599,224 | B2<br>B2<br>B2<br>B2<br>B2 * | 12/2007<br>7/2008<br>11/2008<br>3/2009<br>3/2009<br>10/2009 | Li<br>Maejima<br>Nguyen et al.<br>Li<br>Li<br>Lee |

|----------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------|---------------------------------------------------|

| 7,916,545                                                                  |                              | 3/2011                                                      | Fujiu 365/185.19                                  |

| 7,986,573                                                                  |                              | 7/2011                                                      | Li                                                |

| 8,081,514                                                                  | B2                           | 12/2011                                                     | Mui et al.                                        |

| 8,089,815                                                                  | B2 *                         | 1/2012                                                      | Li et al 365/185.26                               |

| 8,218,381                                                                  | B2                           | 7/2012                                                      | Li                                                |

| 2002/0060926                                                               | A1 $*$                       | 5/2002                                                      | Choi et al 365/185.17                             |

| 2006/0034121                                                               | A1                           | 2/2006                                                      | Khalid et al.                                     |

| 2006/0034140                                                               | A1                           | 2/2006                                                      | Ogawa                                             |

| 2006/0120165                                                               | A1                           | 6/2006                                                      | Hemink                                            |

| 2009/0010067                                                               | A1 $*$                       | 1/2009                                                      | Lee                                               |

| 2009/0059660                                                               | A1                           | 3/2009                                                      | Lee                                               |

| 2011/0063919                                                               | A1 $*$                       | 3/2011                                                      | Chandrasekhar                                     |

|                                                                            |                              |                                                             | et al 365/185.19                                  |

### OTHER PUBLICATIONS

English Abstract of Chinese Publication No. CN1467747 published on Jan. 14, 20014.

Chinese Office Action dated Aug. 13, 2014, Chinese Patent Application No. 201080062255.0.

International Search Report & The Written Opinion of the Interna-tional Searching Authority dated Jan. 24, 2011, Patent Cooperation Treaty, International Patent Application No. PCT.US2010/057645 filed Nov. 22, 2010.

Office Action dated Jul. 19, 2012, European Patent Application No. 10785280.8.

Response to Office Action dated Jan. 29, 2013, European Patent Application No. 10785280.8.

Office Action dated May 24, 2013, European Patent Application No. 10785280.8.

Response to Office Action dated Oct. 3, 2013, European Patent Application No. 10785280.8.

U.S. Appl. No. 12/547,449, filed Aug. 25, 2009. U.S. Appl. No. 12/624,584, filed Nov. 24, 2009.

U.S. Appl. No. 12/624,602, filed Nov. 24, 2009.

\* cited by examiner

Fig. 2

# Fig. 11c

Fig. 12

5

### PROGRAMMING MEMORY WITH SENSING-BASED BIT LINE COMPENSATION TO REDUCE CHANNEL-TO-FLOATING GATE COUPLING

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indi- 10 cates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

#### CROSS-REFERENCE TO RELATED APPLICATIONS

This application is related to U.S. patent application Ser. No. 12/624,584, filed herewith, titled "Programming Memory With Bit Line Floating To Reduce Channel-To-Floating Gate Coupling," issued as U.S. Pat. No. 8,089,815<sup>20</sup> on Jan. 3, 2012, and U.S. patent application Ser. No. 12/624, 602, filed herewith, titled "Programming Memory With Direct Bit Line Driving To Reduce Channel-To-Floating Gate Coupling," issued as U.S. Pat No. 7,986,573 on Jul. 26, 2011, both of which are incorporated herein by reference.<sup>25</sup>

#### BACKGROUND

The present technology relates to non-volatile memory. Semiconductor memory has become increasingly popular 30 for use in various electronic devices. For example, non-volatile semiconductor memory is used in cellular telephones, digital cameras, personal digital assistants, mobile computing devices, non-mobile computing devices and other devices. Electrically Erasable Programmable Read Only 35 Memory (EEPROM) and flash memory are among the most popular non-volatile semiconductor memories. With flash

memory, also a type of EEPROM, the contents of the whole memory array, or of a portion of the memory, can be erased in one step, in contrast to the traditional, full-featured 40 EEPROM.

Both the traditional EEPROM and the flash memory utilize a floating gate that is positioned above and insulated from a channel region in a semiconductor substrate. The floating gate is positioned between the source and drain regions. A 45 control gate is provided over and insulated from the floating gate. The threshold voltage (Vth) of the transistor thus formed is controlled by the amount of charge that is retained on the floating gate. That is, the minimum amount of voltage that must be applied to the control gate before the transistor is 50 turned on to permit conduction between its source and drain is controlled by the level of charge on the floating gate.

Some EEPROM and flash memory devices have a storage element or cell with a floating gate that is used to store two ranges of charges and, therefore, the storage element can be 55 programmed/erased between two states, e.g., an erased state and a programmed state. Such a flash memory device is sometimes referred to as a binary flash memory device because each storage element can store one bit of data.

A multi-state (also called multi-level) flash memory device 60 is implemented by identifying multiple distinct allowed/valid programmed threshold voltage ranges. Each distinct threshold voltage range corresponds to a predetermined value for the set of data bits encoded in the memory device. For example, each storage element can store two bits of data when 65 the element can be placed in one of four discrete charge bands corresponding to four distinct threshold voltage ranges. 2

Typically, a program voltage or pulse Vpgm applied to the control gate during a programming operation is applied as a series of pulses that increase in magnitude over time. The program voltage can be applied to a selected word line. In one possible approach, the magnitude of the pulses is increased with each successive pulse by a predetermined step size, e.g., 0.2-0.4 V. Vpgm can be applied to the control gates of flash memory elements. In the periods between the program pulses, verify operations are carried out. That is, the programming level of each element of a group of storage elements being programmed in parallel is read between successive program pulses to determine whether it is equal to or greater than a verify level to which the element is being programmed. For arrays of multi-state flash memory elements, a verification step may be performed for each state of an element to determine whether the element has reached its data-associated verify level. For example, a multi-state memory element capable of storing data in four states may need to perform verify operations for three compare points.

Moreover, when programming an EEPROM or flash memory device, such as a NAND flash memory device in a NAND string, typically Vpgm is applied to the control gate and the bit line is grounded, causing electrons from the channel of a storage element to be injected into the floating gate. When electrons accumulate in the floating gate, the floating gate becomes negatively charged and the threshold voltage of the storage element is raised so that it is considered to be in a programmed state.

However, as memory devices become smaller, capacitive coupling effects become more problematic during programming.

### BRIEF DESCRIPTION OF THE DRAWINGS

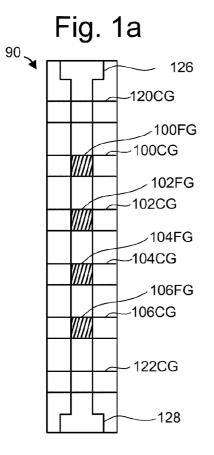

FIG. 1a is a top view of a NAND string.

FIG. 1b is an equivalent circuit diagram of the NAND string.

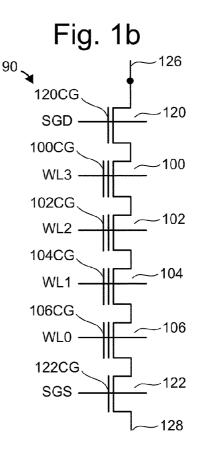

FIG. 2 is a cross-sectional view of the NAND string.

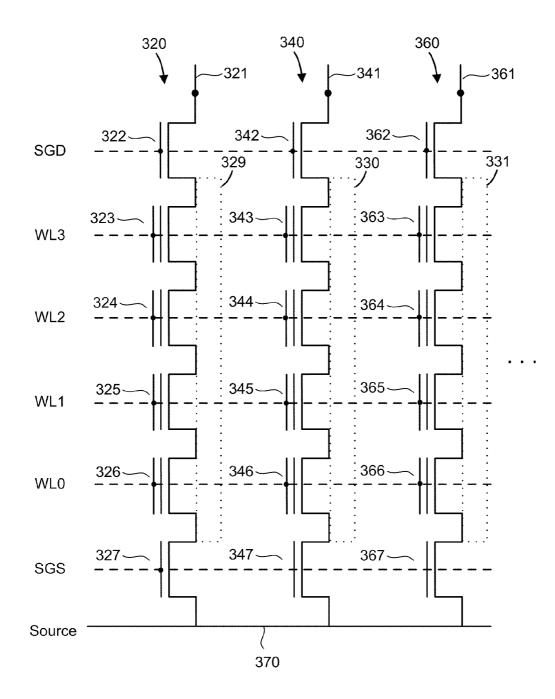

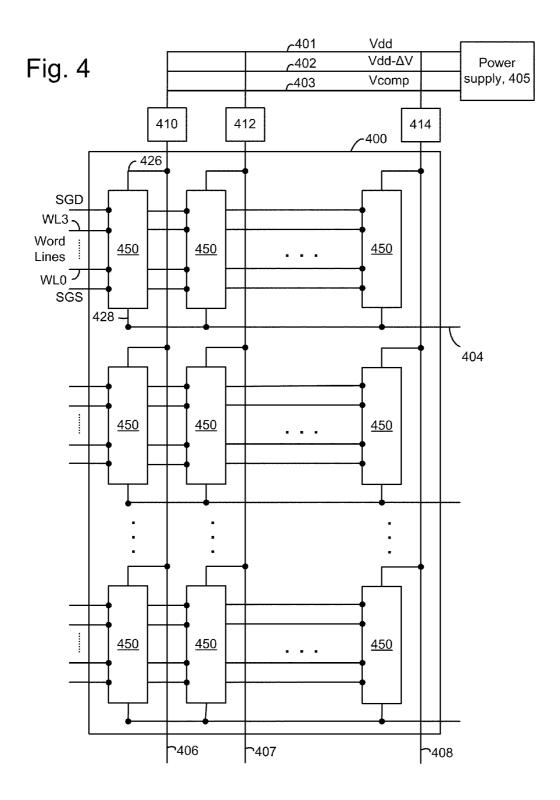

FIG. **3** is a circuit diagram depicting three NAND strings. FIG. **4** is a block diagram of an array of NAND flash storage elements.

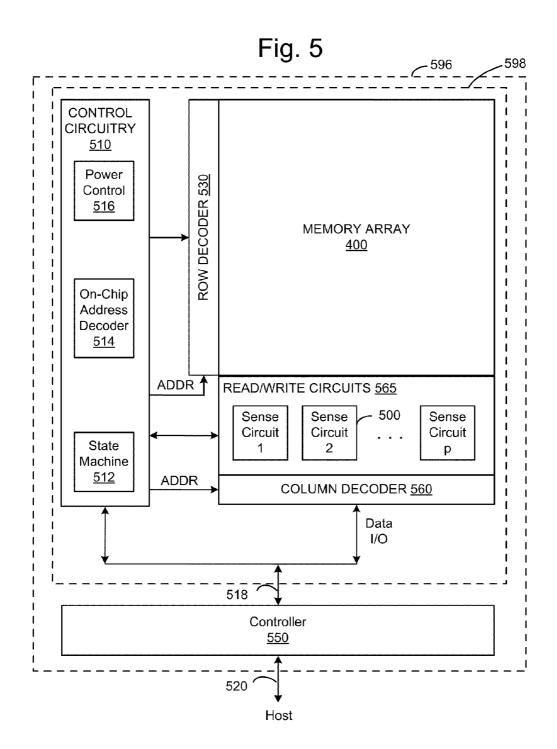

FIG. **5** is a block diagram of a non-volatile memory system using single row/column decoders and read/write circuits.

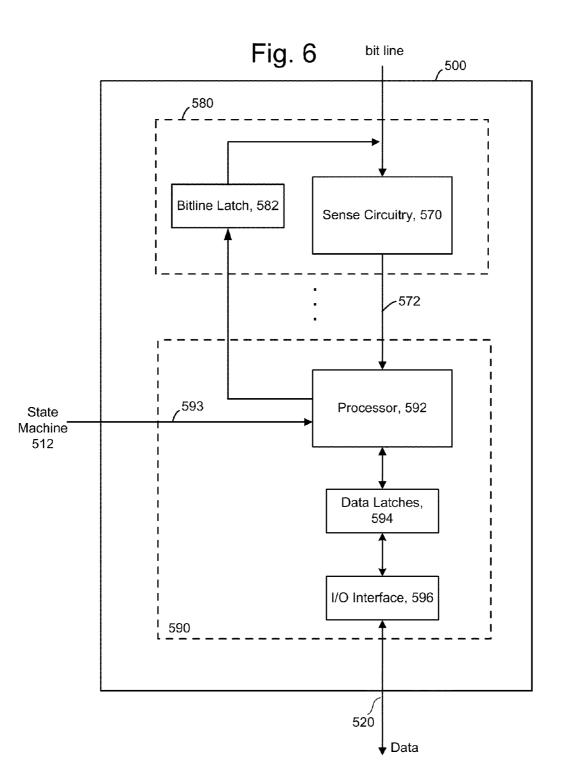

FIG.  $\mathbf{6}$  is a block diagram depicting one embodiment of a sense block.

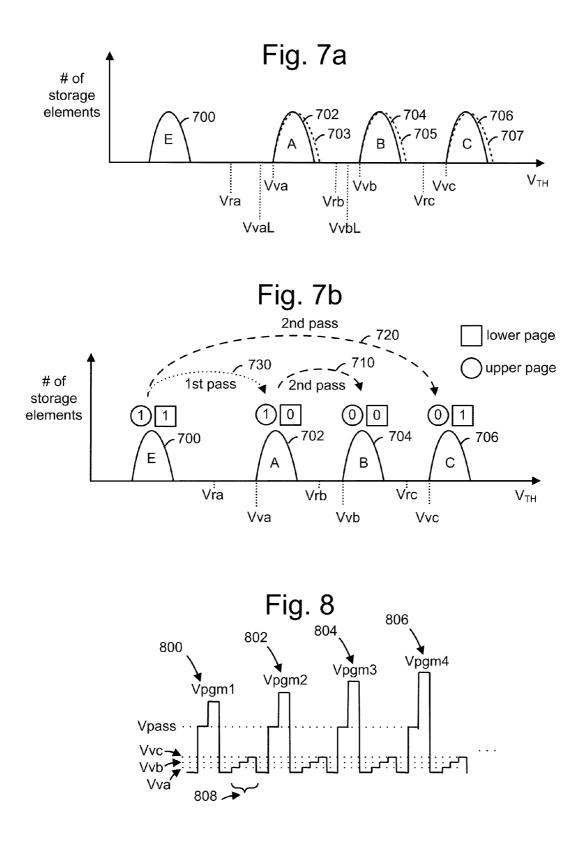

FIG. 7a depicts an example set of threshold voltage distributions, including widened distributions which are due to coupling effects.

FIG. 7b depicts an example set of threshold voltage distributions and two-pass programming.

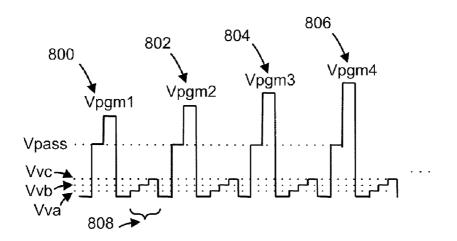

FIG. 8 depicts a series of program and verify pulses which are applied to a selected word line during a programming operation.

FIG. 9 depicts a multi-pass programming operation for a set of storage elements.

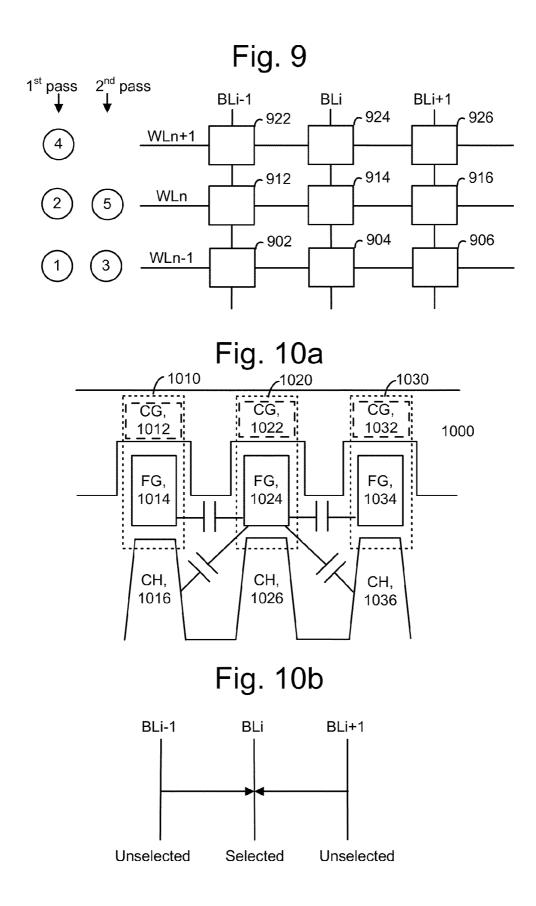

FIG. **10**a depicts a cross-sectional view of NAND strings showing channel-to-floating gate coupling and floating gate-to-floating gate coupling.

FIG. **10**b depicts coupling from unselected bit lines to a selected bit line.

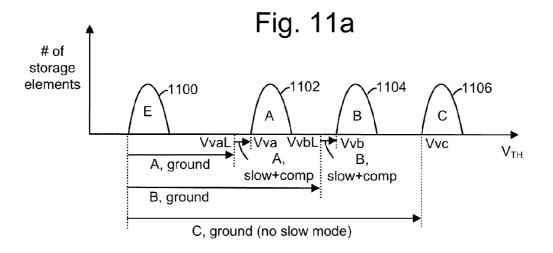

FIG. **11**a depicts an example programming technique which uses offset and target verify levels, and which reduces coupling effects.

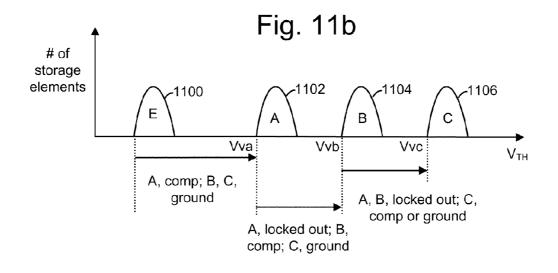

FIG. **11**b depicts an example programming technique which uses only one programming speed mode, and one verify level per state, and which reduces coupling effects.

30

35

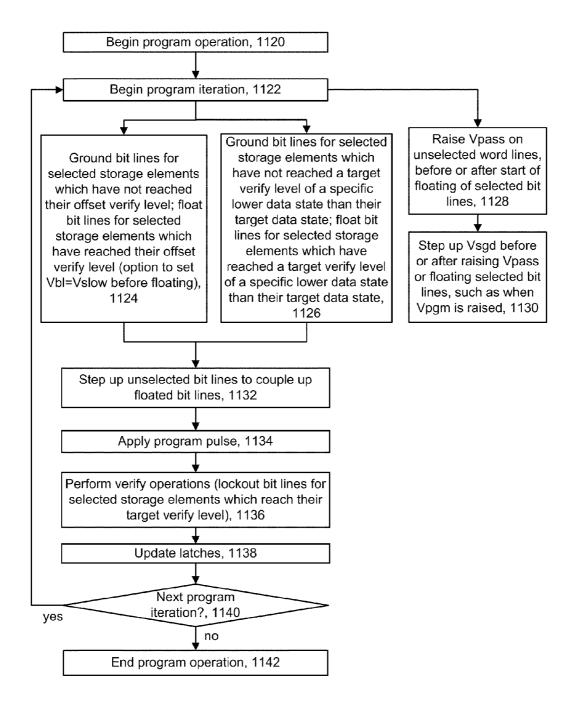

FIG. 11c depicts an example programming process related to FIGS. 11a and 11b.

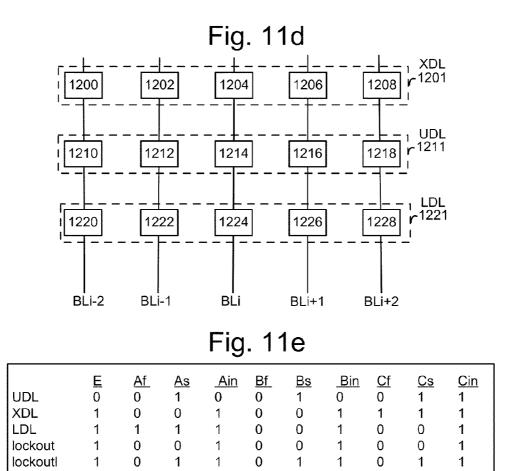

FIG. 11d depicts data latches for respective bit lines.

FIG. 11e depicts bit assignments for the latches of FIG. 11d.

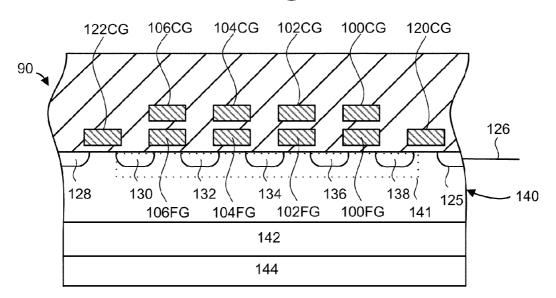

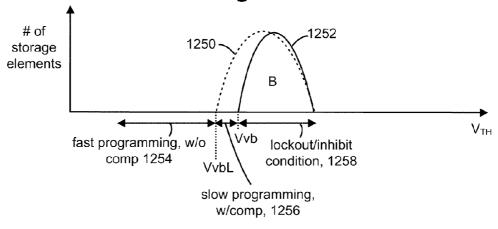

FIG. 12 depicts threshold voltage ranges of a data state for a fast programming mode with no compensation, a slow programming mode with compensation, and a lockout/inhibit condition.

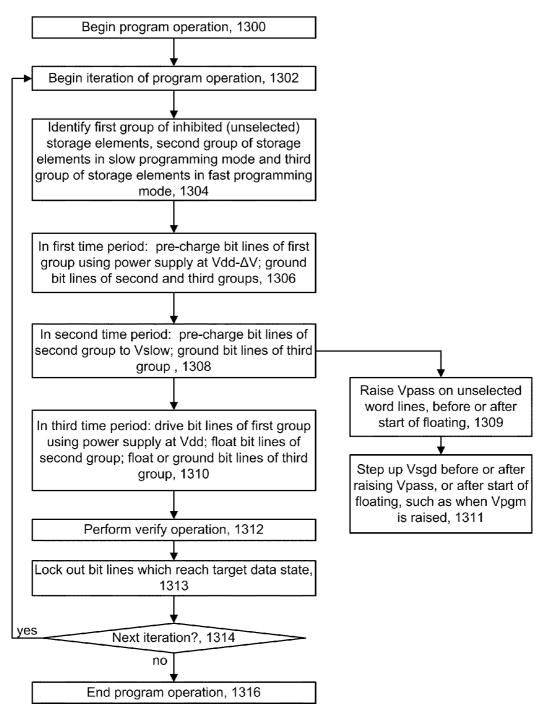

FIG. 13 depicts a method for programming a set of non- 10 volatile storage elements in which a voltage of inhibited bit lines is stepped up using two drive voltages to induce compensation coupling to neighboring bit lines.

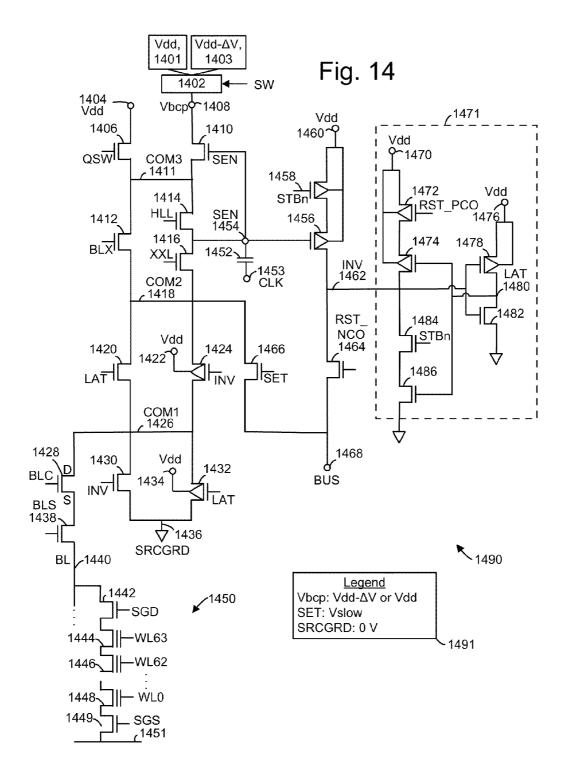

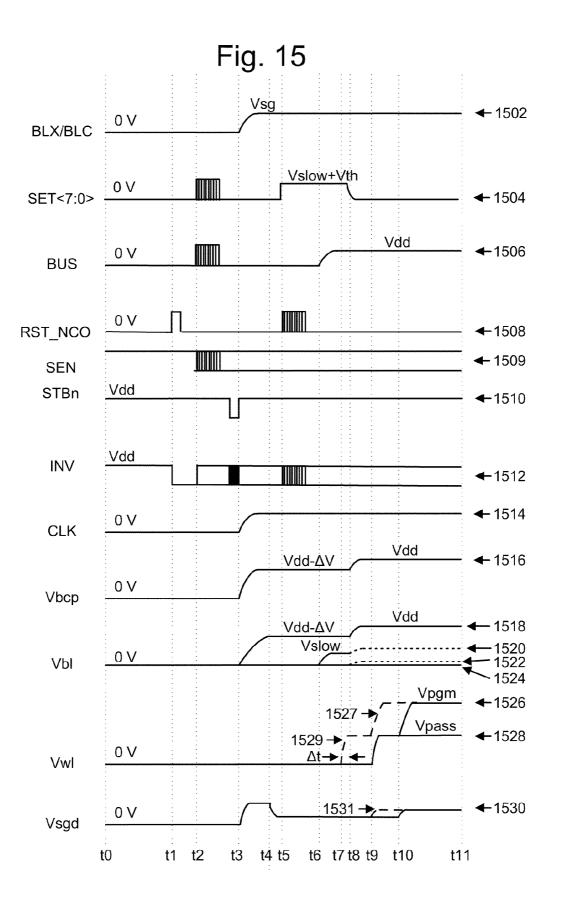

FIG. 14 depicts a sensing circuit in which drive voltages are used for inhibited bit lines, for use with the process of FIG. 13. 15

FIG. 15 depicts a time line associated with the sensing circuit of FIG. 14.

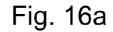

FIG. 16a depicts an alternative sensing circuit.

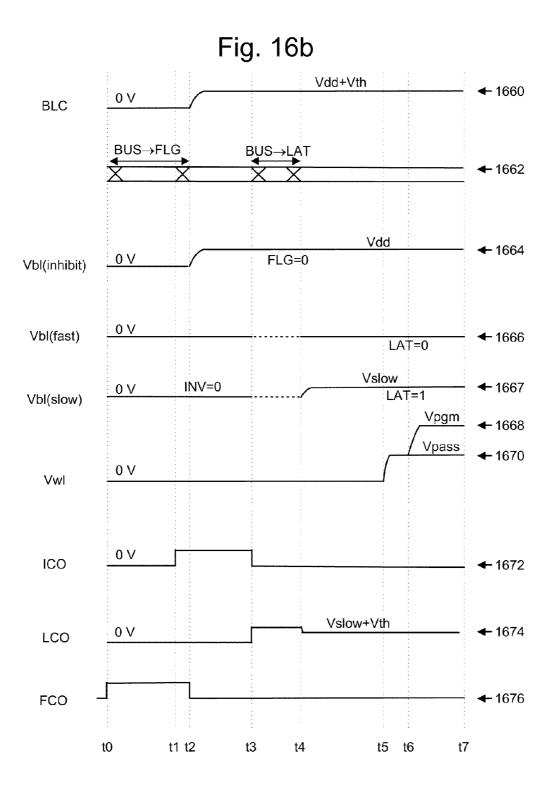

FIG. 16b depicts a time line for programming which is associated with the sensing circuit of FIG. 16a.

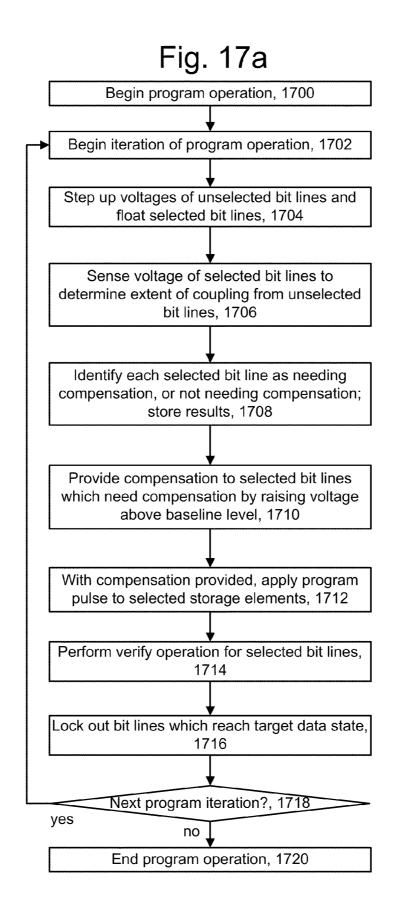

FIG. 17a depicts a method for sensing selected bit lines to determine whether coupling compensation is needed in subsequent programming.

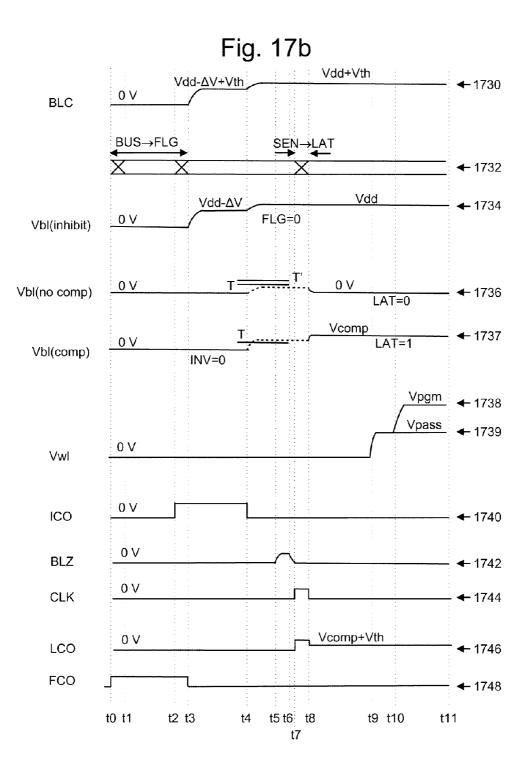

FIG. 17b depicts a time line for sensing and programming which is associated with the sensing circuit of FIG. 16a.

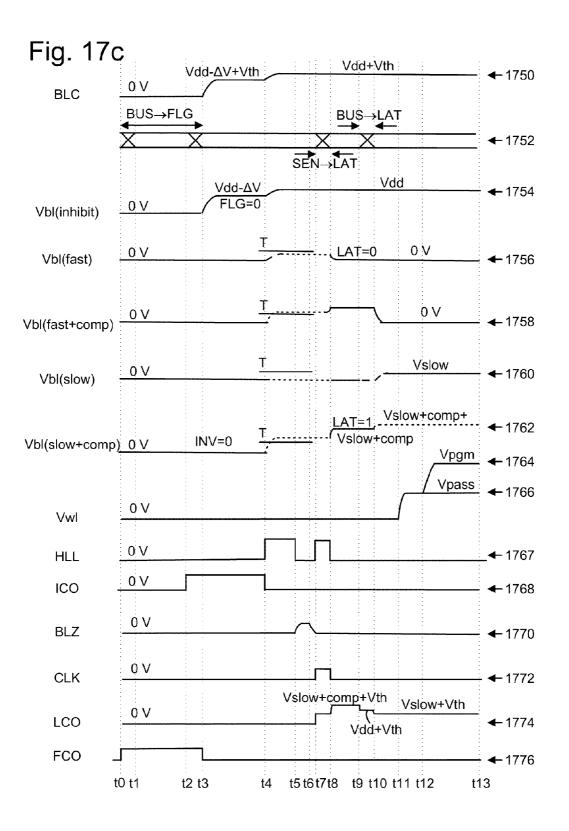

FIG. 17c depicts a time line for sensing which is associated with the sensing circuit of FIG. 16a.

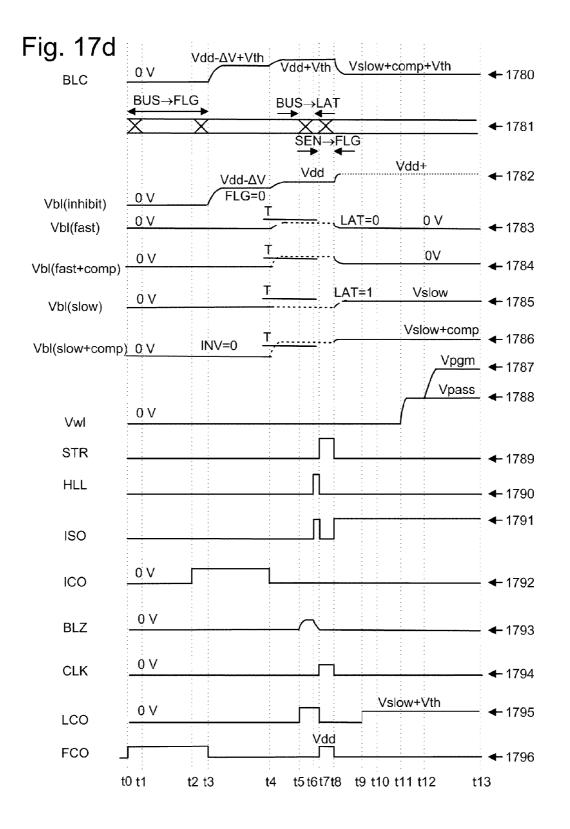

FIG. 17d depicts another time line for sensing which is associated with the sensing circuit of FIG. 16a.

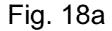

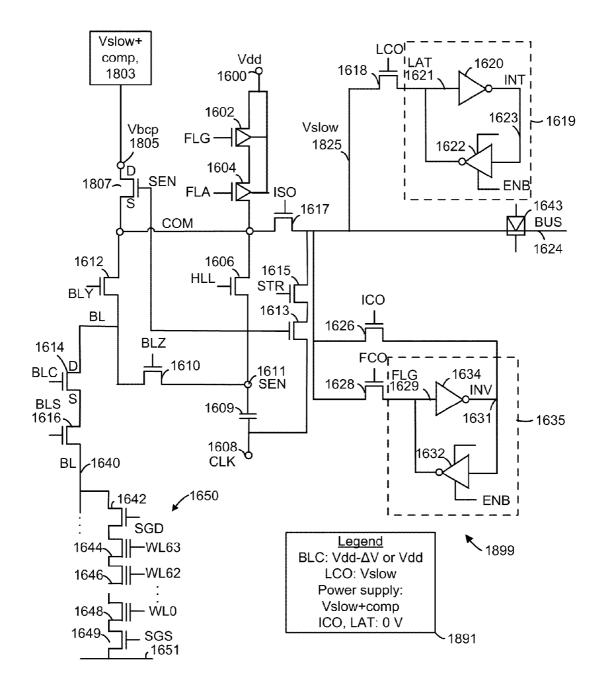

FIG. 18a depicts another alternative sensing circuit. FIG. 18b depicts a time line for sensing and programming

which is associated with the sensing circuit of FIG. 18a.

### DETAILED DESCRIPTION

A method and non-volatile storage system are provided in which coupling effects, including channel-to-floating gate capacitive coupling, are reduced during programming.

As memory devices become smaller, capacitive coupling effects become more problematic. In particular, during pro- 40 gramming, storage elements which have completed programming (also referred to as unselected, locked out or inhibited storage elements) are inhibited by raising the channel potential of an associated substrate channel region via boosting with the help from all the word lines in the block and a floating 45 channel. The floated channel is achieved by modulation from an increased bit line voltage (Vbl). However, this increased channel potential can couple to the floating gate of a nearby storage element (also referred to as a selected storage element) which is still being programmed, inadvertently raising 50 the potential of the floating gate. This is referred to as channel-to-floating gate capacitive coupling. As a result, the programming speed can be increased beyond a desired level for selected storage elements, and their threshold voltage (Vth) distribution widened. 55

This increased programming speed can be experienced by storage elements which are in fast or slow programming modes, which are set by a control. Typically, Vbl of a selected bit line (associated with a selected storage element) is held at 0V to provide the fast programming mode when the Vth of the 60 storage element is far from a target Vth. Subsequently, the slow programming mode is used by raising Vbl to about 0.6-0.8 V to slow down, but not fully inhibit, programming, when the Vth of the storage element is close to the target Vth.

One approach to avoiding such coupling is to allow the bit 65 lines to float for the selected storage element. However this does not allow the slow programming mode to be used, where

4

the Vbl needs to be at a specified non-zero level. Various solutions provided herein provide sensing circuits and programming techniques which drive and/or float bit lines in an optimal way.

In one approach, a programming slow down is provided without the need for additional verify operations and controlimplemented fast or slow programming modes. Instead, the target verify level of one state can be used to slow programming for a selected storage element which is being programmed to a next higher state by floating the bit line of the selected storage element. The channel potential, which is the Vbl passing through to the channel, increases due to coupling from the stepping up of unselected neighbor bit lines (associated with unselected storage elements), thereby slowing the programming speed. This approach automatically and adaptively provides more slowing when there is more bit line-tobit line coupling, and acts as a countermeasure to the channel potential increase due to channel-to-floating gate coupling.

In another approach, channel-to-floating gate capacitive 20 coupling is compensated for in a selected storage element which is in a slow programming mode. In this approach, unselected bit lines are driven with a voltage step up which couples to selected bit lines and is transferred to the associated channels. The channel potential determined by the Vbl 25 could be in the range of 0.8 to 1.2 V, which is higher than their previous bit line bias, thereby compensating for the higher floating gate potential of the selected storage element. As a result, the slow programming mode is carried out for the selected storage elements at the intended slow speed, without any speed up which would otherwise be experienced without such compensation. A similar compensation can be provided for a selected storage element in a fast programming mode, where its channel is initially grounded, then biased due to bit line coupling, so that programming is carried out at the intended fast speed, without any speed up which would otherwise be experienced without such compensation. Although, compensation for selected storage elements which are in a fast programming mode is generally less critical than for slow programming mode storage elements. A variation of this and other approaches relates to the timing of passing Vbl to the channel relative to when the pass voltages are applied to the word lines. The timing for adjusting a drain select gate voltage can also be optimized.

In another approach, as part of a programming operation, a sensing operation is performed to determine whether a selected storage element (and its bit line, referred to as a selected bit line) is adjacent to one or more unselected storage elements (and their bit lines, referred to as unselected bit lines). An unselected bit line is a bit line associated with an unselected storage element on a selected word line. A selected bit line is a bit line associated with a selected storage element on a selected word line. Channel-to-floating gate coupling, from the channel of an unselected storage element to the floating gate of a selected storage element on the same word line, is strongest when the selected storage element is adjacent to one or two unselected storage elements which undergo channel boosting. Sensing can be used to determine when this situation is present, to provide appropriate compensation when it is needed, and to not provide compensation when it is not needed.

In another approach, a compensation voltage alone, or in combination with a slow programming mode bias, is provided directly to the channel of a selected storage element via its bit line.

One example of a suitable memory system uses the NAND flash memory structure, which arranges multiple transistors in series between two select gates. The transistors in series and the select gates are referred to as a NAND string. FIG. 1a is a top view showing one NAND string 90. FIG. 1b is an equivalent circuit thereof. The NAND string depicted includes four transistors, 100, 102, 104 and 106, in series and sandwiched between a first select gate 120 and a second select 5 gate 122. Select gate 120 connects the NAND string to bit line 126. Select gate 122 connects the NAND string to source line 128. Select gates 120 and 122 are controlled by applying the appropriate voltages to control gates 120CG and 122CG, respectively. Each of the transistors 100, 102, 104 and 106 has 10 a control gate and a floating gate. Transistor 100 has control gate 100CG and floating gate 100FG. Transistor 102 includes control gate 102CG and floating gate 102FG. Transistor 104 includes control gate 104CG and floating gate 104FG. Transistor 106 includes a control gate 106CG and floating gate 15 106FG. Control gates 100CG, 102CG, 104CG and 106CG are connected to word lines WL3, WL2, WL1 and WL0, respectively. In one embodiment, transistors 100, 102, 104 and 106 are each memory cells. In other embodiments, the memory cells may include multiple transistors or may be 20 different than that depicted. Select gates 120 and 122 are connected to drain-side select line SGD and source-side select line SGS, respectively.

FIG. 2 provides a cross-sectional view of the NAND string described above. The transistors of the NAND string are 25 formed in p-well region 140. The p-well region in turn may be within an n-well region 142 of a p-type substrate 144. Each transistor includes a stacked gate structure that consists of a control gate (100CG, 102CG, 104CG and 106CG) and a floating gate (100FG, 102FG, 104FG and 106FG). The float- 30 ing gates are formed on the surface of the p-well on top of an oxide or other dielectric film The control gate is above the floating gate, with an inter-polysilicon dielectric layer separating the control gate and floating gate. The control gates of the memory cells (100, 102, 104 and 106) form the word lines. 35 N+ doped layers or regions 130, 132, 134, 136 and 138 are shared between neighboring cells, whereby the cells are connected to one another in series to form a NAND string. These N+ doped layers form the source and drain of each of the cells. For example, N+ doped layer 130 serves as the drain of 40 transistor 122 and the source for transistor 106, N+ doped layer 132 serves as the drain for transistor 106 and the source for transistor 104, N+ doped layer 134 serves as the drain for transistor 104 and the source for transistor 102, N+ doped layer 136 serves as the drain for transistor 102 and the source 45 for transistor 100, and N+ doped layer 138 serves as the drain for transistor 100 and the source for transistor 120. N+ doped layer 125 connects to the bit line 126 for the NAND string, while N+ doped layer 128 connects to a common source line for multiple NAND strings. Each memory cell can store data 50 represented in analog or digital form, in one or more bits.

Other types of non-volatile memory in addition to NAND flash memory can also be used.

As part of a programming operation, the potential of a channel region of the substrate which is associated with an 55 unselected storage element and, e.g., an unselected NAND string **90**, can be boosted. An unselected storage element or NAND string may be referred to as an inhibited or locked out storage element or NAND string as it is inhibited or locked out from programming in a given programming iteration of a 60 programming operation. For example, channel region **141** may be provided in the p-well **140** of the substrate **144** when any of the storage elements which are provided by control gates and floating gates **100**CG/**100**FG, **102**CG/**100**FG, **104**CG/**104**FG and **106**CG/**106**FG is an unselected storage 65 element in a programming operation, e.g., when the NAND string **90** is an unselected NAND string. The channel region

6

141 represents a conductive path in the substrate, extending in and between the doped regions 130, 132, 134, 136 and 138. Boosting can be achieved in different ways. For example, in a pre-charge operation, which occurs before a pass voltage is applied to an unselected word line, a voltage supplied on the bit line 126 can be passed to the channel 141 via the drain-side select gate transistor 120CG.

In one possible scenario, with an appropriate Vbl, the drain-side select gate transistor provides a voltage of Vbl to the channel, as a pre-charge voltage, as the control gate of the drain-side transistor is biased at Vdd+Vth where Vdd is the supply voltage to the sensing circuits and Vth is the threshold voltage of the drain-side select gate transistor. As the control gate voltage rises, the channel is boosted to a higher potential. The drain-side select gate transistor may subsequently be rendered non-conductive so that the bit line is cutoff from the channel 141, and the boosted potential is maintained in the channel. Channel boosting can also be achieved by applying pass voltages to the word lines and floating the channel. The pass voltages couple to the channel, raising its potential.

FIG. **3** is a circuit diagram depicting three NAND strings. A typical architecture for a flash memory system using a NAND structure will include several NAND strings. For example, three NAND strings **320**, **340** and **360** are shown in a memory array having many more NAND strings. Each of the NAND strings includes two select gates and four storage elements. While four storage elements are illustrated for simplicity, modern NAND strings can have up to thirty-two or sixty-four storage elements, for instance.

For example, NAND string 320 includes select gates 322 and 327, and storage elements 323-326, NAND string 340 includes select gates 342 and 347, and storage elements 343-346, NAND string 360 includes select gates 362 and 367, and storage elements 363-366. Each NAND string is connected to the source line 370 by its select gates (e.g., select gates 327, 347 or 367). A selection line SGS is used to control the source side select gates. The various NAND strings 320, 340 and 360 are connected to respective bit lines 321, 341 and 361, by drain-side select transistors in the select gates 322, 342, 362, respectively. These select transistors are controlled by a drain select line SGD. In other embodiments, the select lines do not necessarily need to be in common among the NAND strings; that is, different select lines can be provided for different NAND strings. Example channel regions 329, 330 and 331 which are associated with the NAND strings 320, 340 and 360, respectively, may be created in the substrate. Note that the storage elements and channel regions are depicted as if they were rotated 90 degrees from their actual position.

Word lines are connected to the control gates for storage elements as follows: WL3 (storage elements 323, 343 and 363), WL2 (storage elements 324, 344 and 364), WL1 (storage elements 325, 345 and 365), and WL0 (storage elements 326, 346 and 366). Each word line connects the control gates of each storage element in the row. Or, the control gates may be provided by the word lines themselves.

When programming a flash storage element, a program voltage is applied to the control gate of the storage element, e.g., via an associated word line, and the bit line associated with the storage element is grounded. Electrons from the channel are injected into the floating gate. When electrons accumulate in the floating gate, the floating gate becomes negatively charged and the Vth of the storage element is raised.

FIG. 4 illustrates an example of an array 400 of NAND storage elements, such as those shown in FIGS. 1a and 1b. Along each column, a bit line 406 is coupled to the drain terminal 426 of the drain-side select gate for the NAND string

**450**. Along each row of NAND strings, a source line **404** may connect all the source terminals **428** of the source select gates of the NAND strings.

The array of storage elements is divided into a large number of blocks of storage elements. As is common for flash EEPROM systems, the block is the unit of erase. That is, each block contains the minimum number of storage elements that are erased together. Each block is typically divided into a number of pages. A page is the smallest unit of programming. One or more pages of data are typically stored in one row of storage elements. For example, a row typically contains several interleaved pages or it may constitute one page. All storage elements of a page will be read or programmed together. A large number of pages form a block, anywhere from 8 pages, for example, up to 32, 64, 128 or more pages. In some embodiments, a row of NAND strings comprises a block.

Example sense circuits **410**, **412**, **414** communicate with bit lines **406**, **407** and **408**, respectively. The sense circuits are  $_{20}$ in communication with power supply lines **401**, **402** and **403** at Vdd, Vdd- $\Delta$ V and Vcomp, respectively, which are provided by one or more power supplies **405**. These voltages are described further below. The sense circuits also communicate with one or more control circuits to exchange control signals  $_{25}$ and data.

FIG. 5 is a block diagram of a non-volatile memory system using single row/column decoders and read/write circuits. A memory device 596 having read/write circuits for reading and programming a page of storage elements in parallel, accord- 30 ing to one embodiment. Memory device 596 may include one or more memory die 598. Memory die 598 includes a twodimensional array of storage elements 400, control circuitry 510, and read/write circuits 565. In some embodiments, the array of storage elements can be three dimensional. The 35 memory array 400 is addressable by word lines via a row decoder 530 and by bit lines via a column decoder 560. The read/write circuits 565 include multiple sense blocks 500 (typically, each sense block includes a set of sense circuits or sense amplifiers, one for each bit line) and allow a page of 40 storage elements to be read or programmed in parallel. Example sense circuits are described is further detail below. Typically a controller 550 is included in the same memory device 596 (e.g., a removable storage card) as the one or more memory die 598. Commands and data are transferred 45 between the host and controller 550 via lines 520 and between the controller and the one or more memory die 598 via lines 518.

The control circuity **510** cooperates with the read/write circuits **565** to perform memory operations on the memory 50 array **400**. The control circuitry **510** includes a state machine **512**, an on-chip address decoder **514**, and a power control module **516**. The state machine **512** provides chip-level control of memory operations. The on-chip address decoder **514** provides an address interface between that used by the host or 55 a memory controller to the hardware address used by the decoders **530** and **560**. The power control module **516** controls the power and voltages supplied to the word lines and bit lines during memory operations, and may include the power supply **405** of FIG. **4**.

In some implementations, some of the components of FIG. **5** can be combined. In various designs, one or more of the components (alone or in combination), other than storage element array **400**, can be thought of as a managing or control circuit. For example, one or more managing or control circuits may include any one of or a combination of control circuitry **510**, state machine **512**, decoders **514/560**, power

control module **516**, sense blocks **500** (comprising sense circuits, discussed further below), read/write circuits **565**, controller **550**, and so forth.

In another embodiment, a non-volatile memory system uses dual row/column decoders and read/write circuits. Access to the memory array **400** by the various peripheral circuits is implemented in a symmetric fashion, on opposite sides of the array.

FIG. 6 is a block diagram depicting one embodiment of a sense block. An individual sense block **500** is partitioned into a core portion, referred to as a sense module **580**, and a common portion **590**. In one embodiment, there is a separate sense module **580** for each bit line and one common portion **590** for a set of multiple sense modules **580**. In one example, a sense block will include one common portion **590** and eight sense modules **580**, each analogous to the sense circuits discussed further below. Each of the sense modules in a group will communicate with the associated common portion via a data bus **572**.

Sense module **580** comprises sense circuitry **570** that determines whether a conduction current in a connected bit line is above or below a predetermined threshold level. Sense module **580** also includes a bit line latch **582** that is used to set a voltage condition on the connected bit line. For example, a predetermined state latched in bit line latch **582** will result in the connected bit line being pulled to a state designating program inhibit.

Common portion **590** comprises a processor **592**, a set of data latches **594** and an I/O Interface **596** coupled between the set of data latches **594** and data bus **520**. Processor **592** performs computations. For example, one of its functions is to determine the data stored in the sensed storage element and store the determined data in the set of data latches. The set of data latches **594** is used to store data bits determined by processor **592** during a read operation. It is also used to store data bits imported from the data bus **520** during a programming operation. The imported data bits represent write data meant to be programmed into the memory. I/O interface **596** provides an interface between data latches **594** and the data bus **520**.

During reading or other sensing, a state machine 512 controls the supply of different control gate voltages to the addressed storage element. As it steps through the various predefined control gate voltages corresponding to the various memory states supported by the memory, the sense module 580 may trip at one of these voltages and an output will be provided from sense module 580 to processor 592 via bus 572. At that point, processor 592 determines the resultant memory state by consideration of the tripping event(s) of the sense module and the information about the applied control gate voltage from the state machine via input lines 593. It then computes a binary encoding for the memory state and stores the resultant data bits into data latches 594. In another embodiment of the core portion, bit line latch 582 serves both as a latch for latching the output of the sense module 580 and as a bit line latch as described above.

During program or verify, the data to be programmed is stored in the set of data latches **594** from the data bus **520**. The programming operation, under the control of the state 60 machine, comprises a series of programming voltage pulses applied to the control gates of the addressed storage elements. Each program pulse is followed by a read back (verify) to determine if the storage element has been programmed to the desired memory state. Processor **592** monitors the read back 65 memory state relative to the desired memory state. When the two are in agreement, the processor **592** sets the bit line latch **582** so as to cause the bit line to be pulled to a state designating program inhibit. This inhibits the storage element coupled to the bit line from further programming even if program pulses appear on its control gate. In other embodiments, the processor initially loads the bit line latch 582 and the sense circuitry sets it to an inhibit value during the verify process.

Data latch stack 594 contains a stack of data latches corresponding to the sense module. In one embodiment, there are three data latches per sense module 580. The data latches can be implemented as a shift register so that the parallel data stored therein is converted to serial data for data bus 520, and 10 vice-versa. All the data latches corresponding to the read/ write block of m storage elements can be linked together to form a block shift register so that a block of data can be input or output by serial transfer. In particular, the bank of read/ write modules is adapted so that each of its set of data latches 15 will shift data in to or out of the data bus in sequence as if they are part of a shift register for the entire read/write block.

FIG. 7a depicts an example set of threshold voltage distributions for a four-state memory device in which each storage element stores two bits of data. A first Vth distribution 700 is 20 provided for erased (E-state) storage elements. Three Vth distributions 702, 704 and 706 represent programmed states A, B and C, respectively, in which channel-to-floating gate coupling is compensated. Widened Vth distributions 703, 705 and 707 occur for programmed states A, B and C, respec- 25 tively, due to channel-to-floating gate coupling. Such coupling increases the potential on the floating gate of a selected storage element so that its programming speed, e.g., represented as a change in Vth per program pulse, is sped up above an intended programming speed, resulting in widening of the 30 Vth distributions on the upper tail end. In one embodiment, the threshold voltages in the E-state are negative, and the threshold voltages in the A-, B- and C-states are positive.

Read reference voltages, Vra, Vrb and Vrc, are also provided for reading data from storage elements. By testing 35 whether the threshold voltage of a given storage element is above or below Vra, Vrb and Vrc, the system can determine the state, e.g., programming condition, the storage element is in.

Further, verify reference voltages, Vva, Vvb and Vvc, are 40 provided. When programming storage elements to the A-state, B-state or C-state, the system will test whether those storage elements have a threshold voltage greater than or equal to Vva, Vvb or Vvc, respectively.

In full sequence programming, storage elements can be 45 programmed from the E-state directly to any of the programmed states A, B or C. For example, a population of storage elements to be programmed may first be erased so that all storage elements in the population are in the E-state. A series of program pulses such as depicted in FIG. 8 is used to 50 program storage elements directly into the A-, B- and C-states. While some storage elements are being programmed from the E-state to the A-state, other storage elements are being programmed from the E-state to the B-state and/or from the E-state to the C-state.

One example of a slow programming mode uses low (offset) and high (target) verify levels for one or more data states. For example, VvaL and Vva are offset and target verify levels, respectively, for the A-state, and VvbL and Vvb are offset and target verify levels, respectively, for the B-state. During pro- 60 gramming, when the Vth of a storage element which is being programmed to the A-state as a target state (e.g., an A-state storage element) exceeds VvaL, its programming speed is slowed, such as by raising Vbl to a level, e.g., 0.6-0.8 V, which is between a nominal program or non-inhibit level, e.g., 0 V 65 and a full inhibit level, e.g., 2-3 V. This provides greater accuracy by avoiding large step increases in Vth. When the

Vth reaches Vva, the storage element is locked out from further programming. Similarly, when the Vth of a B-state storage element exceeds VvbL, its programming speed is slowed, and when the Vth reaches Vvb, the storage element is locked out from further programming. In one approach, a slow programming mode is not used for the highest state since some overshoot is typically acceptable. Instead, the slow programming mode can be used for the programmed states, above the erased state, and below the highest state.

FIG. 7b illustrates an example of a two-pass technique of programming a multi-state storage element that stores data for two different pages: a lower page and an upper page. Four states are depicted by repeating the threshold voltage distributions 700, 702, 704 and 706 from FIG. 7a. These states, and the bits they represent, are: E-state (11), A-state (10), B-state (00) and C-state (01). For E-state, both pages store a "1." For A-state, the lower page stores a "0" and the upper page stores a "1." For B-state, both pages store "0." For C-state, the lower page stores "1" and the upper page stores "0." Note that although specific bit patterns have been assigned to each of the states, different bit patterns may also be assigned.

In a first programming pass, the storage element's threshold voltage level is set according to the bit to be programmed into the lower logical page. If that bit is a logic "1," the threshold voltage is not changed since it is in the appropriate state as a result of having been earlier erased. However, if the bit to be programmed is a logic "0," the threshold level of the storage element is increased to be A-state, as shown by arrow 730. That concludes the first programming pass.

In a second programming pass, the storage element's Vth is set according to the bit being programmed into the upper logical page. If the upper logical page bit is to store a logic "1," then no programming occurs since the storage element is in one of the states E or A, depending upon the programming of the lower page bit, both of which carry an upper page bit of "1." If the upper page bit is to be a logic "0," then the Vth is shifted. If the first pass resulted in the storage element remaining in the E-state, then in the second phase the storage element is programmed so that the Vth is increased to be within C-state, as depicted by arrow 720. If the storage element had been programmed into A-state as a result of the first programming pass, then the storage element is further programmed in the second pass so that the Vth is increased to be within B-state, as depicted by arrow 710. The result of the second pass is to program the storage element into the state designated to store a logic "0" for the upper page without changing the data for the lower page.

Note that a slow programming mode can also be used with this technique.

In one approach, a system can be set up to perform full sequence writing if enough data is written to fill up an entire page. If not enough data is written for a full page, then the programming process can program the lower page programming with the data received. When subsequent data is received, the system will then program the upper page. In yet another embodiment, the system can start writing in the mode that programs the lower page and convert to full sequence programming mode if enough data is subsequently received to fill up an entire (or most of a) word line's storage elements.

In another possible programming technique, in a first step, the lower page is programmed If the lower page is to remain data 1, then the storage element state remains at E-state. If the data is to be programmed to 0, then the threshold of voltage of the storage element is raised such that the storage element is programmed to an intermediate distribution which extends between states A and B.

In programming the upper page, if the storage element is in the E-state and the upper page is to remain at 1, then the storage element will remain in E-state. If the storage element is in E-state and its upper page data is to be programmed to 0, then the threshold voltage of the storage element will be 5 raised so that the storage element is in A-state. If the storage element was in the intermediate Vth distribution and the upper page data is to remain at 1, then the storage element will be programmed to target B-state. If the storage element is in the intermediate Vth distribution and the upper page data is to become data 0, then the threshold voltage of the storage element will be raised so that the storage element is in C-state.

Although the programming examples depict four data states and two pages of data, the concepts taught can be applied to other implementations with more or fewer than 15 four states and more or fewer than two pages. For example, memory devices with eight or sixteen states per storage element are currently planned or in production.

Moreover, in the example programming techniques discussed, the Vth of a storage element is raised as it is pro- 20 grammed to a target data state. However, programming techniques can be used in which the Vth of a storage element is lowered as it is programmed to a target data state. Programming techniques which measure storage element current can be used as well. The concepts herein can be adapted to dif- 25 ferent programming techniques.

FIG. 8 depicts a series of program and verify pulses which are applied to a selected word line during a programming operation. A programming operation may include multiple programming iterations, where each iteration applies one or 30 more program pulses (voltages) followed by one or more verify voltages, to a selected word line. In one possible approach, the program voltages are stepped up in successive iterations. Moreover, the program voltages may include a first portion which has a pass voltage (Vpass) level, e.g., 6-8 V, 35 followed by a second portion at a program level, e.g., 12-25 V. For example, first, second, third and fourth program pulses 800, 802, 804 and 806 have program voltages of Vpgm1, Vpgm2, a Vpgm3 and Vpgm4, respectively, and so forth. A set 808 of one or more verify voltages, such as Vva, Vvb and 40 Vvc, may be provided after each program pulse. In some cases, one or more initial program pulses are not followed by verify pulses because it is not expected that any storage elements have reached the lowest program state (e.g., A-state). Subsequently, program iterations may use verify pulses for 45 the A-state, followed by program iterations which use verify pulses for the A- and B-states, followed by program iterations which use verify pulses for the B- and C-states, for instance.

In one option, even-odd program pulses are used. In this case, in a single program iteration, one program pulse is used 50 to program selected storage elements of even-numbered bit lines, followed by another program pulse to program selected storage elements of odd-numbered bit lines, followed by one or more verify pulses for both the even- and odd-numbered bit lines. 55

FIG. 9 depicts a multi-pass programming operation for a set of storage elements. The components depicted may be a subset of a much larger set of storage elements, word lines and bit lines. In one approach, storage elements on WLn–1, e.g., storage elements **902**, **904** and **906**, are programmed in a first 60 programming pass. This step is represented by the circled "1." Next ("2"), storage elements on WLn, e.g., storage elements **912**, **914** and **916**, are programmed in a first programming pass. In this example, when a word line is selected for programming, verify operations occur after each program pulse. 65 During the verify operations on WLn, one or more verify voltages are applied to WLn and pass voltages are applied to

the remaining word lines including WLn-1 and WLn+1. The pass voltages are used to turn on (make conductive) the unselected storage elements so that a sensing operation can occur for the selected word line. Next ("3"), storage elements on WLn-1 are programmed in a second programming pass. Next ("4"), storage elements on WLn+1 are programmed in a first programming pass. Next ("5"), the storage elements on WLn are programmed in a second programming pass to their respective target states.

FIG. 10a depicts a cross-sectional view of NAND strings showing channel-to-floating gate coupling and floating gateto-floating gate coupling. A bit line or NAND string direction goes into the page, and a word line direction goes from left to right. A word line 1000 extends across multiple NAND strings. A first NAND string includes a channel region (CH) 1016. See also the channel regions discussed in connection with FIGS. 2 and 3. A storage element 1010 in the first NAND string includes a control gate (CG) 1012, which is a portion of the word line 1000, and a floating gate (FG) 1014. A second NAND string includes a channel region 1026. A storage element 1020 in the second NAND string includes a control gate 1022, which is a portion of the word line 1000, and a floating gate 1024. A third NAND string includes a channel region 1036. A storage element 1030 in the third NAND string includes a control gate 1032, which is a portion of the word line 1000, and a floating gate 1034.

As memory devices are scaled down, storage element-tostorage element interferences play an increasingly important role. As mentioned at the outset, one of these interferences is channel-to-floating gate coupling which occurs during programming. In all-bit line programming, consider a selected storage element 1020 of a selected word line 1000 which undergoes programming. When an adjacent storage element (e.g., 1010 and/or 1030) of an adjacent bit line, on the same word line 1000, reaches its target data state, it is locked out from further programming. As a result, in the next program iteration, a substrate channel region (e.g., 1016 and/or 1036) of the locked out or unselected storage element is boosted to prevent the floating gate (e.g., 1014 and/or 1034) of the unselected storage element from being increased when a program pulse is applied to the selected word line 1000. However, the boosted potential in the channel (e.g., 1016 and/or 1036) couples up to the floating gate 1024 of the selected storage element 1020, if the channel 1026 is kept at a fixed voltage such as 0V, leading to an increase in the effective electric field between the floating gate 1024 and the channel 1026 when a program pulse is applied. The amount of coupling depends on the channel potential and coupling coefficients. This results in a larger jump in the Vth of the selected storage element than is desired. The Vth distributions of the storage elements are therefore widened undesirably, as shown in FIG. 7a.

In addition to channel-to-floating gate coupling, floating gate-to-floating gate coupling can also increase the effective Vpgm which is seen by a selected storage element. This is represented by coupling from floating gates **1014** and/or **1034** to floating gate **1024**.

For example, if a program voltage with a step size of 0.2 V is applied to the word line **1000**, due to the coupling from the channel **1016**, the potential of the floating gate **1024** may increase by an amount which would be expected if the step size was higher, such as 0.3 V, and there was no coupling from the channel **1016**. Coupling from the channel **1036** can similarly inadvertently increase the potential of the floating gate **1024** so that it is programmed faster than expected. This is mainly a concern in an all bit line (ABL) programming technique where adjacent bit lines/NAND strings are concurrently programmed. With ABL, a neighbor storage element

can be a programming storage element with a channel at 0 V at the beginning of programming. As programming proceeds, the neighbor storage element is changed to be an inhibited storage element with a boosted channel voltage as high as, e.g., 8 V. This sudden change could cause neighbor storage 5 elements to experience a sudden increase in the electric field for programming.

One characteristic of ABL programming is that the program finish points can be quite random and unpredictable. In the even/odd program technique, discussed above, the odd- 10 numbered NAND chains are unselected when the even-numbered NAND chains are programmed, and vice-versa. The unselected NAND channel is always boosted at a high potential from the beginning of the program sequence. Channelto-floating gate coupling effectively makes the selected storage elements see a higher electric field for programming, but the selected storage elements are only programmed faster in the first program pulse in which the higher field is seen. The subsequent program pulses are not affected by the constant coupling from the unselected neighbor channels and there- 20 fore there would be no sudden Vth change for the selected storage elements following a steady state programming. Even though the even/odd program technique has the advantage of no channel-to-floating gate coupling side effects, its performance is only half that of ABL programming. Therefore, it is 25 worth while to have compensation technique for ABL programming without a performance penalty.

With ABL programming, to overcome the sudden electric field change on the selected storage element, the channel of the selected storage element can be compensated with a cer- 30 tain voltage, e.g. 0.5 V, to reduce the effective voltage across floating gate to the channel. This channel bias can be supplied through the bit line through the selected gate SGD, as shown in FIG. **3**. The voltage on the bit line **341** can be passed to the channel **330** by raising the gate voltage **342** to an appropriate 35 level. The bit line-to-bit line coupling is relatively strong as the bit lines are very close to each other. This fact can be utilized to obtain the bit line potential needed to modulate the channel potentials.

FIG. **10**b depicts coupling from unselected bit lines to a 40 selected bit line. Coupling represented by the arrows can occur from unselected bit lines to selected bit lines. Such coupling is highest when both adjacent unselected bit lines couple to a selected bit line. This bit line coupling can be used to compensate and control the channel voltages of the 45 selected storage elements.

Generally, the coupling which is experienced by a selected bit line depends on a pattern of one or more neighboring bit lines. For example, coupling can be experienced from one or more non-adjacent bit lines. It is also possible for coupling 50 effects to be transferred across a chain of bit lines, in a ripple effect. Consider a series of adjacent bit lines with the pattern: U1-S2-S3-S4-U5, where U and S represent unselected and selected bit lines, respectively. For S3, coupling can be received from U1 and U5 even though they are non-adjacent 55 bit lines. The coupling ratio between adjacent bit lines can be relatively high, e.g., 45%; another 5% is from the next-next neighbor coupling or ground. The coupling from a bit line which is two bit lines away from another bit line is 45%× 45%=20.25%, which is significant. Thus, S3 could receive 60 40.5% of the coupling in total, which is very close to the case where a selected storage element has an adjacent unselected neighbor on one side. There are intended and un-intended coupling effects. The coupling from U5 to S4 or from U1 to S1 are the intended couplings which will provide a slow down 65 effect to compensate the channel coupling effects from U5 to S4 and from U1 to S1. The S3 bit line coupling from both U1

and U5 (e.g., 40.5%) is very close to 45% direct coupling effect, and is an unintended coupling effect and leads to an undesirable programming slow down. S3 is not affected by coupling from its direct neighbors, i.e. S2 and S4, because they do not have the inhibited channels to couple up the floating gate of the selected storage element associated with S3.

Various approaches to reducing channel-to-floating gate coupling include the use of even-odd program pulses, discussed above. However, this results in a performance penalty. It is also possible to provide less boosting for the unselected storage elements, but this increase the risk of program disturb. A floated bit line technique with the slow programming mode is also possible, but is difficult to implement effectively. The inhibit bit line which is floated in such an implementation can be coupled by the slow programming mode bit line (a bit line associated with a slow programming mode selected storage element), and the final step up in the inhibited Vbl may not be sufficient to couple up the slow programming mode bit line to sufficiently slow down the program. Another approach is the use of a smaller program pulse step size. However, this also results in a performance penalty.

FIG. **11**a depicts threshold voltage distributions **1100**, **1102**, **1104** and **1106** in an example programming technique which uses offset and target verify levels, and which reduces coupling effects.

In one approach, A- and B-state storage elements are first programmed in a fast programming mode and then in a slow programming mode, as their Vth approaches respective target verify levels. C-state storage elements do not have slow down to enhance performance. As discussed in connection with FIG. 7a, slow and fast programming modes can be used to achieve tighter Vth distributions. A storage element can be initially programmed from the erased state to a higher state in the fast programming mode in which its bit line is at 0V. Since the storage element is far from its target verify level, coupling effects can be ignored because the sudden Vth jump caused by the coupling can not over-program the storage element beyond the desired Vth range. When the Vth of the storage element passes an offset verify level such as VvaL or VvbL, which is offset from the target verify level Vva or Vvb, respectively, the storage element enters a slow programming mode in which the rate of increase of Vth with each program pulse is reduced, such as by raising Vbl to, e.g., Vslow=0.6-0.8 V. When the storage element is in the slow programming mode, and therefore close to its target verify level, coupling effects should be compensated since precise control is desired. An extra slow down is needed on top of the intended slow down to compensate channel coupling effects. This technique can be called a double slow down (DSD). One approach to providing an additional slow down is to float the bit line after raising Vbl to Vslow. When the Vth of the storage element passes the target verify level, the storage element is locked out from further programming by raising its Vbl.

In some situations, the final program technique with an intended slow down when approaching the target may not be necessary.

Another approach uses one programming speed mode, but still performs verify operations at the offset and target verify levels. In this case, when an offset verify level of a data state is reached, the bit lines are floated for the selected storage elements which are to be programmed to the data state. This can be done without driving Vbl higher, as with the some other approaches. When the target verify level of the data state is reached, the bit lines for those selected storage elements are locked out. The offset verify levels VvaL and VvaB can be considered to be trigger verify levels for A- and B-state storage elements, respectively, which trigger bit line floating and/or setting Vbl=Vslow.

However, these approaches use additional verify opera- 5 tions, resulting in a performance penalty.

FIG. 11b depicts threshold voltage distributions in an example programming technique which reduces coupling effects in the case where only one program speed mode, and one verify level per state, is used throughout the program 10 operation. In this case, the storage elements are either in the fast programming mode or an inhibit mode. To compensate channel-to-floating gate coupling, the Vth window can be divided into three regions (assuming four data states are used) without adding any extra verify operations. In a first region, 15 below Vva, B- and C-state storage elements will be in a fast programming mode since they are far from their destinations. The A-state storage elements can be slowed down if necessary by floating their associated bit lines. The floated bit lines can be coupled by the neighbor bit lines when the neighbors 20 get inhibited. After the A-state storage elements pass Vva, they get inhibited.

In a second region, from Vva to Vvb, when the B-state storage elements pass Vva, their associated bit lines are floated to receive the coupling from the neighbor inhibited bit 25 lines so that they slow down to prevent over programming. In a third region, above Vvb, after the B-state storage elements pass the B verify level (Vvb), they are inhibited. The C-state storage elements are in the fast programming mode until they reach Vvc. The target verify levels Vva and Vvb can be 30 considered to be trigger verify levels for B- and C-state storage elements, respectively, which trigger bit line floating.

This approach allows coupling from one or more adjacent or other neighboring unselected bit lines, if present, to reduce the programming speed for a selected bit line for all, or a 35 selected portion, of a programming operation. Note that this approach does not require knowing whether there is one or more adjacent unselected bit lines, so that steps for obtaining this information, and the associated performance penalty, are avoided. The programming speed is reduced automatically in 40 proportion to the amount of coupling which is present. In particular, floating a selected bit line will allow the bit line to be coupled higher by neighboring unselected bit lines. The bit line, with a large capacitance on the order of 3 pF, can serve as a power supply to the associated channel, which has a very 45 small capacitance (perhaps 1% of 3 pF). For the bit lines with a coupled voltage, the channel is at the same voltage as the bit line. An inhibited bit line's voltage is sufficiently high relative to the pass transistor SGD that the channel floats and is dissociated from the bit line. The floating channels are 50 coupled later on by the rising word line voltage and achieve a high boosted voltage to prevent further programming.

An indication that a selected storage element should have its bit line floated and thereby be subjected to slowed programming as a form of compensation can be made by setting 55 a "slow down" bit in a UDL latch, as discussed further below.

Ideally, the slow down via a floated bit line should be done about 500 mV before the target verify level (assuming a worst case channel-to-floating gate coupling of 500 mV). Providing a slow down via floated bit lines as discussed for A- and 60 B-state storage elements may result in about two additional verify pulses. However, no additional programming pulses are incurred because the program pulses are shared with C-state programming. The slow down for C-state storage elements may result in about two additional programming 65 pulses. However, such tradeoffs result in tighter Vth distributions. To reduce the performance penalty, one implementa-

tion is to not slow down the C-state storage elements. The C-state actually has a lower probability of channel-to-floating gate coupling effects than the other two states, A and B, since most of the storage element programming to the other states are inhibited when the C-state storage elements continue programming. Moreover, if the neighbor storage elements are inhibited many program pulses before the C-state storage elements reach their verify level, the channel-to-floating gate coupling phenomenon will not widen the Vth distribution.

Note that when relatively more bit lines are grounded, early in the programming operation, there is less chance of coupling across bit lines, since a grounded bit line generally stops such coupling.

In further detail, assume a staircase increasing Vpgm is used as in FIG. 8. Typically, a first set of the program pulses are used to program the A-state storage elements, an overlapping second set of program pulses are used to program the B-state storage elements, and an overlapping third set of program pulses are used to program the C-state storage elements. Assume there is some slowing down at the very beginning of the A-state phase due to bit line floating. This results in finishing the A-state programming phase later compared to a case with no slow down. Moreover, if we have a slow down for the B-state, we will also finish the B-state programming phase later compared to a case with no slow down. However, since the storage elements share the same program pulses, it is acceptable for the A- and B-state storage elements to take longer to program, and to perform more verify operations, since the overall programming time is not increased. The overall programming time is based on the programming time of the highest state.

Thus, when the C-state storage elements are slowed down, there is a penalty in overall programming time. Generally, note that the channel-to-floating gate coupling effect involves a probability that a bit line is almost locked out when a neighbor bit line gets locked out, which occurs relatively infrequently. The combination of this rare event in the C-state is an even rarer event. Slowing down the C-state storage elements can increase the overall programming time by, e.g., two program iterations.

FIG. 11c depicts an example programming process related to FIGS. 11a and 11b. A programming operation begins at step 1120. A programming iteration begins at step 1122.

In one option, corresponding to FIG. **11**a, at step **1124**, the bit lines are grounded for the selected storage elements which have not reached their offset verify level (which is a lower verify level than the selected storage element's target verify level), and the bit lines are floated to provide compensation for the selected storage elements which have reached their offset verify level. For example, VvbL is the offset verify level for a B-state storage element, where the target data state is the B-state and the target verify level is Vvb. An option is to set Vbl=Vslow before floating the bit lines, e.g., so that they float at a level which is slightly above Vslow. Otherwise, Vbl=0 V before floating the bit lines, e.g., so that they float at a level which is slightly above 0 V.

In another option, corresponding to FIG. **11**b, at step **1126**, the bit lines are grounded for the selected storage elements which have not reached the target verify level of a specific lower data state than their target data state (which is a lower verify level than their target verify level), and the bit lines are floated to provide compensation for the selected storage elements which have reached the target verify level of the specific lower data state. For example, Vva is a target verify level of a lower data state than a target data state of the B state. That is, the A-state is one state lower than the B-state. In an eightlevel device with states Er (denotes an erase state different

from the higher E state), A, B, C, D, E, F and G, state D is two states lower than state F, for instance.

Step **1132** includes stepping up the voltage on the unselected bit lines to couple up the floated bit lines. A program pulse is applied at step **1134**.

Step 1128 includes raising Vpass on unselected word lines. This can occur before or after the start of the floating of the selected bit lines. Step 1130 includes stepping up Vsgd before or after raising Vpass or floating the selected bit lines. Vsgd can be stepped up at the same time (before Vpgm when the 10 channel boosting relies on Vpass, or after Vpgm when the channel boosting relies on Vpgm) Vpgm is raised. This is an optional step in normal programming where the inhibit bit lines do not have the step up. FIG. 15, discussed further below, illustrates some of the steps of FIG. 11c. For example, 15 it shows Vbl for a grounded bit line (1524), Vbl for a floated bit line (1522), where the floating starts at t8, stepping up of Vbl of unselected bit lines (1518) at t8, raising Vpass (1529) on unselected word lines before (at t7) the floating (at t8) of the selected bit lines, raising Vpass (1528) on unselected 20 word lines after (at t9) the floating (at t8) of the selected bit lines, and stepping up Vsgd (1530 or 1531, at t9 or t10, respectively) after raising Vpass (at t7 to t9, respectively). Vsgd is the gate voltage of a drain select transistor (e.g., 322, 342 and 362 in FIG. 3) that is provided between a storage 25 element and a respective bit line (e.g., 321, 341 and 361 in FIG. 3).

Step **1136** includes performing verify operations. A result of the verify operations is used to lockout the bit lines for the selected storage elements which reach their target verify 30 level. Step **1138** includes updating latches in the sense circuits based on the results of the verify operations. If there is a next program iteration at decision step **1140**, processing continues at step **1122** in a next program iteration. If decision step **1140** is false, the programming operation ends at step **1142**. 35

Note that steps **1124**, **1128**, **1130**, **1132** can **1134** overlap in time, at least in part. Similarly, steps **1126**, **1128**, **1130**, **1132** can **1134** overlap in time, at least in part. Generally, a bit line which is to be coupled up should be floated before stepping up the unselected bit lies. Moreover, the desired bit line and SGD 40 voltages should be established by the time Vpgm is applied.

Note that the various programming techniques described herein can be implemented with appropriate logic in a control circuit.

FIG. **11**d depicts data latches for respective bit lines. As 45 mentioned, data latches can be used to store a slow down bit. The bit can have one value (1) which indicates that an associated storage element should be subject to a slow down by having its bit line floated during at least part of a programming operation. The bit can have another value (0) which 50 indicates that the associated storage element should be subject to fast programming by having its bit line grounded during at least part of a programming operation. The bit can have another value (0) which 50 indicates that the associated storage element should not be subject to a slow down, and instead should be subject to fast programming by having its bit line grounded during at least part of a programming operation. The bit value can change during the programming operation and be read by control 55 circuits to control the bit lines appropriately, typically via an associated sense circuit.

Generally, multiple data latches, each storing one bit of data, can be provided for each bit line. The latches identify when an associated storage element has reached certain mileposts in a programming operations. For example, latches may identify that a storage element has not yet completed programming (e.g., its Vth is below a target verify level such as Vva, Vvb or Vvc), or has completed programming (e.g., its Vth is above a target verify level). Latches may also identify 65 that a storage element's Vth is below an offset verify level (e.g., VvaL or VvbL), is above an offset verify level (e.g.,

VvaL or VvbL) but below a target verify level (e.g., Vva, Vvb or Vvc), e.g., in a slow programming mode, or is above the target verify level.

A first set of latches 1201, referred to as XDL latches, includes latches 1200, 1202, 1204, 1206 and 1208. The XDL latches can be used to store a lower page of data, for instance. An XDL latch is flipped when a lower page bit is stored in an associated storage element. A second set of latches 1211, referred to as UDL latches, includes latches 1210, 1212, 1214, 1216 and 1218. In one possible implementation, a UDL latch is flipped when an associated storage element is in a slow programming mode, e.g., when its Vth is between offset and target verify levels. In the implementation of FIG. 11a, the UDL latch stores a bit which is flipped when an associated storage element transitions from a slow programming mode in which its channel is floated to a fast programming mode in which its channel is grounded. A third set of latches 1221, referred to as LDL latches, includes latches 1220, 1222, 1224, 1226 and 1228. The latches are connected to representative bit lines BLi-2, BLi-1, BL, BLi+1 and BLi+2. The LDL latches can be used to store an upper page of data, for instance. An LDL latch is flipped when an associated storage element completes programming, e.g., when its Vth exceeds a target verify level such as Vva, Vvb or Vvc.

FIG. **11**e depicts bit assignments for the latches of FIG. 11d. E denotes the erased state. Af, Bf and Cf denote the fast programming mode for the A-state, B-state and C-state storage elements, respectively, with the channels grounded. As, Bs and Cs denote the slowed programming mode for the A-state, B-state and C-state storage elements, respectively, with the bit lines floated. Ain, Bin and Cin denote the inhibited mode for the A-state, B-state and C-state storage elements, respectively. Lockout and lockoutl denote first and second data transfers from the data latches to control the bit 35 line in the sense circuit, respectively. The first transfer puts data into the sense node, with a capacitor as a dynamic latch, and then transfers the data to the latches, and the second transfer replaces some data onto the latch, as discussed further below. These data transfers provide a way to control the voltages in the sense circuit. For example, we may use one voltage for inhibiting and one voltage for slowing down. Lockoutl can be used to indicate whether a bit line is in a slow programming mode.

In this implementation, UDL=1 indicates the slow programming mode is in effect for the A, B- and C-states. During programming, the control circuits read the latch data for a selected storage element and, in response to the data, determine whether the selected storage element should be programmed with its bit line floated or grounded. The control circuits then transfer in corresponding data to the sense circuits.

FIG. 12 depicts threshold voltage ranges of a data state for a fast programming mode with no compensation, a slow programming mode with compensation, and a lockout/inhibit condition. Generally, channel-to-floating gate coupling is of highest concern for storage elements which are in a slow programming mode, when more precise control of the rate of increase of Vth is desired. The highest state (e.g., the C-state) may not use the slow programming mode since compensation for channel-to-floating gate coupling is less important than for other states. C-state programming is therefore not slowed down and does not result in an overall performance penalty. The slow programming mode for the A- and B-states incurs a penalty, such as a couple more verify operations. As a result, for the B-state as an example, it is possible to have a range of threshold voltages 1254 in which fast programming occurs, with the channel grounded, and there is no compensation for channel-to-floating gate coupling. The range **1254** extends up to VvbL. A range of threshold voltages **1256** is provided in which slow programming occurs with compensation for channel-to-floating gate coupling, and corresponds to a Vth distribution **1250**. The range **1256** extends from VvbL to Vvb. A range of threshold voltages **1258**, above Vvb, and corresponding to a Vth distribution **1252**, is also provided in which B-state storage elements are in a locked out/inhibit condition. The discussion can be generalized to other states as well.

A potential drawback is that the storage elements which are 10 close to the range **1256**, e.g., close to and just below VvbL, are in danger of being influenced by channel-to-floating gate coupling and having their Vth jump to the upper tail of the Vth distribution **1252**, causing Vth distribution widening.

An alternative approach is to float the bit lines of the fast 15 programming mode storage elements to slow down their programming, regardless of the target state. Both options could be implemented in a memory device to determine which is optimal.

Various programming techniques which provide compen- 20 sation for channel-to-floating gate coupling are detailed below.