(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2011-0061650

(43) 공개일자 2011년06월09일

(51) Int. Cl.

G11C 16/34 (2006.01) G11C 16/26 (2006.01)

G11C 7/10 (2006.01)

(21) 출원번호 10-2011-7009708

(22) 출원일자(국제출원일자) 2009년09월30일

심사청구일자 없음

(85) 번역문제출일자 2011년04월28일

(86) 국제출원번호 PCT/US2009/059069

(87) 국제공개번호 WO 2010/039859

국제공개일자 2010년04월08일

(30) 우선권주장

61/194,751 2008년09월30일 미국(US)

PCT/US2009/049333 2009년06월30일 세계지적재산권기구(WIPO)(WO)

(71) 출원인

엘에스아이 코포레이션

미합중국 캘리포니아 95035, 바버 레인 밀피타스 1621

(72) 별명자

하랏슈 에리히 에프

미국 펜실베니아주 18017 베들레헴 바바리 스트리트 5105

엔 존슨

미국 캘리포니아주 94539 프레몬트 로렐 글렌 테라스 600

(74) 대리인

제일광장특허법인

전체 청구항 수 : 총 20 항

**(54) 소프트 데이터 값 생성 방법 및 소프트 데이터 값 생성 시스템****(57) 요 약**

성능 인자 조정에 기초한 메모리 장치에 대한 소프트 데이터 생성 방법 및 장치가 제공된다. 적어도 하나의 판독 값을 획득하는 단계와, 획득된 적어도 하나의 판독 값에 기초하여 소프트 데이터 값을 생성하고 메모리 장치의 하나 이상의 성능 인자에 기초하여 조정(adjustment)을 생성하는 단계에 의해 메모리 장치에 대해 적어도 하나의 소프트 데이터 값이 생성된다. 판독 값은, 예를 들어, 데이터 비트, 전압 수준, 전류 수준 또는 저항 수준을 포함할 수 있다. 판독 값은 예를 들어 소프트 데이터 또는 생성된 소프트일 수 있다. 가능한 성능 인자는 인듀어런스(endurance), 판독 사이클의 수, 리텐션(retention) 시간, 온도, 프로세스 코너, 셀간 간섭 영향, 메모리 어레이 내의 위치 및 공격자 셀의 패턴을 포함한다. 하나 이상의 패턴 의존 성능 인자 및/또는 위치 특정 성능 인자도 고려될 수 있다. 생성된 소프트 데이터 값은 하나 이상의 LLR(log likelihood ratio)을 생성하는데 사용되는 소프트 판독 값 또는 하나 이상의 LLR 그 자체 일 수 있다.

**대 표 도 - 도1**

(종래기술)

## 특허청구의 범위

### 청구항 1

메모리 장치에 대해 적어도 하나의 소프트 데이터 값은 생성하는 방법으로서,

적어도 하나의 판독 값을 획득하는 단계와,

상기 획득된 적어도 하나의 판독 값에 기초하여 상기 소프트 데이터 값을 생성하고 상기 메모리 장치의 하나 이상의 성능 인자에 기초하여 조정(adjustment)을 생성하는 단계를 포함하는

소프트 데이터 값 생성 방법.

### 청구항 2

제 1 항에 있어서,

상기 조정은 상기 획득된 적어도 하나의 판독 값에 기초하여 공칭(nominal) 값을 조정하고, 상기 조정은 상기 메모리 장치의 하나 이상의 성능 인자에 기초하는 오프셋 값을 포함하는

소프트 데이터 값 생성 방법.

### 청구항 3

제 2 항에 있어서,

상기 성능 인자는 인듀어런스(endurance), 프로그램/소거 사이클의 수, 판독 사이클의 수, 리텐션(retention) 시간, 온도, 온도 변화, 프로세스 코너, 셀간 간섭 영향, 메모리 어레이 내의 위치, 상기 판독 값이 획득되는 워드라인의 위치, 상기 판독 값이 획득되는 페이지의 위치, 상기 판독 값이 판독되는 워드라인 내의 페이지의 위치 및 공격자 셀의 패턴 중 하나 이상을 포함하는

소프트 데이터 값 생성 방법.

### 청구항 4

제 2 항에 있어서,

상기 조정은 셀 내 상이한 비트, 워드라인 내 상이한 페이지, 상이한 비트 라인, 상이한 하드 판독 데이터 값 중 하나 이상에 대한 별개의 성능 인자에 기초하는

소프트 데이터 값 생성 방법.

### 청구항 5

제 1 항에 있어서,

상기 판독 값은 데이터 비트, 전압 수준, 전류 수준 및 저항 수준 중 하나 이상을 포함하는

소프트 데이터 값 생성 방법.

### 청구항 6

제 1 항에 있어서,

상기 판독 값은 소프트 데이터와 하드 데이터 중 하나 이상을 포함하는

소프트 데이터 값 생성 방법.

#### 청구항 7

제 1 항에 있어서,

상기 소프트 데이터 값은 (i) 하나 이상의 LLR(log likelihood ratio)을 생성하는데 사용되는 소프트 판독 값과

(ii) 하나 이상의 LLR 중 하나 이상을 포함하는

소프트 데이터 값 생성 방법.

#### 청구항 8

제 1 항에 있어서,

상기 소프트 데이터 값은 상기 적어도 하나의 판독 값의 신뢰도(reliability)를 나타내는

소프트 데이터 값 생성 방법.

#### 청구항 9

제 1 항에 있어서,

상기 단계 중 하나 이상은 제어기, 판독 채널, 신호 처리 유닛 및 디코더 중 하나 이상에 의해 구현되는

소프트 데이터 값 생성 방법.

#### 청구항 10

제 1 항에 있어서,

상기 조정은 미리 획득되고 메모리에 저장되는

소프트 데이터 값 생성 방법.

#### 청구항 11

제 1 항에 있어서,

상기 조정을 측정하는 단계를 더 포함하는

소프트 데이터 값 생성 방법.

#### 청구항 12

제 1 항에 있어서,

상기 성능 인자는 하나 이상의 패턴 의존 성능 인자를 포함하는

소프트 데이터 값 생성 방법.

### 청구항 13

제 1 항에 있어서,

상기 성능 인자는 하나 이상의 위치 특정(location-specific) 성능 인자를 포함하는

소프트 데이터 값 생성 방법.

### 청구항 14

제 1 항에 있어서,

상기 메모리 장치는 플래시 메모리 장치인

소프트 데이터 값 생성 방법.

### 청구항 15

제 1 항에 있어서,

상기 조정은 상기 판독 값의 신뢰도 값을 감소시키는

소프트 데이터 값 생성 방법.

### 청구항 16

제 2 항에 있어서,

상기 조정은 상기 공칭 값의 신뢰도 값을 상기 오프셋 값을 동일한 양만큼 감소시키는

소프트 데이터 값 생성 방법.

### 청구항 17

메모리 장치에 대해 적어도 하나의 소프트 데이터 값을 생성하는 시스템으로서,

메모리와,

상기 메모리에 결합된 적어도 하나의 프로세서를 포함하고,

상기 프로세서는

적어도 하나의 판독 값을 획득하고,

상기 획득된 적어도 하나의 판독 값에 기초하여 상기 소프트 데이터 값을 생성하고 상기 메모리 장치의 하나 이상의 성능 인자에 기초하여 조정을 생성하도록 동작하는

소프트 데이터 값 생성 시스템.

### 청구항 18

제 17 항에 있어서,

상기 조정은 상기 획득된 적어도 하나의 판독 값에 기초하여 공칭(nominal) 값을 조정하고, 상기 조정은 상기 메모리 장치의 하나 이상의 성능 인자에 기초하는 오프셋 값을 포함하는

소프트 데이터 값 생성 시스템.

### 청구항 19

제 18 항에 있어서,

상기 성능 인자는 인듀어런스(endurance), 프로그램/소거 사이클의 수, 판독 사이클의 수, 리텐션(retention) 시간, 온도, 온도 변화, 프로세스 코너, 셀간 간섭 영향, 메모리 어레이 내의 위치, 상기 판독 값이 획득되는 워드라인의 위치, 상기 판독 값이 획득되는 페이지의 위치, 상기 판독 값이 판독되는 워드라인 내의 페이지의 위치 및 공격자 셀의 패턴 중 하나 이상을 포함하는

소프트 데이터 값 생성 시스템.

### 청구항 20

제 17 항에 있어서,

상기 소프트 데이터 값은 (i) 하나 이상의 LLR(log likelihood ratio)을 생성하는데 사용되는 소프트 판독 값과 (ii) 하나 이상의 LLR 중 하나 이상을 포함하는

소프트 데이터 값 생성 시스템.

## 명세서

### 기술 분야

#### 관련 출원의 상호 참조

[0001] 본 출원은 2008.9.30.자로 출원된 미국 특허 가출원 61/194,751호 및 2009.6.30.자로 출원되고 명칭이 "Methods and Apparatus for Soft Demapping and Intercell Interference Mitigation in Flash Memories"인 국제 특허 출원 PCT/US09/49333호의 우선권을 주장하며, 이들 각각은 본 명세서에 참조로 포함된다.

[0003] 본 출원은 명칭이 "Methods and Apparatus for Soft Data Generation for Memory Devices"인 국제 특허 출원, 명칭이 "Methods and Apparatus for Soft Data Generation for Memory Devices Using Reference Cells"인 국제 특허 출원, 명칭이 "Methods and Apparatus for Soft Data Generation for Memory Devices Using Decoder Performance Feedback"인 국제 특허 출원과 관련되며, 이들 각각은 본 출원과 동시에 출원되고 본 명세서에 참조로 포함된다.

#### 발명의 분야

[0005] 본 발명은 일반적으로는 플래시 메모리 장치에 관한 것이고, 더 구체적으로는 검출 및 디코딩 성능을 개선하는 성능 인자 조정에 기초한, 개선된 소프트 데이터 생성 기술에 관한 것이다.

## 배경 기술

[0006] 플래시 메모리 장치와 같은 많은 메모리 장치는 데이터를 저장하는데 아날로그 메모리 셀을 사용한다. 각 메모리 셀은, 저장 값이라고도 지칭되는 전하 또는 전압과 같은 아날로그 값을 저장한다. 저장 값은 셀에 저장된 정보를 나타낸다. 플래시 메모리 장치에서, 예를 들어, 각 아날로그 메모리 셀은 통상 특정 전압을 저장한다. 각 셀에 대한 가능한 아날로그 값의 범위는 통상 문턱 영역들로 나누어지고, 각 영역은 하나 이상의 데이터 비트 값에 대응한다. 희망하는 하나 이상의 비트에 대응하는 공칭 아날로그 값을 기록함으로써 데이터가 아날로그 메모리 셀에 기록된다.

[0007] 예를 들어, SLC(single-level cell) 플래시 메모리 장치는 메모리 셀 (또는 2개의 가능한 메모리 상태) 마다 하나의 비트를 저장한다. 반면, MLC(Multi-level cell) 플래시 메모리 장치는 메모리 셀 마다 2 이상의 비트를 저장한다(즉, 각 셀은 4개 이상의 프로그램가능 상태를 갖는다). MLC 플래시 메모리 장치에 대한 더 자세한 논

의에 대해서는, 예를 들어, 본 명세서에 참조로 포함되는 2009.3.11.자로 출원된 명칭이 "Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding And Per-Page Coding"인 국제 특허 출원 PCT/US09/36810호를 참조하라.

[0008] 메모리 셀에 저장된 아날로그 값은 종종 왜곡된다. 왜곡은 통상적으로, 예를 들어, 백 패턴 의존성(BPD), 잡음 및 셀간 간섭(ICI)에 기인한다. 플래시 메모리 장치에서의 왜곡에 대한 더 자세한 논의에 대해서는, 예를 들어, 본 명세서에 참조로 포함되는 J. D. Lee 등의 "Effects of Floating-Gate Interference on NAND Flash Memory Cell Operation," IEEE Electron Device Letters, 264-266 (2002 3월) 또는 Ki-Tae Park, 등의 "A Zeroing Cell-to-Cell Interference Page Architecture WithTemporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories," IEEE J. of Solid State Circuits, Vol. 43, No. 4, 919-928, (2008 4 월)을 참조하라.

[0009] ICI 및 기타 외란(disturbances)의 효과를 감소시키기 위해 많은 기술이 제안 또는 제시되어 왔다. 예를 들어, Ki-Tae Park 등은 ICI를 감소시키는 홀/짝(even/odd) 프로그래밍, 상향(bottom up) 프로그래밍 및 다단(multistage) 프록래밍과 같은 기존 프로그래밍 기술을 설명한다. 2009.6.30.자로 출원된 명칭이 "Methods and Apparatus for Soft Demapping and Intercell Interference Mitigation in Flash Memories"인 국제 특허 출원 PCT/US09/49333호는 플래시 메모리에서의 소프트 디매핑 및 외란 감소를 위한 방법 및 장치를 개시한다.

## 발명의 내용

### 해결하려는 과제

[0010] 이들 기존의 방법은 플래시 메모리의 디코딩 성능을 개선하는데 도움을 주었지만, 이들은 많은 한계를 가지고 있으며, 이를 극복하면 플래시 메모리의 신뢰성이 더 개선될 것이다. 예를 들어, 최근의 플래시 메모리는 통상 디코딩을 위해 플래시 제어 시스템에 하드 데이터만을 제공한다. 그러나, 소프트 데이터가 디코딩 프로세스에서 에러 레이트 성능을 개선할 수 있음이 잘 알려져 있다. 그러므로, 플래시 메모리로부터의 하드 데이터를 이용하여 소프트 데이터를 추정 또는 강화하고 그에 의해 디코딩 성능을 개선하는 소프트 데이터 생성 기술에 대한 필요성이 존재한다.

### 과제의 해결 수단

[0011] 일반적으로, 성능 인자 조정에 기초한 메모리 장치에 대한 소프트 데이터 생성 방법 및 장치가 제공된다. 본 발명의 일 태양에 따르면, 적어도 하나의 판독 값을 획득하는 단계와, 상기 획득된 적어도 하나의 판독 값에 기초하여 상기 소프트 데이터 값을 생성하고 상기 메모리 장치의 하나 이상의 성능 인자에 기초하여 조정(adjustment)을 생성하는 단계에 의해 메모리 장치에 대해 적어도 하나의 소프트 데이터 값이 생성된다. 상기 판독 값은 소프트 데이터 및/또는 하드 데이터일 수 있고, 데이터 비트, 전압 수준, 전류 수준 또는 저항 수준(또는 그들의 결합)을 포함할 수 있다. 생성된 소프트 데이터 값은, 예를 들어, (i) 하나 이상의 LLR(log likelihood ratio)을 생성하는데 사용되는 소프트 판독 값 또는 (ii) 하나 이상의 LLR을 포함할 수 있다.

[0012] 예시적인 실시형태에서, 상기 조정은 상기 획득된 적어도 하나의 판독 값에 기초하여 공칭(nominal) 값을 조정하고, 상기 조정은 상기 메모리 장치의 하나 이상의 성능 인자에 기초하는 오프셋 값을 포함한다.

[0013] 성능 인자는, 예를 들어, 인듀어런스(endurance), 프로그램/소거 사이클의 수, 판독 사이클의 수, 리텐션(retention) 시간, 온도, 온도 변화, 프로세스 코너, 셀간 간섭 영향, 메모리 어레이 내의 위치, 상기 판독 값이 획득되는 워드라인의 위치, 상기 판독 값이 획득되는 페이지의 위치, 상기 판독 값이 판독되는 워드라인 내의 페이지의 위치 및 공격자 셀의 패턴 중 하나 이상을 포함할 수 있다. 성능 인자 중 하나 이상은 셀 내 하나 이상의 상이한 비트, 워드라인 내 상이한 페이지, 상이한 비트 라인 또는 상이한 하드 판독 데이터 값에 대해 변화될 수 있다.

[0014] 본 발명 및 본 발명의 추가적인 특징 및 장점의 더 완전한 이해는 이후의 상세한 설명 및 도면을 참조하여 얻어질 것이다.

## 도면의 간단한 설명

[0015]

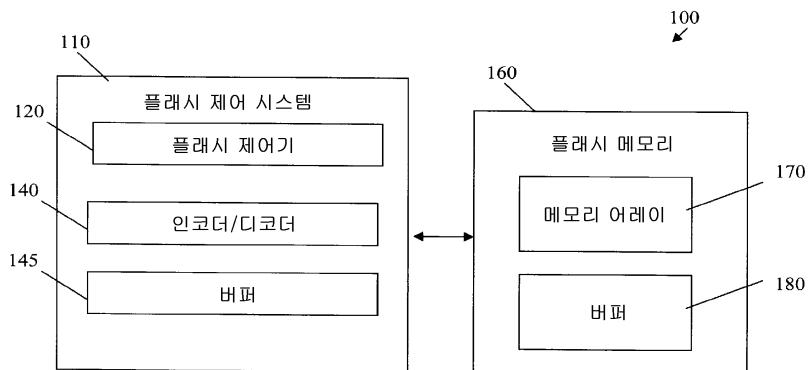

도 1은 종래 플래시 메모리 시스템의 개략적 블록도이다.

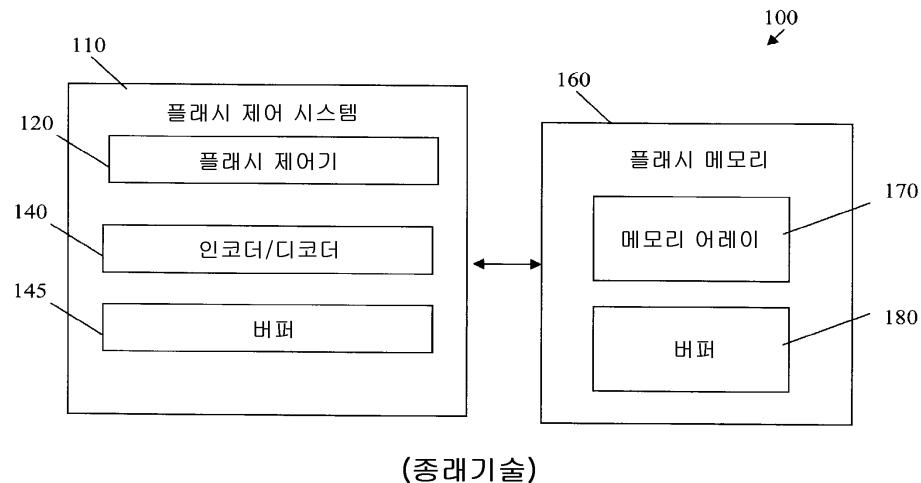

도 2는 도 1의 예시적 플래시 메모리에 대한 예시적인 문턱 전압 분포를 도시한다.

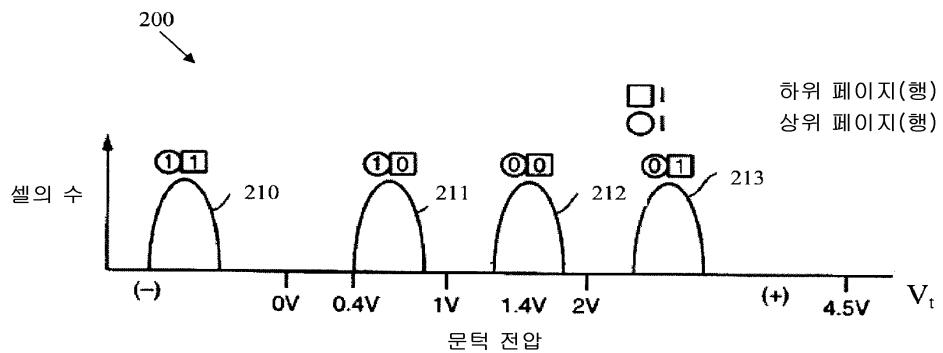

도 3은 MLC 플래시 메모리 장치에서의 예시적인 플래시 셀 어레이의 아키텍처를 도시한다.

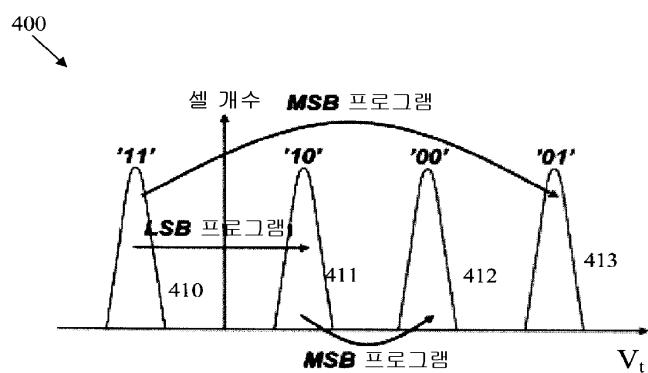

도 4는 도 2의 전압 할당 방식에 대한 예시적인 2 단계 MLC 프로그래밍 방식을 도시한다.

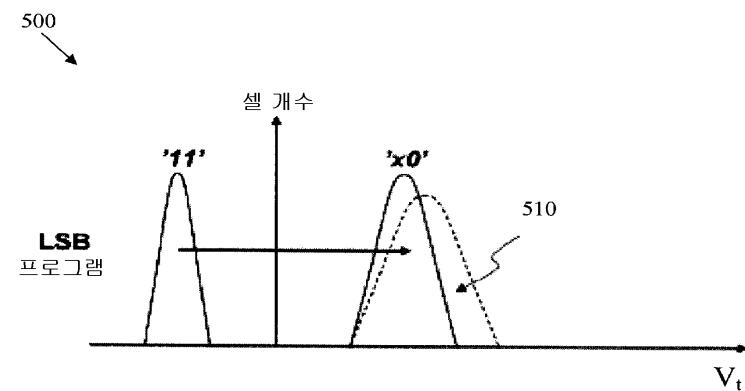

도 5a 및 5b는, 다 함께, 이웃 셀에 가해진 ICI를 감소시키는 다른 MLC 프로그래밍 방식을 도시한다.

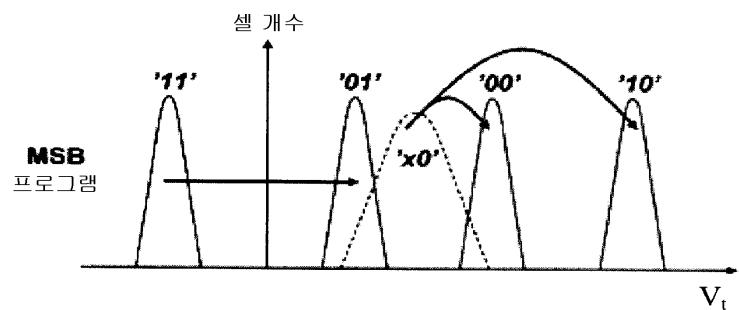

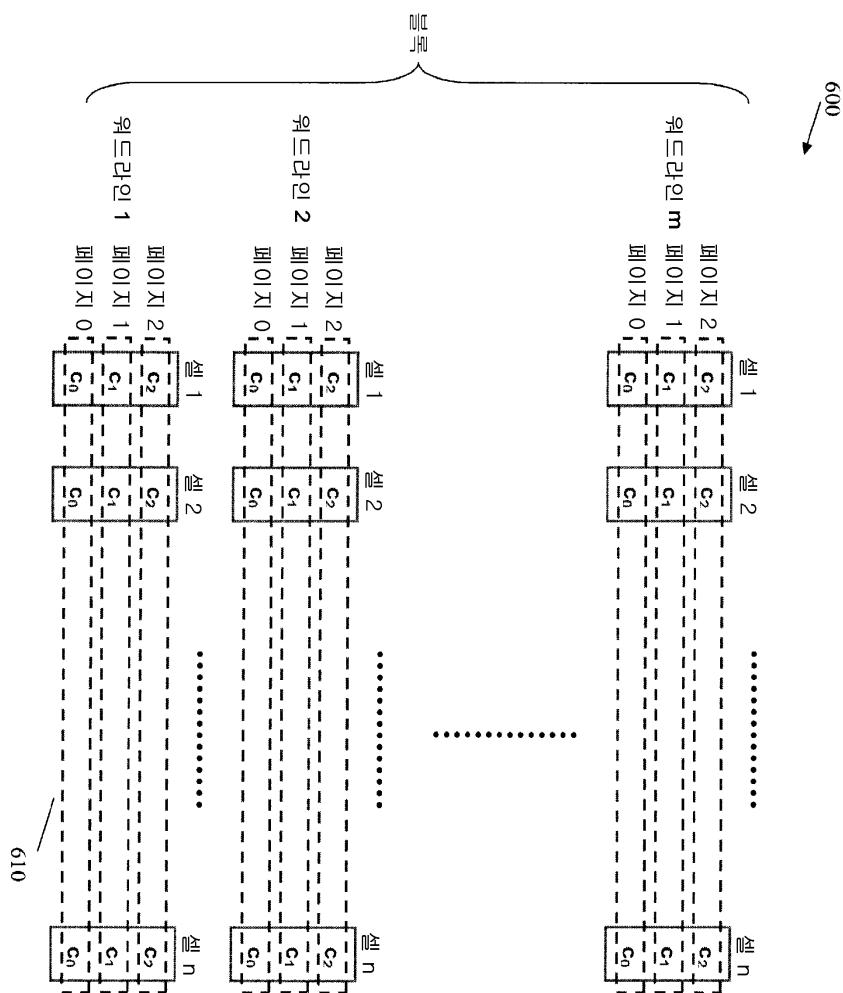

도 6은 MLC 플래시 메모리 장치에서의 예시적인 플래시 셀 어레이를 더 자세히 도시한다.

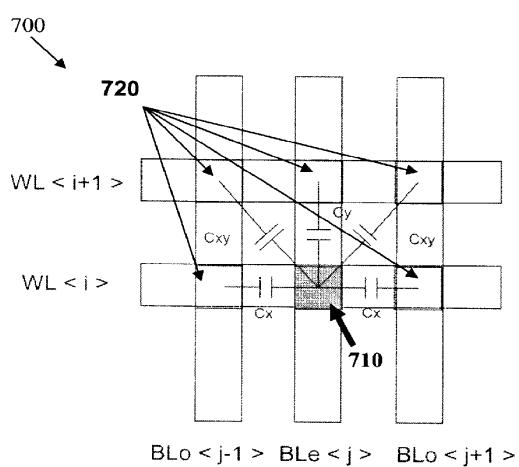

도 7은 다수의 예시적인 공격자 셀에 기인하여 타겟 셀에 존재하는 셀간 간섭, 백 패턴 의존성, 잡음 및 기타 왜곡과 같은 외란을 도시한다.

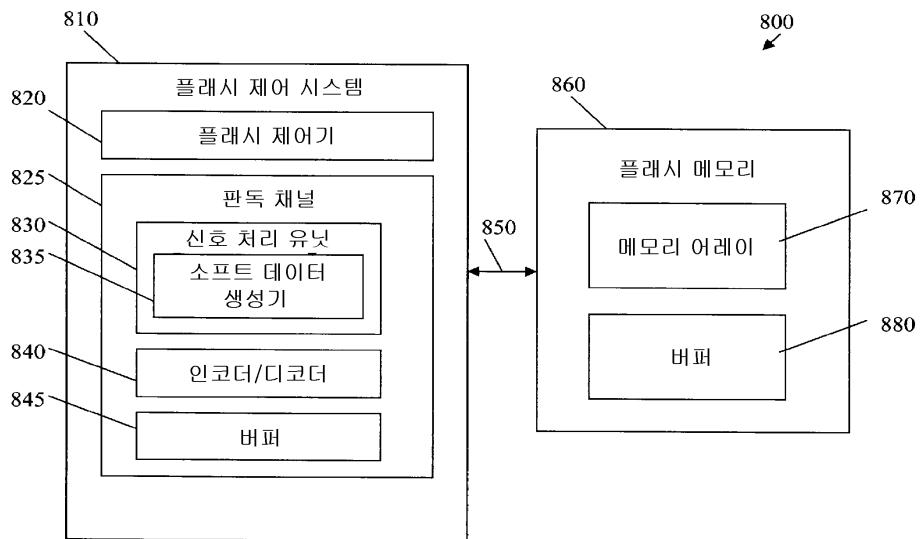

도 8은 본 발명에 따라 제어기 기반 소프트 데이터 생성 기술을 포함하는 예시적인 플래시 메모리 시스템의 개략적 블록도이다.

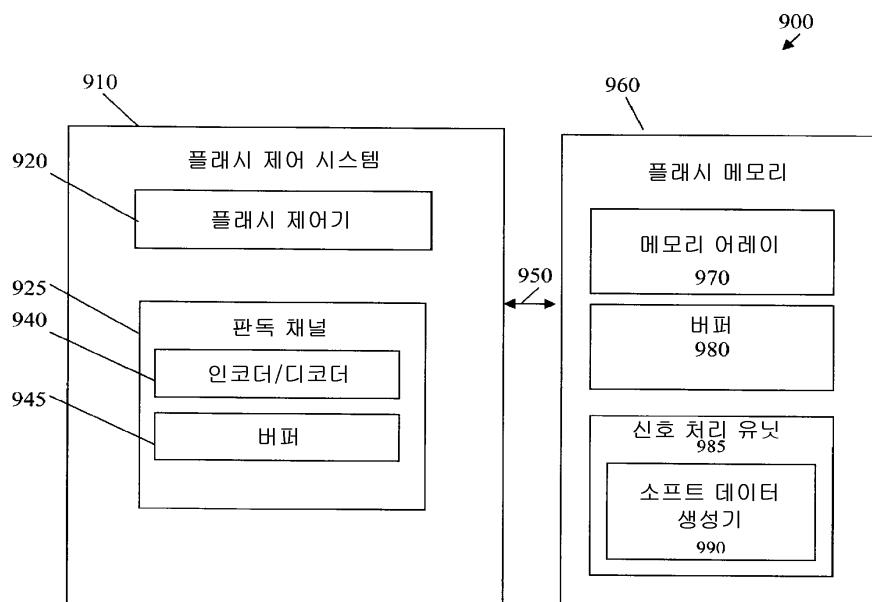

도 9는 본 발명의 다른 실시형태에 따라 메모리 기반 소프트 데이터 생성 기술을 포함하는 예시적인 플래시 메모리 시스템의 개략적 블록도이다.

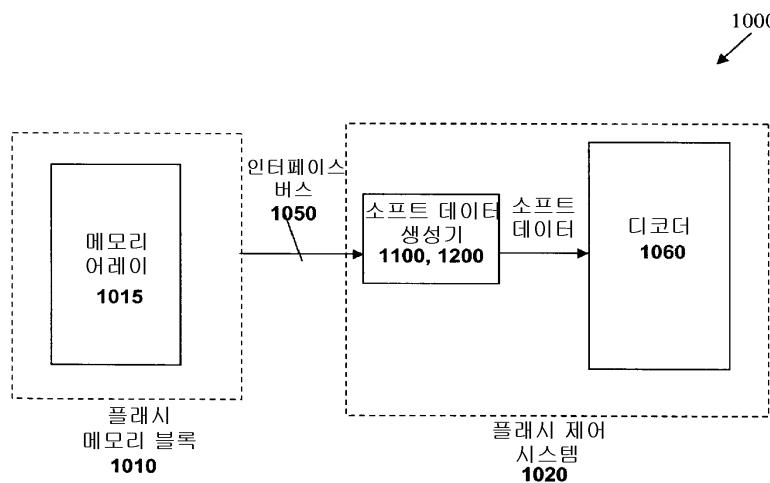

도 10은 본 발명에 따라 소프트 데이터 생성을 갖는 예시적인 플래시 메모리 시스템을 도시한다.

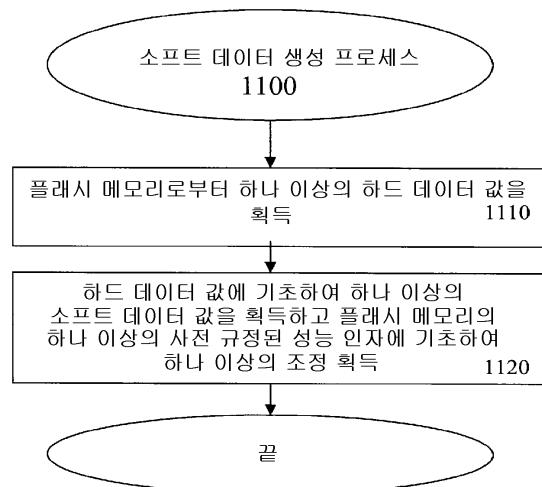

도 11은 본 발명의 특징을 포함하는 예시적인 소프트 데이터 생성 프로세스를 설명하는 흐름도이다.

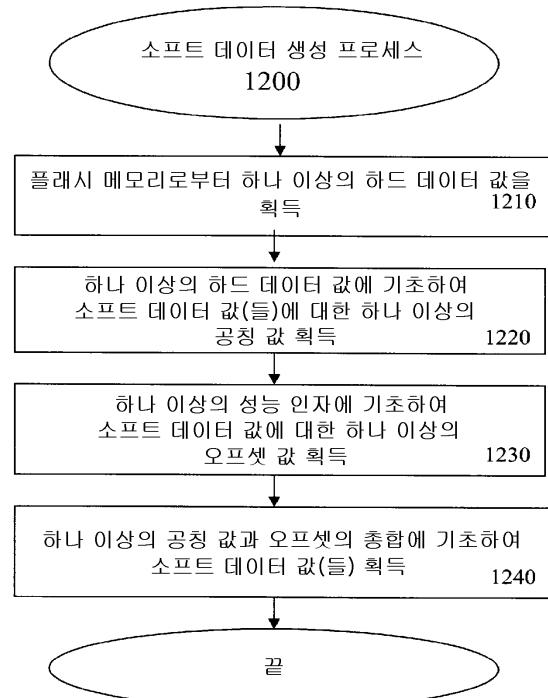

도 12는 본 발명의 특징을 포함하는 소프트 데이터 생성 프로세스의 예시적인 다른 구현을 설명하는 흐름도이다.

도 13은 본 발명의 특징을 포함하는 예시적인 하드 데이터-소프트 데이터 매핑 데이터베이스로부터의 샘플 표이다.

### **발명을 실시하기 위한 구체적인 내용**

[0016]

본 발명의 다양한 태양은 단일 레벨 셀 또는 다중 레벨 셀(MLC) NAND 플래시 메모리 장치와 같은 메모리 장치에서의 개선된 디코딩을 위한 소프트 데이터 생성 기술에 관한 것이다. 본 명세서에서, 다중 레벨 셀 플래시 메모리는 각 메모리 셀이 2 이상의 비트를 저장하는 메모리를 포함한다. 통상, 하나의 플래시 셀에 저장된 다수의 비트는 상이한 페이지에 속한다. 본 발명이 여기서 아날로그 값을 전압으로 저장하는 메모리 셀을 이용하여 설명되지만, 본 발명은, 저장된 데이터를 나타내기 위해 전압, 전류 또는 저항을 사용하는 것과 같은 메모리 장치에 대한 여하한 저장 방식과 함께 사용될 수 있으며, 이는 당업자에게 명백할 것이다.

[0017]

도 1은 종래의 플래시 메모리 시스템(100)의 개략 블록도이다. 도 1에 도시된 바와 같이, 예시적인 플래시 메모리 시스템(100)은 플래시 제어 시스템(110)과 플래시 메모리 블록(160)을 포함한다. 예시적인 플래시 제어 시스템(110)은 플래시 제어기(120), 인코더/디코더 블록(140) 및 하나 이상의 버퍼(145)를 포함한다. 다른 실시형태에서, 인코더/디코더 블록(140) 및 일부 버퍼(145)는 플래시 제어기(120) 내에서 내현될 수 있다. 인코더/디코더 블록(140) 및 버퍼(145)는, 예를 들어, 공지된 상용의 기술 및/또는 제품을 이용하여 구현될 수 있다.

[0018]

예시적인 플래시 메모리 블록(160)은 메모리 어레이(170)와 하나 이상의 버퍼(180)를 포함할 수 있으며, 이들 각각은 공지된 사용의 기술 및/또는 제품을 이용하여 구현될 수 있다. 메모리 어레이(170)는, NAND 플래시 메모리, PCM(phase-change memory), MRM 메모리, NOR 플래시 메모리 또는 다른 비휘발성 플래시 메모리와 같은 단일 수준(single-level) 또는 다중 수준(multi-level) 셀 플래시 메모리로 구현될 수 있다. 본 발명이 주로 다중 수준 셀 NAND 플래시 메모리의 맥락에서 설명되지만, 본 발명은 단일 수준 셀 플래시 메모리 및 기타 비휘발성 메모리에도 적용될 수 있으며, 이는 당업자에게 명백할 것이다.

[0019]

### 다중 수준 셀 플래시 메모리

[0020]

다중 수준 셀 NAND 플래시 메모리에서, 특정 셀과 관련된 전압 값을 사전 결정된 메모리 상태로 변환하는데 문턱 검출기가 통상 채용된다. 도 2는, 본 명세서에 참조로 포함되는 미국 특허 제6,522,580호의 개시 내용에 기초하여, 도 1의 예시적 다중 수준 셀 플래시 메모리(170)에 대한 예시적인 문턱 전압 분포를 도시한다. 일반적으로, 셀의 문턱 전압은 셀이 특정량의 전류를 도전시키기 위해 셀에 인가되어야 하는 전압이다. 문턱 전압은

셀에 저장된 데이터의 척도이다.

[0021] 도 2에 도시된 예시적인 실시형태에서, 각 저장 소자는 각 메모리 셀에 2비트의 데이터를 저장하기 위해 4개의 가능한 데이터 상태를 사용한다. 도 2는 4개의 피크(210-213)를 도시하고, 각각의 피크는 하나의 상태에 대응한다. 다중 수준 셀 플래시 장치에서, 문턱 전압 분포 그래프(200)의 상이한 피크(210-213)는 셀에 2 비트를 저장하는데 사용된다.

[0022] 문턱 전압 분포 그래프(200)의 피크(210-213)는 대응하는 이진 값으로 라벨링된다. 그러므로, 셀이 제1상태(210)에 있으면, 하위 비트(least significant bit)라고도 함)에 대한 "1"과 상위 비트(msb(most significant bit)라고도 함)에 대한 "1"을 나타낸다. 상태(210)는 일반적으로 셀의 최초의 미프로그램(unprogrammed) 또는 소거 상태이다. 유사하게, 셀이 제2상태(211)에 있으면, 하위 비트에 대한 "0"과 상위 비트에 대한 "1"을 나타낸다. 셀이 제3상태(212)에 있으면, 하위 비트에 대한 "0"과 상위 비트에 대한 "0"을 나타낸다. 마지막으로, 셀이 제4상태(213)에 있으면, 하위 비트에 대한 "1"과 상위 비트에 대한 "0"을 나타낸다.

[0023] 문턱 전압 분포(210)는 0 볼트 아래의 음의 문턱 전압 수준을 갖는 소거 상태("11" 데이터 상태)에 있는 어레이 내의 셀의 문턱 전압  $V_1$ 의 분포를 나타낸다. "10"과 "00" 사용자 데이터를 각각 저장하는 메모리 셀의 문턱 전압 분포(212 및 212)는 각각 0과 1 볼트 사이 및 1과 2 볼트 사이로 도시된다. 문턱 전압 분포(213)는 "01" 데이터 상태로 프로그램된 셀의 분포를 도시하며, 판독 폐스 전압(read pass voltage)의 2와 4.5 볼트 사이로 설정된 문턱 전압 수준을 갖는다.

[0024] 그러므로, 도 2의 예시적인 실시형태에서, 0 볼트, 1 볼트 및 2 볼트가 각 수준 또는 상태 사이의 전압 수준 문턱으로 사용될 수 있다. 전압 수준 문턱은 플래시 메모리(160)(예를 들어, 플래시 메모리(160)내의 감지 회로)에 의해 주어진 셀의 전압 수준 또는 상태를 결정하는데 사용된다. 플래시 메모리(160)는, 측정된 전압과 전압 수준 문턱의 비교에 기초하여 각 셀에 하나 이상의 비트를 할당할 것이고, 이는 플래시 제어 시스템(110)으로 하드 디시젼(hard decision)으로서 전송된다. 추가하여 또는 다르게는, 소프트 정보를 이용하는 구현에 있어서, 플래시 메모리(160)는 측정된 전압 또는 측정된 전압의 양자화된 버전을 소프트 정보로서 플래시 제어 시스템(110)에 전송할 수 있고, 이 경우 메모리 셀에 저장된 비트의 수보다 많은 비트가 측정된 전압을 나타내는데 사용된다.

[0025] 또한, 셀은 통상 공지의 프로그램/확인(Program/Verify) 기술을 이용하여 프로그램됨이 중요하라. 일반적으로, 프로그램/확인 사이클 동안, 플래시 메모리(160)는, 셀 트랜지스터에 전하를 저장하기 위해 최소 타겟 문턱 전압을 초과할 때까지 점진적으로 증가하는 전압을 인가한다. 예를 들어, 도 2의 예에서 '10' 데이터 상태를 프로그램할 때, 플래시 메모리(160)는 0.4V의 최소 타겟 문턱 전압을 초과할 때까지 셀 트랜지스터에 전하를 저장하도록 증가하는 전압을 점진적으로 인가할 수 있다.

[0026] 이후에 자세히 설명하는 바와 같이, 단일의 메모리 셀에 저장된 2 비트 각각은 상이한 페이지로부터 온 것이다. 달리 말하면, 각 메모리 셀에 저장된 2 비트 각각은 상이한 페이지 주소를 운반한다. 도 2에 도시된 오른쪽의 비트는 하위 페이지 주소가 입력될 때 액세스된다. 왼쪽 비트는 상위 페이지 주소가 입력될 때 액세스된다.

[0027] 도 3은 MLC(multi-level cell) 플래시 메모리 장치(160)의 예시적 플래시 셀 어레이(300)의 아키텍쳐를 도시하는데, 여기서 각각의 예시적인 셀은 통상 2 비트를 저장하는 부동 게이트 트랜지스터에 대응한다. 도 3에서, 각 셀은 2개의 비트가 속하는 2 개의 페이지에 대한 2개의 숫자와 관련된다. 예시적인 셀 어레이 섹션(300)은 워드라인 n 내지 n+2 및 4개의 비트라인을 도시한다. 예시적인 플래시 셀 어레이(300)는 짹수 및 홀수 페이지로 분할되고, 여기서, 예를 들어, (번호 0 및 2를 갖는 셀과 같은) 짹수를 갖는 셀은 짹수 페이지에 대응하고, (번호 1 및 3을 갖는 셀과 같은) 홀수를 갖는 셀은 홀수 페이지에 대응한다. 워드라인 n은 예를 들어 짹수 비트라인의 짹수 페이지(0과 2)과, 홀수 비트라인의 홀수 페이지(1 및 3)을 저장한다.

[0028] 또한, 도 3은 짹수나 홀수 비트라인 셀이 표시된 순서로 연속하여(아래에서 위로) 선택되고 프로그램되는 예시적인 프로그램 시퀀스를 나타낸다. 숫자는 페이지가 프로그램되는 순서를 나타낸다. 예를 들어, 페이지 0은 페이지 1 전에 프로그램된다. 짹수 및 홀수 페이지의 프로그래밍에 대한 추가적인 논의에 대해서는, 예를 들어, 본 명세서에 참조로 포함되는 K.-T. Park 등의 "A Zeroing Cell-to-Cell Interference Page Architecture with Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories," (IEEE Journal of Solid-State Circuits, Vol. 43, No. 4, 919-928 (2008 4월))을 참조하라.

[0029] 도 4는 도 2의 전압 할당 방식에 대한 예시적인 2단 MLC 프로그래밍 방식(400)을 도시한다. 도 4에 도시된 바

와 같이, LSB 프로그램 단계 동안, 소거 상태(410)에 있는 선택된 셀의 상태는 LSB가 0이면 최저 프로그램 상태(411)로 이동한다. 그러므로, LSB 프로그래밍 단계에서, 메모리 셀은 소거 상태 '11'로부터 '10'으로 프로그램된다. 다음, MSB 프로그램 단계동안, 2개의 상태, 상태 '00'(412)와 '01'(413)가 이전 LSB 데이터에 따라 순차적으로 형성된다. 일반적으로, MSB 프로그래밍 단계동안, '10' 상태는 '00'으로 프로그램되고 상태 '11'은 '01'로 프로그램된다.

[0030] 도 4의 프로그래밍 방식(400)은 상태 410으로부터 상태 413으로의 상태 변화와 관련된 최대 전압 변이를 도시함을 유의하라. 상태 변화와 관련된 최대 전압 변이를 감소시켜 전압 변이에 의해 유발되는 ICI를 감소시키기 위해 많은 프로그래밍 방식이 제안 또는 제시되어왔다.

[0031] 도 5a 및 5b는, 함께, 이웃 셀에 가해진 ICI를 감소시키는 다른 MLC 프로그래밍 방식(500)을 도시한다. 도 5a에 도시된 바와 같이, LSB 프로그래밍 단계 동안, 메모리 셀은 상태 '11'로부터 임시 (중간) 상태로서 'x0'로 SLC 프로그래밍과 유사한 방법으로 프로그램된다. 동일한 워드라인 내의 인접 셀도 LSB 프로그램된 후에, ICI에 의해 도 5a에서 퍼크(510)로 도시된 바와 같이 분포가 넓어질 수 있다. 그 후, 도 5b에 도시된 MSB 프로그래밍 단계에서, 'x0' 상태는 입력 데이터에 대응하는 최종 상태로서 '00'이나 '10'으로 프로그램되거나, 그렇지 않으면 '11' 상태가 최종 '01' 상태로 프로그램된다. 일반적으로, '11' 셀을 제외한 모든 메모리 셀은 MSB 프로그래밍 단계에서 LSB에 대한 임시 프로그램 상태로부터 그들의 최종 단계로 재 프로그램되어, 인접 셀에 의해 유발된 ICI가 많이 감소될 수 있다. 최종 상태의 셀은 중간 상태에 있을 때 겪었던 ICI를 겪지 않는 데, 이는 셀이 최종 상태로 재 프로그램됐기 때문이다. 최종 상태의 셀은 최종 상태에 있는 아래로 겪은 ICI만을 겪을 것이다. 상술한 바와 같이, 중간 프로그램 상태를 이용하는 도 5a 및 5b의 다단계 프로그래밍 시퀀스는 최대 전압 변화를 감소시키고, 그에 따라 이를 전압 변화에 의해 유발되는 ICI를 감소시킨다. 도 5b에서 예를 들어, MSB 프로그래밍 단계 동안 최대 전안 변이는 상태 '11'에서 '01'로의 전이 및 상태 'x0'에서 '10'으로의 전이에 각각 관련된다는 것을 볼 수 있다. 이를 전압 변이는 도 4에서 상태 '11'로부터 '01'로의 최대 전압 변이보다 현저히 작다.

[0032] 도 6은 MLC(multi-level cell) 플래시 메모리 장치(130) 내의 예시적인 플래시 셀 어레이(600)를 더 자세히 도시한다. 도 6에 도시된 바와 같이, 플래시 셀 어레이(600)는 플래시 셀,  $c_i$ 당 3 비트를 저장한다. 도 6은 한 블록에 대한 플래시 셀 어레이 아키텍쳐를 도시하는데, 여기서 각 예시적인 셀은 통상 3 비트를 저장하는 부동 게이트 트랜지스터에 대응한다. 예시적인 셀 어레이(600)는 m개의 워드라인과 n개의 비트라인으로 이루어진다. 통상, 현재의 다중 페이지(multi-page) 셀 플래시 메모리에서, 단일 셀 내의 비트는 서로 다른 페이지에 속한다. 도 6의 예에서, 각 셀에 대한 세 개의 비트는 세 개의 상이한 페이지에 대응하고, 각 워드라인은 3 페이지를 저장한다. 다음 논의에서, 페이지 0, 1 및 2는 워드라인 내의 하위, 중간 및 상위 페이지 수준이라고 지칭한다.

[0033] 상술한 바와 같이, 플래시 셀 어레이는 짹수 및 홀수 페이지로 더 나눠질 수 있으며, 이 경우, 예를 들어, (도 6의 셀 2 및 4와 같은) 짹수를 갖는 셀은 짹수 페이지에 대응하고 (도 6의 셀 1 및 3과 같은) 홀수를 갖는 셀은 홀수 페이지에 대응한다. 이 경우에, (페이지 0과 같은) 페이지는 짹수 셀 내 짹수 페이지(짜수 페이지 0)을, 홀수 셀 내 홀수 페이지(홀수 페이지 0)을 포함할 것이다.

#### 셀간 간섭 및 기타 외란

[0035] 도 7은 다수의 예시적인 공격자 셀에 기인하여 타겟 셀에 존재하는 셀간 간섭, 백 패턴 의존성, 잡음 및 기타 왜곡과 같은 외란을 도시한다. 도 7에서 다음의 표기법이 사용된다.

[0036] WL: 워드라인;

[0037] BL: 비트라인;

[0038] BLo: 홀수 비트라인;

[0039] BLe: 짹수 비트라인; 및

[0040] C: 커페시턴스.

[0041] 예를 들어, ICI가 타겟 셀(710)이 프로그램된 후에 프로그램되는 공격자 셀(720)에 의해 유발된다. ICI는 타겟 셀(710)의 전압  $V_t$ 를 변화시킨다. 예시적인 실시형태에서, "상향(bottom up)" 프로그래밍 방식이 가정되고, 워드라인  $i$  및  $i+1$ 의 인접 공격자 셀이 타겟 셀(710)에 대해 ICI를 유발한다. 블록의 이러한 상향 프로그래밍으

로, 하위 워드라인 i-1로부터의 ICI가 제거되고, 도 7에 도시된 바와 같이 5 개까지의 이웃 셀이 공격자 셀(720)로서 ICI에 기여한다. 그러나, 본 명세서에 개시된 기술은 워드라인 i-1과 같은 다른 워드라인으로부터의 공격자 셀이 ICI에 기여하는 경우로도 일반화될 수 있으며, 이는 당업자에게 명백할 것이다. 워드라인 i-1, i 및 i+1로부터의 공격자 셀이 ICI에 기여하는 경우, 8개까지의 최근접 이웃 셀이 고려되어야 한다. 타겟 셀로부터 더 면 다른 셀은, 그들의 ICI에의 기여가 무시할 수 있다면, 무시될 수 있다. 일반적으로, 공격자 셀(720)은 프로그래밍 시퀀스 방식(상향 또는 홀수/짝수 기술 등)을 분석함으로써 식별되어 주어진 타겟 셀(710) 후에 프로그램되는 공격자 셀(720)을 식별한다.

[0042] 일반적으로,  $V_t$ 는 셀 상에 저장된 데이터를 나타내는 전압이고 판독 동작 동안 획득된다.  $V_t$ 는 판독 동작에 의해, 예를 들어, 셀 당 저장된 비트 수보다 더 높은 정확도의 소프트 전압 값으로서 또는 셀 당 저장된 비트 수(예를 들어, 3비트/셀 플래시에 대해 3비트)와 동일한 해상도를 갖는, 하드 전압 수준으로 양자화된 값으로 획득될 수 있다.

[0043] ICI 감소 기술에 대한 추가적인 논의에 대해서는, 예를 들어, 각각 본 명세서에 참조로 포함되는, 명칭이 "Methods and Apparatus for Read-Side Intercell Interference Mitigation in Flash Memories"인 국제 특허 출원 PCT/US09/49326호, 또는 명칭이 ""Methods and Apparatus for Write-Side Intercell Interference Mitigation in Flash Memories"인 국제 특허 출원 PCT/US09/49327호를 참조하라.

[0044] 도 8은 본 발명에 따른 제어기 기반 소프트 데이터 생성 기술을 포함하는 예시적인 플래시 메모리 시스템(800)의 개략적인 블록도이다. 도 8에 도시된 바와 같이, 예시적인 플래시 메모리 시스템(800)은 인터페이스(850)에 의해 연결된 플래시 메모리 블록(860)과 플래시 제어 시스템(810)을 포함한다. 예시적인 플래시 제어 시스템(810)은 통상 하나 이상의 집적 회로 상에 플래시 제어기(820)와 판독 채널(825)을 포함한다.

[0045] 예시적인 판독 채널(825)은 신호 처리 유니(830), 인코더/디코더 블록(840) 및 하나 이상 버퍼(845)를 포함한다. "판독 채널"이라는 용어는 기록 채널도 포함함을 유의하라. 다른 실시형태에서, 인코더/디코더 블록(840) 및 일부 버퍼(845)는 플래시 제어기(820) 내에서 구현될 수 있다. 인코더/디코더 블록(840)과 버퍼(845)는, 예를 들어, 본 발명의 특징 및 기능을 제공하기 위해 본 명세서와 같이 변경한 공지된 상용의 기술 및/또는 제품을 이용하여 구현될 수 있다.

[0046] 예시적인 신호 처리 유닛(830)은, 예를 들어, 각각 도 12a 및 12b와 관련하여 후술하는 하나 이상의 소프트 디매퍼 및/또는 소프트 데이터 생성 프로세스(835)를 구현하는 하나 이상의 프로세서를 포함한다. 예시적인 플래시 메모리 블록(860)은, 각각 공지된 상용의 기술 및/또는 제품을 이용하여 구현될 수 있는 메모리 어레이(870)와 하나 이상의 버퍼(880)를 포함한다.

[0047] 개시된 소프트 데이터 생성 기술의 다양한 실시형태에서, 예시적인 인터페이스(850)는 공격자 셀과 관련된 정보를 나타내는 값과 같은 종래의 플래시 메모리 시스템과 관련된 추가적인 정보를 운반하여야 할 수 있다. 그러므로, 인터페이스(850)는 종래 플래시 메모리 시스템의 인터페이스에 비해 더 큰 용량 또는 더 빠른 레이트를 가질 필요가 있을 수 있다. 인터페이스(850)는 선택적으로는 예를 들어, 명칭이 "Methods and Apparatus for Interfacing Between a Flash Memory Controller and a Flash Memory Array"이고 2009년 6월 30일에 출원되었으며 본 명세서에 참조로 포함되는 국제 특허 출원 PCT/US09/49328호(대리인 정리번호 08-0769)의 교시에 따라 구현될 수 있는데, 이는, 예를 들어, 더블 데이터 레이트(DDR) 기술을 이용하여 인터페이스(850)의 정보 운반 용량을 증가시킨다. 기록 동작 동안, 인터페이스(850)는 타겟 셀에 저장될 프로그램 값을 전달하는데, 통상 페이지 또는 워드라인 수준 액세스 기술을 이용한다. 예시적인 페이지 또는 워드라인 수준 액세스 기술에 대한 더 상세한 논의에 대해서는, 예를 들어, 본 명세서에 참조로 포함되는, 명칭이 "Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding and Per-Page Coding"인 2009년 3월 11일자로 출원된 국제 특허 출원 PCT/US09/36810호를 참조하라.

[0048] 판독 동작 동안, 인터페이스(850)는 타겟 셀 및 공격자 셀에 대해 메모리 어레이(870)로부터 획득된 하드 및/또는 소프트 판독 값을 전달한다. 예를 들어, 타겟 셀로 페이지에 대한 판독 값에 더하여, 상위/하위 워드라인 또는 인접한 짝수 또는 홀수 비트 라인의 하나 이상의 인접 페이지에 대한 판독 값이 인터페이스 버스를 통해 전달된다. 도 8의 실시형태에서, 개시된 소프트 데이터 생성 기술이 플래시 메모리 외부에서, 통상 최저 면적을 달성하기 위해 논리 회로를 위해 최적화된 처리 기술에서 구현된다. 그러나, 이는 인터페이스(850) 상에 전달될 수 있는 추가적인 공격 셀 데이터를 희생하게 된다.

[0049] 도 9는 본 발명의 다른 실시형태에 따른 메모리 기반 소프트 데이터 생성 기술을 포함하는 예시적인 플래시 메

모리 시스템(900)의 개략적인 블록도이다. 도 9에 도시된 바와 같이, 예시적인 플래시 메모리 시스템(900)은 플래시 제어 시스템(910)과 플래시 메모리 블록(960)을 포함하고, 이들은 인터페이스(950)에 의해 연결된다.

[0050] 예시적인 플래시 제어 시스템(910)은 플래시 제어기(920)과 선택적인 판독 채널(925)을, 통상 하나 이상의 접적 회로 상에 포함한다. 다른 실시형태에서, 인코더/디코더 블록(940) 및 일부 베퍼(945)는 플래시 제어기(920) 내에 구현될 수 있다. 예시적인 플래시 제어기(920)는, 예를 들어, 본 발명의 특성 및 기능을 지원하도록 본 명세서에서와 같이 수정된, 공지된 상용의 기술 및/또는 제품을 이용하여 구현될 수 있다. 예시적인 판독 채널(925)은 인코더/디코더 블록(940)과 하나 이상의 베퍼(945)를 포함한다. 인코더/디코더 블록(940) 및 베퍼(945)는 공지된 상용의 기술 및/또는 제품을 이용하여 구현될 수 있다.

[0051] 예시적인 플래시 메모리 블록(960)은 메모리 어레이(970) 및 하나 이상의 베퍼(980)를 포함하며, 각각은 공지된 상용 기술 및/또는 제품을 이용하여 구현될 수 있다. 또한, 예시적 플래시 메모리 블록(960)은, 각각이 예를 들어 도 12a 및 12b와 관련하여 후술되는 하나 이상의 소프트 디매핑 및/또는 소프트 데이터 생성 프로세스(990)를 구현하는 하나 이상의 프로세서를 포함하는 예시적인 신호 처리 유닛(985)을 포함한다.

[0052] 개시된 소프트 데이터 생성 기술의 다양한 실시형태에서, 예시적인 인터페이스(950)는, 공격자 셀과 관련된 정보를 나타내는 값과 같은 종래의 플래시 메모리 시스템에 관한 추가적인 정보를 운반하여야 할 수 있다. 그러므로, 인터페이스(950)는 종래 플래시 메모리 시스템의 인터페이스에 비해 더 큰 용량 또는 더 빠른 레이트를 가질 필요가 있을 수 있다. 인터페이스(950)는 선택적으로는 예를 들어, 명칭이 "Methods and Apparatus for Interfacing Between a Flash Memory Controller and a Flash Memory Array"이고 2009년 6월 30일에 출원되었으며 본 명세서에 참조로 포함되는 국제 특허 출원 PCT/US09/49328호(대리인 정리번호 08-0769)의 교시에 따라 구현될 수 있는데, 이는, 예를 들어, 더블 데이터 레이트(DDR) 기술을 이용하여 인터페이스(950)의 정보 운반 용량을 증가시킨다.

[0053] 기록 동작 동안, 인터페이스(950)는 타겟 셀 및 공격 셀에 저장될 프로그램 데이터를 전달한다. 판독 동작 동안, 인터페이스(950)는 타겟 셀(들) 및 선택적으로는 공격자 셀에 대해 새로운 하드 또는 소프트 판독 값 또는 데이터를 전달한다. 통상, 단일 판독 액세스에 대해 운반되는 정보는 한 페이지 또는 워드라인의 데이터이다. 타겟 셀에 대한 데이터를 전송하는 것만이, 통상 논리 회로가 아니라 메모리에 최적화된 플래시 메모리를 제조하는데 사용되는 메모리 처리 기술을 이용하여 메모리 내에 소프트 데이터 생성 프로세스를 구현하는 것을 비용으로, 인터페이스(950)에 대한 대역폭 요구를 감소시킨다는 점을 유의하라.

#### 성능 조정에 기초한 소프트 데이터 생성

[0055] 이전에 언급한 바와 같이, 현재 플래시 메모리(860, 960)는 통상 디코딩을 위해 플래시 제어 시스템(810, 910)으로 하드 데이터를 제공하기만 한다. 그러나, 소프트 데이터가 디코딩 프로세스에서 에러 레이트 성능을 개선할 수 있다는 것이 잘 알려져 있다. 그러므로, 본 발명은 소프트 데이터를 추정 또는 강화하고 그에 의해 디코딩 성능을 개선하기 위해 플래시 메모리(860, 960)로부터의 하드 데이터를 사용하는 소프트 데이터 생성 기술을 제공한다.

[0056] 본 발명의 일 태양에 따르면, 하드 데이터에 기초하여 플래시 메모리 장치(860, 960)와 같은 메모리 장치에 대해 소프트 데이터가 생성되고, 하나 이상의 성능 인자에 기초하여 조정(adjustment)가 생성된다. 본 명세서에서 사용되는 때에, 소프트 데이터는, 플래시 메모리 장치(860, 960)의 메모리 셀 내에 저장된 비트의 수보다 많은 수의 비트가 측정된 전압을 나타내는데 사용되는 경우 소프트 값(soft value)을 포함하거나, 또는 메모리 셀 내에 저장된 비트의 신뢰도(reliability)를 나타내는 LLR을 포함한다. 하드 데이터는 메모리 셀 내에 저장된 (전압 수준과 같은) 수준 또는 (소프트 정보가 없는) 검출된 데이터 비트를 지칭하고, 이들은 플래시 메모리(870, 970)로부터 판독되고 종래의 플래시 메모리 장치에서 플래시 제어 시스템에 제공된다.

[0057] 예시적인 실시형태에 있어서, 소프트 데이터 값은, 플래시 메모리 블록(810, 910)에 의해 할당된 하드 데이터 값에 기초하는 공칭(nominal) 값과 플래시 메모리 블록(810, 910)의 성능에 영향을 주는 하나 이상의 인자를 보상하는 오프셋 값(또는 델타 값)의 합이다. 이 소프트 데이터 값은, 이후 LLR을 계산하는데 사용되는 (소프트 전압 값과 같은) 소프트 판독 값 또는 저장된 비트의 신뢰도를 나타내는 LLR 중 어느 하나이다. LLR의 생성 및 사용에 대한 더 자세한 논의에 대해서는, 예를 들어, 각각이 본 명세서에 참조로 포함되는, 명칭이 "Methods and Apparatus for Soft Demapping and Intercell Interference Mitigation in Flash Memories"이고 2009년 6월 30일에 출원된 국제 특허 출원 PCT/US09/49333 및 본 출원과 동일자로 출원된 명칭이 "Methods and Apparatus for Soft Data Generation in Flash Memories"인 국제 특허 출원을 참조하라. 소프트 데이터 생성

기(835, 990)에 의해 생성된 LLR은 LPDC(Low Parity Density Check) 디코더와 같은 디코더에 제공된다.

[0058] 도 10은 예시적인 플래시 메모리 시스템(1000)의 개략적 블록도이다. 도 10은 본 발명의 소프트 데이터 생성 기술을 더 자세히 도시한다. 도 10에 도시된 바와 같이, 플래시 메모리 시스템(1000)은 인터페이스 버스(1050)에 의해 연결된, 플래시 제어 시스템(1020)과 플래시 메모리 블록(1010)을 포함한다.

[0059] 플래시 메모리 블록(1010)은 메모리 어레이(1015)에 포함된다. 플래시 메모리 블록(1010)은 메모리 어레이(1015)를 판독하고 판독되는 각 셀에 저장된 하드 데이터 값(즉, 하드 데이터 비트 또는 하드 전압 수준과 같은 하드 수준)을 결정한다. 이후에 논의되는 바와 같이, 하드 데이터 값은 통상 플래시 메모리 블록(1020)에 의해 할당되고, 추가의 디코딩 및 처리를 위해 인터페이스(1050)를 통해 플래시 제어기(1020)로 전달된다.

[0060] 예시적인 플래시 제어기(1020)는 도 11 및 12와 관련하여 후술하는 소프트 데이터 생성기(1100) 및 디코더(1060)를 포함한다. 일반적으로, 소프트 데이터 생성기(1100, 1200)는 플래시 메모리 블록(1020)에 의해 할당된 하드 데이터 값 및 하나 이상의 성능 인자 조정을 사용하여 소프트 데이터를 생성한다. 디코더(1060)는, 예를 들어, 신뢰 전파, 메시지 전달, 합-곱 또는 최소-합 알고리즘과 같은 LDPC 알고리즘을 사용하여 구현될 수 있다. 본 명세서에서 설명되는 소프트 데이터 생성기(1100, 1200)의 기능은 플래시 제어기(820), 판독 채널(825), 신호 처리 유닛(830) 및 디코더(840) 중 하나 이상에서 구현될 수 있음을 유의하라(예를 들어, 도 8 참조).

[0061] 이전에 언급한 바와 같이, 본 발명의 일 태양은 하드 데이터와 추가 성능 인자의 함수로서 소프트 데이터를 계산한다. 일 예시적인 실시형태에서, 소프트 데이터 값은 플래시 메모리 블록(1010)에 의해 할당된 하드 데이터 수준에 기초한 공칭 값과 플래시 메모리 블록(1010)의 성능에 영향을 주는 하나 이상의 성능 인자를 보상하는 오프셋 값(또는 델타 값)의 합이다.

[0062] 예시적인 실시형태에서, 플래시 메모리 블록(1010)의 성능에 영향을 주는 성능 인자는, 인듀어런스(endurance) (예를 들어, 프로그램/소거 사이클의 수), 판독 사이클의 수, 리텐션(retention) 시간, 플래시 메모리의 온도 또는 온도 변화, 플래시 메모리를 제조하는데 사용되는 프로세스 코너, 셀간 간섭 영향 또는 다른 외란 메커니즘에 기인한 영향, 메모리 어레이 내의 위치 (워드라인 내 페이지 수준, 짹수 또는 홀수 비트라인 등) 및 공격자 셀에 저장된 데이터 패턴 중 하나 이상을 포함한다. 도 13과 관련하여 후술하는 바와 같이, 일 예시적 실시 형태에서, 오프셋 값은 각각의 프로그램 수준에 대한 각각의 성능 인자에 대해 할당될 수 있다. 성능 열화를 보상하는 오프셋 값을 획득하기 위해, 성능 인자가 예를 들어 제조 테스트 동안에 미리 또는 간헐적이나 주기적으로 측정될 수 있다. 이를 성능 인자는 플래시 제어 시스템(810, 910)의 레지스터 또는 플래시 메모리(860, 960)에 저장되거나 프로그램될 수 있다.

[0063] 예를 들어, 소프트 데이터 값은 다음과 같이 계산될 수 있다.

$$\text{소프트 데이터 값} = \begin{cases} \text{nominal value}_0 - \text{offset} & (\text{하드 데이터 값이 } 0\text{인 경우}) \\ \text{nominal value}_1 - \text{offset} & (\text{하드 데이터 값이 } 1\text{인 경우}) \end{cases}$$

[0064] 여기서 소프트 데이터 값은, 예를 들어, LLR을 나타내고 소프트 데이터 값의 부호는 하드 데이터 값을 나타내며 소프트 데이터 값의 크기(magnitude)는 신뢰도를 나타내고, nominal value<sub>0</sub>은 비트 0에 대한 최대 가능 신뢰도를 나타내는 양수이고, nominal value<sub>1</sub>은 비트 1에 대한 최대 가능 신뢰도를 나타내는 음수이며, offset은 플래시 메모리 블록(1010)의 성능에 영향을 주는 고려되는 성능 인자를 보상하는 총합(aggregate) 오프셋 값이다. 예를 들어, 0인 하드 데이터 값에 대해 nominal value<sub>0</sub>은 +2이고, 1인 하드 데이터 값에 대해 nominal value<sub>1</sub>은 -2이다. 고려되는 성능 인자에 기초하여, 오프셋이 0보다 클 때 공칭 값의 크기는 감소된다. 달리 말하면, 소프트 데이터 값과 관련되는 신뢰도는 하드 데이터 값의 신뢰도를 감소시키는 성능 인자에 기초하여 감소된다.

[0066] 통상, 소프트 데이터 값의 크기는 대응 하드 데이터 값의 신뢰도를 나타내고, 소프트 데이터 값의 부호는 대응 하드 데이터 값이 이진 0인지 1인지를 나타낸다. 예시적인 실시형태에서, 소프트 데이터 값은 -2과 +2 사이에서 변화할 수 있는데, 2는 최대 신뢰도를 갖는 이진 0의 값에 대응하고 -2는 최대 신뢰도를 갖는 이진 1의 값에 대응한다. 위의 식에서 채용된 오프셋 값은 플래시 메모리 장치의 신뢰도에 영향을 줄 외란을 특징화한다. 일반적으로, 오프셋 값은 예상되는 외란에 비례하여 변한다(예를 들어, 외란이 클수록 오프셋 값이 크다).

[0067] 일 예시적인 실시형태에서, 오프셋은 선택적으로 사전 규정된 값으로 포화(saturate)될 수 있다. 예를 들어, 오프셋이 플래시 메모리에 의해 할당된 비트에 대응하는 소프트 데이터 값의 부호를 변화시키지 않도록 보장하

기 위해 오프셋이 포함될 수 있다.

[0068] 도 11은 본 발명의 특징을 포함하는 예시적인 소프트 데이터 생성 프로세스(1100)를 설명하는 흐름도이다. 일반적으로, 소프트 데이터 생성 프로세스(1100)는 하드 데이터 값을 소프트 데이터 값으로 직접, 예를 들어, 다양한 고려되는 성능 인자를 다루는 하드-소프트(hard-to-soft) 데이터 매핑 데이터베이스(1300)를 이용하여, 매핑함으로써 소프트 데이터 값을 생성한다.

[0069] 도 11에 도시된 바와 같이, 소프트 데이터 생성 프로세스(1100)는 최초에 단계 1110 동안 플래시 메모리(1010) 으로부터 하나 이상의 하드 데이터 값을 획득한다. 그 후, 단계 1120 동안, 소프트 데이터 생성 프로세스(1100)는 하나 이상의 하드 데이터 값에 기초하여 하나 이상의 소프트 데이터 값을 획득하고, 플래시 메모리(1010)의 하나 이상의 사전 규정된 성능 인자에 기초하여 하나 이상의 조정을 획득한다. 예를 들어, 소프트 데이터 생성 프로세스(1100)는 하드-소프트 도 13 데이터 매핑 데이터베이스(1300) 내에서 룩업(look-up)을 수행하기 위해 하드 데이터를 이용할 수 있다. 소프트 데이터 값은 후에 LLR을 계산하는데 사용되는 (소프트 전압 수준과 같은) 소프트 판독 값 또는 저장된 비트의 신뢰도를 나타내는 LLR 중 어느 하나를 나타낸다.

[0070] 도 12는 본 발명의 특징을 포함하는 소프트 데이터 생성 프로세스(1200)의 예시적인 다른 구현을 설명하는 흐름도이다. 일반적으로, 소프트 데이터 생성 프로세스(1200)는, 플래시 메모리 블록(1010)에 의해 할당된 하드 데이터 값에 기초하는 공칭 값과 플래시 메모리 블록(1010)의 성능에 영향을 주는 하나 이상의 성능 인자를 보상하는 오프셋 값을 더함으로써 소프트 데이터 값을 생성한다. 소프트 데이터 값은 후에 LLR을 계산하는데 사용되는 (소프트 전압 수준과 같은) 소프트 판독 값 또는 저장된 비트의 신뢰도를 나타내는 LLR 중 어느 하나를 나타낸다.

[0071] 도 12에 도시된 바와 같이, 소프트 데이터 생성 프로세스(1200)는 최초에 단계 1210 동안 플래시 메모리(1010) 으로부터 하나 이상의 하드 데이터 값을 획득한다. 그 후, 소프트 데이터 생성 프로세스(1200)는 단계 1220 동안 하나 이상의 하드 데이터 값에 기초하여 대응하는 하나 이상의 공칭 값을 획득하고, 단계 1230 동안 하나 이상의 고려되는 성능 인자에 기초하여 대응하는 하나 이상의 오프셋 값을 획득한다. 마지막으로, 단계 1240 동안 소프트 데이터 생성 프로세스(1200)는 획득된 하나 이상의 공칭 값과 오프셋 값의 총합(aggregation)에 기초하여 하나 이상의 희망 소프트 데이터 값을 획득한다.

[0072] 도 13은 플래시 메모리 셀 내에 LSB(least significant bit) 및 MSB(most significant bit)를 저장하는 예시적인 2비트/셀 MLC 플래시 메모리에 대한 본 발명의 특징을 포함하는 예시적인 하드 데이터-소프트 데이터(hard data-to-soft data) 매핑 데이터베이스(1300)로부터의 샘플 표이다. MLC 플래시 메모리 내 상이한 페이지 수준 (MSB와 LSB 페이지 등)은 다양한 성능 인자에 의해 상이하게 영향을 받으므로, 플래시 메모리 시스템의 여러 레이트 성능은 상이한 페이지 수준에 대해 별도의 오프셋을 사용함으로써 개선될 수 있다. 예시적인 하드 데이터-소프트 데이터 매핑 데이터베이스(1300)는 기록(1310)에 표시된 하드 데이터 값(예를 들어, 이진 1 또는 이진 0) 및 기록(1320)에 표시된 프로그램/소거 사이클의 수에 기초하여 기록(1330 및 1340)에 각각 LSB와 MSB에 대한 소프트 데이터를 기록한다. 이 예시적인 데이터베이스(1300)에서, 여러 레이트 성능을 개선하기 위해 이진 1 및 0에 대해 별도의 오프셋이 사용된다. 이진 1과 0에 대해 동일한 오프셋을 사용하고, 또한 MSB와 LSB 페이지와 같은 상이한 페이지 수준에 대해 동일한 오프셋을 사용하는 것은 여러 레이트 성능을 회생하여 데이터베이스의 복잡도를 감소시킬 수 있다.

[0073] 하드 데이터-소프트 데이터 매핑 데이터베이스(1300)는 짹수/홀수 비트 라인에 대한 오프셋 및/또는 메모리 어레이 내의 상이한 워드라인 위치와 같은 추가의 위치 특정(location-specific) 성능 인자 오프셋을 표시할 수도 있다.

[0074] 하드 데이터-소프트 데이터 매핑 데이터베이스(1300)는 위에서 논의한 예시적인 구현을 가정하되, 이진 0의 값은 +2로 매핑될 수 있고 이진 1의 값은 -2에 매핑될 수 있음을 유의하라. 패턴 의존성 및/또는, 판독 사이클 수, 프로세스 코너 및 온도 변화와 같은 추가적인 성능 인자를 설명하기 위해 예시적인 표(1300)는 선택적으로 다차원 표로 구현될 수 있음을 유의하라.

[0075] 패턴 의존 및 위치 특정 성능 인자의 더 상세한 논의에 대해서는, 예를 들어, 본 출원과 동일자로 출원되고 본 명세서에 참조로 포함되는 명칭이 "Methods and Apparatus for Soft Data Generation in Flash Memories" 국제 특허 출원을 참조하라.

[0076] 프로그램/소거 사이클 및 인듀어런스를 설명하고 상이한 전압 수준에 대해 상이한 오프셋을 채용하는 도 4에 도시된 전압 분포에 대한 예시적인 구현을 고려하자. 또한, 이 구현에서, 성능 인자 오프셋은 통상-통상(TT;

typical-typical), 고속-고속(FF; fast-fast) 및 저속-저속(SS; slow-slow)와 같은 복수의 상이한 프로세스 코너에 대해 특정된다. 이 예시적인 구현에서의 다음 성능 인자는, 예를 들어, 해당 성능 인자와 관련된 조건 하에서 플래시 메모리의 오프셋을 특징지우는 측정 또는 다른 제조 테스트에 기초할 수 있다:

[0077] (1) 인듀어런스 인자: 500 소거/프로그램 사이클마다, 오프셋은 비트 라벨 '11'을 갖는 수준 0(410)에 대해 0.125, 비트 라벨 '10'을 갖는 수준 1(411) 및 비트 라벨 '01'을 갖는 수준 3(413)에 대해 0.375, 비트 라벨 '00'을 갖는 수준 2(412)에 대해 0.25.

[0078] (2) 프로세스 코너 인자: 플래시 메모리가 제조되는 상이한 프로세스 코너에 대해 오프셋은, SS: 0.25 ; TT: 0; FF: 0.375.

[0079] 그러므로, 500 소거/프로그램 사이클 후의 수준 1 및 SS 프로세스 코너에 대해, 소프트 데이터는 LSB(하드 데이터 비트=0)에 대해  $2 - 0.375 - 0.25 = 1.375$ 일 것이다. MSB 비트(하드 데이터 비트=1)에 대한 소프트 데이터는  $-2 + 0.375 + 0.25 = -1.375$ 일 것이다. 이 예시적인 실시형태에서, 셀에서 동일한 성능 인자 오프셋이 LSB와 MSB 양자 모두에 대해 사용된다. 상술한 바와 같이, 여러 레이트 성능을 더 개선하기 위해, LSB와 MSB 양자 모두에 대해 상이한 성능 인자 오프셋이 사용될 수 있다.

[0080] 본 발명의 다른 태양에 따르면, 강화된 소프트 데이터 값이 플래시 메모리 장치에 의해 최초에 할당되는 소프트 데이터 값으로부터 생성된다. 강화된 소프트 데이터 값을 생성하기 위해 최초 소프트 데이터 값은 하나 이상의 고려되는 성능 인자에 기초하여 조정된다. 이를 강화된 소프트 데이터 값은 LLR 또는 신뢰도를 계산하는데 사용되는 (소프트 판독 전압과 같은) 소프트 판독 값을 나타내거나, LLR 또는 신뢰도를 나타낸다.

[0081] 일 예시적인 구현에서, 하나 이상의 소프트 판독 값이 플래시 메모리로부터 획득되고, LLR과 같은 소프트 정보가 소프트 판독 값에 기초하여 획득된다. 그 후, 소프트 소프트 정보(LLR 등)은 플래시 메모리의 하나 이상의 성능 인자에 기초하여 조정되어, 이후 여러 레이트 성능을 개선하기 위해 디코더로 전달되는 강화된 소프트 정보, 즉 강화된 소프트 데이터 값을 획득한다.

[0082] 다른 예시적인 구현에서, 하나 이상의 소프트 판독 값은 플래시 메모리로부터 획득된다. 대응하는 공칭 값은 그러면 소프트 판독 값에 기초하여 결정되고, 대응하는 오프셋 값은 하나 이상의 고려되는 성능 인자에 기초하여 획득된다. 그러면, LLR과 같은 희망 소프트 정보, 즉 소프트 데이터 값은 공칭 값 및 오프셋 값에 기초하여 획득된다.

#### 프로세스, 시스템 및 제품(article of manufacture)의 상세 사항

[0084] 여기의 다수의 플로우 차트가 단계의 예시적인 순서를 설명하는 한편, 순서가 변할 수 있다는 것 또한 본원발명의 실시예이다. 알고리즘의 다양한 치환(permuations)은 본 발명의 다른 실시예로서 고려된다. 당업자가 자명하게 알 수 있듯이, 본원 발명의 예시적 실시예가 소프트웨어 프로그램 내 프로세싱 단계와 관련하여 설명되었지만, 다양한 기능이 소프트웨어 프로그램 내 프로세싱 단계로서의 디지털 도메인 내에서, 회로 구성요소에 의한 하드웨어 내에서, 또는 스테이트 머신 또는 하드웨어와 소프트웨어 모두의 조합으로 구현될 수도 있다. 이러한 소프트웨어는, 예를 들어, 디시탈 신호 프로세서, 애플리케이션 특정 집적 회로, 마이크로 컨트롤러 또는 범용(general-purpose) 컴퓨터에서 사용될 수도 있다. 이러한 하드웨어와 소프트웨어는 집적 회로 내에 구현된 회로 내에서 구현될 수도 있다.

[0085] 그래서, 본원 발명의 기능은 이러한 방법의 실행을 위한 방법과 장치의 형태로 구현될 수 있다. 본원 발명의 하나 이상의 측면은, 예를 들어, 저장 매체에 저장되거나, 머신에 로딩되거나/되고 머신에 의해 실행되거나, 어떠한 전송 매체를 넘어 전송되는 프로그램 코드의 형태로 구현되고, 이 프로그램 코드가 컴퓨터와 같은 머신에 로딩되고 이에 의해 실행되는 경우, 그 머신은 본 발명을 실행하는 장치가 된다. 범용 프로세서에 구현된 경우, 프로그램 코드 세그먼트는 프로세서와 결합되어 특정 논리 회로와 유사하게 동작하는 장치를 제공한다. 본 발명은 또한 하나 이상의 집적 회로, 디지탈 신호 프로세서, 마이크로프로세서와 마이크로 컨트롤러의 형태로 구현될 수 있다.

[0086] 해당 분야에 알려진 바와 같이, 여기에 논의된 방법과 장치는 그 위에서 구현되는 컴퓨터 판독 가능한 코드 수단을 가지는 컴퓨터 판독 가능한 매체를 그 자체가 포함하는 제조 물품으로서 배포될 수도 있다. 컴퓨터 판독 가능한 프로그램 코드 수단은 컴퓨터 시스템과 결합하여 동작 가능하여 여기에 논의된 방법을 수행하거나 장치를 제조하기 위하여 모든 또는 일부의 단계를 수행할 수 있다. 컴퓨터 판독 가능한 매체는 기록 가능한 매체(예를 들어, 플로피 디스크, 하드 드라이브, 컴팩트 디스크, 메모리 카드, 반도체 장치, 칩, ASIC)일 수도 있고, 송신 매체(예를 들어, 광섬유, 월드와이드 웹, 케이블 또는 시간 분할 다중 접속, 코드 분할 다중 접속

또는 다른 무선 주파수 채널을 이용하는 무선 채널을 포함하는 네트워크)일 수도 있다. 컴퓨터 시스템으로 사용하는 데에 적절한 정보를 저장할 수 있는 공지되거나 개발된 임의의 매체가 사용될 수도 있다. 컴퓨터 판독 가능한 코드 수단은 컴퓨터가, 컴팩트 디스크의 표면 상의 높이 변화 또는 자기 매체의 자성 변화와 같은, 인스트리션과 데이터를 읽을 수 있게 하는 임의의 메카니즘이다.

[0087] 여기에 설명된 컴퓨터 시스템과 서버는 각각 관련 프로세서를 구성하여 여기에 개시된 방법, 단계와, 기능을 구현할 메모리를 각각 포함한다. 메모리는 분산되어 있거나 로컬일 수 있고, 프로세스는 분산되어 있거나 하나(singular)일 수 있다. 메모리는, 전기적, 자기적 또는 광학적 메모리로서 또는 이를 또는 다른 타입의 저장장치의 임의의 조합으로서 구현될 수 있다. 또한, "메모리"라는 용어는 관련 프로세서에 의해 접속되는 어드레스 가능한 공간 내 어드레스로부터 또는 어드레스로 판독되거나 기록될 수 있는 임의의 정보를 포함하기에 충분하도록 넓게 해석되어야 한다. 이러한 정의로, 네트워크 상 정보도 관련 프로세서가 네트워크로부터 정보를 검색할 수 있기 때문에 메모리 내에 있다.

[0088] 여기에 도시되고 설명된 실시예와 변형예는 단순히 본 발명의 원리를 설명하는 것이고 다양한 변형을 본 발명의 범위와 정신을 벗어나지 않고 당업자에 의해 구현할 수도 있다는 것을 알 수 있을 것이다.

## 도면

### 도면1

### 도면2

## 도면3

## 도면4

## 도면5a

## 도면5b

도면6

도면7

## 도면8

## 도면9

## 도면10

**도면11****도면12**

**도면13**

하드 디아이터-소프트 디아이터 평 데이터베이스(1300)

| 1310 | P/E 사이클 | 0 | 1000 | 5000 | 10000 | 0  | 1000 | 5000 | 10000 |

|------|---------|---|------|------|-------|----|------|------|-------|

| 1320 | LSB     | 2 | 1.5  | 1    | 0     | -2 | -1.5 | -1   | 0     |

| 1330 | MSB     | 2 | 1.8  | 1.5  | 0.3   | -2 | -1.8 | -1.5 | -0.3  |

| 1340 |         |   |      |      |       |    |      |      |       |