(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2025-9752

(P2025-9752A)

(43)公開日 令和7年1月20日(2025.1.20)

(51)国際特許分類

H 0 3 B 28/00 (2006.01)

F I

H 0 3 B

28/00

A

審査請求 未請求 請求項の数 6 O L (全10頁)

(21)出願番号 特願2024-8972(P2024-8972)

(22)出願日 令和6年1月24日(2024.1.24)

(31)優先権主張番号 特願2023-107605(P2023-107605)

(32)優先日 令和5年6月29日(2023.6.29)

(33)優先権主張国・地域又は機関

日本国(JP)

(71)出願人 300045710

安田 博

大阪府枚方市禁野本町 2 丁目 7 - 4 0

(72)発明者 安田 博

大阪府枚方市禁野本町 2 丁目 7 - 4 0

(54)【発明の名称】 ダイレクト・デジタル・シンセサイザ

## (57)【要約】

【課題】従来のダイレクト・デジタル・シンセサイザは2のべき乗のクロックが必要であったり、そうでない場合は周波数がきっちりとしていなかった。また小数点以下の桁数を多くするのは難しかった。

【解決手段】アキュムレータ出力と周波数設定データと加算する加算器に加えて、加算器出力が所定値を超えた場合には所定値を引くことによって2のべき乗のクロックでなくてもよいようにした。また、周波数設定データを所定値で割った商と剰余をそれぞれ上位桁と下位桁に設定することによって周波数設定範囲を広くした。また、小数点以下のアキュムレータを別途設けることによって小数点以下の設定も容易にできるようにした。

【選択図】図4

**【特許請求の範囲】**

**【請求項 1】**

クロック信号によって作動する第1のアキュムレータと、(前記第1のアキュムレータの出力値) + (第1の周波数設定データ)を演算する第1の演算器と、(前記第1のアキュムレータの出力値) + (第1の周波数設定データ) - (所定値)を演算した結果を得る第2の演算器と、前記第2の演算器の出力に応じて前記第1の演算器の出力か前記第2の演算器の出力かを選択する第1のセレクターを具え、前記第1のアキュムレータの入力は前記第1のセレクターの出力であることを特徴とするダイレクト・デジタル・シンセサイザ。

**【請求項 2】**

請求項1に記載のダイレクト・デジタル・シンセサイザにおいて、前記第1のセレクターが前記第2の演算器を選択したときに値を1つ増加させるインクリメンタを備えたことを特徴とするダイレクト・デジタル・シンセサイザ。

**【請求項 3】**

請求項1に記載のダイレクト・デジタル・シンセサイザにおいて、第2のアキュムレータと、(前記第2のアキュムレータ) + (第2の周波数設定データ)を演算する第3の演算器を具え、前記第1のセレクターが前記第2の演算器の出力を選択したときに前記第2のアキュムレータの前記第3の演算器の出力への更新を有効とすることを特徴とするダイレクト・デジタル・シンセサイザ。

**【請求項 4】**

請求項1に記載のダイレクト・デジタル・シンセサイザにおいて、クロック信号によって作動する第3のアキュムレータと、(前記第3のアキュムレータの出力値) + (第3の周波数設定データ)を演算する第4の演算器と、(前記第3のアキュムレータの出力値) + (第3の周波数設定データ) - (第2の所定値)を演算した結果を得る第5の演算器と、前記第5の演算器の出力に応じて前記第4の演算器の出力か前記第5の演算器の出力を選択する第2のセレクターを具え、前記第3のアキュムレータの入力は前記第2のセレクターの出力であり、前記第1のアキュムレータは前記第2のセレクターが前記第5の演算器を選択したときに更新を有効とすることを特徴とするダイレクト・デジタル・シンセサイザ。

**【請求項 5】**

請求項1に記載のダイレクト・デジタル・シンセサイザにおいて、前記所定値は前記クロック信号の周波数を設定単位周波数で割った値の2のべき乗分の1の値(べき数は0を含む)であることを特徴とするダイレクト・デジタル・シンセサイザ。

**【請求項 6】**

請求項3および4に記載のダイレクト・デジタル・シンセサイザにおいて、前記クロック信号の周波数を設定単位周波数で割った値を前記所定値で割った商を前記第2の周波数設定データとし、剩余を前記第1の周波数設定データとしたことを特徴とするダイレクト・デジタル・シンセサイザ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、設定した周波数を精度よく得ることができるダイレクトデジタルシンセサイザ(Direct Digital Synthesizer:以下「DDS」と略称する)に関するものである。

**【背景技術】**

**【0002】**

基準となるクロックから任意の周波数を得られるDDSはいろいろな分野で広く使われている。従来のDDSは入手が容易な水晶発振器を基準クロックとして用いた場合、きっちりした周波数を得られないという問題点があり、そのため精度が悪いという問題点があった。そのため高分解能のDDSを用いてできるだけ目標周波数に近い周波数を設定して

10

20

30

40

50

使用しているのが現状である。

### 【0003】

一部では基準となるクロックに2のべき乗の周波数の水晶発振器を使用してきっちりした周波数を得ているものもあるが、特注の水晶発振器を必要としたり設定できる周波数範囲に制限があつたりしている。

### 【先行技術文献】

#### 【特許文献】

#### 【0004】

【特許文献1】特開平9-83250号公報

#### 【非特許文献】

#### 【0005】

【非特許文献1】ANALOG DEVICES AD9833 Datasheet

発行日不明

### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

解決しようとする問題点は、入手が容易な水晶発振器を基準クロックとして用いた場合、きっちりとした精度の高い周波数を発生させることができない点である。例えば、従来のDDSであるAD9833は28ビットのアキュムレータを有し、クロックに25MHzを使うと分解能は、 $25000000 / 2^{28} = 0.093$ となり、0.093Hzの高分解能が得られるがきっちりと0.1Hzにはならない。分解能をきっちり0.1Hzにするためには、 $0.1 \times 2^{28} = 26843545.6$ となるため26.8435456Hzのクロックが必要になり、あまり市販されておらず少量生産の場合入手困難でもある。

#### 【0007】

本発明では入手が容易な水晶発振器を基準クロックとして用いてもきっちりとした正確な周波数を発生させることができるDDSを提供することを目的とするものである。

#### 【0008】

また小数点以下の端数を含む周波数も容易に発生させることができるDDSを提供することを目的とするものである。

#### 【課題を解決するための手段】

#### 【0009】

本発明は、クロック周波数/設定周波数単位を2のべき乗で割った値を所定値として、アキュムレータの更新値が所定値を超えたときに、その値を引いた値でアキュムレータの値を更新することによって目標の周波数設定を容易にしてかつ正確にするものである。(べき数は0を含む。)

#### 【0010】

また、その値を引いた値を選択した場合に上位のアキュムレータの更新を許可することによって、目標の周波数設定データを、クロック周波数/設定周波数単位を2のべき乗で割った値で割った商と剩余をそれぞれ第2の周波数設定データおよび第1の周波数設定データとして上位桁と下位桁に設定をするように構成することによって高い周波数まで対応したものである。

#### 【0011】

また、目標周波数が小数点を持つ場合、下位のアキュムレータが小数点以下が例えば1桁の場合は10を、2桁の場合は100を、3桁の場合は1000を超えた場合にその値を引き、上位のアキュムレータの更新を許可することによって小数点以下の周波数を容易に設定できるようにした。

### 【発明の効果】

#### 【0012】

本発明のDDSは、目標の周波数設定が容易にでき、かつ周波数がきっちりしたもので

10

20

30

40

50

あり、また小数点以下の設定も容易にできるという利点がある。そのため基準となるクロックの精度と同じ精度の周波数を得られるという利点がある。

## 【図面の簡単な説明】

【 0 0 1 3 】

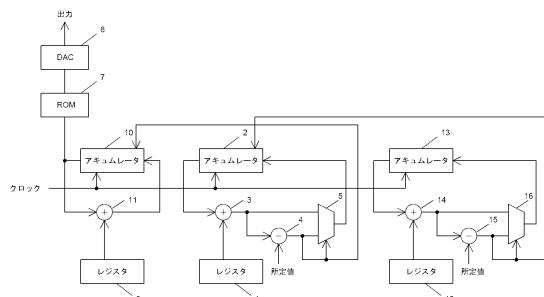

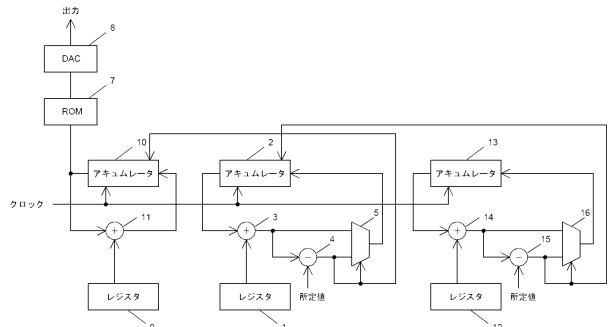

【図1】図1は本発明のDDSの第1の実施例を示すブロック図である。(実施例1)

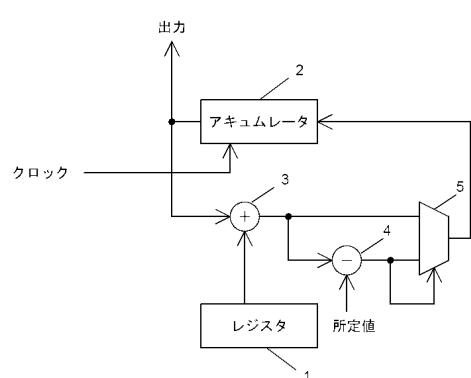

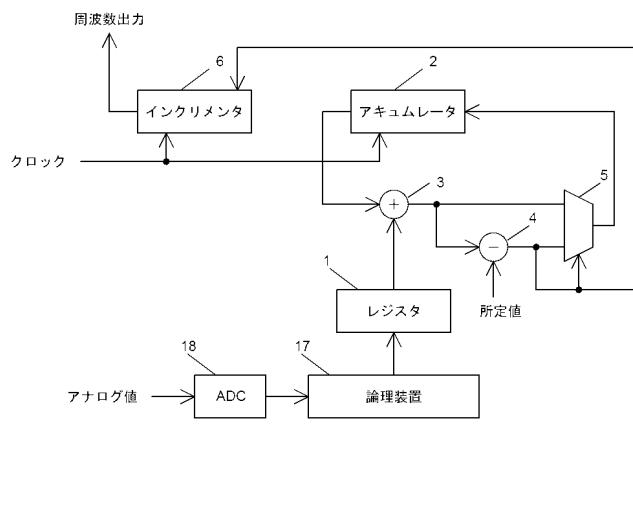

【図2】図2は本発明のDDSの第2の実施例を示すブロック図である。(実施例2)

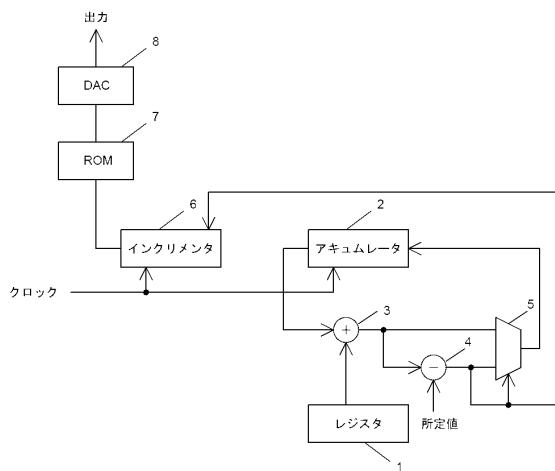

【図3】図3は本発明のDDSの第3の実施例を示すブロック図である。(実施例3)

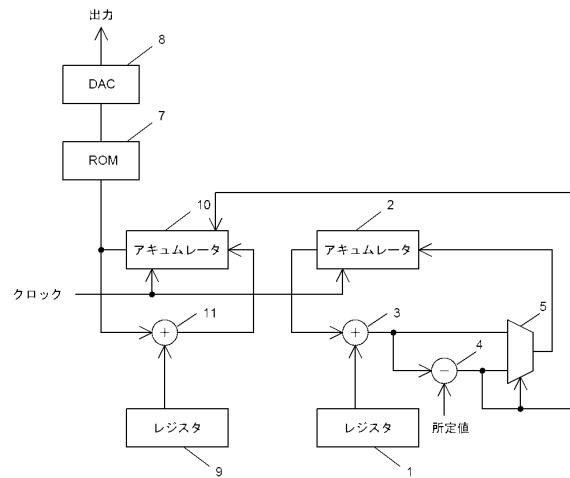

【図4】図4は本発明のDDSの第4の実施例を示すブロック図である。(実施例4)

【図5】図5は本発明のDDSの第5の実施例を示すブロック図である。(実施例5)

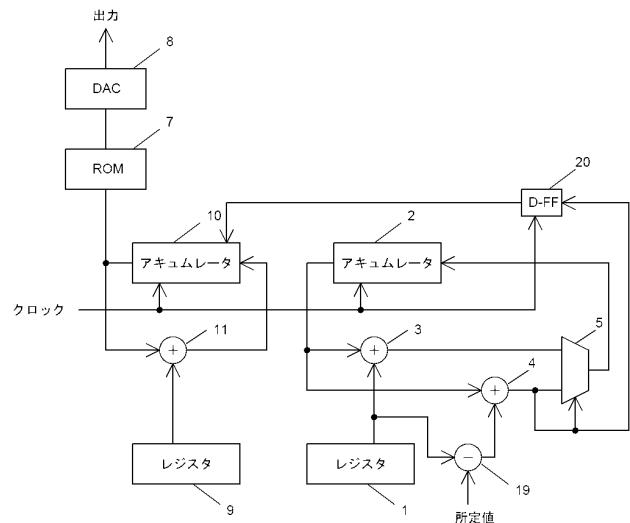

【図6】図6は本発明のDDSの第6の実施例を示すブロック図である。(実施例6)

## 【発明を実施するための形態】

[ 0 0 1 4 ]

目標の周波

ラジオ周波数範囲を省くこと、また水晶発振子の取扱いを省くことにより、ラジオ回路に特殊な周波数の水晶発振子も不要とし一般的に入手容易な水晶発振子で構成できるようにするという目的を実現した。

【美施阴】

【0015】

卷一

図1は、本発明装置の実施例1のプロック図であって、レジスタ1には周波数設定データが設定されており、アキュムレータ2の出力値とレジスタ1の設定値を第1の演算器3で加算する。第2の演算器4で第1の演算器3の出力値から所定値を減算し、セレクタ5には第1の演算器3の出力と第2の演算器4の出力が入力され、第2の演算器4の出力が負の値の場合は第1の演算器3の出力が、そうでない場合には第2の演算器4の出力が選択されてセレクタ5から出力される。セレクタ5の出力はアキュムレータ2に入力され、アキュムレータはクロックに同期してセレクタ5の出力値に値が更新される。

【 0 0 1 6 】

このように構成すると、アキュムレータ2の最上位ビットからはレジスタ1で設定された周波数設定データに基づく周波数のパルスが出力される。

ここで周波数設定データは出力周波数 / 設定単位周波数の計算で求められたデータであり、出力周波数は周波数設定データ × 設定単位周波数である。

【 0 0 1 7 】

例えばクロックを16MHz、所定値を160000000とすると、アキュムレータ2はクロック毎にレジスタ1に設定された値の増分で増加し、160000000を超えた場合には160000000を引いた値に戻る。それによってレジスタ1の設定値×1Hzの周波数がアキュムレータ2の最上位ビットから出力され、設定単位周波数は1Hzとなる。このときアキュムレータは0～159999999の値になるのでビット数は24ビットあればよい。レジスタ1のビット数も同様である。周波数の設定範囲は1～159999999Hzである。

[ 0 0 1 8 ]

クロックを 16 MHz、所定値を 1600000000 とすると、レジスタ 1 の設定値 × 0.1 Hz の周波数がアキュムレータ 2 の最上位ビットから出力され、設定単位周波数は 0.1 Hz となる。このときアキュムレータは 0 ~ 159999999 の値になるのでビット数は 28 ビット必要である。レジスタ 1 のビット数も同様である。周波数の設定範囲は 0.1 ~ 15999999.9 Hz である。

[ 0 0 1 9 ]

ここで言うレジスタとはマイコンなどの論理装置（図示せず）から値を設定して保持するものか、マイコンの出力ポートレジスタを指す。レジスタ1では論理装置から周波数設定データを設定して、その値を加算器3に供給している。アキュムレータとは累積加算を目的としたレジスタで、イネーブル信号によってクロックに同期して値が加算結果と置き換える。実施例1では常にイネーブル状態になっており、クロック毎に値が更新される。

**【実施例 2】****【0020】**

図 2 は、本発明装置の実施例 2 のブロック図であり、実施例 1 に対してインクリメンタ 6、ROM 7、DAC (デジタル／アナログ変換器) 8 を追加して正弦波などのアナログ波形を出力できるようにしたものである。またレジスタ 1、アキュムレータ 2、第 1 の演算器 3、第 2 の演算器 4、セレクタ 5 は実施例 1 と同じ動作をする。

**【0021】**

クロックが 16 MHz、設定周波数単位 = 1 Hz の場合、 $16000000 / 1 = 2^10 \times 15625$  であるので、インクリメンタ 6 を 10 ビット、所定値を 15625 とし、第 4 の演算器の出力値が正または 0 の値になったときにインクリメンタ 6 の値を 1 つ増加させるようにインクリメンタ 6 をイネーブルする。インクリメンタ 6 は 10 ビットの範囲で増加し、オーバーフローすると 0 に戻る。その単調増加する出力を正弦波などに変換するための ROM 7 に入力し、正弦波に変換した値を DAC 8 に入力するとその出力からは正弦波が出力される。周波数の設定範囲は 1 ~ 15625 Hz である。

**【0022】**

クロックが 16 MHz、設定周波数単位 = 10 Hz の場合、 $16000000 / 10 = 2^9 \times 3125$  であるので、インクリメンタ 6 を 9 ビット、所定値を 3125 とし、第 4 の演算器の出力値が正または 0 の値になったときにインクリメンタ 6 の値を 1 つ増加させないようにインクリメンタ 6 をイネーブルする。インクリメンタ 6 は 9 ビットの範囲で増加し、オーバーフローすると 0 に戻る。その単調増加する出力を正弦波などに変換するための ROM 7 に入力し、正弦波に変換した値を DAC 8 に入力するとその出力からは正弦波が出力される。周波数の設定範囲は 10 ~ 31250 Hz である。

**【0023】**

ここで、もし ROM 7 への出力を 12 ビットにしたい場合は、設定周波数単位を 1 / 4 Hz にすれば、 $16000000 / (1 / 4) = 2^{12} \times 15625$  となり、インクリメンタ 6 は 12 ビットとなるため、ROM 7 への出力は 12 ビットにできる。ここでの所定値は 15625 である。

**【0024】**

このように設定周波数単位を 2 のべき乗分の 1 にすることによってべき乗値に応じて ROM 7 への出力ビット数を増やすことができる。

**【0025】**

もちろん変換する波形は正弦波である必要はなく、ROM 7 のデータによって三角波や矩形波やその他任意の波形が出力できる。

**【0026】**

インクリメンタとはイネーブル信号が入力されたときにクロックに同期して値が 1 つ増加するものを指す。(アキュムレータの一種であるが、増加値が 1 であることからインクリメンタと称した。)

**【実施例 3】****【0027】**

図 3 は、本発明装置の実施例 3 のブロック図であり、実施例 2 では設定周波数単位 = 1 Hz の場合 15625 Hz までという低い周波数しか設定できなかつたので、高い周波数まで設定できるように改良したものである。インクリメンタ 6 の代わりにレジスタ 9、第 2 のアキュムレータ 10、第 3 の演算器 11 を設け、第 2 のレジスタ 9 には周波数設定の上位データが設定されており、第 2 のアキュムレータ 10 の出力値と第 2 のレジスタ 9 の設定値を第 3 の演算器 11 で加算する。第 3 の演算器 11 の出力は第 2 のアキュムレータ 10 に入力され、第 2 の演算器 4 の出力値が正または 0 の値になったときにアキュムレータ 2 の繰り上がりとしてクロックに同期して第 2 のアキュムレータ 10 の値が第 3 の演算器 11 の出力値に更新されるようにイネーブルする。またレジスタ 1、アキュムレータ 2、第 1 の演算器 3、第 2 の演算器 4、セレクタ 5、ROM 7、DAC 8 は実施例 2 と同じ動作をする。

10

20

30

40

50

**【 0 0 2 8 】**

ここでクロックが 16 MHz、設定周波数単位 = 1 Hz の場合、周波数設定データを 15625 で割った商と剰余を求め、第 2 のレジスタ 9 には第 2 の周波数データとして商を、レジスタ 1 には第 1 の周波数データとして剰余を設定し、第 2 の演算器 4 に入力される所定値は 15625 とする。そうすることによって、周波数の設定範囲の最大値は  $1023 \times 15625 + 15624 = 159999999$  Hz となり、1 ~ 159999999 Hz の周波数が生成できる。ここで 15625 とは 16 MHz である 16000000 を 2 のべき乗である  $2^{10}$  で割った値である。

**【 0 0 2 9 】**

アキュムレータ 10 は  $2^{10}$  で 1 周するので、10 ビットアドレスの ROM 7 を介して DAC 8 出力可能だが、アキュムレータ 2 は 2 のべき乗で 1 周しないので ROM を介して DAC 出力をすると波形が不連続となり目標となる波形を出力することができない。そのため、もっと多ビットで出力したい場合は実施例 2 で説明したように設定周波数単位を 2 のべき乗分の 1 にすればべき乗の値に応じて出力ビット数を増やすことができる。

**【 実施例 4 】****【 0 0 3 0 】**

図 4 は、本発明装置の実施例 4 のブロック図であり、実施例 3 では設定周波数単位 = 1 Hz の場合、1 Hz 単位の設定しかできなかったものを、第 3 のレジスタ 12、第 3 のアキュムレータ 13、第 4 の演算器 14、第 5 の演算器 15、第 2 のセレクタ 16 の追加により小数点以下の周波数を設定できるようにしたものである。またレジスタ 1、アキュムレータ 2、第 1 の演算器 3、第 2 の演算器 4、セレクタ 5、ROM 7、DAC 8、第 2 のレジスタ 9、第 2 のアキュムレータ 10、第 3 の演算器 11 は実施例 3 と同じ動作をする。

**【 0 0 3 1 】**

ここでは小数点以下 3 桁が設定できるようにしたものを説明する。小数点以下 3 桁のデータが第 3 のレジスタ 12 に設定され、第 3 のアキュムレータ 13 の出力値と第 4 の演算器 14 で加算され、その出力は第 5 の演算器 15 で所定値が引かれる。ここで所定値は 1000 である。つまり第 4 の演算器 14 の出力が 1000 未満の場合には第 2 のセレクタ 16 によって第 4 の演算器 14 の出力が選択され、1000 以上の場合には 1000 を引いた第 5 の演算器 15 の出力が選択され、クロックに同期して第 3 のアキュムレータ 13 が選択された値と置き換わる。この場合第 3 のアキュムレータ 13 は 0 から 999 までの値になり得るので 10 ビットを必要とする。

**【 0 0 3 2 】**

第 5 の演算器 15 の出力が選択された信号はアキュムレータ 2 のイネーブル端子に入力され、アキュムレータ 2 の値が更新される。

**【 0 0 3 3 】**

このように構成された DDS では、第 2 のレジスタ 9 に実施例 3 で述べた商を、レジスタ 1 には剰余を、小数点以下の周波数値を第 3 のレジスタ 12 に設定することにより、0.001 ~ 1599999.999 Hz までが生成可能となる。

**【 0 0 3 4 】**

ここで所定値は、設定が小数点以下 1 桁であれば 10、2 桁であれば 100 であって構成は同様である。また更に桁が増えたとしても所定値と第 3 のアキュムレータ 13 に必要なビット数が変わるだけで構成は同様である。第 3 のアキュムレータ 13 に必要なビット数は、所定値が 10 の場合は 4 ビット、100 の場合は 7 ビットである。

**【 実施例 5 】****【 0 0 3 5 】**

図 5 は、本発明装置の実施例 5 のブロック図であり、アナログ値に比例した周波数を出力する V - F コンバータを本発明の DDS で構成した例であり、アナログ値が 1 V のとき 25 kHz を出力し、アナログ値に比例した周波数を出力する V - F コンバータ（電圧 - 周波数変換器）の例で説明する。

10

20

30

40

50

## 【0036】

18はアナログ値をデジタル値に変換するA D C（アナログ／デジタル変換器）、17はマイコンなどの論理装置であり、レジスタ1、アキュムレータ2、第1の演算器3、第2の演算器4、セレクタ5、インクリメンタ6は実施例2と同じ動作をする。

## 【0037】

アナログ値である電圧はA D C 18でデジタル値に変換され論理装置17に取り込まれる。このA D Cは10ビットで、基準電圧は1.023Vとすると、電圧1Vのときデジタル値は1000になり、0.001Vのときデジタル値は1になる。そしてデジタル値が1000のとき25kHzで、デジタル値が1のときは25Hzが出力されるべき周波数である。

10

## 【0038】

クロックを16MHz、設定単位周波数を25Hzとすると、 $16000000 / 25 = 2^9 \times 1250$ となるので、インクリメンタ6は9ビット、所定値を1250と設定すると、デジタル値が1000のときは25kHz、1のときは25Hzとデジタル値に比例した周波数が出力され、デジタル値はアナログ値に比例するので、アナログ値に比例した周波数が出力される。

## 【実施例6】

## 【0039】

図6は、本発明の実施例6のブロック図であり、今までの実施例では、第2の演算器は第1の演算器から所定値を引くものであったので、1クロックの時間内で2つの演算器を通す演算が必要で、あまりクロック周波数が高くできない問題があり、本実施例はそれを解決し、実施例3を高速化したものである。

20

## 【0040】

レジスタ1、アキュムレータ2、第1の演算器3、セレクタ5、R O M 7、D A C 8、第2のレジスタ9、第2のアキュムレータ10、第3の演算器11は実施例3と同じ動作をするが、第2の演算器4は実施例3と異なり減算器19を追加した加算器となっている。また高速化のためにパイプラインとしてD - F F (Dフリップフロップ)20を追加している。

## 【0041】

第1のレジスタ1に設定する周波数設定の下位データはアキュムレータ2の出力値と第1の演算器3で加算するとともに、減算器19で所定値を減算した値をアキュムレータ2の出力値と第2の演算器4で加算する。セレクタ5には第1の演算器3の出力と第2の演算器4の出力が入力され、第2の演算器4の出力が負の値の場合は第1の演算器3の出力が、そうでない場合には第2の演算器4の出力が選択されてセレクタ5から出力される。セレクタ5の出力はアキュムレータ2に入力され、アキュムレータはクロックに同期してセレクタ5の出力値に値が更新される。また第2の演算器4の出力が負の場合はD - F F 20がセットされる。

30

## 【0042】

第3の演算器11の出力は第2のアキュムレータ10に入力され、D - F F 20がセットされているときにアキュムレータ2の繰り上がりとしてクロックに同期して第2のアキュムレータ10の値が第3の演算器11の出力値に更新されるようにイネーブルする。

40

## 【0043】

このように構成すると実施例3では第1の演算器3と第2の演算器4の遅れが加算されたが、本実施例では加算されることがないので高速になる。減算器19に関しては入力値は毎クロックごとに変化するのではないので気にする必要はない。ここで第2のレジスタ9と第1のレジスタ1はマイコンなどの論理装置から設定して保持するレジスタかまたはマイコン出力ポートレジスタであり、減算器19はマイコン内で減算計算して減算結果を出力ポートレジスタに出力してもよい。

## 【0044】

またセレクタ5の選択までの遅れ時間はD - F F 20をパイプラインとして用いること

50

によってアキュムレータ 10 の演算遅れと累積することができないため高速になる。

#### 【0045】

実施例 4 における第 5 の演算器 15 の場合や、第 5 の演算器 15 の出力からアキュムレータ 2 への信号線も同様に構成することによって高速化することができる。

#### 【0046】

今までの説明ではクロックの生成には水晶発振器を用いてきたが、もっと入手し易い周波数の水晶発振器の出力を PLL に入力して必要な周波数のクロックを得てもよい。DDS を FPGA で構成する場合、FPGA は通常クロック生成用の PLL を持っていて、例えば水晶発振器に 10 MHz のものを使用して PLL で 64 週倍して 640 MHz を得て、それを 40 分周して 16 MHz のクロックを得ることができる。DDS の発生周波数をもっと高くしたい場合には 20 分周して 32 MHz や 10 分周して 64 MHz のクロックを作ることができる。

10

#### 【産業上の利用可能性】

#### 【0047】

DDS は無線機器やファンクションジェネレータと呼ばれる周波数発生器に広く使用されている。その発生周波数が容易に発生でき精度が高いものは非常に有用である。また小数点以下の桁数が増えたとしても容易に対応できるものである。その他にも周波数可変が要求される用途は多々あり本発明が適用できる。

#### 【符号の説明】

#### 【0048】

|    |                       |    |

|----|-----------------------|----|

| 1  | レジスタ（第 1 のレジスタ）       | 20 |

| 2  | アキュムレータ（第 1 のアキュムレータ） |    |

| 3  | 第 1 の演算器              |    |

| 4  | 第 2 の演算器              |    |

| 5  | セレクタ（第 1 のセレクタ）       |    |

| 6  | インクリメンタ               |    |

| 7  | R OM                  |    |

| 8  | D AC                  |    |

| 9  | 第 2 のレジスタ             |    |

| 10 | 第 2 のアキュムレータ          | 30 |

| 11 | 第 3 の演算器              |    |

| 12 | 第 3 のレジスタ             |    |

| 13 | 第 3 のアキュムレータ          |    |

| 14 | 第 4 の演算器              |    |

| 15 | 第 5 の演算器              |    |

| 16 | 第 2 のセレクタ             |    |

| 17 | 論理装置                  |    |

| 18 | A DC                  |    |

| 19 | 減算器                   |    |

| 20 | D - F F               | 40 |

【図面】

【図1】

【図2】

10

【図3】

【図4】

20

30

40

50

【図5】

【図6】

10

20

30

40

50