US 20160027810A1

(19) **United States**

(12) **Patent Application Publication**

Umezaki

(10) **Pub. No.: US 2016/0027810 A1**

(43) **Pub. Date: Jan. 28, 2016**

(54) **SEMICONDUCTOR DEVICE, DISPLAY MODULE, AND ELECTRONIC APPLIANCE**

(71) Applicant: **Semiconductor Energy Laboratory Co., Ltd.**, Kanagawa-ken (JP)

(72) Inventor: **Atsushi Umezaki**, Isehara Kanagawa (JP)

(73) Assignee: **Semiconductor Energy Laboratory Co., Ltd.**, Kanagawa-ken (JP)

(21) Appl. No.: **14/804,772**

(22) Filed: **Jul. 21, 2015**

(30) **Foreign Application Priority Data**

Jul. 24, 2014 (JP) ..... 2014-150532

**Publication Classification**

(51) **Int. Cl.**

**H01L 27/12** (2006.01)

(52) **U.S. Cl.**

**CPC ..... H01L 27/1225 (2013.01); H01L 27/124 (2013.01)**

(57)

**ABSTRACT**

The circuit includes a first transistor; a second transistor whose first terminal is connected to a gate of the first transistor for setting the potential of the gate of the first transistor to a level at which the first transistor is turned on; a third transistor for setting the potential of a gate of the second transistor to a level at which the second transistor is turned on and bringing the gate of the second transistor into a floating state; and a fourth transistor for setting the potential of the gate of the second transistor to a level at which the second transistor is turned off. With such a configuration, a potential difference between the gate and a source of the second transistor can be kept at a level higher than the threshold voltage of the second transistor, so that operation speed can be improved.

FIG. 1

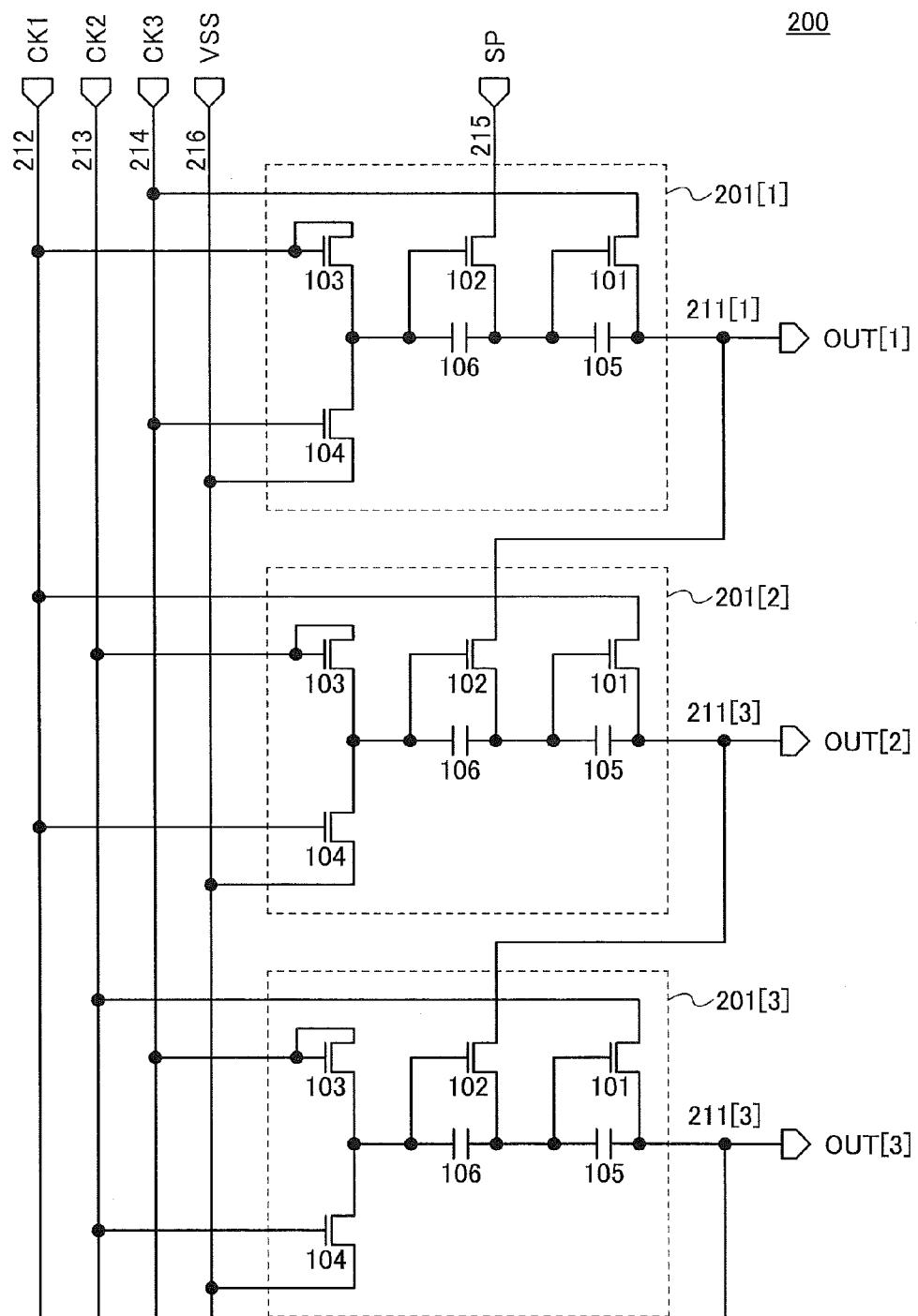

FIG. 2A

FIG. 2B

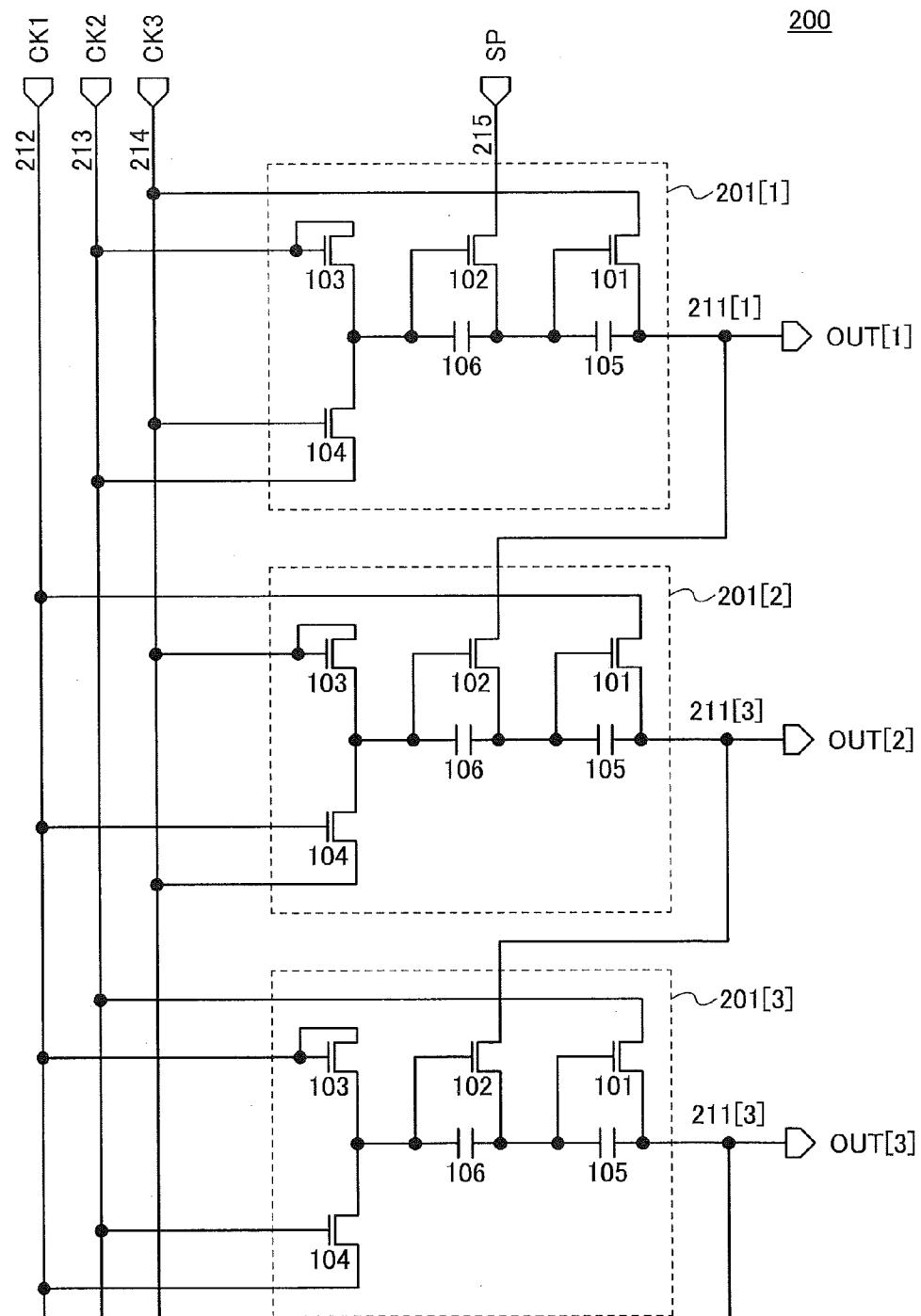

FIG. 3A

FIG. 3B

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7

FIG. 8A

FIG. 8B

FIG. 9A

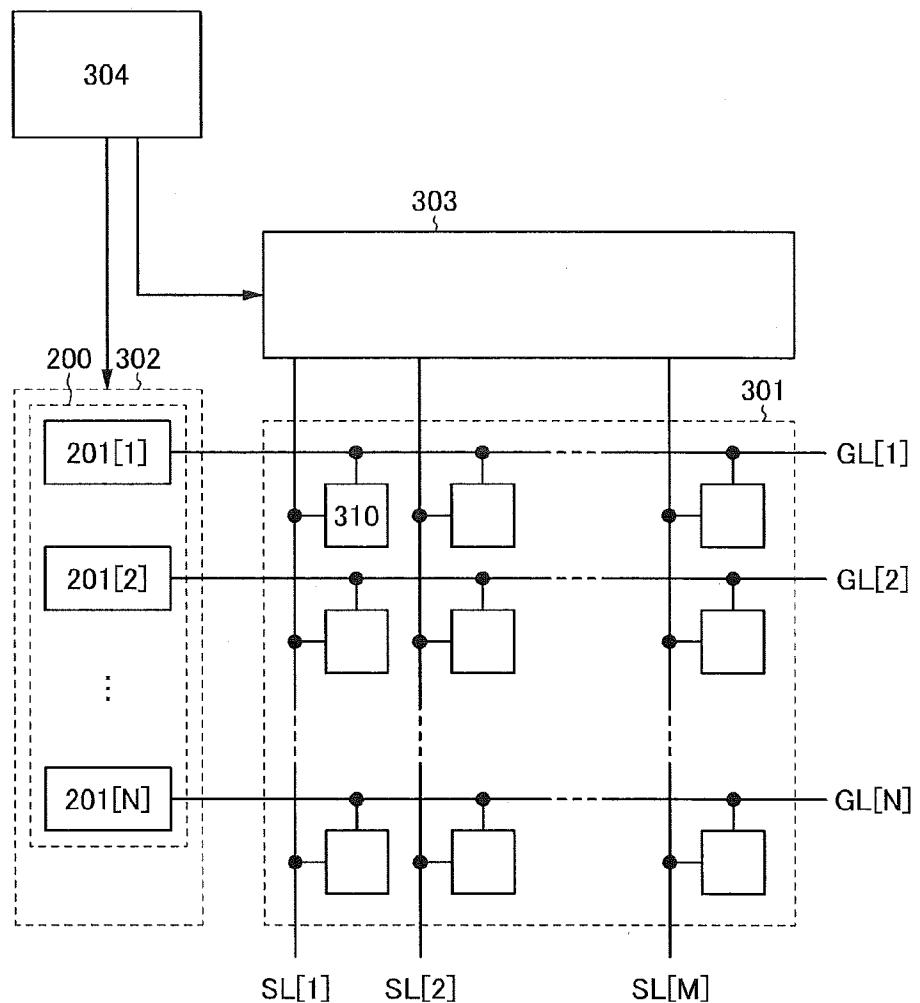

FIG. 9B

FIG. 10A

FIG. 10B

FIG. 11A

FIG. 11B

FIG. 12A

FIG. 12B

FIG. 13A

FIG. 13B

FIG. 14A

FIG. 14B

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

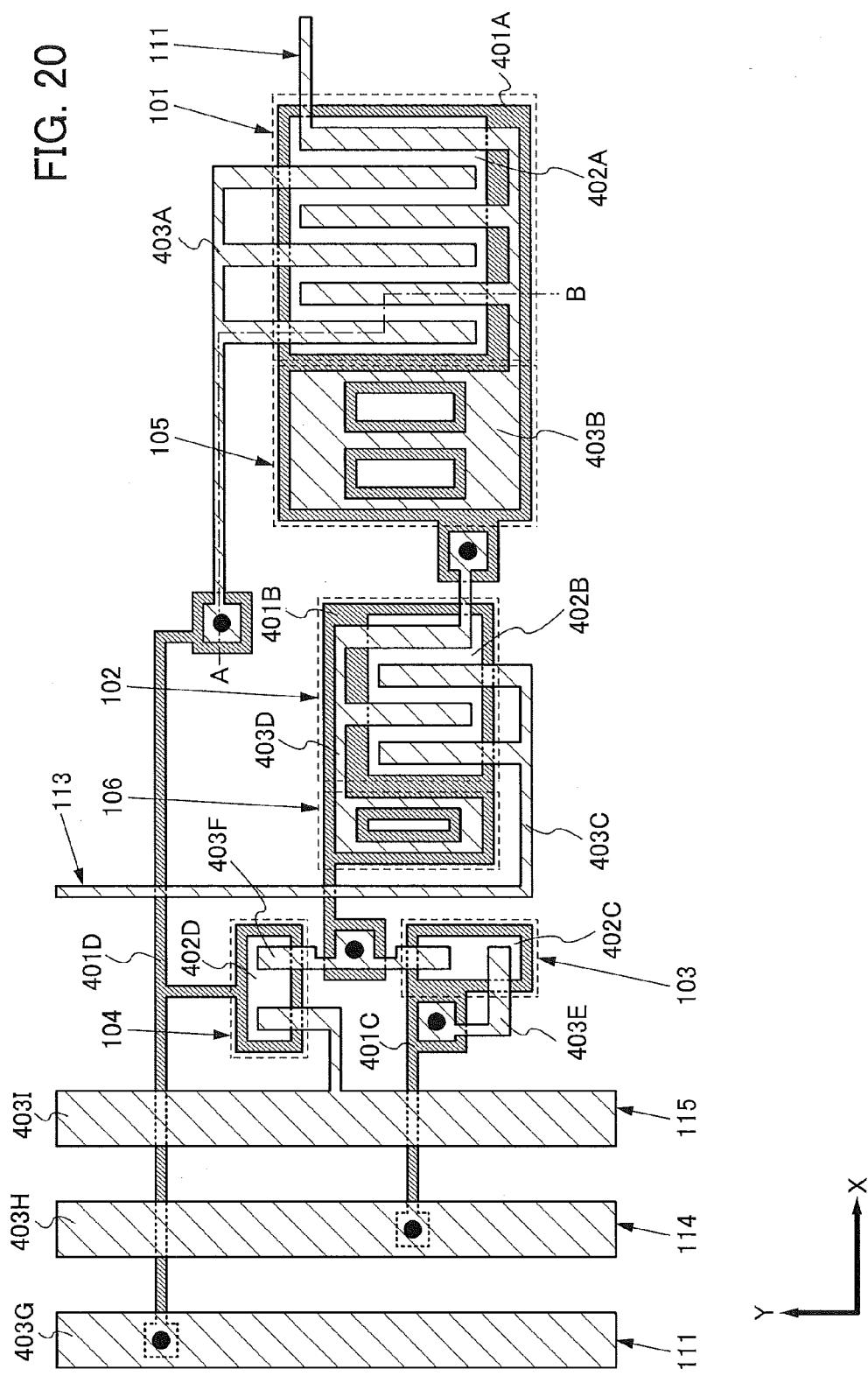

FIG. 20

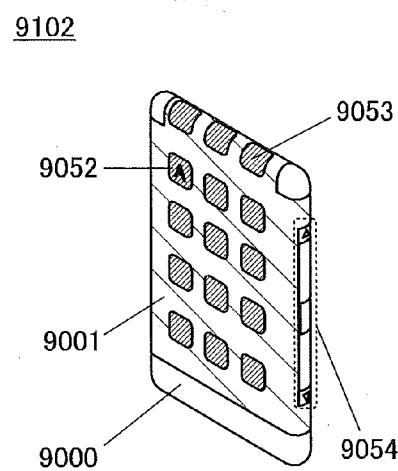

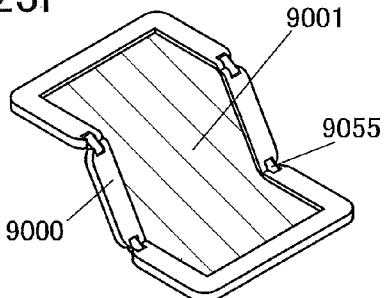

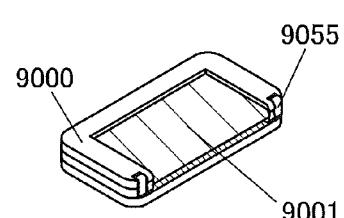

FIG. 23

FIG. 24

FIG. 25A

FIG. 25D

FIG. 25B

FIG. 25E

FIG. 25C

FIG. 25F

FIG. 25G

FIG. 26

## SEMICONDUCTOR DEVICE, DISPLAY MODULE, AND ELECTRONIC APPLIANCE

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] One embodiment of the present invention relates to a semiconductor device, a display module, and an electronic appliance.

[0003] Note that one embodiment of the present invention is not limited to the above technical field. The technical field of one embodiment of the invention disclosed in this specification and the like relates to an object, a method, or a manufacturing method. In addition, one embodiment of the present invention relates to a process, a machine, a manufacture, or a composition of matter. Another embodiment of the present invention relates to a semiconductor device, a display device, a light-emitting device, a power storage device, a memory device, or a driving method or manufacturing method thereof.

[0004] 2. Description of the Related Art

[0005] A circuit which can be applied to a driver circuit of a memory device, an image sensor, a display device, or the like has been developed. In particular, a circuit formed using transistors having the same polarity has been actively developed. A technique relating to such a circuit is disclosed in Patent Document 1.

[0006] In Patent Document 1, a potential difference between a gate and a source of a transistor is decreased gradually. When the potential difference between the gate and the source of the transistor is equal to or lower than the threshold voltage of the transistor, the transistor is turned off, and a node in a circuit is brought into a floating state.

### REFERENCE

#### Patent Document

[0007] [Patent Document 1] Japanese Published Patent Application No. 2005-050502

### SUMMARY OF THE INVENTION

[0008] In a conventional circuit, a potential difference between a gate and a source of a transistor is decreased gradually, and thus the drain current of the transistor is also decreased gradually. Therefore, the time required for change in a potential of a node in a circuit is long, and thus high-speed operation is difficult. Furthermore, W/L of the transistor needs to be increased, which makes it difficult to reduce a layout area. In addition, it is difficult to shorten the rise time and the fall time of a signal.

[0009] An object of one embodiment of the present invention is to provide a novel semiconductor device. Another object of one embodiment of the present invention is to provide high-speed operation or to provide a configuration which enables it. Another object of one embodiment of the present invention is to reduce a layout area or to provide a configuration which enables it. Another object of one embodiment of the present invention is to reduce a driving voltage or to provide a configuration which enables it. Another object of one embodiment of the present invention is to shorten the rise time and the fall time of a signal or to provide a configuration which enables it.

[0010] One embodiment of the present invention does not necessarily achieve all the objects listed above and only needs to achieve at least one of the objects. The description of the

above objects does not disturb the existence of other objects. Other objects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

[0011] One embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, a third transistor, and a fourth transistor. One of a source and a drain of the first transistor is electrically connected to a first wiring, the other of the source and the drain of the first transistor is electrically connected to a second wiring, one of a source and a drain of the second transistor is electrically connected to a third wiring, the other of the source and the drain of the second transistor is electrically connected to a gate of the first transistor, one of a source and a drain of the third transistor is electrically connected to a fourth wiring, the other of the source and the drain of the third transistor is electrically connected to a gate of the second transistor, one of a source and a drain of the fourth transistor is electrically connected to a fifth wiring, and the other of the source and the drain of the fourth transistor is electrically connected to the gate of the second transistor.

[0012] One embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, a third transistor, and a fourth transistor. One of a source and a drain of the first transistor is electrically connected to a first wiring, the other of the source and the drain of the first transistor is electrically connected to a second wiring, one of a source and a drain of the second transistor is electrically connected to a third wiring, the other of the source and the drain of the second transistor is electrically connected to a gate of the first transistor, one of a source and a drain of the third transistor is electrically connected to a fourth wiring, the other of the source and the drain of the third transistor is electrically connected to a gate of the second transistor, one of a source and a drain of the fourth transistor is electrically connected to a fifth wiring, and the other of the source and the drain of the fourth transistor is electrically connected to the gate of the second transistor.

[0013] One embodiment of the present invention is a semiconductor device including a first transistor, a second transistor, a third transistor, and a fourth transistor. One of a source and a drain of the first transistor is electrically connected to a first wiring, the other of the source and the drain of the first transistor is electrically connected to a second wiring, one of a source and a drain of the second transistor is electrically connected to a third wiring, the other of the source and the drain of the second transistor is electrically connected to a gate of the first transistor, one of a source and a drain of the third transistor is electrically connected to a fourth wiring, the other of the source and the drain of the third transistor is electrically connected to a gate of the second transistor, one of a source and a drain of the fourth transistor is electrically connected to a fifth wiring, and the other of the source and the drain of the fourth transistor is electrically connected to the gate of the second transistor.

[0014] Note that in one embodiment of the present invention, a gate of the fourth transistor may be connected to the first wiring or the second wiring.

[0015] One embodiment of the present invention is a display module including the above semiconductor device and an FPC.

[0016] Another embodiment of the present invention is an electronic appliance including the above display module, and, an antenna, an operation button, or a speaker.

[0017] One embodiment of the present invention can provide a novel semiconductor device. One embodiment of the present invention can provide high-speed operation or a configuration which enables it. One embodiment of the present invention can reduce a layout area or provide a configuration which enables it. One embodiment of the present invention can reduce a driving voltage or provide a configuration which enables it. One embodiment of the present invention can shorten the rise time and the fall time of a signal or provide a configuration which enables it.

[0018] Note that the description of these effects does not disturb the existence of other effects. One embodiment of the present invention does not necessarily achieve all the effects listed above. Other effects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

#### BRIEF DESCRIPTION OF THE DRAWINGS

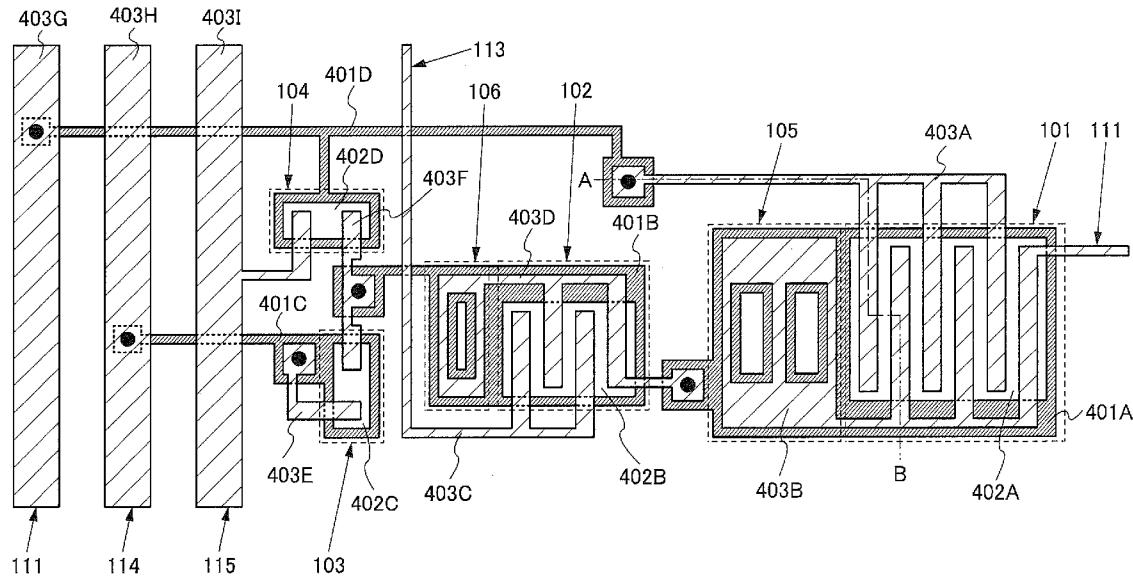

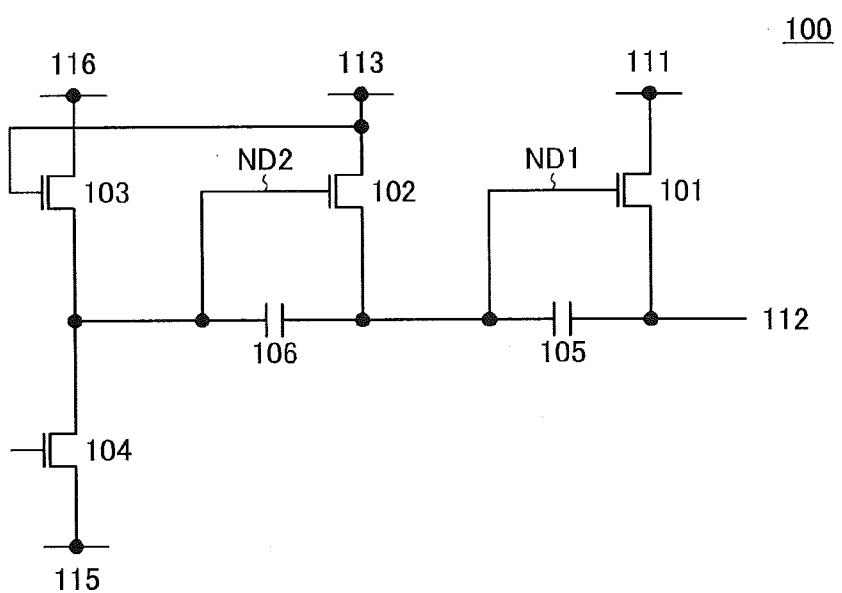

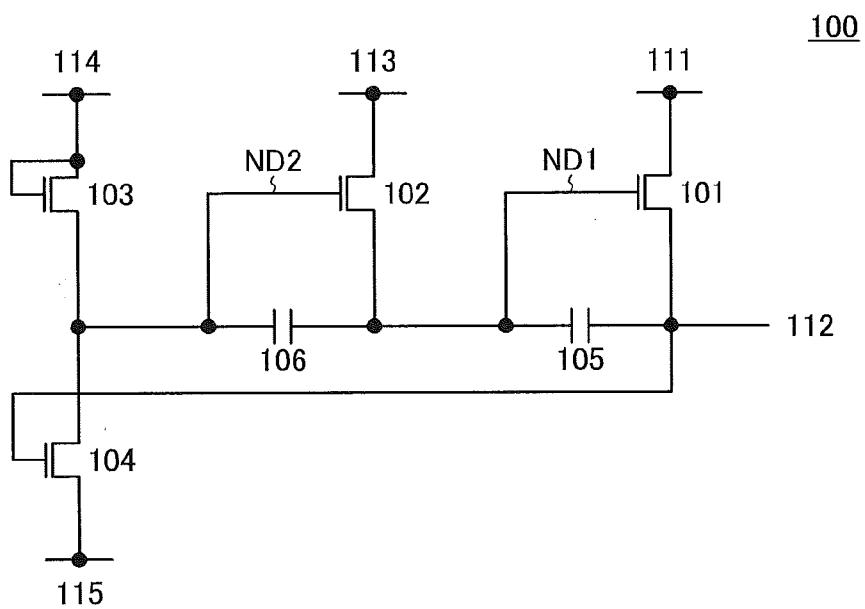

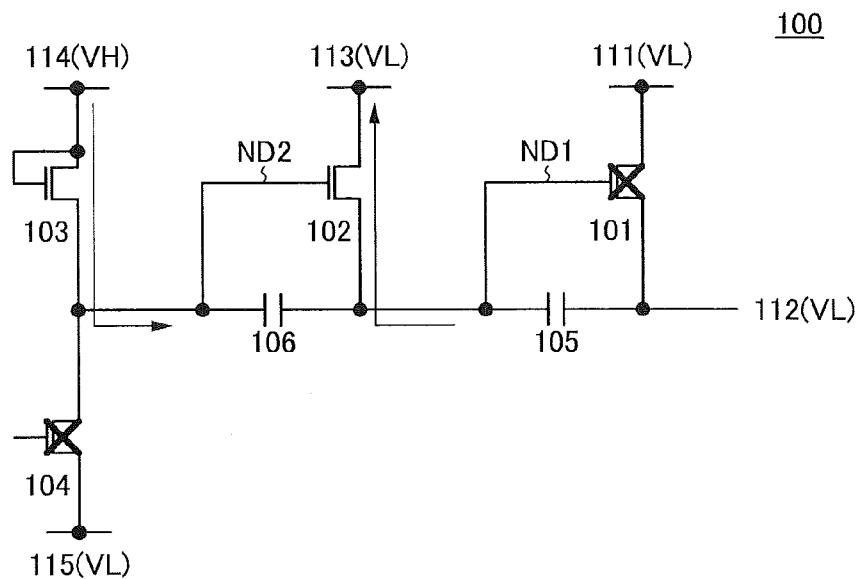

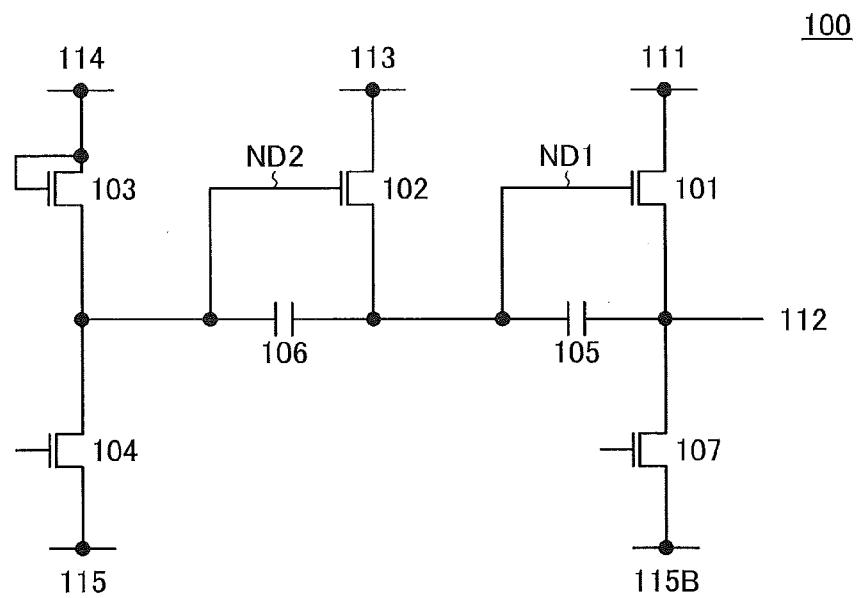

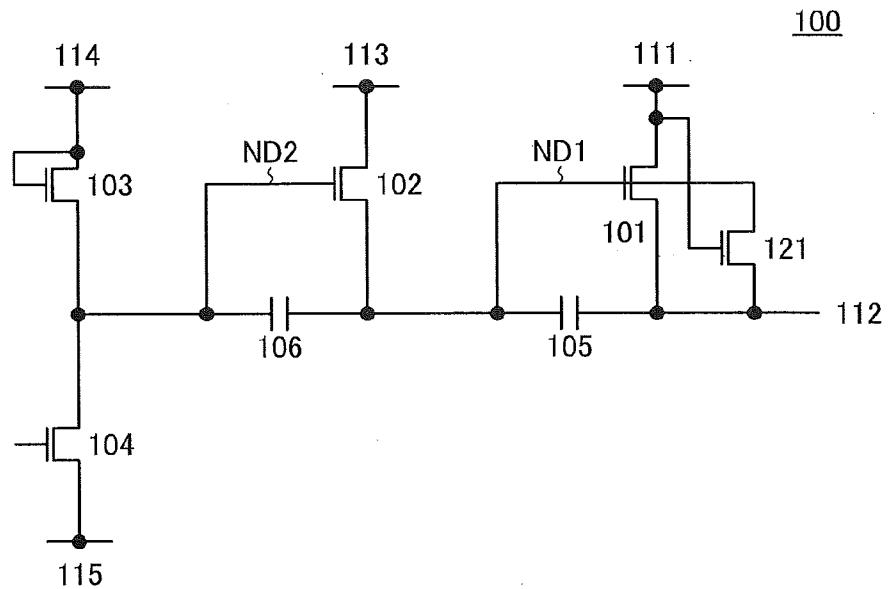

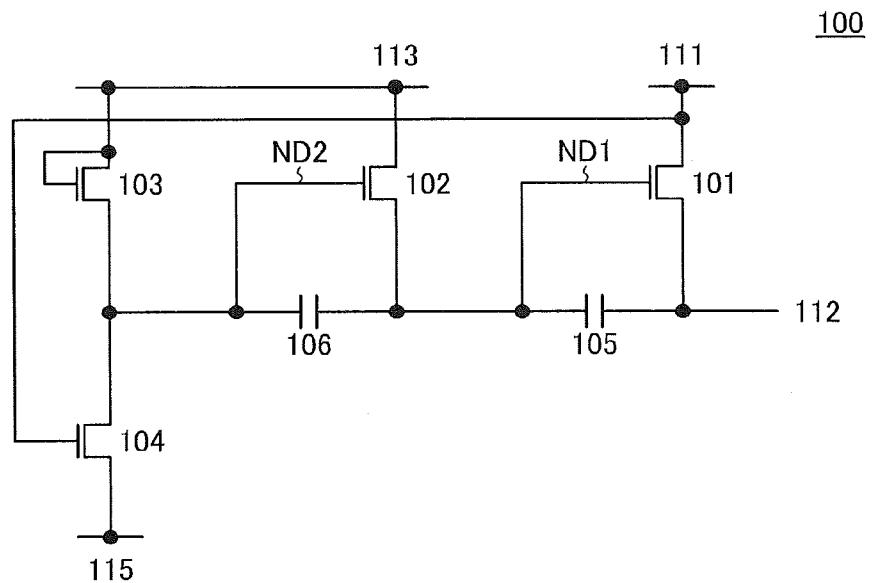

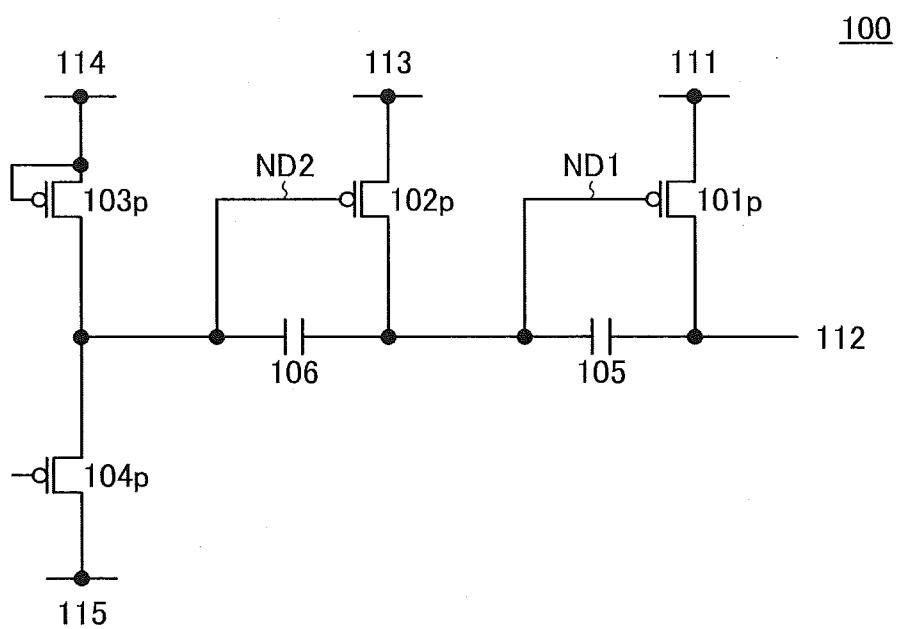

[0019] FIG. 1 illustrates an example of a semiconductor device.

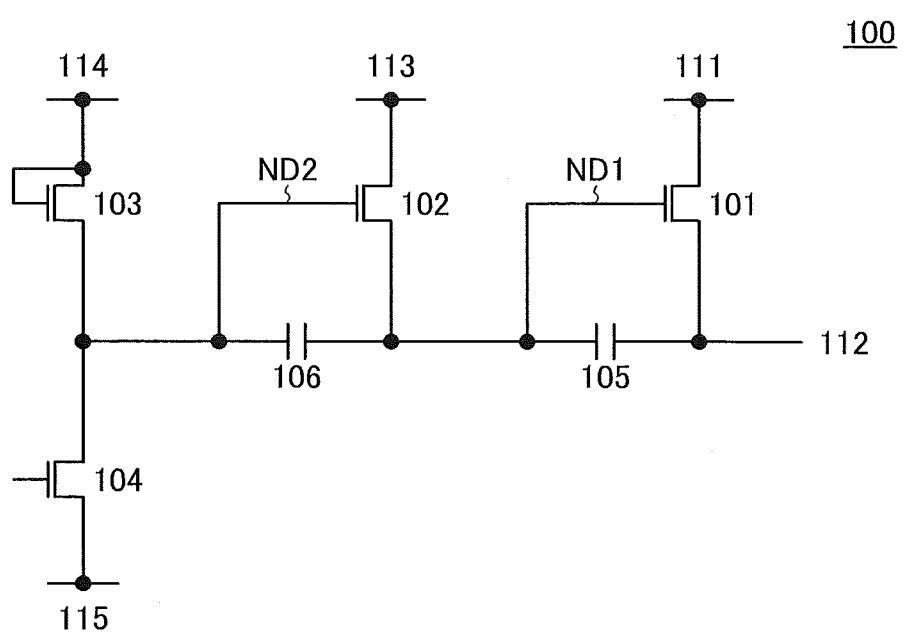

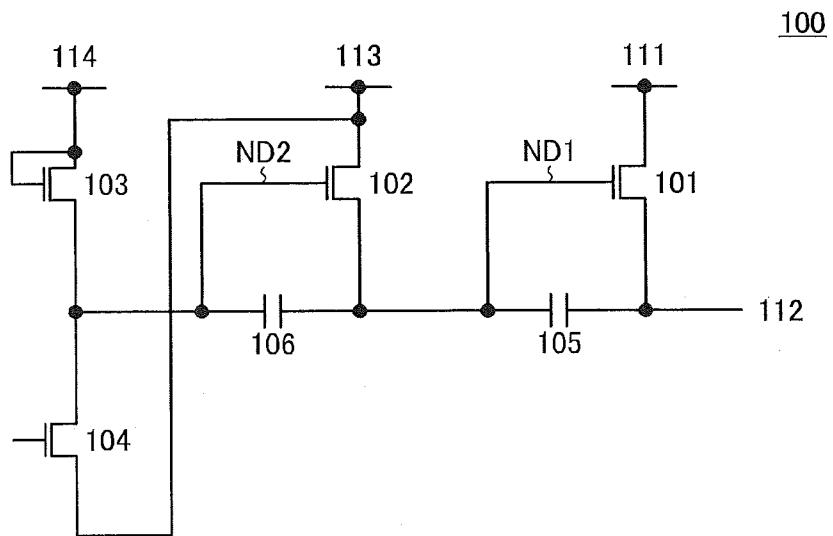

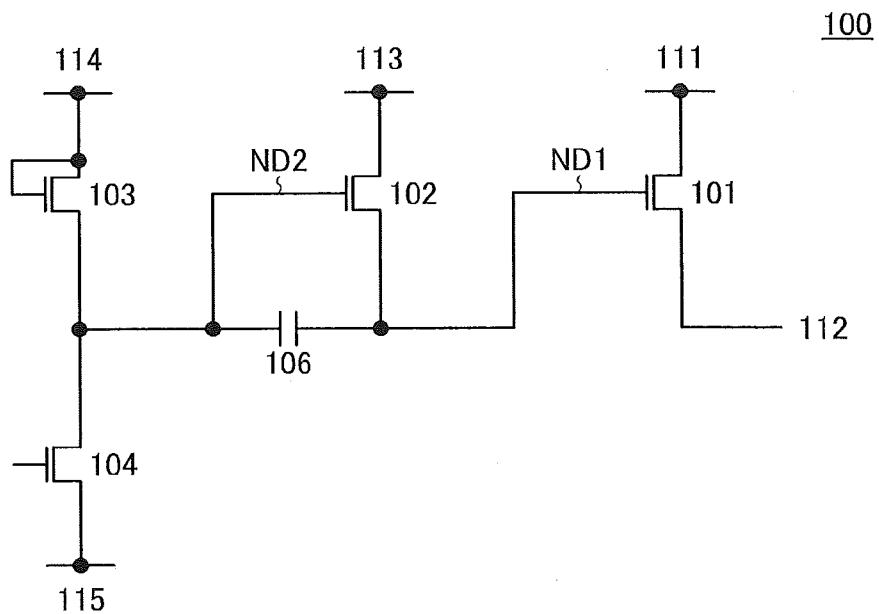

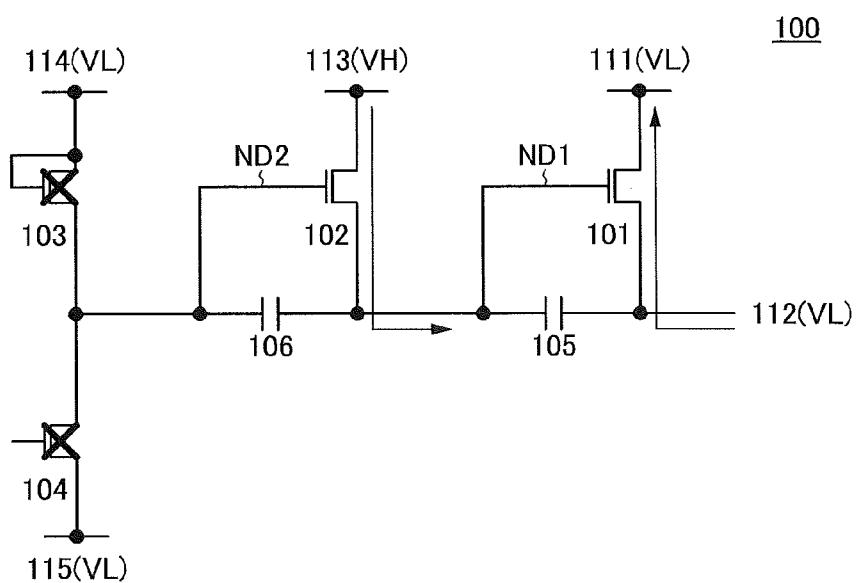

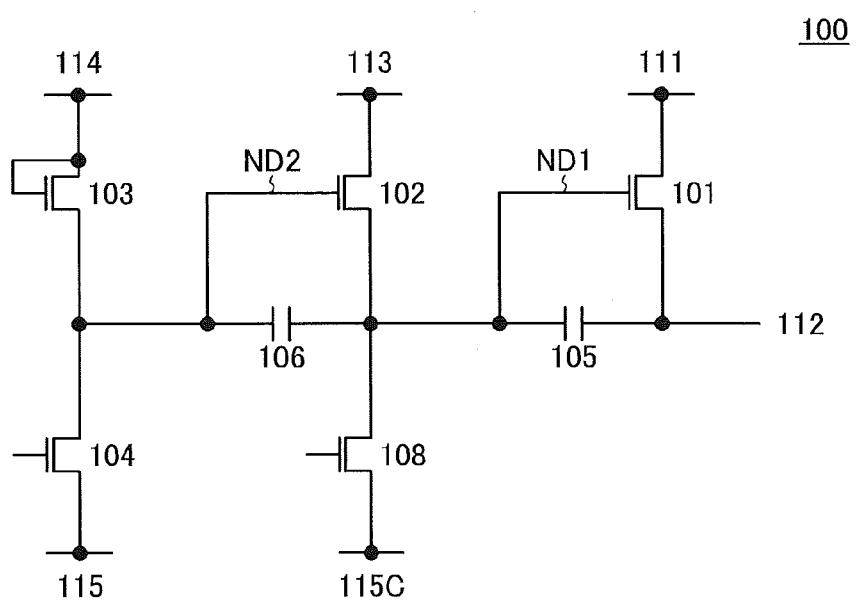

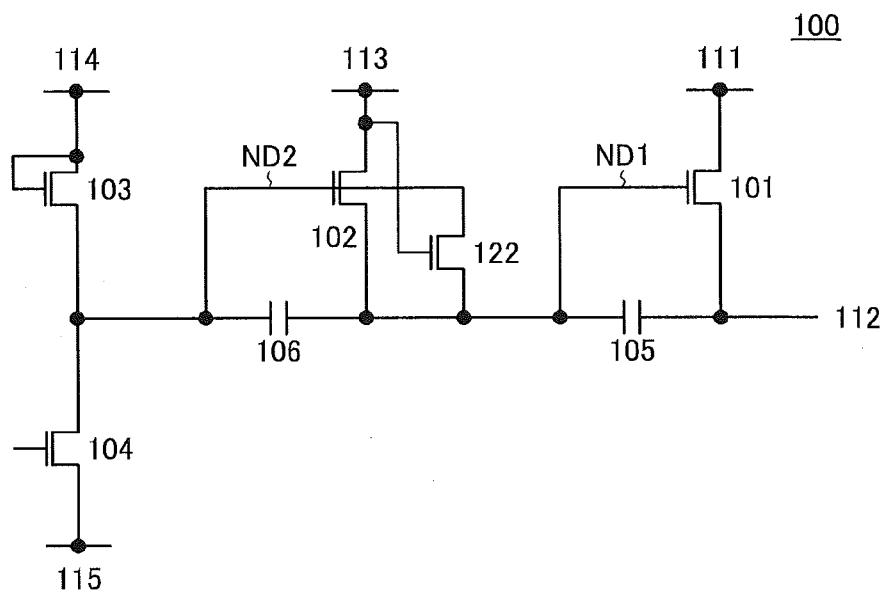

[0020] FIGS. 2A and 2B each illustrate an example of a semiconductor device;

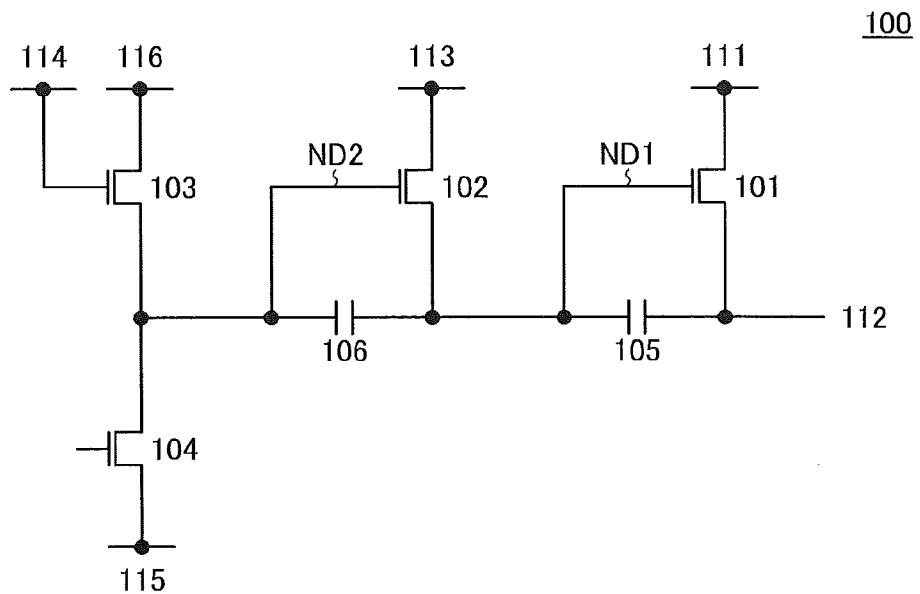

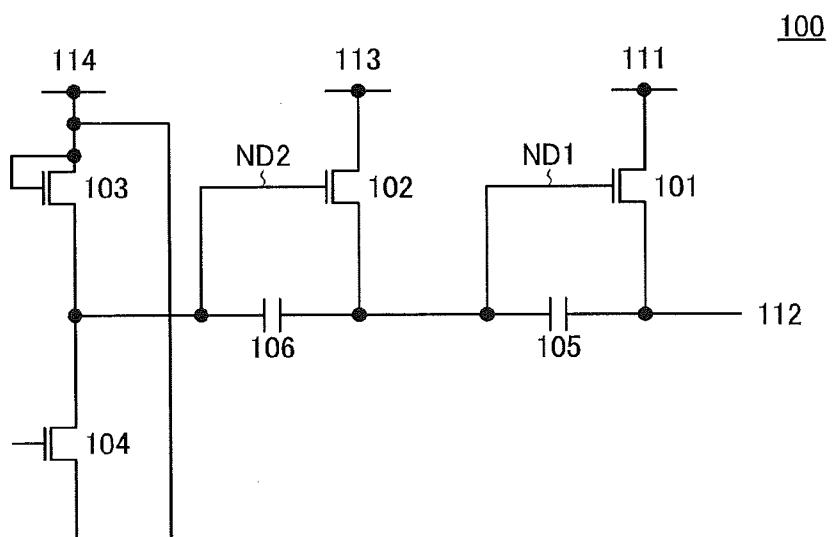

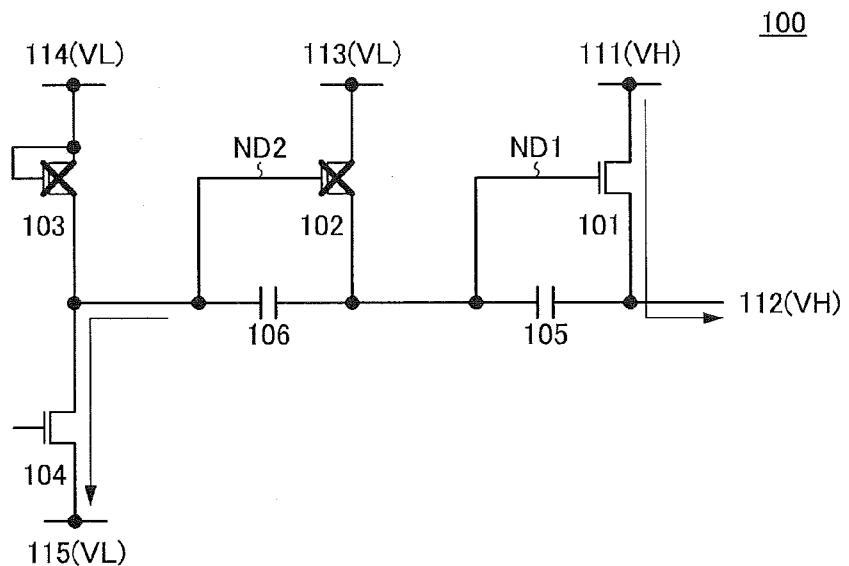

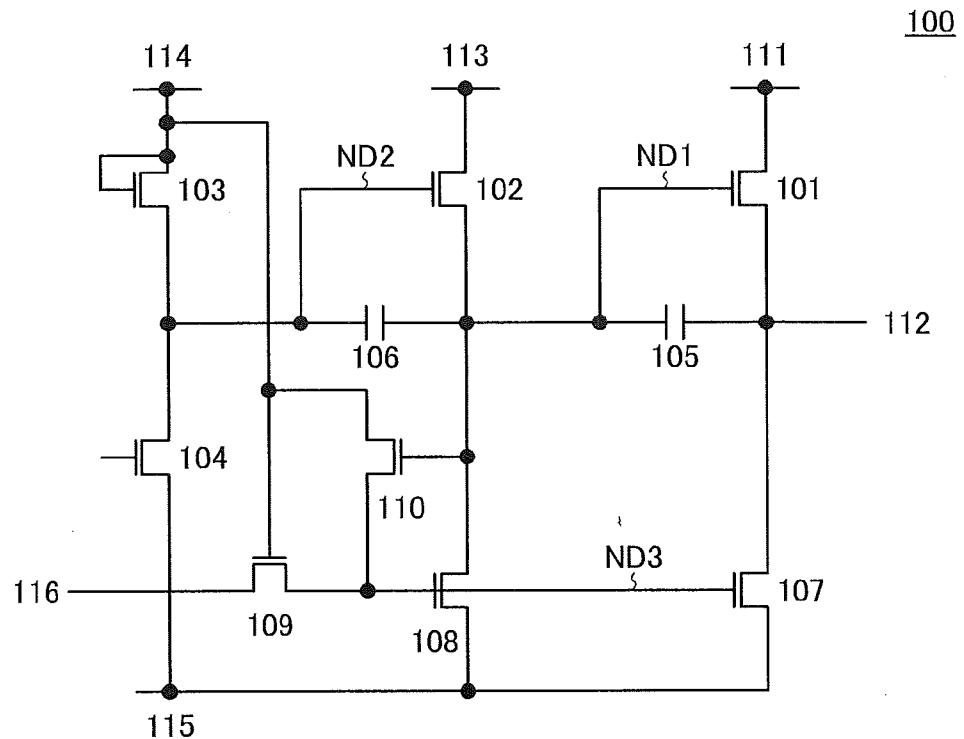

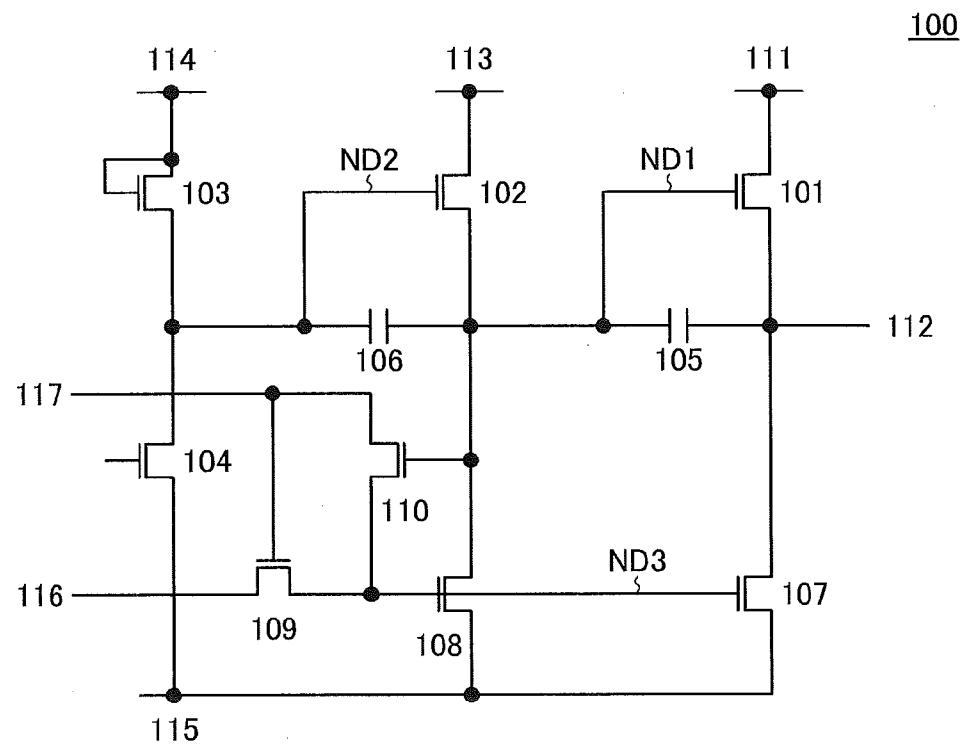

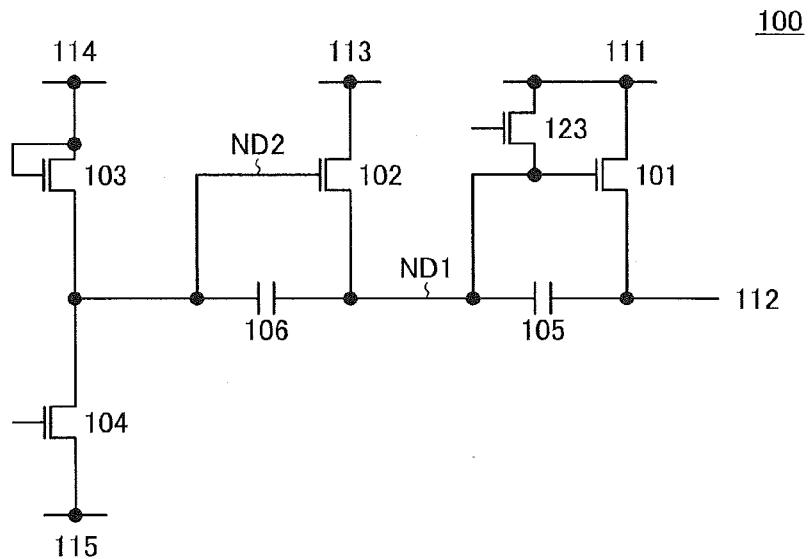

[0021] FIGS. 3A and 3B each illustrate one example of a semiconductor device.

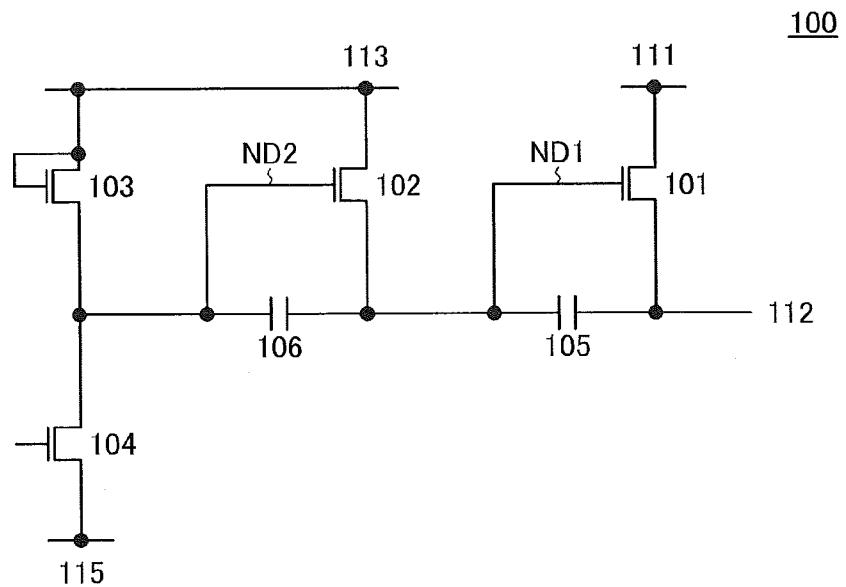

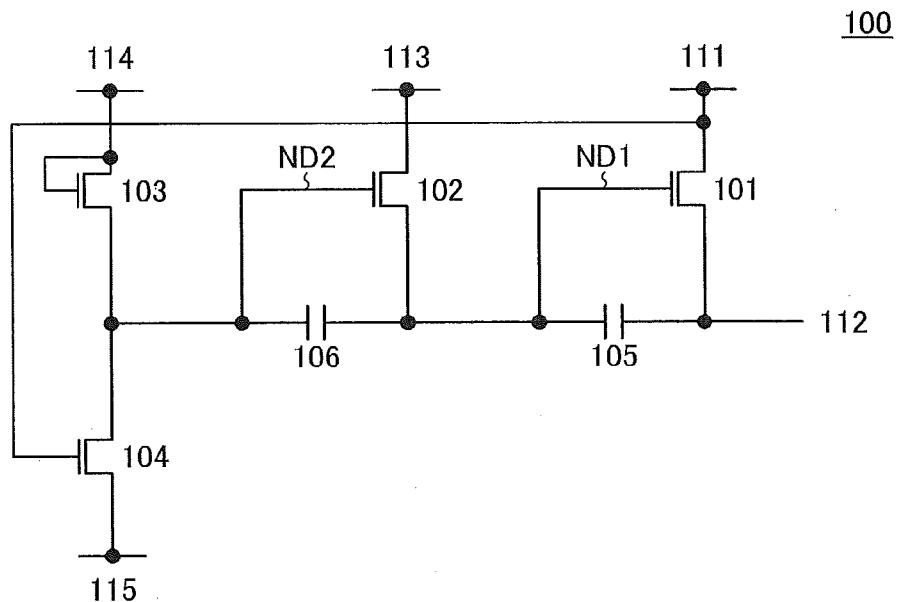

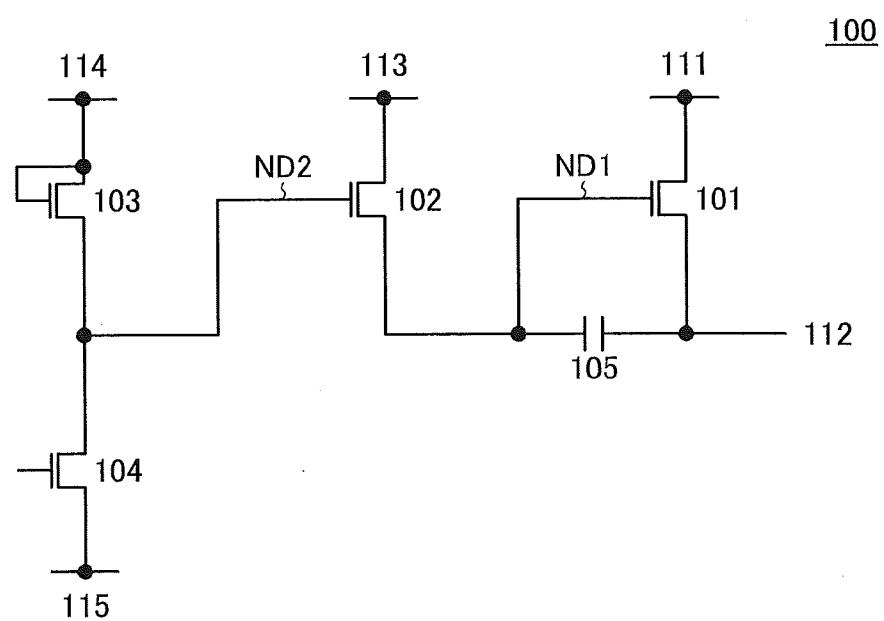

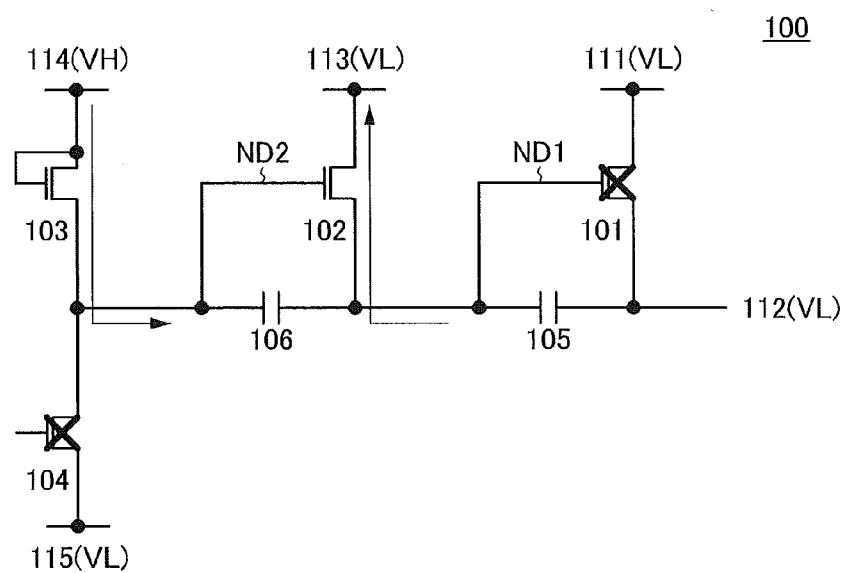

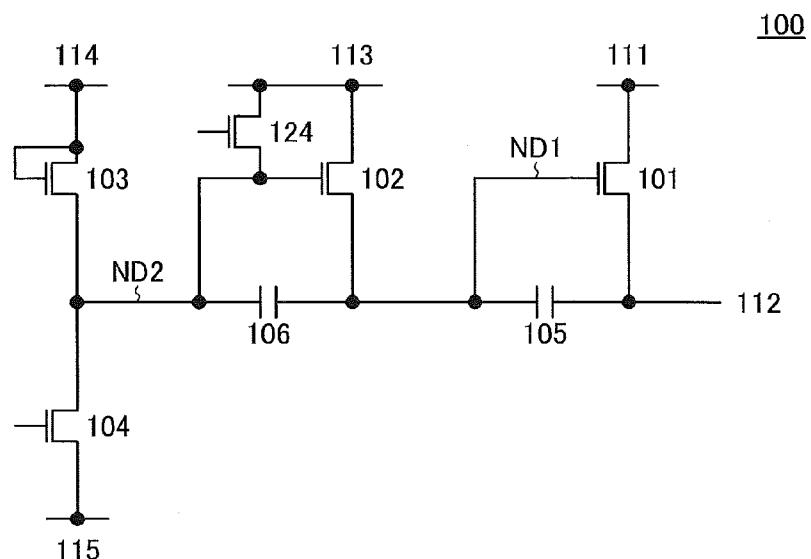

[0022] FIGS. 4A and 4B each illustrate an example of a semiconductor device.

[0023] FIGS. 5A and 5B each illustrate an example of a semiconductor device.

[0024] FIGS. 6A and 6B each illustrates an example of a semiconductor device.

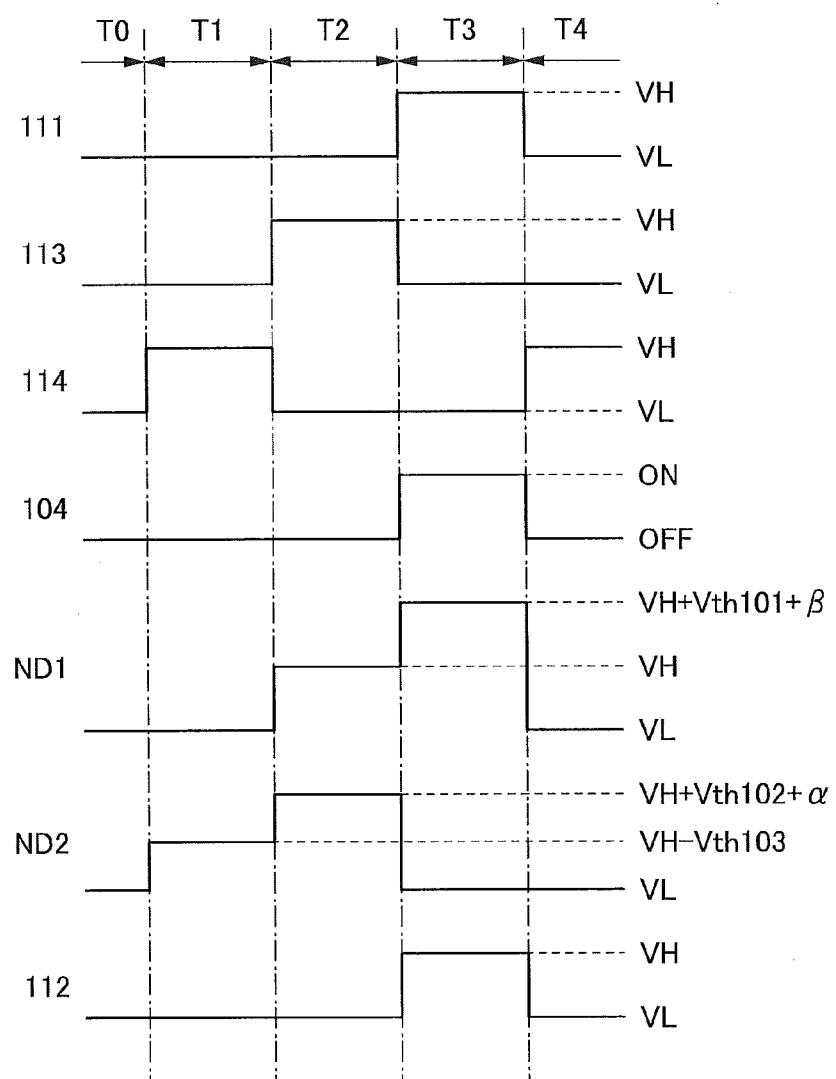

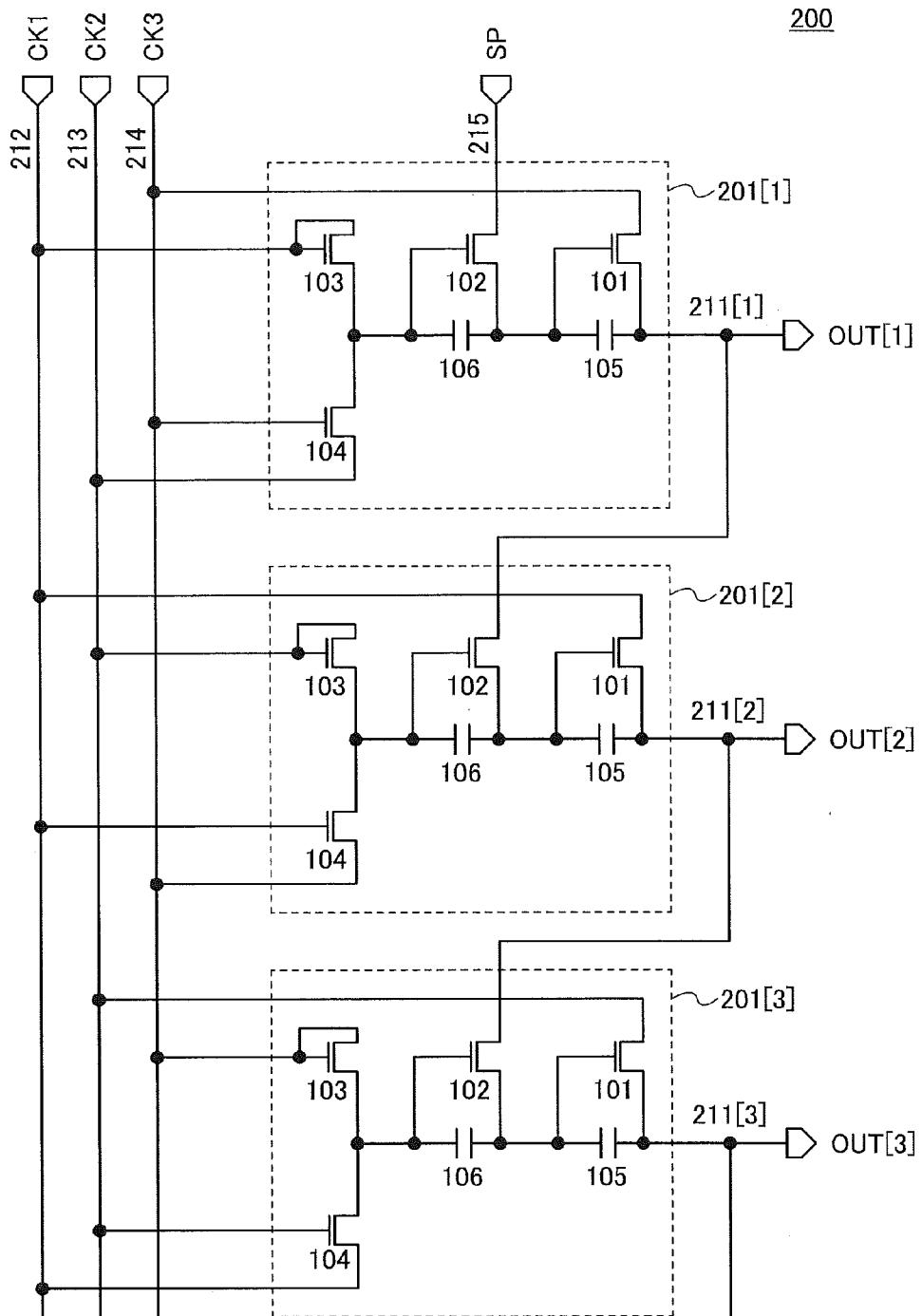

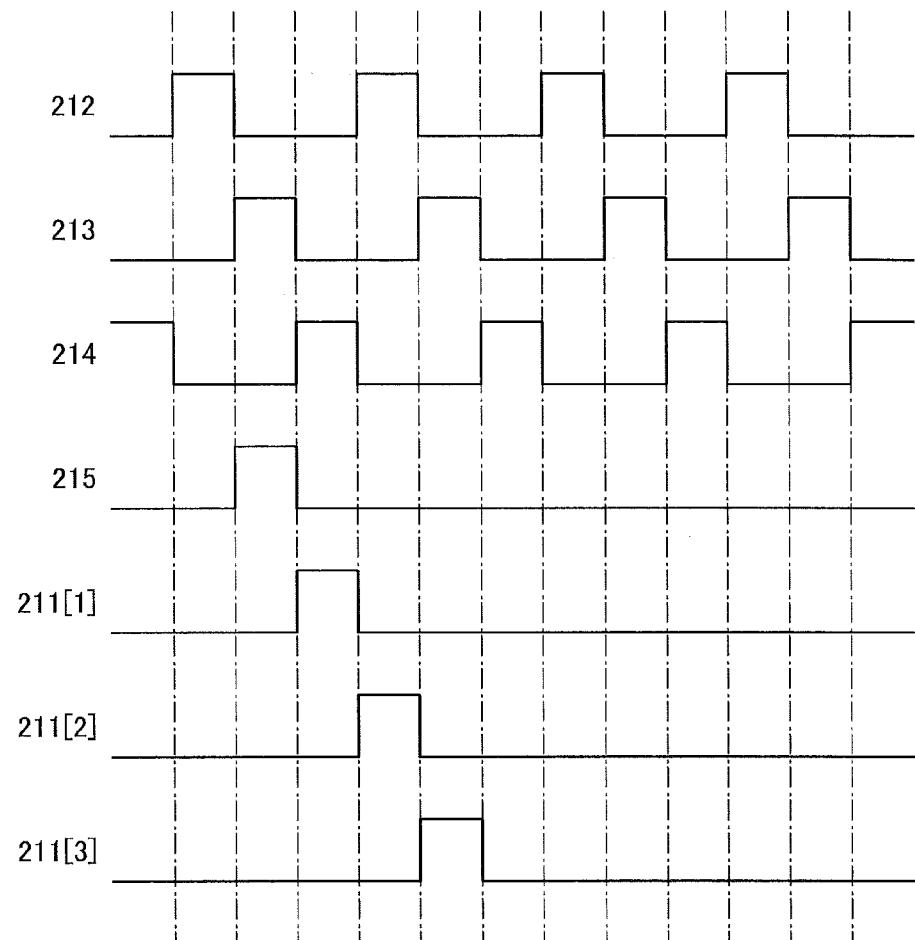

[0025] FIG. 7 is a timing chart showing an example of operation of a semiconductor device.

[0026] FIGS. 8A and 8B illustrate an example of a semiconductor device.

[0027] FIGS. 9A and 9B illustrate an example of a semiconductor device;

[0028] FIGS. 10A and 10B each illustrate an example of a semiconductor device.

[0029] FIGS. 11A and 11B each illustrate examples of a semiconductor device.

[0030] FIGS. 12A and 12B each illustrate an example of a semiconductor device.

[0031] FIGS. 13A and 13B each illustrate an example of a semiconductor device.

[0032] FIGS. 14A and 14B each illustrate an example of a semiconductor device.

[0033] FIG. 15 illustrates an example of a semiconductor device.

[0034] FIG. 16 is a timing chart showing an example of operation of a semiconductor device.

[0035] FIG. 17 illustrates an example of a structure of a semiconductor device.

[0036] FIG. 18 illustrates an example of a semiconductor device.

[0037] FIG. 19 illustrates an example of a display device.

[0038] FIG. 20 illustrates an example of a semiconductor device.

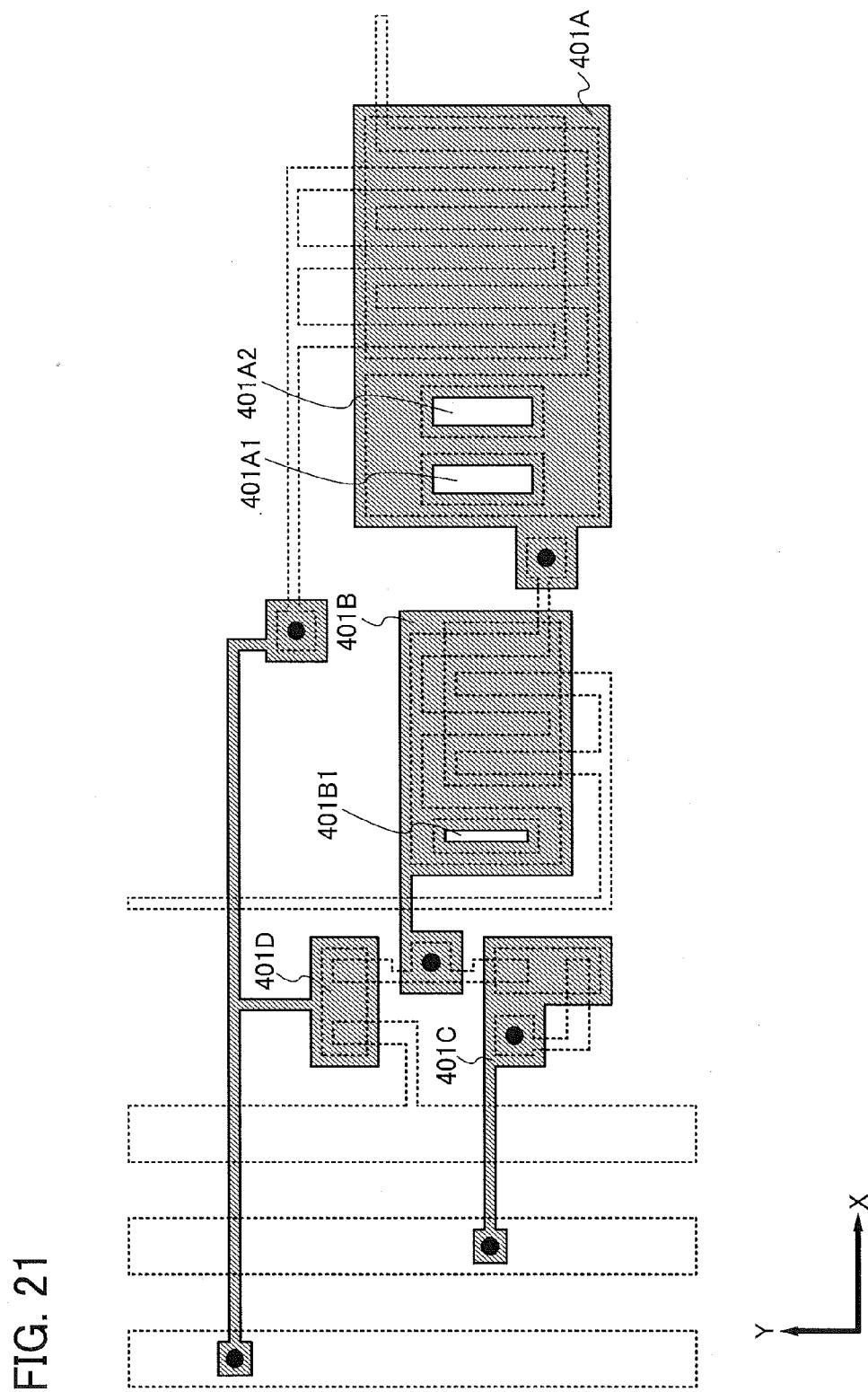

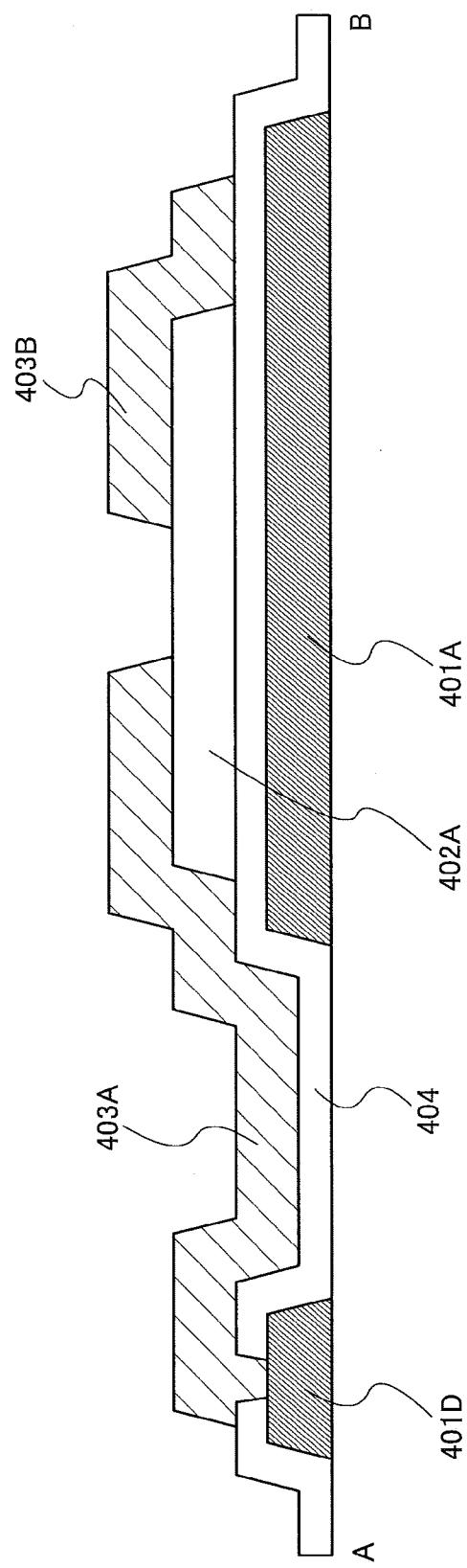

[0039] FIG. 21 illustrates an example of a semiconductor device.

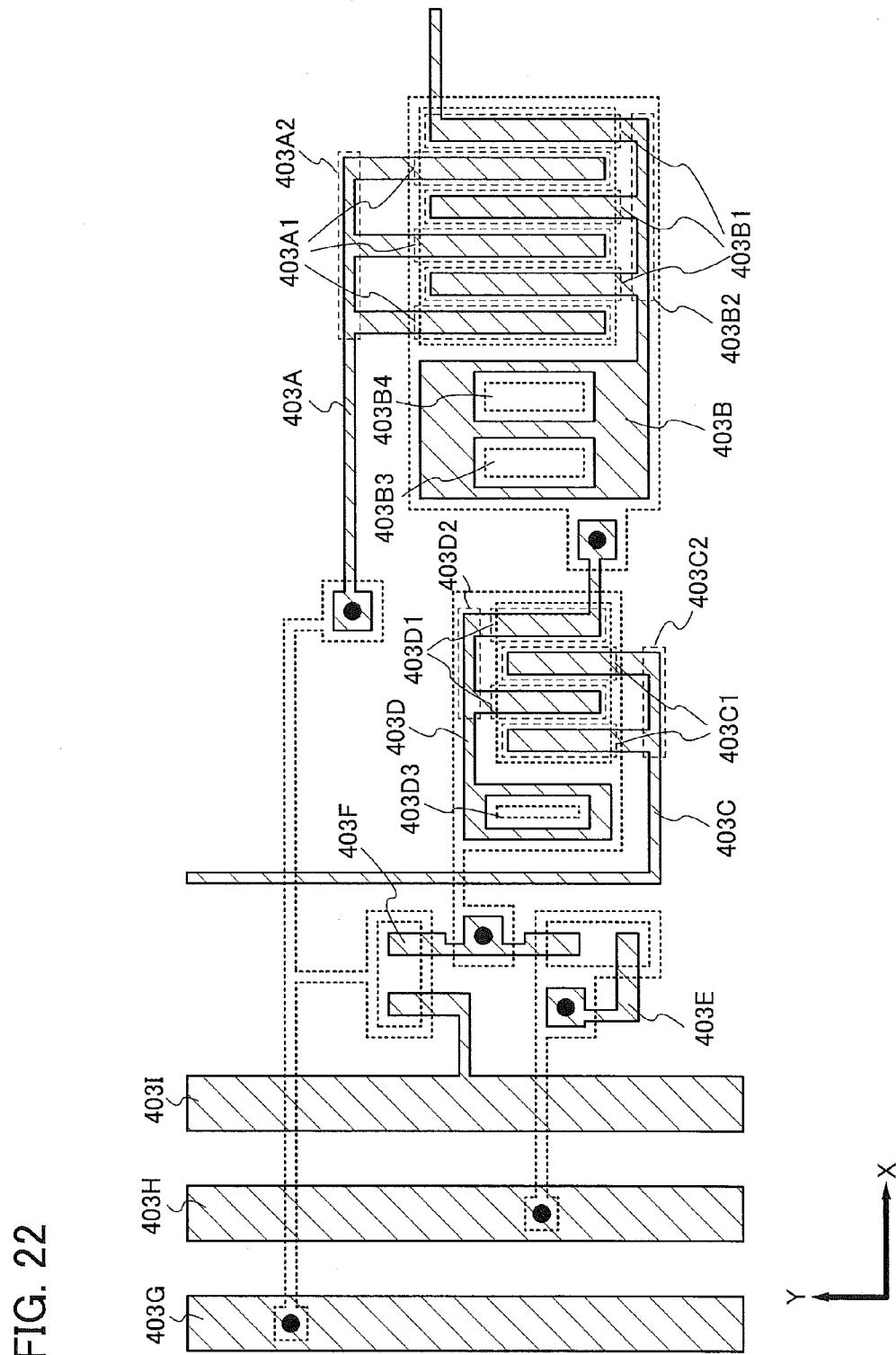

[0040] FIG. 22 illustrates an example of a semiconductor device.

[0041] FIG. 23 illustrates an example of a semiconductor device.

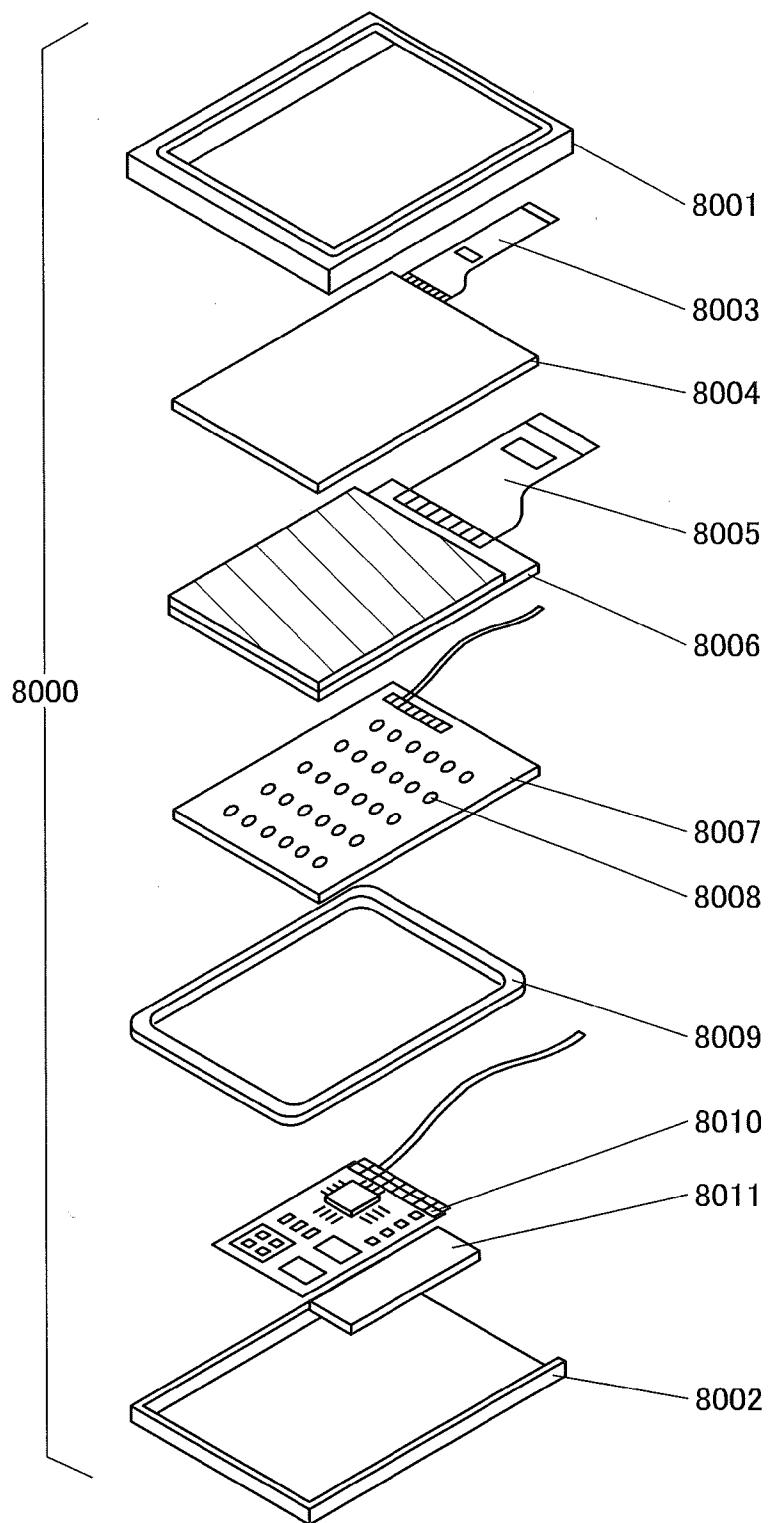

[0042] FIG. 24 illustrates an example of a display module.

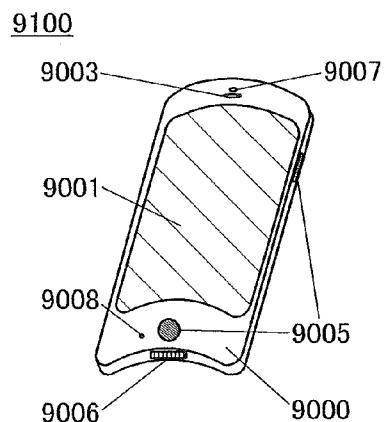

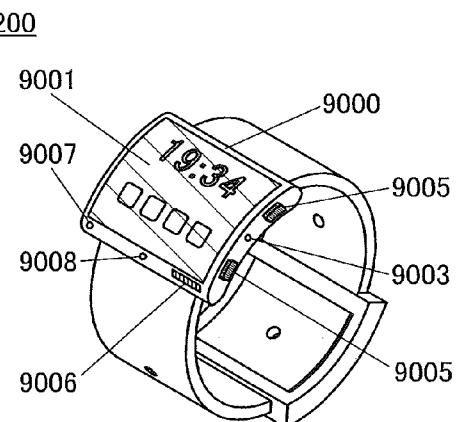

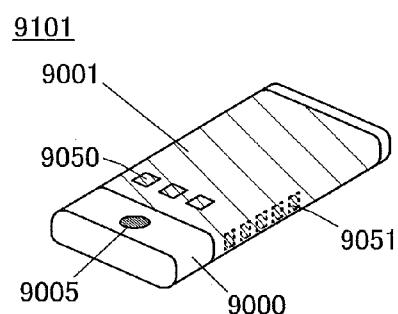

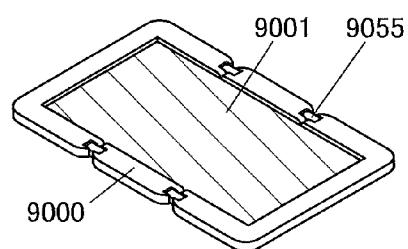

[0043] FIGS. 25A to 25G illustrate examples of an electronic appliance.

[0044] FIG. 26 illustrates an example of a semiconductor device.

#### DETAILED DESCRIPTION OF THE INVENTION

[0045] Hereinafter, embodiments of the present invention will be described below in detail with reference to the accompanying drawings. Note that the present invention is not limited to the following description and it is easily understood by those skilled in the art that the mode and details can be variously changed without departing from the scope and spirit of the present invention. Therefore, the present invention should not be interpreted as being limited to the description of embodiments below.

[0046] One embodiment of the present invention includes, in its category, devices such as an imaging device, a radio frequency (RF) tag, a display device, and an integrated circuit. The display device includes, in its category, a display device including an integrated circuit, such as a liquid crystal display device, a light-emitting device in which a light-emitting element typified by an organic light-emitting element is provided in each pixel, an electronic paper, a digital micro-mirror device (DMD), a plasma display panel (PDP), and a field emission display (FED).

[0047] In describing structures of the present invention with reference to the drawings, the same reference numerals are used in common for the same portions in different drawings in some cases.

[0048] Note that in this specification and the like, part of a diagram or a text described in one embodiment can be taken out to constitute one embodiment of the invention. Thus, in the case where a diagram or a text related to a certain portion is described, the context taken out from part of the diagram or the text is also disclosed as one embodiment of the invention, and one embodiment of the invention can be constituted. The embodiment of the present invention is clear. Therefore, for example, in a diagram or text in which one or more active elements (e.g., transistors), wirings, passive elements (e.g., capacitors), conductive layers, insulating layers, semiconductor layers, components, devices, operating methods, manufacturing methods, or the like are described, part of the diagram or the text is taken out, and one embodiment of the invention can be constituted. For example, from a circuit diagram in which N circuit elements (e.g., transistors or capacitors; N is an integer) are provided, it is possible to constitute one embodiment of the invention by taking out M circuit elements (e.g., transistors or capacitors; M is an integer, where M<N). For another example, it is possible to take out some given elements from a sentence "A includes B, C, D, E, or F" and constitute one embodiment of the invention, for example, "A includes B and E", "A includes E and F", "A includes C, E, and F", or "A includes B, C, D, and E".

[0049] Note that in the case where at least one specific example is described in a diagram or text described in one embodiment in this specification and the like, it will be readily appreciated by those skilled in the art that a broader concept of the specific example can be derived. Therefore, in the diagram or the text described in one embodiment, in the case where at least one specific example is described, a broader concept of the specific example is disclosed as one embodiment of the invention, and one embodiment of the invention can be constituted. The embodiment of the present invention is clear.

**[0050]** Note that in this specification and the like, a content described in at least a diagram (or may be part of the diagram) is disclosed as one embodiment of the invention, and one embodiment of the invention can be constituted. Therefore, when a certain content is described in a diagram, the content is disclosed as one embodiment of the invention even when the content is not described with a text, and one embodiment of the invention can be constituted. In a similar manner, part of a diagram, which is taken out from the diagram, is disclosed as one embodiment of the invention, and one embodiment of the invention can be constituted. The embodiment of the present invention is clear.

**[0051]** In addition, contents that are not specified in any text or drawing in the specification can be excluded from one embodiment of the invention. Alternatively, when the range of a value that is defined by the maximum and minimum values is described, part of the range is appropriately narrowed or part of the range is removed, whereby one embodiment of the invention excluding part of the range can be constituted. In this manner, it is possible to specify the technical scope of one embodiment of the present invention so that a conventional technology is excluded, for example.

**[0052]** In this specification and the like, it might be possible for those skilled in the art to constitute one embodiment of the invention even when portions to which all the terminals of an active element (e.g., a transistor), a passive element (e.g., a capacitor), or the like are connected are not specified. In other words, one embodiment of the invention can be clear even when connection portions are not specified. Further, in the case where a connection portion is disclosed in this specification and the like, it can be determined that one embodiment of the invention in which a connection portion is not specified is disclosed in this specification and the like, in some cases. In particular, in the case where the number of portions to which the terminal is connected might be plural, it is not necessary to specify the portions to which the terminal is connected. Thus, it might be possible to constitute one embodiment of the invention by specifying only portions to which some of terminals of an active element (e.g., a transistor), a passive element (e.g., a capacitor), or the like are connected.

**[0053]** Note that in this specification and the like, it might be possible for those skilled in the art to specify the invention when at least the connection portion of a circuit is specified. Alternatively, it might be possible for those skilled in the art to specify the invention when at least a function of a circuit is specified. In other words, when a function of a circuit is specified, one embodiment of the present invention can be clear. Further, it can be determined that one embodiment of the present invention whose function is specified is disclosed in this specification and the like. Therefore, when a connection portion of a circuit is specified, the circuit is disclosed as one embodiment of the invention even when a function is not specified, and one embodiment of the invention can be constituted. Alternatively, when a function of a circuit is specified, the circuit is disclosed as one embodiment of the invention even when a connection portion is not specified, and one embodiment of the invention can be constituted.

**[0054]** In this specification and the like, when it is explicitly described that X and Y are connected, the case where X and Y are electrically connected, the case where X and Y are functionally connected, and the case where X and Y are directly connected are included therein. Accordingly, without being limited to a predetermined connection relation, for example,

a connection relation shown in drawings or text, another connection relation is included in the drawings or the text.

**[0055]** Here, X and Y each denote an object (e.g., a device, an element, a circuit, a wiring, an electrode, a terminal, a conductive film, or a layer).

**[0056]** Examples of the case where X and Y are directly connected include the case where an element that enables an electrical connection between X and Y (e.g., a switch, a transistor, a capacitor, an inductor, a resistor, a diode, a display element, a light-emitting element, or a load) is not connected between X and Y, and the case where X and Y are connected without the element that allows the electrical connection between X and Y provided therebetween.

**[0057]** For example, in the case where X and Y are electrically connected, one or more elements that enable electrical connection between X and Y (e.g., a switch, a transistor, a capacitor, an inductor, a resistor, a diode, a display element, a light-emitting element, or a load) can be connected between X and Y. A switch is controlled to be on or off. That is, a switch is conducting or not conducting (is turned on or off) to determine whether current flows therethrough or not. Alternatively, the switch has a function of selecting and changing a current path. Note that the case where X and Y are electrically connected includes the case where X and Y are directly connected.

**[0058]** For example, in the case where X and Y are functionally connected, one or more circuits that enable functional connection between X and Y (e.g., a logic circuit such as an inverter, a NAND circuit, or a NOR circuit; a signal converter circuit such as a DA converter circuit, an AD converter circuit, or a gamma correction circuit; a potential level converter circuit such as a power supply circuit (e.g., a step-up circuit or a step-down circuit) or a level shifter circuit for changing the potential level of a signal; a voltage source; a current source; a switching circuit; an amplifier circuit such as a circuit that can increase signal amplitude, the amount of current, or the like, an operational amplifier, a differential amplifier circuit, a source follower circuit, or a buffer circuit; a signal generation circuit; a memory circuit; and/or a control circuit) can be connected between X and Y. Note that for example, in the case where a signal output from X is transmitted to Y even when another circuit is interposed between X and Y, X and Y are functionally connected. Note that the case where X and Y are functionally connected includes the case where X and Y are directly connected and the case where X and Y are electrically connected.

**[0059]** Note that in this specification and the like, an explicit description "X and Y are electrically connected" means that X and Y are electrically connected (i.e., the case where X and Y are connected with another element or another circuit provided therebetween), X and Y are functionally connected (i.e., the case where X and Y are functionally connected with another circuit provided therebetween), and X and Y are directly connected (i.e., the case where X and Y are connected without another element or another circuit provided therebetween). That is, in this specification and the like, the explicit description "X and Y are electrically connected" is the same as the description "X and Y are connected".

**[0060]** Note that, for example, the case where a source (or a first terminal or the like) of a transistor is electrically connected to X through (or not through) Z1 and a drain (or a second terminal or the like) of the transistor is electrically connected to Y through (or not through) Z2, or the case where

a source (or a first terminal or the like) of a transistor is directly connected to one part of  $Z1$  and another part of  $Z1$  is directly connected to  $X$  while a drain (or a second terminal or the like) of the transistor is directly connected to one part of  $Z2$  and another part of  $Z2$  is directly connected to  $Y$ , can be expressed by using any of the following expressions.

[0061] The expressions include, for example, “ $X$ ,  $Y$ , a source (or a first terminal or the like) of a transistor, and a drain (or a second terminal or the like) of the transistor are electrically connected to each other, and  $X$ , the source (or the first terminal or the like) of the transistor, the drain (or the second terminal or the like) of the transistor, and  $Y$  are electrically connected to each other in this order”, “a source (or a first terminal or the like) of a transistor is electrically connected to  $X$ , a drain (or a second terminal or the like) of the transistor is electrically connected to  $Y$ , and  $X$ , the source (or the first terminal or the like) of the transistor, the drain (or the second terminal or the like) of the transistor, and  $Y$  are electrically connected to each other in this order”, and “ $X$  is electrically connected to  $Y$  through a source (or a first terminal or the like) and a drain (or a second terminal or the like) of a transistor, and  $X$ , the source (or the first terminal or the like) of the transistor, the drain (or the second terminal or the like) of the transistor, and  $Y$  are provided to be connected in this order”. When the connection order in a circuit configuration is defined by an expression similar to the above examples, a source (or a first terminal or the like) and a drain (or a second terminal or the like) of a transistor can be distinguished from each other to specify the technical scope.

[0062] Other examples of the expressions include, “a source (or a first terminal or the like) of a transistor is electrically connected to  $X$  through at least a first connection path, the first connection path does not include a second connection path, the second connection path is a path between the source (or the first terminal or the like) of the transistor and a drain (or a second terminal or the like) of the transistor,  $Z1$  is on the first connection path, the drain (or the second terminal or the like) of the transistor is electrically connected to  $Y$  through at least a third connection path, the third connection path does not include the second connection path, and  $Z2$  is on the third connection path” and “a source (or a first terminal or the like) of a transistor is electrically connected to  $X$  at least with a first connection path through  $Z1$ , the first connection path does not include a second connection path, the second connection path includes a connection path through which the transistor is provided, a drain (or a second terminal or the like) of the transistor is electrically connected to  $Y$  at least with a third connection path through  $Z2$ , and the third connection path does not include the second connection path” Still another example of the expression is “a source (or a first terminal or the like) of a transistor is electrically connected to  $X$  through at least  $Z1$  on a first electrical path, the first electrical path does not include a second electrical path, the second electrical path is an electrical path from the source (or the first terminal or the like) of the transistor to a drain (or a second terminal or the like) of the transistor, the drain (or the second terminal or the like) of the transistor is electrically connected to  $Y$  through at least  $Z2$  on a third electrical path, the third electrical path does not include a fourth electrical path, and the fourth electrical path is an electrical path from the drain (or the second terminal or the like) of the transistor to the source (or the first terminal or the like) of the transistor”. When the connection path in a circuit structure is defined by an expression similar to the above examples, a source (or a first terminal or the like)

and a drain (or a second terminal or the like) of a transistor can be distinguished from each other to specify the technical scope.

[0063] Note that these expressions are examples and there is no limitation on the expressions. Here,  $X$ ,  $Y$ ,  $Z1$ , and  $Z2$  each denote an object (e.g., a device, an element, a circuit, a wiring, an electrode, a terminal, a conductive film, and a layer).

[0064] Even when independent components are electrically connected to each other in a circuit diagram, one component has functions of a plurality of components in some cases. For example, when part of a wiring also functions as an electrode, one conductive film functions as the wiring and the electrode. Thus, “electrical connection” in this specification includes in its category such a case where one conductive film has functions of a plurality of components.

#### Embodiment 1

[0065] In this embodiment, a semiconductor device of one embodiment of the present invention will be described.

[0066] A structure of a semiconductor device of one embodiment of the present invention will be described with reference to FIG. 1. Note that one embodiment of the present invention is not limited to the structure described below.

[0067] A semiconductor device illustrated in FIG. 1 includes a circuit 100. The circuit 100 has a function of controlling the potential of a wiring 112 based on the potentials of a wiring 111, a wiring 113, a wiring 114, and a wiring 115. The circuit 100 outputs a signal based on the potentials of the wiring 111, the wiring 113, the wiring 114, and the wiring 115 to the wiring 112. The potential of the wiring 112 is controlled by the signal. As described above, the circuit 100 serves as a logic circuit or a sequential circuit.

[0068] The circuit 100 includes a transistor 101, a transistor 102, a transistor 103, a transistor 104, a capacitor 105, and a capacitor 106. A first terminal (also referred to as one of a source and a drain) of the transistor 101 is connected to the wiring 111, and a second terminal (also referred to as the other of the source and the drain) of the transistor 101 is connected to the wiring 112. A first terminal and a second terminal of the transistor 102 are connected to the wiring 113 and a gate of the transistor 101, respectively. A first terminal, a second terminal, and a gate of the transistor 103 are connected to the wiring 114, a gate of the transistor 102, and the wiring 114, respectively. A first terminal and a second terminal of the transistor 104 are connected to the wiring 115 and the gate of the transistor 102, respectively. A first terminal and a second terminal of the capacitor 105 are connected to the wiring 112 and the gate of the transistor 101, respectively. A first terminal and a second terminal of the capacitor 106 are connected to the gate of the transistor 101 and the gate of the transistor 102, respectively.

[0069] The semiconductor device in this embodiment has a connection relation described above, and thus can have a novel configuration.

[0070] Note that the gate of the transistor 101, the second terminal of the transistor 102, the second terminal of the capacitor 105, or a first terminal of the capacitor 106 is denoted by a node ND1. In addition, the gate of the transistor 102, a second terminal of the transistor 103, the second terminal of the transistor 104, or the second terminal of the capacitor 106 is denoted by a node ND2.

[0071] Note that the potentials of the wirings 111, 113, 114, and 115 are controlled in such a manner that a signal, voltage,

or the like is input to the wirings. The potentials of the wirings **111**, **113**, and **114** each have a high level and a low level for convenience. That is, signals each having a high level and a low level are input to each of the wirings **111**, **113**, and **114**. A high-level potential is **VH**, and a low-level potential is **VL** ( $VH > VL$ ). The potential of the wiring **115** is **VL**. Note that the potential of the wiring **115** may have a high level and a low level. That is, a signal having a high level and a low level may be input to the wiring **115**.

[0072] Note that the wirings **111**, **113**, and **114** may each be referred to as an input terminal. The wiring **112** may be referred to as an output terminal. The wirings **111**, **112**, **113**, and **114** may each be referred to as a signal line. The wiring **115** may be referred to as a power supply line.

[0073] Transistors which can be used as the transistors **101**, **102**, **103**, and **104** are described. Note that one embodiment of the present invention is not limited to the transistors described below.

[0074] As the transistors **101**, **102**, **103**, and **104**, a transistor including amorphous silicon in a channel formation region, a transistor including polycrystalline silicon in a channel formation region, a transistor including single crystal silicon in a channel formation region, a transistor including an oxide semiconductor in a channel formation region, a transistor including a compound semiconductor in a channel formation region, and the like can be used. In particular, a transistor including an oxide semiconductor in a channel formation region (also referred to as an OS transistor) has a higher mobility and an extremely lower off-state current than a transistor including amorphous silicon in a channel formation region. Accordingly, the channel width of the transistor can be made small, leading to a reduction in a layout area.

[0075] The conductivity type or the polarity of the transistors **101**, **102**, **103**, and **104** is described. Note that one embodiment of the present invention is not limited to the conductivity type or the polarity described below.

[0076] The transistors **101**, **102**, **103**, and **104** preferably have the same conductivity type. Alternatively, all the transistors included in the circuit **100** preferably have the same conductivity type. Further alternatively, all the transistors provided over the same substrate as the circuit **100** preferably have the same conductivity type. Thus, simplification of a manufacturing process, improvement in yield, reduction in manufacturing cost, or the like can be achieved.

[0077] It is particularly preferable that the transistors **101**, **102**, **103**, and **104** be n-channel transistors. Alternatively, it is preferable that all the transistors included in the circuit **100** be n-channel transistors. Further alternatively, it is preferable that all the transistors provided over the same substrate as the circuit **100** be n-channel transistors. This enables a transistor including an oxide semiconductor in a channel formation region (also referred to as an OS transistor) to be used. In FIG. 1, the case where the transistors **101**, **102**, **103**, and **104** are n-channel transistors is illustrated. However, the transistors **101**, **102**, **103**, and **104** may be p-channel transistors. Alternatively, all the transistors included in the circuit **100** may be p-channel transistors. Further alternatively, all the transistors provided over the same substrate as the circuit **100** may be p-channel transistors. FIG. 26 illustrates a structure in which the transistor **101**, the transistor **102**, the transistor **103**, and the transistor **104** in FIG. 1 are replaced with a transistor **101p**, a transistor **102p**, a transistor **103p**, and a transistor **104p**, respectively. The transistors **101p**, **102p**, **103p**, and **104p** are p-channel transistors. Furthermore, also in a con-

figuration other than the configuration in FIG. 1, an n-channel transistor may be replaced with a p-channel transistor as in the configuration in FIG. 26.

[0078] Note that description is made on the assumption that the transistors **101**, **102**, and **103** are n-channel transistors for convenience.

[0079] Functions of the transistors **101**, **102**, **103**, and **104**, and the capacitors **105** and **106** are described. Note that one embodiment of the present invention is not limited to the functions described below.

[0080] The transistor **101** controls conduction and non-conduction between the wiring **111** and the wiring **112**. When the wiring **111** and the wiring **112** are brought into electrical contact, the potential of the wiring **111** is supplied to the wiring **112**, and the potential of the wiring **112** is controlled based on the potential of the wiring **111**. When the potential of the wiring **111** is at a high level, the potential of the wiring **112** is increased. In particular, when the potential of the node **ND1** is higher than the sum of the potential of the wiring **111** at a high level and the threshold voltage of the transistor **101**, the potential of the wiring **112** is increased to **VH**. When the potential of the wiring **111** is at a low level, the potential of the wiring **112** is decreased to **VL**.

[0081] The transistor **102** controls conduction and non-conduction between the wiring **113** and the node **ND1**. When the wiring **113** and the node **ND1** are brought into electrical contact, the potential of the wiring **113** is supplied to the node **ND1**, and the potential of the node **ND1** is controlled based on the potential of the wiring **113**. When the potential of the wiring **113** is at a high level, the potential of the node **ND1** is increased. In particular, when the potential of the node **ND2** is higher than the sum of the potential of the wiring **113** at a high level and the threshold voltage of the transistor **102**, the potential of the node **ND1** is increased to **VH**. Thus, the potential of the node **ND1** is set to a level at which the transistor **101** is turned on. When the potential of the wiring **113** is at a low level, the potential of the node **ND1** is decreased to **VL**. Consequently, the potential of the node **ND1** is set to a level at which the transistor **101** is turned off.

[0082] The transistor **103** controls conduction and non-conduction between the wiring **114** and the node **ND2**. When the wiring **114** and the node **ND2** are brought into electrical contact, the potential of the wiring **114** is supplied to the node **ND2**, and the potential of the node **ND2** is controlled based on the potential of the wiring **114**. When the potential of the wiring **114** is at a high level, the potential of the node **ND2** is increased. However, since the gate of the transistor **103** is connected to the wiring **114**, when the potential of the node **ND2** is increased to a value obtained by subtracting the threshold voltage of the transistor **103** from the potential of the wiring **114** at a high level, the transistor **103** is turned off. Thus, the node **ND2** is brought into a floating state. In this manner, the potential of the node **ND2** is set to a level at which the transistor **102** is turned on, and the node **ND2** is brought into a floating state. Furthermore, when the potential of the wiring **114** is at a low level, the transistor **103** is turned off, leading to non-conduction between the wiring **114** and the node **ND2**.

[0083] Note that as illustrated in FIG. 2A, a first terminal and the gate of the transistor **103** may be connected to a wiring **116** and the wiring **114**, respectively. The potential of the wiring **116** is preferably **VH**. Note that the potential of the wiring **116** can have a high level and a low level. In FIG. 2A, the transistor **103** controls conduction and non-conduction

between the wiring 116 and the node ND2. When the wiring 116 and the node ND2 are brought into electrical contact, the potential of the wiring 116 is supplied to the node ND2, and the potential of the node ND2 is controlled based on the potential of the wiring 116. When the potential of the wiring 116 is VH or at a high level, the potential of the node ND2 is increased. However, since the gate of the transistor 103 is connected to the wiring 114, when the potential of the node ND2 is increased to a value obtained by subtracting the threshold voltage of the transistor 103 from the potential of the wiring 114 at a high level, the transistor 103 is turned off. Thus, the node ND2 is brought into a floating state. In this manner, the potential of the node ND2 is set to a level at which the transistor 102 is turned on, and the node ND2 is brought into a floating state.

[0084] Note that as illustrated in FIG. 2B, the first terminal and the gate of the transistor 103 may be connected to the wiring 114 and the wiring 116, respectively. In FIG. 2B, the transistor 103 controls conduction and non-conduction between the wiring 114 and the node ND2. When the wiring 114 and the node ND2 are brought into electrical contact, the potential of the wiring 114 is supplied to the node ND2, and the potential of the node ND2 is controlled based on the potential of the wiring 114. When the potential of the wiring 114 is at a high level, the potential of the node ND2 is increased. However, since the gate of the transistor 103 is connected to the wiring 116, when the potential of the node ND2 is increased to a value obtained by subtracting the threshold voltage of the transistor 103 from the potential of the wiring 116, the transistor 103 is turned off. Thus, the node ND2 is brought into a floating state. In this manner, the potential of the node ND2 is set to a level at which the transistor 102 is turned on, and the node ND2 is brought into a floating state. When the potential of the wiring 114 is at a low level, the potential of the node ND2 is decreased to VL. Thus, the potential of the node ND2 is set to a level at which the transistor 102 is turned off.

[0085] Note that as illustrated in FIG. 3A, the first terminal and the gate of the transistor 103 may be connected to the wiring 113. In FIG. 3A, the transistor 103 controls conduction and non-conduction between the wiring 113 and the node ND2. When the wiring 113 and the node ND2 are brought into electrical contact, the potential of the wiring 113 is supplied to the node ND2, and the potential of the node ND2 is controlled based on the potential of the wiring 113. When the potential of the wiring 113 is at a high level, the potential of the node ND2 is increased. However, since the gate of the transistor 103 is connected to the wiring 113, when the potential of the node ND2 is increased to a value obtained by subtracting the threshold voltage of the transistor 103 from the potential of the wiring 113 at a high level, the transistor 103 is turned off. Thus, the node ND2 is brought into a floating state. In this manner, the potential of the node ND2 is set to a level at which the transistor 102 is turned on, and the node ND2 is brought into a floating state. Furthermore, when the potential of the wiring 113 is at a low level, the transistor 104 is turned off, leading to non-conduction between the wiring 113 and the node ND2.

[0086] Note that as illustrated in FIG. 3B, the first terminal and the gate of the transistor 103 may be connected to the wiring 116 and the wiring 113, respectively. In FIG. 3B, the transistor 103 controls conduction and non-conduction between the wiring 116 and the node ND2. When the wiring 116 and the node ND2 are brought into electrical contact,

potential of the wiring 116 is supplied to the node ND2, and the potential of the node ND2 is controlled based on the potential of the wiring 116. When the potential of the wiring 116 is at VH or a high level, the potential of the node ND2 is increased. However, since the gate of the transistor 103 is connected to the wiring 113, when the potential of the node ND2 is increased to a value obtained by subtracting the threshold voltage of the transistor 103 from the potential of the wiring 113 at a high level, the transistor 103 is turned off. Thus, the node ND2 is brought into a floating state. In this manner, the potential of the node ND2 is set to a level at which the transistor 102 is turned on, and the node ND2 is brought into a floating state.

[0087] Note that although not illustrated, the first terminal and the gate of the transistor 103 may be connected to the wiring 114 and the wiring 113, respectively.

[0088] Note that although not illustrated, the first terminal and the gate of the transistor 103 may be connected to the wiring 113 and the wiring 116, respectively.

[0089] The transistor 104 controls conduction and non-conduction between the wiring 115 and the node ND2. When the wiring 115 and the node ND2 are brought into electrical contact, the potential of the wiring 115 is supplied to the node ND2, and the potential of the node ND2 is controlled based on the potential of the wiring 115. When the potential of the wiring 115 is at VL or a low level, the potential of the node ND2 is decreased to VL. Thus, the potential of the node ND2 is set to a level at which the transistor 102 is turned off.

[0090] Note that as illustrated in FIG. 4A, the first terminal of the transistor 104 may be connected to the wiring 113. In FIG. 4A, the transistor 104 controls conduction and non-conduction between the wiring 113 and the node ND2. When the wiring 113 and the node ND2 are brought into electrical contact, the potential of the wiring 113 is supplied to the node ND2, and the potential of the node ND2 is controlled based on the potential of the wiring 113. When the potential of the wiring 113 is at VL or a low level, the potential of the node ND2 is decreased to VL. Thus, the potential of the node ND2 is set to a level at which the transistor 102 is turned off.

[0091] Note that as illustrated in FIG. 4B, the first terminal of the transistor 104 may be connected to the wiring 114. In FIG. 4B, the transistor 104 controls conduction and non-conduction between the wiring 114 and the node ND2. When the wiring 114 and the node ND2 are brought into electrical contact, the potential of the wiring 114 is supplied to the node ND2, and the potential of the node ND2 is controlled based on the potential of the wiring 114. When the potential of the wiring 114 is at VL or a low level, the potential of the node ND2 is decreased to VL. Thus, the potential of the node ND2 is set to a level at which the transistor 102 is turned off.

[0092] Note that as illustrated in FIG. 5A, the gate of the transistor 104 may be connected to the wiring 111.

[0093] Note that as illustrated in FIG. 5B, the gate of the transistor 104 may be connected to the wiring 112.

[0094] The capacitor 105 holds a potential difference between the wiring 112 and the node ND1. When the node ND1 is in a floating state, the potential of the node ND1 is changed based on a change in the potential of the wiring 112. Accordingly, when the potential of the node ND1 is increased in accordance with the increase in the potential of the wiring 112, the potential of the node ND1 can become higher than the sum of the potential of the wiring 111 at a high level and the threshold voltage of the transistor 101.

[0095] Note that as illustrated in FIG. 6A, the capacitor 105 may be omitted. The potential difference between the wiring 112 and the node ND1 is held by parasitic capacitance between the second terminal and the gate of the transistor 101.

[0096] The capacitor 106 holds a potential difference between the node ND1 and the node ND2. When the node ND2 is in a floating state, the potential of the node ND2 is changed based on a change in the potential of the node ND1. Accordingly, when the potential of the node ND2 is increased in accordance with the increase in the potential of the node ND1, the potential of the node ND2 can become higher than the sum of the potential of the wiring 113 at a high level and the threshold voltage of the transistor 102.

[0097] Note that as illustrated in FIG. 6B, the capacitor 106 may be omitted. The potential difference between the node ND1 and the node ND2 is held by parasitic capacitance between the second terminal and the gate of the transistor 102.

[0098] Note that the transistors 101, 102, 103, and 104, and the capacitors 105 and 106 do not necessarily have all the functions described above.

[0099] Note that the configurations of the circuit 100 described with reference to FIG. 1, FIGS. 2A and 2B, FIGS. 3A and 3B, FIGS. 4A and 4B, FIGS. 5A and 5B, FIGS. 6A and 6B, and the like; and a configuration of the circuit 100 described without a drawing can be combined as appropriate.

[0100] Operation of the semiconductor device in this embodiment is described using the configuration in FIG. 1 as an example. Note that one embodiment of the present invention is not limited to the operation described below.

[0101] A timing chart in FIG. 7 shows, as an example, the potential of the wiring 111, the potential of the wiring 113, the potential of the wiring 114, on/off of the transistor 104, the potential of the node ND1, the potential of the node ND2, and the potential of the wiring 112.

[0102] For convenience's sake, four periods, that is, a period T1, a period T2, a period T3, and a period T4 are described separately. For example, one frame period has the periods T1 to T4.

[0103] Note that for convenience, in a period T0 just before the period T1, the potential of the wiring 111 is at a low level, the potential of the wiring 113 is at a low level, the potential of the wiring 114 is at a low level, the potential of the node ND1 is VL, the potential of the node ND2 is VL, and the potential of the wiring 112 is VL. Since the potential of the node ND1 is VL, the transistor 101 is off. Furthermore, since the potential of the node ND2 is VL, the transistor 102 is off.

[0104] The operation in the period T1 is described with reference to FIG. 8A. The potential of the wiring 111 is kept at a low level, the potential of the wiring 113 is kept at a low level, the potential of the wiring 114 is changed from a low level to a high level, and the transistor 104 is kept off.

[0105] The transistor 103 is turned on because the potential of the wiring 114 is set at a high level. Accordingly, the potential of the wiring 114 at a high level is supplied to the node ND2; therefore, the potential of the node ND2 is increased from VL.

[0106] After that, when the potential of the node ND2 is higher than the sum (VL+Vth102) of the potential of the first terminal of the transistor 102 (VL) and the threshold voltage of the transistor 102 (Vth102), the transistor 102 is turned on. Accordingly, the potential of the wiring 113 at a low level is supplied to the node ND1, and thus the potential of the node

ND1 is kept at VL. The transistor 101 is kept off because the potential of the node ND1 is kept at VL. Thus, the potential of the wiring 112 is kept at VL.

[0107] After that, when the potential of the node ND2 is increased to a value (VH-Vth103) obtained by subtracting the threshold voltage of the transistor 103 (Vth103) from the potential of the gate of the transistor 103 (VH), the transistor 103 is turned off. Thus, the node ND2 is brought into a floating state, and the potential of the node ND2 is kept at VH-Vth103.

[0108] Note that in FIG. 2A, since the first terminal of the transistor 103 is connected to the wiring 116, the potential of the wiring 116 (e.g. VH) is supplied to the node ND2.

[0109] The operation in the period T2 is described with reference to FIG. 8B. The potential of the wiring 111 is kept at a low level, the potential of the wiring 113 is changed from a low level to a high level, the potential of the wiring 114 is changed from a high level to a low level, and the transistor 104 is kept off.

[0110] Since the potential of the wiring 114 is set at a low level, the transistor 103 is kept off. Accordingly, the node ND2 is kept in a floating state, and thus the potential of the node ND2 is kept at VH-Vth103. Since the potential of the node ND2 is kept at VH-Vth103, the transistor 102 is kept on. Accordingly, the potential of the wiring 113 at a high level is supplied to the node ND1, and thus the potential of the node ND1 is increased from VL. At this time, the capacitor 106 holds a potential difference between the node ND1 and the node ND2, and the node ND2 is in a floating state. Accordingly, the potential of the node ND2 is increased from VH-Vth103 in accordance with the increase in the potential of the node ND1.

[0111] After that, when the potential of the node ND1 is higher than the sum (VL+Vth101) of the potential of the first terminal of the transistor 101 (VL) and the threshold voltage of the transistor 101 (Vth101), the transistor 101 is turned on. Accordingly, the potential of the wiring 111 at a low level is supplied to the wiring 112, and thus the potential of the wiring 112 is kept at VL.

[0112] After that, when the potential of the node ND2 is increased to a level (VH+Vth102+ $\alpha$ ) ( $\alpha$  is a positive number) higher than the sum of the potential of the first terminal of the transistor 102 (VH) and the threshold voltage of the transistor 102 (Vth102) in accordance with the increase in the potential of the node ND1, the potential of the node ND1 is increased to VH.

[0113] Note that in FIG. 2B, it is preferable that the potential of the wiring 114 be kept at a high level in the period T2 in order to keep the transistor 103 off.

[0114] Note that in FIGS. 3A and 3B, the transistor 103 is turned on in the period T2 for the first time after the period T0. Specifically, when the potential of the wiring 113 is set at a high level, the transistor 103 is turned on. Accordingly, in FIG. 3A, the potential of the wiring 113 at a high level is supplied to the node ND2, and thus the potential of the node ND2 is increased from VL. On the other hand, in FIG. 3B, the potential of the wiring 116 (e.g. VH) is supplied to the node ND2, and thus the potential of the node ND2 is increased from VL. After that, when the potential of the node ND2 is higher than VL+Vth102, the transistor 102 is turned on. Accordingly, the potential of the wiring 113 at a high level is supplied to the node ND1, and thus the potential of the node ND1 is increased from VL. After that, when the potential of the node ND2 is set at VH-Vth103, the transistor 103 is

turned off, and thus the node ND2 is brought into a floating state. At this time, the potential of the node ND1 is increased. The capacitor 106 holds a potential difference between the node ND1 and the node ND2. Accordingly, the potential of the node ND2 is increased from VH-Vth103 in accordance with the increase in the potential of the node ND1. After that, when the potential of the node ND1 is higher than VL+Vth101, the transistor 101 is turned on. Accordingly, the potential of the wiring 111 at a low level is supplied to the wiring 112, and thus the potential of the wiring 112 is kept at VL. After that, when the potential of the node ND2 is increased to VH+Vth102+ $\alpha$  in accordance with the increase in the potential of the node ND1, the potential of the node ND1 is increased to VH. As described above, in FIGS. 3A and 3B, the operation in the periods T1 and T2 of FIG. 1 can be collectively performed in the period T2. Consequently, the operation speed can be improved.

[0115] The operation in the period T3 is described with reference to FIG. 9A. The potential of the wiring 111 is changed from a low level to a high level, the potential of the wiring 113 is changed from a high level to a low level, the potential of the wiring 114 is kept at a low level, and the transistor 104 is changed from an off state to an on state.

[0116] Since the potential of the wiring 114 is kept at a low level, the transistor 103 is kept off. The transistor 104 is turned on. Accordingly, the potential of the wiring 115 is supplied to the node ND2, and thus the potential of the node ND2 is decreased from VH+Vth102+ $\alpha$  to VL. Since the potential of the node ND2 is set at VL, the transistor 102 is turned off. Thus, the node ND1 is brought into a floating state, and the potential of the node ND1 is kept at VH. Since the potential of the node ND1 is kept at VH, the transistor 101 is kept on. Accordingly, the potential of the wiring 111 at a high level is supplied to the wiring 112, and thus the potential of the wiring 112 is increased from VL. At this time, the capacitor 105 holds a potential difference between the wiring 112 and the node ND1, and the node ND1 is in a floating state. Thus, the potential of the node ND1 is increased from VH in accordance with the increase in the potential of the wiring 112.

[0117] After that, when the potential of the node ND1 is increased to a level (VH+Vth101+ $\beta$  ( $\beta$  is a positive number)) higher than the sum of the potential of the first terminal of the transistor 101 (VH) and the threshold voltage of the transistor 101 (Vth101) in accordance with the increase in the potential of the wiring 112, the potential of the wiring 112 is increased to VH.

[0118] Note that in FIG. 4A, since the first terminal of the transistor 104 is connected to the wiring 113, the potential of the wiring 113 at a low level is supplied to the node ND2. Furthermore, in FIG. 4B, since the first terminal of the transistor 104 is connected to the wiring 114, the potential of the wiring 114 at a low level is supplied to the node ND2.

[0119] The operation in the period T4 is described with reference to FIG. 9B. The potential of the wiring 111 is changed from a high level to a low level, the potential of the wiring 113 is kept at a low level, the potential of the wiring 114 is changed from a low level to a high level, and the transistor 104 is changed from on to off.

[0120] Since the potential of the wiring 114 is set at a high level, the transistor 103 is turned on. Accordingly, the potential of the wiring 114 at a high level is supplied to the node ND2, and thus the potential of the node ND2 is increased. At this time, the potential of the node ND1 is VH+Vth101+ $\beta$ , and accordingly the transistor 101 is kept on. Accordingly, the

potential of the wiring 111 at a low level is supplied to the wiring 112, and thus the potential of the wiring 112 is decreased from VH to VL.

[0121] After that, when the potential of the node ND2 is higher than the sum of the potential of the first terminal of the transistor 102 (VL) and the threshold voltage of the transistor 102 (Vth102), the transistor 102 is turned on. Accordingly, the potential of the wiring 113 at a low level is supplied to the node ND1, and thus the potential of the node ND1 is decreased from VH+Vth101+ $\beta$  to VL. The transistor 101 is turned off because the potential of the node ND1 is set at VL.

[0122] After that, when the potential of the node ND2 is increased to a level obtained by subtracting the threshold voltage of the transistor 103 (Vth103) from the potential of the gate of the transistor 103 (VH), the transistor 103 is turned off. Thus, the node ND2 is brought into a floating state, and the potential of the node ND2 is kept at VH-Vth103.

[0123] Note that since the first terminal of the transistor 103 is connected to the wiring 116 in FIG. 2A, the potential of the wiring 116 (e.g. VH) is supplied to the node ND2.

[0124] The semiconductor device in this embodiment has connection relations which enable the above operation, whereby the potential of the node ND2 can be set at VH+Vth102+ $\alpha$ .

[0125] In the semiconductor device in this embodiment, the potential of the node ND2 is set at VH+Vth102+ $\alpha$ , whereby a potential difference between the gate and the source of the transistor 102 can be kept at a level higher than the threshold voltage of the transistor 102.

[0126] In the semiconductor device in this embodiment, the potential difference between the gate and the source of the transistor 102 is kept at a level higher than the threshold voltage of the transistor 102, whereby the potential of the node ND1 can be increased to VH.

[0127] In the semiconductor device in this embodiment, the potential difference between the gate and the source of the transistor 102 is kept at a level higher than the threshold voltage of the transistor 102, whereby the time required for change in the potential of the node ND1 can be shortened.

[0128] In the semiconductor device in this embodiment, the potential of the node ND1 is increased to VH, whereby the potential difference between the gate and the source of the transistor 101 can be made large.

[0129] In the semiconductor device in this embodiment, the potential difference between the gate and the source of the transistor 101 is made large, whereby the time required for change in the potential of the wiring 112 can be shortened. That is, a signal whose rise time and the fall time are short can be output to the wiring 112.

[0130] In the semiconductor device in this embodiment, the potential difference between the gate and the source of each of the transistors 101 and 102 is made large, whereby a driving voltage can be made low. This reduces the power consumption.

[0131] In the semiconductor device in this embodiment, the potential differences between the gates and the sources of the transistors 101 and 102 are made large, whereby the channel width of each of the transistors 101 and 102 can be made small. Thus, the layout area can be decreased.

[0132] Since the time required for change in the potential of the node ND1 and the time required for change in the potential of the wiring 112 can be shortened in the semiconductor device in this embodiment, the operation speed can be improved.

[0133] W/L (W is the channel width and L is the channel length) of each of the transistors **101**, **102**, **103**, and **104** is described. Note that one embodiment of the present invention is not limited to the W/L described below.

[0134] The transistor **101** drives a potential of the wiring **112**, the transistor **102** drives a potential of the node **ND1**, and the transistors **103** and **104** drive a potential of the node **ND2**. The load of the wiring **112** is often larger than any of the loads of the node **ND1** and the node **ND2**. Therefore, W/L of the transistor **101** is preferably larger than that of the transistors **102**, **103**, and **104**. Alternatively, the W/L of the transistor **101** is preferably the largest among the transistors included in the circuit **100**. Further alternatively, the W/L of the transistor **101** is preferably the largest among transistors provided over the same substrate as the circuit **100**. Note that a transistor whose W/L is the same or substantially the same as that of the transistor **101** may be provided. In this manner, the drive capability of the transistor **101** can be improved, which enables the load of the wiring **112** to be made large. Furthermore, the transistors **102**, **103**, and **104** can be downsized, leading to reduction in a layout area.

[0135] Even when the potential of the node **ND1** is increased, the potential difference between the gate and the source of the transistor **102** can be kept at a level of greater than or equal to the threshold voltage of the transistor **102**, and thus the W/L of the transistor **102** can be made low. On the other hand, when the potential of the node **ND2** is increased, a potential difference between the gate and the source of the transistor **103** is decreased gradually; therefore, the W/L of the transistor **103** is preferably high. Therefore, the W/L of the transistor **103** is preferably higher than that of the transistor **102**. In this manner, the drive capability of the transistor **103** can be improved, and thus the time required for change in the potential of the node **ND2** can be shortened. Furthermore, reduction in size of the transistor **102** can be achieved, leading to reduction in a layout area. But it is also possible to make the W/L of the transistor **102** higher than that of the transistor **103**.

[0136] A transistor which can be additionally included in any of the configurations of the circuit **100** described with reference to FIG. 1, FIGS. 2A and 2B, FIGS. 3A and 3B, FIGS. 4A and 4B, FIGS. 5A and 5B, and FIGS. 6A and 6B; the configuration of the circuit **100** described without a drawing; and a configuration obtained by combining them is described. Note that one embodiment of the present invention is not limited to a configuration described below.

[0137] A transistor **107** may be additionally included in any of the above configurations of the circuit **100**. FIG. 10A illustrates a case where the transistor **107** is additionally included in the circuit **100** in FIG. 1. A first terminal and a second terminal of the transistor **107** are connected to a wiring **115B** and the wiring **112**, respectively. The potential of the wiring **115B** is preferably **VL**. Note that the potential of the wiring **115B** may have a high level and a low level. The transistor **107** controls conduction and non-conduction between the wiring **115B** and the wiring **112**. When the transistor **107** is turned on, the wiring **115B** and the wiring **112** are brought into electrical contact, and the potential of the wiring **112** is controlled based on the potential of the wiring **115B**. When the potential of the wiring **115B** is **VL** or at a low level, the potential of the wiring **112** is **VL**. Furthermore, the transistor **107** preferably has the same polarity as the transistors **101** to **104**.

[0138] In the period **T1**, the transistor **107** is turned on. Accordingly, the potential of the wiring **115B** is supplied to the wiring **112**, and thus the potential of the wiring **112** is set at **VL**. Note that in the period **T1**, the transistor **107** may be off.

[0139] In the period **T2**, the transistor **107** is turned on. Accordingly, the potential of the wiring **115B** is supplied to the wiring **112**, and thus the potential of the wiring **112** is set at **VL**. Note that in the period **T2**, the transistor **107** may be off.

[0140] In the period **T3**, the transistor **107** is turned off.

[0141] In the period **T4**, the transistor **107** is turned on. Accordingly, the potential of the wiring **115B** is supplied to the wiring **112**, and thus the potential of the wiring **112** is set at **VL**. Note that in the period **T4**, the transistor **107** may be off.

[0142] In FIG. 10A, the circuit **100** includes the transistor **107**, whereby the wiring **112** is prevented from being brought into a floating state, which can stabilize the potential of the wiring **112**. Accordingly, malfunctions can be prevented.

[0143] Note that the first terminal of the transistor **107** may be connected to the wiring **111**, **113**, **114**, or **115**. A gate of the transistor **107** may be connected to the wiring **113** or **114**.

[0144] A transistor **108** may be additionally included in the circuit **100** having any of the above configurations. FIG. 10B illustrates a case where the transistor **108** is additionally included in the circuit **100** in FIG. 1. A first terminal and a second terminal of the transistor **108** are connected to a wiring **115C** and the node **ND1**, respectively. The potential of the wiring **115C** is preferably **VL**. Note that the potential of the wiring **115C** may have a high level and a low level. The transistor **108** controls conduction and non-conduction between the wiring **115C** and the node **ND1**. When the transistor **108** is turned on, the wiring **115C** and the node **ND1** are brought into electrical contact, and the potential of the node **ND1** is controlled based on the potential of the wiring **115C**. When the potential of the wiring **115C** is **VL** or at a low level, the potential of the node **ND1** is set at **VL**. Thus, the potential of the node **ND1** is set to a level at which the transistor **101** is turned off. Furthermore, the transistor **108** preferably has the same polarity as the transistors **101** to **104**.

[0145] In the period **T1**, the transistor **108** is turned on. Accordingly, the potential of the wiring **115C** is supplied to the node **ND1**, and thus the potential of the node **ND1** is set at **VL**. Note that in the period **T1**, the transistor **108** may be off.

[0146] In the period **T2**, the transistor **108** is turned off.

[0147] In the period **T3**, the transistor **108** is turned off.

[0148] In the period **T4**, the transistor **108** is turned on. Accordingly, the potential of the wiring **115C** is supplied to the node **ND1**, and thus the potential of the node **ND1** is set at **VL**. Note that in the period **T4**, the transistor **108** may be off.

[0149] In FIG. 10B, the circuit **100** includes the transistor **108**, whereby the node **ND1** is prevented from being brought into a floating state, which can stabilize the potential of the node **ND1**. Accordingly, malfunctions can be prevented.

[0150] Note that the first terminal of the transistor **108** may be connected to the wirings **111**, **113**, **114**, or **115**. A gate of the transistor **108** may be connected to the wiring **114**.

[0151] Note that in the case where the transistors **107** and **108** are both additionally included in the circuit **100**, the gate of the transistor **107** may be connected to the gate of the transistor **108**. Alternatively, the first terminal of the transistor **107** may be connected to the first terminal of the transistor **108**.

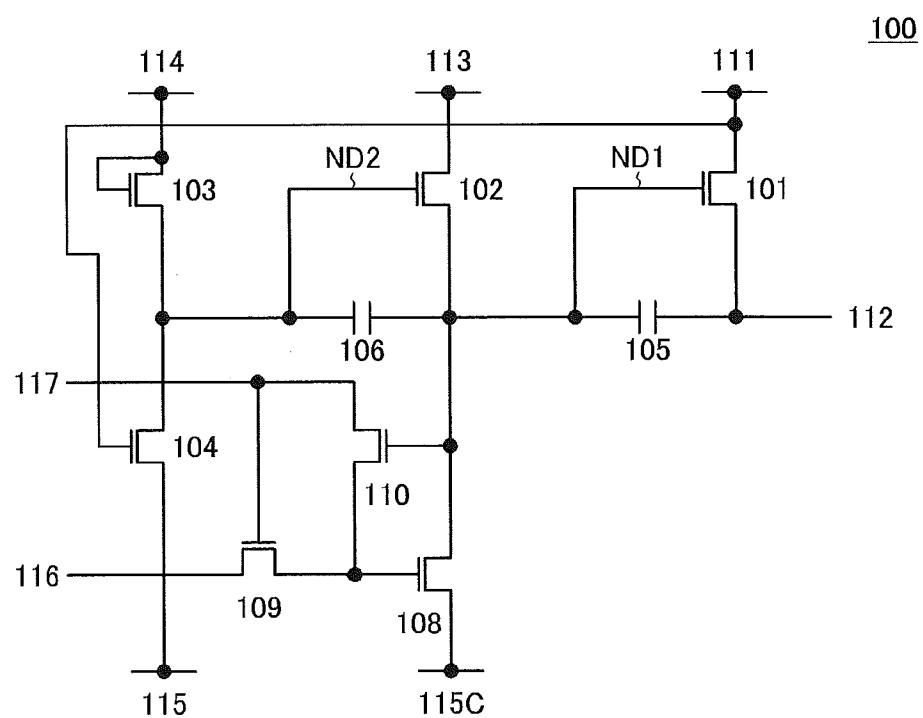

[0152] In the circuit 100 having any of the above configurations, the transistors 107 and/or 108 may be additionally included, and a transistor 109 and a transistor 110 may be additionally included. FIG. 11A illustrates a case where the transistors 109 and 110 are additionally included in addition to the transistors 107 and 108 in the circuit 100 illustrated in FIG. 1. The first terminal of the transistor 109 is connected to the wiring 116, the second terminal of the transistor 109 is connected to the gates of the transistors 107 and 108, and the gate of the transistor 109 is connected to the wiring 114. A first terminal, a second terminal, and a gate of the transistor 110 are connected to the wiring 114, the gates of the transistors 107 and 108, and the node ND1, respectively. Note that the gate of the transistor 107, the gate of the transistor 108, the second terminal of the transistor 109, or the second terminal of the transistor 110 is referred to as a node ND3. The transistor 109 controls conduction and non-conduction between the wiring 116 and the node ND3. When the transistor 109 is turned on, the wiring 116 and the node ND3 are brought into electrical contact, and the potential of the node ND3 is controlled based on the potential of the wiring 116. When the potential of the wiring 116 is VH or at a high level, the potential of the node ND3 is increased. However, since the gate of the transistor 109 is connected to the wiring 114, when the potential of the node ND3 is increased to a level obtained by subtracting the threshold voltage of the transistor 109 from the potential of the wiring 114 at a high level, the transistor 109 is turned off. Thus, the node ND3 is brought into a floating state. In this manner, the potential of the node ND3 is set to a level at which the transistor 107 or the transistor 108 is turned on, and the node ND3 is brought into a floating state. The transistor 110 controls conduction and non-conduction between the wiring 114 and the node ND3. When the transistor 110 is turned on, the wiring 114 and the node ND3 are brought into electrical contact, and the potential of the node ND3 is controlled based on the potential of the wiring 114. When the potential of the wiring 114 is at a low level, the potential of the node ND3 is decreased to VL. In this manner, the potential of the node ND3 is set to a level at which the transistor 107 or 108 is turned off. The transistors 109 and 110 preferably have the same polarity as the transistors 101 to 104.

[0153] Since the wiring 114 is set at a high level in the period T1, the transistor 109 is turned on. Since the potential of the node ND1 is set at VL, the transistor 110 is turned off. Accordingly, the potential of the wiring 116 is supplied to the node ND3, and thus the potential of the node ND3 is increased from VL. After that, when the potential of the node ND3 is higher than the sum of the potential of the first terminal of the transistor 107 (VL) and the threshold voltage of the transistor 107 (Vth107), the transistor 107 is turned on. Furthermore, when the potential of the node ND3 is higher than the sum of the potential of the first terminal of the transistor 108 (VL) and the threshold voltage of the transistor 108 (Vth108), the transistor 108 is turned on. After that, when the potential of the node ND3 is set to a level obtained by subtracting the threshold voltage of the transistor 109 (Vth109) from the potential of the gate of the transistor 109 (VH), the transistor 109 is turned off. Thus, the node ND3 is brought into a floating state, and the potential of the node ND3 is kept at VH-Vth109.

[0154] Since the potential of the wiring 114 is set at a low level in the period T2, the transistor 109 is turned off. Furthermore, when the potential of the node ND1 is higher than

the sum of the potential of the first terminal of the transistor 110 (VL) and the threshold voltage of the transistor 110 (Vth110), the transistor 110 is turned on. Accordingly, the potential of the wiring 114 at a low level is supplied to the node ND3, and thus the potential of the node ND3 is decreased from VH-Vth109 to VL. Accordingly, the transistors 107 and 108 are turned off.

[0155] Since the potential of the wiring 114 is kept at a low level in the period T3, the transistor 109 is kept off. Furthermore, since the potential of the node ND1 is set at VH+Vth110+β, the transistor 110 is kept on. Accordingly, the potential of the wiring 114 at a low level is supplied to the node ND3, and thus the potential of the node ND3 is kept at VL. Accordingly, the transistors 107 and 108 are kept off.

[0156] Since the potential of the wiring 114 is set at a high level in the period T4, the transistor 109 is turned on. Since the potential of the node ND1 is set at VL, the transistor 110 is turned off. Accordingly, the potential of the wiring 116 is supplied to the node ND3, and thus the potential of the node ND3 is increased from VL. After that, when the potential of the node ND3 is higher than the sum of the potential of the first terminal of the transistor 107 (VL) and the threshold voltage of the transistor 107 (Vth107), the transistor 107 is turned on. Furthermore, when the potential of the node ND3 is higher than the sum of the potential of the first terminal of the transistor 108 (VL) and the threshold voltage of the transistor 108 (Vth108), the transistor 108 is turned on.

[0157] In FIG. 11A, the circuit 100 includes the transistors 109 and 110, whereby a signal for controlling the transistors 107 or 108 can be generated in the circuit 100. Accordingly, the number of signals can be reduced.

[0158] Note that as illustrated in FIG. 11B, the gate of the transistor 109 and the first terminal of the transistor 110 may be connected to a wiring 117. The potential of the wiring 117 has a high level (e.g. VH) and a low level (e.g. VL).

[0159] Note that the gate of the transistor 109 may be connected to the wiring 117, and the first terminal of the transistor 110 may be connected to the wiring 114. Alternatively, the gate of the transistor 109 may be connected to the wiring 114, and the first terminal of the transistor 110 may be connected to the wiring 117.

[0160] Note that a configuration in which the second terminals of the transistors 109 and 110 are connected to the gate of the transistor 107 and are not connected to the gate of the transistor 108 may be employed. Alternatively, a configuration in which the second terminals of the transistors 109 and 110 are connected to the gate of the transistor 108 and are not connected to the gate of the transistor 107 may be employed.

[0161] Note that the first terminal of the transistor 110 may be connected to the wirings 115, 115B, 115C, or 117.

[0162] In the circuit 100 having any of the above configurations, a transistor 121 may be additionally included. FIG. 12A illustrates a case where the transistor 121 is additionally included in the circuit 100 in FIG. 1. A first terminal, a second terminal, and a gate of the transistor 121 are connected to the wiring 112, the node ND1, and the wiring 111, respectively. The transistor 121 controls conduction and non-conduction between the wiring 112 and the node ND1. When the transistor 121 is turned on, the wiring 112 and the node ND1 are brought into electrical contact. For example, in the case where the potential of the wiring 112 is increased from VL and the potential of the node ND1 is increased from VH as in the period T3, an increase in the potential of the node ND1 is suppressed, and the time required for change in the potential

of the wiring 112 is shortened. Note that since the gate of the transistor 121 is connected to the wiring 111, when the potential of the wiring 112 is set to a level obtained by subtracting the threshold voltage of the transistor 121 from the potential of the wiring 111 at a high level, the transistor 121 is turned off. The transistor 121 preferably has the same polarity as the transistors 101 to 104.

[0163] In the period T1, the wiring 111 is at a low level, and thus the transistor 121 is turned off.

[0164] In the period T2, the wiring 111 is at a low level, and thus the transistor 121 is turned off.

[0165] In the period T3, the wiring 111 is set at a high level, and thus the transistor 121 is turned on. Note that when the potential of the wiring 112 is increased to a level obtained by subtracting the threshold voltage of the transistor 121 (V<sub>th</sub> 121) from the potential of the gate of the transistor 121 (V<sub>H</sub>), the transistor 121 is turned off.

[0166] Since the wiring 111 is set at a low level in the period T4, the transistor 121 is turned off.

[0167] In FIG. 12A, the circuit 100 includes the transistor 121, whereby the potential of the node ND1 can be prevented from being too high. Thus, deterioration of the transistor connected to the node ND1 can be suppressed, and damage of the transistor can be prevented, for example.

[0168] In the circuit 100 having any of the above configurations, a transistor 122 may be additionally included. FIG. 12B illustrates a case where the transistor 122 is additionally included in the circuit 100 in FIG. 1. A first terminal, a second terminal, and a gate of the transistor 122 are connected to the node ND1, the node ND2, and the wiring 113, respectively. The transistor 122 controls conduction and non-conduction between the node ND1 and the node ND2. When the transistor 122 is turned on, the node ND1 and the node ND2 are brought into electrical contact. For example, in the case where the potential of the node ND1 is increased from VL and the potential of the node ND2 is increased from VH-V<sub>th</sub>103 as in the period T2, an increase in the potential of the node ND2 is suppressed, and the time required for change in the potential of the node ND1 is shortened. Note that since the gate of the transistor 122 is connected to the wiring 113, when the potential of the node ND1 is set to a level obtained by subtracting the threshold voltage of the transistor 122 from the potential of the wiring 113 at a high level, the transistor 122 is turned off. The transistor 122 preferably has the same polarity as the transistors 101 to 104.