(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-39829

(P2005-39829A)

(43) 公開日 平成17年2月10日(2005.2.10)

(51) Int.C1.<sup>7</sup>

**H03K 5/00**

**G02F 1/133**

**G09G 3/20**

**G09G 3/36**

F 1

H03K 5/00

G02F 1/133 505

G09G 3/20 611C

G09G 3/20 612K

G09G 3/36

テーマコード(参考)

2H093

5C006

5C080

審査請求 未請求 請求項の数 24 O L (全 17 頁)

(21) 出願番号 特願2004-207325 (P2004-207325)

(22) 出願日 平成16年7月14日 (2004.7.14)

(31) 優先権主張番号 2003-047759

(32) 優先日 平成15年7月14日 (2003.7.14)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 390019839

三星電子株式会社

大韓民国京畿道水原市靈通区梅灘洞416

(74) 代理人 100094145

弁理士 小野 由己男

(74) 代理人 100106367

弁理士 稲積 朋子

(72) 発明者 権 秀 現

大韓民国京畿道水原市八達区梅灘3洞12

69-2番地202号

Fターム(参考) 2H093 NA16 NC21 NC34 NC35 NC49

ND34 ND39 ND40 ND60 NH16

5C006 AA16 AA22 AC27 AC28 AF51

AF72 AF83 BB16 BC12 BC16

BF07 BF43 FA16 FA32 FA52

最終頁に続く

(54) 【発明の名称】信号処理装置及び方法

## (57) 【要約】

**【課題】** VCOやPLL回路を使用せず、クロック変調によってEMIが減少された信号処理装置、及びEMIを低減させる信号処理方法と該信号処理装置を含む表示装置を提供することにある。

**【解決手段】** メインクロックを変調する信号処理装置に関し、この信号処理装置は、メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロック、そしてメインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックを生成する遅延手段を含むクロック生成部、第1の遅延クロックを受けて入力信号を処理する第1の処理ブロック、そして第2の遅延クロックを受けて入力信号を処理する第2の処理ブロックを含む。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

メインクロックを変調する信号処理装置であって、

前記メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロックと前記メインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックとを生成する遅延手段を含むクロック生成部と、

前記第1の遅延クロックを受けて入力信号を処理する第1の処理ブロックと、

前記第2の遅延クロックを受けて入力信号を処理する第2の処理ブロックと、を含む信号処理装置。

**【請求項 2】**

前記第1の処理ブロックの第1の出力信号が前記第2の処理ブロックに入力され、

前記第1の出力信号がタイミングの余裕をもって前記第2の処理ブロックで前記第2の遅延クロックに同期され処理されるように、前記第1の遅延時間が前記第2の遅延時間よりも大きい、請求項1に記載の信号処理装置。

**【請求項 3】**

前記遅延手段は複数のトランジスタを備えた遅延回路を含む、請求項1または請求項2に記載の信号処理装置。

**【請求項 4】**

前記第2の処理ブロックの第2の出力信号が前記信号処理装置の出力信号であり、前記第2の遅延時間は0である、請求項1または請求項2に記載の信号処理装置。

**【請求項 5】**

請求項1の信号処理装置を含む表示装置。

**【請求項 6】**

前記表示装置は、液晶表示装置、プラズマ表示装置、有機EL表示装置のうちのいずれか1つである、請求項5に記載の表示装置。

**【請求項 7】**

メインクロックを変調する信号処理装置における信号処理方法であって、

前記メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロックを生成する段階と、

前記第1の遅延クロックを受けて入力信号を処理して第1の出力信号を生成する段階と

、前記メインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックを生成する段階と、

前記第2の遅延クロックを受けて入力信号を処理して第2の出力信号を生成する段階と

、を含む信号処理方法。

**【請求項 8】**

前記第2の出力信号を生成する段階の入力信号は前記第1の出力信号であり、

前記第1の出力信号がタイミングの余裕をもって前記第2の遅延クロックに同期して処理されるように前記第1の遅延時間が前記第2の遅延時間よりも大きい、請求項7に記載の信号処理方法。

**【請求項 9】**

前記信号処理装置が複数のトランジスタを含む遅延回路を備えた、請求項7または請求項8に記載の信号処理方法。

**【請求項 10】**

前記第2の出力信号が前記信号処理装置の出力信号であり、

前記第2の遅延時間は0である、請求項7または請求項8に記載の信号処理方法。

**【請求項 11】**

メインクロックを変調する信号処理装置であって、

前記メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロックを生成する

10

20

40

50

遅延手段を含み、前記メインクロックと前記第1の遅延クロックに基づいて複数の周波数成分を含む合成クロックを生成するクロック生成部と、

前記合成クロックを受けて入力信号を処理する処理ブロックと、

を備え、前記合成クロックは、前記メインクロックの上昇エッジに同期する第1のクロックと、前記第1の遅延クロックの上昇エッジに同期する第2のクロックを含む信号処理装置。

#### 【請求項12】

前記合成クロックは、前記2つのクロックに続けて生成され、前記メインクロックの上昇エッジに同期し、前記メインクロックの1クロックの時間間隔と実質的に同じである時間間隔であるような第3のクロックを含む、請求項11に記載の信号処理装置。

10

#### 【請求項13】

前記第1の遅延時間は、前記合成クロックが前記信号処理装置が許容するクロックになる範囲で決められる、請求項11または請求項12に記載の信号処理装置。

#### 【請求項14】

前記遅延手段は前記メインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックを生成し、

前記クロック生成部は前記第2の遅延クロックにさらに基づいて前記合成クロックを生成し、

前記合成クロックは他の2つのクロックのうちの第1のクロックが前記メインクロックの上昇エッジに同期し、第2のクロックが前記第2の遅延クロックの上昇エッジに同期する、請求項11または請求項12に記載の信号処理装置。

20

#### 【請求項15】

前記第1の遅延時間及び前記第2の遅延時間は、前記合成クロックが前記信号処理装置が許容するクロックになる範囲で決められる、請求項14に記載の信号処理装置。

#### 【請求項16】

前記遅延手段は、複数のトランジスタを有する遅延回路を含む、請求項11または請求項12に記載の信号処理装置。

#### 【請求項17】

請求項11の信号処理装置を含む表示装置。

#### 【請求項18】

前記表示装置は、液晶表示装置、プラズマ表示装置、有機EL表示装置のうちのいずれか1つである、請求項17に記載の表示装置。

30

#### 【請求項19】

メインクロックを変調する信号処理装置における信号処理方法であって、

前記メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロックを生成する段階と、

前記メインクロックと前記第1の遅延クロックに基づいて複数の周波数成分を含む合成クロックを生成する段階と、

前記合成クロックに基づいて入力信号を処理する段階と、

を含み、前記合成クロックは、前記メインクロックの上昇エッジに同期する第1のクロックと、前記第1の遅延クロックの上昇エッジに同期する第2のクロックとを含む、信号処理方法。

40

#### 【請求項20】

前記合成クロックは、前記2つのクロックに続けて生成され、前記メインクロックの上昇エッジに同期し、前記メインクロックの1クロックの時間間隔と実質的に同じである時間間隔であるような第3のクロックを含む、請求項19に記載の信号処理方法。

#### 【請求項21】

前記第1の遅延時間は、前記合成クロックが前記信号処理装置が許容するクロックになる範囲で決められる、請求項19または請求項20に記載の信号処理方法。

#### 【請求項22】

50

前記メインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックを生成する段階をさらに含み、

前記合成クロックは、前記第2の遅延クロックにさらに基づいて生成され、他の2つのクロックのうちの第1のクロックが前記メインクロックの上昇エッジに同期し、第2のクロックが前記第2の遅延クロックの上昇エッジに同期する、請求項19または請求項20に記載の信号処理方法。

#### 【請求項23】

前記第1の遅延時間及び前記第2の遅延時間は、前記合成クロックが前記信号処理装置が許容するクロックになる範囲で決められる、請求項22に記載の信号処理方法。

#### 【請求項24】

前記信号処理装置が複数のトランジスタを含む遅延回路を具備している、請求項19または請求項20に記載の信号処理方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、信号処理装置及び方法に関し、特に、クロック変調によってEMIが減少された信号処理装置、及びEMIを低減する信号処理方法と該信号処理装置を含む液晶表示装置に関する。

##### 【背景技術】

##### 【0002】

多数の電子装置は、同期化のためにクロック信号を要するマイクロプロセッサまたはデジタル回路を使用する。例えば、クロック信号は、マイクロプロセッサやデジタル回路で、イベント等の正確なタイミングを提供する。クロック信号を使用するマイクロプロセッサやデジタル回路などで、EMIを生じさせ放射しやすく、特にシステムが高速化されるほどその傾向は強い。

##### 【0003】

EMIは、電磁波の一種であって導線に高周波の電流が流れる時に、導線周囲に電場と磁場が混在し、空気中に伝播される電子干渉現象である。EMIは、電子装置の誤動作を起こしたり、人体に害を及ぼすなど、磁界環境を悪化するので、これに対する規制が強化されており、各製造社もその規制に対応するために努力を続けている。

##### 【0004】

一方、通常の液晶表示装置(LCD)は、2つの表示板とその間に入っている誘電率異方性を有する液晶層を含む。液晶層に電界を印加し、この電界の強さを調節して液晶層を通過する光の透過率を調節することによって所望の画像が得られる。このような液晶表示装置は、携帯が簡便な平板表示装置(FPD)の代表的なものであり、その中でも薄膜トランジスタ(TFT)をスイッチング素子としえ利用したTFT-LCDが主に利用されている。

##### 【0005】

このような液晶表示装置でもクロックを使用する複数のデジタル回路を備えており、これらによって多量のデータを処理しているため、多量のEMIが発生しやすい。特に、解像度が向上するほど動作の周波数が増加し、EMIの放出量が増加する。

##### 【0006】

EMIは、フィルタリング、遮蔽、雑音カッピング経路の分離などによって低減できる。EMI低減のために、フィルタやバイパスコンデンサなどの部品が使用されたり、印刷回路基板の信号線の細心な経路の設定が要求される。また、EMIを低減させる方法として、VCOやPLL回路を利用してクロック周波数を変調する方法がある。しかし、このような方法は、製造コストを上昇させたり、多くの工学的な努力が要求される。

#### 【発明の開示】

#### 【発明が解決しようとする課題】

##### 【0007】

10

20

30

40

50

本発明が目的とする技術的課題は、VCOやPLL回路を使用せず、クロック変調によってEMIが減少された信号処理装置、及びEMIを低減させる信号処理方法と該信号処理装置を含む表示装置を提供することにある。

【課題を解決するための手段】

【0008】

このような技術的課題を解決するための本発明の一実施例による、メインクロックを変調する信号処理装置は、前記メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロック、そして前記メインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックを生成する遅延手段を含むクロック生成部、前記第1の遅延クロックを受けて入力信号を処理する第1の処理ブロック、そして前記第2の遅延クロックを受けて入力信号を処理する第2の処理ブロックを含む。

【0009】

前記第1の処理ブロックの第1の出力信号が前記第2の処理ブロックに入力され、前記第1の出力信号がタイミングの余裕をもって前記第2の処理ブロックで前記第2の遅延クロックに同期されて処理されるように、前記第1の遅延時間が前記第2の遅延時間よりも大きいのが好ましい。

【0010】

前記遅延手段は、複数のトランジスタを含む遅延回路であり得る。

【0011】

前記第2の処理ブロックの第2の出力信号が前記信号処理装置の出力信号であり、前記第2の遅延時間は0であり得る。

【0012】

本発明の他の実施例による表示装置は前記信号処理装置を含む。

【0013】

前記表示装置は、液晶表示装置、プラズマ表示装置、そして有機EL表示装置のうちのいずれか1つの表示装置であることができる。

【0014】

本発明の他の実施例によるメインクロックを変調する信号処理装置における信号処理方法は、前記メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロックを生成する段階、前記第1の遅延クロックを受けて入力信号を処理して第1の出力信号を生成する段階、前記メインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックを生成する段階、そして、前記第2の遅延クロックを受けて入力信号を処理して第2の出力信号を生成する段階を含む。

【0015】

前記第2の出力信号を生成する段階の入力信号は、前記第1の出力信号であり、前記第1の出力信号がタイミングの余裕をもって前記第2の遅延クロックに同期されて処理されるように、前記第1の遅延時間が前記第2の遅延時間よりも大きいのが好ましい。

【0016】

前記信号処理装置が複数のトランジスタを含む遅延回路を備えることができる。

【0017】

前記第2の出力信号が前記信号処理装置の出力信号であり、前記第2の遅延時間は0であり得る。

【0018】

本発明の他の実施例によるメインクロックを変調する信号処理装置は、前記メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロックを生成する遅延手段を含み、前記メインクロックと前記第1の遅延クロックに基づいて複数の周波数の成分を含む合成クロックを生成するクロック生成部、そして前記合成クロックを受けて入力信号を処理する処理ブロックを含み、前記合成クロックは、2つのクロックのうちの第1のクロックは前記メインクロックと前記第1の遅延クロックのうちのいずれか一方の上昇エッジに同期し、第2のクロックはもう一方の上昇エッジに同期する。

10

20

30

40

50

## 【0019】

前記合成クロックは、前記2つのクロックに続く第3のクロックが前記第1のクロックの上昇エッジに同期し、前記第3のクロックの周期は前記メインクロックの周期と実質的に同じであることができる。

## 【0020】

前記遅延手段は、前記メインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックを生成し、前記クロック生成部は、前記第2の遅延クロックにさらに基づいて前記合成クロックを生成し、前記合成クロックは、その他の2つのクロックのうちの第1のクロックが前記メインクロックと前記第2の遅延クロックのうちのいずれか一方の上昇エッジに同期し、第2のクロックがもう一方の上昇エッジに同期することができる。

10

## 【0021】

前記第1の遅延時間の最大値は、前記合成クロックが前記信号処理装置が許容するクロックになる範囲で決められるのが好ましい。

## 【0022】

前記第1の遅延時間及び前記第2の遅延時間の最大値は、前記合成クロックが前記信号処理装置が許容するクロックになる範囲で決められるのが好ましい。

## 【0023】

前記遅延手段は、複数のトランジスタを含む遅延回路であることができる。

## 【0024】

本発明の他の実施例による表示装置は前記信号処理装置を含む。

20

## 【0025】

本発明の他の実施例によるメインクロックを変調する信号処理装置における信号処理方法は、前記メインクロックを第1の遅延時間分だけ遅延させた第1の遅延クロックを生成する段階、前記メインクロックと前記第1の遅延クロックに基づいて複数の周波数の成分を含む合成クロックを生成する段階、そして、前記合成クロックに基づいて入力信号を処理する段階を含み、前記合成クロックは、2つのクロックのうちの第1のクロックが前記メインクロックと前記第1の遅延クロックのうちのいずれか一方の上昇エッジに同期し、第2のクロックがもう一方の上昇エッジに同期する。

## 【0026】

前記合成クロックは、前記2つのクロックに続く第3のクロックが前記第1のクロックの上昇エッジに同期し、前記第3のクロックの周期は前記メインクロックの周期と実質的に同じであることができる。

30

## 【0027】

前記メインクロックを第2の遅延時間分だけ遅延させた第2の遅延クロックを生成する段階をさらに含み、前記合成クロックは、前記第2の遅延クロックにさらに基づいて生成され、他の2つのクロックのうちの第1のクロックが前記メインクロックと前記第2の遅延クロックのうちのいずれか一方の上昇エッジに同期し、第2のクロックがもう一方の上昇エッジに同期することができる。

## 【0028】

前記第1の遅延時間の最大値は、前記合成クロックが前記信号処理装置が許容されるクロックになる範囲で決められるのが好ましい。

40

## 【0029】

前記第1の遅延時間及び前記第2の遅延時間の最大値は、前記合成クロックが前記信号処理装置が許容するクロックになる範囲で決められるのが好ましい。

## 【0030】

前記信号処理装置が複数のトランジスタを含む遅延回路を備えることができる。

## 【発明の効果】

## 【0031】

本発明によれば、入力クロックを遅延させた遅延クロック、または複数の周波数成分を含む合成クロックを利用して電力消費を時間的にあるいは周波数成分別に分散させること

50

によって電力ピーク値を低くし、E M Iを低減させることができる。

【発明を実施するための最良の形態】

【0032】

添付した図面を参考にして本発明の実施例について本発明の属する技術分野における通常の知識を有する者が容易に実施できるように詳細に説明する。

【0033】

以下、本発明の実施例による信号処理装置及び方法が適用される液晶表示装置について図面を参照して詳細に説明する。

【0034】

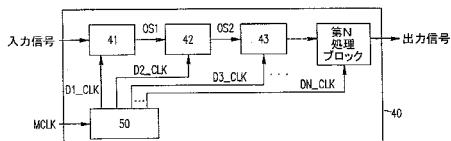

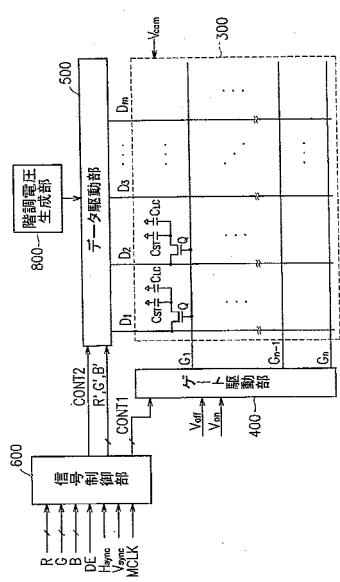

図1は本発明の一実施例による液晶表示装置のブロック図であり、図2は本発明の1実施例による液晶表示装置の1画素の等価回路図である。 10

【0035】

図1に示したように、本発明の1実施例による液晶表示装置は、液晶表示板組立体300及びこれに連結されたゲート駆動部400、データ駆動部500、データ駆動部500に連結された階調電圧生成部800、そしてこれらを制御する信号制御部600を含む。

【0036】

液晶表示板組立体300は、等価回路に示すように、複数の表示信号線G1-Gn、D1-Dmと、これに連結されて概ね行列状に配列された複数の画素とを含む。

【0037】

表示信号線G1-Gn、D1-Dmは、ゲート信号（走査信号ともいう）を伝達する複数のゲート線G1-Gnと、データ信号を伝達するデータ信号線またはデータ線D1-Dmを含む。ゲート線G1-Gnは概ね行方向にのびて、互いに平行であり、データ線D1-Dmは概ね列方向にのびて、互いにほぼ平行である。 20

【0038】

各画素は、表示信号線G1-Gn、D1-Dmに連結されたスイッチング素子Qと、これに連結された液晶蓄電器CLC及び維持蓄電器CSTを含む。維持蓄電器CSTは必要に応じて省略することもできる。

【0039】

スイッチング素子Qは、下部表示板100に備えられており、三端子素子としてその制御端子及び入力端子が各々ゲート線G1-Gn及びデータ線D1-Dmに連結されており、出力端子は液晶蓄電器CLC及び維持蓄電器CSTに連結されている。 30

【0040】

液晶蓄電器CLCは、下部表示板100の画素電極190と、上部表示板200の共通電極270とを2つの端子とし、2つの電極190、270間の液晶層3は誘電体として機能する。画素電極190は、スイッチング素子Qに連結されており、共通電極270は、上部表示板200の全面に形成され、共通電圧Vcomの印加を受ける。図2の構成に代えて、共通電極270を下部表示板100に設けることもでき、そのときは、2つの電極190、270を全て線状または棒形に形成することができる。

【0041】

維持蓄電器CSTは、下部表示板100に具備される別個の信号線（図示せず）と画素電極190とが重なってなされ、この別個の信号線には共通電圧Vcomなどの決められた電圧が印加される。しかし、維持蓄電器CSTは、画素電極190が絶縁体を媒介としてすぐ上の前段ゲート線と重なってなされることもできる。

【0042】

一方、色表示を実現するために、各画素が色相を表示するようにしなければならないが、これは画素電極190に対応する領域に赤色、緑色、または青色のカラーフィルター230を備えることによって可能である。図2で、カラーフィルター230は上部表示板200の該当領域に形成されているが、これとは異なって、下部表示板100の画素電極190の上または下に形成することもできる。

【0043】

50

20

30

40

50

液晶表示板組立体 300 の 2 つの表示板 100、200 のうちの少なくとも一方の外側面には、光を偏光させる偏光子（図示せず）が取り付けられている。

【0044】

階調電圧生成部 800 は、画素の透過率に係る 2 組の複数階調電圧を生成する。2 組のうちの 1 組は共通電圧  $V_{com}$  に対してプラス値を有し、もう 1 組はマイナス値を有する。

【0045】

ゲート駆動部 400 は、液晶表示板組立体 300 のゲート線  $G_1 - G_n$  に連結され、外部からのゲートオン電圧  $V_{on}$  とゲートオフ電圧  $V_{off}$  の組み合わせからなるゲート信号をゲート線  $G_1 - G_n$  に印加し、通常、複数の集積回路から構成される。

【0046】

データ駆動部 500 は、液晶表示板組立体 300 のデータ線  $D_1 - D_m$  に連結され、階調電圧生成部 800 からの階調電圧を選択してデータ信号として画素に印加し、通常、複数の集積回路から構成される。

【0047】

複数のゲート駆動集積回路またはデータ駆動集積回路は、TCP (tape carrier package)（図示せず）に実装し、TCP を液晶表示板組立体 300 に装着することも、TCP を利用せずガラス基板上にこれらの集積回路を直接装着 (COG 方式) することもできる。そして、これらの集積回路のような機能を行う回路を液晶表示板組立体 300 に直接実装することもできる。

【0048】

信号制御部 600 は、ゲート駆動部 400 及びデータ駆動部 500 などの動作を制御する制御信号を生成し、各該当する制御信号をゲート駆動部 400 及びデータ駆動部 500 に提供する。

【0049】

以下、このような液晶表示装置の表示動作についてさらに詳細に説明する。

【0050】

信号制御部 600 は、外部のグラフィック制御機（図示せず）から RGB 映像信号 (R、G、B) 及びその表示を制御する入力制御信号、例えば、垂直同期信号  $V_{sync}$  と水平同期信号  $H_{sync}$ 、メインクロック  $MCLK$ 、データイネーブル信号  $DE$  などの提供を受ける。信号制御部 600 は、入力映像信号 (R、G、B) と入力制御信号に基づいて映像信号 (R、G、B) を液晶表示板組立体 300 の動作条件に合うように適切に処理し、ゲート制御信号  $CONT_1$  及びデータ制御信号  $CONT_2$  などを生成した後、ゲート制御信号  $CONT_1$  をゲート駆動部 400 に送り、データ制御信号  $CONT_2$  と処理した映像信号 (R'、G'、B') はデータ駆動部 500 に送る。

【0051】

ゲート制御信号  $CONT_1$  は、ゲートオンパルス（ゲート信号のハイ区間）の出力開始を指示する垂直同期開始信号  $STV$ 、ゲートオンパルスの出力時期を制御するゲートクロック信号  $CPV$  及びゲートオンパルスの幅を限定する出力イネーブル信号  $OE$  などを含む。

【0052】

データ制御信号  $CONT_2$  は、映像信号 (R'、G'、B') の入力開始を指示する水平同期開始信号  $STH$  と、データ線  $D_1 - D_m$  に該当データ電圧の印加を指示するロード信号  $LOAD$ 、共通電圧  $V_{com}$  に対するデータ電圧の極性（以下、“共通電圧に対するデータ電圧の極性”を略して“データ電圧の極性”という）を反転させる反転信号  $RVS$  及びデータクロック信号  $HCLK$ などを含む。

【0053】

データ駆動部 500 は、信号制御部 600 からのデータ制御信号  $CONT_2$  によって、1 行の画素に対応する映像信号 (R'、G'、B') を順次に受信し、階調電圧生成部 800 からの階調電圧のうちの各映像信号 (R'、G'、B') に対応する階調電圧を選択することによ

10

20

30

40

50

って、映像信号（R'、G'、B'）を該当データ電圧に変換する。

【0054】

ゲート駆動部400は、信号制御部600からのゲート制御信号CONT1によってゲートオン電圧Vonをゲート線G1-Gnに印加して、このゲート線G1-Gnに連結されたスイッチング素子Qをターンオンする。

【0055】

1つのゲート線G1-Gnにゲートオン電圧Vonが印加され、これに連結された1行のスイッチング素子Qがターンオンしている間（この期間を1Hまたは1水平周期（horizontal period）といい、水平同期信号Hsync、データタイネーブル信号DE、ゲートクロックCPVの1周期と同一である）、データ駆動部500は、各データ電圧を該当データ線D1-Dmに供給する。データ線D1-Dmに供給されたデータ電圧は、ターンオンしたスイッチング素子Qを通じて該当画素に印加される。

【0056】

このような方式で、1フレーム期間の間、全てのゲート線G1-Gnに対して順次にゲートオン電圧Vonを印加し、全ての画素にデータ電圧を印加する。1フレームが終了すれば次のフレームが開始され、各画素に印加されるデータ電圧の極性が直前のフレーム極性と反対になるようにデータ駆動部500に印加される反転信号RVSの状態が制御される（フレーム反転）。この時、1フレーム期間内でも反転信号RVSの特性に従って1つのデータ線を通じて流れるデータ電圧の極性が変わったり（ライン反転）、1画素行に印加されるデータ電圧の極性も互いに異なることができる（ドット反転）。

【0057】

以下、このような液晶表示装置に適用される本発明の1実施例による信号処理装置について詳細に説明する。

【0058】

第1に、クロックを時間的に分離して信号処理装置の電力消費を時間的に分散させることによってEMIが低減される信号処理装置について説明する。

【0059】

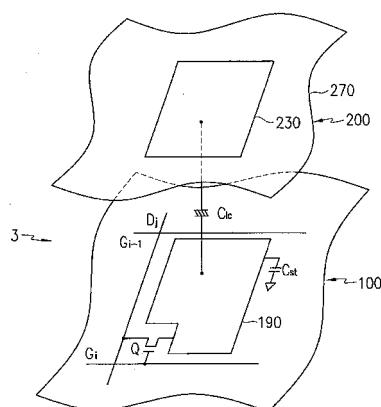

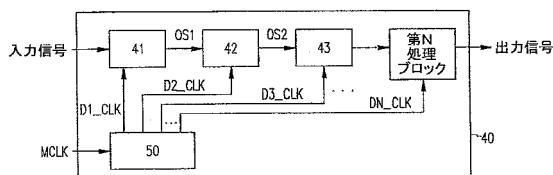

図3は本発明の他の実施例による信号処理装置40のブロック図である。

【0060】

本実施例の信号処理装置40は、クロックを使用するN個の処理ブロック及びクロック生成部50を含む。ここで信号処理装置40は、前述した液晶表示装置の信号制御部600に対応することができ、N個の処理ブロックは、信号制御部600内の各処理ブロックに対応することができる。

【0061】

本実施例ではNを4として説明するが、Nの値は4より小さい場合、あるいは大きい場合も想定できる。

【0062】

第1の処理ブロック41は、外部からの信号を受信して処理した後、第1の出力信号OS1を出力し、第2の処理ブロック42は、第1の出力信号OS1を受信して処理した後、第2の出力信号OS2を出力し、第3の処理ブロック43は、第2の出力信号OS2を受信して処理した後、第3の出力信号OS3を出力し、第4の処理ブロック44は、第3の出力信号OS3を受信して処理した後、第4の出力信号OS4を出力する。第4の出力信号OS4は、本実施例の信号処理装置40の出力信号である。図4では、各処理ブロックを連続接続（cascade connection）させているが、これに限定されるものではなく、処理ブロックそれが外部から入力信号を受信し処理した後、他の処理ブロックまたは外部に出力信号を送るように構成できる。

【0063】

クロック生成部50は、メインクロックMCLKを受信し、本実施例の信号処理装置40内の処理ブロックの数と同一の4個の遅延クロックD1\_CLK、D2\_CLK、D3\_CLK、D4\_CLKを生成する。

10

20

30

40

50

## 【0064】

クロック生成部50は、遅延クロックを生成する遅延手段を含む。遅延手段は、複数のトランジスタを含む遅延回路であることができる。このような遅延回路は、トランジスタに入力される信号がトランジスタを通過しながら発生する時間遅延を利用するものであって、複数のトランジスタを連結し、必要な時間分だけ遅延された信号を得ることができる。

## 【0065】

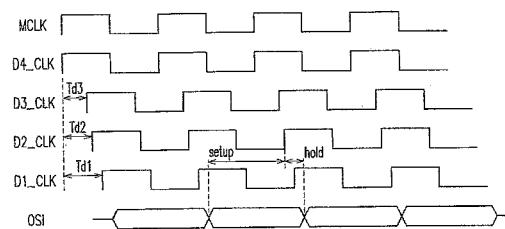

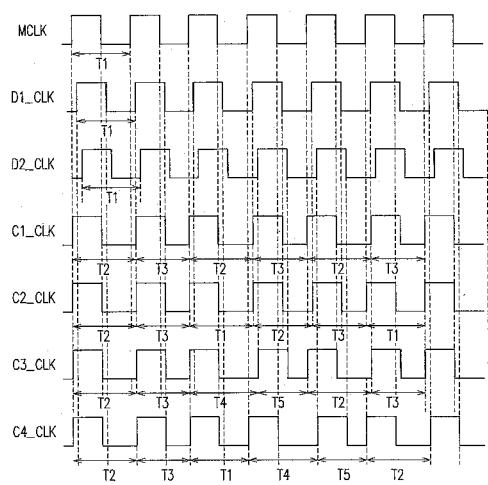

図4は本発明の他の実施例による信号処理装置40におけるクロック信号及び第1の処理プロックの出力信号の波形図である。

## 【0066】

図4のように、第1の遅延クロックD1\_CLKは、メインクロックMCLKから第1の遅延時間Td1分だけ、第2の遅延クロックD2\_CLKは第2の遅延時間Td2分だけ、第3の遅延クロックD3\_CLKは第3の遅延時間Td3分だけ、第4の遅延クロックD4\_CLKは第4の遅延時間Td4分だけ、それぞれ遅延させたクロックである。

## 【0067】

クロック生成部50は、第1の遅延クロックD1\_CLKを第1の処理プロック41に入力し、第2の遅延クロックD2\_CLKを第2の処理プロック42に入力し、第3の遅延クロックD3\_CLKを第3の処理プロック43に入力し、第4の遅延クロックD4\_CLKを第4の処理プロック44に入力する。

## 【0068】

各処理プロックは、入力された該当遅延クロックに同期して処理動作を行う。

## 【0069】

各遅延時間は次の式1を充足するように設定するのが好ましい。

式1

$$Td4 < Td3 < Td2 < Td1$$

このように遅延時間を設定すれば、遅延時間が最も大きい遅延クロックが最初の処理プロックに、遅延時間が最も小さい遅延クロックが最後の処理プロックに入力される。即ち、最も大きい時間遅延を有する第1の遅延クロックD1\_CLKが信号処理装置40で最も早く処理される第1の処理プロック41に入力され、最も小さい時間遅延を有する第4の遅延クロックD4\_CLKが第4の処理プロック44に入力される。また、図4のように、各処理プロックが正常に動作するために、入力信号のセットアップタイムとホールドタイムの規格に合うように各遅延時間を設定する。セットアップタイムは、クロック信号が入る前から入力データが安定した状態に維持されるべき最小の時間であり、ホールドタイムは、各処理プロックが出力値を得るために、入力がクロックパルスの転移直後に継続して維持されるべき最少の時間である。このようにすれば、第1の遅延クロックD1\_CLKに同期して処理された第1の処理プロック41の第1の出力信号OS1が、第2の処理プロック42に入力された後、第2の遅延クロックD2\_CLKに同期して処理されるように、十分なタイミングの余裕を持つことになる。

## 【0070】

一方、各遅延時間は、各遅延クロックの上昇エッジの間隔が同一になるように設定するが、各遅延クロックに同期する各処理プロックの電力消費量に応じて適切に個別的に設定することもできる。つまり、電力消費の大きい処理プロックに入力される遅延クロックは、前後の他の遅延クロックとのクロック間隔が広くなるように遅延時間を設定できる。そうすると、電力消費の大きい処理プロックの最大電力値を低くすることができ、これによってEMI低減効果はさらに大きくなる。

## 【0071】

最後の遅延クロックの遅延時間、即ち、本実施例で第4の遅延クロックD4\_CLKの第4の遅延時間Td4は、0とすることができます。言い換えれば、第4の遅延クロックD4\_CLKは、遅延回路によって遅延されたクロックを用いるのではなく、メインクロックMCLKをそのまま用いることができる。このようにして遅延回路を最少化することができます。

10

20

30

40

50

できる。

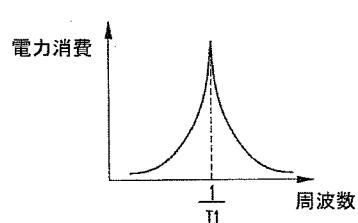

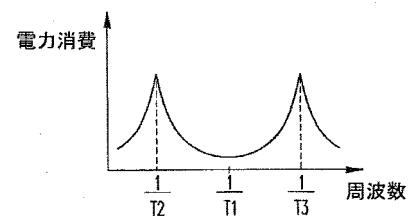

【0072】

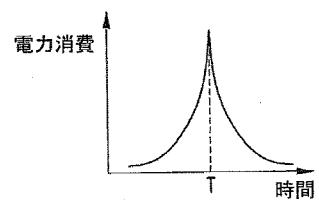

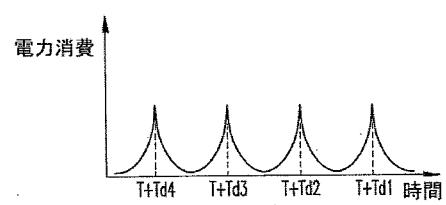

図5aは単一クロックの場合、時間軸に対する信号処理装置の電力消費を示した波形図であり、図5bは本発明の一実施例による複数の遅延クロックの場合、時間軸に対する信号処理装置の電力消費を示した波形図である。

【0073】

図5aに示したように、単一クロックの上昇エッジや下降エッジによって信号処理装置の内部の全処理ブロックが動作すれば、クロックの上昇エッジや下降エッジが起こる時間Tで集中的に電力が消費する。したがって、時間Tで、電力のピーク値も相対的に大きく、ピーク値が大きければ大きいほどEMIも多くの発生する。

10

【0074】

しかし、図5bのように、本発明の一実施例による複数の遅延クロックを信号処理装置の各処理ブロックに入力し、各処理ブロックの動作が時間的に分散されると、信号処理装置が消費する全体電力も分散される。したがって、各遅延クロックの上昇エッジや下降エッジが起こる各時点T+Td4、T+Td3、T+Td2、T+Td1における電力ピーク値は、単一クロックの場合よりも小さく、ピーク値が小さいとEMIの発生も少ない。

【0075】

結局、入力クロックを遅延手段によって時間的に分離した複数の遅延クロックを信号処理装置の各処理ブロックに入力し、電力消費を時間的に分散させることにより電力ピーク値を低くすることで、信号処理装置のEMIを低減させることができる。

20

【0076】

第2に、信号処理装置に入力されるクロックを複数の周波数を有するクロックに合成し、信号処理装置の電力消費を周波数の帯域別に分散させることによってEMIを低減する方法について説明する。

【0077】

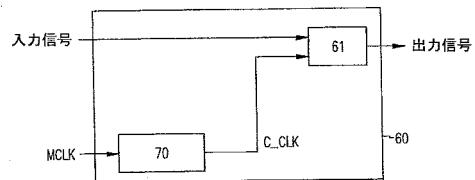

図6は本発明の他の実施例による信号処理装置60のブロック図である。

【0078】

本実施例の信号処理装置60は、クロックを使用する処理ブロック61及びクロック生成部70を含む。ここで、信号処理装置60は、前述したような液晶表示装置の信号制御部600と対応する。

30

【0079】

クロック生成部70は、メインクロックMCLKを受信して1以上の遅延クロックを生成した後、メインクロックMCLK及び生成された遅延クロックを利用して複数の周波数の成分を有する合成クロックCCLKを生成する。

【0080】

クロック生成部70は、遅延クロックを生成する遅延手段を含む。遅延手段は、複数のトランジスタを含む遅延回路であり得る。このような遅延回路は、トランジスタに入力される信号がトランジスタを通過するうちに発生する時間遅延を利用してしたるもので、複数のトランジスタを連結して、必要な時間分だけ遅延された信号を得ることができる。

40

【0081】

図7は本発明の他の実施例による信号処理装置60のクロック信号の波形図である。

【0082】

図7に示したように、クロック生成部70は、メインクロックMCLKを第1の遅延時間Td1分だけ遅延した第1の遅延クロックD1\_CCLK及びメインクロックMCLKを第2の遅延時間Td2分だけ遅延した第2の遅延クロックD2\_CCLKを生成し、遅延されたクロックとメインクロックMCLKを利用して2つ以上の周波数成分を有する合成クロックCCLKを生成する。メインクロックMCLK、第1の遅延クロックD1\_CCLK、及び第2の遅延クロックD2\_CCLKの周期は全てT1である。

【0083】

2つの周波数成分を有する合成クロックC1\_CCLKは、2つのクロックを1単位とし

50

て、2つのクロックのうち一方のクロックの上昇エッジをメインクロックMCLKの上昇エッジに同期させ、もう一方のクロックの上昇エッジを第1の遅延クロックD1\_CCLKの上昇エッジに同期させて生成される。このような二つのクロックを繰り返すと、上昇エッジの周期が交互にT2及びT3となる合成クロックC1\_CCLKが生成する。合成クロックC\_CCLKの下降エッジも、各々二つのクロックのうち一方のクロックの下降エッジはメインクロックMCLKの下降エッジに同期させ、もう一方のクロックの下降エッジは第1の遅延クロックD1\_CCLKの下降エッジに同期させる。そうすると、合成クロックC1\_CCLKの下降エッジの周期も交互にT2及びT3となる。ここで、 $T_2 = T_1 + T_{d1}$ であり、 $T_3 = T_1 - T_{d1}$ である。

【0084】

10

3つの周波数成分を有する合成クロックC2\_CCLKは、3つのクロックを一単位として、3つのクロックのうち2つのクロックの上昇エッジをメインクロックMCLKの上昇エッジに同期させ、残りの1つのクロックの上昇エッジを第1の遅延クロックD1\_CCLKの上昇エッジに同期させて生成する。このような3つのクロックを繰り返すと、上昇エッジの周期が交互にT2、T3及びT1となる合成クロックC2\_CCLKが生成される。合成クロックC2\_CCLKの下降エッジも、各々3つのクロックのうちの2つのクロックの下降エッジをメインクロックMCLKの下降エッジに同期させ、残りの1つのクロックの下降エッジを第1の遅延クロックD1\_CCLKに同期させる。そうすると、合成クロックC2\_CCLKの下降エッジの周期も交互にT2、T3及びT1となる。

【0085】

20

4つの周波数成分を有する合成クロックC3\_CCLKは、4つのクロックを一単位として、4つのクロックのうち2つのクロックの上昇エッジをメインクロックMCLKの上昇エッジに同期させ、残りの1つのクロックの上昇エッジを第1の遅延クロックD1\_CCLKに同期させ、残りの1つのクロックの上昇エッジを第2の遅延クロックD2\_CCLKに同期させて生成する。合成クロックC3\_CCLKでメインクロックMCLKに同期するクロックが連続して現れないように、同期するクロックの順番を設定し、1単位の4つのクロックを繰り返すと、上昇エッジの周期が交互にT2、T3、T4及びT5となる合成クロックC3\_CCLKが生成される。合成クロックC3\_CCLKの下降エッジも同一の方法で処理する。ここで、 $T_2 = T_1 + T_{d1}$ 、 $T_3 = T_1 - T_{d1}$ 、 $T_4 = T_1 + T_{d2}$ であり、 $T_5 = T_1 - T_{d2}$ である。

30

【0086】

5つの周波数成分T1、T2、T3、T4、T5を有する合成クロックC4\_CCLKは、5つのクロックを一単位とし、前述した合成クロックC3\_CCLKで1単位の4つのクロックのうちの所定位置にメインクロックMCLKの上昇エッジに同期する1つのクロックを繰り返して挿入することによって生成する。図7では第3のクロックに挿入した。

【0087】

6つ以上の周波数成分を有する合成クロックも、前記のような方法で生成することができる。

【0088】

40

クロック生成部70は、前記の方法によって生成された合成クロックC\_CCLKを処理ブロック61に入力する。合成クロックC\_CCLKは、必要に応じて所定個数の周波数成分を含むことができる。

【0089】

処理ブロック61は、入力された合成クロックに同期されて処理動作を行う。

【0090】

信号処理装置が、合成クロックC\_CCLKをクロックとして認識できる範囲内で各遅延時間を設定するのが好ましい。即ち、処理ブロック61が正常に作動するために、入力信号のセットアップタイムとホールドタイムの規格に合うように各遅延時間を設定する。

【0091】

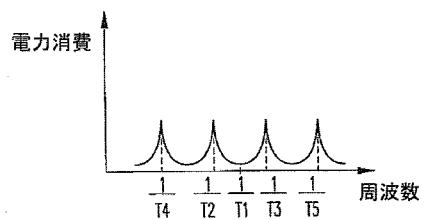

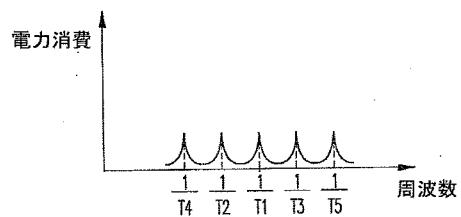

図8aはメインクロックMCLKが変調されず、処理ブロック61に入力された場合、

50

周波数の軸に対する信号処理装置の電力消費を示した波形図であり、図8b～図8eは本発明の他の実施例による合成クロックCCLKが処理プロックに入力された場合、周波数の軸に対する信号処理装置の電力消費を示した波形図である。

【0092】

図8aに示したように、單一周波数 $1/T_1$ を有するメインクロックMCLKによって信号処理装置内部の全処理プロックが作動すると、クロック周波数 $1/T_1$ で電力が集中的に消耗される。したがって、クロック周波数 $1/T_1$ で、電力のピーク値が相対的に大きく、ピーク値が大きいほどEMIの発生も多くなる。

【0093】

ところが、本発明の一実施例による2つの周波数成分を有する合成クロックC1CLKが処理プロック61に入力されると、処理プロック61は、2つの周波数 $1/T_2$ 、 $1/T_3$ に従って動作し、図8bに示したように、信号処理装置が消費する電力もこれらの周波数 $1/T_2$ 、 $1/T_3$ に従って分散されて消費される。したがって、合成クロックC1CLKの各周波数 $1/T_2$ 、 $1/T_3$ における電力ピーク値は、メインクロックMCLKの場合よりも小さく、ピーク値が小さいとEMIの発生も少なくなる。

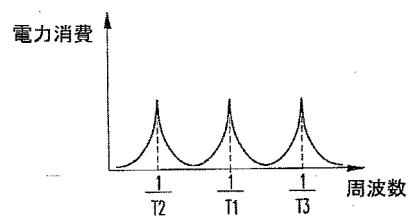

【0094】

図8c～図8eは、それぞれ3つ～5つの周波数成分を有する合成クロックによって処理プロックが作動する場合の信号処理装置が消費する電力の分布を示す。ここで、合成クロックC1CLKの周波数成分の数によって消費電力のピークの数が決められ、ピークの数が多いほど電力分散が多く生じ、電力ピーク値は小さくなる。これにより、EMIの低減効果はさらに大きくなる。

【0095】

結局、入力クロックを複数の周波数成分を含むように変調した合成クロックを信号処理装置の処理プロックに入力すれば、電力消費の分布が複数の周波数成分別に分散され、EMIが低減する。

【0096】

以上で、本発明の好ましい実施例について詳細に説明したが、本発明の権利範囲はこれに限定されず、特許請求の範囲で定義している本発明の基本概念を利用した当業者の様々な変形及び改良形態も本発明の権利範囲に属するものである。

【図面の簡単な説明】

30

【0097】

【図1】本発明の1実施例による液晶表示装置のプロック図である。

【図2】本発明の1実施例による液晶表示装置の1画素の等価回路図である。

【図3】本発明の他の実施例による信号処理装置のプロック図である。

【図4】本発明の他の実施例による信号処理装置におけるクロック信号及び第1の処理プロックの出力信号の波形図である。

【図5a】单一クロックが入力された場合、時間軸に対する信号処理装置の電力消費を示した波形図である。

【図5b】本発明の一実施例による複数の遅延クロックが入力された場合、時間軸に対する信号処理装置の電力消費を示した波形図である。

40

【図6】本発明の他の実施例による信号処理装置のプロック図である。

【図7】本発明の他の実施例による信号処理装置におけるクロック信号の波形図である。

【図8a】メインクロックが変調されず、処理プロックに入力された場合、周波数軸に対する信号処理装置の電力消費を示した波形図である。

【図8b】本発明の他の実施例による合成クロックが処理プロックに入力された場合、周波数軸に対する信号処理装置の電力消費を示した波形図である。

【図8c】本発明の他の実施例による合成クロックが処理プロックに入力された場合、周波数軸に対する信号処理装置の電力消費を示した波形図である。

【図8d】本発明の他の実施例による合成クロックが処理プロックに入力された場合、周波数軸に対する信号処理装置の電力消費を示した波形図である。

50

【図8e】本発明の他の実施例による合成クロックが処理ブロックに入力された場合、周波数軸に対する信号処理装置の電力消費を示した波形図である。

【符号の説明】

【0098】

3 液晶層

400、600 信号処理装置

41、42、43、61 処理ブロック

500、700 クロック生成部

3000 液晶表示板組立体

4000 ゲート駆動部

5000 データ駆動部

6000 信号制御部

8000 階調電圧生成部

10 1000 下部表示板

1900 画素電極

2000 上部表示板

2300 カラーフィルター

2700 共通電極

【図1】

【図2】

【図3】

【図4】

【図5 a】

【図5 b】

【図6】

【図7】

【図8 a】

【図8 b】

【図8 c】

【図 8 d】

【図 8 e】

---

フロントページの続き

F ターム(参考) 5C080 AA05 AA10 BB05 CC03 DD12 EE29 FF11 JJ02 JJ04

JJ05 JJ06