(12) 发明专利申请

(10) 申请公布号 CN 119356934 A

(43) 申请公布日 2025.01.24

(21) 申请号 202411218767.1

(51) Int.Cl.

(22) 申请日 2019.06.03

G06F 11/10 (2006.01)

(30) 优先权数据

G06F 13/16 (2006.01)

62/692,960 2018.07.02 US

16/150,239 2018.10.02 US

(62) 分案原申请数据

201910496617.X 2019.06.03

(71) 申请人 三星电子株式会社

地址 韩国京畿道水原市灵通区三星路129

号

(72) 发明人 牛迪民 克里希纳·马拉迪

郑宏忠

(74) 专利代理机构 北京市柳沈律师事务所

11105

专利代理人 邵亚丽

权利要求书3页 说明书15页 附图8页

(54) 发明名称

存储装置以及用于存储错误管理的方法

(57) 摘要

根据一个一般方面，提供了一种存储装置以及多芯片系统。存储装置可包括多个堆叠的集成电路裸片，所述多个堆叠的集成电路裸片包括存储单元裸片及逻辑裸片。存储单元裸片可被配置成将数据存储在存储地址处。逻辑裸片可包括与所述堆叠的集成电路裸片的接口且所述接口被配置成在存储单元裸片与至少一个外部器件之间传送存储器存取。逻辑裸片可包括可靠性电路，可靠性电路被配置成改善存储单元裸片内的数据错误。可靠性电路可包括备用存储器以及地址表，备用存储器被配置成存储数据，地址表被配置成将与错误相关联的存储地址映射到备用存储器。可靠性电路可被配置成判断存储器存取是否与错误相关联，且如果是，则利用备用存储器来完成存储器存取。

1.一种存储装置,包括:

第一器件,包括:

存储单元裸片,被配置成至少部分地基于存储地址来存储数据;以及

逻辑裸片,包括:

与所述存储单元裸片的接口,其中所述接口被配置成将存储器存取传送至所述存储单元裸片;以及

第二器件,被配置成发送与错误相关联的存储地址;

其中,所述逻辑裸片被配置成:

从所述第二器件接收所述存储地址;

基于所述第二器件的状态,将所述存储地址映射到备用存储器的一部分,其中所述第二器件的所述状态与客户机接合;以及

基于与所述存储单元裸片的存储器存取,确定所述存储器存取与所述错误相关联,且至少部分地利用所述备用存储器来完成所述存储器存取。

2.根据权利要求1所述的存储装置,其中与所述错误相关联的所述存储地址存储于地址数据结构中,所述地址数据结构包括:

纠错码部分,用于防止所述地址数据结构中的错误;且

有效指示符,被配置成指示所述存储地址的现用状态。

3.根据权利要求1所述的存储装置,其中所述逻辑裸片被配置成:

接收对在存储地址处的数据的存储器写入要求;

确定所述存储地址与错误相关联;且

将所述数据写入到所述备用存储器的所述一部分。

4.根据权利要求1所述的存储装置,其中与所述错误相关联的所述存储地址存储于地址数据结构中,且所述逻辑裸片被配置成通过以下步骤来确定所述存储地址与错误相关联:

确定所述存储地址作为存储地址条目存储在所述地址数据结构内;以及

确定有效指示符指示所述存储地址条目是现用的。

5.根据权利要求1所述的存储装置,其中所述逻辑裸片被配置成:

接收对在存储地址处的数据的存储器读取要求;

确定所述存储地址与错误相关联;且

从所述备用存储器的一部分取回所述数据。

6.根据权利要求1所述的存储装置,其中与所述错误相关联的所述存储地址存储于地址数据结构中,且所述逻辑裸片被配置成:

接收指示存储地址与错误相关联的消息;

将所述存储地址置于所述地址数据结构中;且

将所述存储地址与所述备用存储器的所述一部分相关联。

7.根据权利要求6所述的存储装置,其中所述逻辑裸片被配置成通过以下步骤接收指示存储地址与错误相关联的消息:

接收对预定义的存储地址的存储器写入要求,其中所述预定义的存储地址与所述地址数据结构相关联。

8. 根据权利要求1所述的存储装置,其中所述逻辑裸片被配置成:

监测所述备用存储器的使用量级别,以及

提供所述备用存储器的所述使用量级别的指示符。

9. 根据权利要求1所述的存储装置,其中所述逻辑裸片被配置成基于所述第一器件的操作状态而提供关于所述逻辑裸片的地址映射操作的信息。

10. 一种用于存储错误管理的方法,所述方法包括:

由处理器件基于对包括存储器裸片以及逻辑裸片的存储器器件的第一存取来确定与所述存储器裸片的一部分相关联的错误;

基于所述确定,从所述处理器件向所述逻辑裸片传送与所述存储器裸片的所述一部分相关联的所述错误的第一指示;

基于所述确定,从所述处理器件向所述处理器件的驱动器传送与所述存储器裸片的所述一部分相关联的所述错误的第二指示,其中所述第二指示指示与所述错误相关联的存储地址;

由所述驱动器将与所述错误相关联的所述存储地址存储于数据结构中;

从所述处理器件向所述逻辑裸片传送对所述存储器裸片的所述一部分的第二存取;以及

由可靠性电路基于所述第一指示,使用备用存储器的至少一部分执行所述第二存取。

11. 根据权利要求10所述的方法,其中所述第一指示包括与所述存储器裸片的所述一部分相关联的地址。

12. 根据权利要求11所述的方法,还包括由所述可靠性电路将与所述存储器裸片的所述一部分相关联的所述地址映射到所述备用存储器的所述一部分。

13. 根据权利要求12所述的方法,其中:

所述第二存取包括写入要求;以及

执行所述第二存取包括基于所述映射,将与所述写入要求相关联的数据写入至所述备用存储器的所述一部分。

14. 根据权利要求12所述的方法,其中:

所述第二存取包括读取要求;以及

执行所述第二存取包括基于所述映射,从所述备用存储器的所述一部分读取与所述读取要求相关联的数据。

15. 根据权利要求11所述的方法,还包括将所述地址存储于非易失性存储器中。

16. 根据权利要求10所述的方法,其中所述第一器件包括主机器件。

17. 根据权利要求10所述的方法,其中所述可靠性电路被设置于逻辑裸片上。

18. 一种存储装置,包括:

第一器件,包括逻辑裸片,所述逻辑裸片包括:

与存储器裸片的第一接口,其中所述存储器裸片被配置成基于存储地址而存储数据;

第二接口,被配置成传送所述存储器裸片的存储器存取;以及

备用存储器,被配置成存储数据;

其中所述逻辑裸片被配置成:

从第二器件接收与错误相关联的存储地址;

将与所述错误相关联的所述存储地址映射到所述备用存储器的一部分；

将所述存储地址存储于地址数据结构中，所述地址数据结构包括针对所述地址数据结构中的错误的纠错码部分；

基于与所述存储单元裸片的存储器存取，确定所述存储器存取与所述错误相关联，且至少部分地利用所述备用存储器的所述一部分来完成所述存储器存取；以及

向所述第二器件提供所述备用存储器的容量的指示。

19. 根据权利要求18所述的存储装置，其中所述逻辑裸片被配置成：

接收对在所述存储地址处的数据的存储器写入要求；

确定所述存储地址与所述错误相关联；且

将所述数据写入到所述备用存储器的一部分。

20. 根据权利要求18所述的存储装置，其中所述逻辑裸片被配置成：

接收对在所述存储地址处的数据的存储器读取要求；确定所述存储地址与所述错误相关联；且

从所述备用存储器的被映射的部分取回所述数据。

## 存储装置以及用于存储错误管理的方法

[0001] 本发明是2019年06月03日所提出的申请号为201910496617.X、发明名称为《存储装置以及多芯片系统》的发明专利申请的分案申请。

### 技术领域

[0002] 本说明内容涉及存储器纠错,且更具体来说涉及高带宽存储器(HBM)可靠性、可存取性及可服务性(RAS)高速缓存架构。

### 背景技术

[0003] 高带宽存储器(High Bandwidth Memory,HBM)是用于堆叠的动态随机存取存储器(dynamic random-access memory,DRAM)的高性能随机存取存储器(random-access memory, RAM)接口。高带宽存储器通常结合高性能图形加速器及网络器件一起使用。使用HBM的第一器件是图形处理单元(graphical processing unit, GPU)。

[0004] 与双倍数据速率第四代同步DRAM(doubledata rate fourth-generation synchronous DRAM, DDR4)或双倍数据速率类型五同步图形随机存取存储器(doubledata rate type five synchronous graphics random-access memory, GDDR5)相比,HBM以实质上较小的形状因子在使用较小的功率的同时实现较高的带宽。这常常是通过堆叠许多(例如,8个)DRAM裸片来实现的,所述许多DRAM裸片包括具有存储器控制器的可选的基础裸片且通过硅通孔(through-silicon via, TSV)及微凸块来进行互连。

[0005] HBM存储器总线与其他DRAM存储器(例如DDR4或GDDR5)相比非常宽。四个DRAM裸片的HBM堆叠(4-Hi)的每个裸片通常具有两个128位信道以实现总共8个信道以及总共1024位的宽度。具有四个4-Hi HBM堆叠的图形卡/GPU因此将具有宽度为4096位的存储器总线。相比之下,GDDR存储器的总线宽度是32位,对于具有512位存储器接口的图形卡来说具有16个信道。

[0006] 相对于DDR4或GDDR5,对存储器的较大多数的连接需要将HBM存储器连接到GPU(或其他处理器)的新方法。一些公司使用特制硅芯片(被称为插入件)来连接存储器与GPU。这种插入件(interposer)已增加需要使存储器与处理器实体接近的优点,从而减少存储路径。然而,由于半导体器件制作明显比印刷电路板制造更昂贵,因此,这会使最终产品的成本增加。

### 发明内容

[0007] 根据一个一般方面,一种存储装置可包括多个堆叠的集成电路裸片。所述堆叠的集成电路裸片可包括存储单元裸片及逻辑裸片。所述存储单元裸片可被配置成以基于存储地址的随机存取方式来存储数据。所述逻辑裸片可包括与所述多个堆叠的集成电路裸片的接口,且所述接口被配置成在所述存储单元裸片与至少一个外部器件之间传送存储器存取。所述逻辑裸片可包括可靠性电路,所述可靠性电路被配置成改善所述存储单元裸片内的数据错误。所述可靠性电路可包括备用存储器以及地址表,所述备用存储器被配置成以

随机存取方式来存储数据,所述地址表被配置成将与错误相关联的存储地址映射到所述备用存储器的一部分。所述可靠性电路可被配置成当进行对所述多个堆叠的集成电路裸片的存储器存取时,判断所述存储器存取是否与错误相关联,且如果是,则至少部分地利用所述备用存储器来完成所述存储器存取。

[0008] 根据另一一般方面,一种多芯片系统可包括处理器,所述处理器包括存储器控制器以及纠错电路,所述存储器控制器被配置成管理往来于所述处理器的数据流,所述纠错电路被配置成检测所存储的数据中是否出现错误。所述系统可包括集成电路的高带宽存储堆叠,所述集成电路的高带宽存储堆叠包括:高带宽存储单元,被配置成基于存储地址而存储数据;以及可靠性电路,被配置成改善所述高带宽存储单元内的数据错误。所述可靠性电路可包括备用存储器以及地址表,所述备用存储器被配置成存储数据,所述地址表被配置成将与所述错误相关联的存储地址映射到所述备用存储器的一部分。所述可靠性电路被配置成当进行对集成电路的所述高带宽存储堆叠的存储器存取时,判断所述存储器存取是否与错误相关联,且如果是,则至少部分地利用所述备用存储器来完成所述存储器存取。

[0009] 根据另一一般方面,一种存储装置可包括逻辑裸片,所述逻辑裸片包括与高带宽存储器裸片的内部接口,其中所述高带宽存储器裸片被配置成基于存储地址而存储数据。所述逻辑裸片可包括外部接口,所述外部接口被配置成在所述高带宽存储器裸片与至少一个外部器件之间传送存储器存取。所述逻辑裸片可包括可靠性电路,所述可靠性电路被配置成改善所述高带宽存储器裸片内的数据错误。所述可靠性电路可包括备用存储器以及地址表,所述备用存储器被配置成存储数据,所述地址表被配置成将与错误相关联的存储地址映射到所述备用存储器的一部分。所述可靠性电路可被配置成当进行对所述高带宽存储器裸片的存储器存取时,判断所述存储器存取是否与错误相关联,且如果是,则至少部分地利用所述备用存储器来完成所述存储器存取。

[0010] 在附图及以下说明内容中阐述一种或多种实施方式的详细情况。通过阅读说明内容及图式以及阅读权利要求书,其他特征将显而易见。

[0011] 实质上在各图中的至少一个图中示出了和/或结合各图中的至少一个图阐述了用于存储器纠错的系统和/或方法,且更具体来说高带宽存储器(HBM)可靠性、可存取性及可服务性(reliability, accessibility, and serviceability, RAS)高速缓存架构,如在权利要求书中更完整地阐述。

## 附图说明

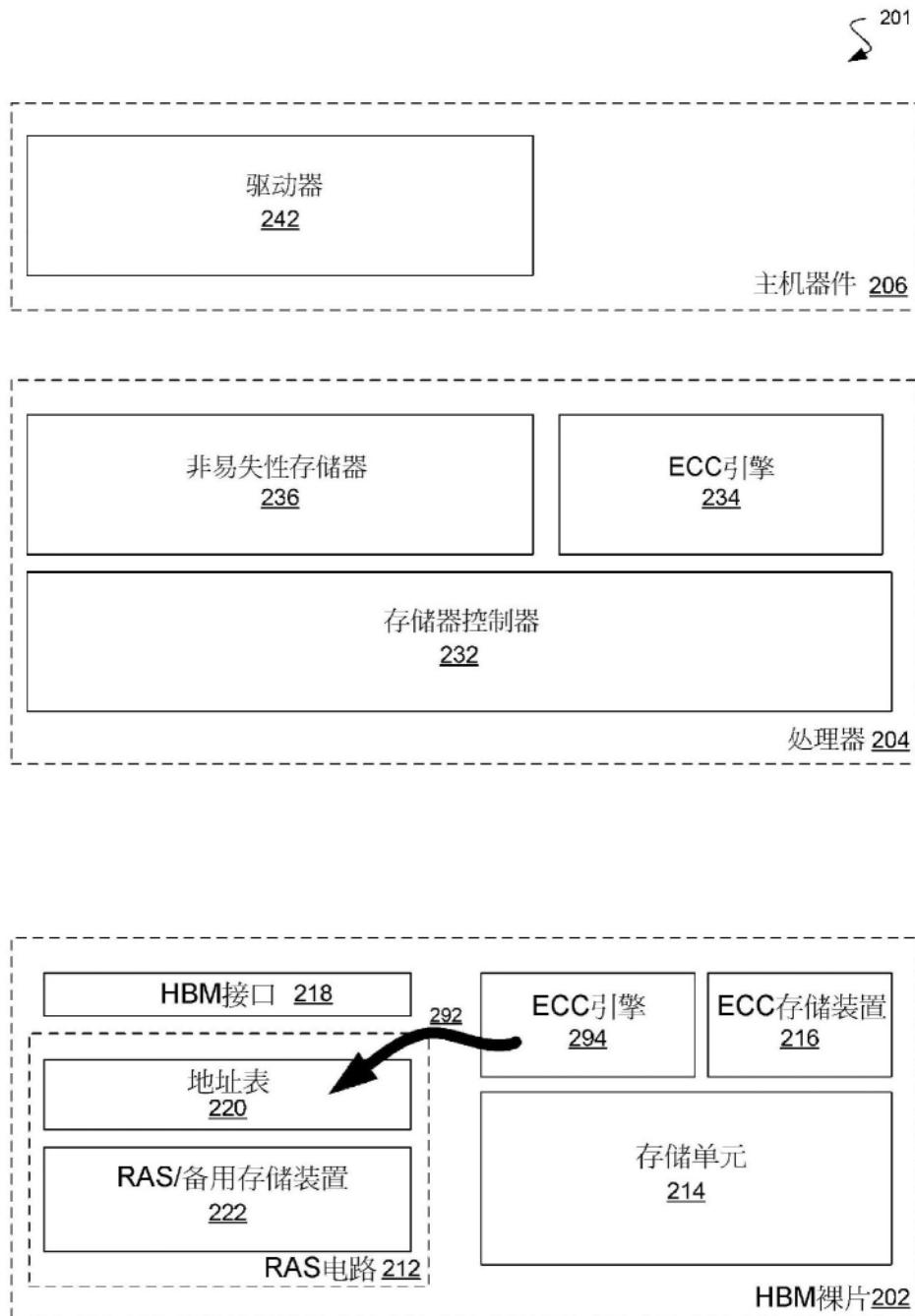

- [0012] 图1是根据所公开主题的系统的示例性实施例的方块图。

- [0013] 图2A是根据所公开主题的系统的示例性实施例的方块图。

- [0014] 图2B是根据所公开主题的系统的示例性实施例的方块图。

- [0015] 图2C是根据所公开主题的系统的示例性实施例的方块图。

- [0016] 图3是根据所公开主题的系统的示例性实施例的方块图。

- [0017] 图4A是根据所公开主题的系统的示例性实施例的方块图。

- [0018] 图4B是根据所公开主题的系统的示例性实施例的方块图。

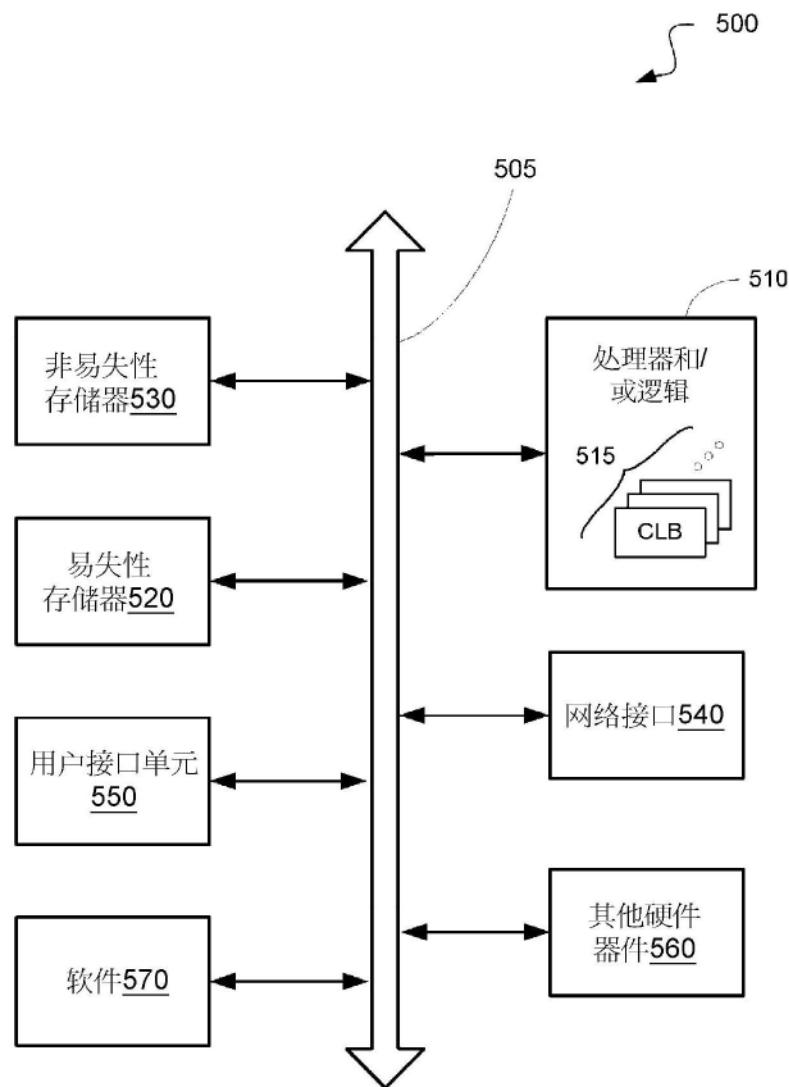

- [0019] 图5是可包括根据所公开主题的原理形成的器件的信息处理系统的示意性方块图。

- [0020] 各个图式中相同的参考符号表示相同的元件。

- [0021] [符号的说明]

- [0022] 100:系统/多芯片系统;

- [0023] 102:逻辑裸片;

- [0024] 104:存储器裸片;

- [0025] 106:路由裸片;

- [0026] 112:逻辑电路;

- [0027] 113:RAS高速缓存或电路;

- [0028] 114:存储阵列/存储器;

- [0029] 123:输入/输出端子或接口/输入/输出接口;

- [0030] 123a、123b:输入/输出接口;

- [0031] 126:通孔;

- [0032] 127:路由结构;

- [0033] 200、201、400、401:系统;

- [0034] 202:HBM裸片/裸片/HBM模块;

- [0035] 204:处理器/GPU;

- [0036] 206:主机器件/主机;

- [0037] 212:可靠性、可存取性及可服务性(RAS)高速缓存或电路/RAS电路/可靠性电路;

- [0038] 214:存储单元;

- [0039] 216:ECC存储装置;

- [0040] 218:HBM接口;

- [0041] 220:地址表/表;

- [0042] 222:RAS或备用存储器或存储装置/备用存储装置/备用存储器/存储装置;

- [0043] 232:存储器控制器;

- [0044] 234:ECC引擎或电路/ECC引擎;

- [0045] 236、530:非易失性存储器;

- [0046] 242:驱动器软件或固件/器件驱动器/驱动器;

- [0047] 282、284、286、292、434、436、474、476:箭头;

- [0048] 294:ECC引擎;

- [0049] 300、302:数据结构;

- [0050] 312:列;

- [0051] 314:有效位或旗标列/有效旗标;

- [0052] 316:被映射的地址列/被映射的存储地址;

- [0053] 412:命令总线;

- [0054] 414:数据总线;

- [0055] 420、470:路由电路;

- [0056] 424:信号/地址表命中/未中;

- [0057] 432:被映射的存储地址;

- [0058] 500:信息处理系统;

- [0059] 505:系统总线;

- [0060] 510:处理器/逻辑;

- [0061] 515:组合逻辑块;

- [0062] 520:易失性存储器;

- [0063] 540:网络接口;

- [0064] 550:用户接口单元;

- [0065] 560:硬件组件;

- [0066] 570:软件组件;

- [0067] ADDRESS#1、ADDRESS#2、ADDRESS#N:存储地址条目。

## 具体实施方式

[0068] 在下文中,将参照附图更充分地阐述各种示例性实施例,在所述附图中示出一些示例性实施例。然而,本发明所公开主题可被实施为许多不同形式,而不应被视为仅限于本文所述示例性实施例。确切来说,提供这些示例性实施例是为了使本公开将透彻及完整,并将向所属领域中的技术人员充分传达本发明所公开主题的范围。在图式中,为清晰起见,可夸大各个层及各个区的大小及相对大小。

[0069] 应理解,当称一元件或层位于另一元件或层“上 (on)”、“连接到 (connected to)”或“耦合到 (coupled to)”另一元件或层时,所述元件或层可直接位于所述另一元件或层上、直接连接到或直接耦合到所述另一元件或层,抑或可存在中间元件或层。相比之下,当称一元件“直接位于 (directly on)”另一元件或层上、“直接连接到 (directly connected to)”或“直接耦合到 (directly coupled to)”另一元件或层时,则不存在中间元件或层。相同的编号自始至终指代相同的元件。本文所用用语“和/或 (and/or)”包括相关列出项中的一个或多个项的任意及所有组合。

[0070] 应理解,尽管在本文中可使用“第一 (first)”、“第二 (second)”、“第三 (third)”等用语来阐述各个元件、组件、区、层和/或区段,然而这些元件、组件、区、层和/或区段不应受限于这些用语。这些用语仅用于区分各个元件、组件、区、层或区段。因此,以下论述的第一元件、组件、区、层或区段也可被称为第二元件、组件、区、层或区段,而此并不背离本发明所公开主题的教示内容。

[0071] 为易于说明,在本文中可使用例如“在…之下 (beneath)”、“在…下面 (below)”、“下部的 (lower)”、“在…上方 (above)”、“上部的 (upper)”等空间相对性用语来阐述图中所示一个元件或特征与另一(其他)元件或特征的关系。应理解,空间相对性用语旨在除图中所绘示的取向外还囊括器件在使用或操作中的不同取向。举例来说,如果图中所示器件被翻转,则被阐述为位于其他元件或特征“下面”或“之下”的元件此时将被取向为位于所述其他元件或特征“上方”。因此,示例性用语“在…下面”可囊括“上方”及“下面”两种取向。器件可具有其他取向(旋转90度或处于其他取向)且本文所用的空间相对性描述语相应地进行解释。

[0072] 同样地,为易于说明,在本文中可使用例如“高 (high)”、“低 (low)”、“上拉 (pull up)”、“下拉 (pull down)”、“1”、“0”等电性用语来阐述图中所示电压电平或电流相对于其他电压电平或电流的关系或者相对于另一(其他)元件或特征的关系。应理解,所述电性相

对用语旨在除了图中所绘示的电压或电流之外还囊括器件在使用或操作中的不同的参考电压。举例来说,如果图中所示器件或信号被反相或使用其他参考电压、电流或电荷,则被阐述为“高”或“被上拉”的元件此时与新的参考电压或电流相比将为“低”或“被下拉”的。因此,示例性用语“高”可囊括相对低的电压或电流或者相对高的电压或电流二者。器件可另外地基于不同的电性参考框架且本文所用的电性相对描述语相应地加以解释。

[0073] 本文所用术语仅是出于阐述特定示例性实施例的目的而并非旨在限制本发明所公开主题。除非上下文清楚地另外指明,否则本文所用单数形式“一(a、an)”及“所述(the)”旨在也包括复数形式。还应理解,当在本说明书中使用用语“包括(comprises)”和/或“包括(comprising)”时,是指明所陈述特征、整数、步骤、操作、元件和/或组件的存在,但不排除一个或多个其他特征、整数、步骤、操作、元件、组件和/或其群组的存在或添加。

[0074] 在本文中参照剖视图阐述示例性实施例,所述剖视图为对理想示例性实施例(及中间结构)的示意性例示。由此,预期会因例如制造技术和/或容差而导致相对于例示形状的变化。因此,示例性实施例不应被视为仅限于本文所示区的特定形状,而是应包含由例如制造引起的形状偏差。举例来说,被例示为矩形的注入区通常应具有圆形特征或曲线特征和/或在其边缘存在注入浓度的梯度而非从注入区到非注入区为二元变化。同样地,通过注入而形成的掩埋区可在所述掩埋区与在进行注入时所经过的表面之间的区中引起一些注入。因此,图中所例示的区为示意性的且其形状并非旨在例示器件的区的实际形状且并非旨在限制本发明所公开主题的范围。

[0075] 除非另外定义,否则本文所用所有用语(包括技术及科学用语)的含义均与本发明所公开主题所属领域中的一般技术人员所通常理解的含义相同。还应理解,用语(例如在常用词典中所定义的用语)应被解释为具有与其在相关技术的上下文中的含义一致的含义,且除非在本文中明确定义,否则不应将其解释为具有理想化或过于正式的意义。

[0076] 在下文中,将参照附图详细解释示例性实施例。

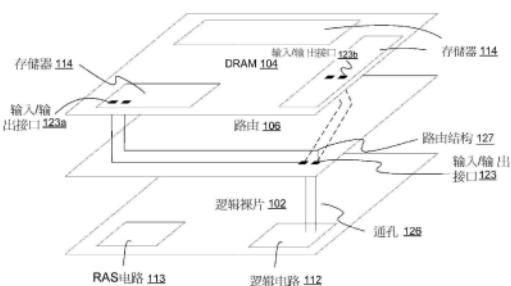

[0077] 图1是根据所公开主题的系统100的示例性实施例的等距方块图。在所示出的实施例中,多个集成电路裸片可堆叠(或其他方式)集成以形成多芯片系统。在各种实施例中,这种多芯片系统100可如以下所述包括RAS高速缓存(cache)或电路。

[0078] 在各种实施例中,高带宽存储器(HBM)可包括随机存取存储器(RAM)的高性能形式。在一些实施例中,HBM可包括使用硅通孔(TSV)进行通信的堆叠的动态RAM(DRAM)存储器。一般来说,高带宽存储器对硅通孔(TSV)与微凸块进行组合来连接叠置在彼此顶部上的多个(例如,4个、8个等)存储单元阵列裸片。在一些实施例中,存储器控制器可在堆叠的最底部处包括在单独的裸片上。

[0079] 在所示出的实施例中,系统100可包括一个或多个存储器(例如,DRAM等)裸片104及逻辑裸片102。在一个实施例中,存储器裸片104及逻辑裸片102可使用或可不使用相同的制造工艺来创建或制造。

[0080] 在所示出的实施例中,存储器裸片104可包括多个存储阵列114。在这种实施例中,存储阵列114可被配置成存储各种数据。在一些实施例中,可由逻辑裸片102或外部器件(例如,外部处理器或主机,如以下所述)来对数据进行存取。

[0081] 在所示出的实施例中,逻辑裸片102可包括一个或多个逻辑电路112。在这种实施例中,逻辑电路112可包括用于接受读取/写入请求或更一般的存储器存取的接口以读取或

存储存储器114内的数据。在各种实施例中，逻辑裸片102可包括RAS高速缓存或电路113，如以下所述。

[0082] 在各种实施例中，逻辑电路112可使用一个或多个通孔126(或微凸块等)来与存储器114进行通信。在这种实施例中，此可实现处理元件(例如，逻辑电路112)与所存储的数据(存储器114)之间的高速通信而无需通过总线或外部接口进行通信。

[0083] 在各种实施例中，系统100也可包括路由裸片106。路由裸片106可被配置成在逻辑裸片102与存储器裸片104之间对信号进行动态路由。在各种实施例中，路由裸片106可通过一个或多个通孔126来与逻辑裸片102进行耦合。通孔126(或通孔126的一部分)可以输入/输出(input/output,I/O)端子或接口123作为终点。在这种实施例中，路由裸片106可在输入/输出接口123与存储所需数据的存储器114之间对信号进行动态路由。

[0084] 在各种实施例中，所述路由可由路由结构127来实现。在各种实施例中，路由结构127可包括各种路由器件，例如(举例来说)多路复用器(multiplexer)、解多路复用器(de-multiplexer)、交叉开关(crossbar switch)、开关、旋转开关、存储器开关、跨交开关(crossover switch)等。应理解，以上仅为几个例示性实例，所公开主题并不受限于上述几个例示性实例。

[0085] 在一些实施例中，路由结构127可被配置成在逻辑电路112的输入/输出接口123与存储器114的相似的输入/输出接口123a或123b之间对输入/输出信号进行路由。在所示出的实施例中，示出两种可能的路由方案。举例来说，实线示出第一路由，其可被用于将逻辑电路112连接到第一存储器(在存储器裸片104的左下角中示出)的输入/输出接口123a。在另一实例中，虚线示出第二路由，其可用于将逻辑电路112连接到第二存储器(在存储器裸片104的右侧中示出)的输入/输出接口123b。然而，在各种实施例中，存储器114可为单片的且不如图中所示分开。应理解，以上仅为几个例示性实例，所公开主题并不受限于上述几个例示性实例。

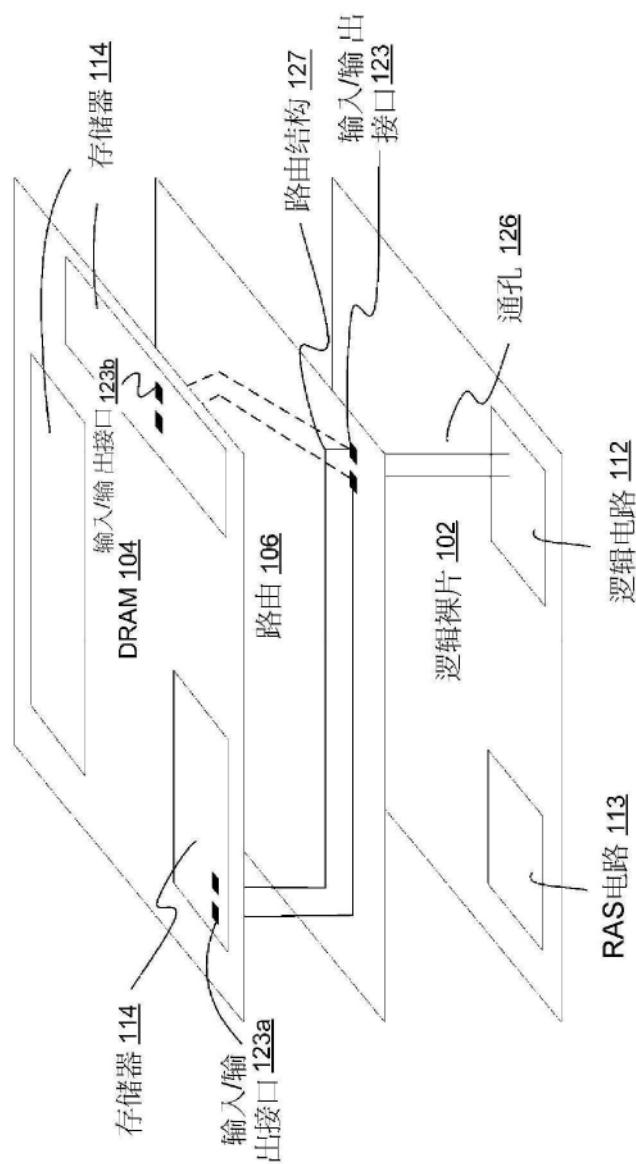

[0086] 图2A是根据所公开主题的系统200的示例性实施例的方块图。在各种实施例中，系统200可为多个分立的集成电路、多芯片模块(multi chip module,MCM)和/或系统芯片(system-on-a-chip,SoC)的一部分。在各种实施例中，系统200可用于例如(举例来说)以下计算器件中：膝上型计算机、台式计算机、工作站、个人数字助理、智能手机、平板计算机及其他适合的计算机或者虚拟机或虚拟机的虚拟计算器件。

[0087] 在一个实施例中，系统200可包括主机器件206。在各种实施例中，这种主机器件可包括中央处理器(central processing unit,CPU)、母板、计算系统。在各种实施例中，主机器件206可包括执行指令且通常读取及存储数据的处理器(未示出)。作为这一过程的一部分，主机器件206可执行驱动器软件或固件242。在所示出的实施例中，器件驱动器242可包括运行或控制附接到计算机的特定类型的器件(例如，处理器204或HBM裸片202)的计算机程序。在这种实施例中，驱动器242可向硬件器件提供软件接口，以使操作系统及其他计算机程序存取硬件功能而无需知晓关于正使用的硬件的确切的详细情况。

[0088] 在所示出的实施例中，系统200可包括处理器204。在各种实施例中，处理器204可包括多种类型的处理器(例如，图形处理器、中心处理器、器件专用处理器、实体处理器等)中的一者。为易于例示，处理器204将作为图形处理单元(GPU)阐述；但是，应理解，以上仅为一个例示性实例，所公开主题并不受限于上述一个例示性实例。在各种实施例中，可采用

GPU 204来产生图形数据或实现大规模并行计算任务。

[0089] 在各种实施例中,处理器204可包括存储器控制器232。在这种实施例中,存储器控制器232可被配置成管理往来于处理器204的数据流。具体来说,在所示出的实施例中,存储器控制器232可被配置成管理处理器204与HBM裸片202之间的数据流。

[0090] 在所示出的实施例中,处理器204可包括纠错码(error correcting or correction code,ECC)引擎或电路234。在这种实施例中,ECC引擎或电路234可被配置成检测在从HBM裸片202接收的数据中的一些数据或任意数据中是否已出现错误。在各种实施例中,ECC引擎234可与存储器控制器232集成在一起或者可为存储器控制器232的一部分。在各种实施例中,ECC引擎234可被配置成检测单位错误或双位错误。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0091] 在所示出的实施例中,处理器204可包括非易失性存储器236。但是,在各种实施例中,存储器可为易失性的或存在于处理器204外部,如以下所述。在这种实施例中,非易失性存储器236可被配置成存储关于哪一存储地址与错误相关联的信息。在一些实施例中,可避免坏的或有错误的存储地址。在另一实施例中,可将坏的或有错误的存储地址重新映射到良好的存储单元或工作存储单元。

[0092] 如上所述,在所示出的实施例中,通过作为非易失性存储器236,可在处理器204的电源循环之间记住这些坏的或有错误的存储地址。在另一实施例中,可使用易失性存储器且可能必须在每一电源循环重新发现坏的或有错误的存储地址。在另一实施例中,处理器204可包括本地或集成的易失性存储器,但是当处理器204结束电源循环时,可将所述数据存储在处理器204的远程或外部的非易失性存储器(例如,硬驱动器(hard drive))中,并在处理器204重新启动时取回所述数据。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0093] 在所示出的实施例中,系统200可包括HBM裸片,或者更准确来说可包括裸片202的堆叠,如上所述。在各种实施例中,HBM裸片202可包括多个存储单元214,如上所述。在各种实施例中,存储单元214可散布在多个集成电路(integrated circuit,IC)裸片之上且被配置成将数据存储在相应的存储地址处。

[0094] 在各种实施例中,HBM裸片202可包括存储单元的ECC存储装置216。在这种实施例中,ECC存储装置216可包括额外的信息(例如,奇偶校验(parity))位以允许或有利于检测存储在存储单元214中的数据内的错误。在各种实施例中,ECC存储装置216可为存储单元214的一部分,且即使ECC存储装置216在实体上分开,仍可同样地散布在多个集成电路(IC)裸片之上,如上所述。在这种实施例中,ECC引擎234可使用此种ECC数据来检测任意错误。

[0095] 在各种实施例中,HBM裸片202可包括HBM接口218,HBM接口218被配置成与处理器204和/或主机器件206进行通信或者在处理器204与主机器件206之间进行通信。在各种实施例中,系统200可包括一条或多条通信总线(未示出)以有利于裸片间(例如,处理器204对HBM裸片202)通信。在这种实施例中,这可包括存储器存取(例如请求及响应)的发送。

[0096] 在各种实施例中,HBM裸片202可包括可靠性、可存取性及可服务性(RAS)高速缓存或电路212(或可靠性电路212)。在这种实施例中,RAS电路212可不被配置成充当传统的高速缓存,从而以可快速存取的方式存储小量数据,同时较大的存储器提供另外的存储。而是,RAS高速缓存或电路212可被配置成充当备份存储器或备用存储器以纠正(或看起来纠

正)或者以其他方式改善在存储单元214内找到的错误。如以下所述,传统上,一旦在存储单元214中检测到错误,可能无法在不采取大量的且耗时的动作的条件下修复或纠正所述错误。利用RAS高速缓存或电路212,可更快速且高效地进行这种修复或纠正。

[0097] 在各种实施例中,RAS电路212可包括RAS或备用存储器或存储装置222。在各种实施例中,备用存储装置222可被配置成存储存储单元214的与错误相关联的一些部分或者以其他方式失修的一些部分的数据。以下将阐述这些组件的操作。

[0098] 在各种实施例中,RAS电路212可包括地址表220,地址表220被配置成存储与错误相关联的一系列存储地址(位于存储单元214内)并将这种存储地址错误映射到备用存储器222的一部分。

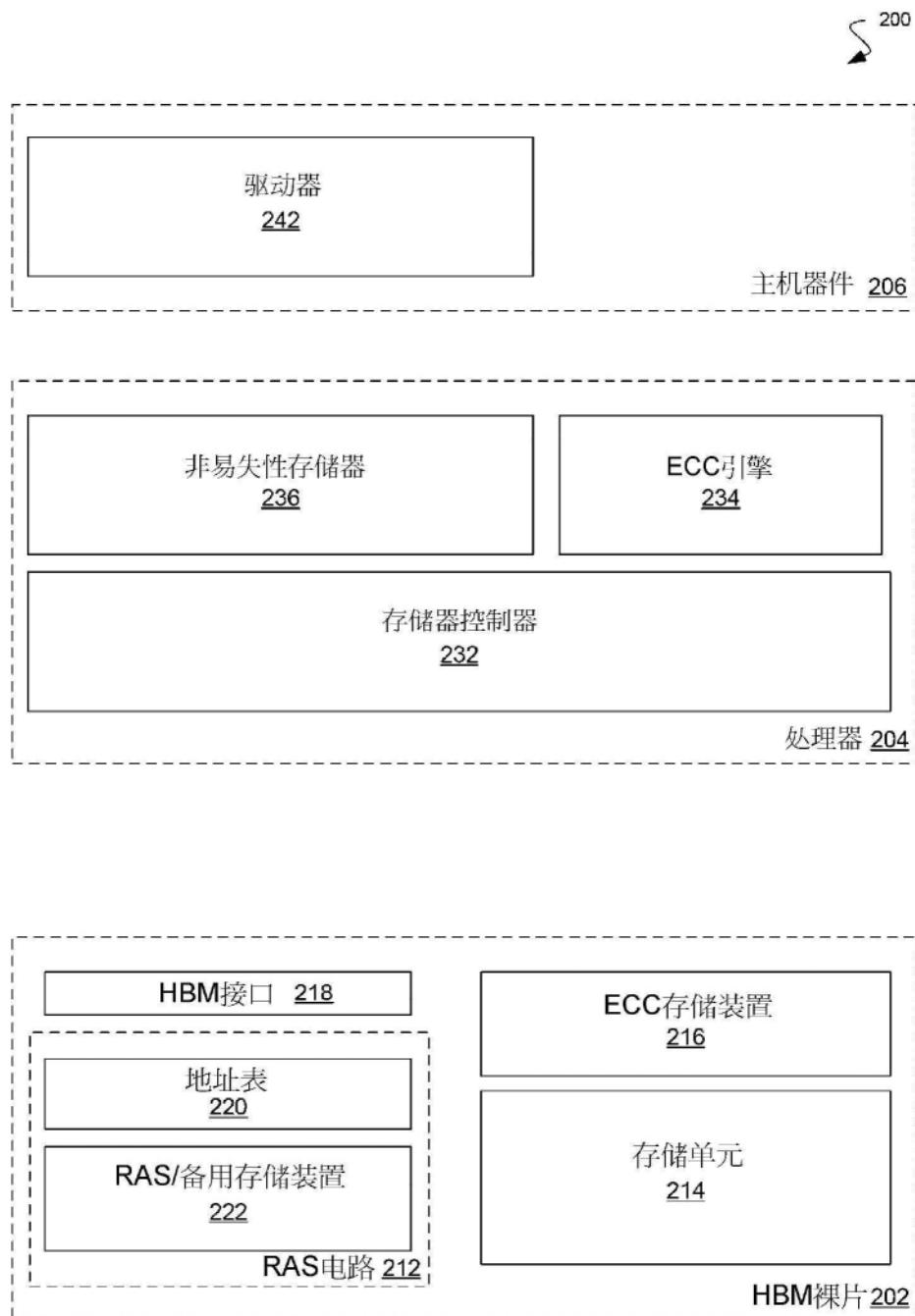

[0099] 图2B是根据所公开主题的系统200的示例性实施例的方块图。图2B所示系统200示出信息流以及事件的相对时序作为对错误进行检测的系统。应理解,以上仅为一个例示性实例,所公开主题并不受限于上述一个例示性实例。

[0100] 在错误处置及检测方面,传统GPU的存储错误管理一般来说如下所述进行。首先,ECC引擎234检测到不可恢复的错误。这种错误常常与存储单元214的特定存储地址相关联且一般来说涉及双位错误或两个单位错误。这种错误可被报告给驱动器242。

[0101] 在这种实施例中,驱动器242转而可将错误报告给应用(未示出)或主机器件206的一部分。驱动器242也可将存储错误登记到GPU的非易失性存储器236中。传统上,系统将无法在进行当前GPU交互的同时改善或防止这种错误的重现。

[0102] 然而,在系统的下一重新附接、重置、重新启动或者GPU交互的下一顺序或序列时,帧缓冲器管理器(未示出,但为处理器204的一部分)可将具有错误的止用页(retired page)加入黑名单。在这种实施例中,可不再使用所述存储地址或页来进行存储。由此,存储地址或页被永久止用,且存储器的功能容量减小。

[0103] 这种传统进程具有一些缺陷。首先,不可能在客户机(例如,主机器件或在主机器件上运行的软件)保持现用的同时将页加入黑名单。第二,在当前GPU上可能止用的页或存储地址的数目部分地因GPU的当前NVM能力而受限。第三,存在大的止用粒度;也就是说,2位错误会引起4千字节(KB)页的止用。另外,这种传统进程最终会引起存储器容量减小且存储单元214的越来越多的部分被加入黑名单。

[0104] 在所示出的实施例中,系统200通过在HBM模块或裸片202上实现额外的逻辑及存储器以对错误进行高速缓存及修复来对所述情况进行补救。详细来说,RAS电路212以至少几千字节的大小在HBM逻辑裸片上实施;但是,应理解,以上仅为示例性实例,所公开主题并不受限于上述示例性实例。这种RAS电路212包括索引区或地址表220以存储由主机206或处理器204接收的地址,且可被HBM裸片202的内部纠错机制保护。RAS电路212也可包括数据区或备用存储装置222,所述数据区或备用存储装置222被配置成存储经修复的数据(其可为任意给定大小)。表220与存储装置222区可具有1-1映射。另外,这些区可利用与HBM逻辑裸片(例如,DRAM、静态随机存取存储器(Static random access memory, SRAM)、闪存等)兼容的任意技术来实施。

[0105] 在所示出的实施例中,再次,纠错进程可以ECC引擎234检测到在给定存储地址处已出现错误开始。如由箭头282所示,ECC引擎234可警告驱动器242,如上所述。再次,如由箭头284所示,驱动器242可将此记录在非易失性存储器236中。

[0106] 然而,代替将存储地址或页加入黑名单以及等待直到处理器204不再立即使用才将存储地址或页加入黑名单,处理器204(通过箭头286示出)可通知HBM裸片202(或HBM裸片202的逻辑裸片)给定存储地址是坏的。HBM裸片202(且更具体来说RAS电路212)可接着采取纠正动作。

[0107] 在所示出的实施例中,RAS电路212可将坏的存储地址登记或录入到地址表220中。坏的存储地址可被映射到备用存储装置222的一部分或存储地址。在各种实施例中,可将在存储地址处的存储单元214中包含的数据复制(包括错误及全部)到备用存储装置222的被映射的部分。在各种实施例中,这可能是不期望的,因为所述数据确实包含错误。在这种实施例中,处理器204可能要求在可读回新数据(不具有错误的数据)之前将新数据写入到HBM裸片202中。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0108] 在这种实施例中,一旦对存储地址进行新的存储器存取(例如,读取或写入),RAS电路212便检查存储地址是否位于地址表220中(且由此与错误相关联)。如果不是,则正常地处理存储器存取。存储器存取由存储单元214实现。如果存储地址与错误相关联,则存储器存取由备用存储装置222实现,具体来说由地址的被地址表220映射的部分实现。

[0109] 在这种实施例中,对坏的存储地址的所有存储器存取均可由备用存储装置222无缝地(对处理器204或主机器件206)实现。在这种实施例中,即使当处理器204与客户机接合时,此也可实现。不需要等到处理器204脱离接合、不使用或作为重新附接的一部分。第二,通过将特定存储地址重新映射到备用存储装置222,HBM裸片202的存储容量不减小。在不加入黑名单的条件下,HBM裸片202看起来具有相同量的存储容量。第三,RAS电路212可提供存储器映射的各种粒度。尽管传统的方法需要将4KB页加入黑名单并止用,然而RAS电路212可允许对高速缓存行、页或其他大小的存储器进行映射。

[0110] 在各种实施例中,向地址表220添加新的存储地址(箭头286)可涉及处理器204(或主机器件206)对预定义的或预留的存储地址实行存储器写入要求。在这种实施例中,RAS电路212可知晓对所述存储地址的任意写入均意指要将新的条目置于地址表220中。在这种实施例中,存储器写入要求的数据部分可包括坏的存储地址。在另一实施例中,向地址表220添加新的存储地址(箭头286)可涉及使用新的消息类型或协议。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0111] 在各种实施例中,处理器204或主机器件206可能能够通过对另一预定义的或预留的存储地址实行存储器读取要求来检查备用存储装置222正在使用或可供用于重新映射的容量。在这种实施例中,RAS存储装置可利用备用存储装置222的当前存储容量或使用量级别来更新寄存器或存储地址,且处理器204或主机器件206可能能够在任意希望的时间从所述存储地址进行读取。在各种实施例中,这可在箭头286的操作之前完成,以便确认这种空间是可用的。在一些实施例中,如果备用存储装置222已满或全部正在使用,则处理器204及主机器件206可回退到传统的加黑名单/止用技术。在另一实施例中,检查备用存储装置222的空闲容量可涉及使用新的消息类型或协议。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0112] 在各种实施例中,当系统200初始化(例如,启动)时,可(由主机器件206或处理器204)从HBM裸片202读取信息。在一个实施例中,可判断HBM裸片202是否包括或支持RAS电路

212。在一个实施例中,可确定使用何种级别的重新映射粒度(例如,256位、512位等)。在另一实施例中,可确定可如何支持高速缓存或备用存储装置222条目和/或地址表220条目。在各种实施例中,可通过对预定义的或预留的地址的存储器读取要求或通过特定消息或协议来进行这些查询。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0113] 同样,在各种实施例中,当系统200初始化(例如,启动)时,可(由主机器件206或处理器204)将信息或设置写入到HBM裸片202。在一个实施例中,可(例如,从非易失性存储器236)将预先存在的一系列坏的存储地址写入到地址表220。在另一实施例中,可为备用存储装置222设置重新映射粒度级别(例如,256位、512位等)。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

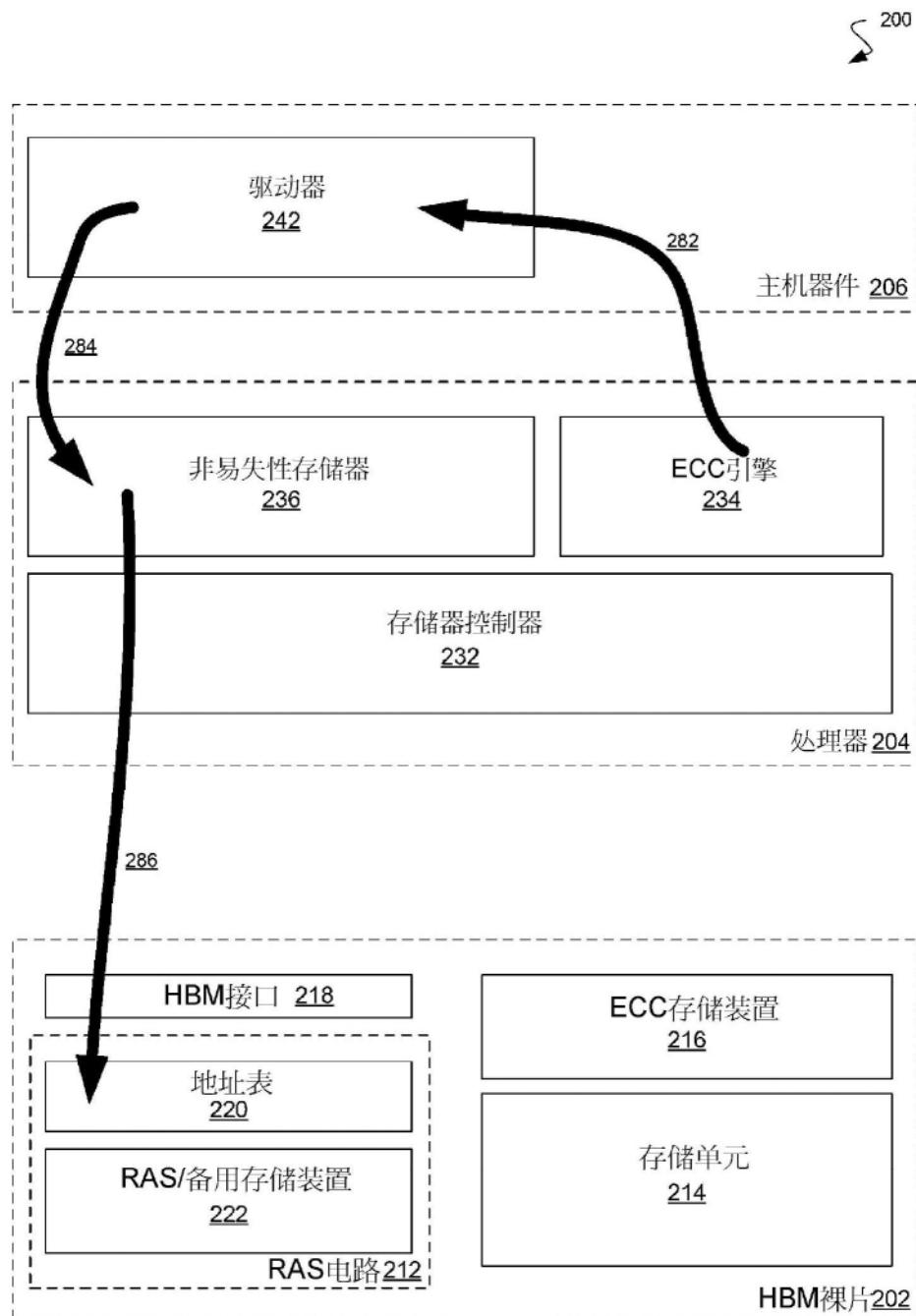

[0114] 图2C是根据所公开主题的系统201的示例性实施例的方块图。在各种实施例中,系统201示出所公开主题的另一变型。

[0115] 在这种实施例中,主机器件206及处理器204可包括与上述相同的组件。HBM裸片202(且具体来说逻辑裸片)可包括其自己的ECC引擎294。在这种实施例中,HBM裸片202可能能够检测存储单元214中的错误并将一或多个坏的存储地址重新映射到备用存储装置222,而无需主机器件206及处理器204的辅助。在各种实施例中,通过使用非易失性存储器,这种重新映射可实质上为永久的。但是,在其他实施例中,在每次重新启动之后均可进行重新映射,即使这并非高效的或期望的。

[0116] 在这种实施例中,ECC引擎294可代替ECC引擎234检测错误。在这种实施例中,主机器件206及处理器204可不知晓任意此种错误。在各种实施例中,主机器件206及处理器204可继续参与上述传统的加黑名单/止用技术,但是由于HBM裸片202内部改善努力,可能不会进行或者仅偶尔进行这种加黑名单/止用。

[0117] 在各种实施例中,如由箭头292所示,HBM裸片202中的ECC引擎294可将坏的存储地址添加到地址表220。坏的存储地址可接着被映射到备用存储装置222的一部分,且如上所述可进行任意未来存储器存取。

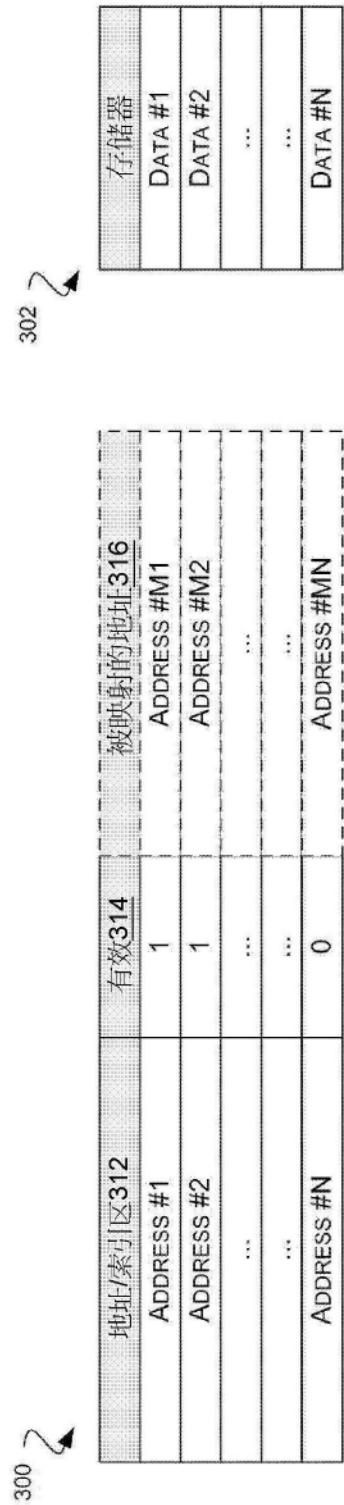

[0118] 图3是根据所公开主题的数据结构300及302的示例性实施例的方块图。在所示出的实施例中,数据结构300及302可表示RAS电路的表及存储装置,如上所述。

[0119] 在所示出的实施例中,数据结构300可表示上述地址表或索引区的一个可能的实施例。在这种实施例中,数据结构300(地址表或索引区)可被配置成存储坏的或有错误的存储地址(或存储区,例如页)。在各种实施例中,可从主机器件或处理器接收这些坏的存储地址。在各种实施例中,数据结构300可被其自己的ECC形式保护。

[0120] 在所示出的实施例中,数据结构300的每一行均可被视为存储地址条目。在这种实施例中,数据结构300可包括指示哪一存储地址是坏的的列312。这可为当进行存储器存取以确定存储器存取应由HBM存储单元实现还是由备用存储装置实现时所检查的列312,如上所述。

[0121] 在所示出的实施例中,每一存储地址条目均可包括有效位或旗标列314。在这种实施例中,这种有效旗标314可指示相应的存储地址条目是否正在使用。在这种实施例中,当主机或处理器将条目写入到数据结构300中时可设置有效旗标314。在另一实施例中,数据结构300可被周期性地(例如,作为重新启动的一部分)擦除且可不包括有效旗标314。

[0122] 在各种实施例中,每一存储地址条目均可包括列的类型字段315。在这种实施例中,可不包括此种字段315,这是因为错误改善可为均匀的或者在所有的地址中实现相同的大小(例如,以字或行计)。然而,在所示出的实施例中,每一地址可与错误改善的不同级别、量或类型(例如1位、1字或各种数目的位)相关联。在一些实施例中,字段315可包括经过已纠正的存储地址的位的数目。然而,在所示出的实施例中,预定义的可为所采用的,例如对于1位来说值为1、对于1字来说值为2等等。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0123] 在所示出的实施例中,每一存储地址条目均可包括被映射的地址列316。在这种实施例中,被映射的地址列316可为备用存储装置中的其中实际上存储有与坏的存储地址(列312)相关联的数据的存储地址或位置。在这种实施例中,当对坏的存储地址进行存储器存取时,所述存取不仅重新定向到备用存储装置而且还重新定址到被映射的存储地址316。在各种实施例中,这可为固定映射。在所示出的实施例中,所述映射可为1对1。然而,在另一实施例中,映射可为组关联的或者采用另一方案。

[0124] 在所示出的实施例中,数据结构300可包括存储地址条目ADDRESS#1,存储地址条目ADDRESS#1具有有效旗标1或被置位(Set)且被映射到地址#M1。同样地,存储地址条目ADDRESS#2可包括有效旗标1或被置位且被映射到地址#M2。可存在多个其他存储地址条目。最终,存储地址条目ADDRESS#N可包括有效旗标0或被清零且被映射到地址#MN。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0125] 在所示出的实施例中,数据结构302可包括多个存储单元,所述多个存储单元分别被配置成将数据存储在相应的存储地址处。在各种实施例中,数据结构302可采用ECC保护。如上所述,当进行对坏的存储地址的存储器写入要求时,可将新的数据存储在备用存储装置或数据结构302中(例如,DATA#1、DATA#2、DATA#N)。如上所述,存储数据的位置可基于存储地址条目。

[0126] 在各种实施例中,数据结构302可为任意大小。在一个这种实施例中,数据结构302可包括150千字节;但是,应理解,以上仅为一个例示性实例,所公开主题并不受限于上述一个例示性实例。在各种实施例中,粒度级别也可为可变的大小(例如,256位)。

[0127] 在一些实施例中,RAS电路可包括多数据结构302和/或300以适应不同的大小或错误图案。举例来说,在各种实施例中,RAS电路可适应以下的错误图案且包括以下的数据结构:单位数据错误、单字数据错误、单行数据错误和/或单列数据错误。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

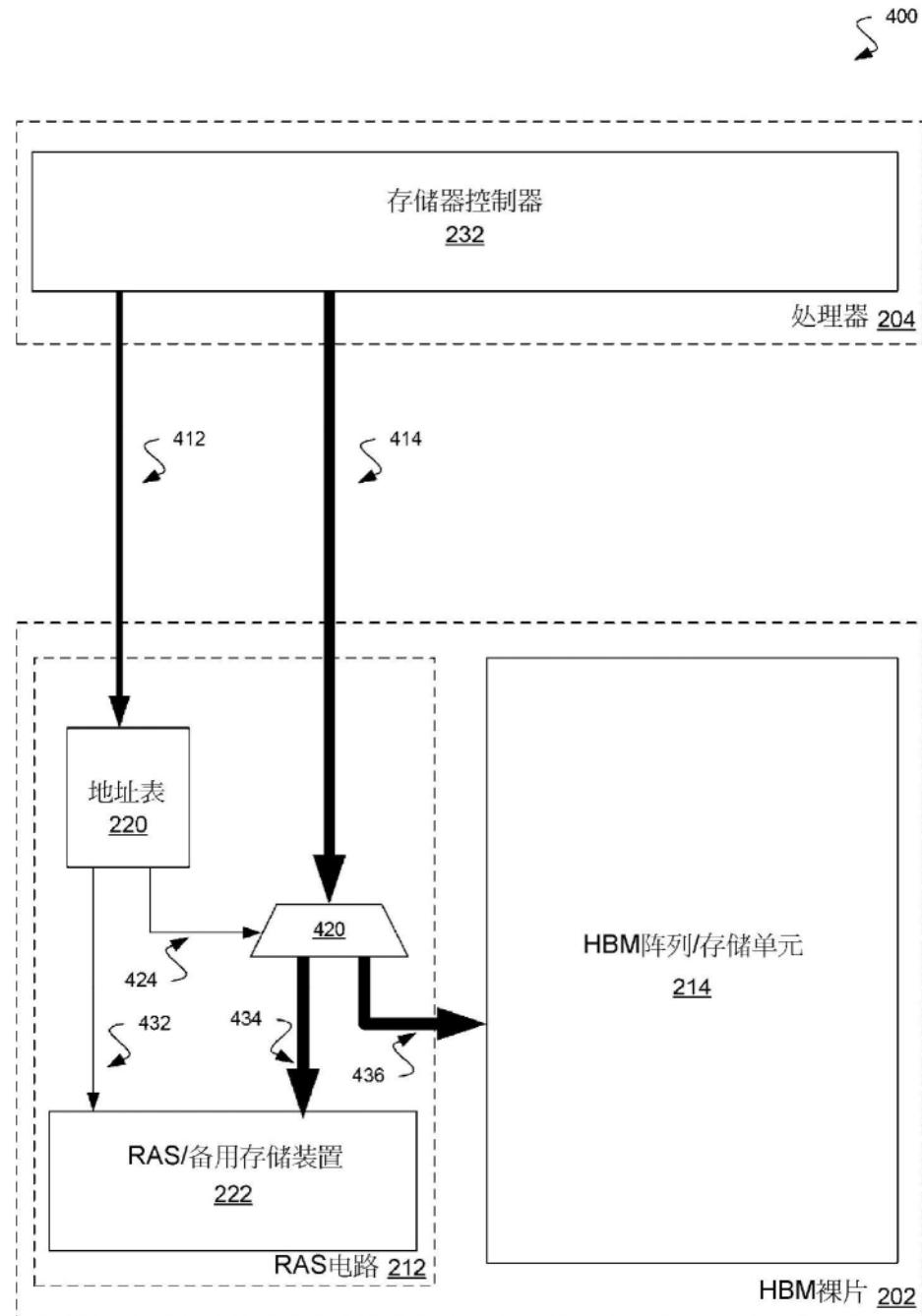

[0128] 图4A是根据所公开主题的系统400的示例性实施例的方块图。在所示出的实施例中,示出存储器写入要求。应理解,以上仅为一个例示性实例,所公开主题并不受限于上述一个例示性实例。

[0129] 在所示出的实施例中,系统400可包括处理器204及HBM裸片202,如上所述。在各种实施例中,处理器204可包括存储器控制器232。HBM裸片202可包括HBM阵列或存储单元214(其可包括ECC存储装置)及RAS电路212,如上所述。在所示出的实施例中,RAS电路212可包括索引区或地址表220以及RAS或备用存储装置222,如上所述。在所示出的实施例中,系统401还可包括命令总线412及数据总线414。

[0130] 在所示出的实施例中,存储器控制器232可向HBM裸片202发出存储器写入要求。在

这种实施例中,命令本身(及存储地址)可通过命令总线412发送且将要写入的数据可通过数据总线414发送。应理解,以上仅为一个例示性实例,所公开主题并不受限于上述一个例示性实例。

[0131] 一旦接收到存储器写入要求,RAS电路212便可判断与存储器存取相关联的存储地址是否在地址表220中列出(且有效)。地址表220可生成地址表命中(如果列出所述地址)或地址表未中(如果未列出所述地址)。这由信号424示出。

[0132] 在所示出的实施例中,RAS电路212可包括解多路复用器(DeMUX)或路由电路420。路由电路420可被配置成根据地址表命中/未中424而将数据路由到存储单元214或备用存储装置222。如上所述,如果出现地址表命中,则路由电路420可将要写入的数据发送到备用存储装置(由箭头434示出)。同样,地址表220可产生被映射的存储地址432,并将被映射的存储地址432发送到备用存储装置222。相反地且还如上所述,如果出现地址表未中,则路由电路420可将要写入的数据发送到存储单元214(由箭头436示出)。同样但未示出,来自命令总线412的存储地址可由存储单元214使用以存储数据。

[0133] 在各种实施例中,可始终将数据写入到存储单元,而不论是否出现地址表命中/未中。在这种实施例中,不需要更改用于对存储单元214实行存储器存取的逻辑以适应RAS电路212的添加。在这种实施例中,当出现地址表命中时,可将数据写入到存储单元214及备用存储装置222二者,但可只忽略存储单元214中的数据,如以下所示。应理解,以上仅为一个例示性实例,所公开主题并不受限于上述一个例示性实例。

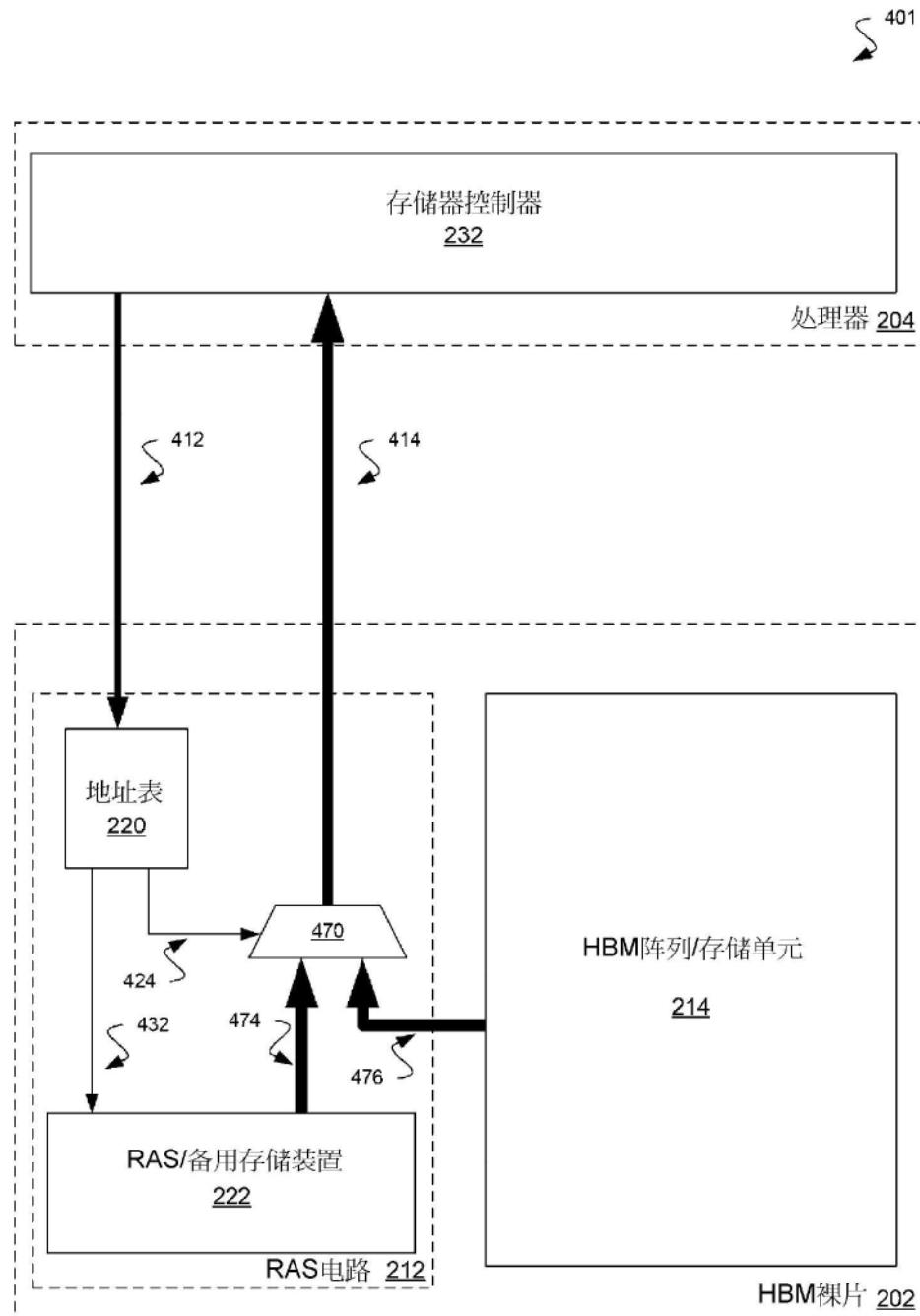

[0134] 图4B是根据所公开主题的系统401的示例性实施例的方块图。在所示出的实施例中,示出存储器读取要求。应理解,以上仅为一个例示性实例,所公开主题并不受限于上述一个例示性实例。

[0135] 在所示出的实施例中,系统401可包括处理器204及HBM裸片202,如上所述。在各种实施例中,处理器204可包括存储器控制器232。HBM裸片202可包括HBM阵列或存储单元214(其可包括ECC存储装置)及RAS电路212,如上所述。在所示出的实施例中,RAS电路212可包括索引区或地址表220以及RAS或备用存储装置222,如上所述。在所示出的实施例中,系统400还可包括命令总线412及数据总线414。

[0136] 在所示出的实施例中,存储器控制器232可向HBM裸片202发出存储器读取要求。在这种实施例中,命令本身(及存储地址)可通过命令总线412发送且数据将通过数据总线414返回。应理解,以上仅为一个例示性实例,所公开主题并不受限于上述一个例示性实例。

[0137] 一旦接收到存储器读取要求,RAS电路212便可判断与存储器存取相关联的存储地址是否在地址表220中列出(且有效)。地址表220可生成地址表命中(如果列出所述地址)或地址表未中(如果未列出所述地址)。这由信号424示出。

[0138] 在所示出的实施例中,RAS电路212可包括多路复用器(multiplexer,MUX)、门控(gating)或路由电路470。路由电路470可被配置成根据地址表命中/未中424而将数据从存储单元214或备用存储装置222路由到数据总线414。如上所述,如果出现地址表命中,则路由电路470可将从备用存储装置取回的数据(由箭头474示出)发送到数据总线414。同样,地址表220可产生被映射的存储地址432,并将被映射的存储地址432发送到备用存储装置222。相反地且还如上所述,如果出现地址表未中,则路由电路470可将从存储单元214取回的数据(由箭头476示出)发送到数据总线414。同样但未示出,来自命令总线412的存储地址

可由存储单元214使用以取回数据。

[0139] 在各种实施例中,可始终将数据写入到存储单元,而不论是否出现地址表命中/未中,如上所述。在这种实施例中,尽管数据被存储在存储单元214的坏的或有错误的存储地址中,然而路由电路470仍会防止将坏的或有错误的数据置于数据总线414上。而是,使用来自备用存储装置222的良好数据。在这种实施例中,数据可始终从存储单元214读取但接着由路由电路470门控。

[0140] 图5是可包括根据所公开主题的原理形成的半导体器件的信息处理系统500的示意性方块图。

[0141] 参照图5,信息处理系统500可包括根据所公开主题的原理构造而成的一个或多个器件。在另一实施例中,信息处理系统500可采用或执行根据所公开主题的原理的一种或多种技术。

[0142] 在各种实施例中,信息处理系统500可包括计算器件,例如(举例来说)膝上型计算机、台式计算机、工作站、服务器、刀片服务器(blade server)、个人数字助理、智能手机、平板计算机及其他适合的计算机或者虚拟机或虚拟机的虚拟计算器件。在各种实施例中,信息处理系统500可由用户(图中未示出)使用。

[0143] 根据所公开主题的信息处理系统500还可包括中央处理器(central processing unit,CPU)、逻辑或处理器510。在一些实施例中,处理器510可包括一个或多个功能单元块(functional unit block,FUB)或组合逻辑块(combinational logic block,CLB)515。在这种实施例中,组合逻辑块可包括各种布尔逻辑运算(例如,与非、或非、非、异或)、稳定化逻辑器件(例如,触发器、锁存器)、其他逻辑器件或其组合。这些组合逻辑运算可以简单方式或复杂方式进行配置,以对输入信号进行处理来实现期望结果。应理解,尽管阐述了同步组合逻辑运算的几个例示性实例,然而所公开主题并不受限于此且可包括异步运算或其混合。在一个实施例中,组合逻辑运算可包括多个互补金属氧化物半导体(complementary metal oxide semiconductor,CMOS)晶体管。在各种实施例中,这些CMOS晶体管可被排列成用于实行逻辑运算的门;但是,应理解,可使用其他技术且所述其他技术处于所公开主题的范围内。

[0144] 根据所公开主题的信息处理系统500还可包括易失性存储器520(例如,随机存取存储器(RAM))。根据所公开主题的信息处理系统500还可包括非易失性存储器530(例如,硬驱动器、光学存储器、与非存储器或闪存存储器)。在一些实施例中,易失性存储器520、非易失性存储器530或它们的组合或一些部分可被称为“存储介质”。在各种实施例中,易失性存储器520和/或非易失性存储器530可被配置成以半永久形式或实质上永久形式存储数据。

[0145] 在各种实施例中,信息处理系统500可包括一个或多个网络接口540,所述一个或多个网络接口540被配置成使信息处理系统500成为通信网络的一部分且通过通信网络进行通信。Wi-Fi协议的实例可包括但不限于电气及电子工程师协会(Institute of Electrical and Electronics Engineers,IEEE)802.11g,IEEE 802.11n。蜂窝协议的实例可包括但不限于:IEEE 802.16m(又名,先进无线城域网(Metropolitan Area Network,MAN)、先进长期演进(Long Term Evolution,LTE)、增强数据速率全球移动通信系统(Global System for Mobile Communications,GSM)演进(Enhanced Data rates for GSM Evolution,EDGE)、演进高速封包存取(Evolved High-Speed Packet Access,HSPA+)。有线

协议的实例可包括但不限于 IEEE 802.3(又名以太网)、光纤信道、电力线通信(例如,家庭插座(HomePlug)、IEEE 1901)。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0146] 根据所公开主题的信息处理系统500还可包括用户接口单元550(例如,显示适配器、触觉接口、人机接口器件)。在各种实施例中,这种用户接口单元550可被配置成从用户接收输入和/或向用户提供输出。也可使用其他种类的器件来实现与用户的交互;举例来说,提供到用户的反馈可为任意形式的感觉反馈,例如,视觉反馈、听觉反馈或触觉反馈;且来自用户的输入可以任意形式接收,包括声学输入、语音输入或触觉输入。

[0147] 在各种实施例中,信息处理系统500可包括一个或多个其他器件或硬件组件560(例如,显示器或监视器、键盘、鼠标、相机、指纹读取器、视频处理器)。应理解,以上仅为几个例示性实例,所公开主题并不受限于上述几个例示性实例。

[0148] 根据所公开主题的信息处理系统500还可包括一条或多条系统总线505。在这种实施例中,系统总线505可被配置成对处理器510、易失性存储器520、非易失性存储器530、网络接口540、用户接口单元550及一个或多个硬件组件560进行通信耦合。经处理器510处理的数据或从非易失性存储器530外部输入的数据可存储在非易失性存储器530中或易失性存储器520中。

[0149] 在各种实施例中,信息处理系统500可包括或执行一个或多个软件组件570。在一些实施例中,软件组件570可包括操作系统(*operating system, OS*)和/或应用。在一些实施例中,OS可被配置成向应用提供一种或多种服务并管理或充当应用与信息处理系统500的各种硬件组件(例如,处理器510、网络接口540)之间的中间介质。在这种实施例中,信息处理系统500可包括一种或多种本地应用,所述一种或多种本地应用可在本地安装(例如,安装在非易失性存储器530内)且被配置成由处理器510直接执行并与OS直接进行交互作用。在这种实施例中,本地应用可包括预先编译的机器可执行代码。在一些实施例中,本地应用可包括脚本解释器(例如,C shell(csh)、苹果脚本(AppleScript)、AutoHotkey)或虚拟执行机(*virtual execution machine, VM*) (例如,Java虚拟机、微软公共语言运行时环境(Microsoft Common Language Runtime)),脚本解释器及虚拟执行机被配置成将源代码或目标代码转换成可执行代码,然后由处理器510来执行所述可执行代码。

[0150] 上述半导体器件可使用各种封装技术来进行包封。举例来说,根据所公开主题的原理构造而成的半导体器件可使用以下中的任意一种来进行包封:层叠封装(package on package, POP)技术、球栅阵列(ball grid array, BGA)技术、芯片尺寸封装(chip scale package, CSP)技术、塑料引线芯片载体(plastic leaded chip carrier, PLCC)技术、塑料双列直插式封装(plastic dual in-line package, PDIP)技术、华夫包装式裸片(die in waffle pack)技术、晶片式裸片(die in wafer form)技术、板上芯片(chip on board, COB)技术、陶瓷双列直插封装(ceramic dual in-line package, CERDIP)技术、塑料公制四方扁平封装(plastic metric quad flat package, PQFP)技术、塑料四方扁平封装(plastic quad flat package, PQFP)技术、小外形集成电路(small outline integrated circuit, SOIC)技术、缩小型小外形封装(shrink small outline package, SSOP)技术、薄型小外形封装(thin small outline package, TSOP)技术、薄型四方扁平封装(thin quad flat package, TQFP)技术、系统级封装(system in package, SIP)技术、多芯片封装(multi-

chip package,MCP)技术、晶片级构造封装(wafer-level fabricated package,WFP)技术、晶片级处理堆叠封装(wafer-level processed stack package,WSP)技术或所属领域中的技术人员将知晓的其他技术。

[0151] 方法步骤可由一个或多个可编程处理器执行计算机程序来实行,以通过对输入数据进行操作并产生输出来实行功能。方法步骤还可由专用逻辑电路(例如,现场可编程门阵列(field programmable gate array,FPGA)或应用专用集成电路(application-specific integrated circuit,ASIC))来实行,且装置可被实施为专用逻辑电路。

[0152] 在各种实施例中,计算机可读介质可包括指令,所述指令在被执行时会使器件实行方法步骤的至少一部分。在一些实施例中,计算机可读介质可包括在磁性介质、光学介质、其他介质或其组合(例如,压缩盘只读存储器(compact disc read only memory,CD-ROM)、硬驱动器、只读存储器、闪存驱动器)中。在这种实施例中,计算机可读介质可为有形的及以非暂时方式实施的制品。

[0153] 尽管已参照示例性实施例阐述了所公开主题的原理,然而对所属领域中的技术人员来说显而易见的是,在不背离这些所公开概念的精神及范围的条件下,可对其作出各种改变及修改。因此,应理解,以上实施例并非限制性的,而是仅为示意性的。因此,所公开概念的范围将由以上权利要求及其等效范围所许可的最广范围的解释来确定,而不应受上述说明约束或限制。因此,应理解,随附权利要求旨在涵盖落于实施例的范围内的所有这种修改及改变。

S

100

图1

图2A

图2B

图2C

图3

图4A

图4B

图5