(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-200692

(P2004-200692A)

(43) 公開日 平成16年7月15日(2004.7.15)

(51) Int.Cl.<sup>7</sup>

H01L 27/146

H01L 27/14

F 1

H01L 27/14

H01L 27/14

H01L 27/14

テーマコード(参考)

4M118

C

K

D

審査請求 未請求 請求項の数 8 O L (全 12 頁)

|              |                              |          |                                                                                                                       |

|--------------|------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2003-417404 (P2003-417404) | (71) 出願人 | 390041542<br>ゼネラル・エレクトリック・カンパニー<br>GENERAL ELECTRIC CO<br>MPANY<br>アメリカ合衆国、ニューヨーク州、スケネ<br>クタディ、リバーロード、1番<br>100093908 |

| (22) 出願日     | 平成15年12月16日 (2003.12.16)     | (74) 代理人 | 弁理士 松本 研一<br>100105588                                                                                                |

| (31) 優先権主張番号 | 10/322,117                   | (74) 代理人 | 弁理士 小倉 博<br>100106541                                                                                                 |

| (32) 優先日     | 平成14年12月17日 (2002.12.17)     | (74) 代理人 | 弁理士 伊藤 信和<br>ジョージ・エドワード・ポッシン<br>アメリカ合衆国、ニューヨーク州、ニスカ<br>ユナ、アルゴンキン・ロード、2361番<br>最終頁に続く                                  |

| (33) 優先権主張国  | 米国(US)                       | (72) 発明者 |                                                                                                                       |

(54) 【発明の名称】イメージング・アレイ及びその製作方法

## (57) 【要約】

【課題】イメージング・アレイの画素形成の方法を提供する。

【解決手段】イメージング・アレイ(10)を製作するための方法は、第1の誘電バリア(66)を形成させること、この第1の誘電バリア上にゲート(50)と少なくとも同じ広がりをもつ光遮断素子(68)を形成させること、並び第1の誘電バリア及び光遮断素子の上に、第1の誘電バリアとの間で光遮断素子を包封するように第2の誘電バリア(70)を形成すること、を含む。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

第 1 の誘電バリア ( 6 6 ) と、

前記第 1 の誘電バリア上に形成させた、ゲート電極 ( 5 0 ) と少なくとも同じ広がりをもつ光遮断素子 ( 6 8 ) と、

前記第 1 の誘電バリア及び前記光遮断素子の上に形成させた第 2 の誘電バリア ( 7 0 ) であって、前記第 1 の誘電バリアと該第 2 の誘電バリアの間に前記光遮断素子を包封している第 2 の誘電バリア ( 7 0 ) と、

を備えるイメージング・アレイ ( 1 0 )。

**【請求項 2】**

前記ゲート電極 ( 5 0 ) 上に形成させたゲート誘電体層 ( 5 6 ) と、

前記ゲート誘電体層上に形成させた半導体層 ( 5 8 ) と、

前記半導体層上に形成させたソース接点 ( 6 0 ) 及びドレイン接点 ( 6 2 ) と、

をさらに備える請求項 1 に記載のイメージング・アレイ ( 1 0 )。

**【請求項 3】**

前記第 1 の誘電バリア ( 6 6 ) が、概ね 2 0 n m と概ね 5 0 n m 厚の間にある第 1 のバリア部分 ( 1 0 0 ) 、及び概ね 2 0 0 n m と概ね 7 0 0 n m 厚の間にある第 2 のバリア部分 ( 1 0 2 ) を備えている、請求項 1 に記載のイメージング・アレイ ( 1 0 )。

**【請求項 4】**

前記光遮断素子 ( 6 8 ) が概ね 5 0 n m と概ね 2 0 0 n m 厚の間にあり、かつ前記第 2 の誘電バリア ( 7 0 ) が概ね 3 0 0 n m と概ね 8 0 0 n m 厚の間にある、請求項 1 に記載のイメージング・アレイ ( 1 0 )。

**【請求項 5】**

前記光遮断素子 ( 6 8 ) と一体に形成したデータ線 ( 3 0 ) をさらに備える請求項 1 に記載のイメージング・アレイ ( 1 0 )。

**【請求項 6】**

前記光遮断素子 ( 6 8 ) と一体に形成した共通線 ( 4 0 ) をさらに備える請求項 1 に記載のイメージング・アレイ ( 1 0 )。

**【請求項 7】**

前記第 1 のバリア部分 ( 1 0 0 ) が酸化ケイ素を含み、かつ前記第 2 のバリア部分が窒化ケイ素を含む、請求項 3 に記載のイメージング・アレイ ( 1 0 )。

**【請求項 8】**

前記光遮断素子 ( 6 8 ) が、モリブデン、アモルファス・シリコン、クロム、銅、タンタル及びアルミニウム材料のうちの少なくとも 1 つを含む、請求項 1 に記載のイメージング・アレイ ( 1 0 )。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、全般的にはイメージング・アレイに関し、さらに詳細には、イメージング・アレイの画素形成に関する。

**【背景技術】****【0 0 0 2】**

X 線を検出するためのイメージング・アレイは、典型的には、シンチレーション材料と結合させたフォトセンサ・アレイを含んでいる。シンチレータで吸収された放射によって光子を発生させ、この光子を続いてフォトダイオードなどのフォトセンサに渡している。この光子はフォトセンサ内で吸収され、入射光子フラックスに対応した電気信号が発生される。水素添加アモルファス・シリコン ( a - S i : H ) は、a - S i : H の光電特性が好都合でありかつこうしたデバイスの製作が比較的容易であるために、フォトセンサの製作によく使用されている。詳細には、フォトダイオードなどの複数の感光性素子を、薄膜トランジスタ ( T F T ) などの必要な任意の制御または切り替え素子と接続して比較的大

10

20

30

40

50

型のアレイの形で形成させることができる。放射線検出器及びディスプレイ・アレイは、典型的には、大型の基板上に製作しており、この基板上には、導体、半導体及び絶縁性の材料からなる層の被着及びパターン形成を介して、TFT、アドレス線、コンデンサ、フォトセンサなどのデバイスを含め多くのコンポーネントを形成させている。

【発明の開示】

【発明が解決しようとする課題】

【0003】

こうしたTFTアレイに関する少なくとも1つの周知の製作工程は、典型的には、最底部ゲートTFTと、複数のデータ及びスキャン・アドレス線とを製作することを含む。周知の最底部ゲートTFTの幾つかでは、その最底部ゲート金属はチャンネル領域を遮蔽している、すなわちバックライトからの光を阻止する光遮断素子の役割を果たしている。光子がTFT内に望ましくない漏れを生じさせる可能性があるため、この光遮断層は望ましい。例えば、ディジタルX線パネルでは、TFT領域を光子に直接露出させているデバイスの最上面に被着させたシンチレータから光が生成される。したがって、TFTチャンネル領域を望ましくない光から遮蔽するために、追加のフォトリソグラフィ・レベルを要するような追加の光遮断層が必要となる。

【課題を解決するための手段】

【0004】

一態様では、イメージング・アレイを製作する方法を提供する。この方法は、第1の誘電バリアを形成させるステップと、この第1の誘電バリア上にゲートと少なくとも同じ広がりをもつ光遮断素子を形成するステップと、第1の誘電バリア及び光遮断素子の上に第1の誘電バリアとの間で光遮断素子を包封するような第2の誘電バリアを形成するステップと、を含む。

【0005】

別の態様では、イメージング・アレイを提供する。このイメージング・アレイは、第1の誘電バリアと、ゲート電極と少なくとも同じ広がりをもつように第1の誘電バリア上に形成させた光遮断素子と、第1の誘電バリアとの間で光遮断素子を包封するように第1の誘電バリア及び光遮断素子の上に形成させた第2の誘電バリアと、を含む。

【0006】

また別の態様では、医用イメージング・システムを提供する。この医用イメージング・システムは、放射線源と、この放射線源と動作可能に結合させた放射線検出器と、を含む。この放射線検出器は、第1の誘電バリアと、ゲート電極と少なくとも同じ広がりをもつように第1の誘電バリア上に形成させた光遮断素子と、第1の誘電バリアとの間で光遮断素子を包封するように第1の誘電バリア及び光遮断素子の上に形成させた第2の誘電バリアと、を含む。

【発明を実施するための最良の形態】

【0007】

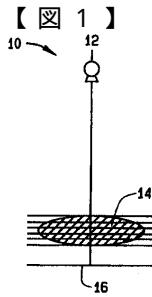

図1は、周知のイメージング・システム10の見取り図である。実施の一形態では、イメージング・システム10は、GE Medical Systems (Milwaukee, Wisconsin) から市販されているSennovision 2000D (ただし、これに限らない)などの医用イメージング・システムである。イメージング・システム10は、円錐形状のビームを投射する放射線源12を含む。実施の一形態では、放射線源12はX線源12であり、またその円錐状ビームはX線ビームである。このX線ビームは被検体14 (すなわち、患者などの撮像対象) を通過する。X線ビームは、被検体14によって減衰を受けた後、放射線検出器16上に当たる。

【0008】

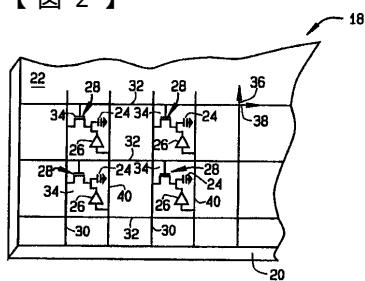

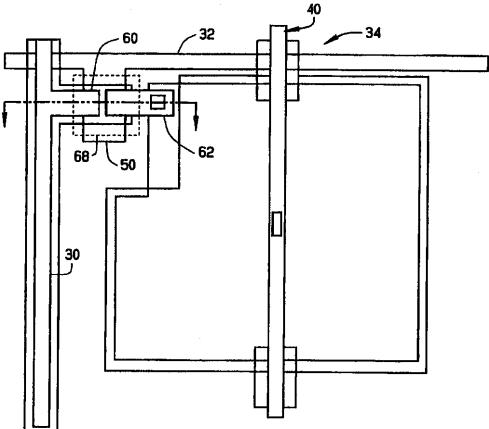

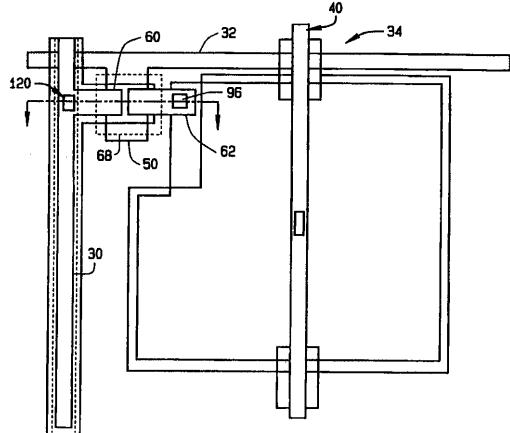

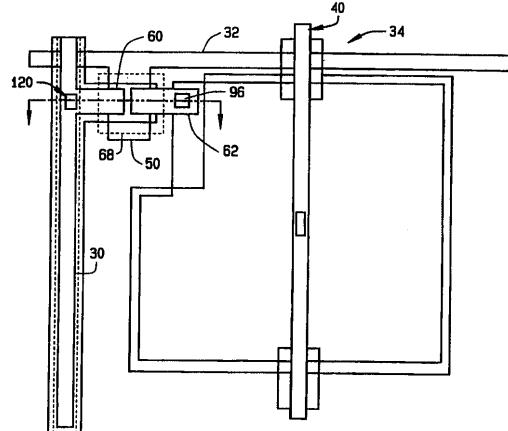

図2は、イメージング・システム10 (図1参照) で使用できる放射線検出器18である。放射線検出器18は、画素アレイ22 (フォトセンサ・アレイと呼ぶこともある) をその上に配置させた基板20を含む。実施の一形態では、フォトセンサ・アレイ22は、コンデンサ24、フォトダイオード26、TFTなどの切り替えデバイス28などの複数

の電子コンポーネントを含んでいる。TFT28は、それぞれのコンデンサ24及びフォトダイオード26をそれぞれのデータ線30に選択的に接続させるためにアレイ22上に配置させている。別の実施形態では、フォトセンサ・アレイ22はコンデンサ24を含まない。フォトセンサ・アレイ22はさらに、複数の個々の画素34をアドレス指定するために複数のスキャン線32を含んでいる。データ線30は画素アレイ22の第1の軸36の方向を向いており、またスキャン線32は画素アレイ22の第2の軸38の方向を向いている。画素アレイ22の第1の軸36と第2の軸38は、互いに実質的に直交するように配置している。

#### 【0009】

図2において図示を容易にするため、フォトセンサ・アレイ22全体に広がっているデータ線30、スキャン線32及び共通線40のうちの数本のみを図示している。データ線30、スキャン線32及び共通線40は、フォトセンサ・アレイ22内の個々の画素34が1本のデータ線30、1本のスキャン線32及び1本の共通線40によってアドレス指定可能となるように横列と縦列の形に配列させている。データ線30、スキャン線32及び共通線40は、モリブデン、クロム及び/またはアルミニウムなどの導体材料を含んでいる。コンデンサ24は、フォトダイオード26と電気的に並列に接続すると共に、TFT28を介してデータ線30と電気的に結合させている。フォトダイオード26は、アレイ22の入射光子に応答する部分を形成していると共に、検出した入射光に対応した電荷を発生させる。X線エネルギーは、フォトセンサ・アレイ22の表面の近傍に配置させたヨウ化セシウムなどの蛍光体層(図示せず)内での吸収によって、可視光エネルギーに変換される。コンデンサ24はフォトダイオード26内で生成された電荷を蓄積し、またスキャン線32がアドレス指定されたときにこの蓄積した電荷をTFT28を通じて放電させる。一部の電荷はフォトダイオード26の自己キャパシタンス上にも蓄積される。

#### 【0010】

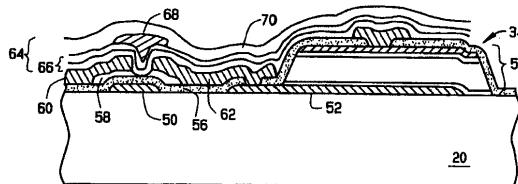

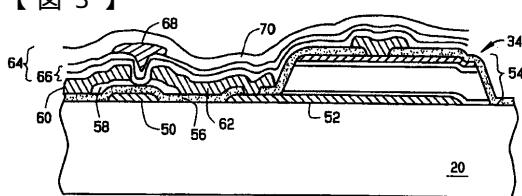

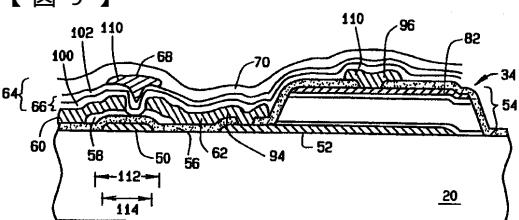

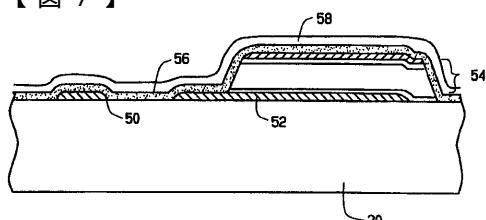

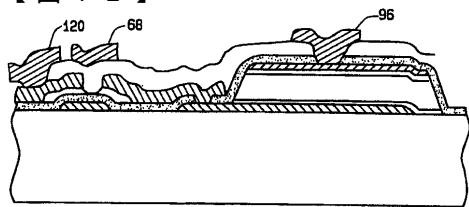

図3は、基板20上に形成させた画素34の一部分の断面像である。図4は、図3に示す画素34の一部分の上面像である。本明細書で使用する場合、「形成させる(form ed)」ことには、パターン形成(patterning)、マスキング、被着(deposition)、及びエッチング(ただし、これらに限らない)など、画素34の各コンポーネントを製作するための工程を含む。例示的な実施の一形態では、本明細書に記載した半導体層及び誘電体層のすべてをプラズマ化学蒸着法(Plasma Enhanced Chemical Vapour Deposition: PECVD)によって被着させている。画素34は、基板20の表面を覆って広がるような、厚さが概ね等しいTFTゲート電極50とダイオード最底部接点52を含んでいる。画素34はさらに、ダイオード最底部接点52上に形成させたダイオード・スタック54を含んでいる。実施の一形態では、ダイオード・スタック54はPINダイオードを含んでいる。PINダイオードは、n+材料層上に被着させた実質的に真性のa-Si層上にp+材料層を被着させて含んでいる。実施の一形態では、ダイオード・スタック54上にダイオード最上部接点(図示せず)を被着、パターン形成及びエッチングさせている。別の実施形態では、このダイオード最上部接点を形成させていない。次いで、ゲート電極50、ダイオード最底部接点52及びダイオード・スタック54の露出部分上にゲート誘電体層56を形成させる。次いで、誘電体層56上に半導体層58を被着させる。ゲート誘電体層56及び半導体層58のパターン形成及びエッチングの後、ソース電極60及びドレイン電極62を被着、マスクキング及びエッティングさせている。画素34はさらに、第1の誘電バリア66、光遮断素子68及び第2の誘電バリア70を含んだ光透過性バリア層64を含む。ソース電極60、ドレイン電極62及び誘電体層56の露出部分上には、第1の誘電バリア66を形成させる。次いで、第1の誘電バリア66上に光遮断素子68を形成させ、続いて第2の誘電バリア70を形成させる。この例示的な実施形態では、光遮断素子68はゲート電極50と少なくとも同じ広がりをもち、また第2の誘電バリア70は第1の誘電バリア66及び光遮断素子68上に形成させ、第1の誘電バリア66と第2の誘電バリア70の間で光遮断素子68を包封している。次いで、イメージング・アレイをシンチレータに結合

10

20

30

40

50

させ、さらにこのシンチレータを封止している。次いでこのイメージング・アレイは、イメージング・システム 10 内で使用することができる検出器 18 を形成させるように複数の外部接点に接続している。

#### 【0011】

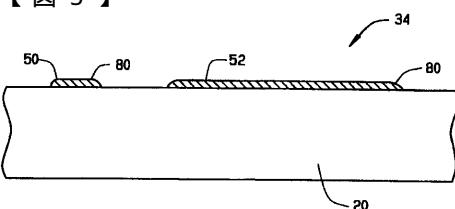

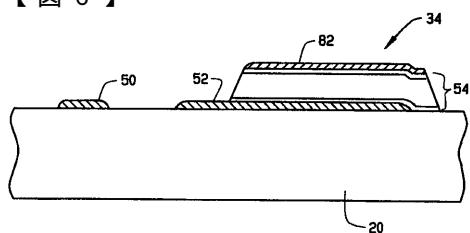

図 5 及び 6 は、図 3 に示す画素 34 の一部分に関する、初期製作ステージと第 1 の後続製作ステージのそれぞれの期間における断面像である。半導体層及び誘電体層は P E C V D によって被着させている。例示的な実施の一形態では、第 1 の金属層 80 を被着、パターン形成かつエッチングし、スキャン線 32 ( 図 2 参照 ) と一緒にとなったゲート電極 50 、及びダイオード最底部接点 52 を形成させている。このパターン形成工程には、フォトレジストを被着すること、このフォトレジストを所望のパターンに従って露出すること、フォトレジストを処理し所望の寸法に対応した選択パターンを有するマスクを残してその一部分を除去すること(ただし、これらに限るものではない)が含まれる。実施の一形態では、第 1 の金属層 80 は概ね 100 オングストローム( )と概ね 4000 厚の間である。別の実施形態では、第 1 の金属層 80 は概ね 2000 である。別法として、第 1 の金属層 80 は概ね 1000 と概ね 3000 厚の間である。第 1 の金属層 80 は、アルミニウム、クロム、銀及び / またはモリブデン(ただし、これらに限るものではない)を含むことがある。

10

#### 【0012】

ゲート金属エッチングに続いて、パターン形成ステップを全く介在させずにダイオード最底部接点 52 上にダイオード・スタック 54 を被着させる。実施の一形態では、ダイオード・スタック 54 上にダイオード最上部接点 82 を被着させる。実施の一形態では、そのダイオード最上部接点はインジウム・スズ酸化物( ITO )などの透明な導体によって形成している。ダイオード・スタック 54 及びダイオード最上部接点 82 はパターン形成しエッチングしている。この同じマスクを使用してダイオード最上部接点 82 に対して第 1 のウェット・エッチングまたはドライ・エッチングし、続いてダイオード・スタック 54 をドライ・エッチングすることがある。別法として、2 つの別々のマスキング・ステップを用いてダイオード最上部接点 82 をダイオード・スタック 54 と比べてより小さく形成し、続いてダイオード・スタック 54 のパターン形成及びエッチングを行うことができる。

20

#### 【0013】

図 7 及び 8 は、図 3 に示す画素 34 の一部分に関する、第 2 の後続製作ステージと第 3 の後続製作ステージのそれぞれの期間における断面像である。この例示的な実施形態では、ゲート電極 50 、ダイオード・スタック 54 、並びにダイオード最底部接点 52 及び基板 20 の露出部分上にゲート誘電体層 56 を被着させている。実施の一形態では、誘電体層 56 は概ね 25 ナノメートル( nm )と概ね 1000 nm 厚の間である。別の実施形態では、誘電体層 56 は概ね 150 nm と概ね 1250 nm 厚の間にある。また別の実施形態では、誘電体層 56 は概ね 250 nm 厚である。誘電体層 56 は、窒化ケイ素( SiN x )及び酸化ケイ素( SiO x )を含む(ただし、これらに限るものではない)。

30

#### 【0014】

誘電体層 56 上には半導体材料層 58 を被着させている。実施の一形態では、半導体材料層 58 は概ね 10 nm と概ね 300 nm 厚の間にある。別の実施形態では、半導体材料層 58 は概ね 200 nm 厚である。また別の実施形態では、半導体材料層 58 は概ね 30 nm と概ね 70 nm 厚の間にある。半導体材料層 58 は、実質的に真性のアモルファス・シリコン(ただし、これに限るものではない)を含むことがある。誘電体層 56 及び半導体材料層 58 は、所望によりダイオード最底部接触部 90 及びダイオード最上部接触部 92 を露出させるようにして、パターン形成しエッチングさせるか、あるいは共被着しパターン形成しつつエッチングさせるかしている。

40

#### 【0015】

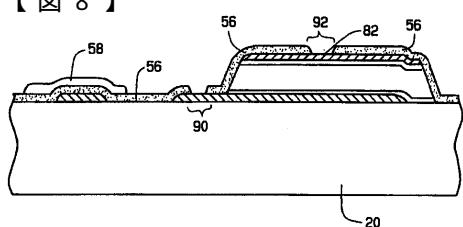

図 9 は、図 3 に示す画素 34 の一部分に関する第 4 の後続製作ステージの間ににおける断面像である。誘電体層 56 、半導体材料層 58 及びダイオード最底部接点 52 の露出部分

50

には第2の金属層94を被着させている。実施の一形態では、第2の金属層94は概ね50nmと概ね1000nm厚の間にある。別の実施形態では、第2の金属層94は概ね500nm厚である。また別の実施形態では、第2の金属層94は概ね150nmと概ね350nm厚の間にある。第2の金属層94は、モリブデン、アルミニウム及び／またはクロム（ただし、これらに限るものではない）を含むことがある。第2の金属層94は、ソース電極60、データ線30と一体となったドレイン電極62、並びにダイオード最上部接点82へのビア96を形成するようにパターン形成しエッチングしている。

#### 【0016】

第1の誘電バリア66、光遮断素子68及び第2の誘電バリア70を含む光透過性バリア層64は、ソース電極60、ドレイン電極62、ダイオード最底部接点52の露出部分、及びダイオード・スタック54上に形成させている。実施の一形態では、第1の誘電バリア66は第1のバリア部分100及び第2のバリア部分102を含んでいる。第1のバリア部分100は概ね20nmと概ね50nm厚の間にある。別の実施形態では、第1のバリア部分100は概ね30nm厚である。また別の実施形態では、第1のバリア部分100は概ね5nmと概ね65nm厚の間にある。第1のバリア部分100はSiO<sub>x</sub>（ただし、これに限るものではない）を含む。第2のバリア部分102は概ね200nmと概ね700nm厚の間にある。別の実施形態では、第2のバリア部分102は概ね450nm厚である。また別の実施形態では、第2のバリア部分102は概ね350nmと概ね550nm厚の間にある。第2のバリア部分102はSiN（ただし、これに限るものではない）を含む。実施の一形態では、第2のバリア部分102は概ね摂氏150度（）と概ね260°の間にある温度で被着させている。別の実施形態では、第2のバリア部分102は概ね240°の温度で被着させている。

#### 【0017】

ゲート50と少なくとも同じ広がりをもつ光遮断素子68を形成させるために第1の誘電バリア66上に第3の金属層110を被着させている。この例示的な実施形態では、光遮断素子68はゲート50と同じ広がりをもつ。実用上は、光遮断素子68は、光遮断素子68の長さ112がゲート50の長さ114を超えるようにしこれによりゲート50の露出部分が覆われるようにして形成させている。光遮断素子68は概ね50nmと概ね200nm厚の間にある。別の実施形態では、光遮断素子68は概ね125nm厚である。また別の実施形態では、光遮断素子68は概ね10nmと概ね500nm厚の間にある。光遮断素子68は、モリブデン(Mo)、アモルファス・シリコン、クロム、タンタルまたはアルミニウムから製作することができる。この例示的な実施形態では、光遮断素子68はa-Siの縁を越えて概ね2マイクロメートル(μm)以上の広がりをもたせ、この部分をゲート50に重複させて、大面積の基板上のフォトリソグラフィ及びMoのオーバーエッチングの間での整列不良のすべてに対する補償を容易にしている。次いで、実質的にITOに浸透しない硝酸及びリン酸を含んだCyanatek12-S（ただし、これに限らない）などの標準Moエッチング剤を用いてMoをウェット・エッチングしている。次いでパターン形成用フォトレジストを酸素内プラズマ・アッシングまたはウェット・ストリッピングによって除去する。この例示的な実施形態では、光遮断素子68はイメージング・アレイ内にパターン形成し、アレイの外部の接触パッドやその他のイメージャ構造上にはパターン形成していない。Moを用いて光遮断素子68を形成することによって、不透明ポリマーによる場合と比べてより大きな光吸収の発生を容易にし、これによって、作業をより容易にするような本明細書に記載するより薄い層の使用が可能となる。

#### 【0018】

次いで、光遮断素子68と、第1の誘電バリア66の露出部分との上に第2の誘電バリア70を形成させる。第2の誘電バリア70は概ね300nmと概ね1500nm厚の間にある。別の実施形態では、第2の誘電バリア70は概ね500nm厚である。また別の実施形態では、第2の誘電バリア70は概ね400nmと概ね600nm厚の間にある。第2の誘電バリア70は、窒化ケイ素(SiNx)を含む（ただし、これに限るものではない）。第2の誘電バリア70は概ね150°と概ね260°の間にある温度で被着させ

10

20

30

40

50

ている。別の実施形態では、第2の誘電バリア70は概ね240 の温度で被着させている。この例示的な実施形態では、第1の誘電バリア66と第2の誘電バリア70との合成厚みは、概ね1マイクロメートルである。さらに、光遮断素子68上に形成させた第2の誘電バリア70に対するパターン形成は、光遮断素子68が光透過性バリア64内に完全に包封されているため光透過性バリア64内に全く光遮断素子68を組み入れない場合に実施すると想定されるパターン形成と同一である。

#### 【0019】

別の例示的な実施形態では、第2の金属層94及び第3の金属層110を被着させた時点で5つの独特的な金属構造を形成することができる。これらの構造には、データ線30、TFTソース接点60、光遮断素子68、TFTドレイン接点62及びダイオード最底部接点52に対するコネクタ、並びに共通線40(図2参照)が含まれる。この例示的な実施形態では、Moを使用する場合、データ線30は概ね400nmを超える厚さである。Moを使用する場合、TFTソース接点60、TFTドレイン接点62及び共通線40は概ね100nmを超える厚さであり、また本明細書に記載したように光遮断素子68も同じ厚さを有する。データ線30、TFTソース接点60、TFTドレイン接点62及び光遮断素子68の厚さは、複数のイメージヤ抵抗要件と工程の頑強性に基づいて選択する。実施の一形態では、データ線30は概ね600nmと1500nm厚の間にある。別の実施形態では、データ線30は概ね1000nm厚である。

#### 【0020】

例えば、ソース60、ドレイン62及び光遮断素子68は、第2の金属被覆94または第3の金属被覆110内に被着させることができる。この例示的な実施形態では、第2の金属被覆94によってTFTソース接点60及びTFTドレイン接点62を形成するが、TFTソース接点60とTFTドレイン接点62を電気的にショートさせることになるため光遮断素子68は形成されていない。実施の一形態では、データ線30の形成は、ソース60と同時ではなく、すなわちデータ線側面と同時にではなく、また第3の金属層110の被着前にデータ線30がTFTと電気的に接続できるようにバリア66の第1の部分内にビア(図示せず)を形成させている。ビアを形成させる場合、第1のバリア部分100は概ね100nmと概ね300nm厚の間とする。例示的な実施の一形態では、第1のバリア部分100は概ね200nm厚である。実施の一形態では、第2のバリア部分102は概ね700nmと概ね900nm厚の間にある。例示的な実施の一形態では、第2のバリア部分102は概ね800nm厚である。

#### 【0021】

表1は、複数の実施形態について、第2の誘電バリア70を被着する前において第2の金属層94と第3の金属層110の各被着時点で形成できる構造の組み合わせを示すと共に、共通／ダイオード最上部ビア96及びデータ／ソース・ビア120を第1のバリア部分100内にどの時点で形成できるかを示している。

#### 【0022】

##### 【表1】

| 実施形態 | データ線 | ソース | 光遮断 | ドレイン | 共通線 | データ／ソース・ビア | 共通／ダイオード・ビア |

|------|------|-----|-----|------|-----|------------|-------------|

| A    | 第2層  | 第2層 | 第3層 | 第2層  | 第2層 | 無          | 無           |

| B    | 第3層  | 第2層 | 第3層 | 第2層  | 第2層 | 有          | 無           |

| C    | 第3層  | 第2層 | 第3層 | 第2層  | 第3層 | 有          | 有           |

| D    | 第2層  | 第2層 | 第3層 | 第2層  | 第3層 | 無          | 有           |

#### 【0023】

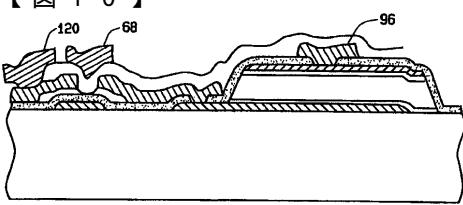

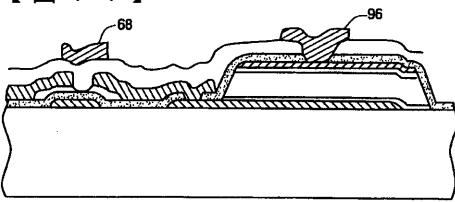

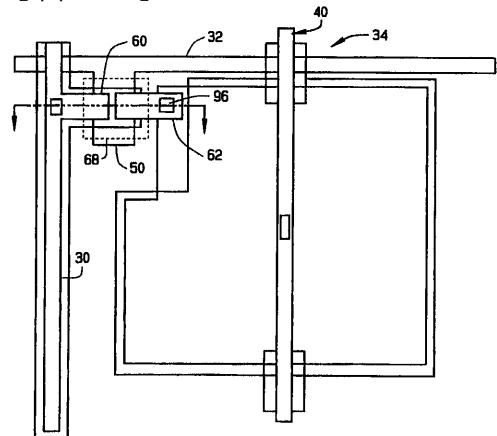

この例では、実施形態Aを本明細書では図9に記載している。図10は、実施形態Bに記載した放射線検出器の画素の一部分の断面像である。図11は図10に示した画素の一部分の上面像である。図のように実施形態Bは、例えば蛍光透視モードで使用する大型のイメージヤ向けに太いデータ線金属を用いてデータ線抵抗の低下を容易にすると共に、ソ

10

20

30

40

50

ース 6 0 及びドレイン 6 2 についてデータ線 3 0 と別のパターン形成を可能としている。実施形態 B に示すように、ソース 6 0 、ドレイン 6 2 及び共通線 4 0 は同じ金属から形成させており、概ね 1 0 0 nm 厚とすることができます。

#### 【 0 0 2 4 】

図 1 2 は、実施形態 C に記載した放射線検出器の画素の一部分の断面像である。図 1 3 は、図 1 2 に示す画素の一部分の上面像である。図 1 4 は実施形態 D に記載した放射線検出器の画素の一部分の断面像である。図 1 5 は図 1 4 に示す画素の一部分の上面像である。別の例示的な実施形態においては、実施形態 C 及び D では光遮断素子 6 8 を共通線 4 0 に接続することができ、また実施形態 B 及び C では光遮断素子 6 8 をデータ線 3 0 に接続することができる、ただし、実施形態 C では光遮断素子 6 8 を共通線 4 0 とデータ線 3 0 の両方には接続しない。実施形態 B 、 C 及び D によって、光遮断素子 6 8 を確実に電気的にフロート状態にさせないことが容易になる。10

#### 【 0 0 2 5 】

本明細書に記載したように、簡約マスクセット・イメージャ工程は、ゲート 5 0 、スキャン線 3 2 及びフォトダイオード最底部接点パッド 5 2 を形成し、次いで、フォトダイオード 5 4 及び薄膜トランジスタを形成することを含む。最後に、第 1 の誘電バリア 6 6 、光遮断素子 6 8 及び第 2 の誘電バリア 7 0 を含む光透過性バリア層 6 4 は、ソース電極 6 0 、ドレイン電極 6 2 、ダイオード最底部接点 5 2 の露出部分、及びダイオード・タック 5 4 上に形成させている。この光透過性バリア層 6 4 によって、その基礎構造の周辺光からの保護を容易にすると共に、この光透過性バリア層 6 4 は、X 線イメージャを形成させる場合にシンチレータをその上に配置させる層となっている。20

#### 【 0 0 2 6 】

本発明について具体的な様々な実施形態に関して記載してきたが、当業者であれば、本特許請求の範囲の精神及び趣旨の域内の修正を伴って本発明を実施できることが理解されよう。

#### 【 図面の簡単な説明 】

#### 【 0 0 2 7 】

【図 1】従来技術のイメージング・システムの見取り図である。

【図 2】フォトセンサ・アレイの代表的な画素の概要図である。

【図 3】放射線検出器の画素の一部分の断面像である。30

【図 4】図 3 に示した画素の一部分の上面像である。

【図 5】初期製作ステージ中における図 3 に示した画素の一部分の断面像である。

【図 6】第 1 の後続製作ステージにおける図 3 に示した画素の一部分の断面像である。

【図 7】第 2 の後続製作ステージにおける図 3 に示した画素の一部分の断面像である。

【図 8】第 3 の後続製作ステージにおける図 3 に示した画素の一部分の断面像である。

【図 9】第 4 の後続製作ステージにおける図 3 に示した画素の一部分の断面像である。

【図 1 0】実施形態 B に記載した放射線検出器の画素の一部分の断面像である。

【図 1 1】図 1 0 に示した画素の一部分の上面像である。

【図 1 2】実施形態 C に記載した放射線検出器の画素の一部分の断面像である。

【図 1 3】図 1 2 に示した画素の一部分の上面像である。40

【図 1 4】実施形態 D に記載した放射線検出器の画素の一部分の断面像である。

【図 1 5】図 1 4 に示した画素の一部分の上面像である。

#### 【 符号の説明 】

#### 【 0 0 2 8 】

1 0 イメージング・システム

1 2 放射線源

1 4 被検体

1 6 放射線検出器

1 8 放射線検出器

2 0 基板

40

50

|       |                  |    |

|-------|------------------|----|

| 2 2   | フォトセンサ・アレイ、画素アレイ |    |

| 2 4   | コンデンサ            |    |

| 2 6   | フォトダイオード         |    |

| 2 8   | TFT、切り替えデバイス     |    |

| 3 0   | データ線             |    |

| 3 2   | スキャン線            |    |

| 3 4   | 画素               |    |

| 3 6   | 画素アレイの第の軸        |    |

| 3 8   | 画素アレイの第の軸        |    |

| 4 0   | 共通線              | 10 |

| 5 0   | TFTゲート電極         |    |

| 5 2   | ダイオード最底部接点       |    |

| 5 4   | ダイオード・スタック       |    |

| 5 6   | ゲート誘電体層          |    |

| 5 8   | 半導体層             |    |

| 6 0   | ソース電極            |    |

| 6 2   | ドレイン電極           |    |

| 6 4   | 光透過性バリア層         |    |

| 6 6   | 第1の誘電バリア         |    |

| 6 8   | 光遮断素子            | 20 |

| 7 0   | 第2の誘電バリア         |    |

| 8 0   | 第1の金属層           |    |

| 8 2   | ダイオード最上部接点       |    |

| 9 0   | ダイオード最底部接触部      |    |

| 9 2   | ダイオード最上部接触部      |    |

| 9 4   | 第2の金属層、第3の金属被覆   |    |

| 9 6   | 共通／ダイオード最上部ビア    |    |

| 1 0 0 | 第1のバリア部分         |    |

| 1 0 2 | 第2のバリア部分         |    |

| 1 1 0 | 第3の金属層、第3の金属被覆   | 30 |

| 1 1 2 | 光遮断素子の長さ         |    |

| 1 1 4 | ゲートの長さ           |    |

| 1 2 0 | データ／ソース・ビア       |    |

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図 9】

【図 7】

【図 10】

【図 8】

【図 1 1】

【図 1 3】

【図 1 2】

【図 1 4】

【図 1 5】

フロントページの続き

(72)発明者 ロバート・エフ・クワスニック

アメリカ合衆国、カリフォルニア州、パロ・アルト、ラモーナ・ストリート、2431番

(72)発明者 ダグラス・アルバグリー

アメリカ合衆国、ニューヨーク州、クリフトン・パーク、クイーンズベリー・コート、1番

F ターム(参考) 4M118 AB01 BA05 CA02 CA05 CA32 CB06 FB03 FB09 FB13 FB16

FB19 FB24 GB11 GB15