(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5442224号

(P5442224)

(45) 発行日 平成26年3月12日(2014.3.12)

(24) 登録日 平成25年12月27日(2013.12.27)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 21/02  | (2006.01) | HO1L 27/12 | B    |

| HO1L 27/12  | (2006.01) | HO1L 29/78 | 626C |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 627D |

| HO1L 29/786 | (2006.01) |            |      |

請求項の数 6 (全 47 頁)

(21) 出願番号 特願2008-184536 (P2008-184536)

(22) 出願日 平成20年7月16日 (2008.7.16)

(65) 公開番号 特開2009-49387 (P2009-49387A)

(43) 公開日 平成21年3月5日 (2009.3.5)

審査請求日 平成23年5月31日 (2011.5.31)

(31) 優先権主張番号 特願2007-190987 (P2007-190987)

(32) 優先日 平成19年7月23日 (2007.7.23)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 大沼 英人

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 綿引 隆

(56) 参考文献 特開平10-326759 (JP, A)

特開2005-203595 (JP, A)

特開2002-170942 (JP, A)

最終頁に続く

(54) 【発明の名称】 S O I 基板の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

一表面上にシリコン酸化層、第1の窒素含有絶縁層、及び第1の接合層が形成され、且つ所定の深さの領域に脆化層が形成された半導体基板と、一表面上に第2の窒素含有絶縁層及び第2の接合層が形成された支持基板とを準備し、

前記半導体基板と、前記支持基板とを、前記シリコン酸化層、前記第1の窒素含有絶縁層、前記第1の接合層、前記第2の窒素含有絶縁層、及び前記第2の接合層を間に挟んで重ね合わせて接合し、

前記半導体基板の側面から前記脆化層にレーザビームを照射した後、

前記脆化層を境として前記半導体基板の一部を分離させ、前記支持基板上に半導体層を形成することを特徴とするS O I 基板の製造方法。 10

## 【請求項2】

一表面上にシリコン酸化層、第1の窒素含有絶縁層、及び第1の接合層が形成され、且つ所定の深さの領域に脆化層が形成された半導体基板と、一表面上に第2の窒素含有絶縁層及び第2の接合層が形成された支持基板とを準備し、

前記半導体基板と、前記支持基板とを、前記シリコン酸化層、前記第1の窒素含有絶縁層、前記第1の接合層、前記第2の窒素含有絶縁層、及び前記第2の接合層を間に挟んで重ね合わせて接合し、

前記支持基板側から、前記半導体基板にレーザビームを照射した後、

前記脆化層を境として前記半導体基板の一部を分離させ、前記支持基板上に半導体層を 20

形成することを特徴とする S O I 基板の製造方法。

【請求項 3】

請求項 2 において、

前記レーザビームとしては、前記支持基板、前記シリコン酸化層、前記第 1 の窒素含有絶縁層、前記第 1 の接合層、前記第 2 の窒素含有絶縁層、及び前記第 2 の接合層は透過し、前記半導体基板に吸収される波長のものを用いることを特徴とする S O I 基板の製造方法。

【請求項 4】

請求項 2 又は請求項 3 において、

前記支持基板としては、絶縁表面を有する基板、又は絶縁性を有し、且つ紫外光又は可視光を透過する透光性を有する基板を用いることを特徴とする S O I 基板の製造方法。 10

【請求項 5】

請求項 1 乃至請求項 4 のいずれか一において、

前記レーザビームとしては、X e C 1 エキシマレーザから射出されるレーザビーム、Ar<sup>+</sup>レーザから射出されるレーザビーム、Y A G レーザの第 2 高調波若しくは第 3 高調波、Y V O<sub>4</sub> レーザの第 2 高調波若しくは第 3 高調波、又はY L F レーザの第 2 高調波若しくは第 3 高調波を用いることを特徴とする S O I 基板の製造方法。

【請求項 6】

請求項 1 乃至請求項 5 のいずれか一において、

前記半導体基板の分離の前に、加熱処理を行うことを特徴とする S O I 基板の製造方法。 20

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、S O I ( S i l i c o n O n I n s u l a t o r ) 基板及びその製造方法に関する。

【0 0 0 2】

なお、本明細書における半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路、及び電子機器は全て範疇に含むものとする。 30

【背景技術】

【0 0 0 3】

V L S I 技術の発展に伴い、バルク単結晶シリコンで実現できるスケーリング則を超える低消費電力化、高速化が求められている。これらの要求を満たすため、S O I 構造が注目されている。この技術は、従来バルク単結晶シリコンで形成されていた電界効果トランジスタ ( F E T ; F i e l d E f f e c t T r a n s i s t o r ) の活性領域 ( チャネル形成領域 ) を単結晶シリコン薄膜とする技術である。S O I 構造を用いて電界効果トランジスタを作製すると、バルク単結晶シリコン基板を用いる場合よりも寄生容量を小さくでき、高速化に有利になることが知られている。

【0 0 0 4】

S O I 基板としては、S I M O X 基板や貼り合わせ基板が知られている。S I M O X 基板は、単結晶シリコン基板に酸素イオンを注入し、1 3 0 0 以上で熱処理を行い埋め込み酸化膜を形成することにより、表面に単結晶シリコン薄膜を形成して S O I 構造を得ている。S I M O X 基板は酸素イオンの注入を精密に制御できるため、単結晶シリコン薄膜を均一な膜厚で形成できる。しかし、酸素イオンの注入に長時間を有し、時間及びコスト面で問題がある。また、1 枚のベース基板で S O I 構造を形成するため、ベース基板の異種基板を支持基板とすることができなかった。 40

【0 0 0 5】

貼り合わせ基板は、絶縁層を間に介して 2 枚の単結晶シリコン基板を貼り合わせ、一方の単結晶シリコン基板を薄膜化することにより、単結晶シリコン薄膜を形成して S O I 構造を得ている。薄膜化の手段の一つとして、水素イオン注入剥離法が知られている。水素 50

イオン注入剥離法は、一方の単結晶シリコン基板に水素イオンを注入することによって、シリコン基板表面から所定の深さに微小気泡層を形成し、該微小気泡層を劈開面として、他方の単結晶シリコン基板に薄い単結晶シリコン層を固定することができる（特許文献1参照）。

【0006】

近年では、ガラスなどの絶縁表面を有する基板に単結晶シリコン層を形成する試みもなされている。例えば、ガラス基板上に単結晶シリコン層を形成したSOI基板の一例として、本出願人によるものが知られている（特許文献2参照）。

【特許文献1】特開2000-124092号公報

【特許文献2】特開平11-163363号公報

10

【発明の開示】

【発明が解決しようとする課題】

【0007】

水素イオン注入剥離法を利用する場合、加熱処理を行うことによりシリコン基板に形成された微小気泡層を体積変化させ、該微小気泡層に沿って劈開することでSOI構造が得られる。しかしながら、微小気泡層を体積変化させて、シリコン基板を該微小気泡層に沿って分離するには600程度の加熱処理が必要であり、分離工程におけるスループットの低下が問題となっていた。

【0008】

本発明は、上述した問題を鑑み、スループット良くSOI基板を製造できる方法を提供することを課題とする。また、当該SOI基板を用いた半導体装置を提供することを課題とする。

20

【課題を解決するための手段】

【0009】

支持基板に半導体基板から分離させた半導体層を転置して、SOI基板を製造する。まず、半導体層の基となる半導体基板を準備する。該半導体基板には所定の深さの領域に脆化層を形成し、且つ、一表面上に絶縁層を形成する。また、絶縁表面を有する支持基板或いは絶縁性を有する支持基板を準備する。半導体基板と支持基板とを、前記絶縁層を間に挟んで重ね合わせて接合した後、半導体基板にレーザビームを選択的に照射して脆化層の一部に吸収させて該脆化層の脆化を進行させる。そして、物理的手段又は加熱処理により、脆化層の脆化を進行させた領域を始点（きっかけ）として、半導体基板を分離する。半導体基板は、脆化層を境として分離される。その結果、支持基板上に半導体層が固着されたSOI基板が製造される。

30

【0010】

なお、本明細書における「脆化」とは、微小な空洞が多数形成され、脆くなっている状態を示す。また、「脆化が進行」とは、形成された空洞の数が増える、空洞が大きくなる、或いは空洞同士が結合して空間を形成し部分的に分離することを範疇に含み、イオンを注入して形成した脆化層よりも状態が脆くなることを示す。また、「分離」とは、分け離されることを示す。また、「イオンを注入」とは電界で加速されたイオンを照射して、該照射したイオンを構成する元素を半導体基板中に含ませることを指す。

40

【0011】

本発明の一は、一表面上に絶縁層が形成され、且つ所定の深さの領域に脆化層が形成された半導体基板を準備し、半導体基板と、支持基板と、を、絶縁層を間に挟んで重ね合わせて接合する。半導体基板の側面から脆化層にレーザビームを選択的に照射した後、物理的手段により、脆化層を境として半導体基板の一部を分離させることにより、支持基板上に半導体層を形成するSOI基板の製造方法である。

【0012】

本発明の一は、一表面上に絶縁層が形成され、且つ所定の深さの領域に脆化層が形成された半導体基板を準備し、半導体基板と、支持基板と、を、絶縁層を間に挟んで重ね合わせて接合する。支持基板側から半導体基板にレーザビームを照射した後、物理的手段によ

50

り、脆化層を境として半導体基板の一部を分離させることにより、支持基板上に半導体層を形成する S O I 基板の製造方法である。

【 0 0 1 3 】

上記構成において、レーザビームとしては、支持基板及び絶縁層は透過し、半導体基板に吸収される波長のものを照射することが好ましい。具体的には、支持基板及び絶縁層に対する透過率が 30 % 以上、好ましくは 50 % 以上、より好ましくは 70 % 以上であるレーザビームを照射することが好ましい。例えば、X e C 1 エキシマレーザ或いは A r + レーザから射出されるレーザビーム、又は Y A G レーザ（基本波 1 0 6 4 n m）の第 2 高調波（5 3 2 n m）或いは第 3 高調波（3 5 5 n m）、Y V O 4 レーザ（基本波 1 0 6 4 n m）の第 2 高調波（5 3 2 n m）或いは第 3 高調波（3 5 5 n m）、或いは Y L F レーザ（基本波 1 0 5 3 n m）の第 2 高調波（5 2 7 n m）或いは第 3 高調波（3 5 1 n m）を照射することが好ましい。10

【 0 0 1 4 】

なお、本明細書における透過とは、対象物に対する透過率が 30 % 以上、好ましくは 50 % 以上、より好ましくは 70 % 以上であることを意味する。

【 0 0 1 5 】

また、上記構成において、支持基板としては、絶縁表面を有する基板又は絶縁性を有し、且つ紫外光又は可視光を透過する透光性を有する基板を用いることが好ましい。具体的には、紫外光及び可視光の透過率が 30 % 以上、好ましくは 50 % 以上、より好ましくは 70 % 以上である基板を用いることが好ましい。20

【 0 0 1 6 】

また、物理的手段による半導体基板の分離の前に、加熱処理を行うこともできる。

【 発明の効果 】

【 0 0 1 7 】

本発明を適用することで、スループットが向上した S O I 基板の製造方法を提供することができ、生産性を向上することができる。また、S O I 基板を用いた半導体装置の生産性の向上も図ることができる。

【 発明を実施するための最良の形態 】

【 0 0 1 8 】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなく、その形態及び詳細を様々に変更しうることは、当業者であれば容易に理解される。したがって、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。30

【 0 0 1 9 】

（実施の形態 1 ）

本形態に係る S O I 基板は、半導体基板から分離させた半導体層、好ましくは単結晶半導体基板から分離させた単結晶半導体層を支持基板に転置して形成する。支持基板としては、半導体基板の異種基板を適用する。以下、図面を参照して本形態に係る S O I 基板の製造方法の一例について説明する。40

【 0 0 2 0 】

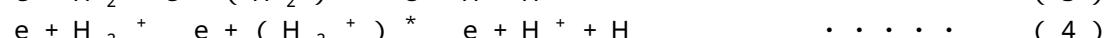

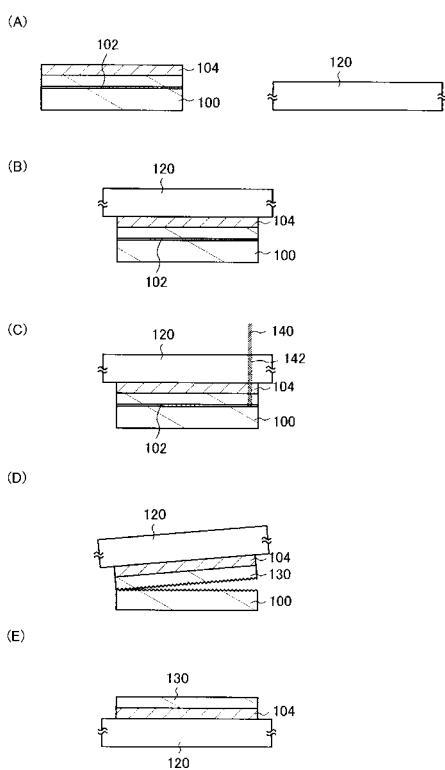

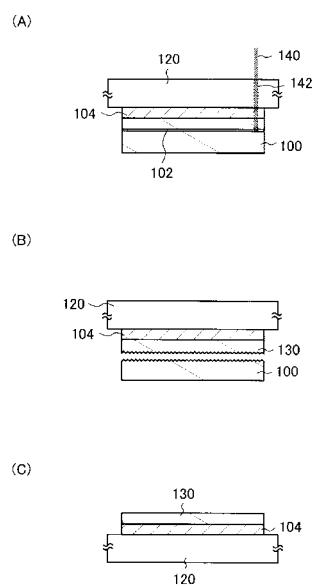

一表面上に絶縁層 1 0 4 が形成され、且つ所定の深さの領域に脆化層 1 0 2 が形成された半導体基板 1 0 0 と、支持基板 1 2 0 を準備する（図 1 ( A ) 参照）。

【 0 0 2 1 】

半導体基板 1 0 0 としては、シリコン基板やゲルマニウム基板などの半導体基板、又はガリウムヒ素やインジウムリンなどの化合物半導体基板を適用する。好ましくは単結晶半導体基板を適用するのが望ましい。また、多結晶半導体基板を適用することも可能である。適用する半導体基板は矩形状でもよいし、円形状でもよい。

【 0 0 2 2 】

10

20

30

40

50

半導体基板 100 に形成する絶縁層 104 は単層構造でも積層構造でもよいが、最上層（後に接合面となる側）は平滑性を有し親水性表面を形成できる層を膜厚 0.2 nm 乃至 500 nm で形成することが好ましい。例えば、熱的な反応又は化学的な反応により形成される酸化膜は表面の平滑性を確保しやすいため好ましい。このような条件を満たして形成される絶縁層は、半導体基板 100 と支持基板 120 とを接合する接合層となる。なお、本明細書において「接合層」とは、一の基板（例えば半導体基板）において、他の基板（例えば支持基板）と接合を形成する接合面に形成する層のことを示す。例えば、有機シランを原料ガスに用いて化学気相成長（CVD；Chemical Vapor Deposition）法により形成される酸化シリコン層を適用することが好ましい。有機シランとしては、テトラエトキシシラン（略称；TEOS：化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ ）<sup>10</sup>、テトラメチルシラン（TMS：化学式  $\text{Si}(\text{CH}_3)_4$ ）、トリメチルシラン（ $(\text{CH}_3)_3\text{SiH}$ ）、テトラメチルシクロテトラシロキサン（TMCDS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（ $\text{SiH}(\text{OC}_2\text{H}_5)_3$ ）、トリスジメチルアミノシラン（ $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ）等のシリコン含有化合物を用いることができる。また、モノシラン、ジシラン、又はトリシラン等の無機シランを原料ガスに用いて CVD 法により形成される酸化シリコン層を適用することもできる。なお、原料ガスに有機シラン又は無機シランを用いて CVD 法により酸化シリコン層を形成する場合、酸素を付与するガスを混合させることが好ましい。酸素を付与するガスとしては、酸素、亜酸化窒素、又は二酸化窒素等を用いることができる。さらに、アルゴン、ヘリウム或いは窒素等の不活性ガス、又は水素ガスを混合させてもよい。CVD 法により酸化シリコン層を形成する場合は、膜厚 10 nm 乃至 500 nm で形成することが好ましい。また、酸化性雰囲気下において熱処理することにより形成される酸化シリコン層、酸素ラジカルの反応により成長する酸化シリコン層、酸化性の薬液により形成されるケミカルオキサイド、シロキサン（ $\text{Si-O-Si}$ ）結合を有する絶縁層を適用することもできる。なお、本明細書におけるシロキサン結合を有する絶縁層とは、シリコン（Si）と酸素（O）との結合を含み、シリコンと酸素との結合で骨格構造が構成されている。シロキサンは置換基を有しており、該置換基として少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素など）が挙げられる。その他、有機基は、フルオロ基を含んでもよい。シロキサン結合を有する絶縁層は、スピントレード法などの塗布法により形成することができる。<sup>20</sup>

#### 【0023】

また、絶縁層 104 は、窒化シリコン層、窒化酸化シリコン層などの窒素含有絶縁層を 1 層以上含むことが好ましい。窒素含有絶縁層はアルカリ金属又はアルカリ土類金属等の金属不純物をブロッキングする効果がある。そのため、支持基板 120 としてガラス基板のような金属不純物を微量に含む基板を適用した場合に、窒素含有絶縁層によって金属不純物が半導体層側に拡散することを防止することができるため好ましい。なお、絶縁層 104 として窒素含有絶縁層を含む積層構造とする場合は、半導体基板 100 と窒素含有絶縁層の間にはシリコン酸化層を形成することが好ましい。具体的には、絶縁層 104 は、半導体基板 100 側からシリコン酸化層、窒素含有絶縁層、接合層の順に形成された積層構造とすることが好ましい。これは半導体基板 100 に窒素含有絶縁層を直接接して形成すると、トラップ準位が形成され界面特性が問題となるからである。窒素含有絶縁層やシリコン酸化層は、CVD 法やスパッタリング法、或いは原子層エピタキシ（ALD）法により形成すればよい。絶縁層 104 として、半導体基板 100 側からシリコン酸化層、窒素含有絶縁層、接合層の積層構造を形成することで、半導体層の金属不純物による汚染を防止しつつ、界面の電気的特性の向上を図ることができる。<sup>30</sup>

#### 【0024】

なお、本明細書における酸化窒化シリコン層とは、その組成として、窒素よりも酸素の含有量が多く、ラザフォード後方散乱法（RBS：Rutherford Backscattering Spectrometry）及び水素前方散乱法（HFS：Hydrogen Forward Scattering）を用いて測定した場合に、濃度範囲<sup>40</sup>

として酸素が 50 atoms % 乃至 70 atoms %、窒素が 0.5 atoms % 乃至 15 atoms %、Si が 25 atoms % 乃至 35 atoms %、水素が 0.1 atoms % 乃至 10 atoms % の濃度範囲で含まれるものという。また、窒化酸化シリコン層とは、その組成として、酸素よりも窒素の含有量が多く、RBS 及び HFS を用いて測定した場合に、濃度範囲として酸素が 5 atoms % 乃至 30 atoms %、窒素が 20 atoms % 乃至 55 atoms %、Si が 25 atoms % 乃至 35 atoms %、水素が 10 atoms % 乃至 30 atoms % の濃度範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子 % としたとき、窒素、酸素、Si 及び水素の含有比率が上記の範囲内に含まれるものとする。

## 【0025】

脆化層 102 は、半導体基板 100 に電界で加速されたイオンを照射することで、該半導体基板 100 の所定の深さの領域に形成される。半導体基板 100 に形成される脆化層 102 の深さは、照射されるイオンの種類と、該イオンの加速電圧と、該イオンの照射角度によって制御することができる。脆化層 102 は、半導体基板 100 の表面からイオンの平均進入深さに近い深さの領域に形成される。また、脆化層 102 の形成される深さは、後に支持基板に転置する半導体層の膜厚を決定する。そのため、脆化層 102 を形成するイオンを照射する際の加速電圧及びイオンのドーズ量は、転置する半導体層の膜厚を考慮して調整する。好ましくは半導体層の膜厚が 5 nm 乃至 300 nm、より好ましくは 10 nm 乃至 200 nm の厚さとなるように、イオンの照射を調整して脆化層 102 を形成する。

## 【0026】

イオンの照射はイオンドーピング装置を用いて行うことが好ましい。すなわち、原料ガスをプラズマ励起して生成された複数種類のイオンを質量分離しないで照射するドーピング方式を用いることが好ましい。本形態の場合、一或いは複数の同一の原子からなる質量が単一のイオン、又は一或いは複数の同一の原子からなる質量が異なるイオンを照射することができる。好ましくは、一或いは複数の同一の原子からなる質量が異なるイオンを照射する。このようなイオンドーピングは、加速電圧 10 kV 乃至 100 kV、好ましくは 30 kV 乃至 80 kV、ドーズ量は  $1 \times 10^{16}$  ions / cm<sup>2</sup> 乃至  $4 \times 10^{16}$  ions / cm<sup>2</sup>、ビーム電流密度が 2  $\mu$ A / cm<sup>2</sup> 以上、好ましくは 5  $\mu$ A / cm<sup>2</sup> 以上、より好ましくは 10  $\mu$ A / cm<sup>2</sup> 以上とすればよい。

## 【0027】

イオンとしては、水素、重水素、ヘリウム、又はフッ素等のハロゲンから選ばれた原料ガスをプラズマ励起して生成された一或いは複数の同一の原子からなる質量が異なるイオンを照射することが好ましい。水素イオンを照射する場合には、H<sup>+</sup>イオン、H<sub>2</sub><sup>+</sup>イオン、H<sub>3</sub><sup>+</sup>イオンを含ませると共に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくとイオンの照射効率を高めることができ、照射時間を短縮することができるため好ましい。それにより、半導体基板 100 に形成される脆化層 102 の領域には  $1 \times 10^{20}$  atoms / cm<sup>3</sup> (好ましくは  $1 \times 10^{21}$  atoms / cm<sup>3</sup>) 以上の水素を含ませることが可能である。半導体基板 100 に局所的に高濃度の水素を照射して形成される脆化層 102 は、結晶構造が乱されて微小な空洞が形成された多孔質構造となる。

## 【0028】

また、イオンを質量分離して特定種類のイオンを半導体基板 100 に照射しても同様に脆化層 102 を形成することができる。この場合にも、質量が大きいイオン ( 例えば H<sub>3</sub><sup>+</sup> イオン ) を選択的に照射することは上記と同様な効果を奏すこととなり好ましい。

## 【0029】

脆化層 102 は、半導体基板 100 に絶縁層 104 を形成した後、該絶縁層 104 側からイオンを照射して形成してもよいし、絶縁層 104 を形成する前に半導体基板 100 にイオンを照射して形成してもよい。また、絶縁層 104 を積層構造とし、イオンを照射する際の保護層として機能できる絶縁層を形成した後にイオンを照射して脆化層 102 を形成し、さらに接合層として機能する絶縁層を形成してもよい。例えば、絶縁層 104 とし

10

20

30

40

50

てシリコン酸化層、窒素含有絶縁層、及び接合層の積層構造を形成する場合、半導体基板100の一表面上にシリコン酸化層及び窒素含有絶縁層を形成した後、イオンを照射して脆化層102を形成し、さらに接合層を形成することができる。半導体基板100にイオンを照射する際、絶縁層を通過させる構成とすることで、半導体基板100の表面荒れを防ぐことができる。なお、イオンを照射して脆化層102を形成した後に接合層として機能する絶縁層を形成する場合は、成膜温度350℃以下で形成することが好ましい。

#### 【0030】

支持基板120としては、絶縁表面を有する基板、又は絶縁性を有し、且つ紫外光又は可視光を透過する透光性を有する基板を適用する。具体的には、紫外光又は可視光の透過率が30%以上、好ましくは50%以上、より好ましくは70%以上の基板を適用することが好ましい。例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、或いはバリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板（「無アルカリガラス基板」とも呼ばれる）、石英基板、結晶化ガラス基板、又はサファイヤ基板が挙げられる。好ましくは、電子工業用に使われるガラス基板を適用すると安価であり、コスト削減を図ることができる。

10

#### 【0031】

次に、半導体基板100と支持基板120とを、絶縁層104を間に挟んで重ね合わせて貼り合わせる（図1（B）参照）。

#### 【0032】

半導体基板100及び支持基板120の接合を形成する面は十分に清浄化しておく。そして、絶縁層104を間に介して、半導体基板100と支持基板120とを密接させることで、接合を形成する。接合は初期の段階においてファン・デル・ワールス力が作用するものと考えられ、支持基板120と半導体基板100とを圧接することで水素結合により強固な接合を形成することが可能になると考えられる。

20

#### 【0033】

なお、支持基板120と半導体基板100を貼り合わせた後は、加熱処理又は加圧処理を行うことが好ましい。加熱処理又は加圧処理を行うことで接合強度を高めることができる。加熱処理を行う際は、その温度範囲は支持基板120の耐熱温度以下で、且つ半導体基板100に形成された脆化層102で体積変化が起きない温度とし、好ましくは室温以上400℃未満とする。また、加圧処理においては、接合面に垂直な方向に圧力が加わるように行い、支持基板120及び半導体基板100の耐圧性を考慮して行う。

30

#### 【0034】

また、半導体基板100と支持基板120との良好な接合を形成するため、支持基板120と半導体基板100とを密接させる前に、いずれか一方又は双方の接合面を活性化しておいてもよい。例えば、原子ビーム若しくはイオンビーム、具体的にはアルゴン等の不活性ガス原子ビーム若しくは不活性ガスイオンビームを照射することで接合面を活性化することができる。その他、ラジカル処理により、接合面を活性化することもできる。このような表面活性化処理を行うことで、異種材料基板間の接合強度を高めることができる。また、いずれか一方又は双方の接合面をオゾン添加水、酸素添加水、水素添加水、又は純水等で洗浄処理してもよい。このように、接合面を親水性にする処理を加えることで、接合面のOH基を増大させることができる。その結果、水素結合による接合をより強固にすることが可能である。

40

#### 【0035】

次に、支持基板120側から半導体基板100にレーザビーム140を選択的に照射する（図1（C）参照）。

#### 【0036】

レーザビーム140は、支持基板120及び絶縁層104を透過し、半導体基板100に吸収される波長を有するものとする。具体的には、レーザビーム140は、支持基板120の露出している表面から絶縁層104と接する側の半導体基板100表面までの基板及び膜に対する透過率が30%以上、好ましくは50%以上、より好ましくは70%以上

50

のもので、且つ半導体基板 100 に吸収されるものが好ましい。レーザビーム 140 の波長は可視領域～紫外領域 (800 nm 以下) の範囲が好ましく、より好ましくは紫外領域 (400 nm 以下) とする。用いるレーザビームとしては、例えば XeCl エキシマレーザ (発振波長 308 nm) から射出されるレーザビーム、固体レーザである YAG レーザ (発振波長 1064 nm) の第 2 高調波 (532 nm) 或いは第 3 高調波 (355 nm) 、 YVO<sub>4</sub> レーザ (発振波長 1064 nm) の第 2 高調波 (532 nm) 或いは第 3 高調波 (355 nm) 、或いは YLF レーザ (発振波長 1053 nm) の第 2 高調波 (527 nm) や第 3 高調波 (351 nm) 、 Ar<sup>+</sup> レーザ (発振波長 364 nm) から射出されるレーザビーム等が挙げられる。なお、本形態に用いるレーザは特に限定されず、所望の発振波長 (好ましくは可視領域～紫外領域の範囲、より好ましくは紫外領域) のレーザビームが得られるものであればよい。また、連続発振型レーザでもパルス型レーザでもよい。

10

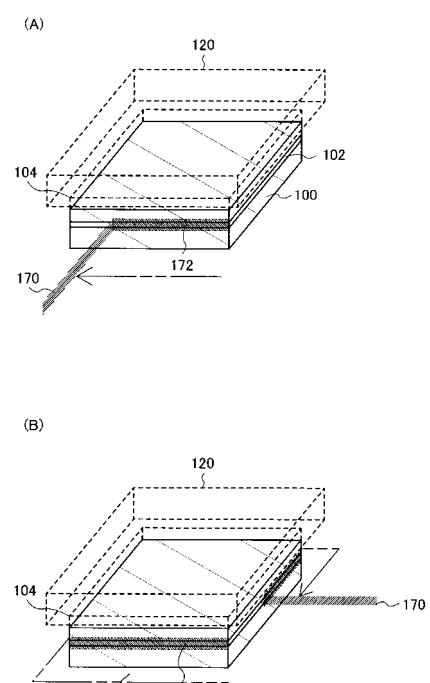

#### 【0037】

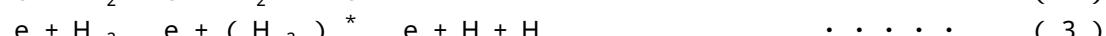

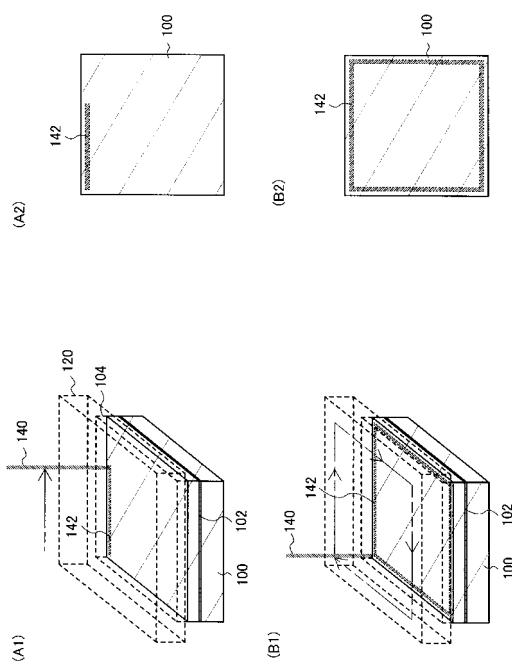

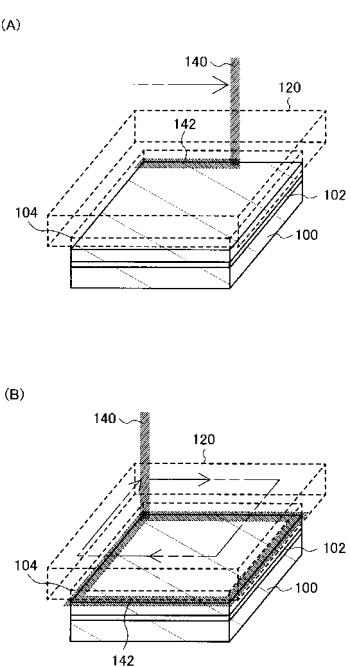

ここで、レーザビーム 140 の照射の一例を図 2 に示す。図 2 (A1)、(B1) は模式的な斜視図を示し、図 2 (A2)、(B2) は上面図を示す。なお、図 2 では絶縁層 104 及び支持基板 120 を点線で示す。

#### 【0038】

本形態において、レーザビーム 140 は半導体基板 100 の周縁付近に選択的に照射することが好ましく、半導体基板 100 が矩形である場合は少なくとも一辺に照射するものとする。図 2 では、半導体基板 100 の周縁付近に沿って 4 辺にレーザビーム 140 を照射する例を示している。また、レーザビーム 140 を選択的に照射した領域を照射領域 142 として示している。

20

#### 【0039】

レーザビーム 140 は、支持基板 120 及び絶縁層 104 を透過して半導体基板 100 に吸収される。なお、レーザビーム 140 は、少なくとも脆化層 102 に到達して吸収されるように照射する。したがって、半導体基板 100 に形成される脆化層 102 の深さは、レーザビーム 140 が到達するように調整する必要もある。具体的には、半導体基板 100 において、イオンを照射する面側の半導体基板 100 表面から膜厚方向 300 nm 以下の深さに脆化層 102 を形成することが好ましい。

#### 【0040】

照射領域 142 における脆化層 102 及び照射領域 142 周辺における脆化層 102 は、レーザビーム 140 を吸収することにより局所的に加熱され温度が上昇する。そのため、脆化層 102 においてレーザビーム 140 を吸収した領域及びレーザビーム 140 を吸収した領域周辺の脆化層 102 は空洞中の水素圧力が上昇し、脆化が進行する。つまり、半導体基板 100 に形成された脆化層 102 は、照射領域 142 に沿って脆化が進行する。例えば、図 2 では、半導体基板 100 の周縁に沿って、部分的に脆化層 102 の脆化が進行することになる。なお、レーザビーム 140 の照射領域 142 における脆化層 102 及び照射領域 142 周辺における脆化層 102 は、加熱されることで溶融する場合もある。脆化層 102 において脆化が進行した部分は、後に半導体基板 100 の分離を行う際の始点 (きっかけ) となる。

40

#### 【0041】

なお、レーザビーム 140 のビーム形状は、面積を有することが好ましい。例えば、光学系を用いてレーザビーム 140 を矩形又は橢円形に整形することが好ましい。これは、脆化層 102 において脆化が進行した部分は分離工程の始点となるため、ある程度の面積を有する領域で脆化を進行させておく方が容易に分離でき、分離の際にクラックなどのダメージが入るのを防ぐことができるからである。なお、レーザビーム 140 を矩形又は橢円形とする場合、レーザビーム 140 の進行方向に対する垂直方向の断面におけるビーム形状の短軸方向は、レーザビーム 140 の走査方向となるようにすることが好ましい。

#### 【0042】

また、図 8 に示すように、半導体基板 100 の周縁或いは周縁をはみ出すようにレーザ

10

20

30

40

50

ビーム 140 を照射してもよい。なお、図 8 (A)、(B) では矩形である半導体基板 100 の周縁に沿って 4 辺にレーザビーム 140 を照射する例を示すが、少なくとも一辺に照射すればよい。半導体基板 100 をはみ出すようにレーザビーム 140 を照射すると、半導体基板 100 の端部に位置する脆化層の脆化が進行することになる。脆化層 102 の脆化が進行した部分は半導体基板 100 の分離を行う際の始点となり、始点が端にくることで一方向に分離が進みやすくなり、容易に分離することが可能となる。

#### 【0043】

次に、物理的手段により、脆化層 102 を境として半導体基板 100 を分離させる。半導体基板 100 は絶縁層 104 を間に介して支持基板 120 に接合されており、脆化層 102 を境として半導体基板 100 の一部を分離させた結果、支持基板 120 上に半導体層 130 が残存する（図 1 (D) 参照）。

10

#### 【0044】

なお、本形態における物理的手段とは、化学ではなく、物理学により認識される手段を指す。具体的には、力学の法則に還元できる過程を有する力学的手段又は機械的手段を指し、例えば人間の手や道具を用いて引き剥がすことである。

#### 【0045】

脆化層 102 は、レーザビーム 140 の照射により部分的に脆化が進行している。半導体基板 100 に物理的な力を加えることで、脆化層 102 の脆化が進行した部分が始点となり、脆化層 102 を境として半導体基板 100 を劈開することができる。また、本形態における分離に必要な時間は、数秒乃至数分程度とすることができる。半導体基板 100 は絶縁層 104 を間に介して支持基板 120 と接合しており、支持基板 120 上には半導体基板 100 と同じ結晶性の半導体層 130 が残存する形態となる。例えば、半導体基板 100 として単結晶シリコン基板を適用し、支持基板 120 としてガラス基板を適用することで、ガラス基板上に絶縁層を間に介して単結晶シリコン層を形成することが可能となる。

20

#### 【0046】

例えば、半導体基板 100 及び支持基板 120 を貼り合わせた状態で、一方を真空チャックやメカチャック等の手法で固定する。そして、物理的な力を加えて他方を引き剥がすことで、脆化層 102 の脆化が進行した部分（レーザビーム 140 が照射された領域又はレーザビーム 140 が照射された領域近傍の脆化層）が始点（きっかけ）となり、脆化層 102 を境として半導体基板 100 を分離することができる。また、半導体基板 100 及び支持基板 120 を貼り合わせた状態で双方を固定し、それぞれを相対する方向へと引っ張ることでも分離することができる。

30

#### 【0047】

なお、レーザビーム 140 の照射後、物理的手段による半導体基板 100 の分離の前に、支持基板 120 の歪み点温度未満で加熱処理を行ってもよい。該加熱処理を行うことで、レーザビーム 140 の照射領域以外の脆化層 102 も脆化が進行し、半導体基板 100 の分離を容易にすることができる。なお、この場合の加熱処理は、物理的手段による半導体基板 100 の分離を行う補助的な役割を果たすものである。

40

#### 【0048】

支持基板 120 に転置された半導体層 130 は、イオン照射工程及び分離工程によって、表面（分離面）は平坦性が損なわれ、凹凸が形成されている。また、半導体層 130 の表面（分離面）には脆化層 102 が残存する場合もある。半導体層 130 表面に凹凸があると、得られた SOI 基板を用いて半導体装置を製造する際、薄く絶縁耐圧の優れたゲート絶縁層の形成が困難となる。そのため、半導体層 130 は平坦化処理を行うことが好ましい（図 1 (E) 参照）。

#### 【0049】

例えば、平坦化処理として、半導体層 130 に対して化学的機械的研磨（CMP；Chemical Mechanical Polishing）や、液体ジェットを利用した研磨などを行うことが好ましい。また、半導体層 130 にレーザビームを照射すること

50

により半導体層130の平坦化を図ってもよい。さらに、C M P処理及びレーザビームの照射や熱処理を組み合わせて行ってもよい。なお、半導体層にレーザビームを照射する、若しくは熱処理を行うことで、半導体層の平坦化と共に結晶欠陥やダメージ等を回復させることもできる。また、C M P処理を行った後、レーザビームの照射や熱処理を行うことで、C M P処理による表面の損傷層を修復させることもできる。さらに、得られた半導体層の薄膜化を目的として、C M P処理等を行ってもよい。なお、半導体層にレーザビームを照射する際は、酸素濃度が10 ppm以下の窒素雰囲気下で行うことが好ましい。これは、酸素雰囲気下でレーザビームの照射を行うと半導体層表面が荒れる恐れがあるからである。

## 【0050】

10

以上により、支持基板120上に絶縁層104を介して半導体層130が固着されたS O I基板を得ることができる。本形態に係るS O I基板は、物理的手段により分離を行うため、分離工程の際に高温長時間の加熱処理を必要とせず、スループットが向上できる。また、あらかじめレーザビームを照射して分離の始点(きっかけ)を形成するため、分離が容易となる。よって、製造時間を短縮することができ、生産性を向上させることができる。さらに、支持基板側からレーザビームを照射する構成としており、半導体層130へのダメージを少なくすることできる。

## 【0051】

なお、本形態では半導体基板100よりも支持基板120の面積が大きい例を図示したが、本発明は特に限定されない。支持基板120は、半導体基板100と同程度の面積のものを適用してもよい。また、半導体基板100と異なる形状のものを適用してもよい。

20

## 【0052】

また、半導体層130を分離した半導体基板100は、再利用することが可能である。すなわち、図1(D)に示すように分離された半導体基板100を、図1(A)の半導体基板として再度利用することができる。なお、半導体基板100を再利用する際には、半導体層130の分離面(劈開面となった面)を平坦化することが好ましい。ここで平坦化処理は、前述した半導体層130の平坦化と同様に行えばよく、C M P処理、液体ジェットを利用した研磨処理、レーザビーム照射、又は熱処理などを適宜行えばよい。また、複数の処理を組み合わせて行い、平坦化や結晶欠陥の修復を図ってもよい。S O I基板の製造において、基となる半導体基板の再利用を行うことで、大幅なコスト削減を実現できる。もちろん、半導体層130を分離した後の半導体基板100はS O I基板を製造する以外の用途に用いてもよい。

30

## 【0053】

なお、本形態に係るS O I基板の製造方法は、脆化層が形成された半導体基板にレーザビームを選択的に照射して部分的に前記脆化層の脆化を進行させた後、該脆化が進行した領域を始点として、脆化層に沿って半導体基板を分離することを特徴としており、S O I基板の構成は特に限定されるものではない。

## 【0054】

40

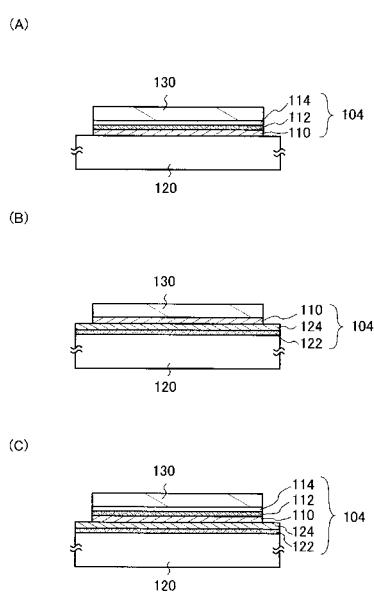

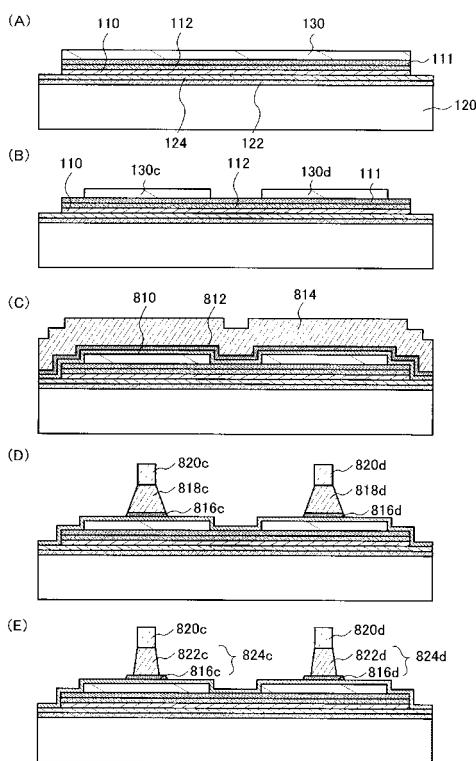

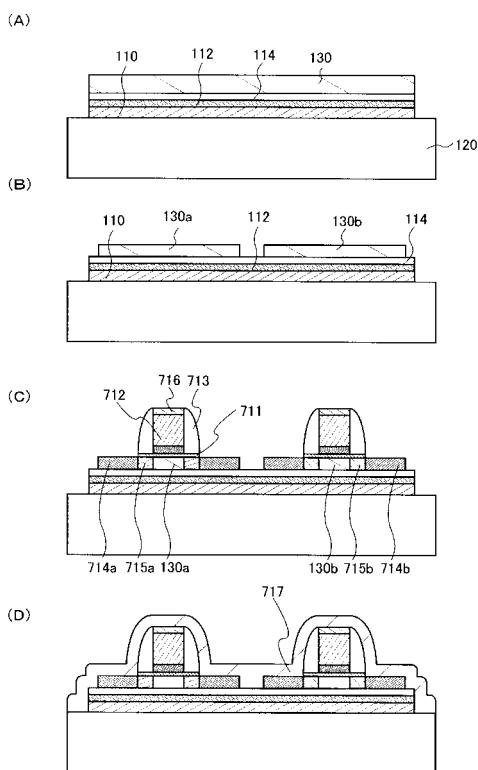

以下、図3及び図4を用いて、本形態に係るS O I基板の構成例を示す。図3(A)は、半導体層130と支持基板120との間に、半導体層130側からシリコン酸化層114、窒素含有絶縁層112、及び接合層110が形成されている例を示している。なお、シリコン酸化層114、窒素含有絶縁層112、及び接合層110の積層構造は、図1における絶縁層104に相当する。

## 【0055】

シリコン酸化層114としては、酸化シリコン層や酸化窒化シリコン層など、少なくとも酸素とシリコンを組成に含む絶縁層を形成する。窒素含有絶縁層112としては、窒化シリコン層や窒化酸化シリコン層、或いは窒化アルミニウム層など、少なくとも窒素を組成に含む絶縁層を形成する。接合層110としては、平滑性を有し親水性表面を形成できる絶縁層を形成し、具体的には有機シランを原料ガスに用いてC V D法により形成される酸化シリコン層やシロキサン結合を有する層などを形成する。窒素含有絶縁層112は、

50

金属不純物が半導体層130側に拡散するのを防止する効果がある。シリコン酸化層114は、半導体層130と良好な界面を形成することが可能である。

【0056】

なお、シリコン酸化層114、窒素含有絶縁層112、及び接合層110の膜厚は実施者が適宜決定すればよいが、シリコン酸化層114の膜厚は10nm乃至500nm、窒素含有絶縁層112の膜厚は10nm乃至500nm、接合層110の膜厚は0.2nm乃至500nm程度（接合層110をCVD法により形成する場合は10nm乃至500nm程度）とすることが好ましい。

【0057】

図3（A）に示す構成のSOI基板を製造する場合、半導体基板にシリコン酸化層114及び窒素含有絶縁層112の積層構造を形成した後、該積層構造が形成された側から半導体基板にイオンを照射して脆化層を形成することが好ましい。シリコン酸化層114及び窒素含有絶縁層112が形成された側からイオンを照射することで、半導体基板の表面荒れを防ぐことができる。窒素含有絶縁層112上に接合層110を形成した後、該接合層110を間に挟んで、半導体基板と支持基板120とを貼り合わせる。支持基板120側からレーザビームを選択的に照射し、照射領域における脆化層の脆化を進行させる。この場合、レーザビームとしては、支持基板120、シリコン酸化層114、窒素含有絶縁層112、及び接合層110を透過し、半導体基板に吸収される波長のものを用いる。また、支持基板120側から照射されるレーザビームは、少なくとも脆化層に到達するものとする。そして、物理的手段により、脆化層を境として半導体基板を分離する。その結果、支持基板120上に接合層110、窒素含有絶縁層112、及びシリコン酸化層114を介して半導体層130が残存する形態となる。半導体基板を分離する前に、レーザビームを選択的に照射し脆化層の脆化を部分的に進行させているため、物理的な力を加えることで、該脆化が進行した領域が始点となり容易に分離を行うことができる。また、物理的手段により分離することで、短時間で行うことができ、製造時間が短縮され、スループットが向上する。なお、シリコン酸化層114及び窒素含有絶縁層112は、半導体基板に脆化層を形成した後に形成してもよい。また、半導体基板上にシリコン酸化層114、窒素含有絶縁層112、及び接合層110を形成した後、脆化層を形成してもよい。

【0058】

図3（B）は、支持基板120側に接合層124と窒素含有絶縁層122を形成する例を示している。半導体層130と支持基板120との間には、半導体層130側から接合層110、接合層124、及び窒素含有絶縁層122が形成され、これらの積層構造は、図1における絶縁層104に相当する。

【0059】

窒素含有絶縁層122は、図3（A）の窒素含有絶縁層112と同様に、窒化シリコン層や窒化酸化シリコン層、或いは窒化アルミニウム層など、少なくとも窒素を組成に含む絶縁層を形成する。窒素含有絶縁層122を形成することで、支持基板120側から半導体層130に金属不純物が拡散するのを防ぐことができる。

【0060】

また、接合層124は、接合層110と同様に平滑性を有し親水性表面を形成できる絶縁層を形成すればよく、例えば有機シランを原料ガスに用いてCVD法により酸化シリコン層を形成する。支持基板120側にも接合層124を設け、該接合層124と接合層110とで接合を形成する構成とすることで、半導体層130と支持基板120との接合強度を高めることができる。

【0061】

なお、窒素含有絶縁層122、及び接合層124の膜厚は実施者が適宜決定すればよいが、窒素含有絶縁層122の膜厚は10nm乃至500nm、接合層124の膜厚は0.2nm乃至500nm程度（接合層124をCVD法により形成する場合は10nm乃至500nm程度）とすることが好ましい。

【0062】

10

20

30

40

50

図3 (B) に示す構成のSOI基板を製造する場合、半導体基板にイオンを照射して脆化層を形成した後、半導体基板上に接合層110を形成する。また、支持基板120上に窒素含有絶縁層122及び接合層124を積層形成する。支持基板120に形成された接合層124と、半導体基板に形成された接合層110とを貼り合わせた後、支持基板120側からレーザビームを選択的に照射して、脆化層の脆化を部分的に進行させる。そして、物理的手段により、半導体基板を脆化層に沿って劈開し、分離させる。その結果、支持基板120上に半導体層130が固着されたSOI基板を得る。なお、半導体基板分離後、得られた半導体層130の表面(分離面)は平坦化するのが好ましい。本形態において、物理的手段による半導体基板の分離の前に、予めレーザビームの照射により脆化層の脆化を部分的に進行させており、該脆化が進行した領域が始点(きっかけ)となるため、容易に分離することが可能である。なお、脆化層を形成するためのイオンの照射は、接合層110に行ってよい。

#### 【0063】

図3 (C) は、半導体層130側にシリコン酸化層114、窒素含有絶縁層112、及び接合層110を形成し、支持基板120側に窒素含有絶縁層122、及び接合層124を形成する例を示している。半導体層130と支持基板120の間には、半導体層130側からシリコン酸化層114、窒素含有絶縁層112、接合層110、接合層124、及び窒素含有絶縁層122が形成され、これらの積層構造は図1における絶縁層104に相当する。

#### 【0064】

図3 (C) に示す構成のSOI基板を製造する場合、半導体基板上にシリコン酸化層114及び窒素含有絶縁層112を形成し、半導体基板のシリコン酸化層114及び窒素含有絶縁層112が形成された側からイオンを照射し、脆化層を形成した後に接合層110を形成する。また、支持基板120上に窒素含有絶縁層122、及び接合層124を形成する。支持基板120に形成された接合層124と、半導体基板に形成された接合層110とを貼り合わせた後、支持基板120側からレーザビームを選択的に照射して、脆化層の脆化を部分的に進行させる。そして、物理的手段により、半導体基板を脆化層に沿って劈開し、分離させる。その結果、支持基板120上に半導体層130が固着されたSOI基板を得る。なお、半導体基板分離後、得られた半導体層130の表面(分離面)は平坦化することが好ましい。本形態において、物理的手段による半導体基板の分離の前に、予めレーザビームの照射により脆化層の脆化を部分的に進行させており、該脆化が進行した領域が始点(きっかけ)となるため、容易に分離することが可能である。なお、脆化層を形成するためのイオンの照射は、接合層110が形成された側から行ってよい。また、脆化層を形成した後、シリコン酸化層114、窒素含有絶縁層112を形成してもよい。

#### 【0065】

また、熱酸化法を利用して、半導体基板の表面に熱酸化膜を形成してもよい。熱酸化法により形成する熱酸化膜は、接合層として機能することもできる。

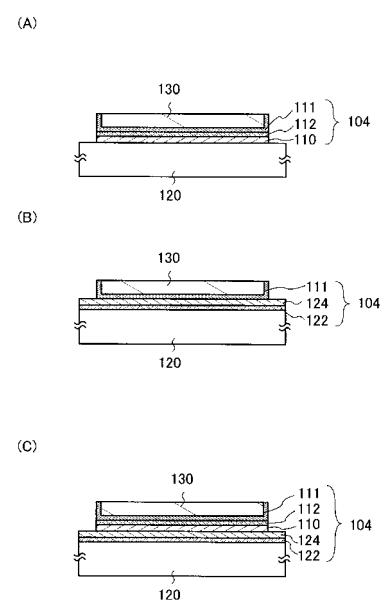

#### 【0066】

図4 (A) は、半導体基板を熱酸化して熱酸化膜111を形成し、該熱酸化膜111と接して窒素含有絶縁層112及び接合層110を積層形成する例を示している。つまり、半導体基板を分離して得られた半導体層130と支持基板120との間には、半導体層130側から熱酸化膜111、窒素含有絶縁層112、及び接合層110が形成されている。なお、半導体基板を熱酸化して形成するため、半導体層130の側面にも熱酸化膜111は形成されている。

#### 【0067】

図4 (B) は、半導体基板を熱酸化して熱酸化膜111を形成し、支持基板120側には窒素含有絶縁層122及び接合層124を形成し、熱酸化膜111と接合層124で接合を形成する例を示している。つまり、半導体基板を分離して得られた半導体層130と支持基板120との間には、半導体層130側から熱酸化膜111、接合層124及び窒素含有絶縁層122が形成されている。図4 (B) では、熱酸化膜111は接合層として

10

20

30

40

50

機能している。なお、半導体基板を熱酸化して形成するため、半導体層130の側面にも熱酸化膜111は形成されている。

【0068】

図4(C)は、半導体基板を熱酸化して形成した熱酸化膜111を介して窒素含有絶縁層112及び接合層110を形成し、支持基板120側には窒素含有絶縁層122及び接合層124を形成し、接合層110及び接合層124で接合を形成する例を示している。つまり、半導体基板を分離して得られた半導体層130と支持基板120との間には、半導体層130側から熱酸化膜111、窒素含有絶縁層112、接合層110、接合層124及び窒素含有絶縁層122が形成されている。なお、半導体基板を熱酸化して形成するため、半導体層130の側面にも熱酸化膜111は形成されている。

10

【0069】

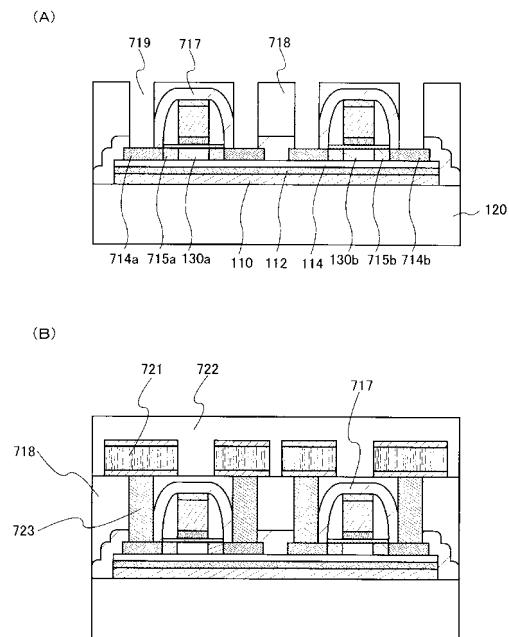

ここで、図4(A)に示すSOI基板の製造方法の一例について、図5を用いて説明する。

【0070】

半導体基板100を準備し、清浄化された半導体基板100を熱酸化して熱酸化膜111を形成する(図5(A)参照)。熱酸化としてはドライ酸化を行えばよく、酸素の他にHCl等を含む酸化性雰囲気下で行ってもよい。半導体基板100としてシリコン基板を適用する場合は、熱酸化膜111として酸化シリコン層が形成される。

【0071】

次に、半導体基板100の所定の深さの領域に脆化層102を形成する。また、半導体基板100上に熱酸化膜111を介して窒素含有絶縁層112及び接合層110を形成する(図5(B)参照)。

20

【0072】

脆化層102は、窒素含有絶縁層112を形成する前に形成してもよいし、窒素含有絶縁層112及び接合層110を形成する前に形成してもよい。つまり、半導体基板100の熱酸化膜111が形成された側からイオンを照射し脆化層102を形成してもよいし、半導体基板100の熱酸化膜111及び窒素含有絶縁層112が形成された側からイオンを照射し脆化層102を形成してもよい。また、半導体基板100の熱酸化膜111、窒素含有絶縁層112及び接合層110が形成された側からイオンを照射し脆化層102を形成してもよい。

30

【0073】

次に、支持基板120と半導体基板100を貼り合わせる。ここでは、半導体基板100表面の熱酸化膜111を介して形成された窒素含有絶縁層112及び接合層110を間に挟んで、半導体基板100と支持基板120を重ね合わせて貼り合わせる(図5(C)参照)。

【0074】

次に、支持基板120側から半導体基板100にレーザビーム140を選択的に照射する(図5(D)参照)。レーザビーム140の照射領域142における脆化層102及び照射領域142周辺における脆化層102は、局所的に加熱され温度が上昇し、空洞中の水素圧力が上昇して脆化が進行する。

40

【0075】

レーザビーム140としては、半導体基板100及び該半導体基板100に形成された脆化層102に吸収される波長を有するものを照射する。レーザビーム140は、少なくとも脆化層102に到達するように照射する。好ましくは可視領域～紫外領域、より好ましくは紫外領域の波長を有するレーザビーム140を照射する。照射領域142における脆化層102は、レーザビーム140を吸収することにより加熱されて、脆化が進行する。なお、照射領域142における脆化層102は、レーザビーム140の照射による加熱により溶融する場合もある。

【0076】

次に、物理的手段により、脆化層102を境として半導体基板100を分離させる。半

50

導体基板 100 は熱酸化膜 111 及び窒素含有絶縁層 112 上に形成された接合層 110 を間に介して支持基板 120 に接合されているため、半導体基板 100 の分離の結果、支持基板 120 上に半導体層 130 が残存する（図 5（D）参照）。

【0077】

脆化層 102 は、レーザビーム 140 の選択的な照射により、部分的に脆化が進行している。半導体基板 100 に物理的な力を加えることで、脆化層 102 の脆化が進行した部分が始点となり、半導体基板 100 を容易に分離することが可能である。このとき、半導体基板 100 は脆化層 102 に沿って劈開し、分離される。また、分離のための所要時間は、数秒乃至数分程度と非常に短くできる。半導体基板 100 は接合層 110 等を間に介して支持基板 120 と接合しており、支持基板 120 上には半導体基板 100 と同じ結晶性の半導体層 130 が残存する形態となる。

【0078】

半導体基板 100 を分離する物理的手段は特に限定されないが、例えば半導体基板 100 及び支持基板 120 を貼り合わせた状態で、一方を固定し、物理的な力を加えて他方を引き剥がすことが可能である。引き剥がす際、脆化層 102 の脆化が進行した部分（レーザビーム 140 が照射された領域）が始点となるため、脆化層 102 に沿って半導体基板 100 を容易に分離することができる。なお、固定する際は真空チャックやメカチャック等の手法を適用すればよい。また、人間の手で引き剥がすことも可能である。

【0079】

レーザビーム 140 の照射後、物理的手段による半導体基板 100 の分離の前に、支持基板 120 の歪み点温度未満で加熱処理を行ってもよい。該加熱処理を行うことで、レーザビーム 140 の照射領域以外の脆化層 102 も脆化が進行し、半導体基板 100 の分離を容易にすることができる。なお、この場合の加熱処理は、物理的手段による半導体基板 100 の分離を行う補助的な役割を果たすものである。

【0080】

支持基板 120 に転置された半導体層 130 は、イオン照射工程及び分離工程によって、表面（分離面）は平坦性が損なわれ、凹凸が形成されている。また、半導体層 130 の表面（分離面）には脆化層 102 が残存する場合もある。半導体層 130 表面に凹凸があると、得られた SOI 基板を用いて半導体装置を製造する際、薄く絶縁耐圧の優れたゲート絶縁層の形成が困難となる。そのため、半導体層 130 は平坦化処理を行うことが好ましい（図 5（E）参照）。

【0081】

以上で、支持基板 120 上に接合層 110、窒素含有絶縁層 112 及び熱酸化膜 111 を介して半導体層 130 が固着された SOI 基板を製造することができる。

【0082】

本形態に係る SOI 基板の製造方法は、脆化層が形成された半導体基板と支持基板とを絶縁層を間に挟んで貼り合わせ、半導体基板にレーザビームを選択的に照射して脆化層の脆化を部分的に進行させた後、物理的手段により半導体基板を分離させる。半導体基板の分離の際、レーザビームの照射により脆化が進行した領域の脆化層が始点となるため、容易に分離することができる。また、物理的手段により半導体基板を分離することで、SOI 基板の製造時間を短縮することができる。よって、SOI 基板の製造におけるスループットが向上し、生産性が向上する。

【0083】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0084】

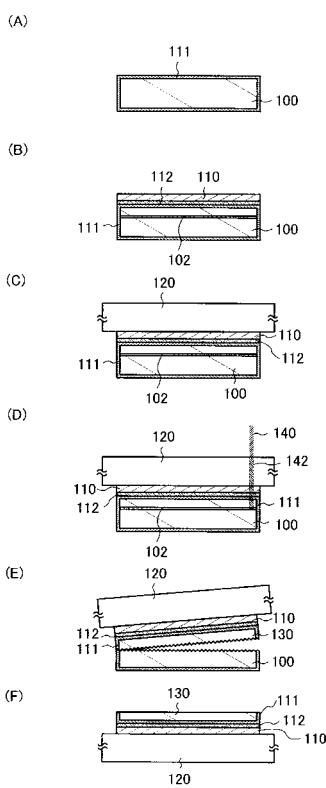

（実施の形態 2）

上記実施の形態では、支持基板側からレーザビームを照射する例を示したが、本形態では半導体基板に直接レーザビームを照射する例を図 6 に示す。

【0085】

10

20

30

40

50

図6( A )、( B )は、半導体基板100と支持基板120とを、絶縁層104を間に挟んで貼り合わせた状態を示す模式的な斜視図である。半導体基板100の所定の深さの領域には、脆化層102が形成されている。半導体基板100、脆化層102、支持基板120、及び絶縁層104の説明は、上記実施の形態1に準じる。また、図6では、支持基板120及び絶縁層104は点線で示している。

#### 【0086】

本形態において、レーザビーム170は半導体基板100の側面に選択的に照射する。また、レーザビーム170は脆化層102に到達するように照射する。半導体基板100の側面に脆化層102が露出している場合は、露出している脆化層102に直接レーザビーム170を照射すればよい。

10

#### 【0087】

レーザビーム170としては、半導体基板100に吸収される波長を有するものとする。具体的には、レーザビーム170の波長は可視領域～紫外領域(800nm以下)が好ましく、より好ましくは紫外領域(400nm以下)とする。用いるレーザビームとしては、例えばXeClエキシマレーザ(発振波長308nm)から射出されるレーザビーム、固体レーザであるYAGレーザ(発振波長1064nm)の第2高調波や第3高調波、YVO<sub>4</sub>レーザの第2高調波や第3高調波、或いはYLFレーザの第2高調波や第3高調波、Ar<sup>+</sup>レーザ(発振波長364nm)から射出されるレーザビーム等が挙げられる。なお、本形態に用いるレーザは特に限定されず、所望の発振波長(好ましくは可視領域～紫外領域、より好ましくは紫外領域)のレーザビームが得られるものであればよい。また、連続発振型レーザでもパルス型レーザでもよい。

20

#### 【0088】

レーザビーム170が照射された照射領域172における脆化層102は、レーザビーム170を吸収することにより加熱され、脆化が進行する。つまり、半導体基板100に形成された脆化層102は、照射領域172に沿って脆化が進行する。例えば、図6( B )では、半導体基板100の側面に露出した脆化層102の脆化が進行することになる。なお、照射領域172における脆化層102は、レーザビーム170の照射による加熱により溶融する場合もある。脆化が進行した領域の脆化層102は、半導体基板100の分離を行う際の始点(きっかけ)となる。

30

#### 【0089】

この後、物理的手段により、脆化層102を境として半導体基板100を分離させ、必要に応じて分離面の平坦化を行うことで、支持基板上に半導体層が固定されたSOI基板を得ることができる。半導体基板100を分離する際は、レーザビームの照射により予め部分的に脆化層の脆化が進行しているため、容易に分離することができる。したがって、スループット良くSOI基板を製造することができ、生産性が向上する。

#### 【0090】

なお、本実施の形態では、レーザビーム170を半導体基板100の側面に選択的に照射するため、レーザビーム170のビーム形状は線状とすることが好ましい。例えば、レーザビーム170の進行方向に対する垂直方向の断面におけるビーム形状の短軸は1μm以下、又は100nm以下とすることもできる。なお、レーザビーム170の進行方向に対する垂直方向の断面におけるビーム形状の長軸方向は、レーザビーム170の走査方向となるようにすることができます。このようにすることで、他の層に与えるダメージを少なくすることができる。特に、半導体基板を分離した後に再利用する場合に、ダメージを防ぐ構成とすることが有効である。

40

#### 【0091】

また、上記実施の形態1では、支持基板120側からレーザビームを照射して透過させる構成としたが、本形態ではレーザビームを直接半導体基板100に照射するため、支持基板120は透光性を有する基板以外のものを適用できる。つまり、支持基板120は絶縁表面を有する基板又は絶縁性を有する基板を適用することができ、例えば表面が絶縁層で被覆された金属基板も適用することができる。

50

## 【0092】

また、本形態に係るSOI基板の製造方法は、半導体基板を分離する前にレーザビームを照射することで、予め部分的に脆化層の脆化を進行させておくことを特徴の一つとしており、SOI基板の構成は特に限定されるものではない。例えば、本明細書に示すその他の構成のSOI基板を形成することができる。

## 【0093】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

## 【0094】

(実施の形態3)

10

本実施の形態では、上記実施の形態と異なるSOI基板の製造方法について説明する。

## 【0095】

所定の深さの領域に脆化層102が形成され、一表面上に絶縁層104が形成された半導体基板100と、支持基板120と、を準備する。次に、半導体基板100と、支持基板120と、を、絶縁層104を間に挟んで重ね合わせて貼り合わせる。そして、支持基板120側からレーザビーム140を選択的に照射し、部分的に脆化層102の脆化を行わせる(図7(A)参照)。

## 【0096】

本形態において、脆化層102と絶縁層104を形成する順序は限定されない。半導体基板100にイオンを照射して脆化層102を形成した後に絶縁層104を形成してもよいし、半導体基板100上に絶縁層104を形成した後に該絶縁層104が形成された側からイオンを照射し脆化層102を形成してもよい。また、絶縁層104を積層構造とする場合は、絶縁層を積層する途中で、半導体基板100にイオンを照射し脆化層102を形成してもよい。なお、絶縁層104の最上層は、有機シランを原料ガスに用いてCVD法により形成される酸化シリコン層やシロキサン結合を有する層などの、平滑性を有し親水性表面を形成できる接合層を形成する。

20

## 【0097】

また、熱酸化法により、半導体基板100表面に熱酸化膜を形成することもできる。さらに、支持基板120側に窒素含有絶縁層及び接合層の積層構造を設けることもできる。支持基板120側にも接合層を設けることで、支持基板と半導体基板の接合強度を高めることができる。

30

## 【0098】

また、ここでは、レーザビーム140を支持基板120側から照射する例を示すが、上記実施の形態2で示したように、半導体基板100の側面から照射してもよい。

## 【0099】

なお、支持基板120側から照射するレーザビーム140のビーム形状は、面積を有するようにすることが好ましい。例えば、光学系を用いてレーザビーム140を矩形又は橢円形に整形することが好ましい。これは、脆化層102はレーザビーム140の照射された領域で脆化が進行されるため、ある程度の面積で脆化を進行させる方が、後の加熱処理により容易に体積変化を起こせるからである。

40

## 【0100】

次に、加熱処理を行い、脆化層102を境として半導体基板100を分離させる。半導体基板100は絶縁層104を間に介して支持基板120に接合されており、脆化層102を境として半導体基板100の一部を分離させた結果、支持基板120上に半導体層130が残存する(図7(B)参照)。

## 【0101】

脆化層102は、レーザビーム140の照射により部分的に脆化が進行している。加熱処理により、脆化層102に形成された微小な空洞に体積変化が起こるが、本形態のようにレーザビームの照射により部分的に脆化層の脆化を進行させておくことで、該脆化を行わせた領域がきっかけとなって脆化層102の体積変化が起こりやすくなり、容易に分

50

離することが可能となる。したがって、加熱処理の温度及び処理時間は、レーザビームを照射しない場合よりも低温短時間とすることが可能である。

【0102】

以上で、支持基板120上に半導体層130が固着されたSOI基板を得ることができる。

【0103】

なお、支持基板120に転置された半導体層130は、イオン照射工程及び分離工程によって、表面(分離面)は平坦性が損なわれ、凹凸が形成されている。また、半導体層130の表面(分離面)には脆化層102が残存する場合もある。半導体層130表面に凹凸があると、得られたSOI基板を用いて半導体装置を製造する際、薄く絶縁耐圧の優れたゲート絶縁層の形成が困難となる。そのため、半導体層130は平坦化処理を行うことが好ましい(図7(C)参照)。

10

【0104】

本形態に係るSOI基板の製造方法は、脆化層が形成された半導体基板と、支持基板と、を、絶縁層を間に挟んで貼り合わせ、半導体基板にレーザビームを選択的に照射して部分的に脆化層の脆化を進行させた後、加熱処理を行うことにより半導体基板を分離させる。半導体基板の分離の際、加熱処理を行うことにより、レーザビームの照射領域の脆化層がきっかけとなって容易に体積変化が起きる。したがって、レーザビームを照射せずに加熱処理のみで分離工程を行うよりも低温短時間の分離工程とすることが可能であり、製造時間を短縮することができる。よって、SOI基板の製造におけるスループットを向上することができる。なお、本形態に係るSOI基板の構成は特に限定されず、本明細書で示すその他の構成のSOI基板を形成してもよい。

20

【0105】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0106】

(実施の形態4)

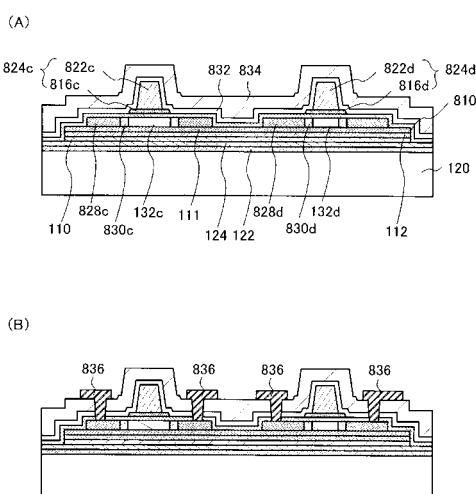

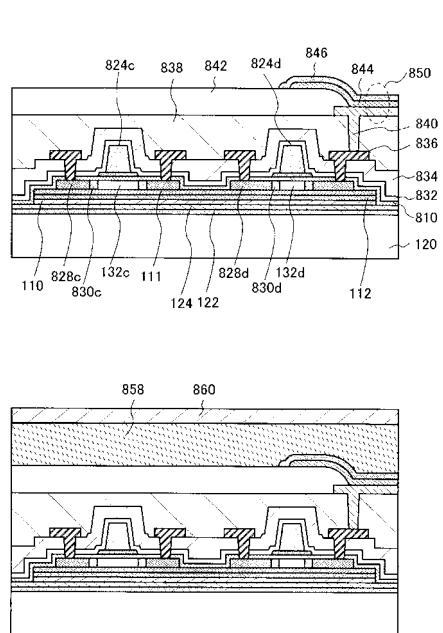

本実施の形態では、上記実施の形態で示したSOI基板を用いて半導体装置を製造する一例を、図13、図14を用いて説明する。

【0107】

30

SOI基板を準備する(図13(A)参照)。本形態では、図3(A)に示す支持基板120上に順に積層された接合層110、窒素含有絶縁層112、及びシリコン酸化層114を介して半導体層130が固着されたSOI基板を適用する例を示す。なお、適用するSOI基板の構成は特に限定されず、本明細書で示すその他の構成のSOI基板を適用できる。

【0108】

支持基板120としては、絶縁表面を有する基板又は絶縁性を有し、且つ紫外光又は可視光を透過する透光性を有する基板を適用する。例えばアルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板(「無アルカリガラス基板」とも呼ばれる)、石英基板、結晶化ガラス基板、又はサファイヤ基板などが適用される。

40

【0109】

接合層110は平滑性を有し親水性表面を形成できる層を形成し、例えば酸化シリコン層又はシロキサン結合を有する層とする。窒素含有絶縁層112はブロッキング層として機能し、例えば窒化シリコン層又は窒化酸化シリコン層で形成すればよい。窒素含有絶縁層112を形成することで、支持基板120から半導体層130側への金属不純物の拡散をブロッキングすることができる。シリコン酸化層114は、酸化シリコン層又は酸化窒化シリコン層を形成する。半導体層130と窒素含有絶縁層112の間にシリコン酸化層114が位置することで、トラップ準位が形成され界面特性が劣化するのを防止することができる。また、窒素含有絶縁層112と支持基板120との間に接合層110が位置す

50

ることで、該接合層 110 が窒素含有絶縁層 112 の内部応力を緩和して、異種材料による応力歪みを緩和することができる。

【0110】

なお、接合層 110、窒素含有絶縁層 112、及びシリコン酸化層 114 の膜厚は実施者が適宜決定すればよい。例えば、接合層 110 の膜厚は 0.2 nm 乃至 500 nm (接合層 110 を CVD 法により形成する場合は 10 nm 乃至 500 nm)、窒素含有絶縁層 112 の膜厚は 10 nm 乃至 500 nm、シリコン酸化層 114 の膜厚は 10 nm 乃至 500 nm とすることができます。一例として、接合層 110 として膜厚 50 nm の酸化シリコン層を形成し、窒素含有絶縁層 112 として膜厚 50 nm の窒化酸化シリコン層を形成し、シリコン酸化層 114 として膜厚 100 nm の酸化窒化シリコン層を形成することができる。

10

【0111】

半導体層 130 の膜厚は 5 nm 乃至 300 nm、好ましくは 10 nm 乃至 200 nm、より好ましくは 10 nm 乃至 60 nm とする。半導体層 130 の膜厚は、上記実施の形態で説明した脆化層 102 を形成する深さを制御することにより適宜設定できる。また、SOI 基板の半導体層 130 を、エッチング等により薄膜化して所望の膜厚としてもよい。半導体層 130 の薄膜化は、Cl<sub>2</sub>、BCl<sub>3</sub> 若しくは SiCl<sub>4</sub> 等の塩素系ガス、CF<sub>4</sub>、NF<sub>3</sub> 若しくは SF<sub>6</sub> 等のフッ素系ガス、又は HBr ガス等を用いてドライエッチングにより行うことができる。また、酸化処理や窒化処理等により半導体層 130 を部分的に変質させて、該変質部分を選択的にエッチングすることもできる。また、CMP 処理や液体ジェットによる研磨などをを利用して、半導体層 130 を薄膜化することもできる。

20

【0112】

半導体層 130 には、n チャネル型電界効果トランジスタの形成領域に合わせて、硼素、アルミニウム、ガリウムなどの p 型不純物元素、又は、リン、砒素などの n 型不純物元素を添加することが好ましい。同様に、p チャネル型電界効果トランジスタの形成領域に合わせて、リン、砒素などの n 型不純物元素、又は、硼素、アルミニウム、ガリウムなどの p 型不純物元素を添加することが好ましい。例えば、n チャネル型電界効果トランジスタの形成領域に対応して p 型不純物元素を添加し、p チャネル型電界効果トランジスタの形成領域に対応して n 型不純物元素を添加して、所謂ウェル領域を形成する。不純物イオンのドーズ量は  $1 \times 10^{12}$  ions/cm<sup>2</sup> 乃至  $1 \times 10^{14}$  ions/cm<sup>2</sup> 程度で行えよ。さらに、電界効果トランジスタのしきい値電圧を制御する場合には、これらのウェル領域に p 型不純物元素、又は、n 型不純物元素を添加すればよい。

30

【0113】

次に、半導体層 130 を選択的にエッチングして、半導体素子の配置に合わせて島状に分離した半導体層 130a、半導体層 130b を形成する (図 13 (B) 参照)。

【0114】

なお、本形態では、半導体層 130 を島状にエッチングすることで素子分離をする例を示すが、本発明は特に限定されない。例えば、半導体素子の配置に合わせて、半導体層間に絶縁層を埋め込むことで素子分離してもよい。

40

【0115】

次に、半導体層 130a、半導体層 130b 上に、ゲート絶縁層 711、ゲート電極 712、及びサイドウォール絶縁層 713 をそれぞれ形成する。サイドウォール絶縁層 713 は、ゲート電極 712 の側面に設ける。そして、半導体層 130a に第 1 不純物領域 714a 及び第 2 不純物領域 715a、半導体層 130b に第 1 不純物領域 714b 及び第 2 不純物領域 715b を形成する。なお、ゲート電極 712 上には絶縁層 716 が形成されている。絶縁層 716 は窒化シリコン層で形成し、ゲート電極 712 を形成する際のエッチング用のハードマスクとして用いる (図 13 (C) 参照)。

【0116】

次に、SOI 基板に設けられたゲート電極 712 等を覆うように、保護層 717 を形成する (図 13 (D) 参照)。窒素含有絶縁層 112 は支持基板 120 側からの金属不純物

50

の拡散を防止するのに対して、保護層 717 は上層側からの金属不純物の汚染を防ぐ効果がある。本形態では、結晶性に優れた半導体層 130 の下層側及び上層側を、ナトリウムなどの可動性の高い金属不純物をブロッキングする効果の高い絶縁層で被覆する。よって、半導体層 130 により製造される半導体素子の電気的特性を向上させることができる。

【0117】

保護層 717 上に層間絶縁層 718 を形成する。層間絶縁層 718 は、BPSG (Boron Phosphorus Silicon Glass) 層を成膜する、或いはポリイミドに代表される有機樹脂を塗布して形成すればよい。そして、層間絶縁層 718 にコンタクトホール 719 を形成する。

【0118】

次に、配線を形成する段階を示す。コンタクトホール 719 にコンタクトプラグ 723 を形成する。コンタクトプラグ 723 は、WF<sub>6</sub> ガスと SiH<sub>4</sub> ガスから CVD 法によりタンゲステンシリサイドを形成し、コンタクトホール 719 に埋め込むことで形成する。また、WF<sub>6</sub> を水素還元してタンゲステンを形成しコンタクトホール 719 に埋め込んでも良い。その後、コンタクトプラグ 723 に合わせて配線 721 を形成する。配線 721 はアルミニウム若しくはアルミニウム合金で形成し、上層と下層にはバリアメタルとしてモリブデン、クロム、チタンなどの金属膜を形成する。さらにその上層に層間絶縁層 722 を形成する（図 14 (B) 参照）。配線は適宜設ければ良く、この上層にさらに配線層を形成して多層配線化しても良い。その場合にはダマシンプロセスを適用しても良い。

【0119】

以上で、支持基板上に半導体層が固着された SOI 基板を用いて、電界効果トランジスタを製造することができる。本発明は、SOI 基板の製造時間の短縮を可能とし、スループットを向上している。したがって、本発明に係る SOI 基板を適用することで、生産性良く電界効果トランジスタを製造することができる。また、本発明を適用することで、単結晶半導体で半導体層 130 を形成することが可能であり、半導体装置の高性能化を図ることもできる。

【0120】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0121】

（実施の形態 5）

本実施の形態では、本発明に係る SOI 基板を用いて半導体装置を製造する一例を、図 9 乃至図 12 を用いて説明する。ここでは、エレクトロルミネンス (EL) 表示装置を製造する一例を示す。

【0122】

SOI 基板を準備する（図 9 (A) 参照）。本形態では、図 4 (C) に示す支持基板 120 上に順に積層された窒素含有絶縁層 122、接合層 124、接合層 110、窒素含有絶縁層 112、及び熱酸化膜 111 を介して半導体層 130 が固着された SOI 基板を適用する例を示す。なお、適用する SOI 基板の構成は特に限定されず、本明細書で示すその他の構成の SOI 基板を適用できる。

【0123】

支持基板 120 としては、絶縁表面を有する基板又は絶縁性を有し、且つ紫外光又は可視光を透過する透光性を有する基板を適用する。例えばアルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板（「無アルカリガラス基板」とも呼ばれる）、石英基板、結晶化ガラス基板、又はサファイヤ基板などが適用される。

【0124】

接合層 110 及び接合層 124 は、平滑性を有し親水性表面を形成できる層を形成し、例えば酸化シリコン層又はシロキサン結合を有する層を形成する。なお、接合層 124 は、支持基板 120 の耐熱性を考慮して形成する必要がある。支持基板 120 としてガラス

10

20

30

40

50

基板を適用する場合は 650 以下の成膜温度とする。例えば、TEOS 等の有機シランを原料ガスに用いて CVD 法により形成することができる。支持基板 120 と接合層 124 との間に形成する窒素含有絶縁層 122 は、窒化シリコン層、窒化酸化シリコン層又は窒化アルミニウム層等の金属不純物をブロッキングする効果を有する膜を形成する。なお、支持基板 120 に接合層 124 及び窒素含有絶縁層 122 を形成する場合、下層（支持基板 120 側）に窒素含有絶縁層 122 を形成し、上層（半導体層 130 側）に接合層 124 を形成することで、窒素含有絶縁層 122 の内部応力を緩和することができる。窒素含有絶縁層 112 は、窒化シリコン層又は窒化酸化シリコン層で形成すればよい。熱酸化膜 111 は、半導体基板を熱酸化して形成するため、半導体層 130 の側面にも形成されている。

10

#### 【0125】

なお、窒素含有絶縁層 122、接合層 124、接合層 110、窒素含有絶縁層 112、及び熱酸化膜 111 の膜厚は実施者が適宜決定すればよい。熱酸化膜 111 の膜厚は、熱酸化の処理時間や加熱温度等により制御できる。

#### 【0126】

半導体層 130 の膜厚は 5 nm 乃至 300 nm、好ましくは 10 nm 乃至 200 nm、より好ましくは 10 nm 乃至 60 nm とする。半導体層 130 の膜厚は、上記実施の形態で説明した脆化層 102 を形成する深さを制御することにより適宜設定できる。また、SOI 基板の半導体層 130 を、エッチング等により薄膜化して所望の膜厚としてもよい。半導体層 130 の薄膜化は、Cl<sub>2</sub>、BCl<sub>3</sub> 若しくは SiCl<sub>4</sub> 等の塩素系ガス、CF<sub>4</sub>、NF<sub>3</sub> 若しくは SF<sub>6</sub> 等のフッ素系ガス、又は HBr ガス等を用いてドライエッチングにより行うことができる。また、酸化処理や窒化処理等により半導体層 130 を部分的に変質させて、該変質部分を選択的にエッチングすることもできる。また、CMP 処理や液体ジェットによる研磨などをを利用して、半導体層 130 を薄膜化することもできる。

20

#### 【0127】

また、半導体層 130 には、n チャネル型電界効果トランジスタの形成領域に合わせて、硼素、アルミニウム、ガリウムなどの p 型不純物元素、又は、リン、砒素などの n 型不純物元素を添加することが好ましい。同様に、p チャネル型電界効果トランジスタの形成領域に合わせて、リン、砒素などの n 型不純物元素、又は、硼素、アルミニウム、ガリウムなどの p 型不純物元素を添加することが好ましい。例えば、n チャネル型電界効果トランジスタの形成領域に対応して p 型不純物元素を添加し、p チャネル型電界効果トランジスタの形成領域に対応して n 型不純物元素を添加して、所謂ウェル領域を形成する。不純物イオンのドーズ量は  $1 \times 10^{12}$  ions/cm<sup>2</sup> 乃至  $1 \times 10^{14}$  ions/cm<sup>2</sup> 程度で行えばよい。さらに、電界効果トランジスタのしきい値電圧を制御する場合には、これらのウェル領域に p 型不純物元素若しくは n 型不純物元素を添加すればよい。

30

#### 【0128】

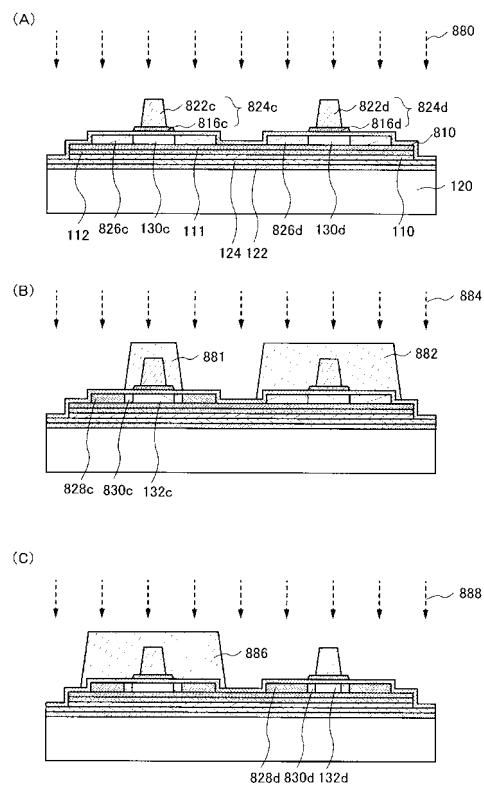

次に、半導体層 130 を選択的にエッチングして、半導体素子の配置に合わせて島状に分離した半導体層 130c、半導体層 130d を形成する（図 9（B）参照）。

#### 【0129】

次に、半導体層 130c、半導体層 130d 上に、ゲート絶縁層 810、ゲート電極を形成する第 1 の導電層 812、及び第 2 の導電層 814 を順に形成する（図 9（C）参照）。

40

#### 【0130】

ゲート絶縁層 810 は、CVD 法、スパッタリング法、又は原子層エピタキシ法等により、酸化シリコン層、酸化窒化シリコン層、窒化シリコン層、又は窒化酸化シリコン層等の絶縁層を用いて、単層膜又は積層膜で形成する。

#### 【0131】

また、ゲート絶縁層 810 は、半導体層 130c、半導体層 130d に対してプラズマ処理を行うことにより、表面を酸化又は窒化することで形成してもよい。この場合のプラズマ処理はマイクロ波（代表的な周波数は 2.45 GHz）を用いて励起したプラズマに

50

よるプラズマ処理も含むものとする。例えばマイクロ波で励起され、電子密度が $1 \times 10^{11} / \text{cm}^3$ 以上 $1 \times 10^{13} / \text{cm}^3$ 以下、且つ電子温度が $0.5 \text{ eV}$ 以上 $1.5 \text{ eV}$ 以下のプラズマを用いた処理も含むものとする。このようなプラズマ処理を適用して半導体層表面の酸化処理又は窒化処理を行うことにより、薄くて緻密な膜を形成することが可能である。また、半導体層表面を直接酸化するため、界面特性の良好な膜を得ることができ。なお、ゲート絶縁層810は、CVD法、スパッタリング法、又は原子層エピタキシ法により形成した膜に対してマイクロ波を用いたプラズマ処理を行うことで形成してもよい。

#### 【0132】

なお、ゲート絶縁層810は半導体層との界面を形成するため、酸化シリコン層、酸化窒化シリコン層が界面となるように形成することが好ましい。これは、窒化シリコン層又は窒化酸化シリコン層のように酸素よりも窒素の含有量が多い膜を形成すると、トラップ準位が形成され界面特性が問題となる恐れがあるからである。

#### 【0133】

ゲート電極を形成する導電層は、タンタル、窒化タンタル、タンゲステン、チタン、モリブデン、アルミニウム、銅、クロム、又はニオブ等から選択された元素、またはこれらの元素を主成分とする合金材料若しくは化合物材料、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体材料を用いて、CVD法やスパッタリング法により、単層膜又は積層膜で形成する。積層膜とする場合は、異なる導電材料を用いて形成することもできるし、同一の導電材料を用いて形成することもできる。本形態では、ゲート電極を形成する導電層を、第1の導電層812及び第2の導電層814で形成する例を示す。

#### 【0134】

ゲート電極を形成する導電層を、第1の導電層812及び第2の導電層814の2層の積層構造とする場合は、例えば、窒化タンタル層とタンゲステン層、窒化タンゲステン層とタンゲステン層、窒化モリブデン層とモリブデン層の積層膜を形成することができる。なお、窒化タンタル層とタンゲステン層との積層膜とすると、両者のエッチング速度の差をつけやすく、高い選択比が取れるため好ましい。なお、例示した2層の積層膜において、先に記載した層がゲート絶縁層810上に形成される層とすることが好ましい。ここでは、第1の導電層812は、 $20 \text{ nm}$ 乃至 $100 \text{ nm}$ の厚さで形成する。第2の導電層814は、 $100 \text{ nm}$ 乃至 $400 \text{ nm}$ の厚さで形成する。なお、ゲート電極は3層以上の積層構造とすることもでき、その場合は、モリブデン層とアルミニウム層とモリブデン層の積層構造を採用するとよい。

#### 【0135】

次に、第2の導電層814上にレジストマスク820c、レジストマスク820dを選択的に形成する。そして、レジストマスク820c、レジストマスク820dを用いて第1のエッチング処理及び第2のエッチング処理を行う。

#### 【0136】

まず、第1のエッチング処理により第1の導電層812及び第2の導電層814を選択的にエッチングして、半導体層130c上に第1の導電層816c及び第2の導電層818c、並びに半導体層130d上に第1の導電層816d及び第2の導電層818dを形成する(図9(d)参照)。

#### 【0137】

次に、第2のエッチング処理により第2の導電層818c及び第2の導電層818dの端部を選択的にエッチングして、第2の導電層822c及び第2の導電層822dを形成する(図9(E)参照)。なお、第2の導電層822c及び第2の導電層822dは第1の導電層816c及び第1の導電層816dよりも幅(キャリアがチャネル形成領域を流れる方向(ソース領域とドレイン領域を結ぶ方向)に平行な方向の長さ)が小さくなるように形成する。このようにして、第1の導電層816c及び第2の導電層822cからなるゲート電極824c、並びに第1の導電層816d及び第2の導電層822dからなる

10

20

30

40

50

ゲート電極 824d を得ることができる。

【0138】

第1のエッティング処理及び第2のエッティング処理に適用するエッティング法は適宜選択すればよいが、エッティング速度を向上するには ECR (Electron Cyclotron Resonance) 方式や ICP (Inductively Coupled Plasma : 誘導結合プラズマ) 方式などの高密度プラズマ源を用いたドライエッティング装置を用いればよい。第1のエッティング処理および第2のエッティング処理のエッティング条件を適宜調節することで、第1の導電層 816c、816d、及び第2の導電層 822c、822d の側面を所望のテーパー形状とすることができます。所望のゲート電極 824c、824d を形成した後、レジストマスク 820c、820d は除去すればよい。 10

【0139】

次に、ゲート電極 824c、ゲート電極 824d をマスクとして、半導体層 130c 及び半導体層 130d に不純物元素 880 を添加する。半導体層 130c には、第1の導電層 816c 及び第2の導電層 822c をマスクとして自己整合的に一対の第1不純物領域 826c が形成される。また、半導体層 130d には、第1の導電層 816d 及び第2の導電層 822d をマスクとして自己整合的に一対の第1不純物領域 826d が形成される（図10（A）参照）。

【0140】

不純物元素 880 としては、硼素、アルミニウム、ガリウムなどの p 型不純物元素、若しくはリン、砒素などの n 型不純物元素を添加する。ここでは、n 型不純物元素であるリンを  $1 \times 10^{17}$  atoms/cm<sup>3</sup> 乃至  $5 \times 10^{18}$  atoms/cm<sup>3</sup> 程度の濃度で含まれるように添加するものとする。 20

【0141】

次に、半導体層 130d を覆うようにレジストマスク 882 を選択的に形成する。また、半導体層 130c を部分的に覆うようにレジストマスク 881 を形成する。そして、レジストマスク 882、及びレジストマスク 881 をマスクとして不純物元素 884 を添加して、半導体層 130c に一対の第2不純物領域 828c と、一対の第3不純物領域 830c と、チャネル形成領域 132c を形成する（図10（B）参照）。

【0142】

不純物元素 884 としては、硼素、アルミニウム、ガリウムなどの p 型不純物元素、若しくはリン、砒素などの n 型不純物元素を添加する。ここでは、n 型不純物元素であるリンを  $5 \times 10^{19}$  atoms/cm<sup>3</sup> 乃至  $5 \times 10^{20}$  atoms/cm<sup>3</sup> 程度の濃度で含まれるように添加するものとする。 30

【0143】

半導体層 130c において、第2不純物領域 828c は第1の導電層 816c 及び第2の導電層 822c と重ならない領域に形成される。チャネル形成領域 132c は第1の導電層 816c と重なる領域に形成される。第3不純物領域 830c は、チャネル形成領域 132c と第2不純物領域 828c の間であって、第1の導電層 816c 及び第2の導電層 822c と重ならない領域に形成される。また、第3不純物領域 830c は、第1の導電層 816c 及び第2の導電層 822c と重ならない領域であって、レジストマスク 881 と重なる領域に形成される。第2不純物領域 828c はソース領域又はドレイン領域として機能する。また、第3不純物領域 830c は LDD 領域として機能する。本形態において、第2不純物領域 828c は、第3不純物領域 830c よりも不純物濃度が高いものとする。 40

【0144】

なお、LDD 領域とは、チャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に形成する低濃度に不純物元素を添加した領域のことである。LDD 領域を設けると、ドレイン領域近傍の電界を緩和してホットキャリア注入による劣化を防ぐという効果がある。また、ホットキャリアによるオン電流値の劣化を防ぐため、ゲート絶縁層を介して LDD 領域をゲート電極と重ねて配置させた構造（「G 50

OLD (Gate-drain Overlapped LDD) 構造」とも呼ぶ)としてもよい。

【0145】

次に、レジストマスク 881 及びレジストマスク 882 を除去した後、半導体層 130c を覆うようにレジストマスク 886 を形成する。そして、レジストマスク 886、第1 の導電層 816d 及び第2 の導電層 822d をマスクとして不純物元素 888 を添加して、半導体層 130d に一対の第2不純物領域 828d と、一対の第3不純物領域 830d と、チャネル形成領域 132d を形成する(図10(C)参照)。

【0146】

不純物元素 888 としては、硼素、アルミニウム、ガリウムなどの p 型不純物元素、若しくはリン、砒素などの n 型不純物元素を添加する。ここでは p 型不純物元素である硼素を  $1 \times 10^{20}$  atoms/cm<sup>3</sup> 乃至  $5 \times 10^{21}$  atoms/cm<sup>3</sup> 程度含まれるように添加するものとする。

【0147】

半導体層 130d において、第2不純物領域 828d は第1の導電層 816d 及び第2 の導電層 822d と重ならない領域に形成される。第3不純物領域 830d は、第1の導電層 816d と重なり、第2の導電層 822d と重ならない領域に形成されており、不純物元素 888 が第1の導電層 816d を貫通して形成される。第2不純物領域 828d はソース領域又はドレイン領域として機能する。また、第3不純物領域 830d は LDD 領域として機能する。本形態において、第2不純物領域 828d は、第3不純物領域 830d よりも不純物濃度が高いものとする。

【0148】

次に、層間絶縁層を形成する。層間絶縁層は、単層膜又は積層膜で形成することができるが、ここでは絶縁層 832 及び絶縁層 834 の2層の積層構造で形成する(図11(A)参照)。

【0149】

層間絶縁層としては、CVD 法やスパッタリング法により、酸化シリコン層、酸化窒化シリコン層、窒化シリコン層、又は窒化酸化シリコン層等を形成することができる。また、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル若しくはエポキシ等の有機材料、シロキサン樹脂等のシロキサン材料、又はオキサゾール樹脂などを用いて、スピンドル法などの塗布法により形成することができる。なお、シロキサン材料とは、Si-O-Si 結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。有機基は、フルオロ基を含んでもよい。オキサゾール樹脂は、例えば、感光性ポリベンゾオキサゾール等である。感光性ポリベンゾオキサゾールは、誘電率が低く(常温 1 MHz で誘電率 2.9)、耐熱性が高く(示差熱天秤(TG/DTA: Thermogravimetry-Differential Thermal Analysis)で昇温 5 / min で熱分解温度 550)、吸水率が低い(常温 24 時間で 0.3 wt %)材料である。オキサゾール樹脂は、ポリイミド等の比誘電率(3.2 ~ 3.4 程度)と比較すると、比誘電率が低いため(2.9 程度)、寄生容量の発生を抑制し、高速動作を行うことができる。

【0150】

例えば、絶縁層 832 として窒化酸化シリコン層を膜厚 100 nm で形成し、絶縁層 834 として酸化窒化シリコン層を膜厚 900 nm で形成する。また、絶縁層 832 及び絶縁層 834 を、プラズマ CVD 法を適用して連続成膜する。なお、層間絶縁層は 3 層以上の積層構造とすることもできる。また、酸化シリコン層、酸化窒化シリコン層又は窒化シリコン層と、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル、エポキシ等の有機材料、シロキサン樹脂等のシロキサン材料、又はオキサゾール樹脂を用いて形成した絶縁層との積層構造とすることもできる。

【0151】

10

20

30

40

50

次に、層間絶縁層（本形態では絶縁層 832 及び絶縁層 834）にコンタクトホールを形成し、該コンタクトホールにソース電極又はドレイン電極として機能する導電層 836 を形成する（図 11（B）参照）。

【0152】

コンタクトホールは、半導体層 130c に形成された第 2 不純物領域 828c、半導体層 130d に形成された第 2 不純物領域 828d に達するように、絶縁層 832 及び絶縁層 834 に選択的に形成する。

【0153】

導電層 836 は、アルミニウム、タングステン、チタン、タンタル、モリブデン、ニッケル、ネオジムから選ばれた一種の元素または当該元素を複数含む合金からなる単層膜または積層膜を用いることができる。例えば、当該元素を複数含む合金からなる導電層として、チタンを含有したアルミニウム合金、ネオジムを含有したアルミニウム合金などを形成することができる。また、積層膜とする場合、例えば、アルミニウム層若しくは上述したようなアルミニウム合金層を、チタン層で挟持する構成とすることができる。

【0154】

次に、発光素子 850 を形成する段階を示す（図 12（A）参照）。ここでは、有機化合物を含む層を発光層として具備する有機発光素子を形成する一例について説明する。

【0155】

まず、導電層 836 と電気的に接続するように画素電極 840 を形成する。画素電極 840 は、導電層 836 を間に介して、半導体層 130d に形成された第 2 不純物領域 828d と電気的に接続される。画素電極 840 の端部を覆う隔壁層 842 を形成した後、画素電極 840 上に有機化合物を含む層 844 と、対向電極 846 とを積層形成する。

【0156】

なお、ここでは、導電層 836 上に設けられた絶縁層 838 上に画素電極 840 が形成されている例を示すが、本発明は特に限定されない。例えば、絶縁層 834 上に画素電極 840 を設ける構成としてもよい。この場合、画素電極 840 は、ソース電極又はドレイン電極として機能する導電層 836 の一部で形成することもできる。

【0157】

絶縁層 838 としては、CVD 法やスパッタ法により酸化シリコン層、酸化窒化シリコン層、窒化シリコン層等を形成することができる。また、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル、エポキシ等の有機材料、シロキサン樹脂等のシロキサン材料、またはオキサゾール樹脂などを用いて、スピンコート法などの塗布法により形成することができる。なお、絶縁層 838 は、上述の材料を用いて単層膜または積層膜で形成することができる。

【0158】

画素電極 840 及び対向電極 846 は、いずれか一方は陽極として機能し、他方は陰極として機能する。また、発光素子の発光は、支持基板 120 側から取り出す場合（下面射出とも呼ばれる）と、支持基板 120 側と逆側の面から取り出す場合（上面射出とも呼ばれる）と、支持基板 120 側及び当該支持基板 120 と逆側の面から取り出す場合（両面射出とも呼ばれる）と、がある。下面射出の場合は、画素電極 840 は透光性電極とし、対向電極 846 は反射電極とすることが好ましい。これに対し、上面射出の場合は、画素電極 840 は反射電極とし、対向電極 846 は透光性電極とすることが好ましい。両面射出の場合は、画素電極 840 及び対向電極 846 ともに透光性電極とすることが好ましい。

【0159】

画素電極 840 又は対向電極 846 として反射電極を形成する場合、タンタル、タングステン、チタン、モリブデン、アルミニウム、クロム、銀等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料等の反射性を有する導電材料を用いて形成することができる。

【0160】

10

20

30

40

50

また、画素電極 840 又は対向電極 846 として透光性電極を形成する場合、酸化インジウムスズ (ITO)、酸化亜鉛 (ZnO)、酸化インジウム亜鉛 (IZO)、又はガリウムを添加した酸化亜鉛 (GZO) 等の透光性を有する導電材料を用いて形成することができる。また、反射性を有する導電材料を数 nm 乃至数十 nm の膜厚で形成することで、可視光を透過させる電極を得ることもできる。

#### 【0161】

また、透光性電極は、導電性高分子（導電性ポリマーともいう）を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した電極は、薄膜におけるシート抵抗が 10000 / 以下、波長 550 nm における透光率が 70 % 以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が 0.1 · cm 以下であることが好ましい。

10

#### 【0162】

導電性高分子としては、いわゆる 電子共役系導電性高分子が用いることができる。例えば、ポリアニリン若しくはその誘導体、ポリピロール若しくはその誘導体、ポリチオフェン若しくはその誘導体、又はこれらの 2 種以上の共重合体などがあげられる。

#### 【0163】

共役導電性高分子の具体例としては、ポリピロール、ポリ(3-メチルピロール)、ポリ(3-ブチルピロール)、ポリ(3-オクチルピロール)、ポリ(3-デシルピロール)、ポリ(3,4-ジメチルピロール)、ポリ(3,4-ジブチルピロール)、ポリ(3-ヒドロキシピロール)、ポリ(3-メチル-4-ヒドロキシピロール)、ポリ(3-メトキシピロール)、ポリ(3-エトキシピロール)、ポリ(3-オクトキシピロール)、ポリ(3-カルボキシルピロール)、ポリ(3-メチル-4-カルボキシルピロール)、ポリ(3-N-メチルピロール)、ポリチオフェン、ポリ(3-メチルチオフェン)、ポリ(3-ブチルチオフェン)、ポリ(3-オクチルチオフェン)、ポリ(3-デシルチオフェン)、ポリ(3-ドデシルチオフェン)、ポリ(3-メトキシチオフェン)、ポリ(3-エトキシチオフェン)、ポリ(3-オクトキシチオフェン)、ポリ(3-カルボキシルチオフェン)、ポリ(3-メチル-4-カルボキシルチオフェン)、ポリ(3,4-エチレンジオキシチオフェン)、ポリアニリン、ポリ(2-メチルアニリン)、ポリ(2-オクチルアニリン)、ポリ(2-イソブチルアニリン)、ポリ(3-イソブチルアニリン)、ポリ(2-アニリンスルホン酸)、ポリ(3-アニリンスルホン酸) 等が挙げられる。

20

#### 【0164】

上記導電性高分子を、単独で導電性組成物として透光性電極を形成してもよい。また、導電性組成物で形成される透光性電極の膜質、膜強度等の膜特性を調整するために、導電性高分子に有機樹脂を添加することもできる。

#### 【0165】

有機樹脂としては、導電性高分子と相溶または混合分散可能である熱硬化性樹脂、熱可塑性樹脂、又は光硬化性樹脂等を用いることができる。例えば、ポリエチレンテレフタレート、ポリブチレンテレフタレート、若しくはポリエチレンナフタレート等のポリエステル系樹脂、ポリイミド若しくはポリアミドイミド等のポリイミド系樹脂、ポリアミド 6、ポリアミド 6,6、ポリアミド 12、若しくはポリアミド 11 等のポリアミド樹脂、ポリフッ化ビニリデン、ポリフッ化ビニル、ポリテトラフルオロエチレン、エチレンテトラフルオロエチレンコポリマー、若しくはポリクロロトリフルオロエチレン等のフッ素樹脂、ポリビニルアルコール、ポリビニルエーテル、ポリビニルブチラール、ポリ酢酸ビニル、若しくはポリ塩化ビニル等のビニル樹脂、エポキシ樹脂、キシレン樹脂、アラミド樹脂、ポリウレタン系樹脂、ポリウレア系樹脂、メラミン樹脂、フェノール系樹脂、ポリエーテル、アクリル系樹脂、又はこれら樹脂の共重合体などが挙げられる。

40

#### 【0166】

さらに、導電性組成物の電気伝導度を調整するために、導電性組成物にアクセプタ性またはドナー性ドーパントをドーピングすることにより、共役導電性高分子の共役電子の酸化還元電位を変化させてもよい。

50

## 【0167】

アクセプタ性ドーパントとしては、ハロゲン化合物、ルイス酸、プロトン酸、有機シアノ化合物、有機金属化合物等を使用することができる。ハロゲン化合物としては、塩素、臭素、ヨウ素、塩化ヨウ素、臭化ヨウ素、フッ化ヨウ素等が挙げられる。ルイス酸としては五フッ化燐、五フッ化ヒ素、五フッ化アンチモン、三フッ化硼素、三塩化硼素、三臭化硼素等が挙げられる。プロトン酸としては、塩酸、硫酸、硝酸、リン酸、ホウフッ化水素酸、フッ化水素酸、過塩素酸等の無機酸と、有機カルボン酸、有機スルホン酸等の有機酸を挙げることができる。有機カルボン酸及び有機スルホン酸としては、カルボン酸化合物及びスルホン酸化合物を使用することができる。有機シアノ化合物としては、共役結合に二つ以上のシアノ基を含む化合物が使用できる。例えば、テトラシアノエチレン、テトラシアノエチレンオキサイド、テトラシアノベンゼン、テトラシアノキノジメタン、テトラシアノアザナフタレン等を挙げられる。

## 【0168】

ドナー性ドーパントとしては、アルカリ金属、アルカリ土類金属、又は4級アミン化合物等を挙げることができる。

## 【0169】

また、導電性組成物を、水または有機溶剤（アルコール系溶剤、ケトン系溶剤、エステル系溶剤、炭化水素系溶剤、又は芳香族系溶剤など）に溶解させて、湿式法により透光性電極となる薄膜を形成することができる。

## 【0170】

導電性組成物を溶解する溶媒としては、特に限定することではなく、上述した導電性高分子及び有機樹脂などの高分子樹脂化合物を溶解するものを用いればよい。例えば、水、メタノール、エタノール、プロピレンカーボネート、N-メチルピロリドン、ジメチルホルムアミド、ジメチルアセトアミド、シクロヘキサン、アセトン、メチルエチルケトン、メチルイソブチルケトン、又はトルエンなどの単独もしくは混合溶剤に溶解すればよい。

## 【0171】

導電性組成物を、上述のように溶媒に溶解した後、塗布法、コーティング法、液滴吐出法（インクジェット法ともいう）、印刷法等の湿式法を用いて絶縁層838上に形成することで、画素電極840を得ることができる。溶媒の乾燥は、熱処理を行ってもよいし、減圧することで行ってもよい。また、有機樹脂が熱硬化性の場合は熱処理を行えばよいし、光硬化性の場合は光照射処理を行えばよい。

## 【0172】

隔壁層842は、CVD法、スパッタリング法、塗布法等により基板全面に絶縁層を形成した後、選択的にエッティングして形成することができる。また、液滴吐出法、印刷法等を用いて、選択的に形成することもできる。その他、ポジ型感光性樹脂を用いて全面に絶縁層を形成した後、当該絶縁層を露光及び現像することにより、所望の形状とすることもできる。

## 【0173】

有機化合物を含む層844としては、少なくとも発光層を形成し、該発光層の他に正孔注入層、正孔輸送層、電子輸送層又は電子注入層を適宜形成してもよい。有機化合物を含む層は、インクジェット法などの塗布法や蒸着法により形成することができる。

## 【0174】

以上で、画素電極840及び対向電極846との間に、少なくとも発光層を有する有機化合物を含む層844が挟持された発光素子850を得ることができる。

## 【0175】

次に、支持基板120と対向させるように対向基板860を設ける（図12（B）参照）。対向基板860と対向電極846との間には、充填剤858を設けてもよいし、不活性ガスを充填させた構成としてもよい。なお、対向電極846を覆うように保護層を形成してもよい。

## 【0176】

10

20

30

40

50

以上の工程により、本形態に係る E L 表示装置が完成する。

【 0 1 7 7 】

S O I 基板を製造する際に、半導体層 1 3 0 の基となる半導体基板として単結晶半導体基板を用いることで、半導体層 1 3 0 を単結晶半導体とすることができます。よって、単結晶半導体でチャネル形成領域を形成することができるため、多結晶半導体をチャネル形成領域として利用する表示装置と比較して、画素ごとにおけるトランジスタ特性のバラツキを低減することができる。そのため、発光装置における表示むらを抑制することができる。

【 0 1 7 8 】

また、本発明は、S O I 基板の製造時間の短縮を可能とし、スループットを向上している。したがって、本発明に係るS O I 基板を適用することで、表示装置の生産性も向上することができる。

【 0 1 7 9 】

また、本形態に係る表示装置を構成するトランジスタの構成は特に限定されない。例えば、上記実施の形態 4 で示す構成のトランジスタを適用することもできる。

【 0 1 8 0 】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【 0 1 8 1 】

( 実施の形態 6 )

20

本発明に係るS O I 基板の製造方法を利用して、大型のガラス基板上に複数の半導体層を接合させたS O I 基板を製造することもできる。

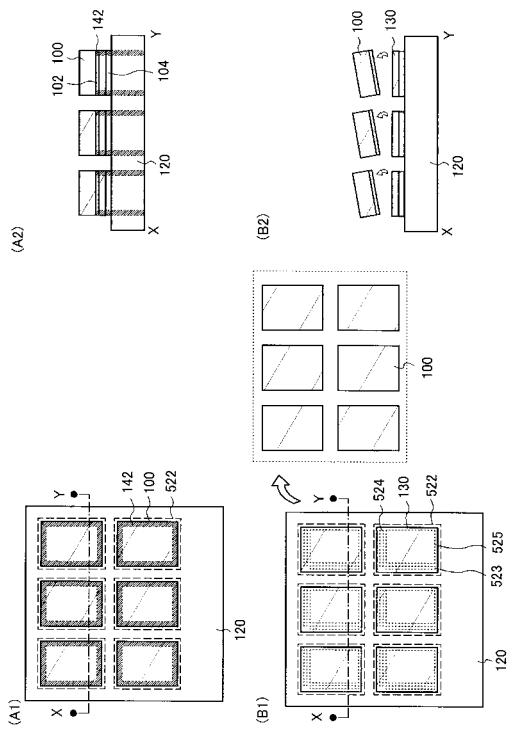

【 0 1 8 2 】

図 1 7 、図 1 8 は支持基板 1 2 0 として表示パネルを製造するマザーガラスと呼ばれる大型のガラス基板を適用し、該大型のガラス基板に複数の半導体層 1 3 0 を固着する例を示している。マザーガラス ( 支持基板 1 2 0 ) からは複数の表示パネルを切り出すものとし、表示パネル 5 2 2 の形成領域を点線で示している。なお、図 1 7 ( A 1 ) 、 ( B 1 ) 及び図 1 8 ( A 1 ) 、 ( B 1 ) は上面の模式図を示している。また、図 1 7 ( A 2 ) 、 ( B 2 ) 及び図 1 8 ( A 2 ) 、 ( B 2 ) は、図 1 7 ( A 1 ) 、 ( B 1 ) 及び図 1 8 ( A 1 ) 、 ( B 1 ) の鎖線 X Y の断面の模式図に相当する。

30

【 0 1 8 3 】

図 1 7 は、1枚のマザーガラス ( 支持基板 1 2 0 ) に対し、複数の半導体基板 1 0 0 を貼り合わせた後、該半導体基板 1 0 0 の分離を行って、複数の半導体層 1 3 0 を形成する一例を示している。

【 0 1 8 4 】

複数の半導体基板 1 0 0 を準備する。半導体基板 1 0 0 は市販の半導体基板を用いてもよいし、所望の大きさ及び形状 ( ここでは表示パネルのパネルサイズ ) に加工したものを使うてもよい。半導体基板 1 0 0 は所定の深さの領域に脆化層 1 0 2 が形成され、一表面上に絶縁層 1 0 4 が形成されている。また、支持基板 1 2 0 として、マザーガラスを準備する。

40

【 0 1 8 5 】

次に、支持基板 1 2 0 に複数の半導体基板 1 0 0 を貼り合わせる。複数の半導体基板 1 0 0 はそれぞれに絶縁層 1 0 4 が形成されており、該絶縁層 1 0 4 を間に挟んで、支持基板 1 2 0 と、複数の半導体基板 1 0 0 と、を貼り合わせる。そして、支持基板 1 2 0 側からレーザビームを選択的に照射し、照射領域 1 4 2 における脆化層 1 0 2 の脆化を進行させる ( 図 1 7 ( A 1 ) 、 ( A 2 ) 参照 ) 。レーザビームは、支持基板 1 2 0 及び絶縁層 1 0 4 は透過し、半導体基板 1 0 0 に吸収される波長を有するものとする。

【 0 1 8 6 】

次に、物理的手段により、脆化層 1 0 2 を境として半導体基板 1 0 0 を分離させる。半導体基板 1 0 0 は、絶縁層 1 0 4 を間に介して支持基板 1 2 0 に接合されており、脆化層

50

102を境として半導体基板100の一部を分離させた結果、支持基板120上に半導体基板100と略同じ結晶性の半導体層130が残存する。複数の半導体基板100はそれに脆化層102が形成されており、それぞれの半導体基板100について脆化層102を境として半導体基板100の分離を行うことにより、支持基板120上に複数の半導体層130が固着されたS0I基板を得る(図17(B1)、(B2)参照)。

【0187】

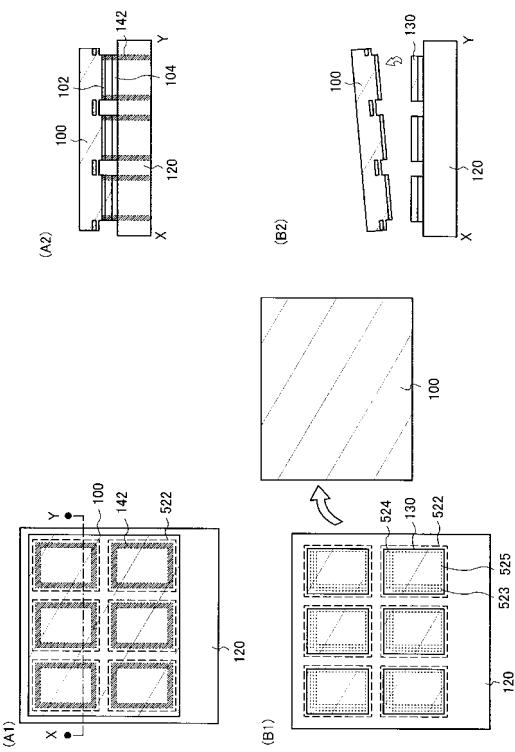

図18は、支持基板120上に、1枚の半導体基板100から複数の半導体層130を形成する一例を示している。

【0188】

まず、半導体基板100を準備し、該半導体基板100の一表面上に絶縁層104を形成する。そして、半導体基板100を選択的にエッチングして溝を形成する。本明細書では、半導体基板100を選択的にエッチングして溝を形成する加工を「溝加工」ともいう。

【0189】

溝加工により、半導体基板100には凹凸が形成される。凹部は溝が形成された領域に該当し、凸部はエッチングされずに残存した領域に該当する。半導体基板100に形成される凸部は、後に支持基板120の転置される半導体層130を形成する。したがって、表示パネル522の形成領域に合わせて凸部を形成するのが好ましい。すなわち表示パネル522の形成領域を考慮して半導体基板100に溝加工を行うことが好ましい。

【0190】

また、半導体基板100の溝加工の深さ(エッチングする深さ)は、支持基板120に転置する半導体層の膜厚を考慮して決定する。支持基板120に転置する半導体層の膜厚は、脆化層102を形成する深さで制御することが可能である。本形態では、脆化層102を形成する深さよりも半導体基板100の溝加工を深くすることが好ましい。このようにすることで、支持基板120に半導体層を転置する際、半導体基板100の凸部のみ、容易に転置することが可能となる。

【0191】

半導体基板100の溝加工された面側からイオンを照射して、半導体基板100の所定の深さの領域に脆化層102を形成する。半導体基板100は予め溝加工されており、凹部と凸部で段違いになるように脆化層102が形成される。なお、半導体基板100の凹部及び凸部で、半導体基板100の表面からの脆化層102の深さは同程度である。

【0192】

次に、支持基板120に半導体基板100を貼り合わせる。支持基板120と、半導体基板100と、は、絶縁層104を間に挟んで貼り合わせる。半導体基板100は溝加工されており、凸部が絶縁層104を間に挟んで支持基板120と接合することとなる。そして、支持基板120側からレーザビームを選択的に照射し、照射領域142における脆化層102の脆化を進行させる(図18(A1)、(A2)参照)。レーザビームは、支持基板120及び絶縁層104は透過し、半導体基板100に吸収される波長を有するものとする。

【0193】

次に、物理的手段により、脆化層102を境として半導体基板100を分離させる。半導体基板100の凸部は、絶縁層104を間に介して支持基板120に接合されている。したがって、支持基板120上に半導体基板100の凸部のみ半導体層130として残存させることができ、支持基板120上に複数の半導体層130が固着されたS0I基板を得ることができる(図18(B1)、(B2)参照)。

【0194】

図18に示すように半導体基板100に溝加工を行うことで、一度の分離工程で複数の半導体層を得ることができる。よって、製造時間が短縮でき、生産性が良好である。

【0195】

なお、半導体基板100に脆化層を形成した後、溝加工を行ってもよい。また、溝加工

10

20

30

40

50

を行った後に接合層として機能する絶縁層を形成してもよい。その場合、支持基板 120 に転置される半導体層の側面に絶縁層が形成された構成となる。

【0196】

図 17、図 18において、得られた半導体層 130 は表示パネルを形成することができる。表示パネル 522 の形成領域には、走査線駆動回路領域 523、信号線駆動回路領域 524、画素形成領域 525 が形成され、これらの領域が含まれるように半導体層 130 を支持基板 120 に接合する。

【0197】

半導体基板 100 の分離において、物理的手段による分離の前に、レーザビームの照射により部分的に脆化層 102 は脆化が進行している。したがって、半導体基板 100 に物理的な力を加えることで、脆化層 102 の脆化が進行した部分が始点（きっかけ）となり容易に分離を行うことができる。また、短時間での分離が可能である。よって、製造時間の短縮が可能であり、スループットを向上することができる。また、表示パネル 522 の形成領域に合わせて半導体層 130 を接合することで、面取り数が増大し、生産性を飛躍的に向上させることができる。

【0198】

なお、本形態に係る SOI 基板の製造方法は、支持基板上に固着される半導体層の基となる半導体基板の分離を行う前に、レーザビームを選択的に照射して部分的に脆化層の脆化を進行させることを特徴としている。したがって、製造する SOI 基板の構成は特に限定されない。

【0199】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

【0200】

(実施の形態 7)

本実施の形態では、本発明に係る SOI 基板を適用した半導体装置の例を示す。

【0201】

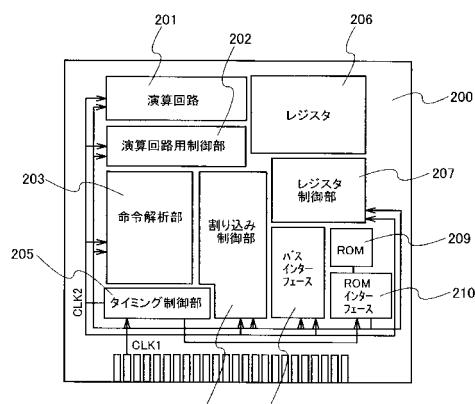

図 15 は半導体装置の一例として、マイクロプロセッサ 200 の一例を示す。このマイクロプロセッサ 200 は、上記実施の形態に係る SOI 基板を適用して製造されるものである。このマイクロプロセッサ 200 は、演算回路 201 (A r i t h m e t i c l o g i c u n i t ; A L U ともいう。)、演算回路制御部 202 (A L U C o n t r o l l e r )、命令解析部 203 (I n s t r u c t i o n D e c o d e r )、割り込み制御部 204 (I n t e r r u p t C o n t r o l l e r )、タイミング制御部 205 (T i m i n g C o n t r o l l e r )、レジスタ 206 (R e g i s t e r )、レジスタ制御部 207 (R e g i s t e r C o n t r o l l e r )、バスインターフェース 208 (B u s I / F )、読み出し専用メモリ 209、及びメモリインターフェース 210 (R O M I / F ) を有している。

【0202】

バスインターフェース 208 を介してマイクロプロセッサ 200 に入力された命令は命令解析部 203 に入力され、デコードされた後に演算回路制御部 202、割り込み制御部 204、レジスタ制御部 207、タイミング制御部 205 に入力される。演算回路制御部 202、割り込み制御部 204、レジスタ制御部 207、タイミング制御部 205 は、デコードされた命令に基づき各種制御を行う。具体的に演算回路制御部 202 は、演算回路 201 の動作を制御するための信号を生成する。また、割り込み制御部 204 は、マイクロプロセッサ 200 のプログラム実行中に、外部の入出力装置や周辺回路からの割り込み要求を、その優先度やマスク状態から判断して処理する。レジスタ制御部 207 は、レジスタ 206 のアドレスを生成し、マイクロプロセッサ 200 の状態に応じてレジスタ 206 の読み出しや書き込みを行う。タイミング制御部 205 は、演算回路 201、演算回路制御部 202、命令解析部 203、割り込み制御部 204、レジスタ制御部 207 の動作のタイミングを制御する信号を生成する。例えばタイミング制御部 205 は、基準クロック

10

20

30

40

50

ク信号 C L K 1 を元に、内部クロック信号 C L K 2 を生成する内部クロック生成部を備えており、クロック信号 C L K 2 を上記各種回路に供給する。なお、図 15 に示すマイクロプロセッサ 200 は、その構成を簡略化して示した一例にすぎず、実際にはその用途によって多種多様な構成を備えることができる。

#### 【 0 2 0 3 】

このようなマイクロプロセッサ 200 は、上記実施の形態に係る S O I 基板を適用することができる。本発明に係る S O I 基板は、その製造においてスループットの向上が図られており、該 S O I 基板を用いることでマイクロプロセッサ等の半導体装置を生産性良く製造することが可能となる。また、 S O I 基板を製造する際に単結晶半導体基板を用いることで単結晶半導体層を得ることができ、該単結晶半導体層によって集積回路を形成することが可能である。よって、高性能化及び処理速度の高速化などを実現することもできる。

10

#### 【 0 2 0 4 】

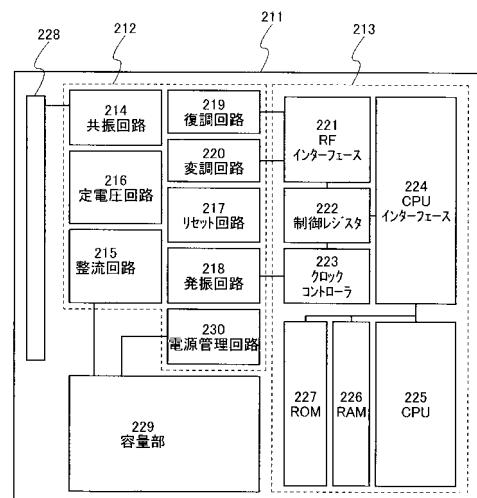

次に、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一例について図 16 を参照して説明する。図 16 は無線通信により外部装置と信号の送受信を行って動作するコンピュータ（以下、「 R F C P U 」という）の一例を示す。 R F C P U 211 は、アナログ回路部 212 とデジタル回路部 213 を有している。アナログ回路部 212 として、共振容量を有する共振回路 214、整流回路 215、定電圧回路 216、リセット回路 217、発振回路 218、復調回路 219 と、変調回路 220 を有している。デジタル回路部 213 は、 R F インターフェース 221、制御レジスタ 222、クロックコントローラ 223、インターフェース 224、中央処理ユニット 225、ランダムアクセスメモリ 226、読み出し専用メモリ 227 を有している。

20

#### 【 0 2 0 5 】

このような構成の R F C P U 211 の動作は概略以下の通りである。アンテナ 228 が受信した信号は共振回路 214 により誘導起電力を生じる。誘導起電力は整流回路 215 を経て容量部 229 に充電される。この容量部 229 はセラミックコンデンサーや電気二重層コンデンサーなどのキャパシタで形成されていることが好ましい。容量部 229 は R F C P U 211 と一体形成されている必要はなく、別部品として R F C P U 211 を構成する絶縁表面を有する基板に取り付けられていれば良い。

#### 【 0 2 0 6 】

30

リセット回路 217 は、デジタル回路部 213 をリセットし初期化する信号を生成する。例えば、電源電圧の上昇に遅延して立ち上がる信号をリセット信号として生成する。発振回路 218 は定電圧回路 216 により生成される制御信号に応じて、クロック信号の周波数とデューティー比を変更する。ローパスフィルタで形成される復調回路 219 は、例えば振幅変調（ A S K ）方式の受信信号の振幅の変動を二値化する。変調回路 220 は、送信データを振幅変調（ A S K ）方式の送信信号の振幅を変動させて送信する。変調回路 220 は、共振回路 214 の共振点を変化させることで通信信号の振幅を変化させている。クロックコントローラ 223 は、電源電圧又は中央処理ユニット 225 における消費電流に応じてクロック信号の周波数とデューティー比を変更するための制御信号を生成している。電源電圧の監視は電源管理回路 230 が行っている。

40

#### 【 0 2 0 7 】

アンテナ 228 から R F C P U 211 に入力された信号は復調回路 219 で復調された後、 R F インターフェース 221 で制御コマンドやデータなどに分解される。制御コマンドは制御レジスタ 222 に格納される。制御コマンドには、読み出し専用メモリ 227 に記憶されているデータの読み出し、ランダムアクセスメモリ 226 へのデータの書き込み、中央処理ユニット 225 への演算命令などが含まれている。中央処理ユニット 225 は、インターフェース 224 を介して読み出し専用メモリ 227、ランダムアクセスメモリ 226、制御レジスタ 222 にアクセスする。インターフェース 224 は、中央処理ユニット 225 が要求するアドレスより、読み出し専用メモリ 227、ランダムアクセスメモリ 226、制御レジスタ 222 のいずれかに対するアクセス信号を生成する機能を有して

50

いる。

【0208】

中央処理ユニット225の演算方式は、読み出し専用メモリ227にOS(オペレーティングシステム)を記憶させておき、起動とともにプログラムを読み出し実行する方式を採用することができる。また、専用回路で演算回路を構成して、演算処理をハードウェア的に処理する方式を採用することもできる。ハードウェアとソフトウェアを併用する方式では、専用の演算回路で一部の処理を行い、残りの演算はプログラムを使って中央処理ユニット225が実行する方式を適用することができる。

【0209】

このようなRFCPU211は、上記実施の形態に係るSOI基板を適用することができる。本発明に係るSOI基板はその製造においてスループットの向上が図られており、該SOI基板を用いることでRFCPU等の半導体装置も生産性良く製造することができる。また、SOI基板を製造する際に単結晶半導体基板を用いることで単結晶半導体層を得ることができ、該単結晶半導体層によって集積回路を作製することが可能である。よって、高性能化、処理速度の高速化などの実現も可能である。なお、図16ではRFCPUの形態について示しているが、通信機能、演算処理機能、メモリ機能を備えたものであれば、ICタグのようなものであっても良い。

【0210】

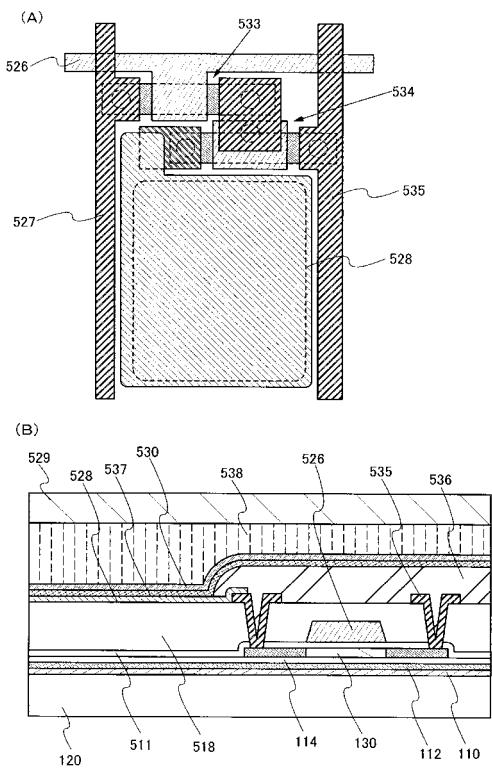

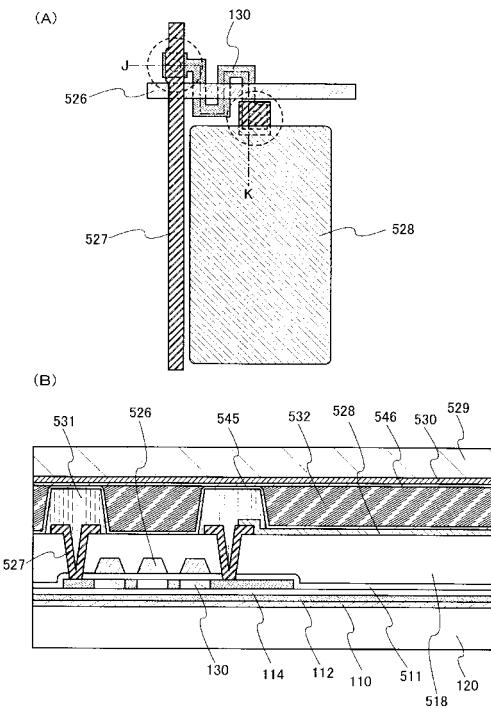

図21は本発明に係るSOI基板を適用し、該SOI基板の半導体層を用いて画素部のトランジスタを形成する液晶表示装置の画素の一例を示す。図21(A)は画素の平面図を示し、半導体層に走査線526が交差し、信号線527、画素電極528が接続する画素を示す。図21(B)は、図21(A)に示す鎖線J-Kで切断した断面図に相当する。

【0211】

図21(B)において、支持基板120上に順に積層された接合層110、窒素含有絶縁層112、及びシリコン酸化層114を間に介して半導体層130が積層された構造を有する領域があり、本形態に係る画素トランジスタは前記領域を含んで構成されている。本形態では、半導体層130は単結晶半導体層とする。つまり、本形態に係るSOI基板を製造する際、半導体層130の基となる半導体基板として単結晶半導体基板を用いるものとする。なお、ここでは図3(A)に示す構成のSOI基板を適用する例を示すが、本形態は特に限定されず、本明細書で示すその他の構成のSOI基板も適用できる。

【0212】

層間絶縁層518上に画素電極528が設けられている。また、層間絶縁層518には、半導体層130と信号線527を接続するコンタクトホールが形成されている。層間絶縁層518に形成されたコンタクトホールによる段差を埋めるように、信号線527上に柱状スペーサ531が設けられている。対向基板529には対向電極530が形成され、柱状スペーサ531によって形成される空隙に配向膜545及び配向膜546によって挟持された液晶層532が設けられている。なお、ここでは図示しないが、必要に応じて支持基板120又は対向基板529の外側に偏光板を設ける。

【0213】

層間絶縁層518は、単層膜又は積層膜で形成することができる。なお、層間絶縁層518は、下層に形成されたトランジスタ等の構造体による凹凸を平滑化して、平坦な表面を形成できる平坦化膜を形成することができる。例えば、スピンドルコート法などの塗布法により、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル若しくはエポキシ等の有機材料、シロキサン樹脂等のシロキサン材料、又はオキサゾール樹脂などを用いて形成することができる。層間絶縁層518として、BPSG層を形成してもよい。また、CVD法やスパッタリング法により、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、又は窒化酸化シリコン層等の絶縁層を形成することもできる。また、有機材料を用いて形成した絶縁層と、無機材料を用いて形成した絶縁層とを積層させてもよい。

10

20

30

40

50

## 【0214】

画素電極528は、反射型液晶表示装置とする場合は、反射電極を形成すればよい。具体的には、タンタル、タンゲステン、チタン、モリブデン、アルミニウム、クロム、銀等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料等の反射性を有する導電材料を用いて形成することができる。なお、画素電極528とは別に反射膜を形成する場合、若しくは透過型液晶表示装置とする場合には、画素電極は透光性電極とすればよく、透光性を有する導電材料を用いて形成すればよい。透光性を有する導電性材料としては、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、又はガリウムを添加した酸化亜鉛(GZO)等を用いることができる。

## 【0215】

10

また、画素電極528は、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性組成物を用いて形成した画素電極は、薄膜におけるシート抵抗が10000 /以下、波長550nmにおける透光率が70%以上であることが好ましい。また、導電性組成物に含まれる導電性高分子の抵抗率が0.1 · cm以下であることが好ましい。なお、導電性高分子の具体的な説明は、上記実施の形態5の画素電極840又は対向電極846に適用できる導電性高分子に準ずる。

## 【0216】

柱状スペーサ531は、エポキシ、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等の有機材料、又は酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の無機材料を用いて基板全面に絶縁層を形成した後、当該絶縁層を所望の形状にエッチング加工して得ることができる。

20

## 【0217】

配向膜545及び配向膜546は、利用する液晶の動作モードに対応して材料を選択すればよく、液晶を一定方向に配列させることができ可能な膜を形成する。例えばポリイミド、ポリアミド等の材料を用いて形成し、配向処理を行うことで配向膜として機能させることができる。配向処理としては、ラビングや、紫外線等の光照射などを行えばよい。配向膜545及び配向膜546の形成方法は特に限定されないが、各種印刷法や液滴吐出法を用いると、選択的に形成することができる。

## 【0218】

液晶層532は、所望の液晶材料を用いて形成する。例えば、液晶層532は、シール材で形成された枠状のシールパターン内に液晶材料を滴下して形成することができる。液晶材料の滴下は、ディスペンサ法や液滴吐出法を用いて行えばよい。なお、液晶材料は予め減圧下で脱気しておくか、滴下後に減圧下で脱気することが好ましい。また、液晶材料の滴下の際に不純物等混入しないように、不活性雰囲気下で行うことが好ましい。また、液晶材料を滴下して液晶層532を形成した後、支持基板120及び対向基板529を貼り合わせるまでは、液晶層532に気泡等入らないように減圧下で行うことが好ましい。また、液晶層532は、支持基板120と対向基板529を貼り合わせた後、シール材で形成された枠状パターン内に、毛細管現象を利用して液晶材料を注入して形成することができる。この場合、あらかじめシール材等に液晶の注入口となる部分を形成しておく。なお、液晶材料は減圧下で注入を行うことが好ましい。

30

## 【0219】

40

対向基板529は、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラス等の各種ガラス基板、石英基板、結晶化ガラス基板、サファイヤ基板等を用いることができる。なお、対向基板529には、支持基板120と貼り合わせる前に対向電極530、配向膜546を形成しておけばよい。また、対向基板529にカラーフィルターやブラックマトリクス等を設ける構成としてもよい。

## 【0220】

図19(A)は本発明に係るSOI基板を適用し、該SOI基板の半導体層を用いて画素部のトランジスタを形成するEL表示装置の一例を示す。なお、上記実施の形態5で示した表示装置とは、トランジスタの構成が異なっている。図19(A)は画素の平面図を

50

示し、信号線 527 に接続する選択トランジスタ 533 と、電流供給線 535 に接続する表示制御トランジスタ 534 を有している。この表示装置は有機化合物を含む層を発光層として具備する発光素子が各画素に設けられる構成となっている。画素電極 528 は表示制御トランジスタ 534 に接続されている。図 19 (B) はこのような画素の要部を示す断面図である。

【0221】

図 19 (B) において、支持基板 120 上に順に積層された接合層 110、窒素含有絶縁層 112、及びシリコン酸化層 114 を間に介して半導体層 130、ゲート絶縁層 511 が積層された構造を有する領域があり、表示制御トランジスタ 534 はそのような領域を含んで構成されている。本形態では、半導体層 130 は単結晶半導体層とする。つまり、本形態に係る SOI 基板を製造する際、半導体層 130 の基となる半導体基板として単結晶半導体基板を用いるものとする。接合層 110、窒素含有絶縁層 112、シリコン酸化層 114、半導体層 130、層間絶縁層 518 などの構成は図 21 (B) と同様である。画素電極 528 は周辺部が絶縁性の隔壁層 536 で囲まれている。画素電極 528 上には少なくとも発光層を有する有機化合物を含む層 537 が形成されている。有機化合物を含む層 537 上には対向電極 530 が形成されている。画素部は封止樹脂 538 が充填され、補強板として対向基板 529 が設けられている。

【0222】

本形態の EL 表示装置はこのような画素をマトリクス状に配列させて表示画面を構成する。この場合、画素のトランジスタのチャネル部を単結晶半導体である半導体層 130 で形成すると、各トランジスタ間で特性バラツキが少なく、画素毎の発光輝度に斑が出ないという利点がある。従って、発光素子の明るさを電流で制御して駆動することが容易となり、トランジスタ特性のバラツキを補正する補正回路も不要となるので、駆動回路の負担を低減することができる。さらに支持基板 120 として透光性の基板を選択するため、支持基板 120 側から光を射出する、ボトムエミッション型の EL 表示装置を構成することができる。

【0223】

このように、液晶表示装置や EL 表示装置にも、本発明に係る SOI 基板を利用することができる。本発明に係る SOI 基板は、その製造においてスループットの向上が図られている。そのため、本発明に係る SOI 基板を用いることで、液晶表示装置や EL 表示装置も生産性良く製造することが可能となる。

【0224】

また、SOI 基板を製造する際に単結晶半導体基板を用いることで、単結晶半導体で半導体層を得ることができる。したがって、単結晶半導体層を用いてトランジスタを形成することができる。単結晶半導体層で形成されるトランジスタは、アモルファスシリコントランジスタよりも電流駆動能力など全ての動作特性が優れているので、トランジスタのサイズを小型化することができる。それにより、表示パネルにおける画素部の開口率を向上させることができる。また、マザーガラスと単結晶半導体層との間にはブロッキング効果の高い絶縁層を設けることで、信頼性が高い表示装置を提供することができる。なお、図 15 及び図 16 で説明したようなマイクロプロセッサも形成することができる。表示装置内にコンピュータの機能を搭載することもできる。また非接触でデータの入出力を可能としたディスプレイを作製することもできる。

【0225】

また、本発明に係る SOI 基板を適用して様々な電気器具を構成することができる。電気器具としては、ビデオカメラ、デジタルカメラ、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等）、記録媒体を備えた画像再生装置（具体的には DVD (d i g i t a l v e r s a t i l e d i s c) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが含まれる。

10

20

30

40

50

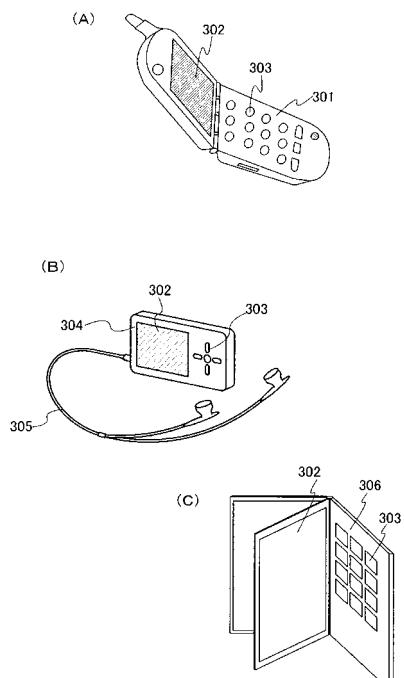

## 【0226】

図20(A)は携帯電話機の一例を示している。本形態に示す携帯電話機301は、表示部302、操作スイッチ303などを含んで構成されている。表示部302においては、図21で説明した液晶表示装置又は図12或いは図19で説明したEL表示装置を適用することができる。本形態に係る表示装置を適用することで、携帯電話機も生産性良く製造することができる。また、S0I基板を適用することで、表示装置を構成するトランジスタは単結晶半導体でチャネル形成領域を形成することが可能である。よって、画質の優れた表示部を構成することができる。さらに携帯電話機301に含まれるマイクロプロセッサやメモリにも本発明に係る半導体装置を適用することができる。

## 【0227】

また、図20(B)は、デジタルプレーヤー304を示しており、オーディオ装置の1つの代表例である。図20(B)に示すデジタルプレーヤー304は、表示部302、操作スイッチ303、イヤホン305などを含んでいる。イヤホン305の代わりにヘッドホンや無線式イヤホンを用いることができる。デジタルプレーヤー304は音楽情報を記憶するメモリ部や、デジタルプレーヤー304を機能させるマイクロプロセッサに本発明に係る半導体装置を適用することができる。本構成のデジタルプレーヤー304は小型軽量化が可能であるが、表示部302においては、図21で説明した液晶表示装置又は図12或いは図19で説明したEL表示装置を適用することで、画面サイズが0.3インチから2インチ程度の場合であっても高精細な画像若しくは文字情報を表示することができる。

## 【0228】

また、図20(C)は、電子ブック306を示している。この電子ブック306は、表示部302、操作スイッチ303を含んでいる。またモデムが内蔵されていてもよいし、無線で情報を送受信できる構成としてもよい。電子ブック306は情報を記憶するメモリ部や、電子ブック306を機能させるマイクロプロセッサに本発明に係る半導体装置を適用することができる。メモリ部は、記録容量が20ギガバイト(GB)乃至200ギガバイトのNOR型不揮発性メモリを用い、映像や音声(音楽)を記録、再生することができる。表示部302においては、図21で説明した液晶表示装置又は図12或いは図19で説明したEL表示装置を適用することで、高画質の表示を行うことができる。

## 【0229】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

## 【実施例1】

## 【0230】

本実施例では、脆化層形成におけるイオンの照射方法について考察する。

## 【0231】

上述の実施の形態では、脆化層形成において、水素(H)に由来するイオン(以下「水素イオン種」と呼ぶ)を半導体基板、代表的には単結晶半導体基板に対して照射している。例えば、原料ガスとして、水素ガス又は水素を組成に含むガスを用い、水素プラズマを発生させ、該水素プラズマ中の水素イオン種を単結晶半導体基板に対して照射している。

## 【0232】

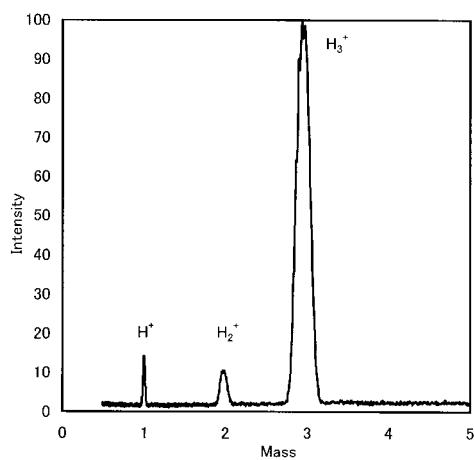

## (水素プラズマ中のイオン)

上記のような水素プラズマ中には、 $H^+$ イオン、 $H_2^+$ イオン、 $H_3^+$ イオンといった水素イオン種が存在する。ここで、各水素イオン種の反応過程(生成過程、消滅過程)について、以下に反応式を挙げる。

10

20

30

40

50

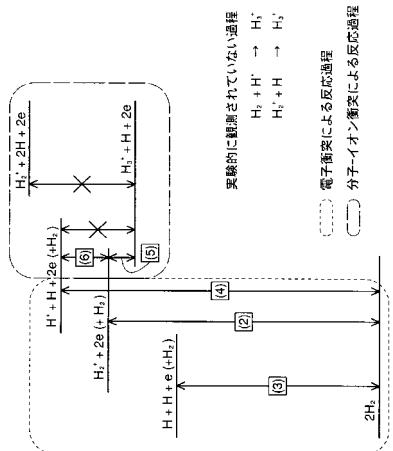

## 【 0 2 3 3 】

図22に、上記の反応の一部を模式的に表したエネルギーダイアグラムを示す。なお、図22に示すエネルギーダイアグラムは模式図に過ぎず、反応に係るエネルギーの関係を厳密に規定するものではない点に留意されたい。

## 【 0 2 3 4 】

(  $H_3^+$  イオンの生成過程 )

10

上記のように、 $H_3^+$  イオンは、主として反応式(5)により表される反応過程により生成される。一方で、反応式(5)と競合する反応として、反応式(6)により表される反応過程が存在する。 $H_3^+$  イオンが増加するためには、少なくとも、反応式(5)の反応が、反応式(6)の反応より多く起こる必要がある(なお、 $H_3^+$  イオンが減少する反応としては他にも(7)、(8)、(9)が存在するため、(5)の反応が(6)の反応より多いからといって、必ずしも $H_3^+$  イオンが増加するとは限らない。)。反対に、反応式(5)の反応が、反応式(6)の反応より少ない場合には、プラズマ中における $H_3^+$  イオンの割合は減少する。

## 【 0 2 3 5 】

上記反応式における右辺(最右辺)の生成物の増加量は、反応式の左辺(最左辺)で示す原料の密度や、その反応に係る速度係数などに依存している。ここで、 $H_2^+$  イオンの運動エネルギーが約11eVより小さい場合には(5)の反応が主要となり(すなわち、反応式(5)に係る速度係数が、反応式(6)に係る速度係数と比較して十分に大きくなり)、 $H_2^+$  イオンの運動エネルギーが約11eVより大きい場合には(6)の反応が主要となることが実験的に確認されている。

20

## 【 0 2 3 6 】

荷電粒子は電界から力を受けて運動エネルギーを得る。該運動エネルギーは、電界によるポテンシャルエネルギーの減少量に対応している。例えば、ある荷電粒子が他の粒子と衝突するまでの間に得る運動エネルギーは、その間に通過した電位差分のポテンシャルエネルギーに等しい。つまり、電界中において、他の粒子と衝突することなく長い距離を移動できる状況では、そうではない状況と比較して、荷電粒子の運動エネルギー(の平均)は大きくなる傾向にある。このような、荷電粒子に係る運動エネルギーの増大傾向は、粒子の平均自由行程が大きい状況、すなわち、圧力が低い状況で生じ得る。

30

## 【 0 2 3 7 】

また、平均自由行程が小さくとも、その間に大きな運動エネルギーを得ることができる状況であれば、荷電粒子の運動エネルギーは大きくなる。すなわち、平均自由行程が小さくとも、電位差が大きい状況であれば、荷電粒子の持つ運動エネルギーは大きくなると言える。

## 【 0 2 3 8 】

これを $H_2^+$  イオンに適用してみる。プラズマの生成に係るチャンバー内のように電界の存在を前提とすれば、該チャンバー内の圧力が低い状況では $H_2^+$  イオンの運動エネルギーは大きくなり、該チャンバー内の圧力が高い状況では $H_2^+$  イオンの運動エネルギーは小さくなる。つまり、チャンバー内の圧力が低い状況では(6)の反応が主要となるため、 $H_3^+$  イオンは減少する傾向となり、チャンバー内の圧力が高い状況では(5)の反応が主要となるため、 $H_3^+$  イオンは増加する傾向となる。また、プラズマ生成領域における電界が強い状況、すなわち、ある二点間の電位差が大きい状況では $H_2^+$  イオンの運動エネルギーは大きくなり、反対の状況では、 $H_2^+$  イオンの運動エネルギーは小さくなる。つまり、電界が強い状況では(6)の反応が主要となるため $H_3^+$  イオンは減少する傾向となり、電界が弱い状況では(5)の反応が主要となるため、 $H_3^+$  イオンは増加する傾向となる。

40

50

## 【0239】

(イオン源による差異)

ここで、水素イオン種の割合（特に  $H_3^+$  イオンの割合）が異なる例を示す。図23は、100%水素ガス（イオン源の圧力： $4.7 \times 10^{-2}$  Pa）から生成されるイオンの質量分析結果を示すグラフである。なお、上記質量分析は、イオン源から引き出されたイオンを測定することにより行った。横軸はイオンの質量である。スペクトル中、質量1、質量2、質量3のピークは、それぞれ、 $H^+$  イオン、 $H_2^+$  イオン、 $H_3^+$  イオンに対応する。縦軸は、スペクトルの強度であり、イオンの数に対応する。図23では、質量が異なるイオンの数量を、質量3のイオンを100とした場合の相対比で表している。図23から、上記イオン源により生成されるイオンの割合は、 $H^+$  イオン： $H_2^+$  イオン： $H_3^+$  イオン = 1 : 1 : 8 程度となることが分かる。なお、このような割合のイオンは、プラズマを生成するプラズマソース部（イオン源）と、当該プラズマからイオンビームを引き出すための引出電極などから構成されるイオンドーピング装置によっても得ることが出来る。

## 【0240】

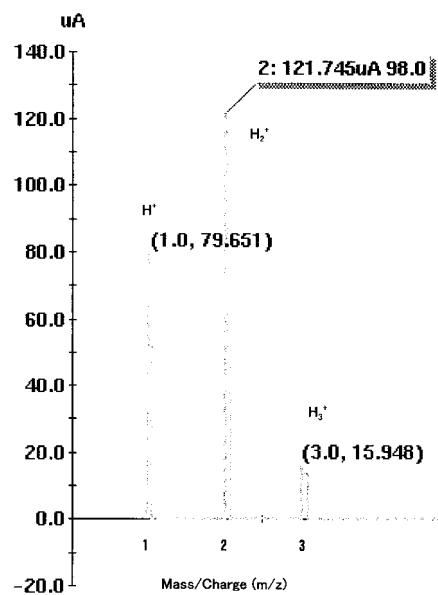

図24は、図23とは異なるイオン源を用いた場合であって、イオン源の圧力がおおよそ  $3 \times 10^{-3}$  Pa の時に、 $PH_3$  から生成したイオンの質量分析結果を示すグラフである。上記質量分析結果は、水素イオン種に着目したものである。また、質量分析は、イオン源から引き出されたイオンを測定することにより行った。図23と同様、横軸はイオンの質量を示し、質量1、質量2、質量3のピークは、それぞれ  $H^+$  イオン、 $H_2^+$  イオン、 $H_3^+$  イオンに対応する。縦軸はイオンの数量に対応するスペクトルの強度である。図24から、プラズマ中のイオンの割合は  $H^+$  イオン： $H_2^+$  イオン： $H_3^+$  イオン = 37 : 56 : 7 程度であることが分かる。なお、図24は原料ガスが  $PH_3$  の場合のデータであるが、原料ガスとして 100% 水素ガスを用いたときも、水素イオン種の割合は同程度になる。

## 【0241】

図24のデータを得たイオン源の場合には、 $H^+$  イオン、 $H_2^+$  イオン及び  $H_3^+$  イオンのうち、 $H_3^+$  イオンが 7% 程度しか生成されていない。他方、図23のデータを得たイオン源の場合には、 $H_3^+$  イオンの割合を 50% 以上（上記の条件では 80% 程度）とすることが可能である。これは、上記考察において明らかになったチャンバー内の圧力及び電界に起因するものと考えられる。

## 【0242】

( $H_3^+$  イオンの照射メカニズム)

図23のような複数の種類の水素イオンを含むプラズマを生成し、生成された複数の種類のイオンを質量分離しないで単結晶半導体基板に照射する場合、単結晶半導体基板の表面には、 $H^+$  イオン、 $H_2^+$  イオン、 $H_3^+$  イオンの各イオンが照射される。イオンの照射からイオン導入領域形成にかけてのメカニズムを再現するために、以下の5種類のモデルを考える。

1. 照射される水素イオン種が  $H^+$  イオンで、照射後も  $H^+$  イオン（或いは  $H$ ）である場合。

2. 照射される水素イオン種が  $H_2^+$  イオンで、照射後も  $H_2^+$  イオン（或いは  $H_2$ ）のままである場合。

3. 照射される水素イオン種が  $H_2^+$  イオンで、照射後に 2 個の  $H$ （或いは  $H^+$  イオン）に分裂する場合。

4. 照射される水素イオン種が  $H_3^+$  イオンで、照射後も  $H_3^+$  イオン（或いは  $H_3$ ）のままである場合。

5. 照射される水素イオン種が  $H_3^+$  イオンで、照射後に 3 個の  $H$ （或いは  $H^+$  イオン）に分裂する場合。

## 【0243】

（シミュレーション結果と実測値との比較）

10

20

30

40

50

上記のモデルを基にして、水素イオン種をシリコン基板に照射する場合のシミュレーションを行った。シミュレーション用のソフトウェアとしては、SRIM (the Stooping and Range of Ions in Matter) を用いた。SRIMは、モンテカルロ法によるイオン導入過程のシミュレーションソフトウェアであり、TRIM (the Transport of Ions in Matter) の改良版である。なお、計算の関係上、モデル2では $H_2^+$ イオンを質量2倍の $H^+$ イオンに置き換えて計算した。また、モデル4では $H_3^+$ イオンを質量3倍の $H^+$ イオンに置き換えて計算した。さらに、モデル3では $H_2^+$ イオンを運動エネルギー1/2の $H^+$ イオンに置き換え、モデル5では $H_3^+$ イオンを運動エネルギー1/3の $H^+$ イオンに置き換えて計算を行った。

10

#### 【0244】

なお、SRIMは非晶質構造を対象とするソフトウェアではあるが、高エネルギー、高ドーズの条件で水素イオン種を照射する場合には、SRIMを適用可能とすることができる。これは、水素イオン種とSi原子の衝突により、シリコン基板の結晶構造が非単結晶構造に変化するためである。

#### 【0245】

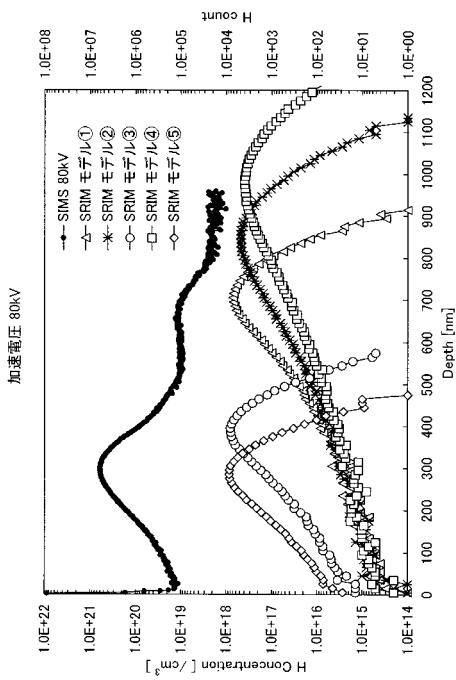

図25に、モデル1乃至モデル5を用いて水素イオン種を照射した場合 (H換算で10万個照射時) の計算結果を示す。また、図25中に、図23の水素イオン種を照射したシリコン基板中の水素濃度 (SIMS (Secondary Ion Mass Spectroscopy) のデータ) をあわせて示す。モデル1乃至モデル5を用いて行った計算の結果については、縦軸を水素原子の数で表しており (右軸)、SIMSデータについては、縦軸を水素原子の密度で表している (左軸)。横軸はシリコン基板表面からの深さである。実測値であるSIMSデータと、計算結果とを比較した場合、モデル2及びモデル4は明らかにSIMSデータのピークから外れており、また、SIMSデータ中にはモデル3に対応するピークも見られない。このことから、モデル2乃至モデル4の寄与は、相対的に小さいことが分かる。イオンの運動エネルギーがkeVであるのに対して、H-Hの結合エネルギーは数eV程度に過ぎないことを考えれば、モデル2及びモデル4の寄与が小さいのは、Si元素との衝突により、大部分の $H_2^+$ イオンや $H_3^+$ イオンが、 $H^+$ イオンやHに分離しているためと思われる。

20

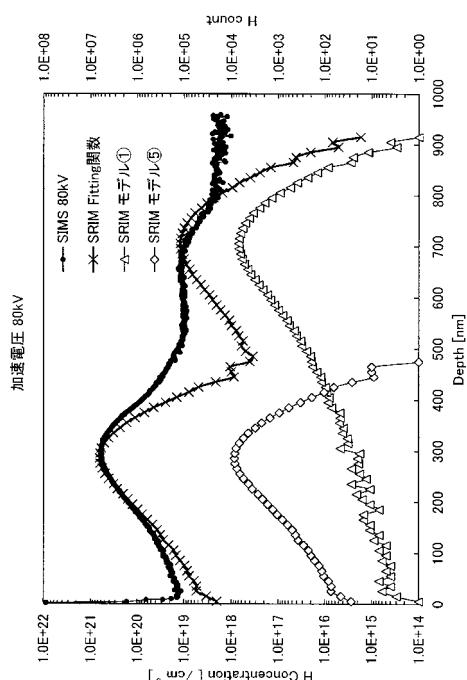

#### 【0246】

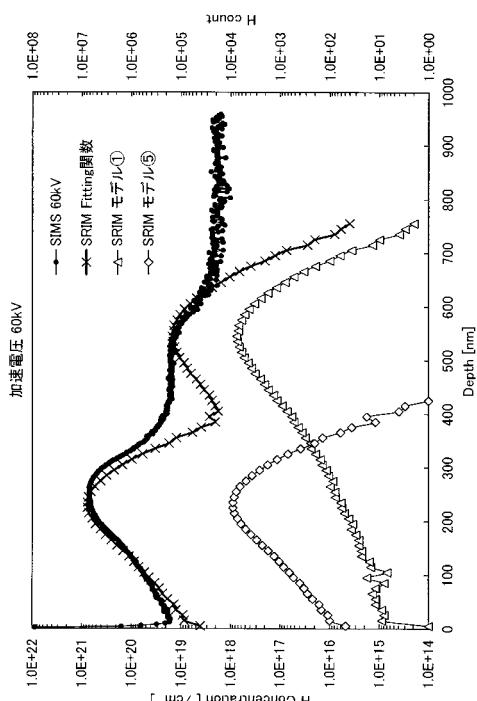

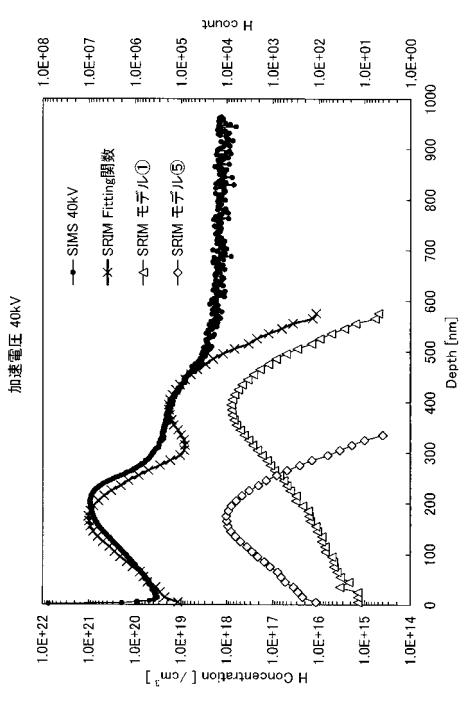

以上の考察により、モデル2乃至モデル4については、以下では考慮しない。図26乃至図28に、モデル1及びモデル5を用いて水素イオン種を照射した場合 (H換算で10万個照射時) の計算結果を示す。また、図23の水素イオン種を照射したシリコン基板中の水素濃度 (SIMSデータ) 及び、上記シミュレーション結果をSIMSデータにフィッティングさせたもの (以下フィッティング関数と呼ぶ) をあわせて示す。ここで、図26は加速電圧を80kVとした場合を示し、図27は加速電圧を60kVとした場合を示し、図28は加速電圧を40kVとした場合を示している。なお、モデル1及びモデル5を用いて行った計算の結果については、縦軸を水素原子の数で表しており (右軸)、SIMSデータ及びフィッティング関数については、縦軸を水素原子の密度で表している (左軸)。横軸はシリコン基板表面からの深さである。

30

#### 【0247】

フィッティング関数はモデル1及びモデル5を考慮して以下の計算式により求めることとした。なお、計算式中、X、Yはフィッティングに係るパラメータであり、Vは体積である。

##### [フィッティング関数]

$$= X / V \times [\text{モデル1のデータ}] + Y / V \times [\text{モデル5のデータ}]$$

#### 【0248】

現実に照射される水素イオン種の割合 ( $H^+$ イオン :  $H_2^+$ イオン :  $H_3^+$ イオン = 1 : 1 : 8程度)を考えれば $H_2^+$ イオンの寄与 (すなわち、モデル3) についても考慮すべきであるが、以下に示す理由により、ここでは除外して考えた。

40

50

・モデル3に示される照射過程により導入される水素は、モデル5の照射過程と比較して僅かであるため、除外しても大きな影響はない(SIMSデータにおいても、ピークが現れていない)。

・モデル5とピーク位置の近いモデル3は、モデル5において生じるチャネリング(結晶の格子構造に起因する元素の移動)により隠れてしまう可能性が高い。すなわち、モデル3のフィッティングパラメータを見積もるのは困難である。これは、本シミュレーションが非晶質シリコンを前提としており、結晶性に起因する影響を考慮していないことによるものである。

#### 【0249】

図29に、上記のフィッティングパラメータをまとめる。いずれの加速電圧においても、導入されるHの数の比は、[モデル1] : [モデル5] = 1 : 4.2 ~ 1 : 4.5程度(モデル1におけるHの数を1とした場合、モデル5におけるHの数は4.2以上4.5以下程度)であり、照射される水素イオン種の数の比は、[H<sup>+</sup>イオン(モデル1)] : [H<sub>3</sub><sup>+</sup>イオン(モデル5)] = 1 : 1.4 ~ 1 : 1.5程度(モデル1におけるH<sup>+</sup>イオンの数を1とした場合、モデル5におけるH<sub>3</sub><sup>+</sup>イオンの数は1.4以上1.5以下程度)である。モデル3を考慮していないことや非晶質シリコンと仮定して計算していることなどを考えれば、実際の照射に係る水素イオン種の比(H<sup>+</sup>イオン : H<sub>2</sub><sup>+</sup>イオン : H<sub>3</sub><sup>+</sup>イオン = 1 : 1 : 8程度)に近い値が得られていると言える。

#### 【0250】

##### (H<sub>3</sub><sup>+</sup>イオンを用いる効果)

図23に示すようなH<sub>3</sub><sup>+</sup>イオンの割合を高めた水素イオン種を単結晶半導体基板に照射することで、H<sub>3</sub><sup>+</sup>イオンに起因する複数のメリットを享受することができる。例えば、H<sub>3</sub><sup>+</sup>イオンはH<sup>+</sup>イオンやHなどに分離して基板内に導入されるため、主にH<sup>+</sup>イオンやH<sub>2</sub><sup>+</sup>イオンを照射する場合と比較して、イオンの導入効率を向上させることができる。これにより、SOI基板の生産性向上を図ることができる。また、同様に、H<sub>3</sub><sup>+</sup>イオンが分離した後のH<sup>+</sup>イオンやHの運動エネルギーは小さくなる傾向にあるから、薄い半導体層の製造に向いている。

#### 【0251】

なお、H<sub>3</sub><sup>+</sup>イオンを効率的に照射するために、図23に示すような水素イオン種を照射可能なイオンドーピング装置を用いることが好ましい。これは、イオンドーピング装置は廉価で、大面積処理に優れているため、このようなイオンドーピング装置を用いてH<sub>3</sub><sup>+</sup>イオンを照射することで、大面積化、低コスト化、生産性向上などの顕著な効果を得ることができるからである。一方で、H<sub>3</sub><sup>+</sup>イオンの照射を第一に考えるのであれば、イオンドーピング装置を用いることに限定して解釈する必要はない。

#### 【図面の簡単な説明】

#### 【0252】

【図1】SOI基板の作製方法の例を示す図。

【図2】レーザビームの照射の例を示す図。

【図3】SOI基板の構成例を示す図。

【図4】SOI基板の構成例を示す図。

【図5】SOI基板の作製方法の例を示す図。

【図6】レーザビームの照射の例を示す図。

【図7】SOI基板の作製方法の例を示す図。

【図8】レーザビームの照射の例を示す図。

【図9】エレクトロルミネセンス表示装置の作製方法の例を示す図。

【図10】エレクトロルミネセンス表示装置の作製方法の例を示す図。

【図11】エレクトロルミネセンス表示装置の作製方法の例を示す図。

【図12】エレクトロルミネセンス表示装置の作製方法の例を示す図。

【図13】半導体装置の作製方法の例を示す図。

【図14】半導体装置の作製方法の例を示す図。

10

20

30

40

50

【図15】S O I 基板により得られるマイクロプロセッサの構成を示すブロック図。

【図16】S O I 基板により得られるR F C P U の構成を示すブロック図。

【図17】表示パネル製造用のマザーガラスに半導体層を接合する例を示す図。

【図18】表示パネル製造用のマザーガラスに半導体層を接合する例を示す図。

【図19】エレクトロルミネセンス表示装置の例を示す図。

【図20】電子機器の例を示す図。

【図21】液晶表示装置の例を示す図。

【図22】水素イオン種のエネルギーダイアグラムについて示す図である。

【図23】イオンの質量分析結果を示す図である。

【図24】イオンの質量分析結果を示す図である。

10

【図25】加速電圧を80 kVとした場合の水素元素の深さ方向のプロファイル（実測値及び計算値）を示す図である。

【図26】加速電圧を80 kVとした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

【図27】加速電圧を60 kVとした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

【図28】加速電圧を40 kVとした場合の水素元素の深さ方向のプロファイル（実測値、計算値、及びフィッティング関数）を示す図である。

【図29】フィッティングパラメータの比（水素元素比及び水素イオン種比）をまとめた図である。

20

【符号の説明】

【0253】

|     |         |

|-----|---------|

| 100 | 半導体基板   |

| 102 | 脆化層     |

| 104 | 絶縁層     |

| 110 | 接合層     |

| 111 | 熱酸化膜    |

| 112 | 窒素含有絶縁層 |

| 114 | シリコン酸化層 |

| 120 | 支持基板    |

| 122 | 窒素含有絶縁層 |

| 124 | 接合層     |

| 130 | 半導体層    |

| 140 | レーザビーム  |

| 142 | 照射領域    |

| 170 | レーザビーム  |

| 172 | 照射領域    |

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図 2 5】

【図 2 6】

【図 2 7】

【図 2 8】

【図 2 9】

| 加速電圧  | 水素元素 (H) 比 (X : Y) | 水素イオン種比 (X : Y / 3) |

|-------|--------------------|---------------------|

| 80 kV | 1:44.1             | 1:14.7              |

| 60 kV | 1:42.5             | 1:14.2              |

| 40 kV | 1:43.5             | 1:14.5              |

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

H 01 L 21 / 02

H 01 L 21 / 336

H 01 L 27 / 12

H 01 L 29 / 786