(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7634603号**

**(P7634603)**

(45)発行日 令和7年2月21日(2025.2.21)

(24)登録日 令和7年2月13日(2025.2.13)

(51)国際特許分類

F I

|         |                 |         |       |         |

|---------|-----------------|---------|-------|---------|

| H 1 0 D | 30/66 (2025.01) | H 1 0 D | 30/66 | 1 0 2 G |

| H 1 0 D | 30/01 (2025.01) | H 1 0 D | 30/66 | 1 0 1 T |

| H 1 0 D | 12/00 (2025.01) | H 1 0 D | 30/66 | 1 0 3 Q |

|         |                 | H 1 0 D | 30/66 | 1 0 1 F |

|         |                 | H 1 0 D | 30/01 | 3 0 1 F |

請求項の数 12 (全34頁) 最終頁に続く

(21)出願番号 特願2023-108125(P2023-108125)

(22)出願日 令和5年6月30日(2023.6.30)

(62)分割の表示 特願2021-568331(P2021-568331

)の分割

原出願日 令和2年5月1日(2020.5.1)

(65)公開番号 特開2023-115346(P2023-115346

A)

(43)公開日 令和5年8月18日(2023.8.18)

審査請求日 令和5年7月31日(2023.7.31)

(31)優先権主張番号 16/413,921

(32)優先日 令和1年5月16日(2019.5.16)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 592054856

ウルフスピード インコーポレイテッド

W O L F S P E E D , I N C .

アメリカ合衆国 ノースカロライナ州 2

7 7 0 3 ダラム シリコン ドライブ 4

6 0 0

(74)代理人 110000855

弁理士法人浅村特許事務所

(72)発明者 ヴァン ブラント、エドワード アール。

アメリカ合衆国、ノースカロライナ、ロ

ーリー、クリート ドライブ 1 4 1 3

(72)発明者 リヒテンヴァルナ、ダニエル ジェイ。

アメリカ合衆国、ノースカロライナ、ロ

ーリー、ホライゾン ハイク コート 2

3 0 8

最終頁に続く

(54)【発明の名称】 リフローされた金属間誘電体層を有するパワー半導体デバイス

**(57)【特許請求の範囲】****【請求項1】**

ワイド・バンドギャップ半導体層構造と、

前記ワイド・バンドギャップ半導体層構造の上側表面上のゲート電極構造であって、前記ワイド・バンドギャップ半導体層構造の上側表面によって定義される面に垂直な方向に実質的に均一な厚さを有するゲート絶縁フィンガーによって前記ワイド・バンドギャップ半導体層構造から離されるゲート・フィンガーを含む、ゲート電極構造と、

リフローされない誘電体物質パターン及びリフローされた誘電体物質パターンを含む、

前記ゲート電極構造上の金属間誘電体パターンと、

前記金属間誘電体パターン上のソース・メタライゼーション構造と

を含み、

前記ゲート電極構造が前記ワイド・バンドギャップ半導体層構造及び前記金属間誘電体パターンの間にあり、

前記金属間誘電体パターンが前記ゲート電極構造と前記ソース・メタライゼーション構造との間にあり、

前記ゲート電極構造の中心より上方の前記リフローされた誘電体物質パターンの厚さが、前記ゲート電極構造の上側端に隣接する前記リフローされた誘電体物質パターンの厚さの少なくとも3倍である、半導体デバイス。

**【請求項2】**

前記ゲート電極構造が、複数のゲート絶縁フィンガーの各々によって前記ワイド・バン

ドギャップ半導体層構造から離される複数のゲート・フィンガーを含み、前記リフローされない誘電体物質パターンが、前記ゲート・フィンガーの各々の上面及び側面をコンフォーマルに囲む複数のリフローされない誘電体フィンガーを含み、請求項1に記載の半導体デバイス。

**【請求項3】**

前記リフローされた誘電体物質パターンの上面が、半梢円の横断面を有する、請求項1に記載の半導体デバイス。

**【請求項4】**

前記リフローされない誘電体物質パターンの厚さが、前記リフローされた誘電体物質パターンの最小厚さを超える、かつ前記リフローされた誘電体物質パターンの最大厚さを超えない、請求項1に記載の半導体デバイス。10

**【請求項5】**

前記リフローされない誘電体物質パターンの上方の角に隣接する前記リフローされた誘電体物質パターンの一部は、前記最小厚さを有する前記リフローされた誘電体物質パターンの一部である、請求項4に記載の半導体デバイス。

**【請求項6】**

前記リフローされた誘電体物質パターンは、ほうりんけい酸ガラス(BPSG: boron-phospho-silicate glass)パターンを含む、請求項1に記載の半導体デバイス。

**【請求項7】**

前記リフローされた誘電体物質パターンの最小厚さに対する前記ゲート電極構造の前記ゲート・フィンガーの上面の中心の上方の前記リフローされた誘電体物質パターンの厚さの比率が、3:1より大きい、請求項1に記載の半導体デバイス。20

**【請求項8】**

前記ゲート電極構造の上方にある前記リフローされた誘電体物質パターンが半梢円の上面を有し、前記リフローされた誘電体物質パターンが垂直な外側の側壁を有する、請求項1に記載の半導体デバイス。

**【請求項9】**

前記リフローされない誘電体物質パターンの最小厚さが、前記半導体デバイスの通常動作中、前記金属間誘電体パターンの破損を回避するのに十分であるように選択される、請求項1に記載の半導体デバイス。30

**【請求項10】**

ワイド・バンドギャップ半導体層構造と、

前記ワイド・バンドギャップ半導体層構造の上側表面上のゲート電極構造と

前記ゲート電極構造上の金属間誘電体パターンであって、少なくとも第1のリフローされた誘電体物質パターンと、前記第1のリフローされた誘電体物質パターンと異なる物質を含む第2のリフローされない誘電体物質パターンとを含む、金属間誘電体パターンと、40

前記金属間誘電体パターン上のソース・メタライゼーション構造と

を含み、

前記ゲート電極構造が前記ワイド・バンドギャップ半導体層構造及び前記金属間誘電体パターンの間にあり、

前記金属間誘電体パターンが前記ゲート電極構造と前記ソース・メタライゼーション構造との間にあり、

前記金属間誘電体パターンの最大厚さが、前記ゲート電極構造の中心の上面の上にある、半導体デバイス。

**【請求項11】**

前記第1のリフローされた誘電体物質パターンが、半梢円の上面及び垂直な外側の側壁を有する、請求項10に記載の半導体デバイス。

**【請求項12】**

前記第1のリフローされた誘電体物質パターンの上面及び前記第2のリフローされない

10

20

30

40

50

誘電体物質パターンの上面の各々が、半橢円の横断面を有する、請求項 10 に記載の半導体デバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は 2019 年 5 月 16 日に出願の米国特許出願シリアル番号 16 / 413,921 に基づく優先権を主張する。この出願の内容全体はその全体が記載されたかのように引用によって本願明細書に組み入れられたものとする。

【0002】

本発明は半導体デバイスに関し、特に、パワー半導体デバイスに関する。

10

【背景技術】

【0003】

パワー半導体デバイスは、大電流を通し高電圧をサポートするために用いられる。例えば、パワー金属酸化物半導体電界効果トランジスタ（「MOSFET」）、絶縁ゲートバイポーラトランジスタ（「IGBT」）及び、他の様々なデバイスを含む技術において、多種多様なパワー半導体デバイスが知られている。これらのパワー半導体デバイスは、通常、炭化ケイ素又は窒化ガリウム系材料のようなワイド・バンドギャップ半導体材料から作製される（本願明細書において、「ワイド・バンドギャップ半導体」という用語は、少なくとも 1.4 eV のバンドギャップを有するあらゆる半導体を含む）。パワー半導体デバイスは、高電圧及び／又は大電流を、（順方向又は逆方向の阻止状態において）ブロックする、又は、（順方向の導通状態において）通すように設計される。例えば、パワー半導体デバイスは、阻止状態において、数百又は数千ボルトの電位にも耐えるように設計され得る。

20

【0004】

パワー半導体デバイスは横型又は縦型の構造を有し得る。横型構造を有するデバイスにおいて、デバイスの端子（例えば、パワー MOSFET のドレイン、ゲート、及び、ソース端子）は、半導体層構造の同じ主要面（すなわち、上側表面又は下面）上にある。これに対して、縦型の構造を有するデバイスでは、半導体層構造の各主要面上に少なくとも 1 つの端子が設けられている（例えば、縦型 MOSFET において、ソース及びゲートは半導体層構造の上側表面にあり得、ドレインは半導体層構造の底面にあり得る）。縦型の構造は、高電流密度に耐えることができ高電圧をブロックすることができる厚い半導体ドリフト層を可能にするので、典型的には、非常に大きい電力を扱う用途に用いられる。本願明細書において、「半導体層構造」という用語は、半導体基板及び／又は半導体エピタキシャル層のような 1 つ又は複数の半導体層を含む構造を意味する。

30

【0005】

従来の炭化ケイ素縦型パワー MOSFET は、例えば、炭化ケイ素ウェーハのような、炭化ケイ素基板上に形成されるエピタキシャル層構造を含む。（1 つ又は複数の別々の層を含むことができる）エピタキシャル層構造は、パワー半導体デバイスのドリフト領域として機能する。MOSFET は、その中に 1 つ又は複数の半導体デバイスが形成されるドリフト領域の上に、及び／又は、の内に形成されるアクティブ領域と、アクティブ領域を囲むことができる終端領域とを有し得る。アクティブ領域は、逆バイアス方向の電圧をブロックし順バイアス方向の電流を提供するための主接合として機能する。パワー MOSFET は典型的にはユニット・セル構造を備えている。ユニット・セル構造とは、アクティブ領域が、単一のパワー MOSFET として機能するように電気的に並列に接続されている多数の個別の「ユニット・セル」 MOSFET を含むことを意味する。大電力の用途においては、そのようなデバイスは数千又は数万ものユニット・セルを含む場合がある。

40

【発明の概要】

【課題を解決するための手段】

【0006】

本発明の実施例によれば、ワイド・バンドギャップ半導体層構造と、ワイド・バンドギ

50

アップ半導体層構造の上側表面上のゲート電極構造と、リフロー可能でない誘電体物質パターン及びリフローされた誘電体物質パターンを含む、ゲート電極構造上の金属間誘電体パターンと、金属間誘電体パターン上のソース・メタライゼーション構造とを含む半導体デバイスが提供される。ゲート電極構造はワイド・バンドギャップ半導体層構造及び金属間誘電体パターンの間にあり、金属間誘電体パターンはゲート電極構造とソース・メタライゼーション構造との間にある。

#### 【0007】

幾つかの実施例においては、リフロー可能でない誘電体物質パターンは、ゲート電極構造とリフローされた誘電体物質パターンとの間にある。

#### 【0008】

幾つかの実施例においては、リフロー可能でない誘電体物質パターンの最小厚さは、半導体デバイスの通常動作中、金属間誘電体パターンの破壊を回避するには十分であるよう選択され得る。

#### 【0009】

幾つかの実施例においては、リフロー可能でない誘電体物質パターンの上側の角 (corner) の厚さは、半導体デバイスの通常動作中、金属間誘電体パターンの破壊を回避するには十分であるよう選択され得る。

#### 【0010】

幾つかの実施例においては、ゲート電極構造は、複数のゲート絶縁フィンガーのそれによってワイド・バンドギャップ半導体層構造から離される複数のゲート・フィンガーを含むことができ、リフロー可能でない誘電体物質パターンは、ゲート・フィンガーそれぞれの上側表面及び側面をコンフォーマルに囲む複数のリフロー可能でない誘電体フィンガーを含むことができる。

#### 【0011】

幾つかの実施例においては、リフローされた誘電体物質パターンは、丸みのある横断面を有することができる。

#### 【0012】

幾つかの実施例においては、金属間誘電体パターンの最小厚さに対するゲート電極構造のゲート・フィンガーの上面の中心より上方の金属間誘電体パターンの厚さの比率は 4 : 1 未満であり得る。

#### 【0013】

幾つかの実施例においては、リフローされた誘電体物質パターンのうち、リフロー可能でない誘電体物質パターンの上側の角に隣接する部分は、リフローされた誘電体物質パターンの最小厚さを有する部分であり得る。

#### 【0014】

幾つかの実施例においては、リフローされた誘電体物質パターンは、ほうりんけい酸ガラス (「BPSG」: boro-phospho-silicate glass) パターンを含み得る。

#### 【0015】

幾つかの実施例においては、半導体デバイスはMOSFETであり得、ワイド・バンドギャップ半導体層構造内に複数のソース領域が設けられ、ソース・メタライゼーション・パターンがソース領域に電気的接続されており、デバイスは、ワイド・バンドギャップ半導体層構造上のソース・メタライゼーション構造の反対側にドレイン・コンタクトを更に含む。

#### 【0016】

幾つかの実施例においては、ソース・メタライゼーション構造は、拡散バリア層、及び、拡散バリア層上の金属のソース・コンタクト層であり得る。

#### 【0017】

幾つかの実施例においては、半導体デバイスは、絶縁ゲート・バイポーラ・ジャンクション・トランジスタであり得る。

10

20

30

40

50

**【 0 0 1 8 】**

幾つかの実施例においては、リフローされた誘電体物質パターンがゲート電極構造とリフロー可能でない誘電体物質パターンとの間にあり得る。

**【 0 0 1 9 】**

本発明の更なる実施例によれば、ワイド・バンドギャップ半導体層構造と、ワイド・バンドギャップ半導体層構造の上側表面上のゲート電極構造と、リフローされた誘電体物質パターンを含む、ゲート電極構造上の金属間誘電体パターンと、金属間誘電体パターン上のソース・メタライゼーション構造とを含む半導体デバイスが提供される。リフローされた誘電体物質パターンの下側部分は実質的に垂直な側壁を有する。

**【 0 0 2 0 】**

幾つかの実施例においては、リフローされた誘電体物質パターンの上側部分は、丸みのある横断面を有することができる。

**【 0 0 2 1 】**

幾つかの実施例においては、ゲート電極構造は、複数のゲート絶縁フィンガーのそれによってワイド・バンドギャップ半導体層構造から離される複数のゲート・フィンガーを含むことができる。

**【 0 0 2 2 】**

幾つかの実施例においては、ゲート絶縁フィンガーは、ワイド・バンドギャップ半導体層構造の上側表面に対して垂直な方向に第1の厚さを有し、リフローされた誘電体物質パターンの下側部分は第1の厚さ以上である第2の厚さを有することができる。

10

**【 0 0 2 3 】**

幾つかの実施例においては、リフローされた誘電体物質パターンの下側部分の厚さは、少なくとも0.1ミクロンであり得る。

**【 0 0 2 4 】**

幾つかの実施例においては、ゲート電極構造はワイド・バンドギャップ半導体層構造と金属間誘電体パターンとの間にあり得、金属間誘電体パターンはゲート電極構造とソース・メタライゼーション構造との間にあり得る。

**【 0 0 2 5 】**

幾つかの実施例においては、リフローされた誘電体物質パターンは、ほうりんけい酸ガラス（「BPSG」）パターンを含み得る。

20

**【 0 0 2 6 】**

幾つかの実施例においては、金属間誘電体パターンの最小厚さに対するゲート電極構造のゲート・フィンガーの上面の中心より上の金属間誘電体パターンの厚さの比率は、少なくとも1:1で、且つ、4:1未満であり得る。

**【 0 0 2 7 】**

本発明の更なる実施例によれば、半導体デバイスを製作する方法が提供される、この方法においては、ワイド・バンドギャップ半導体層構造が形成される。ワイド・バンドギャップ半導体層構造の上側表面上に、伝導性パターンが形成される。伝導性パターンの上に、リフロー可能でない誘電体物質パターンが形成される。伝導性パターンの上に、リフロー可能な誘電体物質を含むリフロー可能な誘電体物質層が形成される。リフロー可能な誘電体物質がリフローされる。ソース・メタライゼーション構造が金属間誘電体パターンの上に形成される。金属間誘電体パターンは、リフロー可能でない誘電体物質パターン、及びリフロー可能な誘電体物質の少なくとも一部を含むリフローされた誘電体物質パターンを含む。

30

**【 0 0 2 8 】**

幾つかの実施例においては、リフロー可能でない誘電体物質パターンは、伝導性パターンとリフローされた誘電体物質パターンとの間にあり得る。

**【 0 0 2 9 】**

幾つかの実施例においては、リフローされた誘電体物質パターンは、伝導性パターンとリフロー可能でない誘電体物質パターンとの間にあり得る。

40

50

**【 0 0 3 0 】**

幾つかの実施例においては、方法は、リフロー可能な誘電体物質を含むリフロー可能な誘電体物質層をリフローして、リフローされた誘電体物質層を形成することと、それからリフローされた誘電体物質層をエッチングして、リフローされた誘電体物質パターンを形成することとを更に含むことができる。

**【 0 0 3 1 】**

幾つかの実施例においては、方法は、リフロー可能な誘電体物質を含むリフロー可能な誘電体物質層をエッチングして、リフロー可能な誘電体物質パターンを形成することと、それからリフロー可能な誘電体物質パターンをリフローして、リフローされた誘電体物質パターンを形成することとを更に含むことができる。

10

**【 0 0 3 2 】**

幾つかの実施例においては、伝導性パターンは複数のゲート・フィンガーを含むことができる。

**【 0 0 3 3 】**

幾つかの実施例においては、リフロー可能でない誘電体物質パターンを形成することは、リフロー可能でない誘電体フィンガーを、それぞれのゲート・フィンガーの各々の上にコンフォーマルに形成することとを含むことができる。

**【 0 0 3 4 】**

幾つかの実施例においては、リフローされた誘電体物質パターンは、ほうりんけい酸ガラス・パターンであり得る。

20

**【 0 0 3 5 】**

幾つかの実施例においては、リフロー可能でない誘電体物質パターンはゲート・フィンガーの側壁上に形成され得る。

**【 0 0 3 6 】**

幾つかの実施例においては、リフローされた誘電体物質パターンはゲート・フィンガーの側壁に直接接触することができる。

**【 0 0 3 7 】**

幾つかの実施例においては、伝導性パターンは半導体パターンを含むことができ、リフロー可能でない誘電体物質パターンを伝導性パターンの上に形成することは、半導体パターンの露出された表面を酸化することとを含むことができる。

30

**【 0 0 3 8 】**

幾つかの実施例においては、半導体パターンは複数のポリシリコンのゲート・フィンガーを含むことができ、ワイド・バンドギャップ半導体層構造が炭化ケイ素半導体層構造を含み得る。

**【 0 0 3 9 】**

幾つかの実施例においては、方法は、ゲート・フィンガーのうちの隣り合うものの間に定められるギャップに、それぞれの犠牲となる構造 (sacrificial structure) を形成することとを更に含むことができる。そして、犠牲となる構造は、リフロー可能な誘電体物質をリフローしている間にリフロー可能な誘電体物質の横方向の拡がりを制限するように配置される。

40

**【 0 0 4 0 】**

幾つかの実施例においては、リフロー可能でない誘電体物質パターンの最小厚さは、半導体デバイスの通常動作中、金属間誘電体パターンの破壊を回避するには十分であるように選択され得る。

**【 0 0 4 1 】**

幾つかの実施例においては、リフロー可能でない誘電体物質パターンの上側の角の厚さは、半導体デバイスの通常動作中、金属間誘電体パターンの破壊を回避するには十分であるように選択され得る。

**【 0 0 4 2 】**

幾つかの実施例においては、リフローされた誘電体物質パターンは、丸みのある横断面

50

を有することができる。

**【 0 0 4 3 】**

幾つかの実施例においては、金属間誘電体パターンの最小厚さに対する伝導性パターンのゲート・フィンガーの上面の中心より上の金属間誘電体パターンの厚さの比率は4:1未満であり得る。

**【 0 0 4 4 】**

本発明の更に他の実施例によれば、半導体デバイスを製作する方法が提供される。この方法においては、ワイド・バンドギャップ半導体層構造が形成され、それから、間隔を置いて配置された複数のゲート・フィンガーがワイド・バンドギャップ半導体層構造の上側表面上に形成される。リフロー可能な誘電体物質を含むリフロー可能な誘電体物質層がゲート・フィンガー上に形成される。ゲート・フィンガー同士の間のギャップにおいて、ワイド・バンドギャップ半導体層構造上に犠牲となる構造が形成される。リフロー可能な誘電体物質はリフローされる。ソース・メタライゼーション・パターンは金属間誘電体パターンの上に形成される。金属間誘電体パターンは、リフロー可能な誘電体物質の少なくとも一部を含むリフローされた誘電体物質パターンを含む。

10

**【 0 0 4 5 】**

幾つかの実施例においては、リフロー可能な誘電体物質層をゲート・フィンガー上に形成することは、リフロー可能な誘電体物質層を、それぞれのゲート・フィンガーの各々の上にコンフォーマルに形成することを含むことができる。

20

**【 0 0 4 6 】**

幾つかの実施例においては、リフローされた誘電体物質パターンは、ほうりんけい酸ガラス・パターンであり得る。

**【 0 0 4 7 】**

幾つかの実施例においては、ゲート・フィンガーは、ポリシリコンのゲート・フィンガーを含むことができ、ワイド・バンドギャップ半導体層構造が炭化ケイ素半導体層構造を含むことができる。

**【 0 0 4 8 】**

幾つかの実施例においては、犠牲となる構造は、リフロー可能な誘電体物質をリフローしている間にリフロー可能な誘電体物質の横方向の拡がりを制限するように配置され得る。

30

**【 0 0 4 9 】**

幾つかの実施例においては、方法は、犠牲となる構造を取り除くことを更に含むことができる。

**【 0 0 5 0 】**

幾つかの実施例においては、リフローされた誘電体物質パターンの下側部分が実質的に垂直な側壁を有することができ、リフローされた誘電体物質パターンの上側部分が丸みのある横断面を有することができる。

**【 0 0 5 1 】**

本発明の更なる実施例によれば、ワイド・バンドギャップ半導体層構造と、ワイド・バンドギャップ半導体層構造の上側表面上のゲート電極構造と、ゲート電極構造上の金属間誘電体パターンであって、金属間誘電体パターンは少なくとも第1の酸化シリコン・パターン及び第2の酸化シリコン・パターンを含み、第2の酸化シリコン・パターンは第1の酸化シリコン・パターンと異なる材質を含む、金属間誘電体パターンと、金属間誘電体パターン上のソース・メタライゼーション構造とを含む半導体デバイスが提供される。ゲート電極構造はワイド・バンドギャップ半導体層構造及び金属間誘電体パターンの間にあり、金属間誘電体パターンはゲート電極構造とソース・メタライゼーション構造との間にあり、金属間誘電体パターンの最小厚さに対する金属間誘電体パターン的最大厚さの比率が4:1未満である。

40

**【 0 0 5 2 】**

幾つかの実施例においては、第1の酸化シリコン・パターンがリフロー可能でない材料パターンを含むことができ、第2の酸化シリコン・パターンがリフローされた材料パー

50

ンを含むことができる。

**【0053】**

幾つかの実施例においては、金属間誘電体パターンの最小厚さはゲート電極構造の上側の角に隣接していてもよい。

**【0054】**

幾つかの実施例においては、金属間誘電体パターンの最大厚さがゲート電極構造のゲート・フィンガーの上面の中心の上にあり得る。

**【0055】**

幾つかの実施例においては、金属間誘電体パターンの最小厚さに対する金属間誘電体パターンの最大厚さの比率は1:1超であり得る。

10

**【0056】**

幾つかの実施例においては、金属間誘電体パターンの最小厚さに対するゲート電極構造のゲート・フィンガーの上面の中心より上の金属間誘電体パターンの厚さの比率は1:1超であり得る。

**【0057】**

幾つかの実施例においては、金属間誘電体パターンの最小厚さがゲート電極構造の上側の角に隣接していてもよい。

**【図面の簡単な説明】**

**【0058】**

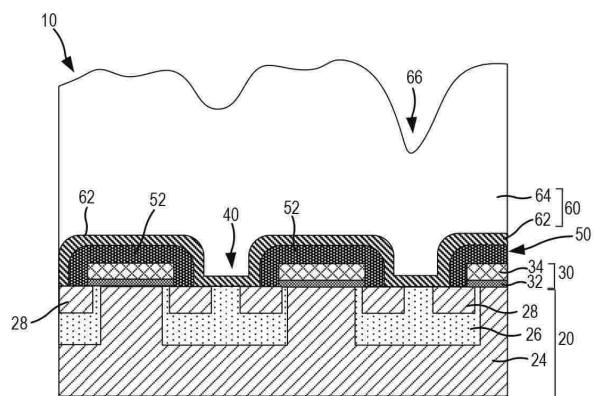

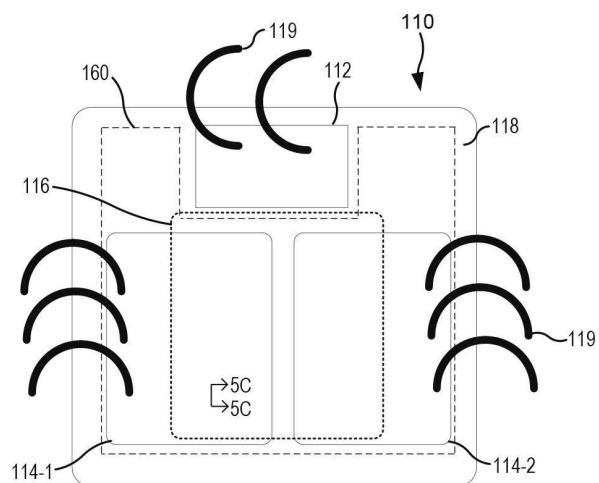

**【図1】**パワーMOSFETの幾つかのユニット・セルのための上側ソース・メタライゼーション構造の概略横断面図である。

20

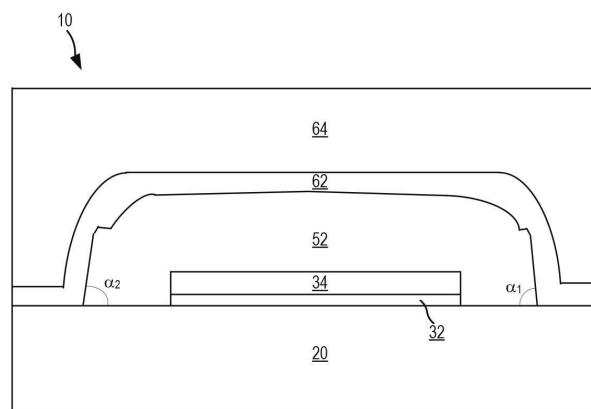

**【図2】**図1のMOSFETにおけるゲート・フィンガーのうちの1つ及び周囲の構造の拡大横断面図である。

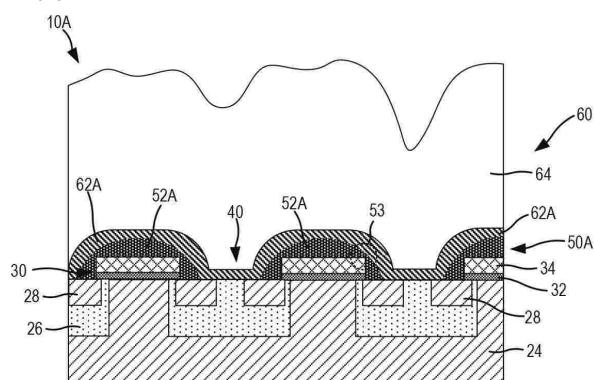

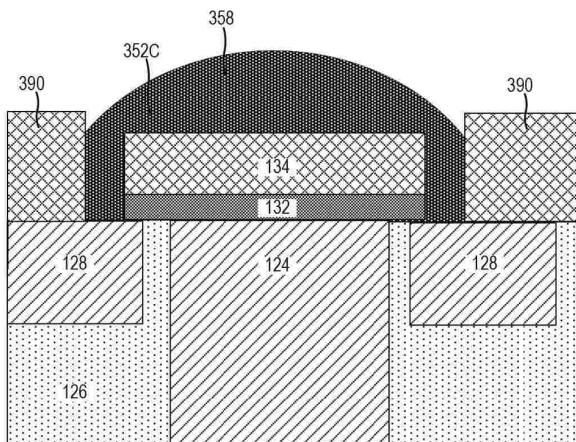

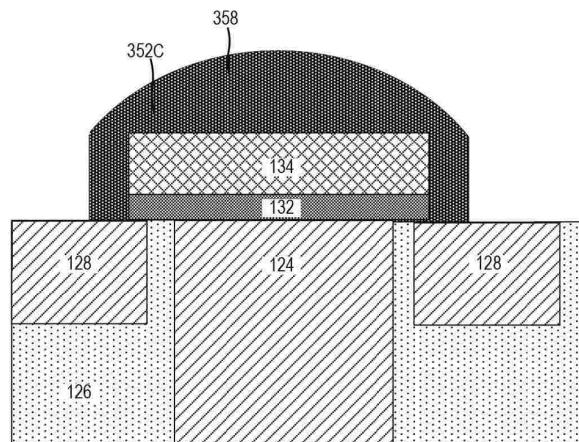

**【図3】**リフロー可能な金属間誘電体パターンを使用して形成されたパワーMOSFETの幾つかのユニット・セルのための上側ソース・メタライゼーション構造の概略横断面図である。

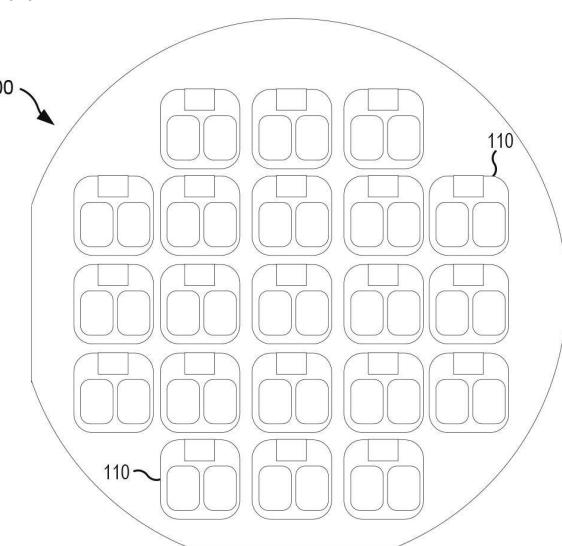

**【図4】**本発明の実施例に従う複数のパワーMOSFETを含む半導体のウェーハの概略平面図である。

**【図5A】**図4の半導体のウェーハに含まれるパワーMOSFETの1つの概略平面図である。

30

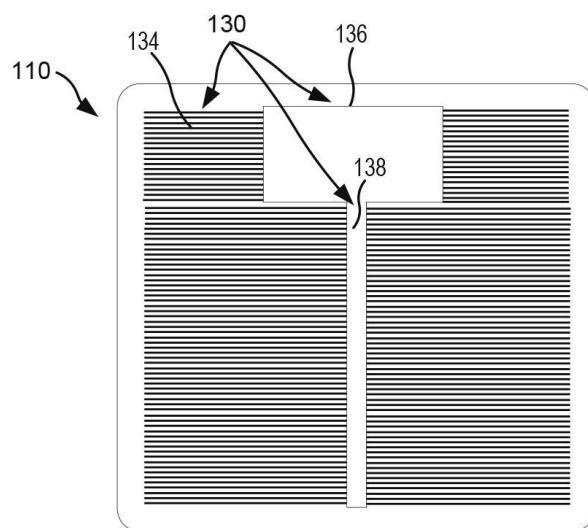

**【図5B】**上側ソース・メタライゼーション構造、ゲート・ボンド・パッド、及び、金属間誘電体パターンを省略した、図5AのパワーMOSFETの概略平面図である。

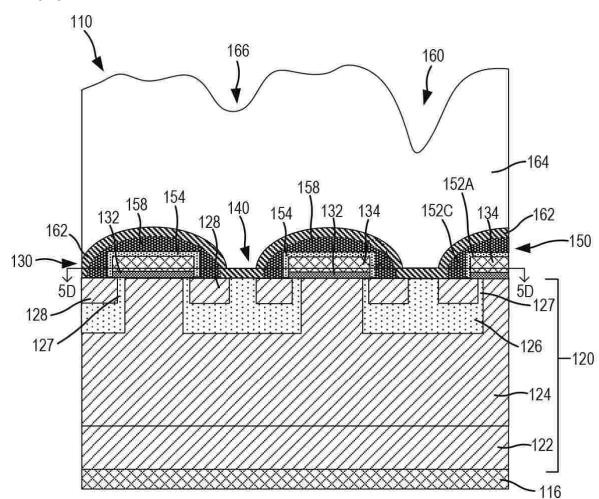

**【図5C】**図5Aのライン5C-5Cに沿う概略断面図である。

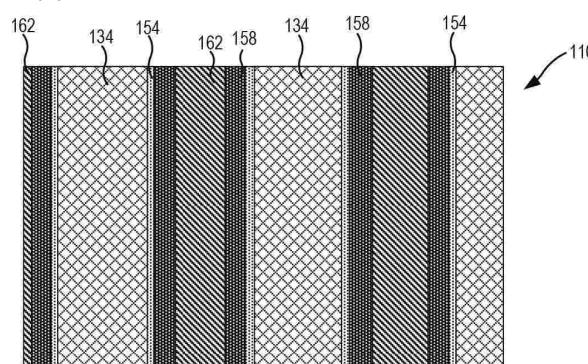

**【図5D】**図5Cのライン5D-5Dに沿う概略断面図である。

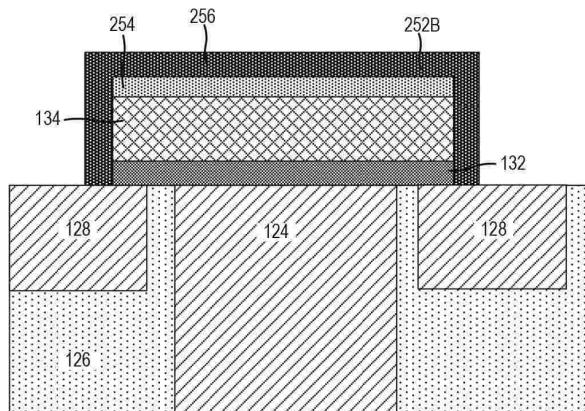

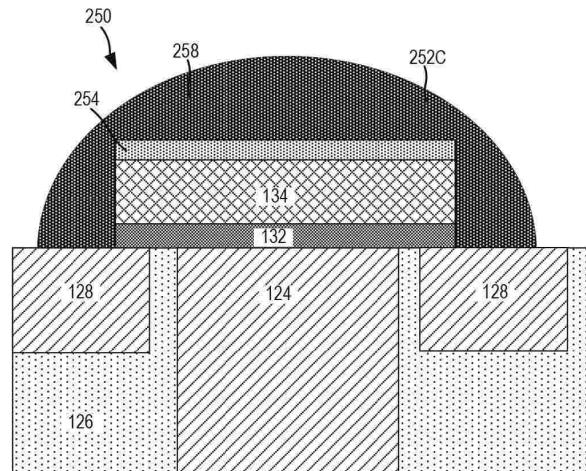

**【図5E】**ソース・メタライゼーション構造を省略した図5Cに示されるユニット・セルのうちの1つの拡大図である。

**【図6A】**図5Aから5EまでのMOSFETの金属間誘電体パターンを形成する方法を例示する概略断面図である。

**【図6B】**図5Aから5EまでのMOSFETの金属間誘電体パターンを形成する方法を例示する概略断面図である。

40

**【図6C】**図5Aから5EまでのMOSFETの金属間誘電体パターンを形成する方法を例示する概略断面図である。

**【図6D】**図5Aから5EまでのMOSFETの金属間誘電体パターンを形成する方法を例示する概略断面図である。

**【図6E】**図5Aから5EまでのMOSFETの金属間誘電体パターンを形成する方法を例示する概略断面図である。

**【図7A】**図5Aから5EまでのMOSFETの金属間誘電体パターンを形成する他の方法を例示する断面図である。

**【図7B】**図5Aから5EまでのMOSFETの金属間誘電体パターンを形成する他の方法を例示する断面図である。

50

【図 8 A】図 5 A から 5 E までの M O S F E T の金属間誘電体パターンの代わりに使われる金属間誘電体パターンを形成する方法を例示する断面図である。

【図 8 B】図 5 A から 5 E までの M O S F E T の金属間誘電体パターンの代わりに使われる金属間誘電体パターンを形成する方法を例示する断面図である。

【図 8 C】図 5 A から 5 E までの M O S F E T の金属間誘電体パターンの代わりに使われる金属間誘電体パターンを形成する方法を例示する断面図である。

【図 8 D】図 5 A から 5 E までの M O S F E T の金属間誘電体パターンの代わりに使われる金属間誘電体パターンを形成する方法を例示する断面図である。

【図 8 E】図 5 A から 5 E までの M O S F E T の金属間誘電体パターンの代わりに使われる金属間誘電体パターンを形成する方法を例示する断面図である。

【図 8 F】図 5 A から 5 E までの M O S F E T の金属間誘電体パターンの代わりに使われる金属間誘電体パターンを形成する方法を例示する断面図である。

【図 9 A】本発明の更なる実施例に従って M O S F E T を形成する方法を例示する概略断面図である。

【図 9 B】本発明の更なる実施例に従って M O S F E T を形成する方法を例示する概略断面図である。

【図 9 C】本発明の更なる実施例に従って M O S F E T を形成する方法を例示する概略断面図である。

【図 9 D】本発明の更なる実施例に従って M O S F E T を形成する方法を例示する概略断面図である。

【図 10】ソース・メタライゼーションを省略した本発明の更なる実施例によるパワー M O S F E T の 1 つのユニット・セルの横断面図である。

【図 11 A】本発明の実施例に従う n チャネル I G B T の簡略回路図である。

【図 11 B】図 11 A の I G B T の一対のユニット・セルの概略断面図である。

【図 12】本発明の実施例に従ってパワー M O S F E T を形成する方法のフローチャートである。

【図 13】本発明の更なる実施例に従ってパワー M O S F E T を形成する方法のフローチャートである。

#### 【発明を実施するための形態】

##### 【0059】

パワー M O S F E T 又はパワー I G B T のようなパワー半導体デバイスは、デバイスの端子を外部構造に接続するために用いる上側メタライゼーション構造を含む。例えば、縦型パワー M O S F E T は、半導体層構造と、デバイスのソース端子として機能する上側ソース・メタライゼーション構造と、デバイスのゲート端子として機能する上側ゲート・メタライゼーション構造と、デバイスの底面上に形成され、M O S F E T のためのドレイン端子として機能する「裏側」ドレイン・メタライゼーション構造とを含む。図 1 は、従来のパワー M O S F E T 1 0 の幾つかのユニット・セルの上側部分の概略横断面図である。

##### 【0060】

図 1 に示されるように、従来のパワー M O S F E T 1 0 は、半導体層構造 2 0 (半導体層構造 2 0 の上側部分だけが図 1 に示される) と、ゲート電極構造 3 0 と、金属間誘電体パターン 5 0 と、半導体層構造 2 0 及びゲート電極構造 3 0 の上側表面上に形成される上側ソース・メタライゼーション構造 6 0 とを含む。半導体層構造 2 0 は、例えば、炭化ケイ素半導体基板(図示せず)を含むことができる。炭化ケイ素半導体基板は、その上にエピタキシャルに成長した炭化ケイ素ドリフト領域 2 4 を有する。ドリフト領域 2 4 の逆導電型を有するウェル領域 2 6 は、ドリフト領域 2 4 の上側表面内に形成される。ソース領域 2 8 はウェル領域 2 6 の中に形成される。図 1 には示されていないが、半導体層構造 2 0 の底面上にドレイン・コンタクトが形成される。

##### 【0061】

ゲート電極構造 3 0 は、半導体層構造 2 0 の上側表面上に形成された複数のゲート・フィンガー 3 4 を含む。各ゲート・フィンガー 3 4 は棒形の半導体又は金属のパターンを有

10

20

30

40

50

し、ゲート・フィンガー34は互いに平行に延びているようにできる。ゲート・フィンガ-34を半導体層構造20から絶縁するために、ゲート電極構造30は、それぞれのゲート・フィンガー34と半導体層構造20の上側表面との間に形成された複数のゲート絶縁フィンガー32を更に含む。ゲート絶縁フィンガー32は、酸化シリコンのストライプを含み得る。金属間誘電体パターン50は、複数の誘電体フィンガー52を含み、ゲート絶縁フィンガー32及びゲート・フィンガー34の形成の後、半導体層構造20の上側表面上に形成される。各誘電体フィンガー52は、ゲート絶縁フィンガー32のうちのそれぞれ1つ及びゲート・フィンガー34のうちのそれぞれ1つの、側壁及び上側表面を覆うことができる。隣り合う誘電体フィンガー52の間にギャップ40が設けられ、半導体層構造20の上側表面のソース領域28を露出させる。隣り合う誘電体フィンガー52間のピッチは小さくすることができ、それ故、ギャップ40は対応する（例えば、1～5ミクロンのような）狭い幅を有する。

#### 【0062】

上側ソース・メタライゼーション構造60は、導電性拡散バリア層62及び金属のソース・コンタクト層64を含む。拡散バリア層62は、半導体層構造20の上側表面において、金属間誘電体パターン50、並びに、露出したウェル領域26及びソース領域28の上にコンフォーマルに形成され得る。拡散バリア層62は、（例えば、湿式のエッティング液のような）物質が金属間誘電体パターン50内に拡散することを防止し得る適度に良好な導体であるように設計され得る。ソース・コンタクト層64は高伝導金属層を含み得る。ギャップ40の一部又は全部の上方のソース・コンタクト層64の上側表面に「鍵穴」と呼ばれる凹部66が存在し得る。

#### 【0063】

MOSFET10の製造の間に湿式のエッティング液のような化学物質がソース・コンタクト層64に適用され得る。特にソース・コンタクト層64の上側表面が深い鍵穴66を含む場合、湿式のエッティング液を完全に洗い落すことは困難な場合がある。潜在的には、如何なる残留する湿式のエッティング液（又は他の腐食性物質）も、ソース金属の結晶粒界に沿って上側ソース・メタライゼーション構造60の中に深く拡散する可能性がある。通常、導電拡散バリア層62は、ソース・コンタクト層64の底に到達した化学物質が更に拡散することを防止するが、拡散バリア層の金属は狭いギャップ40を必ずしも完全には満たすことができないので、拡散バリア層62には、特に、ギャップ40内には、小さい隙間が存在し得る。拡散バリア層62に隙間が存在する場合、化学物質は隙間を通過し、それから金属間誘電体パターン50を侵すことができる。金属間誘電体パターン50が継ぎ目又は他の通路を含む場合、化学物質は継ぎ目に沿って進行することができ、且つ／又は、拡大することができ、上側ソース・メタライゼーション構造60とゲート・フィンガ-34との間に経路を作る。これにより、潜在的には、上側ソース・メタライゼーション構造60とゲート・フィンガ-34との間に電気的短絡を作る可能性がある。そのような電気的短絡は、単一のユニット・セルに発生しても、結果としてMOSFET10を損傷又は破壊する場合がある。

#### 【0064】

図2は、図1のMOSFET10のゲート・フィンガ-34のうちの1つの、一定の比率で拡大された、拡大横断面図である。図2に示されるように、金属間誘電体パターン50の誘電体フィンガー52は、ゲート・フィンガ-34及びその下にあるゲート絶縁フィンガー32の上に実質的にコンフォーマルに形成される。誘電体フィンガー52の側壁及び半導体層構造20の上側表面は、一対の内向きに対向する角度<sub>1</sub>及び<sub>2</sub>を定める。図2に示されるように、角度<sub>1</sub>及び<sub>2</sub>は、各々約90度であり得る。典型的な例である図示された実施例においては、角度<sub>1</sub>及び<sub>2</sub>は各々約80度であり、それ故、ギャップ40の側壁は約100度の角度で上方へ延びる。ギャップ40の側壁がそのような鋭い角度を有するときには、完全にギャップ40を埋めることができない場合がある。それにより、上述のように、結果として拡散バリア層62に隙間が形成され得る。

#### 【0065】

10

20

30

40

50

図3は、図1のMOSFET10の金属間誘電体パターン50とは異なる形状を有する金属間誘電体パターン50Aを含む、図1のMOSFET10の修正版であるMOSFET10Aの一部分の概略横断面図である。図3を参照すると、拡散バリア層62において隙間が形成されるという可能性を減らすための1つの技術は、角度<sub>1</sub>及び<sub>2</sub>の大きさを減少させることである。それにより、ギャップ40の側壁が半導体層構造20の上側表面と共に定める角度を増加させる。ギャップ40の側壁によって定義される角度が増加するにつれて、拡散バリア層の金属が隙間を形成すること無くギャップ40を埋めることができより容易になる。図3に示されるように、角度<sub>1</sub>及び<sub>2</sub>の大きさを減少させる（そして、それ故、ギャップ40の側壁によって定義される角度を増加させる）1つの方法は、例えば、ほうりんけい酸ガラス（「BPSG」：boron-phospho-silicic acid glass）のような、リフロー可能な誘電体物質を使用して（図3に示されない）リフロー可能な金属間誘電体パターンをゲート電極構造30の上面及び側壁上にコンフォーマルに形成することである。BPSGの金属間誘電体パターンは、ゲート電極構造30上にコンフォーマルに形成された後、昇温状態（例えば、500～1000間の温度）でリフローされ、リフローされた金属間誘電体パターン50Aを提供することができる。リフロー・プロセスは誘電体物質の密度を増加させることができ、物質の継ぎ目を減少させるか又は除去することに資する。加えて、リフローされたBPSG物質の表面張力は、結果として、図3に示されるように、一般に半楕円形又は半円形の横断面を有するリフローされた金属間誘電体パターン50Aを形成する別々の誘電体フィンガー52Aを作ることができる。この一般に「丸みのある」輪郭は角度<sub>1</sub>及び<sub>2</sub>を減らすことができ、重大な隙間を形成すること無くギャップ40に拡散バリア層62Aを形成することをより容易にすることができます。10

20

#### 【0066】

リフロー可能な誘電体物質を用いて金属間誘電体パターン50Aを形成することは、拡散バリア層62Aのギャップ埋め特性を大幅に向上させる（それ故、その中の隙間形成を減らす）ことができるが、各ゲート・フィンガー34を覆うリフローされたBPSG物質の厚さは均一でない。特に、図3に示されるように、リフローされたBPSG物質の厚さは、ゲート・フィンガー34の上面の中央の上に最大厚さを有し得、ゲート・フィンガー34の上面の側端に隣接して著しく薄くなり得る。場合によっては、ゲート・フィンガー34の上側端に隣接するリフローされた金属間誘電体パターン50Aの厚さ（図3の領域53を参照）は、ゲート・フィンガー34の上面の中央から上方のリフローされたBPSG物質の厚さの僅か10%～40%の厚さしか有しない場合がある。加えて、リフロー・プロセスは各誘電体フィンガー52Aの横方向の幅を延ばす傾向があり得、それにより、ギャップ40の幅を減らす。リフローされた誘電体フィンガー52Aの上側の薄い「角」領域は、デバイスの動作中、破壊に対して脆弱であり得る。その結果、ゲート・フィンガー34とソース・メタライゼーション構造60との間に短絡を起こし得、それは結果としてデバイスを故障させ得る。加えて、ギャップ40が小さいほど、ソース接触抵抗を増加させ得、且つ又は、拡散バリア層62Aの付着の間に隙間が形成される可能性を増加させ得る。したがって、リフロー可能な金属間誘電体パターン50Aの使用が1つの問題を解決し得るが、別の問題を発生させ得る。30

40

#### 【0067】

本発明の特定の実施例によれば、少なくとも1つのリフロー可能な誘電体物質パターン及び少なくとも1つのリフロー可能でない誘電体物質パターンを含む多層金属間誘電体パターンを含むパワー半導体デバイスが提供される。リフロー可能でない誘電体物質パターンは、ゲート・フィンガーの露出した上面上、及び、ゲート絶縁フィンガー及びゲート・フィンガーの露出した側面上に形成され得る。リフロー可能な誘電体物質パターンは、リフロー可能でない誘電体物質パターン上に形成され得る。或いは、リフロー可能な誘電体物質パターンは、ゲート・フィンガーの露出した上面に、そして、フィンガー及びゲート・フィンガーを絶縁するゲートの露出した側面に形成され得る。それから、リフローされた誘電体物質パターンを形成するためにリフロー可能な誘電体物質パターンはリフローさ50

れ得、リフロー可能でない誘電体物質パターンはリフローされた誘電体物質パターンの上に形成され得る。

#### 【 0 0 6 8 】

何れの場合にも、リフロー可能でない誘電体物質パターンは、例えば、金属間誘電体パターンの破壊を防止するには十分な厚さを有することができる。したがって、ゲート・フィンガーの上側の角に隣接するリフロー可能な誘電体物質パターンの厚さがリフロー・プロセスの間に著しく減らされる場合であっても、誘電体物質の十分な総厚さが依然あり、破壊を避けるであろう。更に、リフロー可能でない誘電体物質パターン及びリフロー可能な誘電体物質パターンの組合せは、図3の実施例のリフロー可能な誘電体物質パターンの厚さとほぼ同じ厚さを有することができる。したがって、リフロー可能な誘電体物質パターンは、より小さい厚さを有し得、それ故、リフロー中に隣り合うゲート・フィンガー間のギャップに入り込むまでには拡がらないであろう。したがって、本発明の実施例に従う金属間誘電体パターンは、完全にリフロー可能な金属間誘電体パターンと関連した潜在的に不利な点を減らすか又は最小化しつつ、完全にリフロー可能な金属間誘電体パターンの有利な点を有し得る。

10

#### 【 0 0 6 9 】

本発明の更なる実施例によれば、リフロー・プロセスの間の金属間誘電体パターンのリフロー可能な誘電体物質の横方向の拡がりを制限するためにダムのような犠牲となる構造を用いて形成された、リフローされた金属間誘電体パターンを含むパワー半導体デバイスが提供される。そのようなダムの使用はゲート・フィンガーの側端に沿う誘電体物質の量を増加させ、金属間誘電体パターンが十分な最小厚さを有し金属間誘電体パターンの破壊を回避することを確実にすることができます。犠牲となるダムはリフロー可能な誘電体物質の横方向の拡がりを防止し得、それにより、隣り合う誘電体フィンガー間のギャップの大きさを維持し得る。

20

#### 【 0 0 7 0 】

金属間誘電体パターンは、例えば、リフロー可能でない層及びリフロー可能な層を有する多層金属間誘電体パターンを含み得る。金属間誘電体パターンの最小厚さに対する金属間誘電体パターンの最大厚さの比率は、幾つかの実施例においては8：1より小さく、他の実施例では6：1より小さく、更に他の実施例では4：1より小さい。各々の場合において、金属間誘電体パターンの最小厚さに対する金属間誘電体パターンの最大厚さの比率は少なくとも1：1である。

30

#### 【 0 0 7 1 】

本願明細書においては説明がパワーMOSFETデバイスに集中しているが、本願明細書において開示される技術がそのようなデバイスに限られていないことは理解されるであろう。例えば、本願明細書において開示される技術はIGBTデバイスにおいても用いられ得る。

#### 【 0 0 7 2 】

以下では、本発明の実施例について、本発明の代表的な実施例が示される図4から図13までを参照して更に詳細に説明されるであろう。

#### 【 0 0 7 3 】

図4は、本発明の実施例に従う複数のパワーMOSFET110を含む半導体のウェーハ100の概略平面図である。包装及びテストのために個々のパワーMOSFET110を分離するためにウェーハ100は後で切り離され（例えば、ダイシングされ）得るように、パワーMOSFET110は行及び列に並べて形成され互いに間隔を置いて配置され得る。幾つかの実施例においては、例えば、ウェーハ100は、（例えば、エピタキシャル成長によって）その上に形成された1つ又は複数の炭化ケイ素層を有する4Hの炭化ケイ素基板を含み得る。他の半導体層（例えば、ポリシリコン層）、絶縁層、及び／又は、金属層が炭化ケイ素半導体層構造の上に形成され、パワーMOSFET110を形成することができる。場合によっては、他の半導体層がその上に形成された後、炭化ケイ素基板は薄くされる、又は、除去されることができる。

40

50

**【 0 0 7 4 】**

図 5 A は、図 4 の半導体のウェーハ 100 に含まれるパワー MOSFET 110 のうちの 1 つの概略平面図である。図 5 B は、上側ソース・メタライゼーション構造、ゲート・ボンド・パッド、及び、金属間誘電体パターンを省略した、図 5 A のパワー MOSFET の概略平面図である。

**【 0 0 7 5 】**

図 5 A に示されるように、ゲート・ボンド・パッド 112 及び 1 つ又は複数のソース・ボンド・パッド 114-1、114-2 は、MOSFET 110 の半導体層構造 120 ( 図 5 C ) の上側表面上に形成され得る。( 図 5 A に点線のボックスとして示される ) ドレイン・ボンド・パッド 116 は MOSFET 110 の底面に設けられ得る。各結合パッド 112、114、116 は、ボンド・ワイヤが熱圧着又は半田付けのような従来技術によつて容易に接続され得る金属( 例えは、アルミニウムのような ) で形成され得る。

10

**【 0 0 7 6 】**

後で詳しく述べるように、MOSFET 110 は、MOSFET 110 の半導体層構造 120 のソース領域 128 を外部デバイスに電気的に接続する上側ソース・メタライゼーション構造 160 を含む。上側メタライゼーション構造 160 の重要な部分はポリイミド層のような保護層 118 によって覆われているので、上側ソース・メタライゼーション構造 160 は図 5 A の破線のボックスによって示される。幾つかの実施例においては、ソース・ボンド・パッド 114-1、114-2 は、保護層 118 の開口部を通して露出する上側メタライゼーション構造 160 の部分であり得る。ゲート・ボンド・パッド 112 及びソース・ボンド・パッド 114-1、114-2 を外部回路等に接続するために用いられ得るボンド・ワイヤ 119 が図 5 A に示される。

20

**【 0 0 7 7 】**

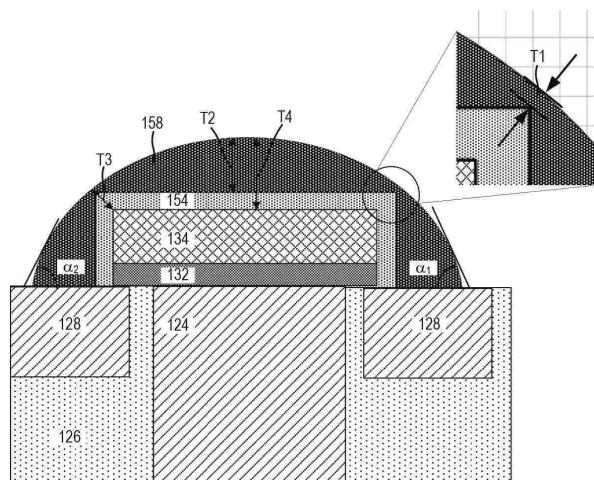

図 5 C は、図 5 B の線 5 C - 5 C に沿う概略断面図である。図 5 D は、図 5 C の線 5 D - 5 D に沿う概略横断面図である。図 5 C 及び図 5 D が、1 つのユニット・セルの全体を図示し、更に、前後関係を示すためにその両側の 2 つのユニット・セルの部分を図示するものであることは理解されるであろう。図 5 E は、図 5 C に示されるユニット・セルのうちの 1 つの、ソース・メタライゼーション構造を省略した、拡大図である。

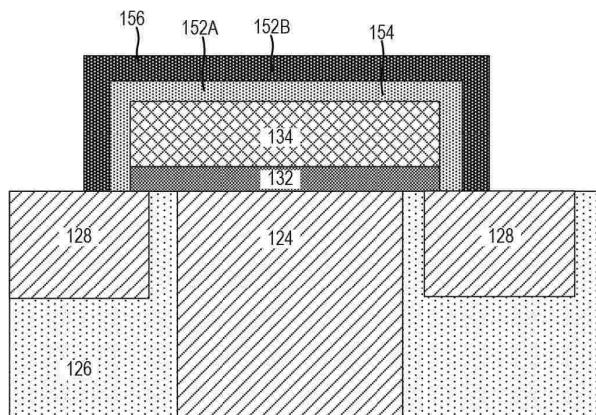

**【 0 0 7 8 】**

図 5 B から図 5 D までを参照して、複数のゲート絶縁フィンガー 132 ( 図 5 C ) 、複数のゲート・フィンガー 134 ( 図 5 B から図 5 D ) 、ゲート・パッド 136 ( 図 5 B ) 、及び、1 つ又は複数のゲート・バス 138 ( 図 5 B ) を含むゲート電極構造 130 が提供され得、1 つ又は複数のゲート・バス 138 は、ゲート・フィンガー 134 をゲート・パッド 136 に電気的に接続する。ゲート・フィンガー 134 、ゲート・バス 138 、及び、ゲート・パッド 136 の間の電気的接続は、従来通りでもよく、それ故、本願明細書においては説明されないか又は図示されない。ゲート絶縁フィンガー 132 は、例えは、酸化シリコンを含むことができ、ゲート・フィンガー 134 を下にある半導体層構造 120 から絶縁することができる。幾つかの実施例においては、ゲート・フィンガー 134 は、例えは、ポリシリコン・パターンを含み得るが、金属又は他の伝導性パターンも使用し得る。ゲート・フィンガー 134 は、デバイス全体に水平に拡がっているようにできる、或いは、半導体層構造 120 の上側表面全体に拡がっている平坦層を含むことができ、平坦層には開口部があり、これらの開口部を通して、上側ソース・メタライゼーション構造 160 ( 後述する ) が半導体層構造 120 のソース領域 128 に接続される。幾つかの実施例においては、ゲート・パッド 136 は、ゲート・ボンド・パッド 112 の直ぐ下にあり得、ゲート・ボンド・パッド 112 に電気的に接続され得る。他の複実施例において、ゲート・パッド 136 は、ゲート・ボンド・パッド 112 としても使用できる。他の構成も可能である。代表的な実施例においては、ゲート・パッド 136 及びゲート・バス 138 は、ポリシリコン及び / 又は金属を含み得る。

30

**【 0 0 7 9 】**

図 5 C から図 5 D に示されるように、金属間誘電体パターン 150 は、それぞれのゲー

40

50

ト・フィンガー 134 及びゲート・バス 138 を覆う複数の個別の誘電体フィンガー 152 を含むことができる。金属間誘電体パターン 150 はゲート電極構造 130 をソース・メタライゼーション構造 160 から絶縁することができる。上記のように、電極構造 130 のゲート・フィンガー 134 は、ポリシリコンのゲート・フィンガーであり得る。したがって、幾つかの実施例においては、「金属間」誘電体パターン 150 が、2つの金属のパターンを互いに絶縁することとは対照的に、半導体パターンを金属のパターンから絶縁するために形成されたパターンであり得ると理解される。

#### 【0080】

上側ソース・メタライゼーション構造 160 は金属間誘電体パターン 150 上に形成され得る。上側ソース・メタライゼーション構造 160 は拡散バリア層 162 及びソース・コンタクト層 164 を含む。MOSFET 110 は並列に電気的接続される複数のユニット・セル・トランジスタを含む。以下では、MOSFET 110 の個別の層 / パターンについてより詳細に説明される。

10

#### 【0081】

図 5C から図 5E までを参照すると、ユニット・セル・トランジスタは、例えば、n 型不純物によって（例えば、 $1 \times 10^{18}$  原子 /  $\text{cm}^3$  ~  $1 \times 10^{21}$  原子 /  $\text{cm}^3$  の）高濃度にドーピングされた 4H の単結晶炭化ケイ素半導体基板のような、n 型炭化ケイ素半導体基板 122 上に形成され得る。本願明細書において、半導体材料の「ドーピング濃度」とは、半導体材料が特定の導電型（すなわち、n 型又は p 型）を有するようにさせるドーパント原子の、半導体材料の 1 立方センチメートル内に存在し二次イオン質量分析法 (SIMS : Secondary Ion Mass Spectrometry) のような標準測定技術を用いて測定されるような、数のことである。幾つかの実施例においては、基板 122 は、任意の適切な厚さ（例えば、100 ~ 500 ミクロン厚）を有することができ、部分的又は完全に除去され得る。図 5C では基板 122 の厚さが一定の拡大比率に従って描かれているものではないことは理解されるであろう。

20

#### 【0082】

半導体基板 122 の下側表面上にドレイン・コンタクトが形成され得る。ドレイン・コンタクトは、半導体基板 122 へのオーミック・コンタクトとして、そして、MOSFET 110 のドレイン端子と外部デバイスとの間の電気的接続を提供するドレイン・ボンド・パッド 116 としてという両方の働きをすることができる。他の実施例においては、ドレイン・コンタクトは、ドレイン・ボンド・パッド 116 とは別であり得る（例えば、ドレイン・コンタクト上にドレイン・ボンド・パッド 116 として機能する第 2 層が形成され得る）。ここに説明される実施例においては、オーミック・ドレイン・コンタクト及びドレイン・ボンド・パッドの両方として機能する单一の金属層 116 が半導体基板 122 の下側表面上に形成される。ドレイン・コンタクト / ドレイン・ボンド・パッド 116 は、例えば、ニッケル、チタン、タングステン及び / 又はアルミニウムのような金属並びに / 或いは合金、並びに / 或いは、これら及び / 又は類似物質の薄い積層スタックを含み得る。

30

#### 【0083】

低濃度にドーピングされた n 型 (n-) の炭化ケイ素ドリフト領域 124 は基板 122 の上側表面上に設けられる。n 型炭化ケイ素ドリフト領域 124 は、例えば、炭化ケイ素基板 122 上のエピタキシャル成長によって形成され得る。n 型炭化ケイ素ドリフト領域 124 は、例えば、 $1 \times 10^{14} \sim 5 \times 10^{16}$  ドーパント /  $\text{cm}^3$  のドーピング濃度を有することができる。n 型炭化ケイ素ドリフト領域 124 は、例えば、基板 122 上に垂直方向の高さ 3 ~ 100 ミクロンを有する厚い領域であり得る。図 5C ではドリフト領域 124 の厚さが一定の拡大比率に従って描かれているものではないことは理解されるであろう。図 5C に示されていないが、幾つかの実施例においては、n 型炭化ケイ素ドリフト領域 124 の上側部分に電流拡散層を提供するために、n 型炭化ケイ素ドリフト領域 124 の上側部分は、その下側部分より高濃度（例えば、 $1 \times 10^{16} \sim 1 \times 10^{17}$  ドーパント /  $\text{cm}^3$  のドーピング濃度）にドーピングされ得る。

40

50

## 【 0 0 8 4 】

p型ウェル領域126がn型ドリフト領域124の上側部分に形成される。それから、高濃度にドーピングされたn型( $n^+$ )の炭化ケイ素ソース領域128が、例えば、イオン・インプランテーションによってウェル領域126の上側部分に形成され得る。チャネル領域127はウェル領域126の側方において定められる。基板122、ドリフト領域124、ウェル領域126、及び、ソース領域128は共にMOSFET110の半導体層構造120を構成することができる。

## 【 0 0 8 5 】

n型ソース領域128が形成された後、(それら全体でゲート絶縁パターンを構成する)複数のゲート絶縁フィンガー132が半導体層構造120の上側表面上に形成され得る。各ゲート絶縁フィンガー132は、例えば、酸化シリコン、窒化シリコン、酸窒化ケイ素等のような誘電体物質の細長いストリップを含み得る。ポリシリコンのゲート・フィンガー134のようなゲート・フィンガー134は、それぞれのゲート絶縁フィンガー132上に形成される。ゲート・フィンガー134及びゲート絶縁フィンガー132は全体でゲート電極構造130を構成する。上記のように、ソース領域128と各ゲート・フィンガー134の直ぐ下にあるドリフト領域124の部分との間にあるウェル領域126の上下方向に延びる部分は、チャネル領域127を構成する。十分なバイアス電圧がゲート・フィンガー134に印加されるときに、チャネル領域127はn型ソース領域128をドリフト領域124に電気的に接続する。バイアス電圧がゲート・フィンガー134に印加されるときに、電流はn型ソース領域128からチャネル領域127を通ってドリフト領域124に、そして、ドレイン・コンタクト116まで流れることができる。

10

## 【 0 0 8 6 】

複数の誘電体フィンガー152を含むことができる金属間誘電体パターン150は、間隔を置いて配置された誘電体物質のストライプの形で形成される。金属間誘電体パターン150は、第1のリフロー可能でない誘電体パターン154及び第2のリフローされた誘電体パターン158を含む多層誘電体パターンを含み得る。後で詳しく述べるように、第2のリフローされた誘電体パターン158は、第2のリフロー可能な誘電体パターン156を形成し、それからデバイスを加熱して第2のリフロー可能な誘電体パターン156の材料をリフローすることによって形成される。第2のリフロー可能な誘電体パターン156は、図5Cに示されず、図6Dにおいて示される(図6A～図6Eは図5Cの金属間誘電体パターン150を形成する方法を例示する)。

20

## 【 0 0 8 7 】

第1のリフロー可能でない誘電体パターン154は、幾つかの実施例においては、ゲート・フィンガー134の露出した上面に、そして、ゲート絶縁フィンガー132及びゲート・フィンガー134の露出した側面上に形成され得る。したがって、第1のリフロー可能でない誘電体パターン154は、それぞれのゲート・フィンガー134の上面及び側面並びに下にあるゲート絶縁フィンガー132の側面を覆う、複数のリフロー可能でない誘電体フィンガー152Aを含むことができる。第1のリフロー可能でない誘電体パターン154は、例えば、酸化シリコン・パターン、窒化シリコン・パターン、又は、それらがリフロー可能なパターンでない酸化シリコン・パターン及び窒化シリコン・パターンの組合せであり得る。例えば、アンドープの、燐だけによってドーピングされた、又は、燐及び少量だけのホウ素によってドーピングされた酸化シリコン・パターンがリフロー可能でないパターンであり得る。しかしながら、多種多様な他のリフロー可能でない誘電体物質(例えば、酸化アルミニウム、酸化マグネシウム、或いは、ケイ酸塩又は酸窒化物混合誘電体を形成するこれら又は他の酸化物及び窒化物と二酸化ケイ素の混合物)が第1のリフロー可能でない誘電体パターン154を形成するために用い得ると理解されるであろう。適切な材料は、比較的大きい(例えば、5eVより大きい)バンドギャップ及び比較的高い破壊電圧を示すことができる。幾つかの実施例においては、第1のリフロー可能でない誘電体パターン154は、リフロー可能でない誘電体物質の複数の層を含むことができる。

30

40

50

## 【0088】

上記のように、本発明の実施例に従う金属間誘電体パターンは、リフロー可能でない誘電体層／パターン及びリフロー可能な誘電体層／パターンの両方を含むことができる。その温度がガラス転移温度に接近するか又は超えるとき、リフロー可能な誘電体層及びパターンは低粘性を有する。

## 【0089】

第1のリフロー可能でない誘電体パターン154は、ゲート・フィンガー134上、及び、その下にあるゲート絶縁フィンガー132上にコンフォーマルに形成され得る。したがって、第1のリフロー可能でない誘電体物質154は、比較的均一な厚さを有することができる。幾つかの実施例においては、第1のリフロー可能でない誘電体パターン154の厚さは、デバイスの動作中、金属間誘電体パターン150の破壊を防止するには十分な厚さであり得る。このような実施例においては、第2のリフローされた誘電体パターン158が極めて薄い領域を有する場合であっても、第1のリフロー可能でない誘電体パターン154はゲート・フィンガー134をソース・メタライゼーション構造160から切り離すことができ、MOSFET110の通常動作中の破損を防止するには十分な厚さを有することができる。例えば、リフローされた誘電体物質パターン158の最小厚さは、幾つかの実施例では少なくとも0.1ミクロンであり得、又は他の実施例では少なくとも0.2ミクロンであり得る。他の実施例においては、第1のリフロー可能でない誘電体パターン154の厚さは金属間誘電体パターン150の破壊を防止するには十分な厚さより少ない場合もあるが、第1のリフロー可能でない誘電体パターン154及び第2のリフローされた誘電体パターン158を合わせた最小限の厚さは破壊を防止するには十分であり得る。更に他の実施例においては、第1のリフロー可能でない誘電体パターン154の厚さは、ゲート絶縁フィンガー132の厚さ以上であり得る。

10

20

30

## 【0090】

幾つかの実施例においては、第2のリフロー可能な誘電体パターン156は、第1のリフロー可能でない誘電体パターン154の上に直接形成され得る。上記のように、第1のリフロー可能でない誘電体パターン154は、それぞれのゲート・フィンガー134の上面及び側面、並びに、その下にあるゲート絶縁フィンガー132の側面を覆う複数のリフロー可能でない誘電体フィンガー152Aを含むことができる。第2のリフロー可能な誘電体パターン156は、それぞれのリフロー可能でない誘電体フィンガー152Aの上面及び側面を覆う複数のリフロー可能な誘電体フィンガー152B（図6Dを参照）を含むことができる。第2のリフロー可能な誘電体パターン156は、例えば、BPSGであり得る。BPSGは、例えば、500～1000の間の温度でリフロー可能な、ホウ素及び燐がドーピングされた酸化シリコン材料である。ホウ素及び燐以外の他の混合元素が流動可能なガラスにおいて用いられ得、且つ／又は、他の流動可能な誘電体物質が用いられ得る。第2のリフロー可能な誘電体パターン156は、その中の誘電体物質をリフローして第2のリフローされた誘電体パターン158を形成するために加熱され得る。第2のリフローされた誘電体パターン158は、複数の誘電体フィンガー152Cを含むことができる。代表的な実施例においては、第2のリフロー可能な誘電体パターン156の厚さに対するリフロー可能でない誘電体パターン154の厚さの比率は、2:1、1:2、1:4、1:7、及び、1:10であり得る。すなわち、第2のリフロー可能な誘電体パターン156の厚さに対するリフロー可能でない誘電体パターン154の厚さの比率は、2:1と1:10との間にあり得る。大部分の用途では、リフロー可能でない誘電体パターン154の厚さは、第2のリフロー可能な誘電体パターン156の厚さより小さい。

40

## 【0091】

図6A～図6Eを参照してより詳細に述べられるように、第2のリフロー可能な誘電体パターン156は第1のリフロー可能でない誘電体パターン154の上にコンフォーマルに形成され得、それから、第2のリフロー可能な誘電体パターン156を例えば800～1000の温度まで加熱することによってリフローされ得、第2のリフロー可能な誘電体パターン156を第2のリフローされた誘電体パターン158に変換することができ

50

る。第2のリフロー可能な誘電体パターン156がリフローされるときに、第2のリフローされた誘電体パターン158を構成するリフローされた誘電体物質の表面張力は、図5Cに示されるように、第2のリフローされた誘電体パターン158に一般に半橿円又は半円形の横断面を有するようにさせることができる。ゲート・フィンガー134の上側端に最も近い第2のリフローされた誘電体パターン158の部分（1つのそのような部分は図5Cの点線の円で囲まれている）の厚さは、第2のリフローされた誘電体パターン158の他の部分の厚さより実質的に小さい場合がある。例えば、図5Cの小部分の（ソース・メタライゼーション構造160を省略した）拡大図である図5Eに示されるように、ゲート・フィンガー134の上側表面端に隣接する第2のリフローされた誘電体パターン158の厚さT1は、第2のリフローされた誘電体パターン158の上側部分の厚さT2よりも2倍、3倍、4倍、5倍、又は、6倍である場合がある。第2のリフローされた誘電体パターン158の下に第1のリフロー可能でない誘電体パターン154を設けることは、ゲート・フィンガー134の上側端に隣接する金属間誘電体パターン150の総厚さが破損を防止するには十分であり得ることを確実にできる。例えば、図5Eに示されるように、ゲート・フィンガー134の上側端における金属間誘電体パターン150の厚さを示す距離T3は、破損を回避するには十分であるように設計され得る。10

#### 【0092】

幾つかの実施例においては、金属間誘電体パターン150の最大厚さは、ゲート・フィンガー134の中心の上面の上（すなわち、T4）にある場合がある。金属間誘電体パターン150の最大厚さが、ゲート・フィンガー134の上側端に隣接する（すなわち、ゲート・フィンガー134の上の角に隣接する）場合がある。本発明の種々の実施例においては、金属間誘電体パターン150の最小厚さ（典型的には、図5EのT3）に対するゲート・フィンガー134の中心の上面より上の金属間誘電体パターン150の厚さ（すなわち、T4）の比率は、8：1より小さい、6：1より小さい、5：1より小さい、4：1より小さい、3：1より小さい、又は、更に2：1より小さい場合さえあり得る。そして、これらの実施例の各々において少なくとも1：1であり得る。20

#### 【0093】

幾つかの実施例においては、リフロー可能でない誘電体パターン154及び第2のリフローされた誘電体パターン158の組合せは、図3の実施例におけるリフローされたBPSG金属間誘電体パターン50Aの厚さとほぼ同じ厚さを有することができる。したがって、第2のリフローされた誘電体パターン158は図3のリフローされたBPSG金属間誘電体パターン50Aより小さい厚さを有することができ、それ故、リフロー中に第2のリフロー可能な誘電体パターン156はさほど横には拡がらなく、それにより、ギャップ140のための適切な幅を維持することができる。したがって、本発明の実施例に従う金属間誘電体パターン150は、完全にリフロー可能な金属間誘電体パターンと関連する潜在的に不利な点を減らすか又は最小化しつつ、完全にリフロー可能な金属間誘電体パターンの有利な点を有することができる。30

#### 【0094】

再び図5Cを参照して、隣り合うリフローされた誘電体フィンガー152Cの間のギャップ140においてn型ソース領域128が露出する。上記のように、炭化ケイ素パワーデバイスにおいては、各ギャップ140の幅は、およそ1から5ミクロン程度のような非常に狭い場合があり得る。更に、技術が発達し続けるにつれて、ギャップ140はより小さくなっており、近い将来、0.5ミクロン程度の小さいギャップ140が市販装置で実現され得る。そのような小ギャップ140では、上側ソース・メタライゼーション構造160内に隙間を形成すること無く上側ソース・メタライゼーション構造160を充填する（後述する）ことが困難な場合がある。40

#### 【0095】

第2のリフローされた誘電体パターン158は丸みのある稜線を有し得、したがって、角度 $\alpha_1$ 及び $\alpha_2$ （図5Eを参照）はより小さくなり得る。そして、結果として完全に拡50

散バリア層の金属で充填することがより容易なギャップ 140 が作られる。したがって、MOSFET 110 は、ギャップ 140 内にある拡散バリア層 162 の部分における隙間の形成の影響をより受け難くなり得る。

#### 【0096】

上側ソース・メタライゼーション構造 160 は、金属間誘電体パターン 150 上に、そして、ギャップ 140 において露出する半導体層構造 120 のウェル領域 126 及び n 型ソース領域 128 上に形成される。上側ソース・メタライゼーション構造 160 は、拡散バリア層 162、及び、拡散バリア層 162 の上に形成されるソース・コンタクト層 164 を含む。拡散バリア層 162 は、隣接層に関して比較的不活性で、その中を通る他の材料の拡散を遅延させるか又は実質的に防止する金属又は金属を含む層であり得る。拡散バリア層 162 は、例えば、チタン、タンゲステン、タンタル、ニッケル、ハフニウム、及び / 又は、インジウムを含む連続導電層を含み得る。例えば、拡散バリア層 162 は、チタン、タンタル、ニッケル、ハフニウム、タンゲステン、窒化チタン、窒化タンゲステン、酸化インジウム、又は、窒化タンタル、或いは、上述した材料の合金を含むことができる。拡散バリア層 162 は、半導体層構造 120 の露出部分上に（例えば、ウェル領域 126 及びソース領域 128 上に）、そして、金属間誘電体パターン 150 上にコンフォーマルに形成され得る。拡散バリア層 162 は、典型的には、ソース・コンタクト層 164 に含まれる金属より伝導性の低い金属で形成される。このように、拡散バリア層 162 は、上側ソース・メタライゼーション構造 160 の抵抗に与える影響を減らすために比較的薄い層であり得る。

10

#### 【0097】

ソース・コンタクト層 164 は拡散バリア層 162 上にコンフォーマルに形成され得る。ソース・コンタクト層 164 は、例えば、ニッケル、チタン、タンゲステン及び / 又はアルミニウムのような金属及び / 又は合金、並びに / 或いは、これら及び / 又は類似物質の薄い積層スタックを含み得る。幾つかの実施例においては、ソース・コンタクト層 164 はアルミニウム層を含み得る。これは、アルミニウムは比較的安価で伝導性が高く堆積が容易で、他の金属のための良好なシード層 (seed layer) として機能することができるからである。ソース・コンタクト層 164 は、拡散バリア層 162 よりかなり厚くできる。ソース・コンタクト層 164 の厚さは、上側ソース・メタライゼーション構造 160 の（低いことが望ましい）抵抗とソース領域 128 の上にあるソース・コンタクト層 164 の部分において形成される傾向がある鍵穴 166 の深さの間のトレードオフを反映し得る。一般的に言って、ソース・コンタクト層 164 の厚さが増加するにつれて、ソース・コンタクト層 164 の抵抗は増加するが、鍵穴 166 の平均深さは減らされる。図 5C に示されるように、ゲート電極構造 130 はワイド・バンドギャップ半導体層構造 120 と金属間誘電体パターン 150との間にあって、金属間誘電体パターン 150 はゲート電極構造 130 とソース・メタライゼーション構造 160 との間にある。

20

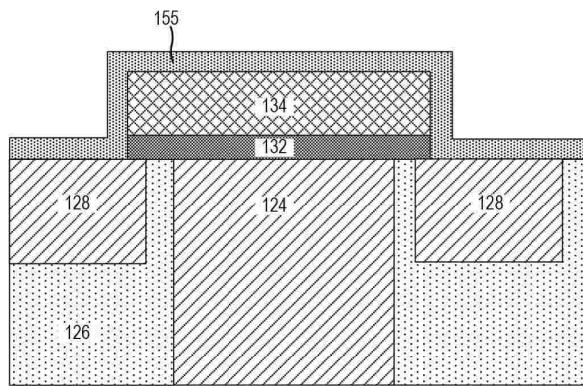

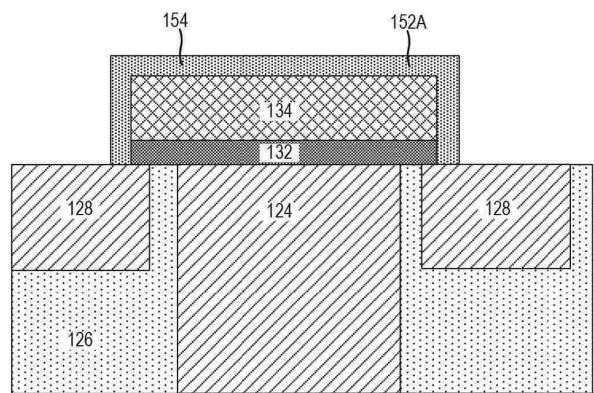

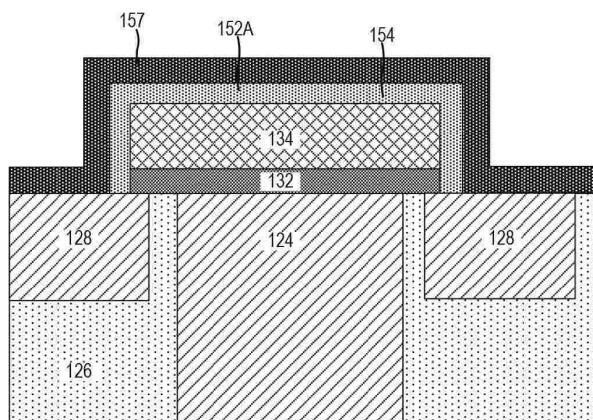

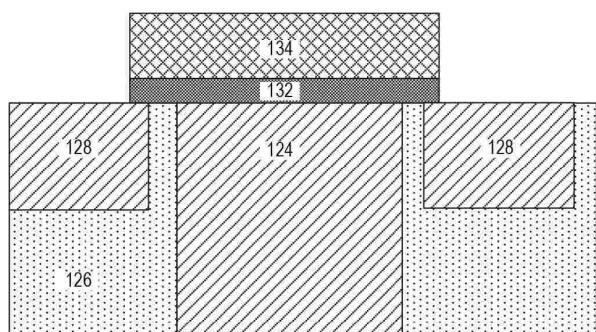

#### 【0098】

図 6A ~ 図 6E は、図 5A ~ 図 5E の MOSFET の金属間誘電体パターン 150 の形成を例示する概略断面図である。図 6A ~ 図 6E は図 5E の拡大図に対応し、図面の簡素化のために単一のユニット・セルを示す。

30

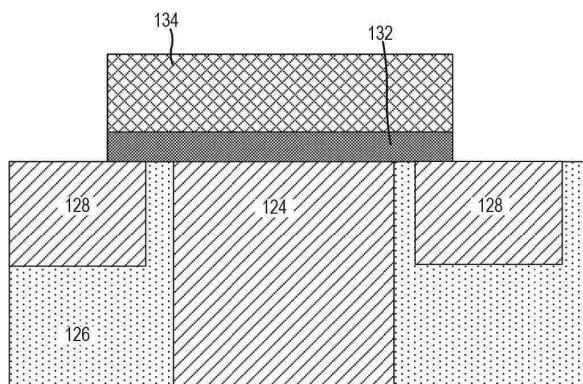

#### 【0099】

図 6A に示されるように、リフロー可能でない誘電体層 155 が、ゲート・フィンガー 134 とゲート絶縁フィンガー 132 の側壁とを覆うように、当該デバイスの上面にコンフォーマルに形成される。図 6B に示されるように、それから、リフロー可能でない誘電体層 155 は第 1 のリフロー可能でない誘電体パターン 154 を形成するために選択的にエッチングされる。第 1 のリフロー可能でない誘電体パターン 154 は複数の誘電体フィンガー 152A (1 つだけが図 6B に示される) を含み、複数の誘電体フィンガー 152A は、それぞれのゲート・フィンガー 134 とそれぞれのゲート絶縁フィンガー 132 の側壁とを覆う。図 6C に示されるように、第 1 のリフロー可能でない誘電体パターン 154 の上に、リフロー可能な誘電体層 157 がコンフォーマルに形成される。図 6D に示

40

50

されるように、それから、リフロー可能な誘電体層 157 は第2のリフロー可能な誘電体パターン 156 を形成するために選択的にエッチングされる。第2のリフロー可能な誘電体パターン 156 は、それぞれの誘電体フィンガー 152A を覆う複数の誘電体フィンガーパターン 152B (1つだけが図 6D に示される) を含む。図 6E に示されるように、最後に、当該デバイスは、例えば、500 ~ 1000 の間の温度まで加熱される。その結果、第2のリフロー可能な誘電体パターン 156 の材料をリフローし、第2のリフロー可能な誘電体パターン 156 を第2のリフローされた誘電体パターン 158 に変換し、個々のリフロー可能な誘電体フィンガー 152B をリフローされた誘電体フィンガー 152C に変換する。最後に、第2のリフローされた誘電体パターン 158 上に、そして、ウェル領域 126 及びソース領域 128 の露出部分上に、拡散バリア層 162 がコンフォーマルに形成され得る。上述の通り、金属間誘電体パターン 150 が第1のリフロー可能でない誘電体パターン 154 を含むことは、金属間誘電体パターン 150 の最小厚さが、デバイス動作中の破損を防止するには十分であることを確実にすることができる。

#### 【0100】

図 6A ~ 図 6E を参照して上に説明した金属間誘電体パターン 150 のための製造プロセスにおいて、第2のリフロー可能な誘電体パターン 156 は、最初に、ソース領域 128 を露出させるためにエッチングされ、それから、第2のリフローされた誘電体パターン 158 を形成するためにリフローされる。しかしながら、他の実施例においては、第2のリフロー可能な誘電体層 157 がリフローされた誘電体層を形成するためにリフローされ得ること、及び、リフローされた誘電体層がそれから、ソース領域 128 を露出させる第2のリフローされた誘電体パターン 158 を形成するようにエッチングされ得ることは理解されるであろう。第2のリフロー可能な誘電体層 157 をリフローすること（すなわち、エッチングの前にリフローを実行すること）は特定の用途において有利であり得る。なぜならば、それにより、リフロー・プロセスの間に横に膨張するリフローされた誘電体層の複数の部分の除去を可能にし、ソース領域 128 を露出させる金属間誘電体パターン 150 の開口部の適切な寸法を維持することができるからである。

#### 【0101】

図 7A 及び図 7B は、図 5A ~ 図 5E のMOSFET 110 の金属間誘電体パターン 150 を形成する他の方法を例示する概略断面図である。図 7A に示されるように、複数のゲート絶縁フィンガー 132 及び複数のゲート・フィンガー 134 を含むゲート電極構造が半導体層構造 120 の上側表面上に形成される。ゲート絶縁フィンガー 132 及びゲート・フィンガー 134 は、図 6A ~ 図 6E の実施例に含まれる、対応するゲート絶縁フィンガー 132 及びゲート・フィンガー 134 より幅広であり得、ゲート・フィンガー 134 は、図 6A ~ 図 6E の実施例に含まれる、対応するゲート・フィンガー 134 より厚くできる。次に、図 7B に示されるように、リフロー可能でない誘電体パターン 154 が、ゲート・フィンガー 134 の露出した上面及び側面を酸化させることによって形成される。ゲート・フィンガー 134 は、例えば、ホウ素をドーピングされないポリシリコンのゲート・フィンガー 134 を含むことができる。それ故、ゲート・フィンガー 134 の酸化処理は各ゲート・フィンガー 134 の上側部分及び側面部分をそれぞれのリフロー可能でない誘電体フィンガー 152A に変換する。酸化プロセスは、各ゲート・フィンガー 134 上に所望の厚さを有する第1のリフロー可能でない誘電体パターン 154 を形成するために、各ゲート・フィンガー 134 の外側部分の所定の厚さを酸化させるように設計され得る。酸化プロセスは、ポリシリコンを酸化させるには十分高いが炭化ケイ素を酸化させるには十分高くない温度で実施され得る。その結果、露出した炭化ケイ素のソース領域 128 は酸化プロセスの間には感知できるほどには酸化されない。第1のリフロー可能でない誘電体パターン 154 が酸化プロセスによって形成された後、第2のリフロー可能な誘電体パターン 156 が形成され得、それから、図 6C ~ 図 6E を参照して上に説明された方法でリフローされ得る。注目すべきことに、第1のリフロー可能でない誘電体パターン 154 を形成するために酸化プロセスを用いることによって、図 6B を参照して上に説明されたエッチングステップは省略され得、それにより、製造プロセスを単純化することが

10

20

30

40

50

できる。

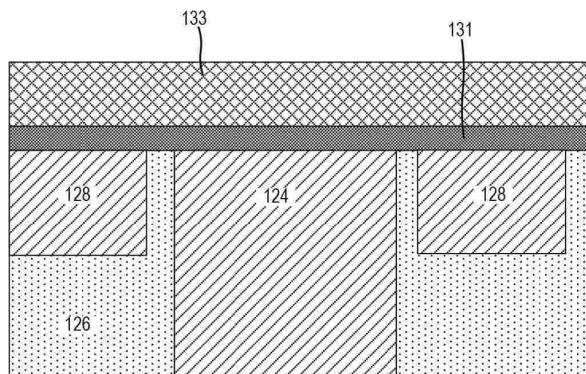

#### 【0102】

図8A～図8Fは、図5A～図5EのMOSFET110の金属間誘電体パターン150の代わりに使われ得る金属間誘電体パターン250を形成する方法を例示する断面図である。図8Aに示されるように、ゲート絶縁層131及びゲート・フィンガー層133が、半導体層構造120上に形成され得る。次に、図8Bに示されるように、リフロー可能でない誘電体層255（例えば、二酸化ケイ素層）がゲート・フィンガー層133上に形成される。リフロー可能でない誘電体層255は、例えば、プラズマ強化化学蒸着、低圧化学蒸着、又は、ゲート電極構造130の上面の酸化によって形成され得る。図8Cに示されるように、ゲート絶縁層131、ゲート・フィンガー層133、及び、リフロー可能でない誘電体層255をエッティングしてソース領域128を露出させるためにエッティングのステップが実行される。それにより、ゲート絶縁層131、ゲート・フィンガー層133、及び、リフロー可能でない誘電体層255を、複数のゲート絶縁フィンガー132、複数のゲート・フィンガー134、及び、複数の誘電体フィンガー252Aを含む第1のリフロー可能でない誘電体パターン254に変換する。なお、本実施例においては、誘電体フィンガー252Aは、ゲート・フィンガー134のそれぞれの上面のみを覆い、ゲート・フィンガー134の側面を覆わないことに注意すべきである。

10

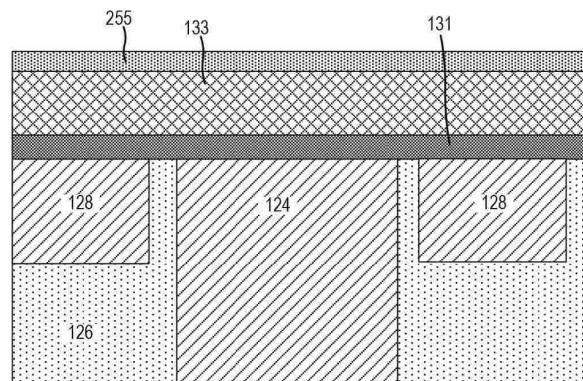

#### 【0103】

図8Dに示されるように、第2のリフロー可能な誘電体層257が当該デバイス上にコンフォーマルに形成される。図8Eに示されるように、それから、第2のリフロー可能な誘電体層257は、第2のリフロー可能な誘電体パターン256を形成するために選択的にエッティングされる。第2のリフロー可能な誘電体パターン256はそれぞれの誘電体フィンガー252Aを覆う複数のリフロー可能な誘電体フィンガー252Bを含む。図8Fに示されるように、最後に、第2のリフロー可能な誘電体パターン256を第2のリフローされた誘電体パターン258に変換するために第2のリフロー可能な誘電体パターン256の材料をリフローするべく、当該デバイスは、例えば、500～1000の間の温度まで加熱される。第2のリフローされた誘電体パターン258は複数のリフロー可能な誘電体フィンガー252Cを含む。金属間誘電体パターン250を形成するためのこの技術は、更に、図6A～図6Eを参照して上に説明した技術より、必要とするエッティングステップを1つ少なくし得る。或いは、他の実施例においては、第2のリフロー可能な誘電体層257がリフローされ得、それから、第2のリフローされた誘電体パターン258を形成するためにエッティングされ得ることは理解されるであろう。

20

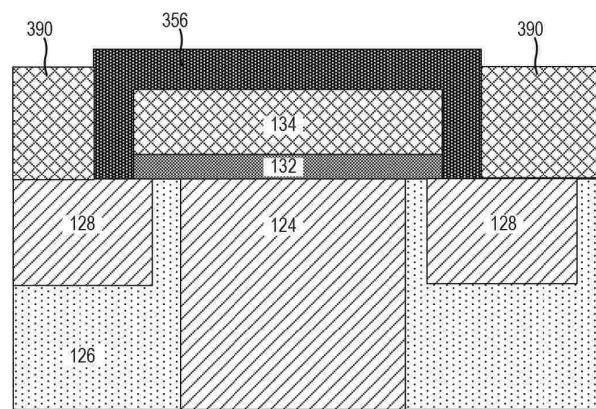

#### 【0104】

本発明の更なる実施例によれば、リフロー・プロセスの間に犠牲となる構造を用いて形成されるリフローされた金属間誘電体パターンを含むパワー半導体デバイスが提供される。特に、犠牲となる構造は、リフロー可能な誘電体パターンの形成の前か後に、デバイス上に堆積させることができる。これらの犠牲となる構造は、リフロー・プロセスの間は適所に残されて、（1）リフロー・プロセスの間はリフロー可能な誘電体物質の側方流動を制限し、且つ／又は、（2）リフロー・プロセスが完了した後、ゲート・フィンガー134の側端に隣接するリフロー可能な誘電体物質の量を増加させるために用いることができる。そのようなパワー半導体デバイスを形成する方法が図9A～図9Dに図示される。

30

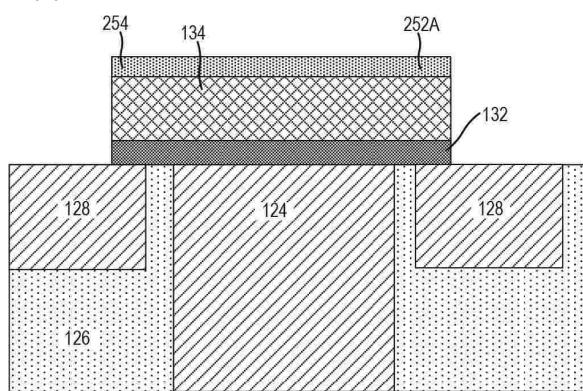

#### 【0105】

図9Aに示されるように、半導体層構造120は、ゲート絶縁フィンガー132及びその上に形成されるゲート・フィンガー134を有して形成され得る。図9Bを参照すると、リフロー可能な誘電体層（図示せず）が、デバイスの上側表面を覆うように形成され、それから、それぞれのゲート・フィンガー134の上面及び側面と、それぞれのゲート絶縁フィンガー132の側面とを覆う誘電体フィンガーを含むリフロー可能な誘電体パターン356を形成するためにエッティングされる。次に、犠牲となるダム390がギャップ140内に形成される。犠牲となるダム390はギャップ140に選択的に堆積され得る。又は、その代わりに、犠牲となる層がデバイスの上面にコンフォーマルに形成され得、

40

50

それから、犠牲となるダム 390 を形成するために選択的にエッチングされ得る。ポリシリコンは BPSG リフローされた誘電体パターンに対して高い選択性をもってエッチングされ得るので、代表的な実施例においては、犠牲となるダム 390 はポリシリコンを含むことができる。

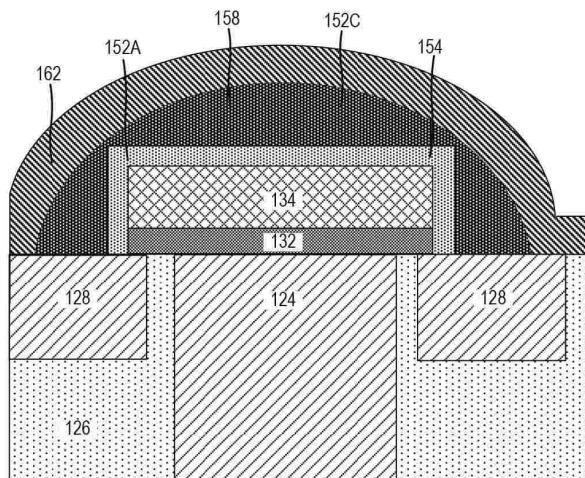

#### 【0106】

図 9C に示されるように、それから、デバイスはリフロー可能な誘電体パターン 356 をリフローするために加熱され得、それにより、リフロー可能な誘電体パターン 356 を複数の誘電体フィンガー 352C を含むリフローされた誘電体パターン 358 に変換する。上記のように、そのようなリフロー・プロセスは、一般には、リフロー可能な誘電体物質に横に広がらせた形状を変えさせて半楕円又は半円形の横断面を有するようにさせる。しかしながら、犠牲となるダム 390 は、リフロー可能な誘電体物質が横に拡がることを妨げる。それ故、ギャップ 140 の大きさを維持することができる。このように、リフローされた誘電体物質パターン 358 の下部は、図 9C に示されるように、実質的に垂直な側壁を有する。加えて、リフロー可能な誘電体物質が横に拡がることを防ぐので、より多くのリフロー可能な誘電体物質がゲート・フィンガー 134 の側壁に沿って保たれる。このことは、ゲート・フィンガー 134 の側端に沿う誘電体フィンガー 352C の厚さを増加させるように作用する。したがって、犠牲となるダム 390 の使用は、金属間誘電体パターン 150 がリフロー可能な誘電体物質を用いて形成されるときに起こり得る、図 3 を参照して上に説明した 2 つの潜在的な問題を減らすか又は防止することができる。図 9D を参照すると、リフロー・プロセスが完了した後、犠牲となるダム 390 は選択性エッチングによって取り除かれ得る。上の説明においてはリフロー可能な誘電体パターン 356 が形成された後に犠牲となるダム 390 が形成されるが、他の実施例においては、リフロー可能な誘電体パターン 356 が形成される前に犠牲となるダム 390 が形成され得る点に留意する必要がある。

10

#### 【0107】

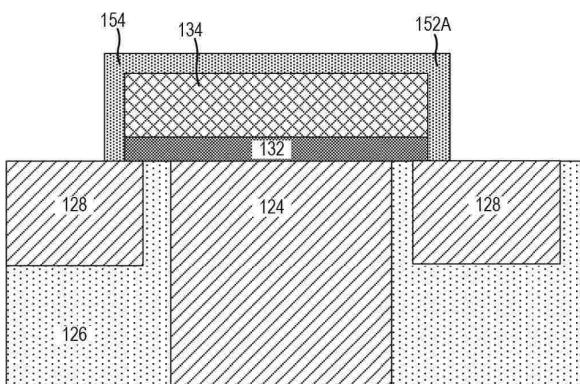

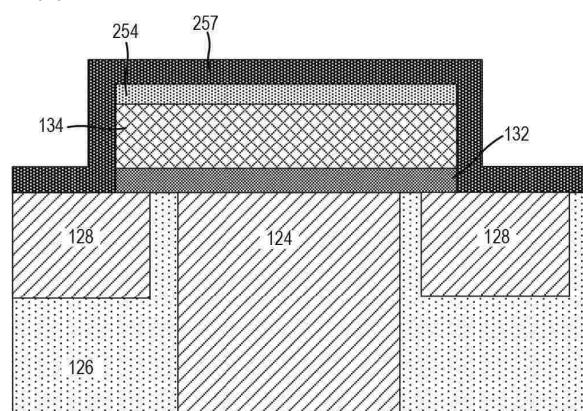

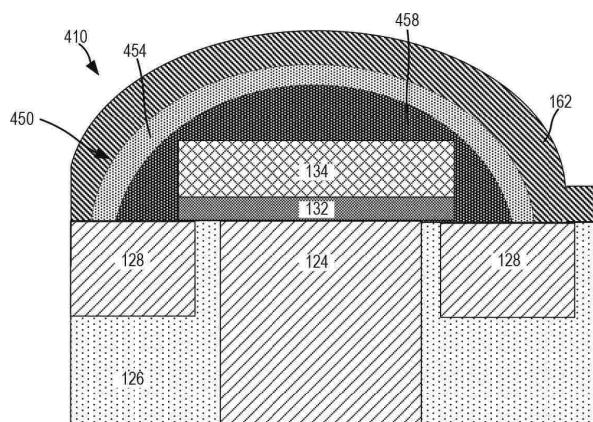

リフロー可能でない誘電体パターン及びリフロー可能な誘電体パターンの両方を有する金属間誘電体パターンを含む実施例についての上の説明において、リフロー可能でない誘電体パターンがゲート・フィンガーとリフロー可能な誘電体パターンとの間にあるよう、リフロー可能でない誘電体パターンはリフロー可能な誘電体パターンの前に形成される。しかしながら、本発明の実施例は、そのようなことには限定されないことは理解されるであろう。特に、リフロー可能でない誘電体パターン及びリフロー可能な誘電体パターンの両方を有する金属間誘電体パターンを含む上に説明された実施例の各々は、リフロー可能な誘電体パターン（又は層）が最初に（例えば、直にゲート・フィンガー上に）形成され、それからリフローされ、そして、リフロー可能でない誘電体パターンがリフローされた誘電体パターンの上に形成されるように、変更され得る。例えば、図 10 は、図 5A～図 5E の MOSFET 110 の変更版である MOSFET 410 のユニット・セルの（そのソース・メタライゼーションの一部の図示が省略された）概略断面図である。図 10 に示されるように、MOSFET 410 の金属間誘電体パターン 450 は、直接ゲート・フィンガー 134 の上に形成されるリフローされた誘電体パターン 458 及びリフローされた誘電体パターン 458 の上に形成されるリフロー可能でない誘電体パターン 454 を含む。

30

#### 【0108】

上に説明した MOSFET はその上側表面上のソース・コンタクト層 164 及びその底面上のドレイン・コンタクト 116 を有する n 型デバイスであるが、p 型デバイスでは、これらの位置が逆転することは理解されるであろう。更に、上に説明したパワー MOSFET 110、及び、本願明細書において説明した他のデバイスが炭化ケイ素ベースの半導体デバイスであるとして示されるが、本発明の実施例がそれらに限定されないことは理解されるであろう。その代わりに、半導体デバイスは、例えば、窒化ガリウム・ベースの半導体デバイス、及び、II～VI 族化合物半導体デバイスを含む、パワー半導体デバイスの用途に適するあらゆるワイド・バンドギャップ半導体をも含むことができる。

40

50

**【 0 1 0 9 】**

本願明細書において説明される金属間誘電体パターンを形成するリフロー可能でない、及び／又は、リフロー可能な誘電体層／パターンは各々、単層を含んでも、多層構造を含んでもよいこともまた理解されるであろう。多くの用途において、多層構造は、拡散バリアとして、及び／又は、周囲の層に化学的適合性を提供するために、より効果的であり得る。

**【 0 1 1 0 】**

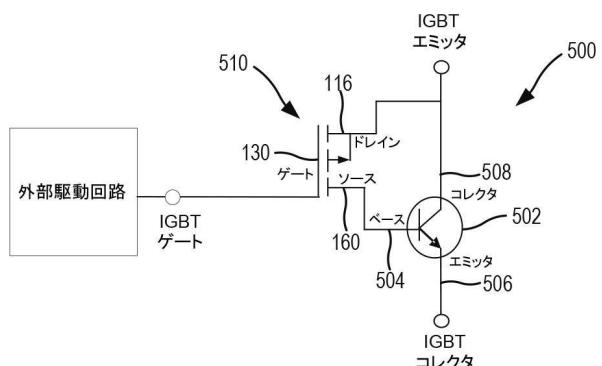

本願明細書において開示される改良された金属間誘電体パターンが縦型パワーMOSFETデバイス以外のパワー半導体デバイスにおいて用いられ得ることも理解されるであろう。例えば、これらの金属間誘電体パターンが、パワーIGBTデバイスで用いられることもできる。パワーIGBTデバイスは、当業者に知られているように、BJT及びMOSFETの組合せであって、MOSFETは、BJTを電流制御デバイスから電圧制御デバイスへ転換するためにBJTのベースへフィードする。

10

**【 0 1 1 1 】**

図11Aは、本発明の複数の実施例に従うIGBT500の小部分の概略断面図である。図11Aに示されるように、IGBT500は、ベース504、エミッタ506、及びコレクタ508を有するp-n-p炭化ケイ素BJT502を含む。IGBT500は、ゲート130、ソース160、及び、ドレイン116を有する炭化ケイ素MOSFET510を更に含む。MOSFET510のソース160はBJT502のベース504に電気的に接続され、炭化ケイ素MOSFET510のドレイン116はBJT502のコレクタ508に電気的に接続される。慣例により、BJT502のコレクタ508はIGBT500の「エミッタ」であり、BJT502のエミッタ506はIGBT500の「コレクタ」であり、MOSFET510のゲート130はIGBT500の「ゲート」である。

20

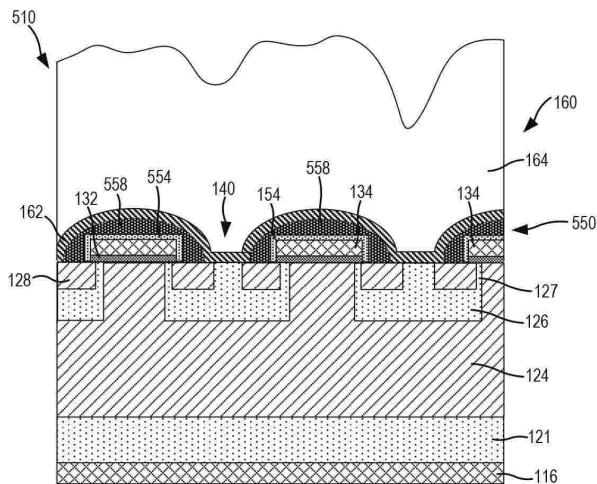

**【 0 1 1 2 】**

図11Bは、図11AのIGBT500の小部分の概略横断面図である。図11Bに示されるように、IGBT500は、例えば、高濃度にドーピングされた(p<sup>+</sup>)p型炭化ケイ素層121の上に形成され得る。P型層121は、例えば、炭化ケイ素基板上にエピタキシャル成長され得、基板はその後で除去され得る。p<sup>+</sup>層121は、IGBT500のコレクタとして(及び、BJT502のエミッタ506としても)機能する。低濃度にドーピングされたn型(n<sup>-</sup>)炭化ケイ素ドリフト領域124が、BJT502のベースとして、そして、MOSFET510のソースとして機能するP型層121上に設けられている。中程度にドーピングされたp型ウェル領域126が、n型ドリフト領域124の上側部分に設けられている。各p型ウェル126の上側部分はp型ドーパントによってより高濃度にドーピングされて、BJT502のコレクタとしても機能する高濃度にドーピングされたp<sup>+</sup>エミッタ領域を形成し得る。高濃度にドーピングされた(n<sup>+</sup>)n型ドレイン領域128もまた、IGBT500のための共用ドレインとして機能する各p型ウェル126の上側部分に形成され得る。ソース・メタライゼーション構造160がp型ウェル領域126及びn<sup>+</sup>ドレイン領域128に接触するために形成され、p<sup>+</sup>炭化ケイ素層121の下側面上にオーミック・コンタクト116が形成される。

30

**【 0 1 1 3 】**

ゲート絶縁フィンガー132及びゲート・フィンガー134は、半導体層構造の上側表面上に設けられている。(各々上で詳述した)第1のリフロー可能でない誘電体パターン554及び第2のリフローされた誘電体パターン558を含む金属間誘電体パターン550が形成される。ギャップ140が隣り合う誘電体フィンガーの間に設けられ、n型ソース領域128及びp型ウェル領域126を露出させる。上側ソース・メタライゼーション構造160は、金属間誘電体パターン550上に、そして、露出したn型ソース領域128及びp型ウェル領域126の上に形成される。上側メタライゼーション構造160は、拡散バリア層162及びソース・コンタクト層164を含む。金属間誘電体パターン550が本願明細書において開示される金属間誘電体パターンの何れとも置き換えられ得るこ

40

50

とは理解されるであろう。

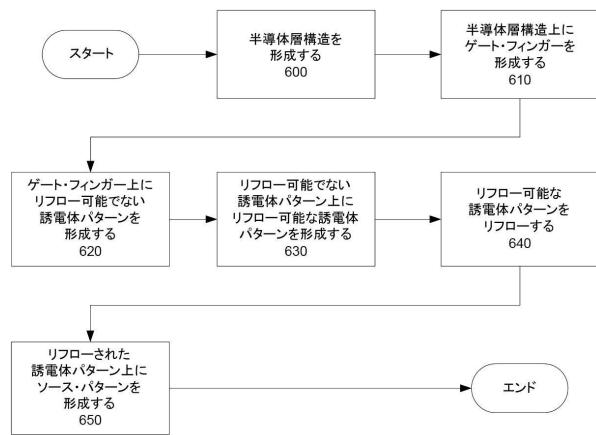

**【0114】**

図12は、本発明の実施例に従ってパワー半導体デバイスを形成する方法のフローチャートである。図12に示されるように、動作は、複数の半導体層を含むワイド・バンドギャップ半導体層構造（「SSL」）の形成（ブロック600）から開始され得る。次に（ブロック610）、例えば、複数のゲート・フィンガーを含むことができる伝導性パターンが、ワイド・バンドギャップ半導体層構造の上側表面上に形成される。（ブロック620）第1のリフロー可能でない誘電体物質パターンが伝導性パターン上に形成される。（ブロック630）第2のリフロー可能な誘電体物質パターンが第1のリフロー可能でない誘電体物質パターン上に形成される。（ブロック640）リフロー可能な誘電体物質パターンが、リフロー可能でない誘電体物質パターン及びリフローされた誘電体物質パターンを含む金属間誘電体パターンを形成するためにリフローされる。（ブロック650）ソース・メタライゼーション構造が、金属間誘電体パターン上に、そして、ワイド・バンドギャップ半導体層構造の露出した上側表面上に形成される。

10

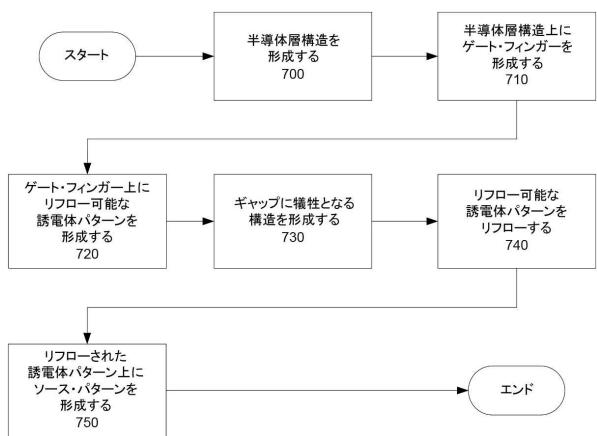

**【0115】**

図13は、本発明の更なる実施例に従ってパワー半導体デバイスを形成する方法のフローチャートである。図13に示されるように、動作は、複数の半導体層を含むワイド・バンドギャップ半導体層構造の形成（ブロック700）から開始され得る。次に（ブロック710）、間隔を置いて配置された複数のゲート・フィンガーが、ワイド・バンドギャップ半導体層構造の上側表面上に形成される。（ブロック720）リフロー可能な誘電体物質パターンが、ゲート・フィンガー・パターン上に形成される。（ブロック730）犠牲となる構造が、リフロー可能な誘電体物質パターンにおけるそれぞれのギャップに形成される。（ブロック740）リフロー可能な誘電体物質パターンが、金属間誘電体パターンを形成するためにリフローされる。（ブロック750）ソース・メタライゼーション・パターンが、金属間誘電体パターンの上に形成される。

20

**【0116】**

したがって、本発明の実施例によれば、破損を回避するための最小限の所望の厚さを依然維持しつつ形状を改善し密度を増加させた金属間誘電体パターンを提供したことにより、ゲートからソースへの電気的短絡に起因するデバイス故障が起き難くなり得たパワーMOSFETが提供され得る。これらの改良された金属間誘電体パターンは、水気又は湿式エッティング液が金属間誘電体パターンを通して拡散する経路を与える継ぎ目を実質的に無くし得、ゲートとソース・メタライゼーションとの間の電気的短絡の可能性を減らす。このように、本発明の実施例によるパワーモノラルトは故障率を低くすることができる。

30

**【0117】**

本発明の実施例に従う技術によって対処される問題は、例えば、炭化ケイ素及び／又は窒化ガリウム・ベースのデバイスのようなワイド・バンドギャップ・パワー半導体デバイスに特有な問題である傾向がある。そのようなデバイスにおいては、隣り合う誘電体フィンガー（例えば、誘電体フィンガー152）間のギャップ（例えば、ギャップ140）は、シリコン・ベースのデバイスのようなナロー・バンドギャップ半導体デバイスに形成されるMOSFETに設けられる対応するギャップより非常に小さくできる。そのことについては、シリコンMOSFETでは、ソース・コンタクト層における隙間が隣り合う誘電体フィンガー間のギャップにおいて形成される傾向が無く、ギャップのサイズが非常に大きいので、形成される如何なる鍵穴も非常に浅い傾向がある。したがって、ナロー・バンドギャップ・デバイスでは、湿式のエッティング液はソース・コンタクト・メタライゼーションを通して浸潤しない傾向があり、それ故、金属間誘電体パターンの密度を高める必要性、及び／又は、金属間誘電体パターンの形状を丸める必要性は弱いか又は無い。

40

**【0118】**

図1を参照して上に説明した従来のパワーモノラルト10の上側ソース・メタライゼーション構造60を通して拡散する腐食性物質の問題に対処する他の潜在的な方法があることには留意する必要がある。1つの例として、ギャップ40のアスペクト比は、例えば

50

、ソース領域28の幅を拡大することによって小さくされ得る。このことにより、上側ソース・メタライゼーション構造60のギャップ充填特性を改善することができる。他の1つの例として、デポジション・パラメータの変更が、ソース・コンタクト層64の材料のギャップ充填特性を改善するために用いられ得る（例えば、デポジション温度の上昇は、改善されたギャップ充填を促進し得る）。更に、ギャップ充填特性は高精度デポジション装置を用いて改善され得る。加えて、より安定した被覆を獲得し隙間を減少させる又は防止するためには、ソース・メタライゼーション構造160の部分（例えば、ギャップ40の部分）を形成するために、例えば、原子層堆積のような、他のデポジション技術が用いられ得る。

#### 【0119】

10

以上、本発明の実施例が示される添付の図面を参照して、本発明について説明した。しかしながら、本発明は、多くの異なる形態で実施され得、本願明細書において記述された実施例に限定されるように解釈されるべきでない。むしろ、これらの実施例は、本開示が完全で行き届いたものとなり本発明の技術範囲を当業者に詳細に伝えるものとなるようという目的で提供されている。図面においては、層及び領域の大きさ及び相対寸法は明確化のために誇張されている場合がある。エレメント又は層が、他のエレメント又は層、「の上に」ある、「に接続される」、又は、「に結合される」と言及されるときには、直接に、他のエレメント又は層、の上にある、それに接続される、又は、それに結合される場合もあり得るが、或いは、間に介在するエレメント又は層が存在する場合もあり得ることは理解されるであろう。対照的に、エレメントが「直に」又は「直接に」他のエレメント又は層、「の上に」ある、「に接続される」、又は、「に結合される」と言及されるときには、間に介在するエレメント又は層は存在しない。本願明細書において使われるとき、「及び／又は」という語句は、関連して列挙されたアイテムの1つ又は複数からなる任意のそして全ての組合せを含む。本開示全体を通して類似の参照符号は類似のエレメントを示す。

#### 【0120】

20

本願明細書において「第1の」と「第2の」という語句が様々の領域、層、及び／又は、エレメントを記述するために使われるが、これらの領域、層、及び／又は、エレメントがこれらの語句によって限定されるべきではないことは理解されるであろう。これらの語句は、1つの領域、層、又は、エレメントを他の領域、層、又は、エレメントと区別するために用いられるだけである。したがって、本発明の要旨を逸脱しない範囲で、以下に記述される第1の領域、層、又は、エレメントは第2の領域、層、又は、エレメントと称され得、同様に、第2の領域、層、又は、エレメントは第1の領域、層、又は、エレメントと称され得る。

30

#### 【0121】

本願明細書において、例えば、「下側の」又は「底の」、及び、「上側の」又は「上の」のような相対的語句は、図面に示されるような1つのエレメントの他のエレメントに対する関係を記述するために使われる場合がある。相対的語句は、図面において描かれる向きだけでなく、デバイスの様々な向きを包含することを意図していることは理解されるであろう。例えば、図中のデバイスが回転されると、他のエレメントの「下」側にあると記載されたエレメントは、この他のエレメントの「上」側に向けられるであろう。したがって、例に取り挙げた語句「下側」は、図の特定の向きによって、「下側」及び「上側」の両方の向きを包含し得る。同様に、図のうちの1つの中のデバイスが回転されると、他のエレメント「の下に」又は「の下方に」として記述されたエレメントは、この他のエレメント「の上方に」向けられるであろう。したがって、例に取り挙げた語句「の下に」又は「の下方に」は上下両方の向きを包含し得る。

40

#### 【0122】

本願明細書において用いられる用語は、具体的な実施例だけを記載するためのものであって、本発明を限定することを意図しない。本願明細書において使われるとき、文脈が別の状況を明確に示さない限り、単数形「1つの(a)」、「ある(an)」、及び、「そ

50

の (the)」は複数形も同様に含むことを意図する。本願明細書において使われるとき、「備える (comprises)」、「備えている (comprising)」、「を含む (includes)」、及び / 又は、「含んでいる (including)」という語句は、記述された特徴、エレメント、及び / 又は、コンポーネントの存在を特定するものであって、1つ若しくは複数の他の特徴、エレメント、コンポーネント、及び / 又は、それらのグループの存在又は付加を排除しないということも更に理解されるであろう。

#### 【0123】

本願明細書において、本発明の実施例は、模式的な図である断面図を参照して記述されている。結果として（例えば、製造技術及び / 又は許容範囲に関して）図示の形態からの変形が想起され得る。したがって、本発明の実施例は、本願明細書において例示される領域の特別な形状に限定されると解釈されるべきではなく、例えば、製造からもたらせられる形状の逸脱を含むことになる。例えば、長方形として図示されたインプラントされた領域は、通常、その端部においては、丸みがあるか湾曲した特徴、及び / 又は、インプラントされた領域からインプラントされていない領域への2値的な変化ではなく、インプラント濃度の勾配を有する。したがって、図面に図示される領域は、本質的に模式的なものであって、それらの形状はデバイスの領域の実際の形状を図示することを意図したものではなく、本発明の技術範囲を限定することを意図しない。

#### 【0124】

本願明細書において開示される実施例が結合され得ることは理解されるであろう。

したがって、第1の実施例に関して描かれ、且つ / 又は、記述されている特徴は第2の実施例においても同様に含まれ得、逆もまた同じである。

#### 【0125】

上記実施例は特定の図を参照して記述されるが、本発明の幾つかの実施例が付加的な及び / 若しくは介在する層、構造、又は、エレメントを含むことができ、且つ / 或いは、特定の層、構造、又は、エレメントは削除し得ることは理解すべきである。本発明の幾つかの代表的実施例が記述されたが、本発明の新規な教示及び利点から実質的に逸脱すること無く、多くの変更が代表的実施例において可能であることは当業者は容易に理解するであろう。したがって、全てのそのような変更は、請求項に記載の本発明の技術範囲内に含まれることを意図している。したがって、ここまでに述べたことは本発明の例示であって、開示される特定の実施例に限定されているように解釈されるべきではなく、開示された実施例に対する変更が他の実施例と同様に添付の請求項の技術範囲に含まれることが意図されていることは理解されるべきである。本発明は、以下の請求項（中で含まれる請求項の同等物を有する）によって定義される。

10

20

30

40

50

## 【図面】

## 【図 1】

## 【図 2】

(関連技術)

## 【図 3】

## 【図 4】

10

20

30

40

50

【図 5 A】

【図 5 B】

10

【図 5 C】

【図 5 D】

20

30

40

50

【図 5 E】

【図 6 A】

10

【図 6 B】

【図 6 C】

20

30

40

50

【図 6 D】

【図 6 E】

10

【図 7 A】

【図 7 B】

20

30

40

50

【図 8 A】

【図 8 B】

10

【図 8 C】

【図 8 D】

20

30

40

50

【図 8 E】

【図 8 F】

10

【図 9 A】

【図 9 B】

20

30

40

50

【図 9 C】

【図 9 D】

10

【図 10】

【図 11 A】

20

30

40

50

【図 1 1 B】

【図 1 2】

【図 1 3】

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

H 1 0 D      12/00      1 0 1 A

(72)発明者 サブリ、シャディ

アメリカ合衆国、ノースカロライナ、ケーリー、ウィーピング トゥリー ドライブ 921

審査官 恩田 和彦

(56)参考文献 特開2001-230319 (JP, A)

特開2008-192691 (JP, A)

特開2008-112823 (JP, A)

国際公開第2016/039074 (WO, A1)

特開平07-106330 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H 1 0 D      3 0 / 6 6

H 1 0 D      3 0 / 0 1

H 1 0 D      1 2 / 0 0