(19) **日本国特許庁(JP)**

(51) Int. Cl.

## (12) 特 許 公 報(B2)

FL

(11) 特許番号

特許第4421036号 (P4421036)

(45) 発行日 平成22年2月24日(2010.2.24)

(24) 登録日 平成21年12月11日 (2009.12.11)

\_\_\_\_\_

G 1 1 C 11/407 (2006.01)

G11C 11/34 362S

請求項の数 5 (全 13 頁)

(21) 出願番号 特願平11-326876

(22) 出願日 平成11年11月17日 (1999.11.17)

(65) 公開番号 特開2001-143468 (P2001-143468A)

(43) 公開日 平成13年5月25日 (2001.5.25) 審査請求日 平成16年3月11日 (2004.3.11)

審判番号 不服2007-5613 (P2007-5613/J1) 審判請求日 平成19年2月22日 (2007. 2. 22) ||(73)特許権者 308014341

富士通マイクロエレクトロニクス株式会社 東京都新宿区西新宿二丁目7番1号

|(74)代理人 100068755

弁理士 恩田 博宣

(74)代理人 100105957

弁理士 恩田 誠

|(72)発明者 古山 孝昭

愛知県春日井市高蔵寺町二丁目1844番 2 富士通ヴィエルエスアイ株式会社内

合議体

審判長 相田 義明審判官 加藤 俊哉

審判官 北島 健次

最終頁に続く

(54) 【発明の名称】半導体記憶装置のデータ書き込み方法及び半導体記憶装置

### (57)【特許請求の範囲】

## 【請求項1】

ワード線活性化コマンドの入力からクロック信号に基づく所定のレイテンシーを経てライトコマンドを入力し、前記ライトコマンドからあらかじめ設定されたライトレイテンシーを経た後に書き込みデータを入力して、データ書き込み動作を行う半導体記憶装置において、

前記ライトコマンドに基づいて書き込みデータの入力回路を活性化し、前記ライトレイテンシーを1より大きな値に設定して書き込みデータを入力し、前記ワード線活性化コマンドからライトコマンドまでのレイテンシーを、前記ライトレイテンシーの伸長を相殺するように短縮したことを特徴とする半導体記憶装置のデータ書き込み方法。

#### 【請求項2】

ワード線活性化コマンドの入力からクロック信号に基づく所定のレイテンシーを経てライトコマンド若しくはリードコマンドを入力し、前記ライトコマンドからあらかじめ設定されたライトレイテンシーを経た後に書き込みデータを入力して、データ書き込み動作を行うとともに、前記リードコマンドからあらかじめ設定されたリードレイテンシーを経た後に読み出し動作を行う半導体記憶装置において、

前記ライトコマンドに基づいて書き込みデータの入力回路を活性化し、前記ライトレイテンシーを<u>1より大きい値で、かつ、</u>前記リードレイテンシーの値より 1 小さい値に設定して書き込みデータを入力し、前記ワード線活性化コマンドからライトコマンドまでのレイテンシーを、前記ライトレイテンシーの伸長を相殺するように短縮したことを特徴とす

る半導体記憶装置のデータ書き込み方法。

## 【請求項3】

前記ワード線活性化コマンドの入力からライトコマンドの入力までのレイテンシーを、前記ワード線活性化コマンドの入力からリードコマンドの入力までのレイテンシーより短くしたことを特徴とする請求項1乃至2のいずれかに記載の半導体記憶装置のデータ書き込み方法。

#### 【請求項4】

クロック信号に基づいてアドレス信号を取り込む第一の入力回路と、

前記クロック信号に基づいて各種コマンド信号を取り込む第二の入力回路と、

前記クロック信号に基づいて書き込みデータを取り込む第三の入力回路と、

前記第一及び第二の入力回路と内部回路との間に介在され、前記クロック信号に基づいてライトレイテンシーを設定するライトレイテンシー設定部と

を備え、前記第一の入力回路で取り込んだアドレス信号及び第二の入力回路で取り込んだ ライトコマンドに基づいて、前記ライトコマンドの取り込み動作から前記ライトレイテン シーを経た後に、前記内部回路において前記第三の入力回路で取り込んだ書き込みデータ の書き込み動作を行う半導体記憶装置において、

前記第二の入力回路から出力されるライトコマンドに基づいて前記第三の入力回路を活性化する初段制御回路を有し、

前記ライトレイテンシーは、あらかじめ設定されたリードレイテンシーより小さく、かつ1より大きい値に設定されていることを特徴とする半導体記憶装置。

### 【請求項5】

前記ライトレイテンシー設定部には、リードレイテンシーの値より 1 小さい値をライトレイテンシーとして設定したことを特徴とする請求項 4 に記載の半導体記憶装置。

#### 【発明の詳細な説明】

## [0001]

## 【発明の属する技術分野】

この発明は、データ書き込み動作及びデータ読み出し動作をクロック信号に同期して行う シンクロナスDRAMに関するものである。

#### [00002]

近年、メモリ周辺機器の動作速度の高速化にともない、DRAM等のメモリの動作速度の高速化が進み、データ書き込み動作及びデータ読み出し動作をクロック信号に同期して行うシンクロナスDRAM(SDRAM)が実用化されるに至った。また、SDRAMにおいても、動作速度の更なる高速化を図るために、SDR(single data rate)からDDR(double data rate)へと移行している。そして、このようなSDRAMにおいて、動作速度の高速化を図りながら、消費電力の低減を図ることが必要となっている。

## [0003]

## 【従来の技術】

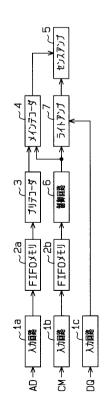

ライトレイテンシーが 1 である従来の D D R S D R A M の書き込み動作関連回路を図 7 に示す。第一の入力回路 1 a にはコラムアドレス信号 A D が入力され、第二の入力回路 1 b にはコマンド信号 C M が入力され、第三の入力回路 1 c には書き込みデータ D Q が入力される。

## [0004]

前記コラムアドレス信号 A D は、 F I F O メモリ 2 a を経て、 プリデコーダ 3 に入力される。 F I F O メモリ 2 a は、入力回路 1 a から出力されるアドレス信号を、この S D R A M のクロック信号の 1 周期分( 1 クロック)遅延させて、 プリデコーダ 3 に順次出力する

#### [0005]

プリデコーダ 3 の出力信号は、メインデコーダ 4 に入力され、そのメインデコーダ 4 から 出力されるコラム選択信号が該当するセンスアンプ 5 に出力される。

前記第二の入力回路1bは、入力されたコマンド信号CMをFIFOメモリ2bに出力す

10

20

30

40

る。 F I F O メモリ 2 b は、入力されたコマンド信号 C M を 1 クロック遅延させて制御回路 6 に順次出力する。制御回路 6 は、コマンド信号 C M に基づいて前記メインデコーダ 4 及びライトアンプ 7 に活性化信号を出力する。

### [0006]

前記第三の入力回路1cに入力される書き込みデータDQは、前記ライトアンプ7に入力される。

そして、書き込み動作時には、コマンド信号 CMに基づいてライトアンプ 7 及びメインデコーダ 4 が活性化され、かつアドレス信号 ADに基づいて特定コラムのセンスアンプ 5 が活性化されるとき、第三の入力回路 1 cからライトアンプ 7 に書き込みデータ DQが入力されて、その書き込みデータ DQがセンスアンプ 5 から記憶セルに書き込まれる。

## [0007]

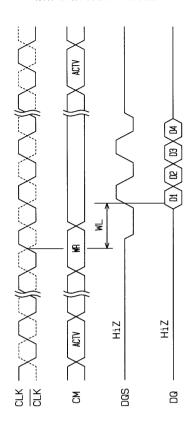

上記のような書き込み動作の動作タイミングを図8に従って説明する。書き込み動作時に前記コマンド信号CMとして外部から入力されるワード線活性化コマンドACTVから所定のレイテンシー(latency)を経てライトコマンドWRが入力される。

#### [0008]

ライトレイテンシW L が 1 の D D R S D R A M では、ライトコマンドW R の入力から 1 クロック後に、入出力制御信号 D Q S とともに書き込みデータ D Q が外部から入力される。

#### [0009]

そして、入出力制御信号 D Q S の立ち上がり及び立ち下がりに基づいて、第三の入力回路 1 c で書き込みデータ D Q を取り込み、その書き込みデータ D Q の取り込みにほぼ同期して活性化されるライトアンプ 7、メインデコーダ 4 及びセンスアンプ 5 の動作により、アドレス信号 A D に基づいて選択した記憶セルに取り込んだ書き込みデータ D Q を 2 ビット分ずつ順次書き込む。

#### [0010]

また、セル情報の読み出し動作時には、ワード線活性化コマンドACTVからライトコマンドWRが入力されるまでのレイテンシーと同一のレイテンシーでリードコマンドRDが入力され、そのリードコマンドRDの入力に基づいて、アドレス信号ADに基づいて選択された記憶セルからセル情報が読み出される。

## [0011]

このような読み出し動作では、リードコマンドの入力に基づいて直ちに読み出し動作が開始されるのに対し、上記書き込み動作では、ライトコマンドWRの入力からライトレイテンシーWLを経て書き込みデータDQの取り込みを開始し、データの取り込みが完了した後に書き込み動作が開始されるため、ワード線選択コマンドACTVの入力から書き込み動作が完了するまでの時間は、ワード線選択コマンドACTVの入力から読み出し動作が完了するまでの時間より長くなっている。

#### [0012]

## 【発明が解決しようとする課題】

上記のようなDDRSDRAMでは、消費電力を低減するために、書き込みデータDQを取り込むための第三の入力回路1cは、書き込みデータDQの入力タイミングに合わせ、ライトコマンドWRの入力に基づいて活性化することが望ましい。

## [0013]

ところが、ライトコマンドWRの入力から書き込みデータDQが入力されるまでのライトレイテンシーは1、すなわち1クロック分の時間である。そして、近年のDDRSDRAMの動作速度の高速化によるクロック信号CLKの高周波数化にともない、1クロック分の時間が極めて短くなっている。

## [0014]

従って、ライトコマンドWRに基づいて第三の入力回路1cを活性化しても、書き込みデータDQの取り込み動作の開始までに、第三の入力回路1cを確実に活性化することはできず、書き込みデータDQの取り込みに支障を来すおそれがある。

## [0015]

50

40

10

10

20

30

40

50

そこで、書き込み動作時には第三の入力回路1cを常時活性化する必要があるが、クロック信号CLK,バーCLKの高周波数化にともない、消費電力が増大するという問題点がある。

## [0016]

一方、ライトコマンドWRの入力から書き込みデータDQの取り込みまでの時間、すなわちライトレイテンシーを長く設定すれば、ライトコマンドWRに基づいて第三の入力回路1 cを活性化しても書き込みデータDQの取り込みに支障を来すことはない。

## [0017]

ところが、従来のDDRSDRAMでは、ワード線活性化コマンドACTVの入力からライトコマンドWRの入力までのレイテンシーは、ワード線活性化コマンドACTVの入力からリードコマンドの入力までのレイテンシーと同一に設定されているので、ライトレイテンシーを長く設定すると、ワード線活性化コマンドACTVが入力されてから、書き込み動作が終了するまでに要する時間が長くなる。従って、書き込み動作の速度が低下するという問題点がある。

#### [0018]

この発明の目的は、書き込み速度を低下させることなく、消費電力を低減し得るSDRA M及びそのデータ書き込み方法を提供することにある。

#### [0019]

## 【課題を解決するための手段】

上記目的を達成するためのデータ書き込み方法は、ワード線活性化コマンドの入力からライトコマンドの入力までのレイテンシーが短縮され、ライトレイテンシーは 1 より大きな値に設定される。書き込みデータは、ライトコマンドに基づいて活性化される入力回路で取り込まれ、取り込まれた書き込みデータに基づいて書き込み動作が行われる。

#### [0020]

上記目的を達成するための半導体記憶装置は、クロック信号に基づいてアドレス信号を取り込む第一の入力回路と、前記クロック信号に基づいて各種コマンド信号を取り込む第二の入力回路と、前記クロック信号に基づいて書き込みデータを取り込む第三の入力回路と、前記第一及び第二の入力回路との間に介在され、前記クロック信号に基づいてライトレイテンシーを設定するライトレイテンシー設定部とを備え、前記第一の入力回路で取り込んだアドレス信号及び第二の入力回路で取り込んだライトコマンドに基づいて、前記ライトコマンドの取り込み動作から前記ライトレイテンシーを経た後に、前記内部回路において前記第三の入力回路で取り込んだ書き込みデータの書き込み動作を行う。そして、ライトレイテンシー設定部には、あらかじめ設定されたリードレイテンシーより小さく、かつ1より大きいライトレイテンシーを設定し、前記第二の入力回路から出力されるライトコマンドに基づいて前記第三の入力回路を活性化する初段制御回路を備える。

## [0021]

## 【発明の実施の形態】

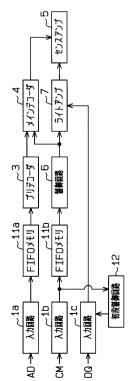

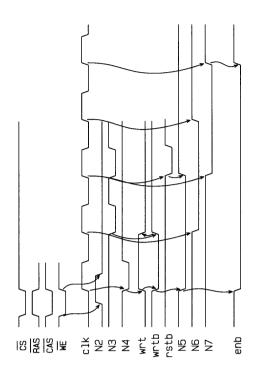

図1は、この発明を具体化したDDRSDRAMの書き込み関連回路の一実施の形態を示す。

### [0022]

この実施の形態は、前記従来例に対し、FIFOメモリ11a,11bの動作と、初段制御回路12とを除いて同一であり、同一構成部分は同一符号を付してその詳細な説明を省略する。

## [0023]

DDRSDRAMのリードレイテンシーRLは、クロック信号CLKの周波数に応じて設定され、周波数が高くなるにつれて2あるいは3というように大きな値が設定される。そして、この実施の形態ではクロック信号CLKに基づいてリードレイテンシーRLが3に設定され、ライトレイテンシーWLは(RL-1)、すなわち2に設定されている。

### [0024]

前記FIFOメモリ11a,11bは、2に設定されたライトレイテンシーWLに対応し

て、入力回路1a,1bの出力信号をクロック信号CLKの2周期分遅延させて順次出力するように構成される。

### [0025]

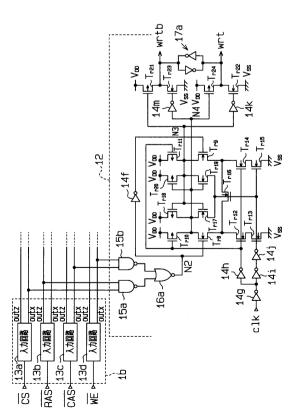

前記入力回路1bは、図2に示すように、具体的には4つの入力回路13a~13dで構成され、各入力回路13a~13dには各制御信号CSバー、RASバー、CASバー、WEバーがそれぞれ入力され、各信号をそれぞれ次段のFIFOメモリに出力する。

#### [0026]

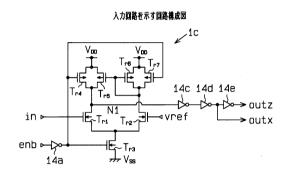

前記入力回路1cは、図4に示す差動回路で構成される。すなわち、1対のNチャネルMOSトランジスタTr1,Tr2のゲートには、入力信号inすなわち書き込みデータDQと基準電圧Vrefがそれぞれ入力され、各トランジスタTr1,Tr2のソースは、NチャネルMOSトランジスタTr3のドレインに接続され、同トランジスタTr3のソースは低電位側電源Vssに接続されている。前記入力回路1a,13a~13dも入力回路1cと同様な回路で構成される。

## [0027]

前記トランジスタTr1のドレインはPチャネルMOSトランジスタTr4, Tr5のドレインに接続され、同トランジスタTr4, Tr5のソースには高電位側電源VDDが供給される。

### [0028]

前記トランジスタTr2のドレインはPチャネルMOSトランジスタTr6,Tr7のドレインに接続され、同トランジスタTr6,Tr7のソースには高電位側電源VDDが供給される。

## [0029]

前記トランジスタTr5,Tr6のゲートは互いに接続されるとともに、前記トランジスタTr2のドレインに接続されている。

前記トランジスタTr4,Tr7のゲートには、活性化信号enbがインバータ回路14aを介して入力され、前記トランジスタTr3のゲートには、活性化信号enbがインバータ回路14aを介して入力される。

### [0030]

前記トランジスタTr1のドレインであるノードN1の電位は、3段のインバータ回路14 c~14eを介して出力信号outzとして出力され、かつ2段のインバータ回路14c ,14dを介して出力信号outxとして出力される。

## [0031]

このような入力回路1cでは、活性化信号enbがHレベルとなると、トランジスタTr3がオフされ、トランジスタTr4,Tr7がオンされる。従って、入力信号inに関わらずノードN1はHレベルに固定され、出力信号outzはLレベル、出力信号outxはHレベルに固定される。

## [0032]

また、活性化信号 e n b が L レベルとなると、トランジスタTr3がオンされ、トランジスタTr4,Tr7がオフされて活性状態となる。

そして、入力信号inの電圧レベルが基準電圧Vrefより高くなると、ノードN1がLレベルとなり、Hレベルの出力信号outzと、Lレベルの出力信号outxが出力される

## [0033]

また、入力信号inの電圧レベルが基準電圧Vrefより低くなると、ノードN1がHレベルとなり、Lレベルの出力信号outzと、Hレベルの出力信号outxが出力される。 【0034】

前記初段制御回路12の具体的構成を図2及び図3に従って説明する。NAND回路15 aには、前記入力回路13aの出力信号outxと、前記入力回路13bの出力信号outzが入力され、NAND回路15bには、前記入力回路13cの出力信号outxと、前記入力回路13dの出力信号outxが入力される。

### [0035]

前記NAND回路15a,15bの出力信号はNOR回路16に入力される。従って、N

20

10

30

40

OR回路16の出力信号であるノードN2は、前記NAND回路15a,15bの入力信号がすべてHレベルとなったとき、すなわち書き込みコマンドWRが入力されたとき、Hレベルとなる。

### [0036]

前記ノードN2は、NチャネルMOSトランジスタTr8のゲートに入力されるとともに、インバータ回路14fを介してNチャネルMOSトランジスタTr9に入力される。

#### [0037]

前記トランジスタTr8のドレインは P チャネルMOSトランジスタTr10のドレインに接続されるとともに、同トランジスタTr10のソースには電源 V DDが供給される。

#### [0038]

前記トランジスタTr9のドレインは P チャネルMOSトランジスタTr11のドレインに接続されるとともに、同トランジスタTr11のソースには電源 V DDが供給される。

#### [0039]

前記トランジスタTr8のソースは、NチャネルMOSトランジスタTr12, Tr13を介して電源 Vssに接続され、前記トランジスタTr9のソースは、NチャネルMOSトランジスタTr14, Tr15を介して電源 Vssに接続されている。また、トランジスタTr8, Tr9のソースは、NチャネルMOSトランジスタTr16を介して接続されている。

#### [0040]

前記トランジスタTr8, Tr10のドレイン、すなわちノードN4は、NチャネルMOSトランジスタTr17及びPチャネルMOSトランジスタTr18のドレインに接続されるとともに、NチャネルMOSトランジスタTr20のゲートに接続される。

## [0041]

前記トランジスタTr17,Tr18のドレインは互いに接続され、前記トランジスタTr19, Tr20のドレインは互いに接続されている。前記トランジスタTr18 ,Tr20のソースには 電源VDDが供給されている。

#### [0042]

前記トランジスタTr9, Tr11のドレイン、すなわちノードN3は、前記トランジスタTr 19, Tr20のドレインに接続されるとともに、前記トランジスタTr17, Tr18のゲートに 接続されている。

### [0043]

前記トランジスタTr10, Tr11, Tr12, Tr14のゲートには、クロック信号CLKが2段のインバータ回路14g,14hを介して入力され、トランジスタTr13, Tr15, Tr16のゲートには、クロック信号CLKが3段のインバータ回路14g,14i,14jを介して入力される。

#### [0044]

また、前記トランジスタTr17 ,Tr19のソースには、クロック信号 C L K が 3 段のインバータ回路 1 4 g , 1 4 i , 1 4 j を介して供給される。そして、前記トランジスタTr17 ~ Tr20は、ノード N 3 , N 4 の電位差を拡大するように動作して、ノード N 3 , N 4 の立ち上がり動作及び立ち下がり動作を高速化する。

## [0045]

前記ノードN3の電圧レベルは、 P チャネルMOSトランジスタT r21のゲートに入力されるとともに、インバータ回路14kを介してNチャネルMOSトランジスタT r22のゲートに入力される。

#### [0046]

前記ノードN4の電圧レベルは、PチャネルMOSトランジスタTr24のゲートに入力されるとともに、インバータ回路14mを介してNチャネルMOSトランジスタTr23のゲートに入力される。

### [0047]

前記トランジスタTr21,Tr24のソースには、電源VDDが供給され、前記トランジスタT

10

20

30

40

r23, Tr22のソースは電源 Vssに接続される。

そして、前記トランジスタTr21 , Tr23のドレインから信号 w r t b が出力され、前記トランジスタTr24 , Tr22のドレインから信号 w r t が出力される。また、トランジスタTr21 , Tr23のドレインと、トランジスタTr24 , Tr22のドレインとの間にはラッチ回路 1 7 a が接続されている。

#### [0048]

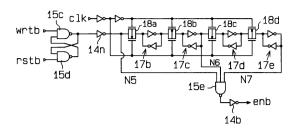

図 3 に示すように、前記信号wrt b は N A N D 回路 1 5 c に入力され、その N A N D 回路 1 5 c の出力信号は、N A N D 回路 1 5 d に入力される。

前記NAND回路15dには、信号rstbが入力される。この信号rstbは、常には Hレベルの信号が入力され、前記各制御信号CSバー、RASバー、CASバー、WEバ ーに基づいて書き込み動作の終了が検出されたとき、Lレベルとなるワンショットパルス 信号が入力される。

#### [0049]

そして、NAND回路15dの出力信号が前記NAND回路15cに入力される。

前記NAND回路15cの出力信号は、インバータ回路14nを介して転送ゲート18aに入力される。前記転送ゲート18aの出力信号は、ラッチ回路17bに入力され、そのラッチ回路17bの出力信号は転送ゲート18bに入力される。

#### [0050]

前記転送ゲート18bの出力信号は、ラッチ回路17cに入力され、そのラッチ回路17 cの出力信号は転送ゲート18cに入力される。

前記転送ゲート18cの出力信号は、ラッチ回路17dに入力され、そのラッチ回路17dの出力信号は転送ゲート18dに入力される。

### [0051]

前記転送ゲート18dの出力信号は、ラッチ回路17eに入力され、そのラッチ回路17eの出力信号(ノードN7)はNAND回路15eに入力される。また、前記インバータ回路14nの出力信号(ノードN5)と、前記ラッチ回路17cの出力信号(ノードN6)がNAND回路15eに入力される。

#### [0052]

前記各転送ゲート18a~18dは、クロック信号CLKと同相の信号と、反転信号とが入力されて、転送ゲート18a,18cと、同18b,18dとが交互に導通するようになっている。

## [0053]

前記NAND回路15 eの出力信号は、インバータ回路14 pに入力され、そのインバータ回路14 pの出力信号が活性化信号 e n b として前記入力回路1 c に入力される。

### [0054]

上記のような初段制御回路12の動作を図5に従って説明する。

書き込みモード時以外には、制御信号WEバーがHレベルとなるため、少なくともNAND回路15bの出力信号がHレベルとなり、ノードN2はLレベルに維持される。すると、トランジスタTr9はオン状態に維持される。

### [0055]

クロック信号 C L K により、トランジスタ T r10 , T r11は間歇的にオンされ、トランジスタ T r12 , T r13及び同 T r14 , T r15はクロック信号 C L K が L レベルから H レベルに立ち上がるとき、 1 段分のインバータ回路の動作遅延時間にかぎり同時にオンして、トランジスタ T r8 , T r9のソースと電源 V ssとを導通させる。

#### [0056]

この結果、ノードN4はHレベルに固定され、ノードN3はクロック信号CLKの反転信号となる。

すると、トランジスタTr21,Tr22,Tr23,Tr24はすべてオフされるか、あるいはトランジスタTr21,Tr22のみがオンされる状態のいずれかとなり、ラッチ回路17aの動作により、信号wr t b は H レベル、信号wr t は L レベルに維持される。

10

20

30

40

10

20

30

40

50

#### [0057]

信号wrtbがHレベルの状態では、NAND回路15cの出力信号は、前サイクルでリセット信号rstbの入力に基づいてLレベルに維持される。すると、インバータ回路14nの出力信号はHレベルに維持され、NAND回路15eの入力信号はすべてHレベルに維持される。

#### [0058]

従って、インバータ回路14pから出力される活性化信号enbは、Hレベルに維持され、第三の入力回路1cは不活性状態に維持される。

入力回路13a~13dにライトコマンドが入力されたとき、すなわちLレベルの制御信号CSバーと、Hレベルの制御信号RASバーと、Lレベルの制御信号CASバーと、Lレベルの制御信号WEバーが入力されると、ノードN2は各制御信号の重なる時間範囲でHレベルとなる。

#### [0059]

### [0060]

ノードN4の立ち下がりに基づいて、信号wrtbはLレベルに立ち下がり、信号wrtbはHレベルに立ち上がり、次にノードN3がLレベルに立ち下がるまで、この状態が維持される。

## [0061]

信号wrtbの立ち下がりに基づいて、活性化信号enbがLレベルに立ち下がる。また、信号wrtbの立ち下がりに基づいてノードN5がLレベルに立ち下がり、ノードN5の立ち下がりから1クロック後にノードN6が立ち下がり、ノードN6の立ち下がりから1クロック後にノードN7が立ち下がる。

#### [0062]

次いで、信号wrtbがHレベルに復帰した状態で、リセット信号rstbがHレベルからLレベルに立ち下がると、ノードN5はLレベルからHレベルに復帰し、次いで1クロック後にノードN6がLレベルからHレベルに復帰し、次いで1クロック後にノードN7がLレベルからHレベルに復帰する。

#### [0063]

このような動作により、活性化信号 e n b はノード N 5 が立ち下がってからノード N 7 が立ち上がるまでの範囲で L レベルとなり、その活性化信号 e n b により前記第三の入力回路 1 c が所定時間の範囲で活性化される。

#### [0064]

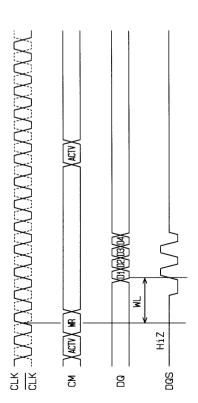

次に、上記のように構成されたDDRSDRAMの書き込み動作を図6に従って説明する

このDDRSDRAMでは、前記従来例に対しクロック信号CLKの高周波数化により、 リードレイテンシーRLが3に設定されている。

## [0065]

書き込み動作時には、外部からワード線選択コマンドACTVの入力に続いてライトコマンドWRを入力する。このライトコマンドWRは、前記各制御信号CSバー、RASバー、CASバー、WEバーを所定レベルに制御することである。

## [0066]

ライトコマンドWRの入力に基づいて、前記初期制御回路12により第三の入力回路1cが活性化される。また、ライトコマンドWRの入力から2に設定されたライトレイテンシーWLを経て、入出力制御信号DQSが外部から入力されるとともに、書き込みデータDQが入力され、その書き込みデータDQが活性化された第三の入力回路1cにより取り込

まれる。

## [0067]

第一の入力回路1aに入力されたアドレス信号ADは、FIFOメモリ11aを経てプリデコーダ3に入力され、そのプリデコーダ3の出力信号がメインデコーダ4に入力される

## [0068]

第二の入力回路1 b に入力されたライトコマンドW R は、F I F O メモリ 1 1 b を経て制御回路6 に入力され、その制御回路6 の出力信号に基づいてライトアンプ7及びメインデコーダ4が活性化され、メインデコーダ4の動作に基づいてセンスアンプ5が活性化される。

[0069]

このような動作により、書き込みデータDQの取り込みに合わせて、ライトアンプ7及びセンスアンプ5が活性化され、2ビットずつの書き込みデータDQが、アドレス信号ADに基づいて選択された記憶セルに順次書き込まれる。

#### [0070]

上記のように構成されたDDRSDRAMでは、次に示す作用効果を得ることができる。(1)ライトレイテンシーWLを2としたことにより、ライトコマンドWRに基づいて書き込みデータDQを取り込むための第三の入力回路1cを活性化しても、書き込みデータDQの取り込み動作に十分間に合わせることができる。従って、書き込み動作時にのみ第三の入力回路1cを活性化することができるので、消費電力を低減することができる。特に、入出力ビット数が16ビットあるいは32ビットというように、多ビットになるほど書き込みデータDQを取り込むための入力回路の数が増大するため、消費電力の低減効果は顕著である。

[0071]

(2) ライトレイテンシーW L は、3に設定されたリードレイテンシーR L より1小さい2とした。すなわち、ライトレイテンシーW L を(R L - 1)としたことにより、ライトコマンドW R に基づく第三の入力回路1 c の活性化を可能としながら、ライトレイテンシーW L を必要以上に長く設定することなく、ワード線活性化コマンドACTVの入力から書き込み動作が完了するまでに要する時間を短縮化することができる。

[0072]

(3) ワード線活性化コマンドACTVが入力されてから、ライトコマンドWRが入力されるまでのレイテンシーを短縮したので、従来例に比してライトレイテンシーWLを長く設定しても、ワード線活性化コマンドACTVの入力から書き込み動作が完了するまでに要する時間を短縮することができる。

[0073]

上記実施の形態は、次に示すように変更することもできる。

・上記実施の形態は、SDRSDRAMに実施することもできる。

[0074]

## 【発明の効果】

以上詳述したように、この発明は書き込み速度を低下させることなく、消費電力を低減し 40 得るSDRAM及びそのデータ書き込み方法を提供することができる。

【図面の簡単な説明】

- 【図1】 一実施の形態の書き込み関連回路を示すブロック図である。

- 【図2】 初段制御回路を示す回路構成図である。

- 【図3】 初段制御回路を示す回路構成図である。

- 【図4】 入力回路を示す回路構成図である。

- 【図5】 初段制御回路の動作を示すタイミング波形図である。

- 【図6】 DDRSDRAMの書き込み動作を示すタイミング波形図である。

- 【図 7 】 従来のDDRSDRAMの書き込み関連回路示すブロック図である。

- 【図8】 従来例の書き込み動作を示すタイミング波形図である。

50

10

20

## 【符号の説明】

| 1 | a | 第一の入力回路 |

|---|---|---------|

| 1 | b | 第二の入力回路 |

| 1 | С | 第三の入力回路 |

1 1 ライトレイテンシー設定部

12 初段制御回路

ACTV ワード線活性化コマンド

W R ライトコマンド W L ライトレイテンシー D Q 書き込みデータ

10

## 【図1】

## 一実施の形態の書き込み関連回路を示すプロック図

## 【図2】

## 初段制御回路を示す回路構成図

【図5】

## 【図3】

初段制御回路を示す回路構成図

【図4】

初段制御回路の動作を示すタイミング波形図

【図6】

DDRSDRAMの書き込み動作を示すタイミング波形図

【図7】

## 従来のDDRSDRAMの書き込み関連回路を示すプロック図

# 【図8】

従来例の書き込み動作を示すタイミング波形図

## フロントページの続き

(56)参考文献 特開2001-67877(JP,A)

特開平9-17819(JP,A)

特開平11-45567(JP,A)

特開平10-241355(JP,A)

特開平11-312970(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C11/407