(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6883482号

(P6883482)

(45) 発行日 令和3年6月9日(2021.6.9)

(24) 登録日 令和3年5月12日(2021.5.12)

(51) Int.Cl.

F 1

GO 1 R 33/07 (2006.01)

GO 1 R 33/07

GO 1 R 31/28 (2006.01)

GO 1 R 31/28

GO 1 R 31/3185 (2006.01)

W

請求項の数 5 (全 11 頁)

(21) 出願番号 特願2017-132422 (P2017-132422)

(22) 出願日 平成29年7月6日(2017.7.6)

(65) 公開番号 特開2018-36252 (P2018-36252A)

(43) 公開日 平成30年3月8日(2018.3.8)

審査請求日 令和2年6月9日(2020.6.9)

(31) 優先権主張番号 特願2016-165827 (P2016-165827)

(32) 優先日 平成28年8月26日(2016.8.26)

(33) 優先権主張国・地域又は機関

日本国(JP)

(73) 特許権者 715010864

エイブリック株式会社

東京都港区三田三丁目9番6号

(72) 発明者 挽地 友生

千葉県千葉市美浜区中瀬1丁目8番地 工

スアイアイ・セミコンダクタ株式会社内

(72) 発明者 有山 稔

千葉県千葉市美浜区中瀬1丁目8番地 工

スアイアイ・セミコンダクタ株式会社内

(72) 発明者 矢野 宏伯

千葉県千葉市美浜区中瀬1丁目8番地 工

スアイアイ・セミコンダクタ株式会社内

審査官 田口 孝明

最終頁に続く

(54) 【発明の名称】センサ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

動作期間と休止期間を備えた間欠動作をするセンサ回路であって、

印加される物理量に応じて2つの異なる電位レベルの物理量検出信号を出力する物理量

検出部と、

前記物理量検出信号を受けて論理信号を出力端子へ出力する出力ドライバと、

前記物理量検出部へ前記間欠動作を制御するための制御信号を出力し、前記休止期間に

サンプリング信号を出力するクロック発生回路と、

前記出力端子の電位を検出し、検出信号を出力する電位検出回路と、

前記サンプリング信号と前記検出信号が入力され、前記クロック発生回路へモード切替

信号を出力するクロック制御回路と、を備え、 10

前記クロック制御回路は、前記検出信号を前記サンプリング信号に基づきサンプリング

したデータに所定の信号パターンを検出すると、前記クロック発生回路をテストモードに

切替えるモード切替信号を出力する

ことを特徴とするセンサ回路。

## 【請求項 2】

前記クロック制御回路は、更に、前記物理量検出部の出力する前記物理量検出信号が入

力され、

前記テストモードにおいて前記物理量検出信号が変化すると、通常モードに切替えるモ

ード切替信号を出力する

10

20

ことを特徴とする請求項 1 に記載のセンサ回路。

【請求項 3】

更に、カウンタを備え、

前記カウンタは、前記検出信号の変動を受けて計数を開始し、タイムアウト時間に達すると前記クロック制御回路にタイムアウト信号を出力し、

前記クロック制御回路は、前記タイムアウト信号によって前記サンプリング信号をマスクする

ことを特徴とする請求項 1 または 2 に記載のセンサ回路。

【請求項 4】

更に、デッドタイム制御回路を備え、

10

前記デッドタイム制御回路は、前記休止期間への遷移後の所定期間に前記クロック制御回路にデッドタイム信号を出力し、

前記クロック制御回路は、前記デッドタイム信号によって前記サンプリング信号をマスクする

ことを特徴とする請求項 1 または 2 に記載のセンサ回路。

【請求項 5】

更に、リセット回路を備え、

前記リセット回路は、前記検出信号の幅が小さいことを検出すると前記クロック制御回路にリセット信号を出力し、

前記クロック制御回路は、前記リセット信号によって前記サンプリング信号をマスクする

20

ことを特徴とする請求項 1 または 2 に記載のセンサ回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、センサ回路に関し、特にテスト回路を有するセンサ回路に関する。

【背景技術】

【0002】

従来から様々な物理量を検出するセンサ回路が電子機器に搭載され活用されている。センサ回路は、電源端子、接地端子、出力端子の三端子のパッケージに搭載されることがある。このように端子数が少ないパッケージに搭載されたセンサ回路は、テストモードへ切り替えるための専用端子を設けることが出来ない場合が多い。このため、端子数の少ないセンサ回路では、出力端子をテスト端子として兼用している。

30

【0003】

従来のセンサ回路は、検出部の出力信号の電位レベルを出力する第 1 の反転部と、検出部の出力信号の電位レベルを反転して出力端子に出力する第 2 の反転部と、第 1 の反転部の電位レベルと第 2 の反転部の電位レベルに応じてテストモードに切り替えるモード切替え回路を備えている。そして、出力端子から強制的に電圧を入力することによって、モード切替え回路は、通常起こりえない電位状態（同電位）を検出しテストモードに切り替えている（例えば、特許文献 1 参照）。

40

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2009 - 31225 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、従来の磁気センサ回路は、出力端子から重畳したノイズ等の意図しない外部入力に対し、テストモードに誤って切り替わってしまう可能性があった。また、出力端子の負荷容量が大きい場合にも、検出結果に応じた通常の出力端子の電位レベルの変化

50

が遅延することにより、意図せずテストモードに切り替わってしまう可能性があった。

【課題を解決するための手段】

【0006】

本発明のセンサ回路は、物理量検出部へ間欠動作を制御するための制御信号を出力し、休止期間にサンプリング信号を出力するクロック発生回路と、出力端子の電位を検出して検出信号を出力する電位検出回路と、検出信号をサンプリング信号に基づきサンプリングしたデータに所定の信号パターンを検出するとクロック発生回路をテストモードに切替えるモード切替信号を出力するクロック制御回路を備えることを特徴とする。

【発明の効果】

【0007】

本発明のセンサ回路によれば、テストモードに誤って切り替わってしまう可能性が低く、安定した動作が可能である。

10

【図面の簡単な説明】

【0008】

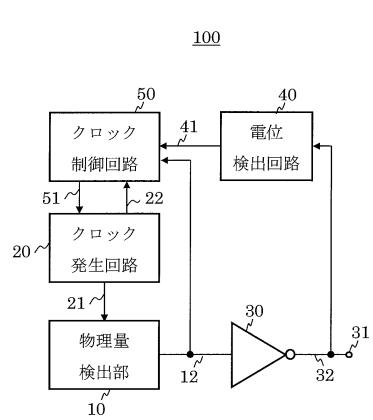

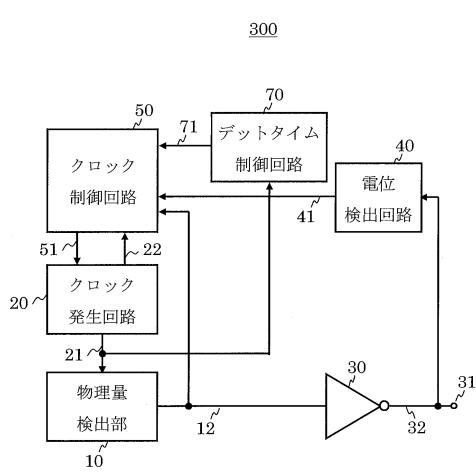

【図1】第1の実施形態のセンサ回路のブロック図である。

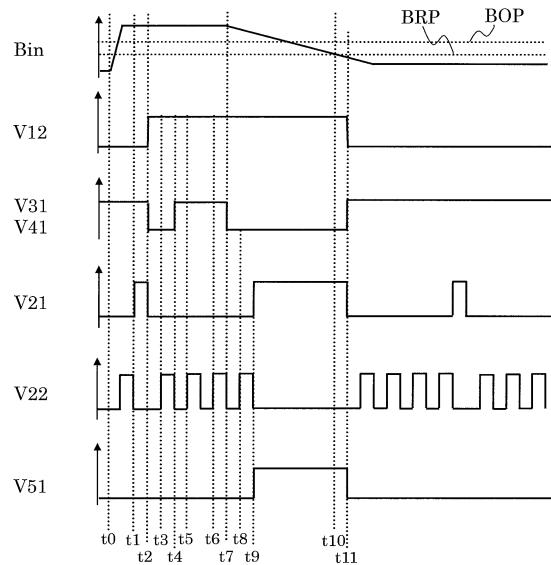

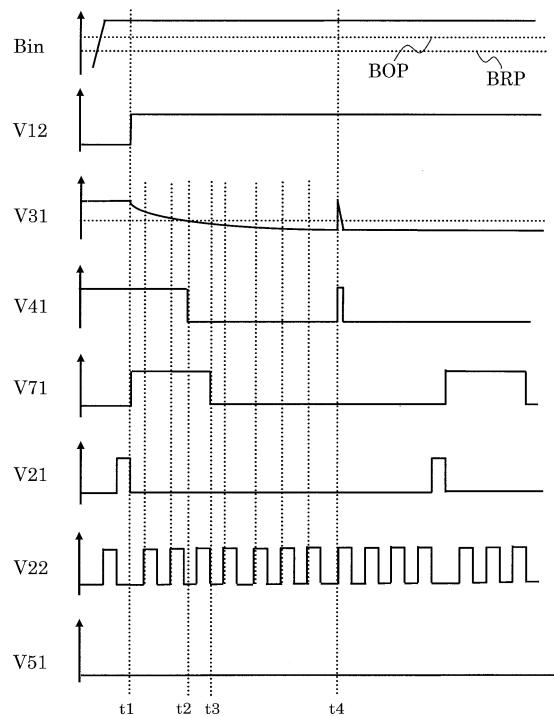

【図2】第1の実施形態のセンサ回路の動作を示すタイミング図である。

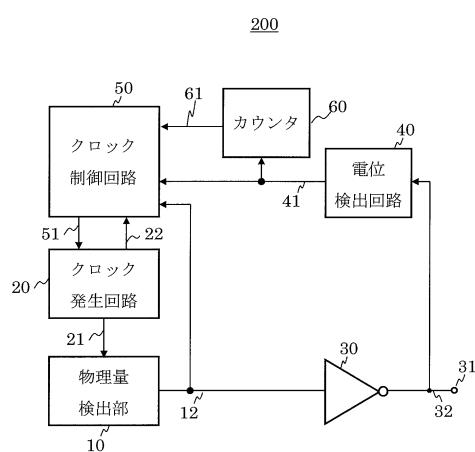

【図3】第2の実施形態のセンサ回路のブロック図である。

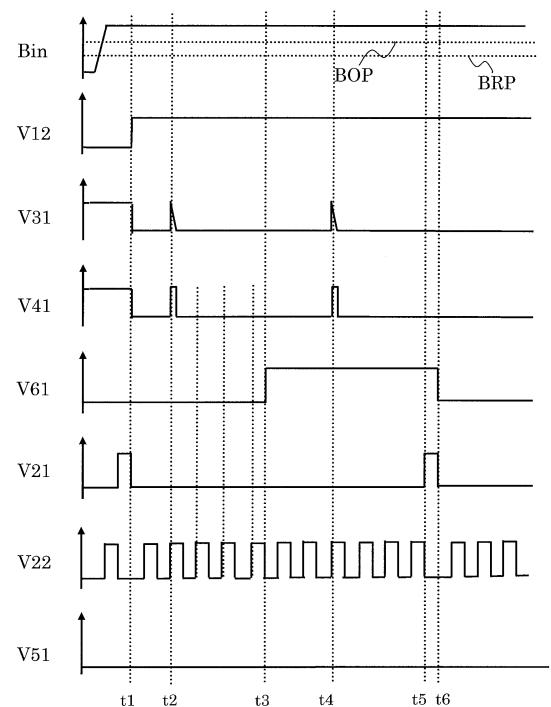

【図4】第2の実施形態のセンサ回路の動作を示すタイミング図である。

【図5】第3の実施形態のセンサ回路のブロック図である。

【図6】第3の実施形態のセンサ回路の動作を示すタイミング図である。

20

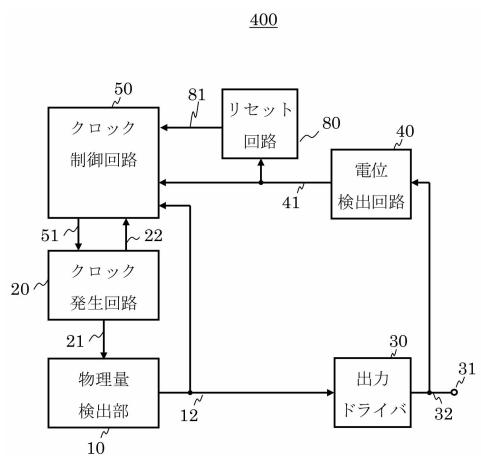

【図7】第4の実施形態のセンサ回路のブロック図である。

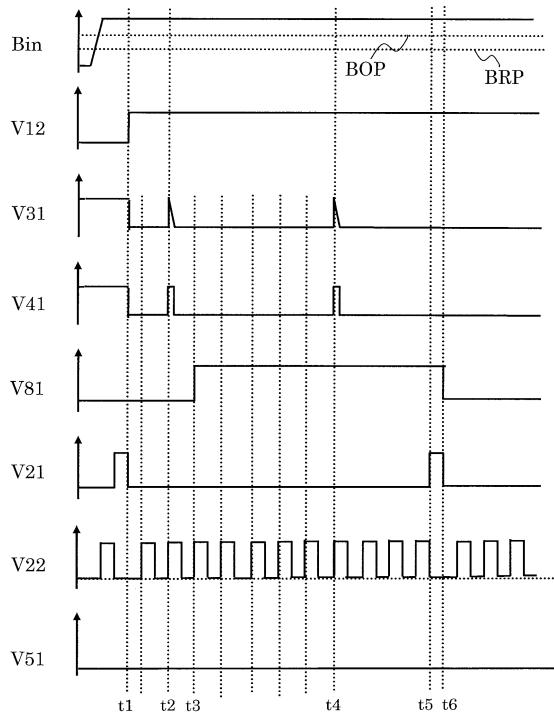

【図8】第4の実施形態のセンサ回路の動作を示すタイミング図である。

【発明を実施するための形態】

【0009】

以下、本発明のセンサ回路について、ホール素子の出力電圧を基準電圧と比較した結果を2値出力する磁気スイッチを例に説明する。

<第1の実施形態>

図1は、第1の実施形態のセンサ回路100のブロック図である。

第1の実施形態のセンサ回路100は、物理量検出部10と、クロック発生回路20と、出力ドライバ30と、電位検出回路40と、クロック制御回路50とで構成されている。

30

【0010】

物理量検出部10は、印加される物理量に応じて2つの異なる電位レベルの物理量検出信号12を出力する。

出力ドライバ30は、入力が物理量検出部10の出力に接続され、出力が出力端子31に接続される。出力ドライバ30は、物理量検出部10の物理量検出信号12を反転して、出力端子31にセンサ回路100の出力論理信号32を出力する。

【0011】

電位検出回路40は、入力が出力端子31に接続され、出力端子31の電位に基づいて2値の電位検出信号41を出力する。

40

クロック発生回路20は、物理量検出部10に検出動作を制御するための制御信号21を出力し、休止期間においてクロック制御回路50にサンプリング信号22を出力する。

クロック制御回路50は、電位検出信号41とサンプリング信号22と物理量検出信号12が入力され、クロック発生回路20にモード切替信号51を出力する。

【0012】

物理量検出部10は、S極またはN極の磁界を検出する磁気スイッチであり、外部から印加された磁束密度の大小に応じて物理量検出信号12の電位レベルを切り替える。また、物理量検出部10は、制御信号21に応じて物理量の検出・解除動作を行う動作期間と、内部回路の動作電流の大部分を遮断する休止期間とを有する間欠駆動を行う。

【0013】

50

クロック制御回路 50 は、サンプリング信号 22 に同期して電位検出信号 41 をサンプリングし、シフトレジスタなどにそのデータを保持する。クロック制御回路 50 は、電位検出信号 41 から所定の信号パターン（ここでは、L H H L、H L L H とする）が得られた場合に、モード切替信号 51 をテストモードに対応するレベルに切り替える。また、クロック制御回路 50 は、物理量検出信号 12 が変化すると、モード切替信号 51 を通常モードに対応するレベルに切り替える。

#### 【0014】

物理量検出部 10 は、例えば、以下に示す動作をするように構成されている。

物理量検出部 10 は、制御信号 21 が H レベルのときに動作期間になり、ホール素子の出力電圧を基準電圧と比較し、制御信号 21 が L レベルのときに休止期間になり、印加された磁束密度が所定の値より小さいと L レベル、所定の値より大きいと H レベルの物理量検出信号 12 を出力する。10

#### 【0015】

出力ドライバ 30 は、例えば、CMOS ドライバが用いられる。出力ドライバ 30 は、印加される物理量が小さいとき、例えば、入力である物理量検出信号 12 が L レベルのとき、Nch ドライバがオフし Pch ドライバがオンして、H レベルの出力論理信号 32 を出力端子 31 に出力する。印加される物理量が大きいとき、例えば、入力である物理量検出信号 12 が H レベルのとき、Nch ドライバがオンし Pch ドライバがオフして、L レベルの出力論理信号 32 を出力端子 31 に出力する。

#### 【0016】

電位検出回路 40 は、例えば、シュミットトリガ回路や、差動対と基準電圧回路によるコンパレータ等で構成される。電位検出回路 40 は、出力端子 31 の電位が H レベルのときに H レベルの電位検出信号 41 を出力し、出力端子 31 の電位が L レベルのときに L レベルの電位検出信号 41 を出力する。20

#### 【0017】

次に、第 1 の実施形態のセンサ回路 100 の動作について説明する。

図 2 は、第 1 の実施形態のセンサ回路 100 の動作を示すタイミング図である。

図 2において、センサ回路 100 に印加される磁束密度を Bin、物理量検出信号 12 の電圧を V12、出力端子 31 の電圧を V31、電位検出信号 41 の電圧を V41、制御信号 21 の電圧を V21、サンプリング信号 22 の電圧を V22、動作周期制御信号 51 の電圧を V51、とする。また、物理量検出部 10 が物理量を検出する閾値を BOP、検出を解除する閾値を BRP、とする。30

#### 【0018】

センサ回路 100 には、タイミング図に示すような磁束密度 Bin が印加される。磁束密度 Bin は、時刻 t0 以前では閾値 BRP より低いので、物理量検出信号 12 は L レベル、出力端子 31 及び電位検出信号 41 の電圧は H レベルである。

#### 【0019】

センサ回路 100 は、時刻 t1 までは通常動作時の休止期間であり、動作周期制御信号 51 は L レベルを維持して、クロック発生回路 20 からサンプリング信号 22 が出力される。時刻 t1 前までのサンプリング信号 22 において、クロック制御回路 50 は、電位検出信号 41 の H レベルを連続して保持しているので、通常動作（動作周期制御信号 51 は L レベル）を維持する。ここで、クロック制御回路 50 は、サンプリング信号 22 の立ち上がりエッジで電位検出信号 41 の電位を読み込むものとする。40

#### 【0020】

センサ回路 100 は、時刻 t1 から時刻 t2 の間は通常動作時の動作期間であり、クロック発生回路 20 は制御信号 21 を H レベルにする。物理量検出部 10 は、動作期間中に磁束密度 Bin が閾値 BOP より高いことを検出して信号処理を行い、制御信号 21 が L レベルになったときに物理量検出信号 12 を H レベルにする。それに応じて、出力端子 31 及び電位検出信号 41 の電圧は L レベルになる。そして、センサ回路 100 は、再び通常動作時の休止期間になり、動作周期制御信号 51 は L レベルを維持して、クロック発生50

回路 20 からサンプリング信号 22 が出力される。

**【0021】**

クロック制御回路 50 は、時刻  $t_3$ において、サンプリング信号 22 によって電位検出信号 41 の L レベルを読み込む。

ここで、時刻  $t_4$  から時刻  $t_7$  において、出力端子 31 に外部から強制的に H レベルを入力されると、クロック制御回路 50 は、時刻  $t_5$ 、 $t_6$  において、サンプリング信号 22 によって電位検出信号 41 の H レベルを読み込み、更に、時刻  $t_8$  において、サンプリング信号 22 によって電位検出信号 41 の L レベルを読み込む。

**【0022】**

従って、クロック制御回路 50 は、入力された信号パターンが L H H L のレベルになる 10 ので、時刻  $t_8$  から時刻  $t_9$  の間ににおいてテストモード入力信号であると判断し、通常動作からテストモードに切替え、H レベルの動作周期制御信号 51 を出力する。

**【0023】**

センサ回路 100 は、時刻  $t_{10}$  までテストモードを維持した後、磁束密度  $B_{in}$  が解除閾値  $B_{RP}$  以下となったことを物理量検出部 10 が検出すると、物理量検出信号 12 が L レベルに変化する。クロック制御回路 50 は、物理量検出信号 12 が L レベルに変化したことを受け、テストモードから通常動作に切替え、L レベルの動作周期制御信号 51 を出力する。

**【0024】**

以上説明したように、本実施形態のセンサ回路 100 は、通常動作時の休止期間において、出力端子 31 に外部から強制的に所定の信号パターンを有する電圧を入力して、それを検出することで通常動作からテストモードに切替え、物理量検出信号 12 のレベルが変化したことを受け、テストモードから通常動作に切替える構成とした。従って、本実施形態のセンサ回路 100 は、テストモードに誤って切り替わってしまう可能性が低く、安定した動作が可能である。 20

**【0025】**

なお、図 2 のタイミング図では、磁束密度  $B_{in}$  が検出閾値  $B_{OP}$  より高い状態からテストモードに切替える説明をしたが、磁束密度  $B_{in}$  が解除閾値  $B_{RP}$  より低い状態からテストモードに切替える場合でも同様である。この場合は、出力端子 31 を強制的に L レベルの電位にして、信号パターンを H L L H として、クロック制御回路 50 はテストモード入力信号であると判断し、通常動作からテストモードに切替えることが出来る。また、信号パターンを L H H L や H L L H として説明したが、これに限らず、更に複雑な信号パターンや短い信号パターンであっても良い。 30

**【0026】**

<第 2 の実施形態>

図 3 は、第 2 の実施形態のセンサ回路 200 のブロック図である。第 2 の実施形態のセンサ回路 200 は、図 1 のセンサ回路 100 に追加してタイムアウト時間を計数するカウンタ 60 を備えた。また、クロック制御回路 50 は、カウンタ 60 が出力するタイムアウト信号 61 を受ける構成とした。その他の構成については、図 1 のセンサ回路 100 と同一であるため、同一の構成要素には同一の符号を付し、説明は省略する。 40

**【0027】**

カウンタ 60 は、電位検出回路 40 から出力される電位検出信号 41 が入力され、クロック制御回路 50 にタイムアウト信号 61 を出力する。クロック制御回路 50 は、H レベルのタイムアウト信号 61 を受けると、サンプリング信号 22 をマスクする。

**【0028】**

次に、第 2 の実施形態のセンサ回路 200 の動作について説明する。

図 4 は、第 2 の実施形態のセンサ回路 200 の動作を示すタイミング図である。

図 4 において、タイムアウト信号 61 の電圧を  $V_{61}$  とする。また、図 2 のタイミング図と同一の動作については、その説明を省略する。

**【0029】**

時刻  $t_1$ において、物理量検出信号 1 2 は H レベルとなり、出力端子 3 1 の電圧は L レベルとなる。

時刻  $t_2$ において、外部からのノイズが出力端子 3 1 に重畳すると、図に示すように電圧  $V_{31}$  が変動し、H レベルの電位検出信号 4 1 が出力される。従って、クロック制御回路 5 0 は、サンプリング信号 2 2 によって電位検出信号 4 1 の H レベルを読み込む。

#### 【0030】

カウンタ 6 0 は、電位検出信号 4 1 の変動を受けて計数を開始し、時刻  $t_3$  においてタイムアウト時間に達すると、タイムアウト信号 6 1 を L レベルから H レベルにする。クロック制御回路 5 0 は、H レベルのタイムアウト信号 6 1 を受けると、サンプリング信号 2 2 をマスクするので、時刻  $t_4$  における外部からのノイズによる電位検出信号 4 1 の H レベルを読み込まない。10

#### 【0031】

従って、クロック制御回路 5 0 は、時刻  $t_2$  以降の信号パターンを H L L H と認識しないので、図 4 のようにノイズがあったとしても、誤ってテストモードに切替えることが無い。

以上説明したように、第 2 の実施形態のセンサ装置では、タイムアウト信号 6 1 を出力するカウンタ 6 0 を備えたので、誤ってテストモードに切替えられるという誤動作をより確実に防止できる。

#### 【0032】

なお、カウンタ 6 0 は、フリップフロップによる論理回路を用いたデジタル回路で構成してもよいし、定電流源と容量素子によるアナログ計時回路で構成してもよい。また、タイムアウト信号 6 1 は、例えば、時刻  $t_5$  または  $t_6$  において、制御信号 2 1 によって H レベルから L レベルにリセットされるようにすれば良い。20

#### 【0033】

##### <第 3 の実施形態>

図 5 は、第 3 の実施形態のセンサ回路 3 0 0 のブロック図である。第 3 の実施形態のセンサ回路 3 0 0 は、図 1 のセンサ回路 1 0 0 に追加して制御信号 2 1 を受けてデッドタイム信号 7 1 を出力するデッドタイム制御回路 7 0 を備えた。また、クロック制御回路 5 0 は、デッドタイム制御回路 7 0 が出力するデッドタイム信号 7 1 を受ける構成とした。その他の構成については、図 1 のセンサ回路 1 0 0 と同一であるため、同一の構成要素には同一の符号を付し、説明は省略する。30

#### 【0034】

デッドタイム制御回路 7 0 は、電位検出信号 4 1 が入力され、クロック制御回路 5 0 にデッドタイム信号 7 1 を出力する。クロック制御回路 5 0 は、H レベルのデッドタイム信号 7 1 を受けると、サンプリング信号 2 2 をマスクする。

#### 【0035】

次に、第 3 の実施形態のセンサ回路 3 0 0 の動作について説明する。

図 6 は、第 3 の実施形態のセンサ回路 3 0 0 の動作を示すタイミング図である。

図 6 において、デッドタイム信号 7 1 の電圧を  $V_{71}$  とする。また、図 2 のタイミング図と同一の動作については、その説明を省略する。40

#### 【0036】

時刻  $t_1$  において、物理量検出信号 1 2 は H レベルとなり、出力ドライバ 3 0 は出力を L レベルにする。ここで、出力端子 3 1 の容量負荷が大きい場合、出力端子 3 1 の電圧  $V_{31}$  は、出力端子 3 1 の容量負荷と出力ドライバ 3 0 のオン抵抗で決まる時定数に従って比較的長い時間をかけて静定する。

#### 【0037】

デッドタイム制御回路 7 0 は、制御信号 2 1 が H レベルになったことを受けて、すなわち休止期間への遷移後の所定期間、H レベルのデッドタイム信号 7 1 を出力する。クロック制御回路 5 0 は、デッドタイム信号 7 1 が H レベルを維持する時刻  $t_3$  まで、サンプリング信号 2 2 をマスクしてサンプリング動作を行わない。従って、クロック制御回路 5 0 50

は、時刻  $t_1$  から時刻  $t_3$  までの電位検出信号 4 1 の H レベルを読み込まない。

**【0038】**

時刻  $t_2$  において、出力端子 3 1 の電圧  $V_{31}$  は電位検出回路 4 0 の判定閾値  $V_{th}$  を下回るので、電位検出信号 4 1 は L レベルになる。よって、デッドタイム信号 7 1 が H レベルを維持する時間は、電圧  $V_{31}$  が判定閾値  $V_{th}$  を下回る時間より長くすればよい。

**【0039】**

従って、クロック制御回路 5 0 は、時刻  $t_4$  において出力端子 3 1 にノイズが重畠したとしても、時刻  $t_1$  以降の信号パターンを H L L H と認識しないので、誤ってテストモードに切替えることが無い。

**【0040】**

このように第 3 の実施形態のセンサ回路 3 0 0 は、クロック制御回路 5 0 にデッドタイム信号 7 1 を出力するデッドタイム制御回路 7 0 を備えたので、誤ってテストモードに切替えられるという誤動作をより確実に防止できる。

**【0041】**

なお、デッドタイム制御回路 7 0 は、フリップフロップによる論理回路で構成してもよいし、定電流源と容量素子と閾値回路による計時回路で構成してもよい。

また、デッドタイム信号 7 1 は、制御信号 2 1 が H レベルになったことを受けて H レベルを出力すると説明したが、発明の趣旨に合えばどのような信号を起点にしても良い。

**【0042】**

<第 4 の実施形態>

20

図 7 は、第 4 の実施形態のセンサ回路 4 0 0 のブロック図である。第 4 の実施形態のセンサ回路 4 0 0 は、図 1 のセンサ回路 1 0 0 に追加してリセット信号 8 1 を出力するリセット回路 8 0 を備えた。また、クロック制御回路 5 0 は、リセット回路 8 0 が出力するリセット信号 8 1 を受ける構成とした。その他の構成については、図 1 のセンサ回路 1 0 0 と同一であるため、同一の構成要素には同一の符号を付し、説明は省略する。

**【0043】**

リセット回路 8 0 は、電位検出信号 4 1 が入力され、クロック制御回路 5 0 へリセット信号 8 1 を出力する。クロック制御回路 5 0 は、H レベルのリセット信号 8 1 を受けると、信号パターンを保持するシフトレジスタをリセットする。

**【0044】**

30

次に、第 4 の実施形態のセンサ回路 4 0 0 の動作について説明する。

図 8 は、第 4 の実施形態のセンサ回路 4 0 0 の動作を示すタイミング図である。

図 8 において、リセット信号 8 1 の電圧を  $V_{81}$  とする。また、図 2 のタイミング図と同一の動作については、その説明を省略する。

**【0045】**

時刻  $t_1$  において、物理量検出信号 1 2 は H レベルとなり、出力ドライバ 3 0 は出力を L レベルにする。リセット信号 8 1 は、休止期間になると L レベルにリセットされる。

時刻  $t_2$  において、外部からのノイズが出力端子 3 1 に重畠すると、図に示すように電圧  $V_{31}$  が変動し、H レベルの電位検出信号 4 1 が出力される。従って、クロック制御回路 5 0 は、サンプリング信号 2 2 によって電位検出信号 4 1 の H レベルを読み込む。

40

**【0046】**

ここで、リセット回路 8 0 は、電位検出信号 4 1 の信号の幅を検出する機能を有する。

例えば、図 8 の時刻  $t_2$  のように幅が小さいことを検出すると、例えば時刻  $t_3$  において、クロック制御回路 5 0 へ H レベルのリセット信号 8 1 を出力する。クロック制御回路 5 0 は、H レベルのリセット信号 8 1 を受けると、信号パターンを保持するシフトレジスタをリセットする。即ち、時刻  $t_2$  でシフトレジスタに読み込まれた H レベルはリセットされる。

従って、時刻  $t_4$  において、外部からのノイズが出力端子 3 1 に重畠したとしても、クロック制御回路 5 0 は、電位検出信号 4 1 を誤って H L L H と認識することがなくなる。

**【0047】**

50

このように第4の実施形態のセンサ回路400は、クロック制御回路50にリセット信号81を出力するリセット回路80を備えたので、誤ってテストモードに切替えられるという誤動作をより確実に防止できる。

なお、リセット信号81は、図8では、制御信号21がHレベルになったことを受けてLレベルになっているが、例えばワンショットパルスにしても良い。

#### 【0048】

以上説明したように、本発明のセンサ回路は、サンプリング信号22に同期して電位検出信号41をサンプリングするクロック制御回路50と、休止期間においてサンプリング信号22を出力するクロック発生回路20と、を備えたので、誤ってテストモードに切替えられるという誤動作をより確実に防止できる。

10

#### 【0049】

なお、実施形態において、物理量検出部10を磁気センサ回路としての説明したが、物理量の検出結果を出力端子31から2値信号として出力するような構成であれば、これに制限されるものではない。例えば、物理量検出部10は、温度センサ回路や光センサ回路であってもよい。

#### 【0050】

また、本発明のセンサ回路は、必ずしもこの構成やセンサ素子に制限されるものではなく、発明の趣旨を逸脱しない範囲で様々な変更や組み合わせなどが可能である。例えば、各実施形態の回路を適宜組み合わせても良い。更に、物理量検出部10と出力端子31とクロック制御回路50の組合せを複数備えて、夫々の出力端子に強制的に電圧を印加して、その組み合わせでテストモードに切替えるような構成としても良い。

20

#### 【符号の説明】

##### 【0051】

- 10 物理量検出部

- 20 クロック発生回路

- 30 出力ドライバ

- 31 出力端子

- 40 電位検出回路

- 50 クロック制御回路

- 60 カウンタ

- 70 デッドタイム制御回路

- 80 リセット回路

- 100、200、300、400 センサ回路

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開2009-031225(JP,A)

特開2006-153699(JP,A)

米国特許出願公開第2009/0273340(US,A1)

特開平11-016395(JP,A)

(58)調査した分野(Int.Cl., DB名)

I P C      G 0 1 R    3 3 / 0 0 - 3 3 / 2 6、

1 5 / 0 0 - 1 7 / 2 2、

1 9 / 0 0 - 1 9 / 3 2、

3 1 / 2 8、

3 1 / 3 0、

3 1 / 3 0 2、

3 1 / 3 1 6、

3 1 / 3 1 7、

3 1 / 3 1 8 3、

3 1 / 3 1 8 5、

3 1 / 3 1 9、

1 1 / 0 0 - 1 1 / 6 6、

2 1 / 0 0 - 2 2 / 1 0、

3 5 / 0 0 - 3 5 / 0 6、

G 0 1 N    2 7 / 7 2 - 2 7 / 9 0、

H 0 1 L    2 7 / 2 2、

2 9 / 8 2、

4 3 / 0 0 - 4 3 / 1 4