(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

16 April 2015 (16.04.2015)

WIPO | PCT

(10) International Publication Number

WO 2015/054433 A1

(51) International Patent Classification:

*G06F 13/42 (2006.01)*

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) International Application Number:

PCT/US2014/059776

(22) International Filing Date:

8 October 2014 (08.10.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/888,475 8 October 2013 (08.10.2013) US

61/927,102 14 January 2014 (14.01.2014) US

61/974,910 3 April 2014 (03.04.2014) US

(71) Applicant: **QUALCOMM INCORPORATED** [US/US];

ATTN: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

(72) Inventor: **SENGOKU, Shoichiro**; 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

(74) Agent: **LOZA, Julio**; Loza & Loza LLP, 305 North Second Avenue #127, Upland, California 91786 (US).

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(54) Title: COEXISTENCE OF I2C SLAVE DEVICES AND CAMERA CONTROL INTERFACE EXTENSION DEVICES ON A SHARED CONTROL DATA BUS

**FIG. 2**

(57) Abstract: A plurality of slave devices is coupled to a control data bus along with at least one master device that is managing access of slave devices to the control data bus. At least one slave device operates in a sI2C protocol mode of operation and at least one other slave device operates in a CCle mode of operation. At least the slave devices using sI2C protocol mode use the control data bus for interrupt requests. In order to maintain the integrity of CCle communications, the slave devices using the sI2C protocol mode disables issuing IRQs when the control data bus operates according to the CCle mode.

WO 2015/054433 A1

**COEXISTENCE OF I2C SLAVE DEVICES AND CAMERA CONTROL

INTERFACE EXTENSION DEVICES ON A SHARED CONTROL DATA BUS**

**CROSS-REFERENCE TO RELATED APPLICATIONS**

**[0001]** The present Application for Patent claims priority to Provisional Application No. App. No.: 61/888,475, entitled “Coexistent of I2C Slave Devices and Camera Control Interface Extension Devices on a Shared Control Data Bus” filed October 8, 2013, and to Provisional Application No. App. No.: 61/974,910, entitled “Coexistent of I2C Slave Devices and Camera Control Interface Extension Devices on a Shared Control Data Bus” filed April 3, 2014, and to Provisional Application No. App. No.: 61/927,102, entitled “Camera Control Interface Extension With In-Band Interrupt” filed January 14, 2014, all of which are assigned to the assignee hereof and hereby expressly incorporated by reference herein.

**Field**

**[0002]** The present disclosure pertains to enabling multimode operations over a shared bus and, more particularly, enabling devices with different protocols to share a single bus.

**Background**

**[0003]** Inter Integrated Circuit (hereinafter “I2C” and also referred to as  $I^2C$ ) is a multi-master serial single-ended bus used for attaching low-speed peripherals to a motherboard, embedded system, cellphone, or other electronic devices. The I2C bus includes a clock (SCL) and data (SDA) lines with 7-bit addressing. The bus has two roles for nodes or devices: master device and slave device. A master node/device is a node/device that generates the clock and initiates communication with a slave node/device. A slave node/device is a node that receives the clock and responds when addressed by the master. The I2C bus is a multi-master bus which means any number of master devices can be present. Additionally, master and slave roles may be changed between messages (after a STOP is sent). I2C defines basic types of messages, each of which begins with a START and ends with a STOP.

**[0004]** In this context of a camera implementation, unidirectional transmissions may be used to capture an image from a sensor and transmit such image data to memory in a baseband processor, while control data may be exchanged between the baseband processor and the sensor as well as other peripheral devices. In one example, a Camera Control Interface (CCI) protocol may be used for such control data between the baseband processor and the image sensor (and/or one or more slave devices). In one example, the CCI protocol may be implemented over an I2C serial bus between the image sensor and the baseband processor.

**[0005]** As technology evolves, there is a need for “hot plug” functionality on an I2C bus. By “hot plug”, it is meant that devices such as a slave device may be plugged into an already active bus (i.e., without shutting down the bus). This hot plug functionality is achieved with what is referred to as subset I2C (i.e., sI2C). The sI2C utilizes the control data bus (SCL and SDA together) as the means for slave devices to perform interrupt requests (IRQ). Additionally, because of a desire to increase speed of the CCI protocol, a CCI extension (CCIE) protocol is described herein that increases speed over the CCI protocol. However, having slave devices performing IRQs using the SDA is incompatible with the CCIE protocol which provides a dedicated IRQ line.

**[0006]** Therefore, a way is needed to increase speed over the CCI protocol and at the same time enable sI2C protocol slave devices to coexist with CCIE devices and be hot pluggable onto the CCIE bus.

## SUMMARY

**[0007]** A device is provided comprising a shared bus, a first slave device, a second slave device, and/or a master device. The first slave device may be coupled to the shared bus and is configured to: (a) operate according to a first protocol mode including issuing in-band interrupt requests over the shared bus; (b) monitor the shared bus for an entry call indicating the shared bus is switching to a second protocol mode; and/or (c) upon detection of the entry call, disable the first slave device from making in-band interrupt requests over the shared bus.

**[0008]** The second slave device may be coupled to the shared bus and is configured to: (a) operate according to the second protocol mode including issuing side-band interrupt requests over an interrupt bus or in-band interrupt request over the shared bus; and/or (b) detect the entry call over the shared bus, the entry call transmitted according to the second protocol mode.

**[0009]** The master device may be coupled to the shared bus and configured to: (a) operate according to both the first protocol mode and the second protocol mode; (b) manage communications over the shared bus; (c) send the entry call over the shared bus indicating the shared bus is switching to a second protocol mode, where the entry call is sent according to the first protocol mode; (d) detect interrupt requests from slave devices according to both the first protocol mode and the second protocol mode; and/or (e) respond to the interrupt requests by granting a requesting slave device access to the shared bus.

**[0010]** The master device may be further configured to send an exit call over the shared bus indicating the shared bus is switching to the first protocol mode, where the exit call is sent according to both the second protocol mode and the first protocol mode.

**[0011]** For in-band interrupts, the second protocol defines an interrupt period within symbols transmitted over the shared bus during which one or more slave devices coupled to the shared bus can assert an interrupt request on a first line of the shared bus while a second line of the shared bus is used by the master device for a heartbeat transmission. In one implementation, the master device and second slave device may be configured to internally mask the first line of the shared bus during the interrupt period.

**[0012]** The master device may be configured to send an interrupt group inquiry call to all slave devices that operate according to the second protocol mode on the shared bus, where such interrupt group inquiry call provides slots in which any asserting slave devices can respond.

**[0013]** The second slave device may be further configured to receive data or commands over the shared bus according to the second protocol mode when the shared bus operates according to the second protocol mode.

**[0014]** The first slave device may be further configured to send an interrupt request over a dedicated interrupt line or bus separate from the shared bus while the shared bus operates according to the second protocol mode.

**[0015]** The device may also include an interrupt router slave device configured to receive interrupt requests from the first slave device over a dedicated line and send the received interrupt request over the dedicated interrupt line or bus according to the second protocol.

**[0016]** In one example, the shared bus may include a first line and a second line. When the shared bus operates according to the first protocol mode, the first line is used for data transmissions and the second line is used for a first clock signal. When the

shared bus operates according to the second protocol mode, both the first line and second line are used for data transmissions while a second clock signal is embedded in symbol-to-symbol transitions with the data transmissions.

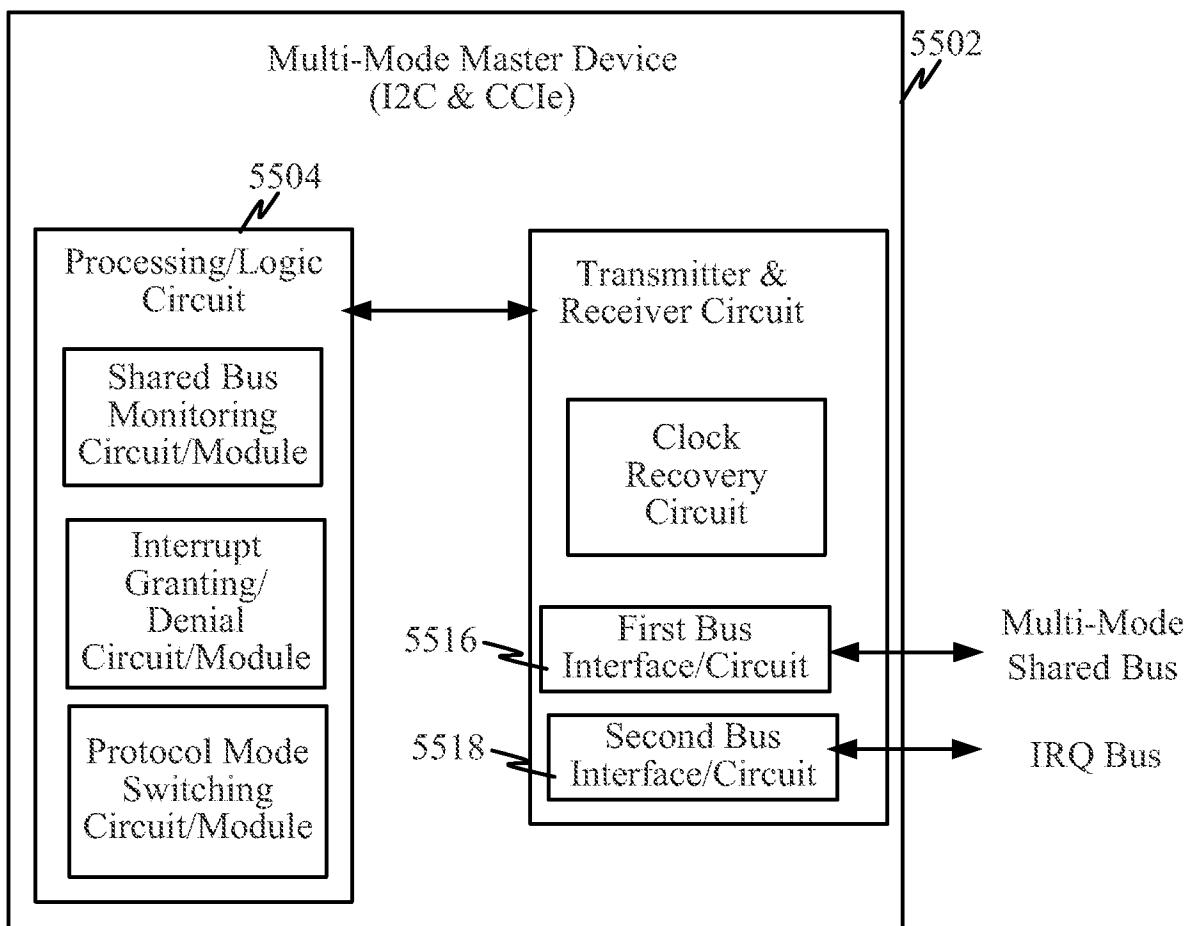

**[0017]** A multi-mode master device may include a first bus interface, a second bus interface, and a processing circuit. The first bus interface may serve to couple to other devices coupled to a shared control data bus, the data bus dynamically configured to operate in either a first protocol mode or a second protocol mode. The second bus interface may serve to couple to a dedicated interrupt line used by at least a subset of the other devices and which issue interrupt requests over the dedicated interrupt line in the second protocol mode. The processing circuit may be configured to: (a) manage data transfers over a shared bus to which a plurality of other devices are coupled, wherein at least a first subset of the other devices operate according to a first protocol mode and a second subset of the other devices operate according to a second protocol mode incompatible with the first protocol mode; (b) dynamically switch operation of the shared bus between the first protocol and second protocol mode by: (1) sending an entry call over the shared bus indicating that the shared bus is to operate according to the second protocol mode, and/or (2) sending an exit call over the shared bus indicating that the shared bus is to operate according to the first protocol mode

**[0018]** The master device may be further configured to: (a) receive interrupt requests from the first subset of devices over the shared bus when the shared bus operates according to the first protocol mode; (b) receive interrupt requests from the second subset of devices over a dedicated interrupt bus when the shared bus operates according to the second protocol mode, and/or (c) receive interrupt requests from the first subset of devices over the dedicated interrupt bus when the shared bus operates according to the second protocol mode. In one implementation, no interrupt requests are received from the first subset of devices when the shared bus operates according to the second protocol mode.

**[0019]** The shared bus includes a first line and a second line. When the shared bus operates according to the first protocol mode, the first line used for data transmissions and the second line used for a first clock signal. When the shared bus operates according to the second protocol mode, both the first line and second line are used for data transmissions while a second clock signal is embedded in symbol-to-symbol transitions with the data transmissions.

**[0020]** The second protocol may define an interrupt period within symbols transmitted over the shared bus during which the second subset of the other devices can assert an interrupt request on a first line of the shared bus while a second line of the shared bus is used by the master device for a heartbeat transmission.

**[0021]** The master device may also be configured to internally mask the first line of the shared bus during the interrupt period.

**[0022]** In one implementation, in response to an in-band interrupt request while operating according to the second protocol mode, the master device may send an interrupt group inquiry call to all slave devices that operate according to the second protocol mode on the shared bus, where such interrupt group inquiry call provides slots in which any asserting slave devices can respond.

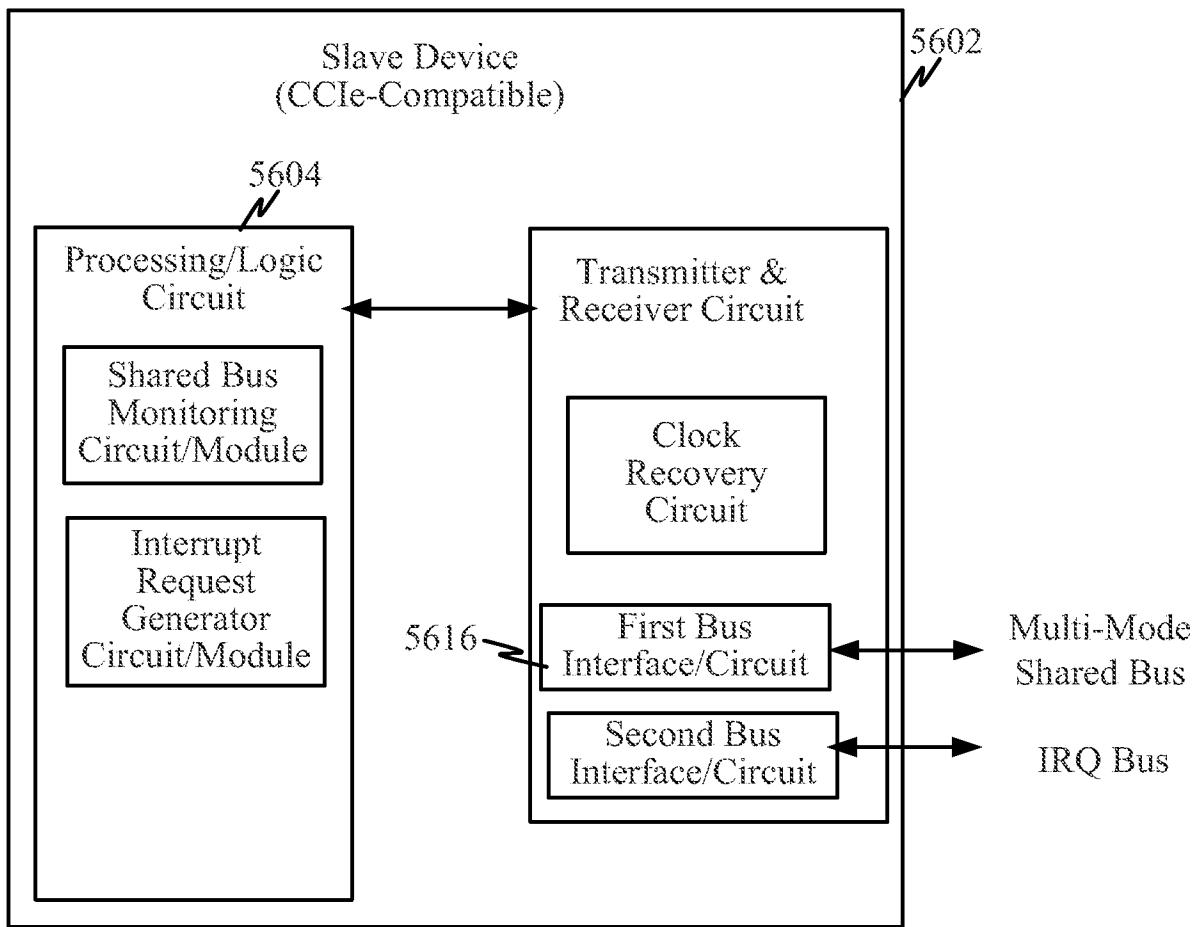

**[0023]** A slave device may comprise a bus interface and a processing circuit. The bus interface may serve to couple to a shared bus shared with a plurality of other devices, wherein at least a first subset of the other devices operate according to a first protocol mode and the slave device operates according to a second protocol mode. The processing circuit may be configured to:

**[0024]** (a) detect an entry call over the shared bus from a master device capable of operating according to the first protocol mode and the second protocol mode, the entry call indicating that the shared bus is to operate according to the second protocol mode; (b) send an interrupt request (IRQ) either in-band over the shared bus or side-band over a separate path to the master device; (c) communicate over the shared bus according to the second protocol mode; (d) monitor the shared bus for an exit call from the master device; and/or (e) disable the slave device from communicating over the shared bus upon detection of an exit call from the master device. The exit call may serve to indicate to the slave device that the shared bus is to operate according to the first protocol mode.

**[0025]** The shared bus may include a first line and a second line. When the shared bus operates according to the first protocol mode, the first line used for data transmissions and the second line used for a first clock signal. When the shared bus operates according to the second protocol mode, both the first line and second line are used for data transmissions while a second clock signal is embedded in symbol-to-symbol transitions with the data transmissions.

**[0026]** A slave device may include a bus interface and a processing circuit. The bus interface may serve to couple to a shared bus shared with a plurality of other devices, wherein the slave device operates according to a first protocol mode and at least a first

subset of the other devices operate according to a second protocol mode. The processing circuit may serve to couple to the bus interface and configured to: (a) detect an entry call over the shared bus from a master device capable of operating according to the first protocol mode and the second protocol mode, the entry call indicating that the shared bus is to operate according to the second protocol mode; and/or (b) disable the slave device from making in-band interrupt requests over the shared bus upon detection of the entry call.

**[0027]** The processing circuit is further configured to monitor the shared bus for an exit call from the master device, the exit call indicating that the shared bus is to operate according to the first protocol mode. The shared bus includes a first line and a second line, when the shared bus operates according to the first protocol mode, the first line used for data transmissions and the second line used for a first clock signal, and when the shared bus operates according to the second protocol mode, both the first line and second line are used for data transmissions while a second clock signal is embedded in symbol-to-symbol transitions with the data transmissions.

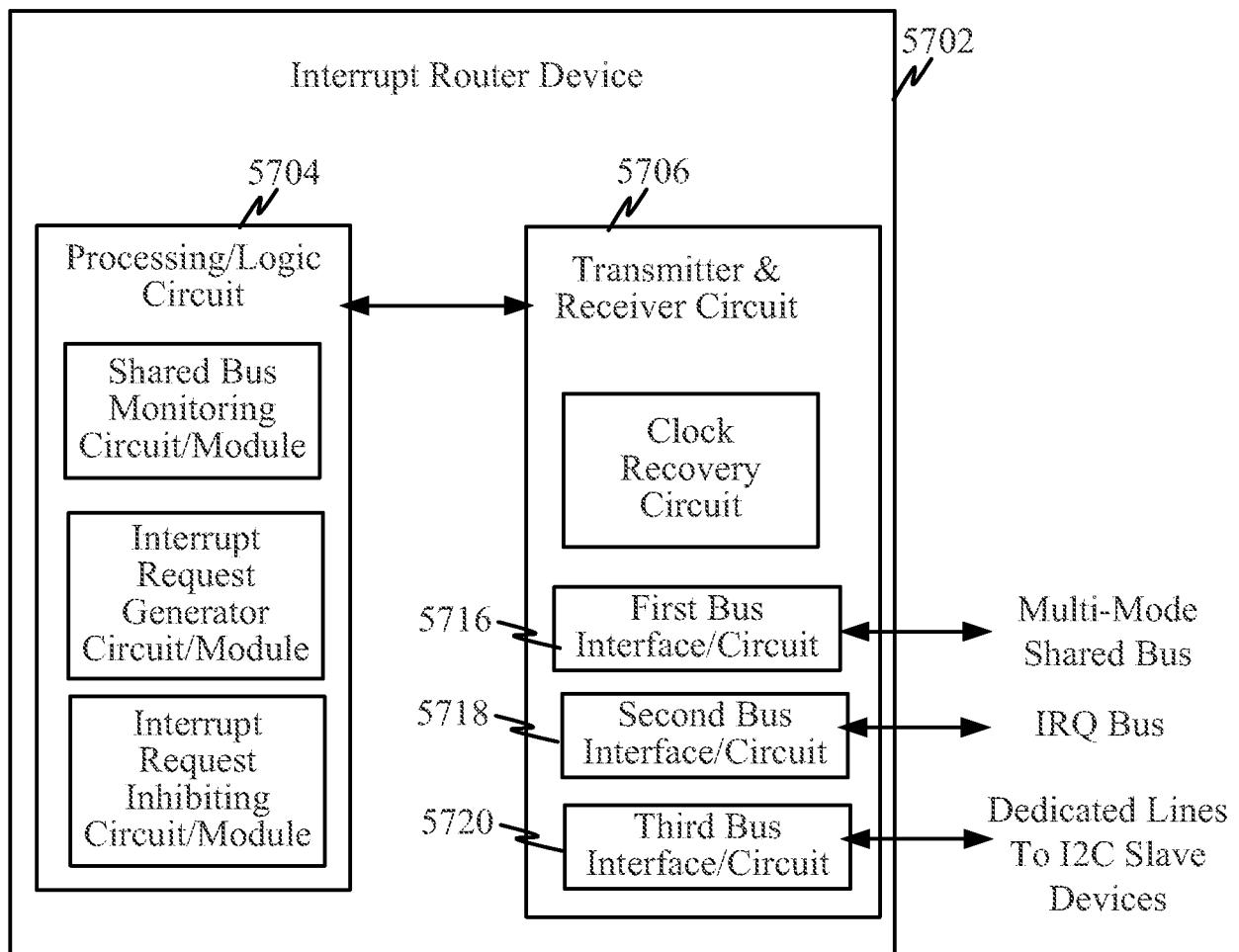

**[0028]** An interrupt request router slave device may include a first bus interface, a second bus interface, a third bus interface, and a processing circuit. The first bus interface may serve to couple to a shared control data bus, the data bus dynamically configured to operate in either a first protocol mode or a second protocol mode. The second bus interface may serve to couple to at least one subset of other slave device coupled to the shared bus, the subset of other slave devices operating according to the first protocol mode including in-band interrupt requests over the shared control data bus. The third bus interface may serve to couple to a dedicated interrupt line used in the second protocol mode to issue interrupt request to a master device that manages the shared bus. The processing circuit may be configured to: (a) receive an interrupt request over the second bus interface from a slave device within the first subset of slave devices; and/or (b) route the received interrupt request to the master device via the third bus interface.

## DRAWINGS

**[0029]** Various features, nature, and advantages may become apparent from the detailed description set forth below when taken in conjunction with the drawings in which like reference characters identify correspondingly throughout.

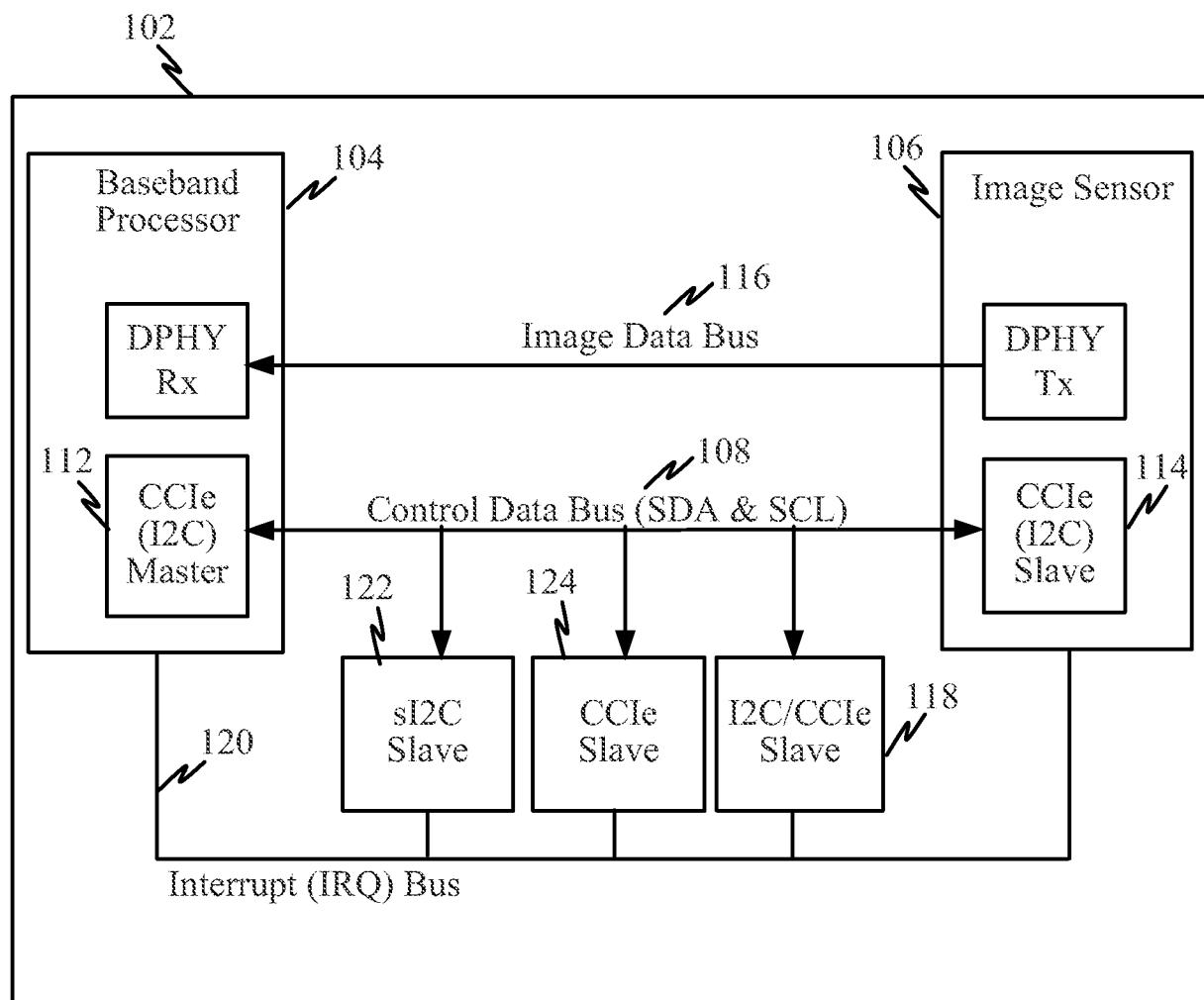

[0030] FIG. 1 is a block diagram illustrating a device having a baseband processor and an image sensor and implementing an image data bus and a multi-mode control data bus.

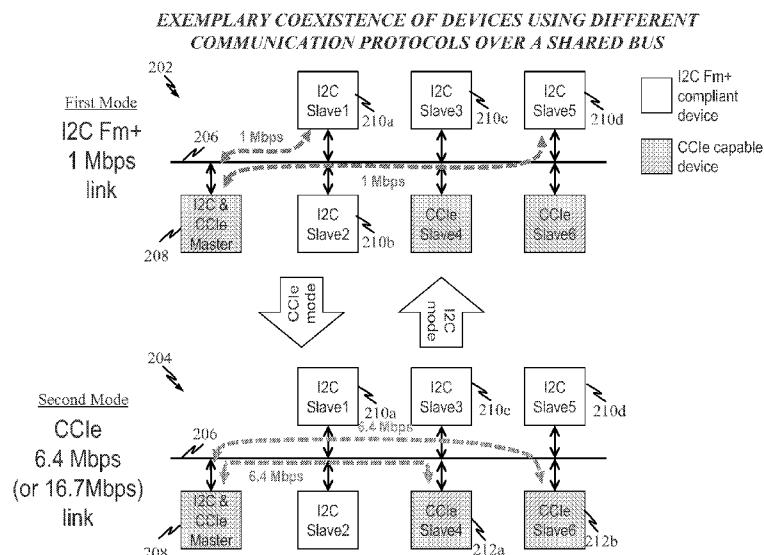

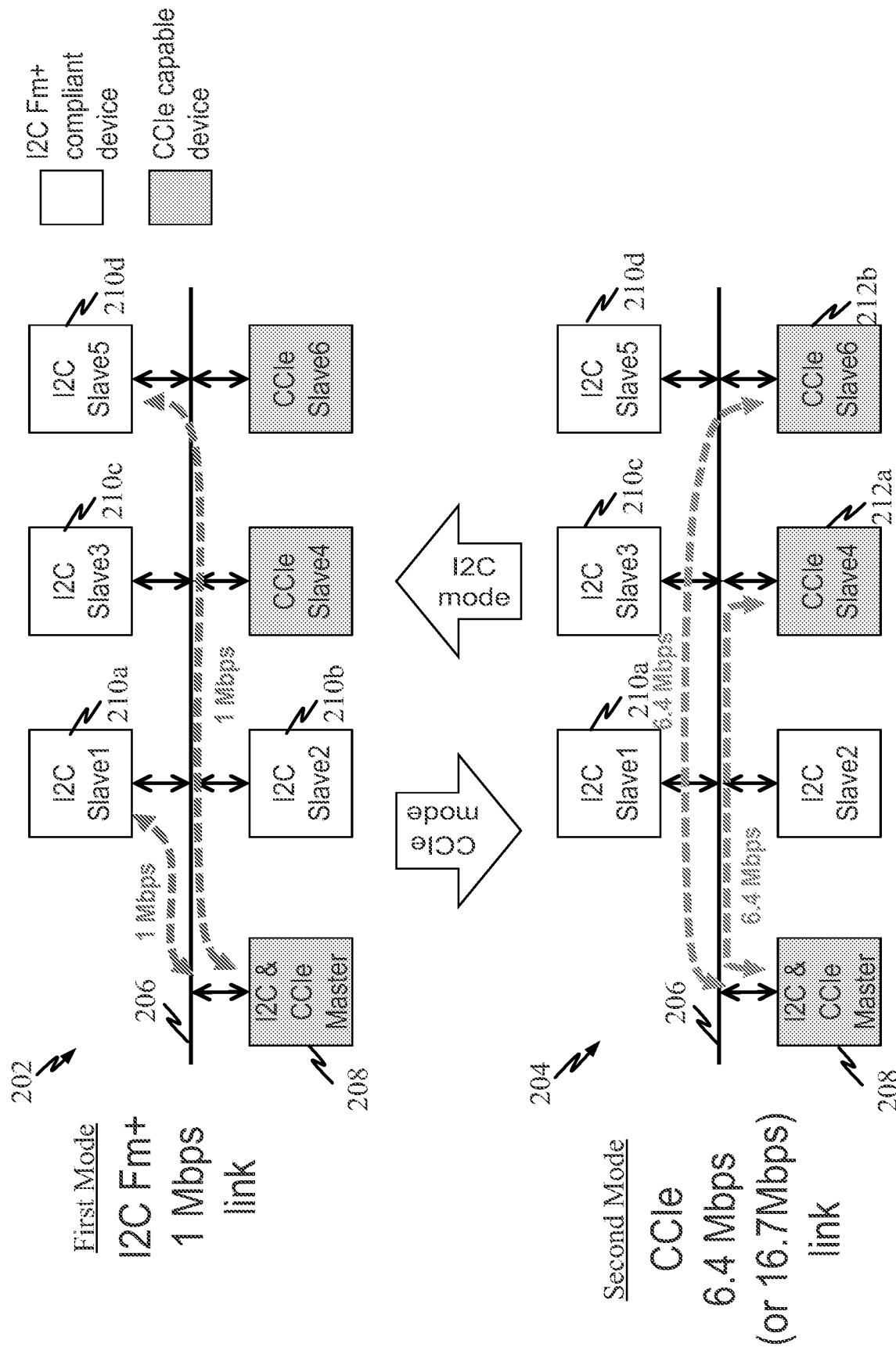

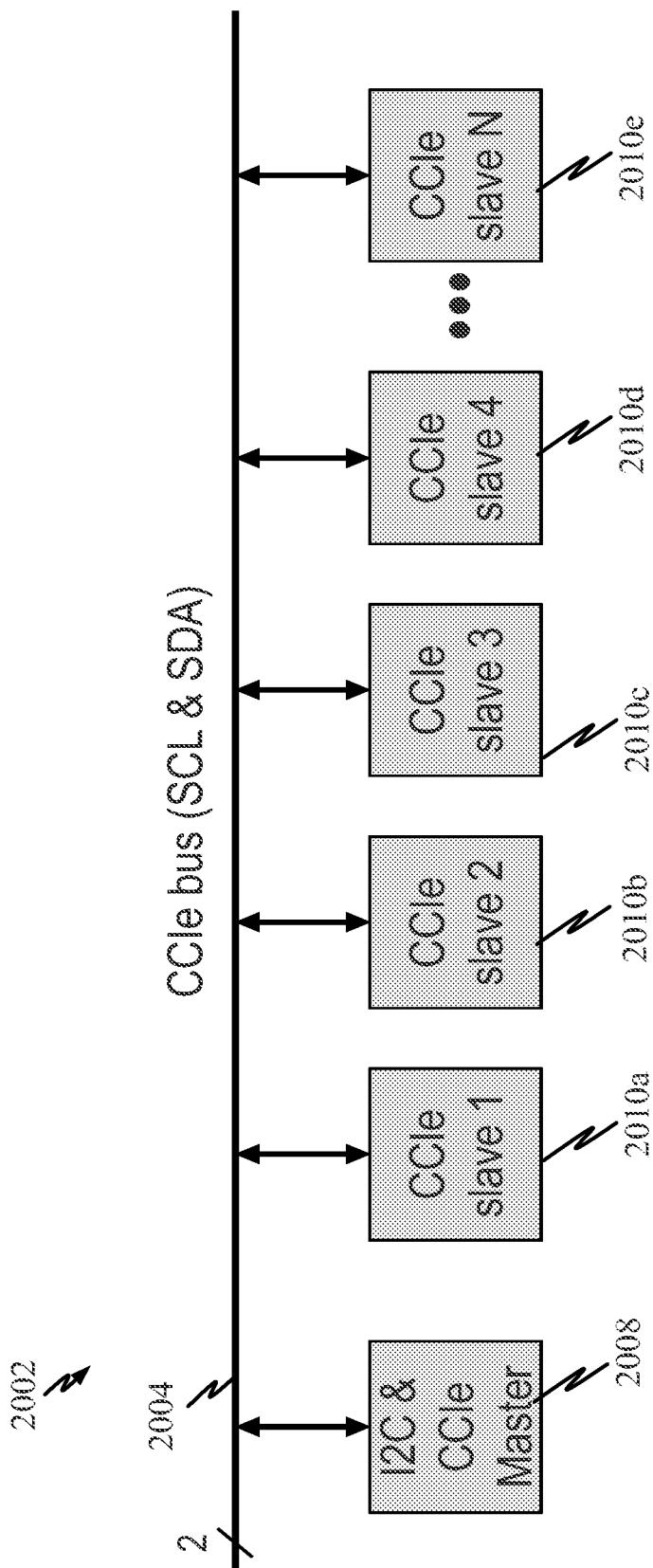

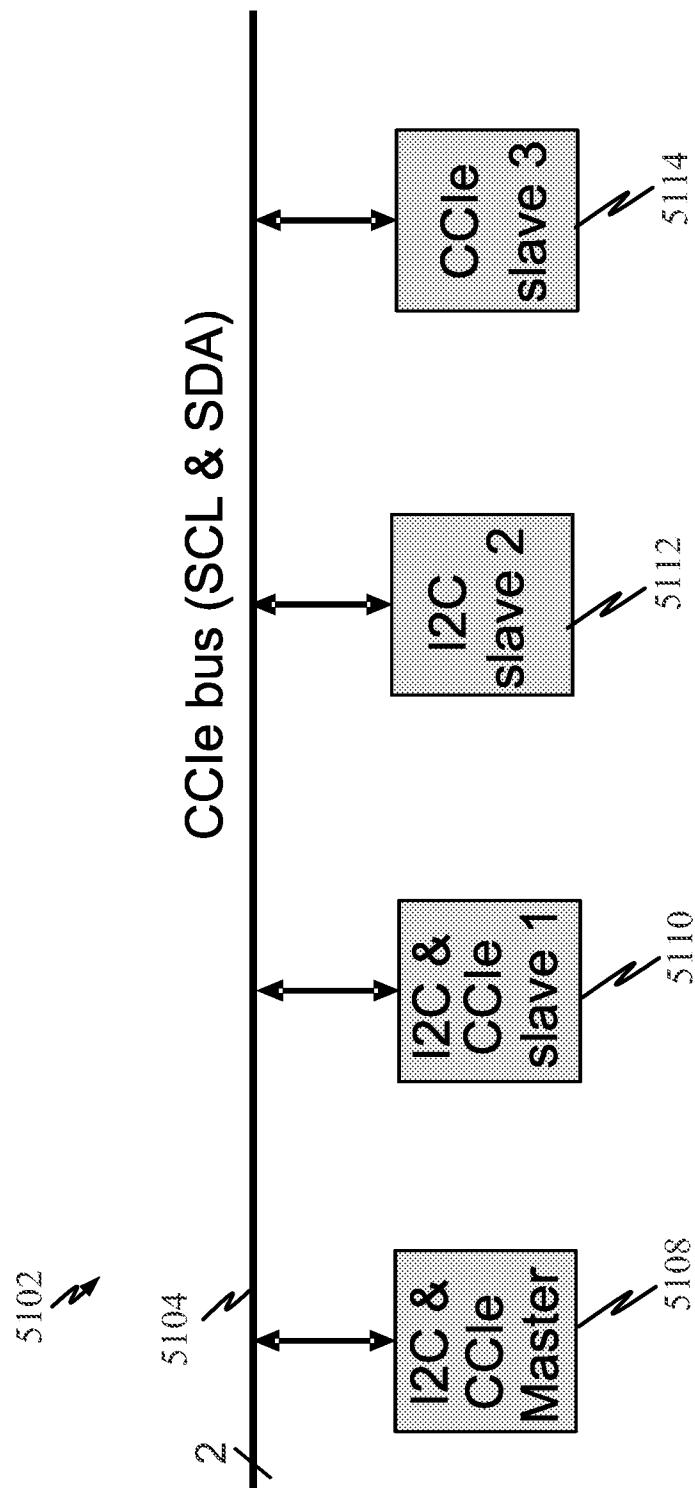

[0031] FIG. 2 is a block diagram illustrating the exemplary coexistence of I2C mode (e.g., legacy CCI or first mode) and CCIe mode (e.g., second mode) over a shared I2C bus (e.g., control data bus).

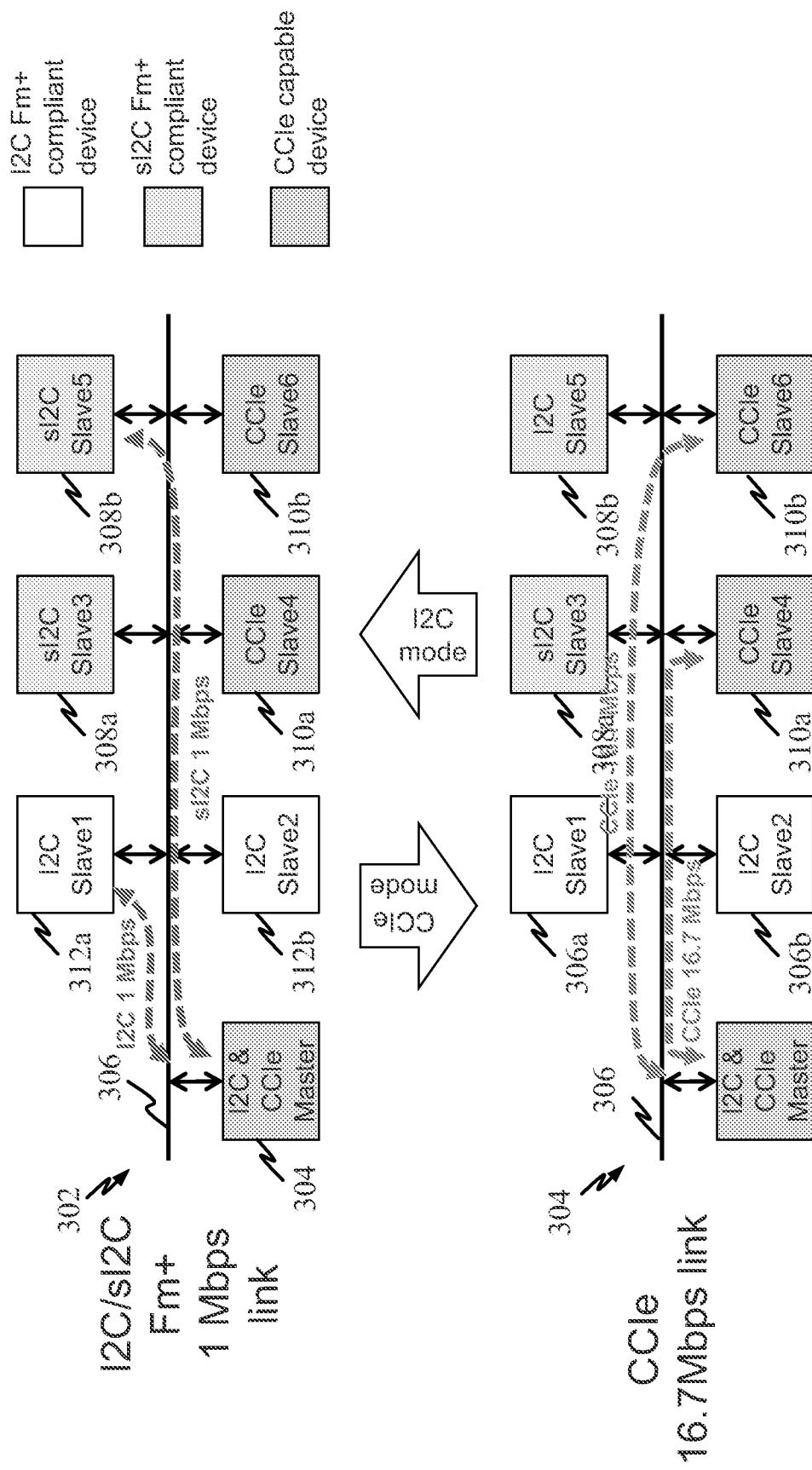

[0032] FIG. 3 is a block diagram illustrating the coexistence of I2C mode (i.e., legacy CCI) and CCIe mode over a common I2C bus including one or more sI2C slave devices, a multi-mode I2C and CCIe master device, one or more I2C slave devices, and one or more CCIe slave devices.

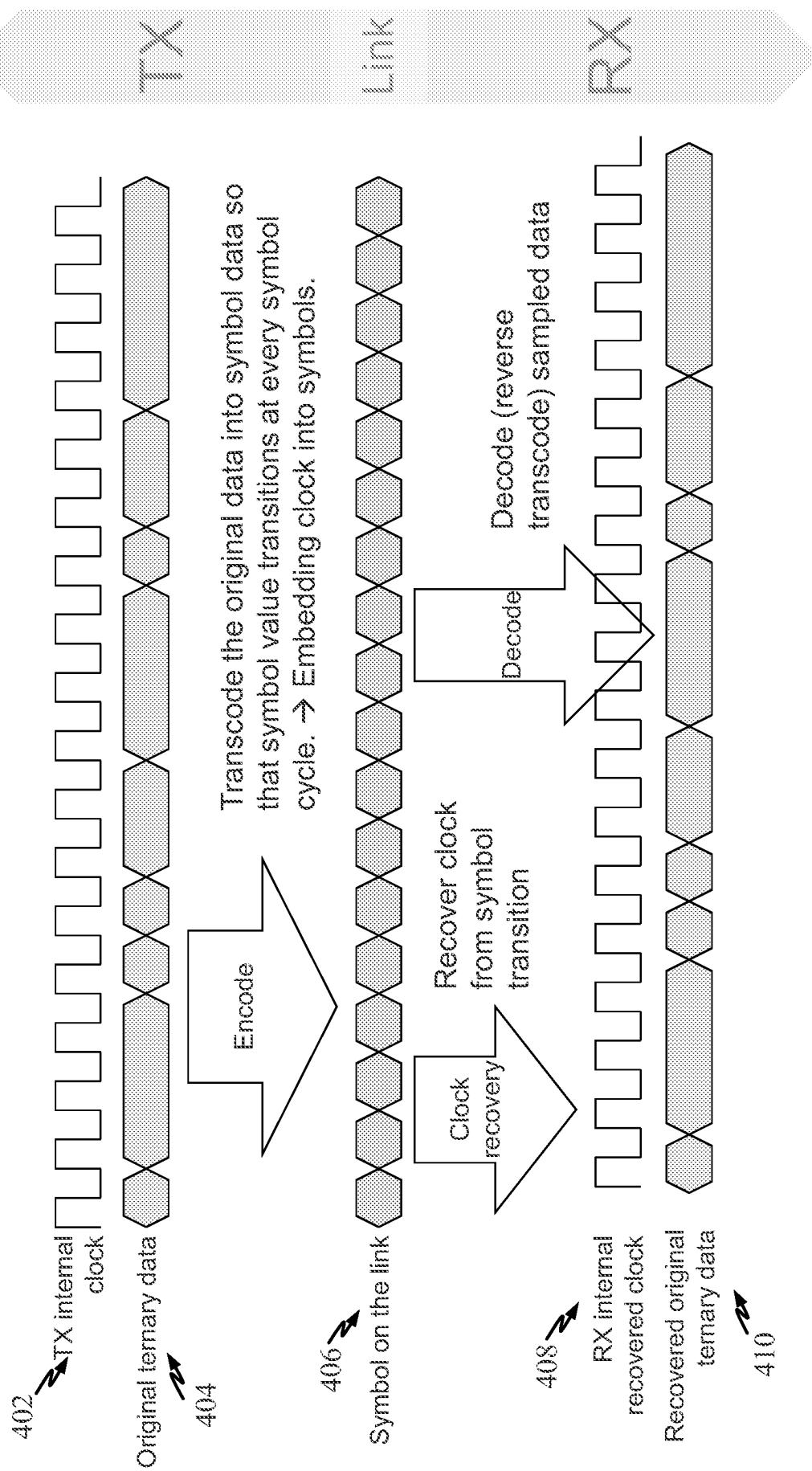

[0033] FIG. 4 illustrates how a clock may be embedded within data symbols, thereby allowing the use of both I2C wires (i.e., SDA line and SCL line) for data transmissions.

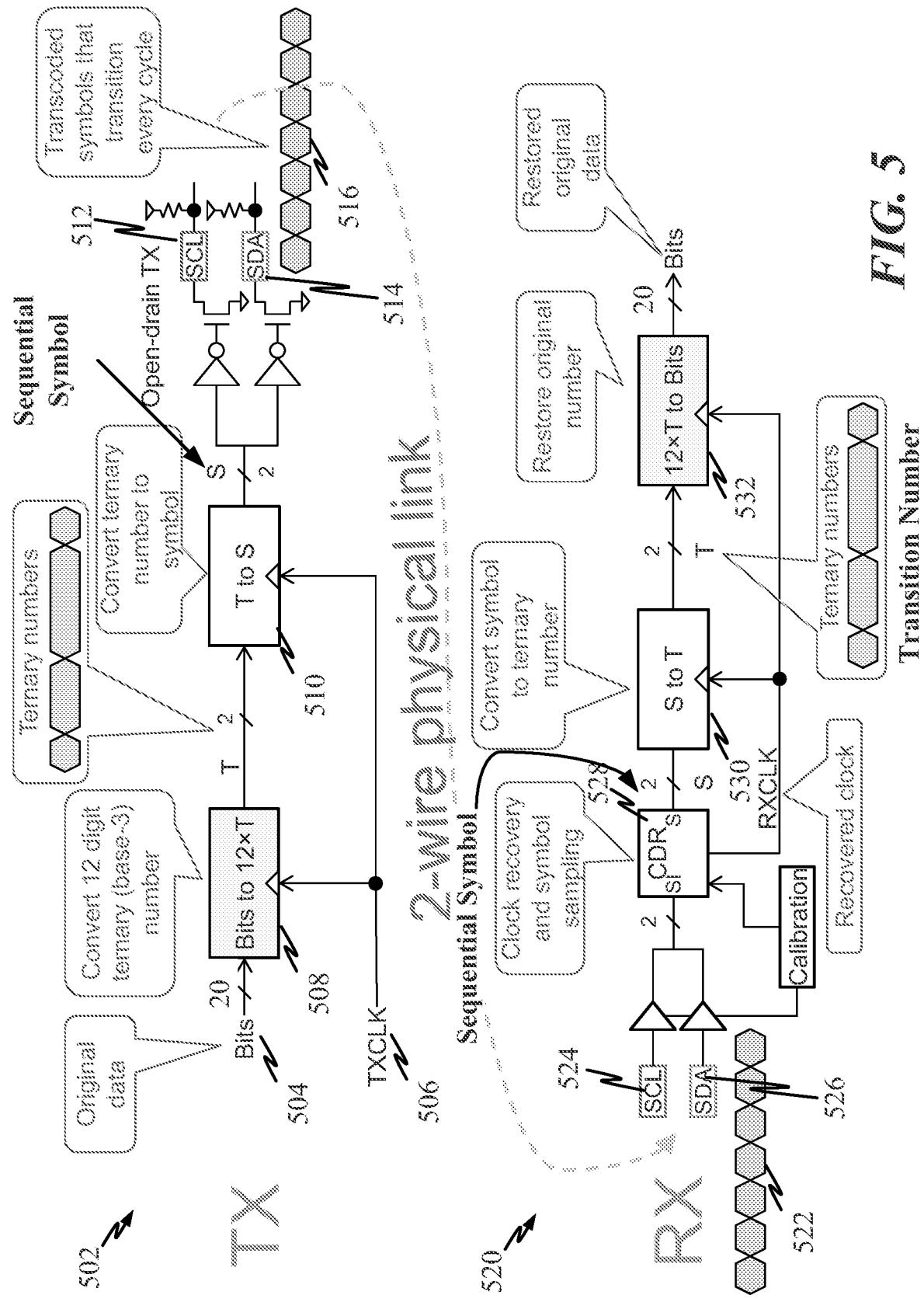

[0034] FIG. 5 is a block diagram illustrating an exemplary method for transcoding of data bits into transcoded symbols at a transmitter to embed a clock signal within the transcoded symbols.

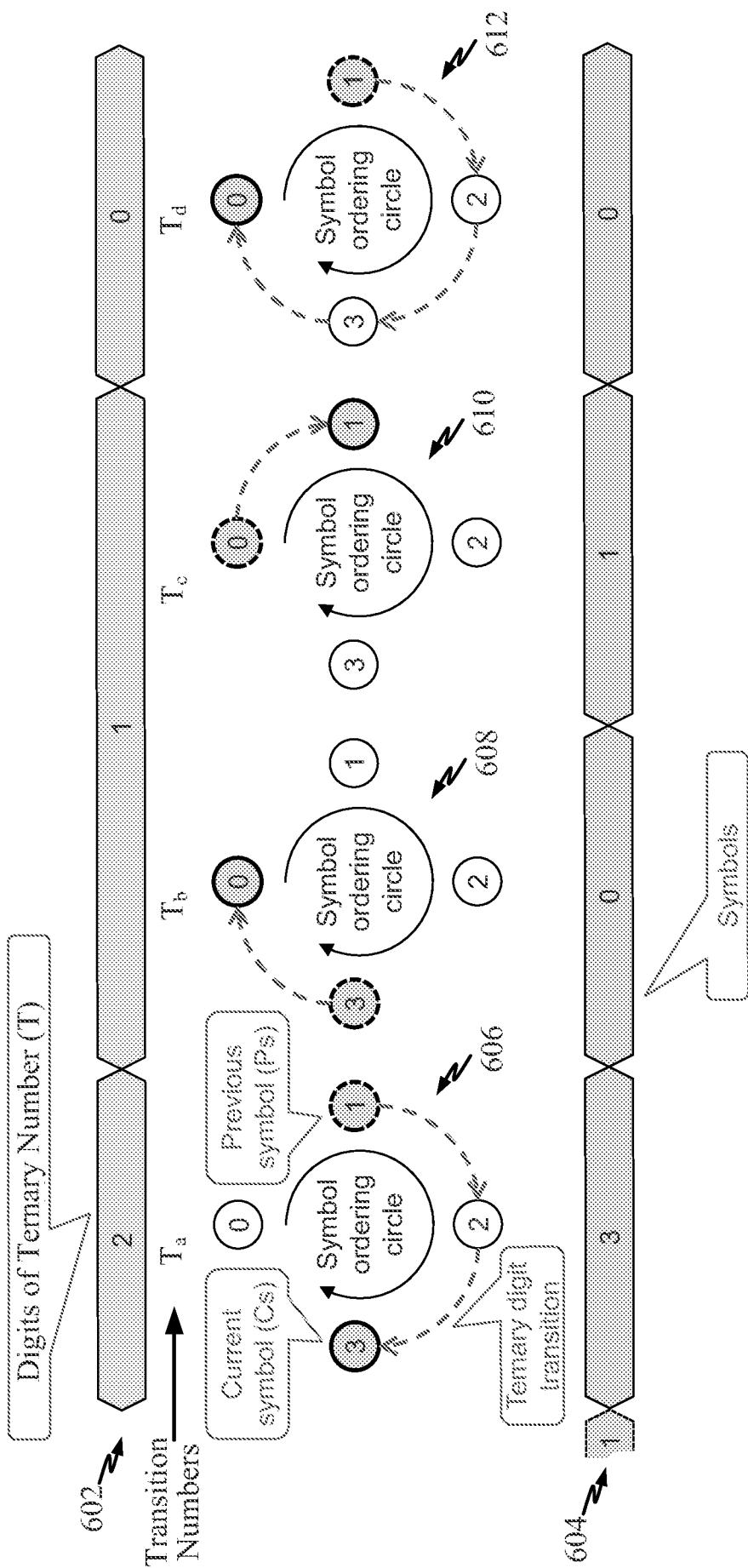

[0035] FIG. 6 illustrates an exemplary conversion between transition numbers and sequential symbols.

[0036] FIG. 7 further illustrates an exemplary conversion between transition numbers and sequential symbols.

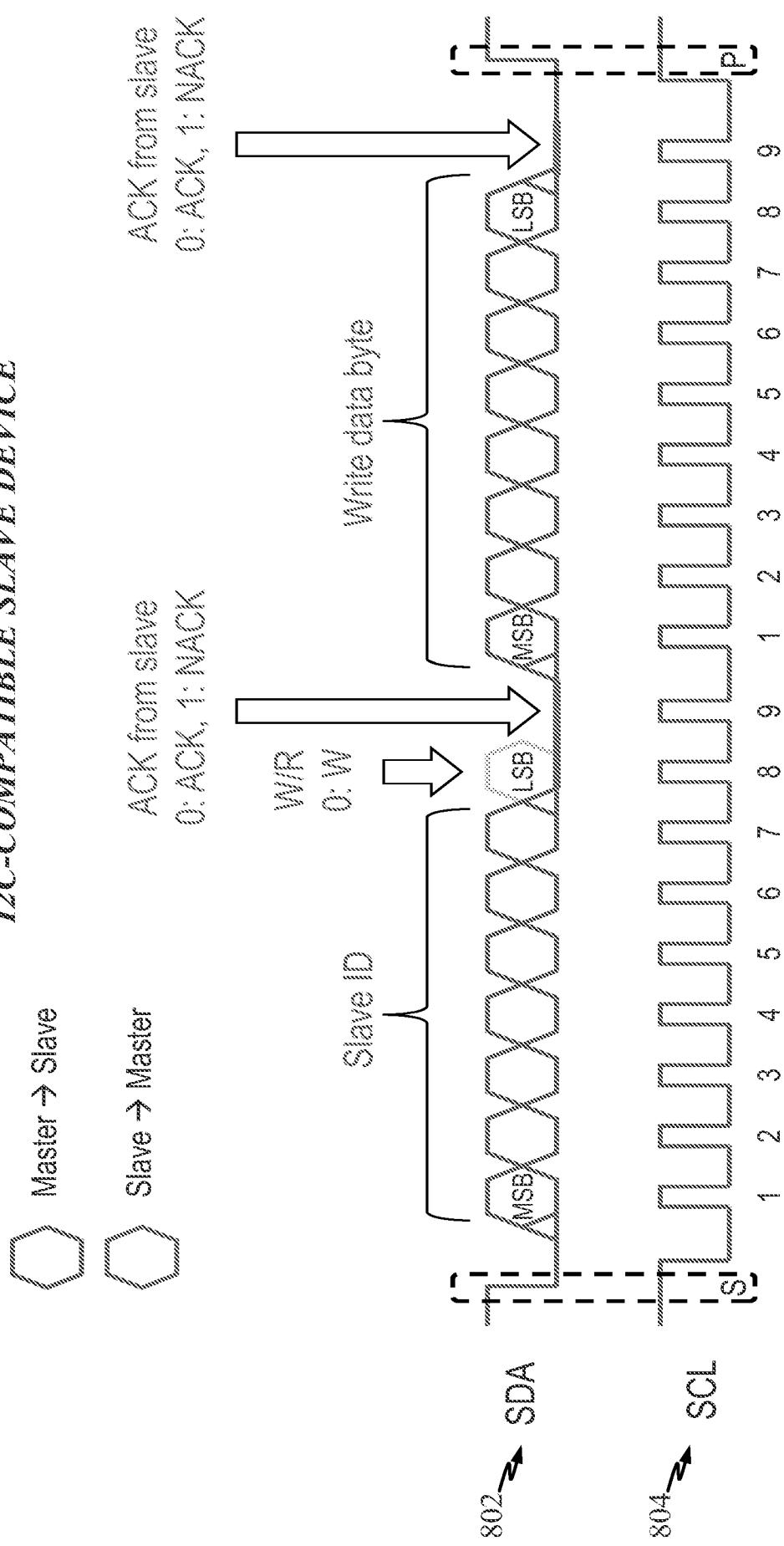

[0037] FIG. 8 illustrates a timing diagram of an I2C one byte write data operation.

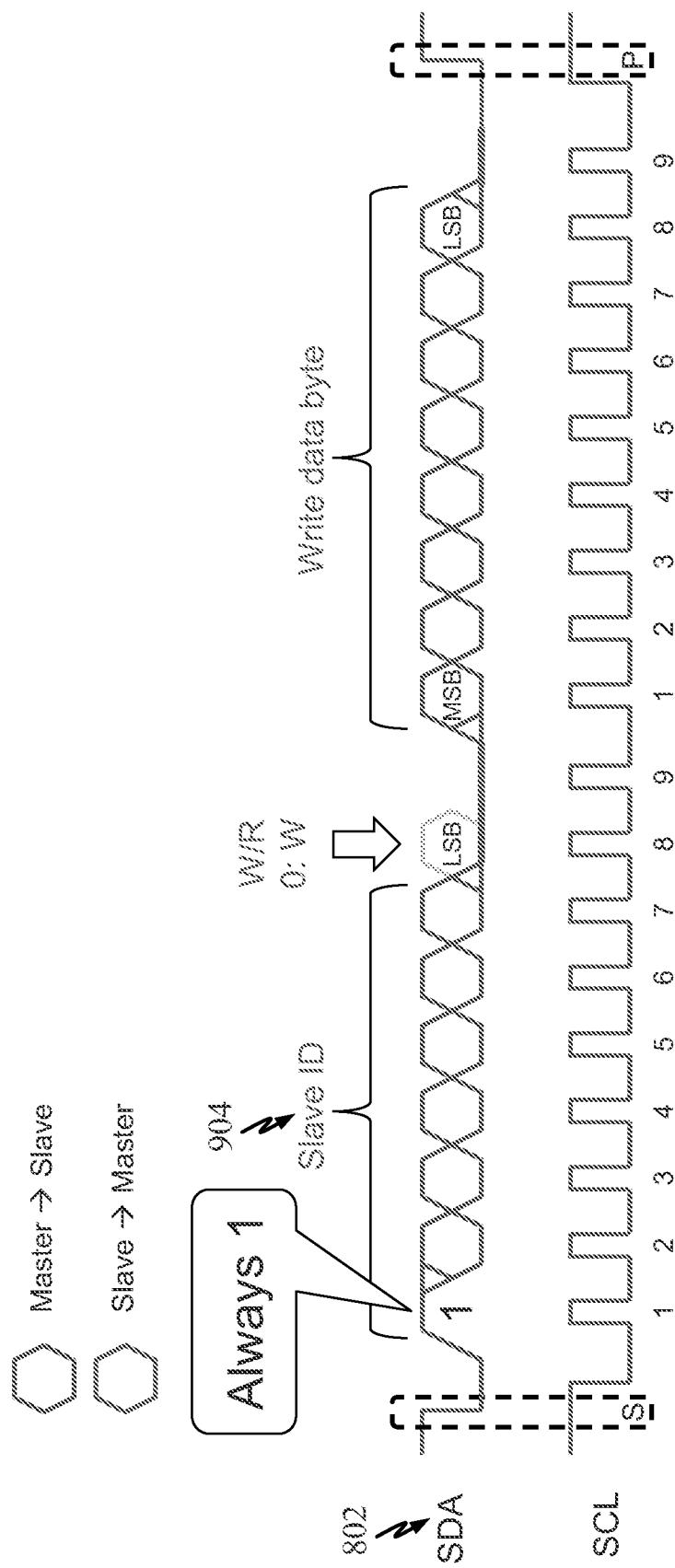

[0038] FIG. 9 illustrates a timing diagram of a sI2C one byte write data operation wherein the most significant bit (MSB) is one (1), in accordance with the sI2C protocol.

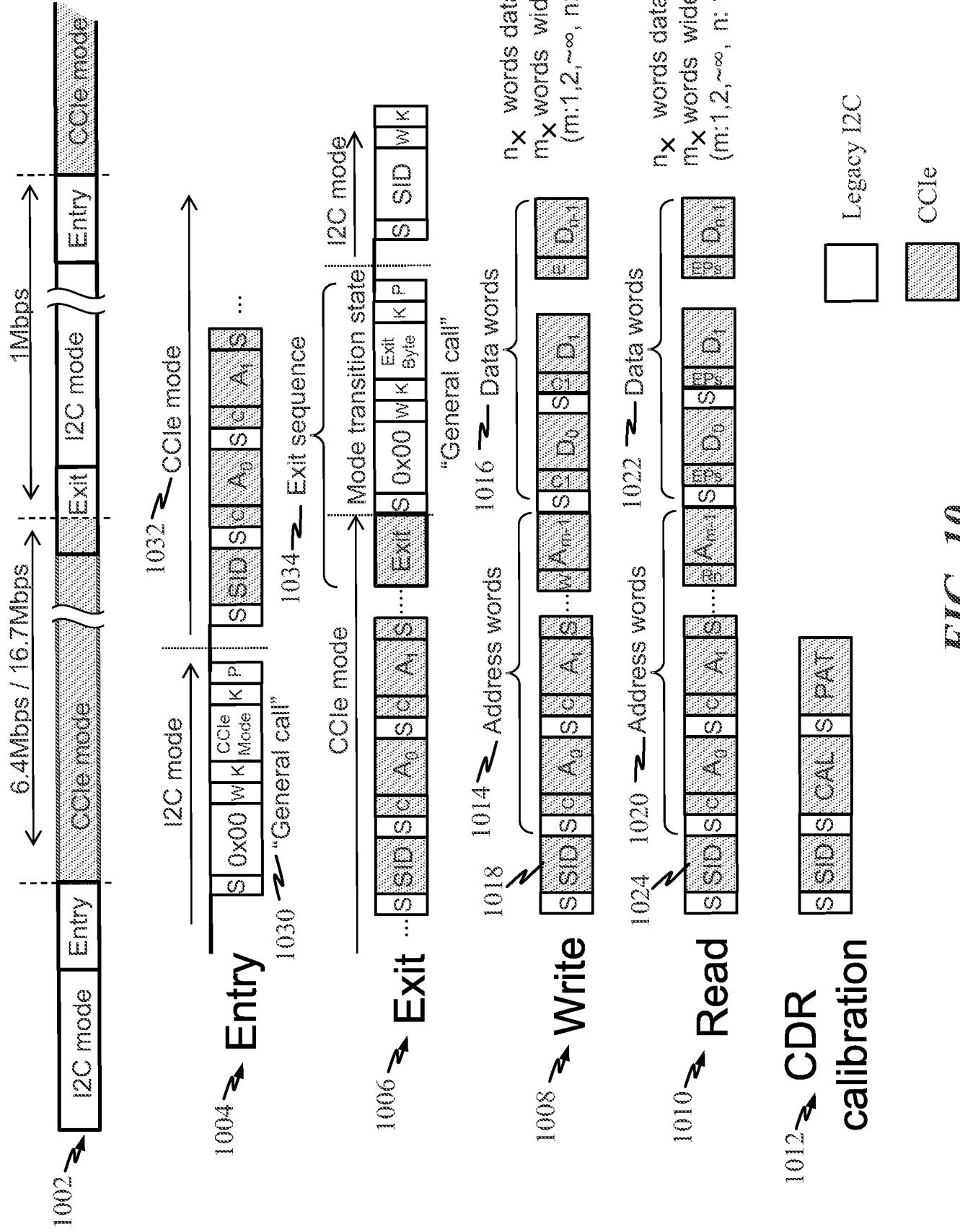

[0039] FIG. 10 illustrates one example of the CCIe protocol.

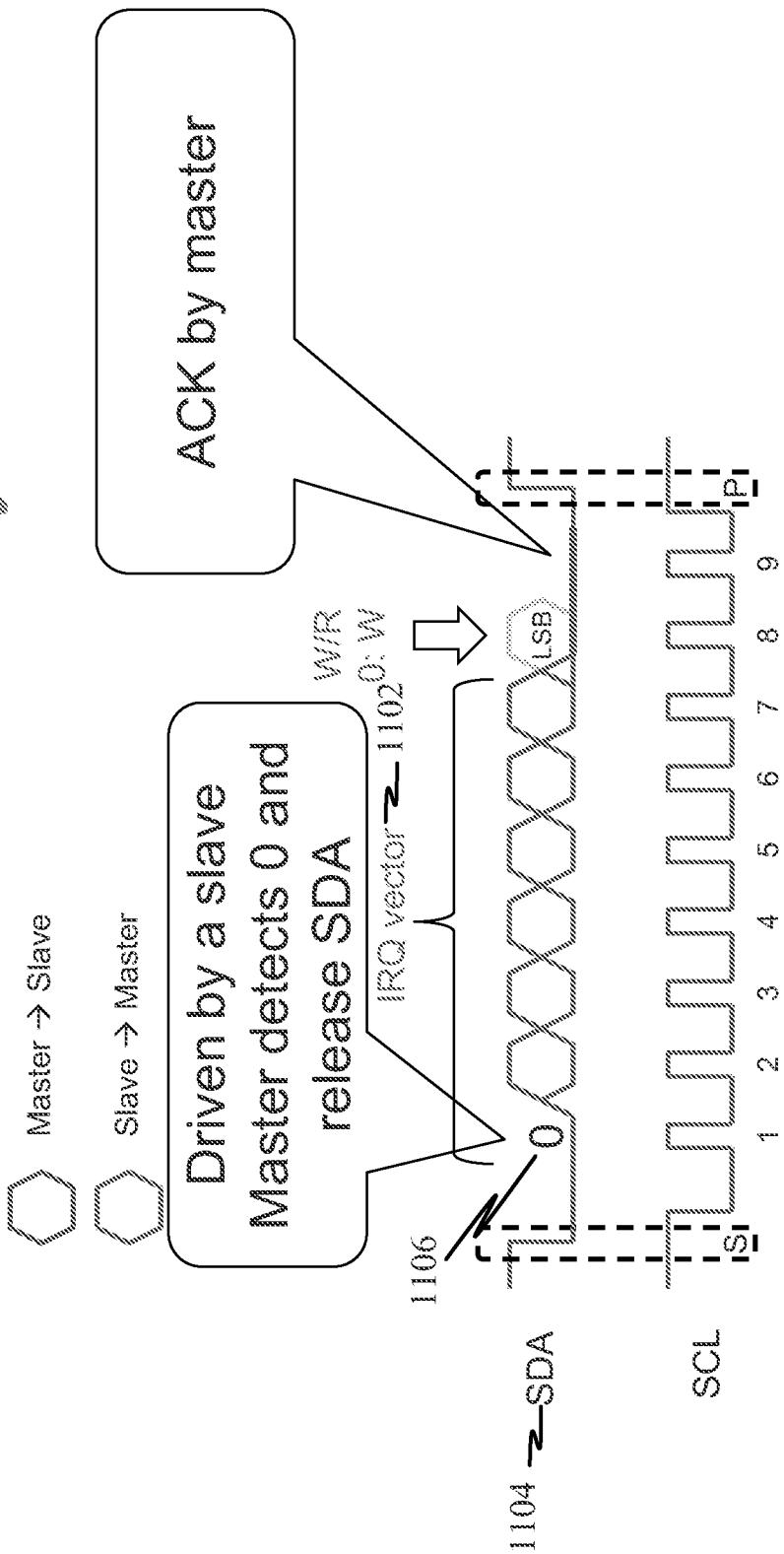

[0040] FIG. 11 illustrates a diagram of an exemplary in-band interrupt signal (IRQ) sent by a sI2C-compatible slave device over a shared bus.

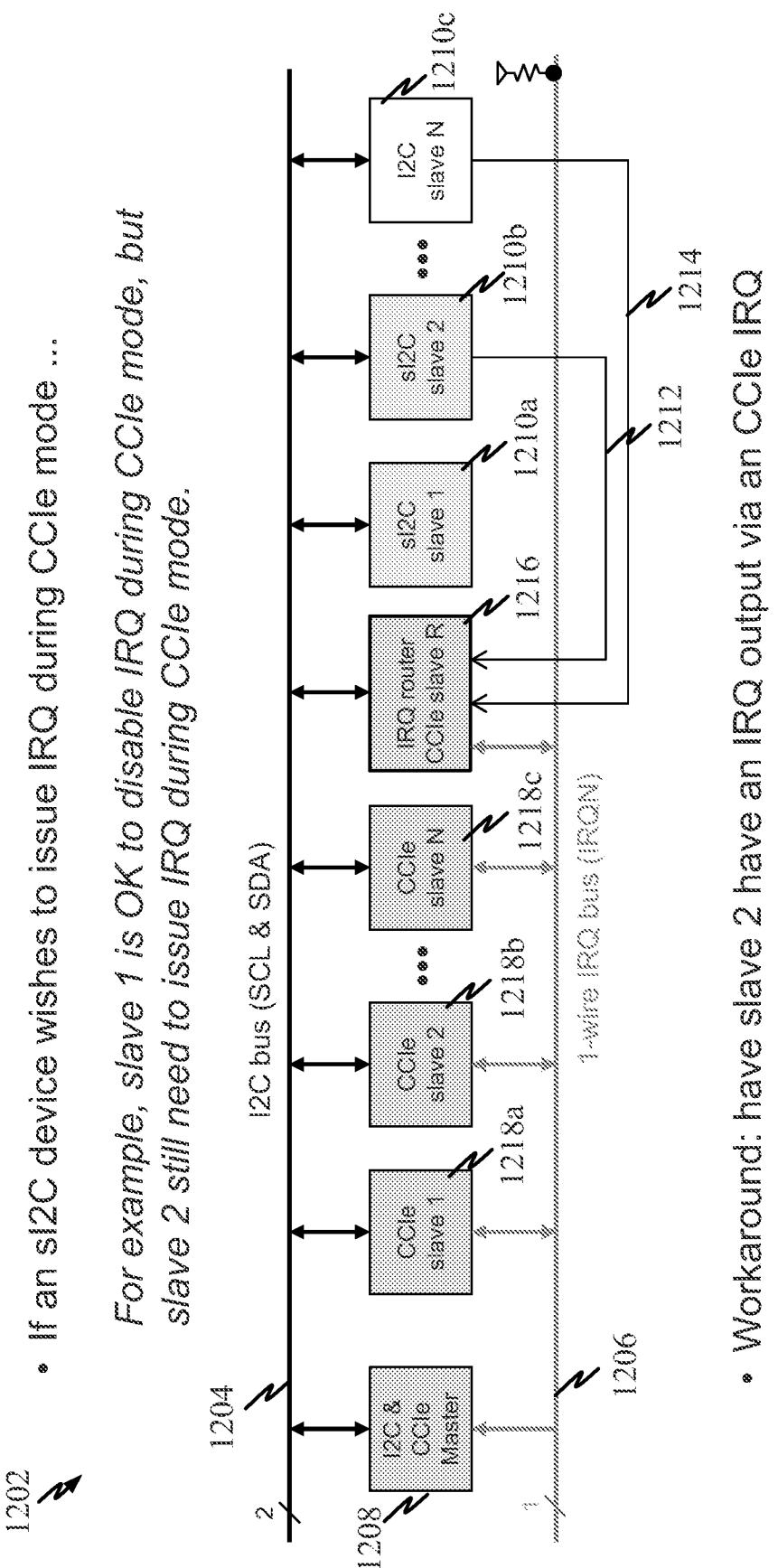

[0041] FIG. 12 illustrates an additional way of a sI2C slave device to issue an interrupt signal (IRQ) in a mixed protocol mode environment (e.g., where a shared bus can operate according to or dynamically switch between distinct communication protocols).

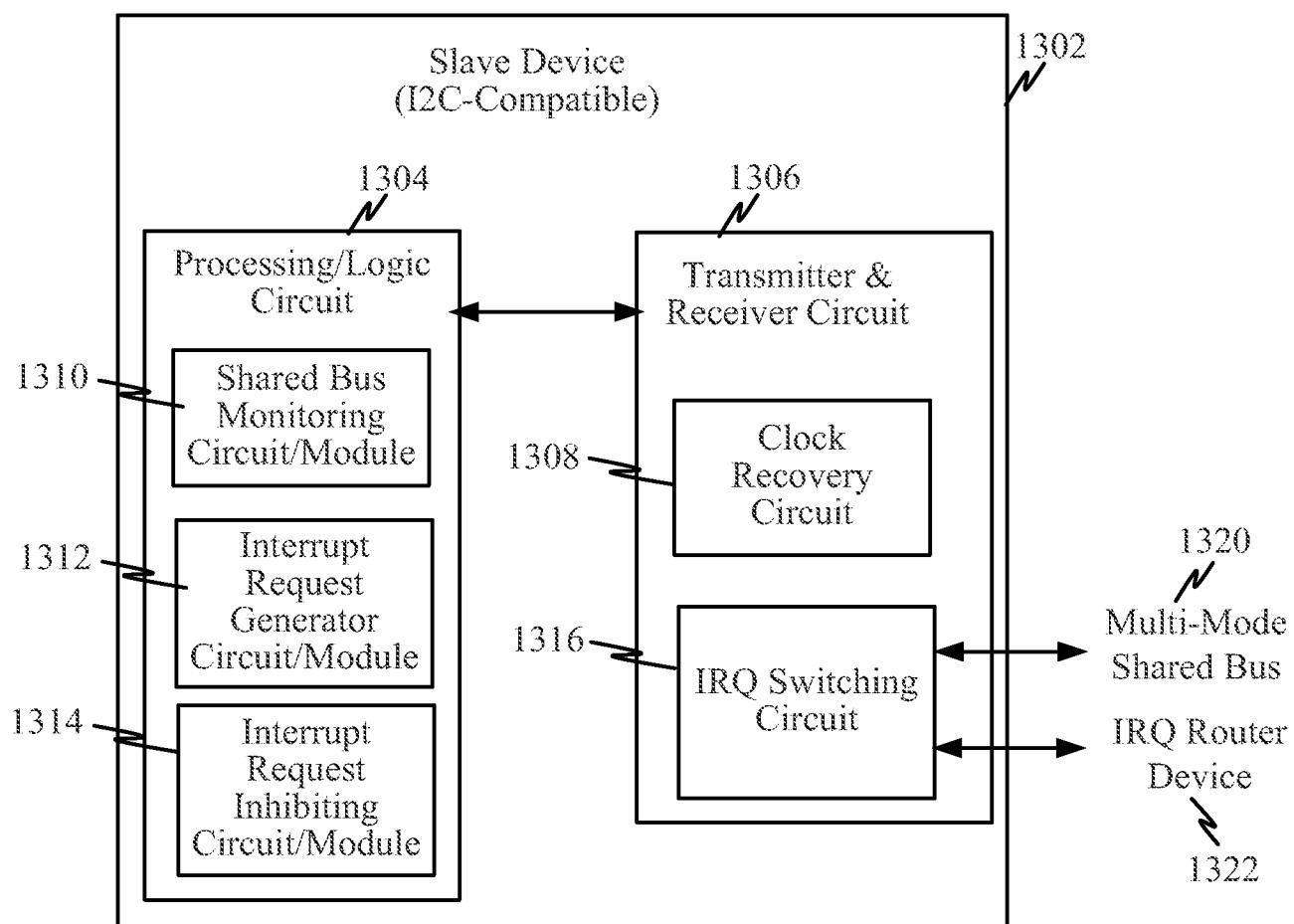

[0042] FIG. 13 illustrates an exemplary slave device comprising a transmitter and receiver circuit and a processing/logic circuit.

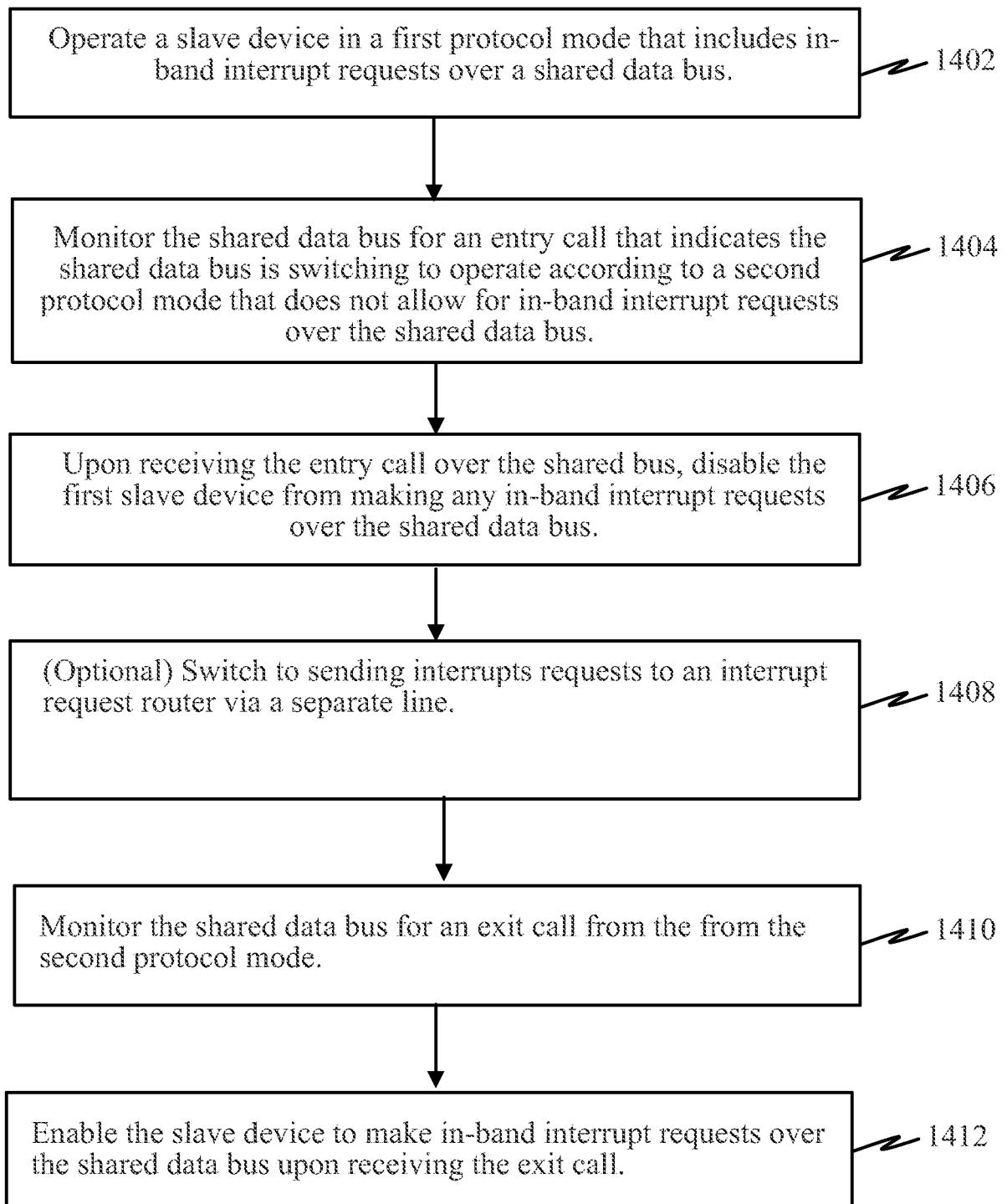

[0043] FIG. 14 illustrates a method for permitting a single-mode slave device to coexist on a shared data bus that switches between multiple communications modes.

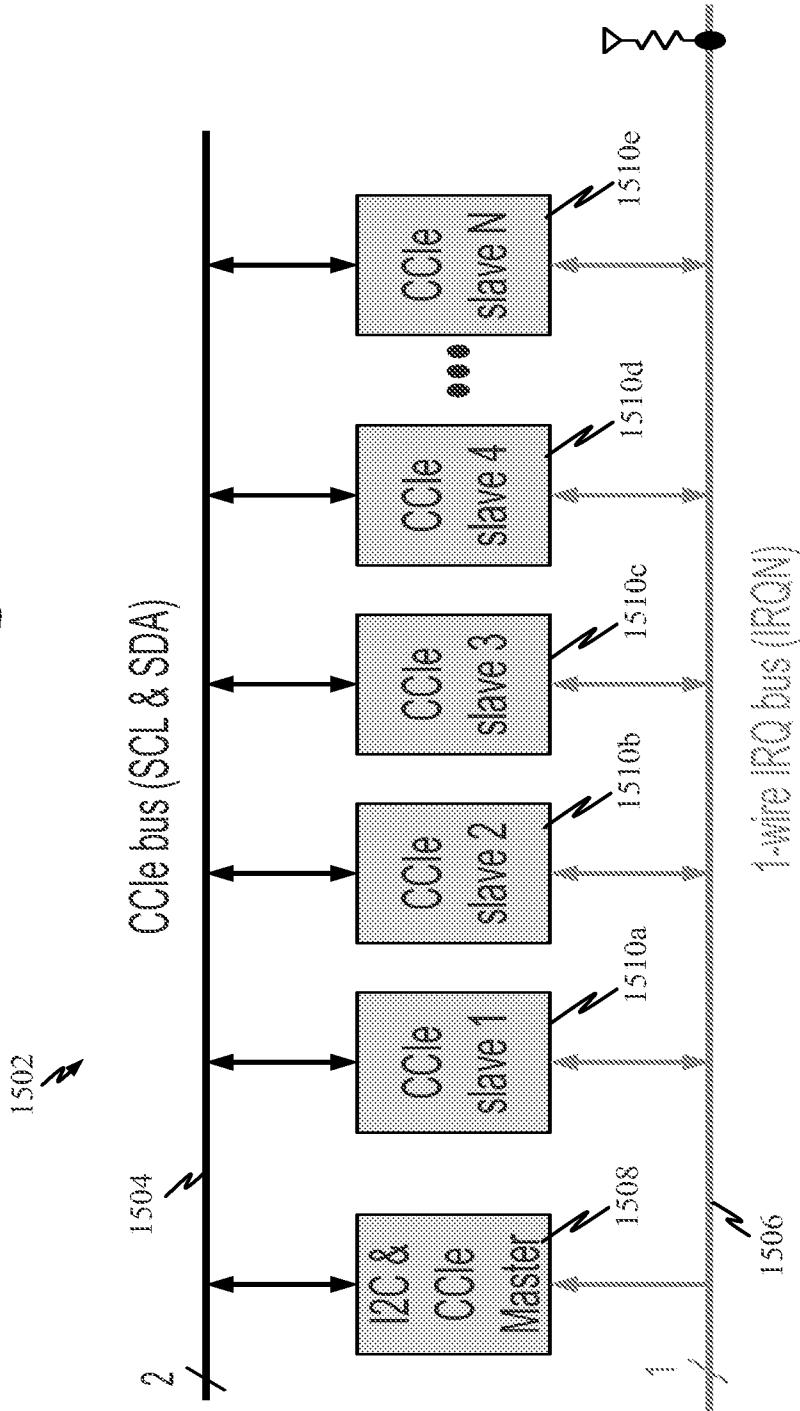

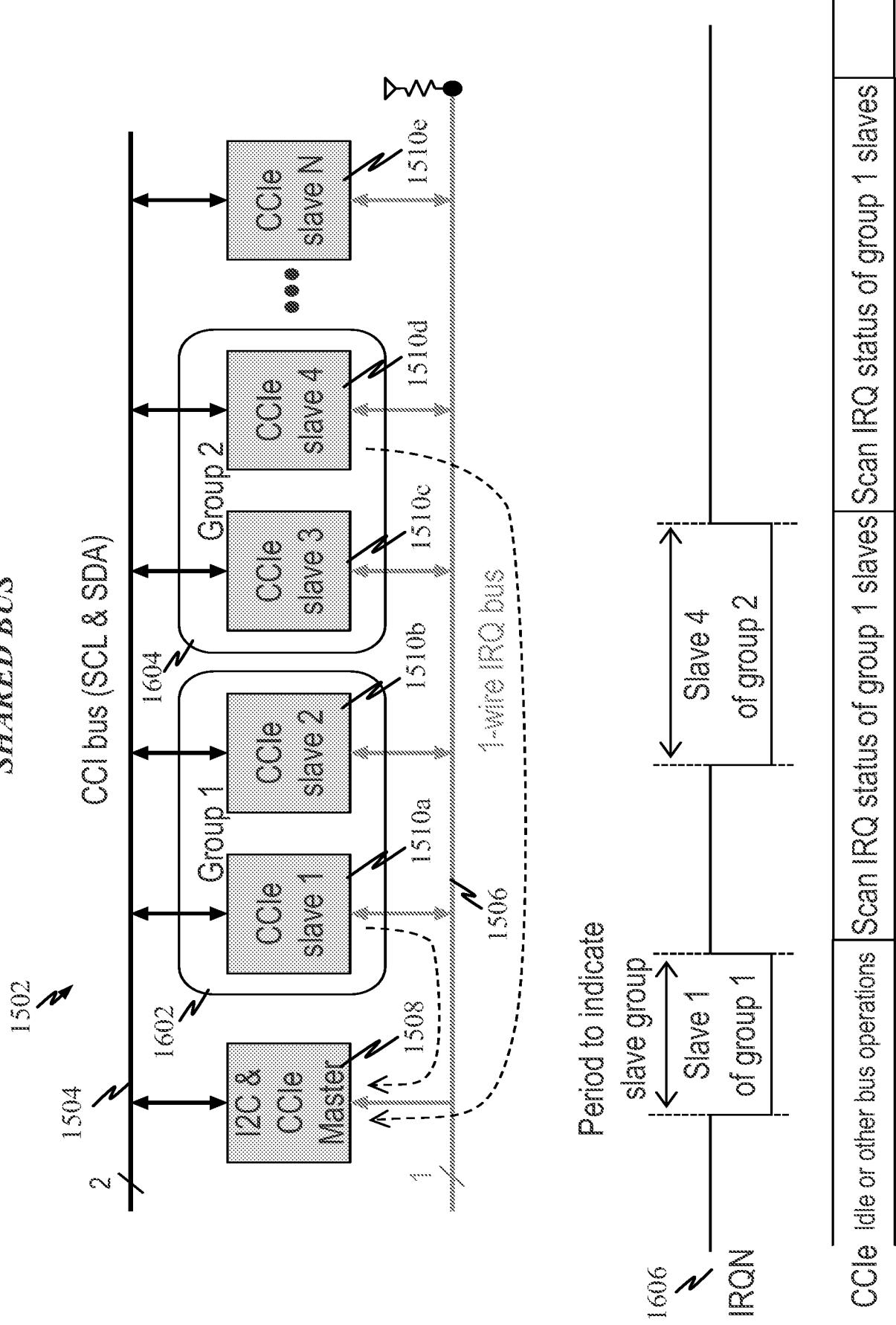

**[0044]** FIG. 15 is a block diagram illustrating a system having a master device and a plurality of slave devices coupled to a shared control data bus and a shared interrupt bus/request.

**[0045]** FIG. 16 is a block diagram illustrating how the plurality of slave devices in FIG. 15 may be logically grouped for purposes of issuing interrupts.

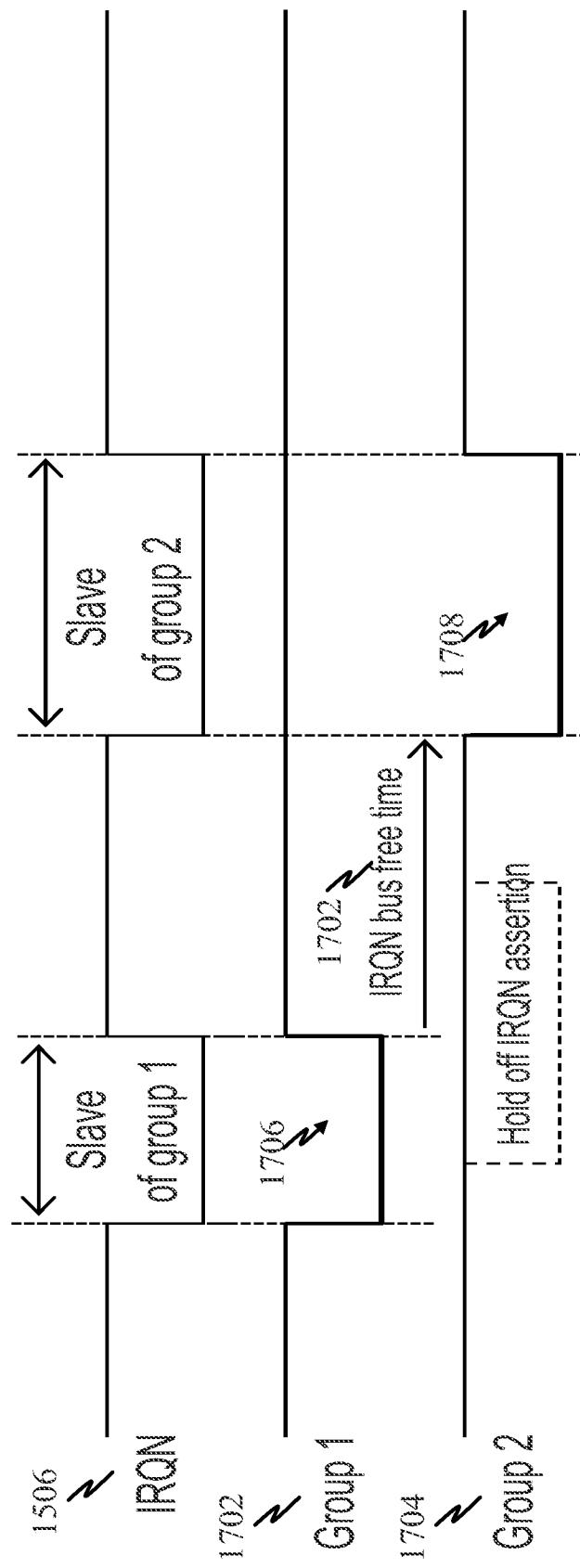

**[0046]** FIG. 17 illustrates a first example of how IRQ signals may be arbitrated over the IRQ line or bus.

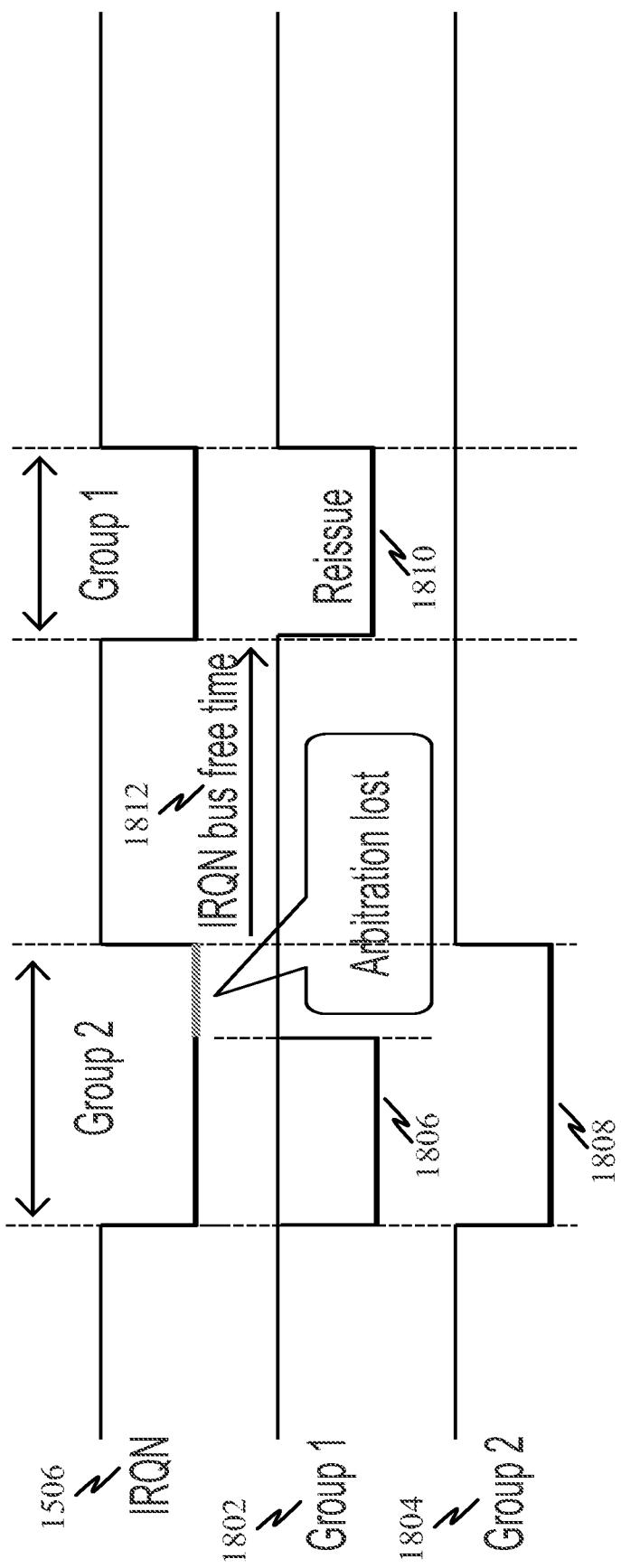

**[0047]** FIG. 18 illustrates a second example of how IRQ signals may be arbitrated over the IRQ line or bus.

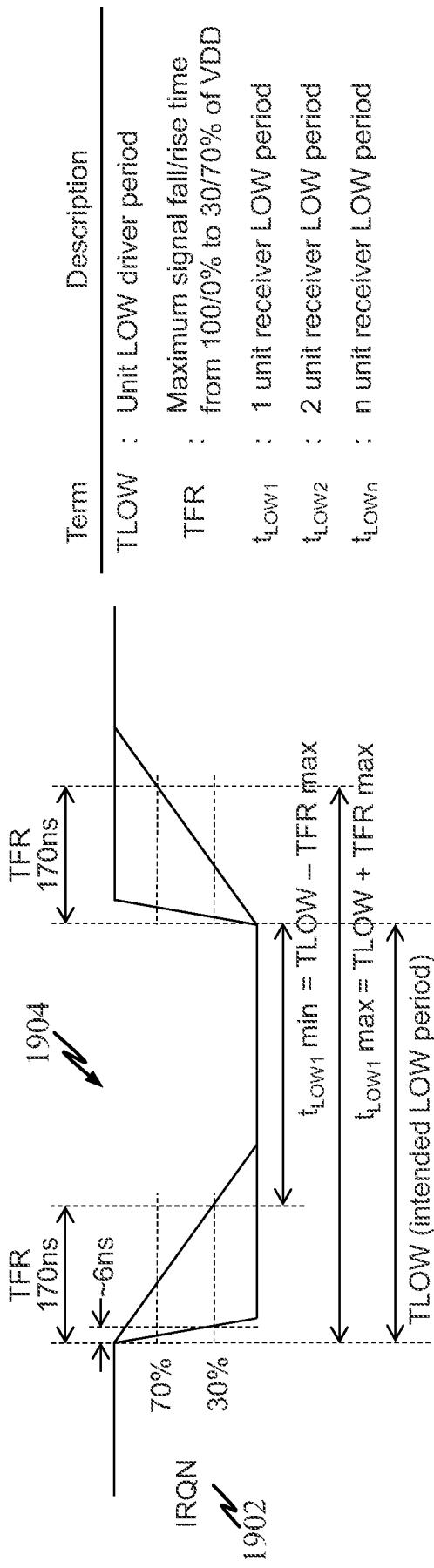

**[0048]** FIG. 19 illustrates a shortest IRQ signal length that may be feasible in one example.

**[0049]** FIG. 20 is a block diagram illustrating an exemplary system in which the interrupt bus has been eliminated in favor of in-band interrupts.

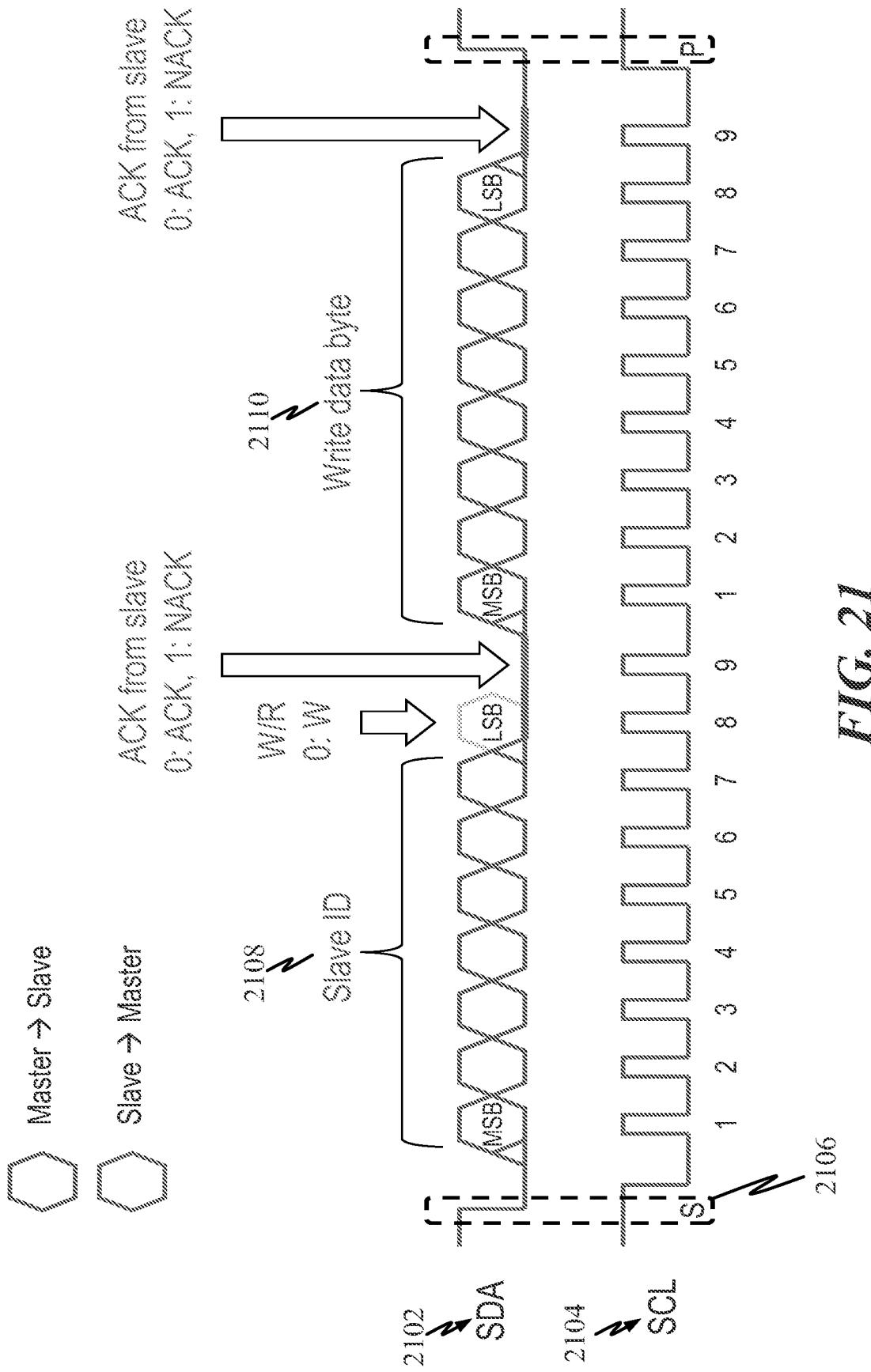

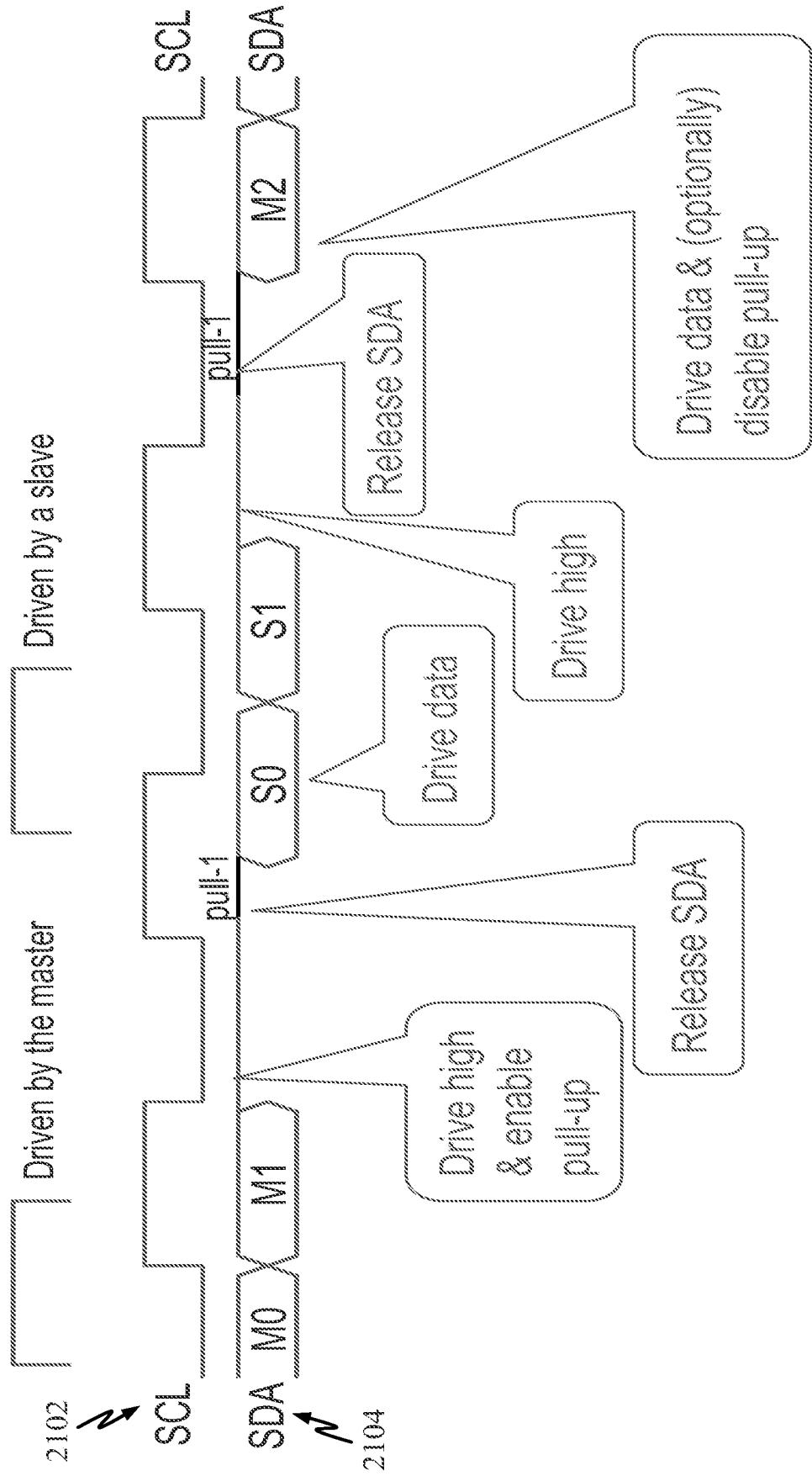

**[0050]** FIG. 21 illustrates an exemplary timing diagram of an I2C one byte write data operation.

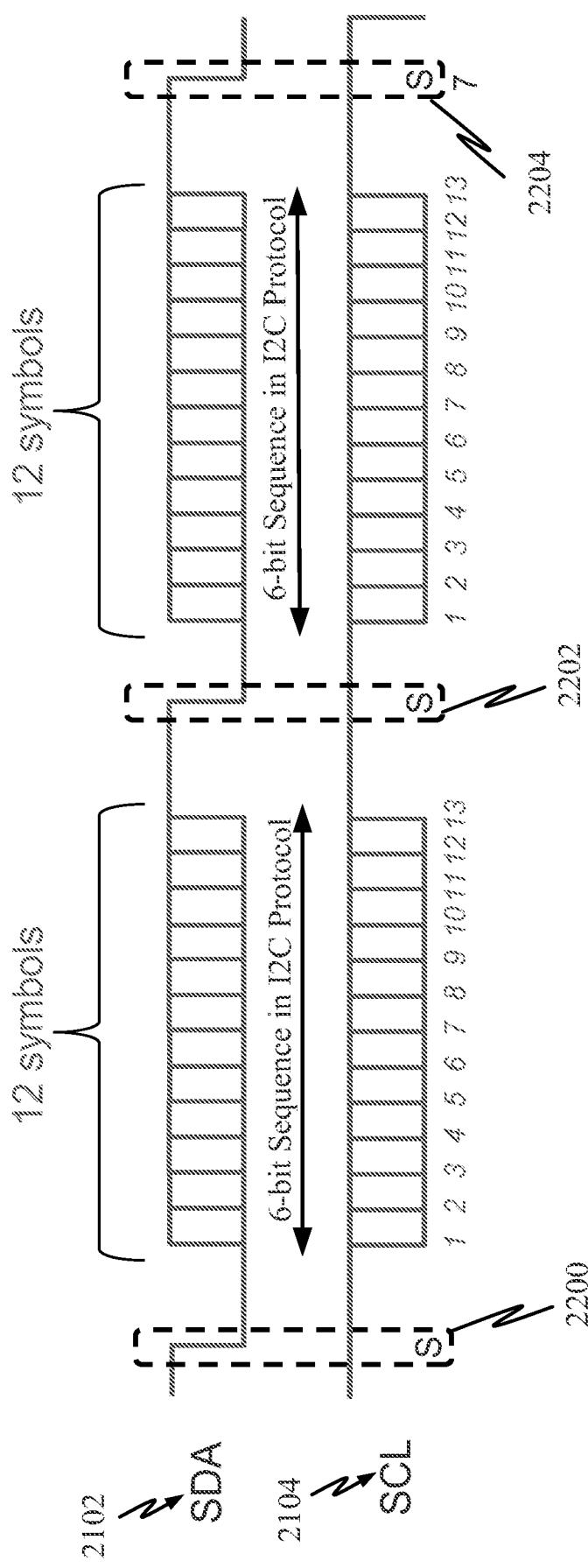

**[0051]** FIG. 22 illustrates an exemplary CCIE transmission in which data bits have been transcoded into twelve symbols for transmission over the SDA line and the SCL line.

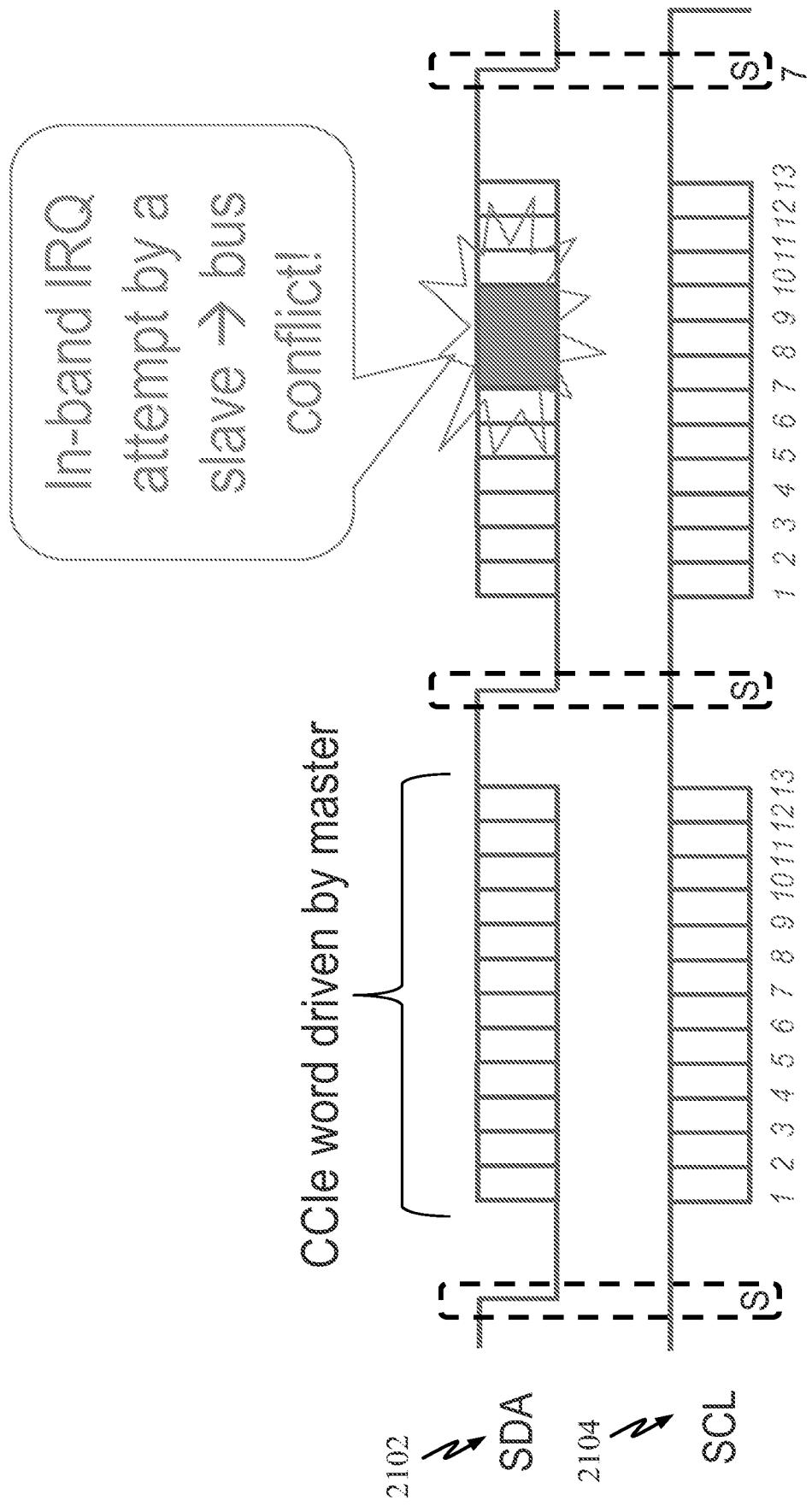

**[0052]** FIG. 23 illustrates that a slave device should not be allowed to drive the control data bus to assert an IRQ while the master device is driving the control data bus in order to avoid collisions.

**[0053]** FIG. 24 illustrates a solution to avoid the potential for collisions of FIG. 23.

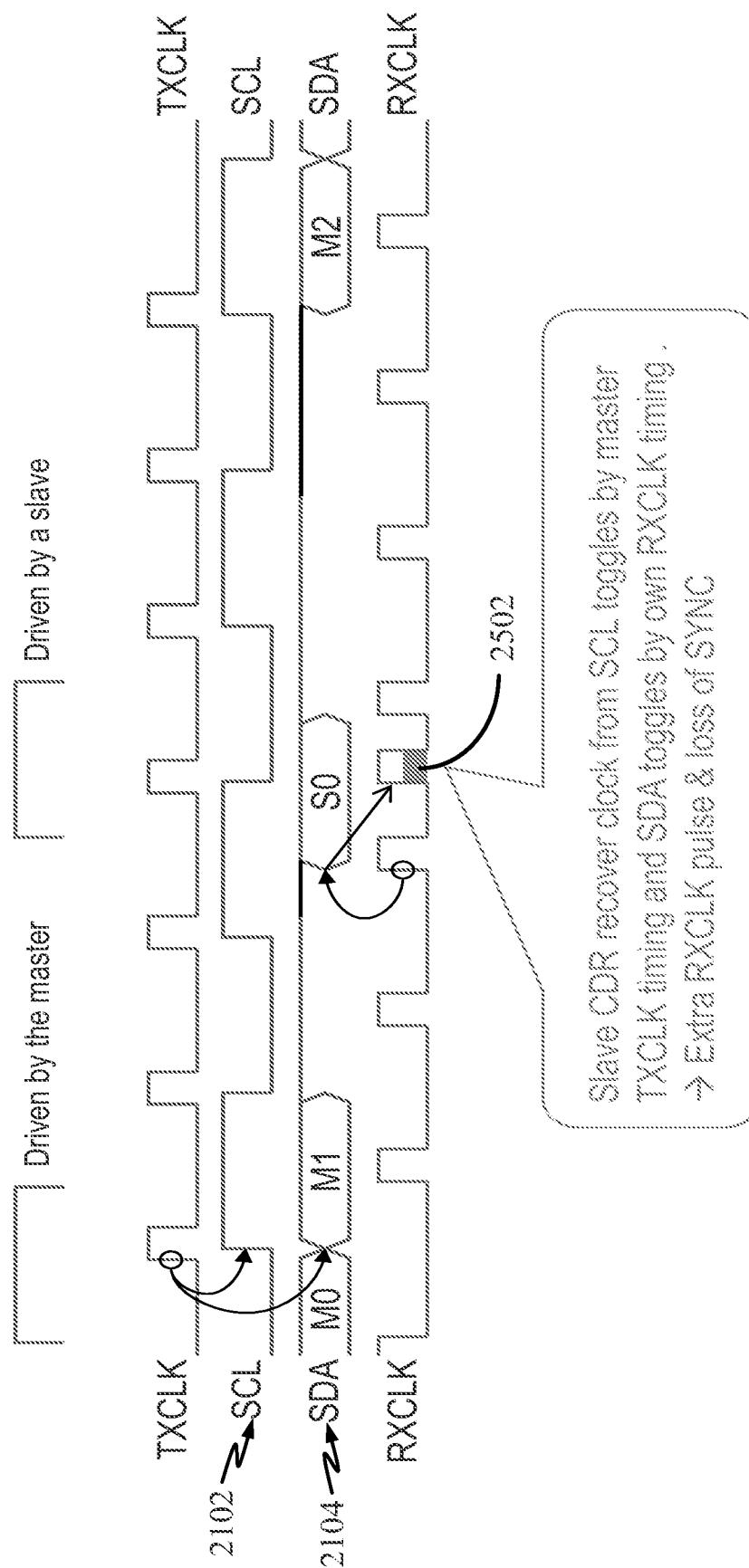

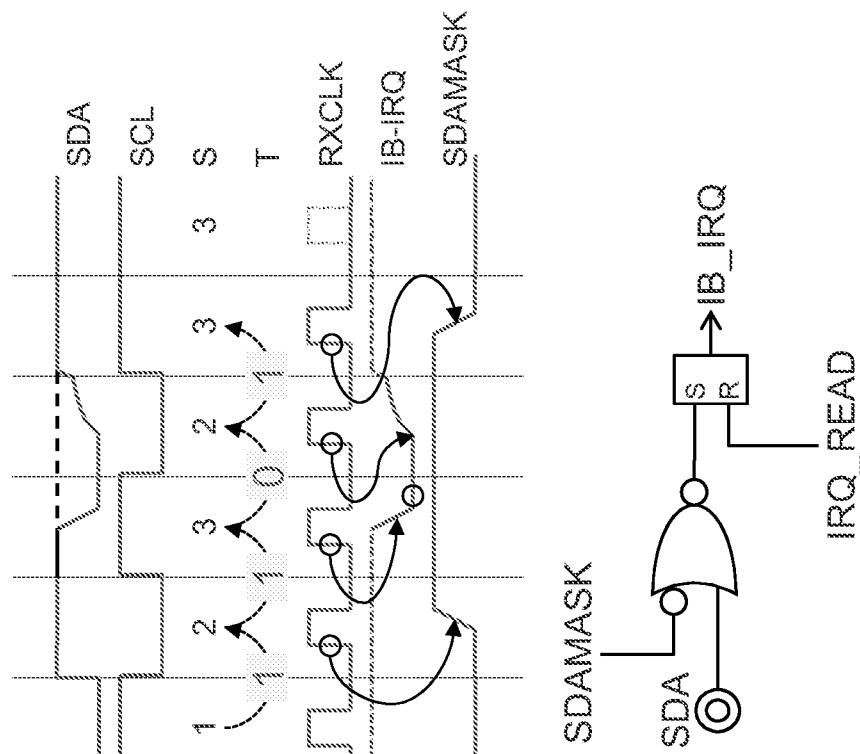

**[0054]** FIG. 25 illustrates that when the slave device sends the in-band IRQ on the SDA line, it may cause an erroneous clock to be detected.

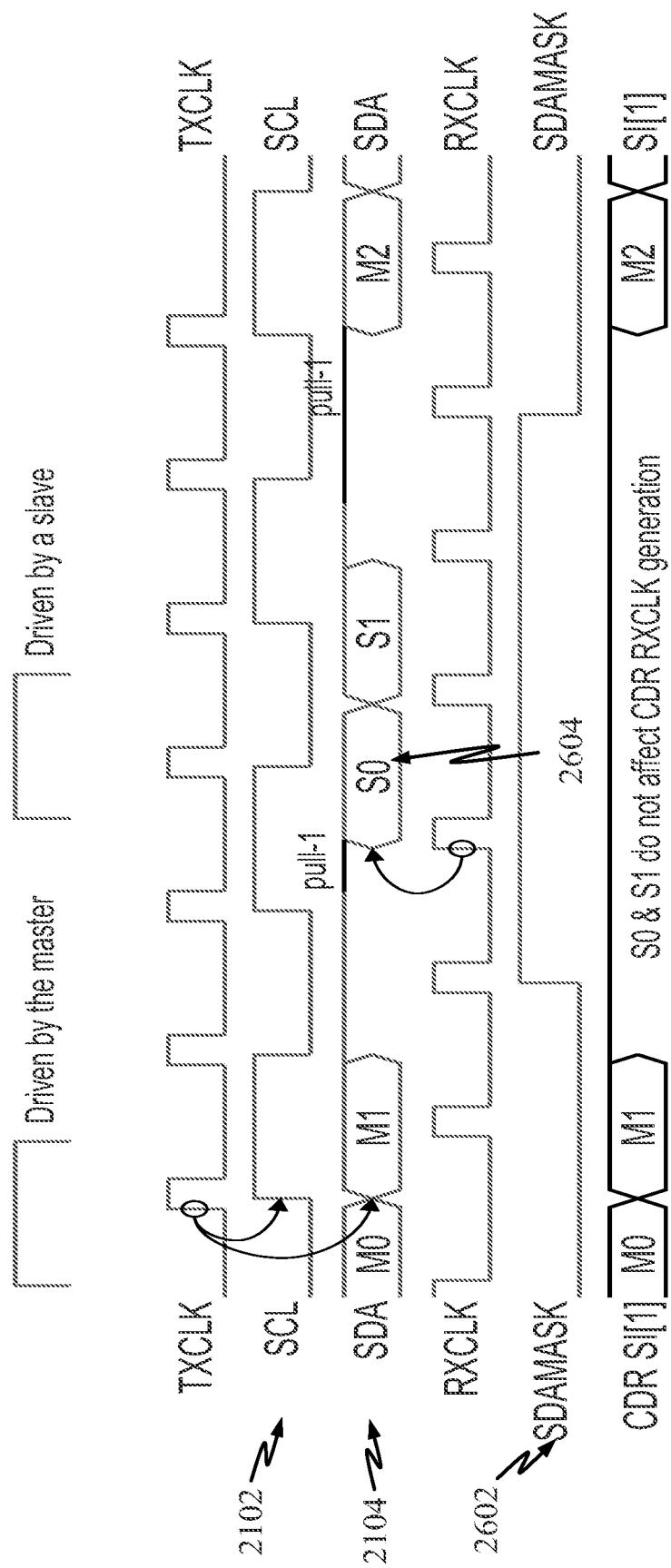

**[0055]** FIG. 26 illustrates a solution to avoid the extra receiver clock pulse and synchronization loss illustrated in FIG. 25.

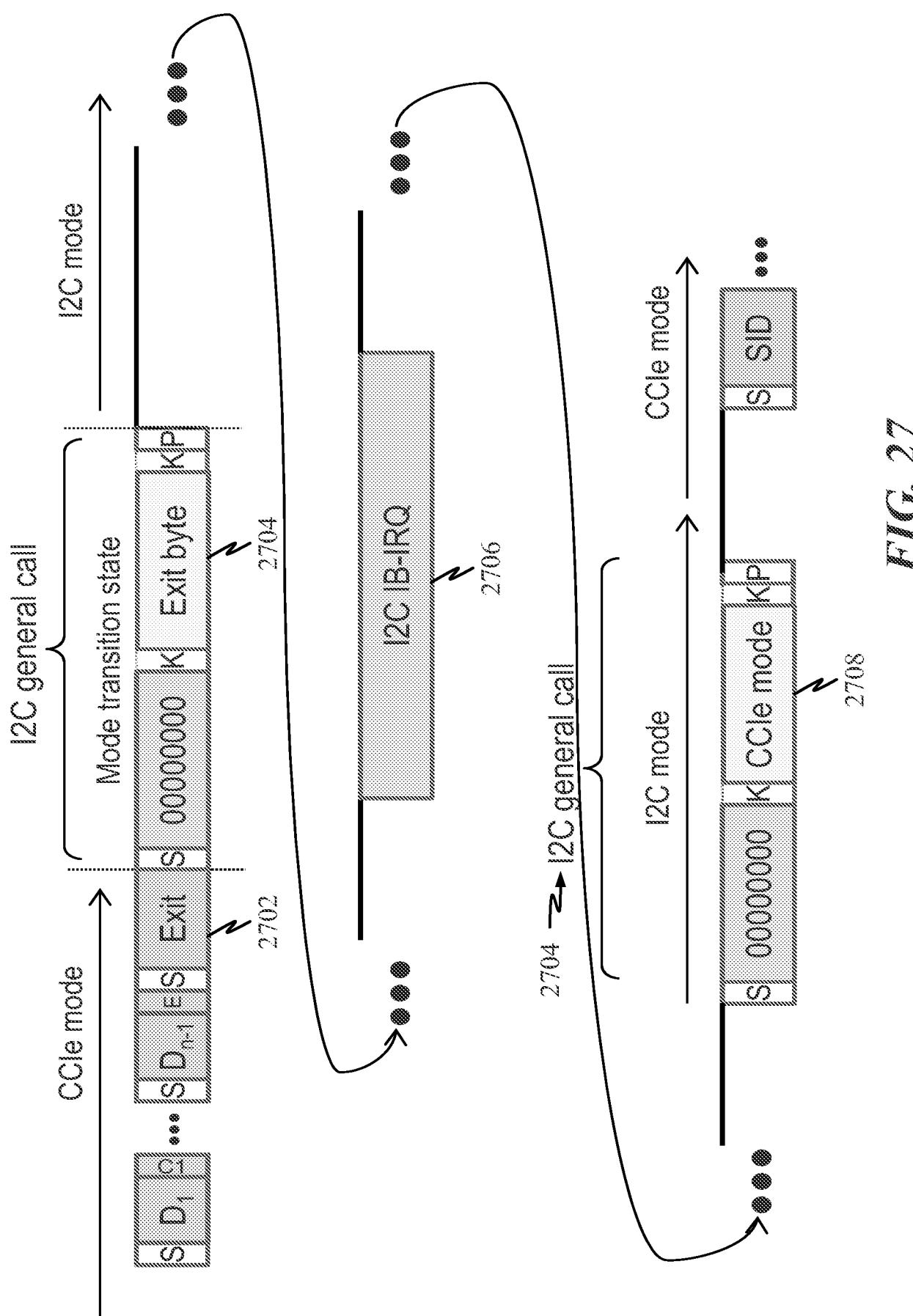

**[0056]** FIG. 27 illustrates one approach to implementing an in-band IRQ period while supporting both I2C mode and CCIE mode.

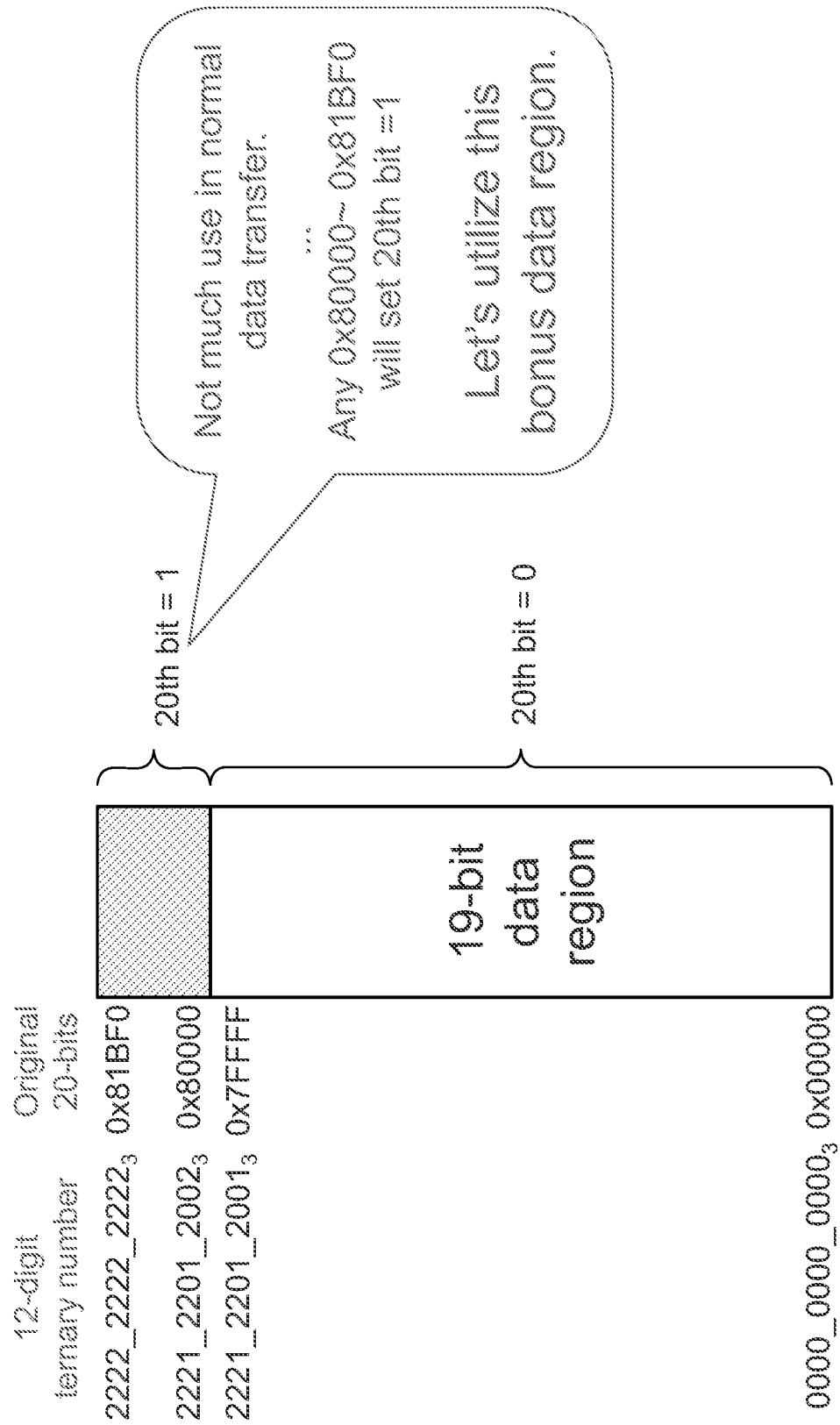

**[0057]** FIG. 28 illustrates the bit 19 (i.e., the 20<sup>th</sup> bit when the bit count starts at the first bit being bit 0).

**[0058]** FIG. 29 illustrates that bit 19 may span the numbers 2221\_2201\_2002<sub>3</sub> to 2222\_2222\_2222<sub>3</sub>, and that range of numbers may be subdivided into six subdivisions on the left side of FIG. 29.

**[0059]** FIG. 30 illustrates a range within the bit 19 number space that may be used to define the heartbeat.

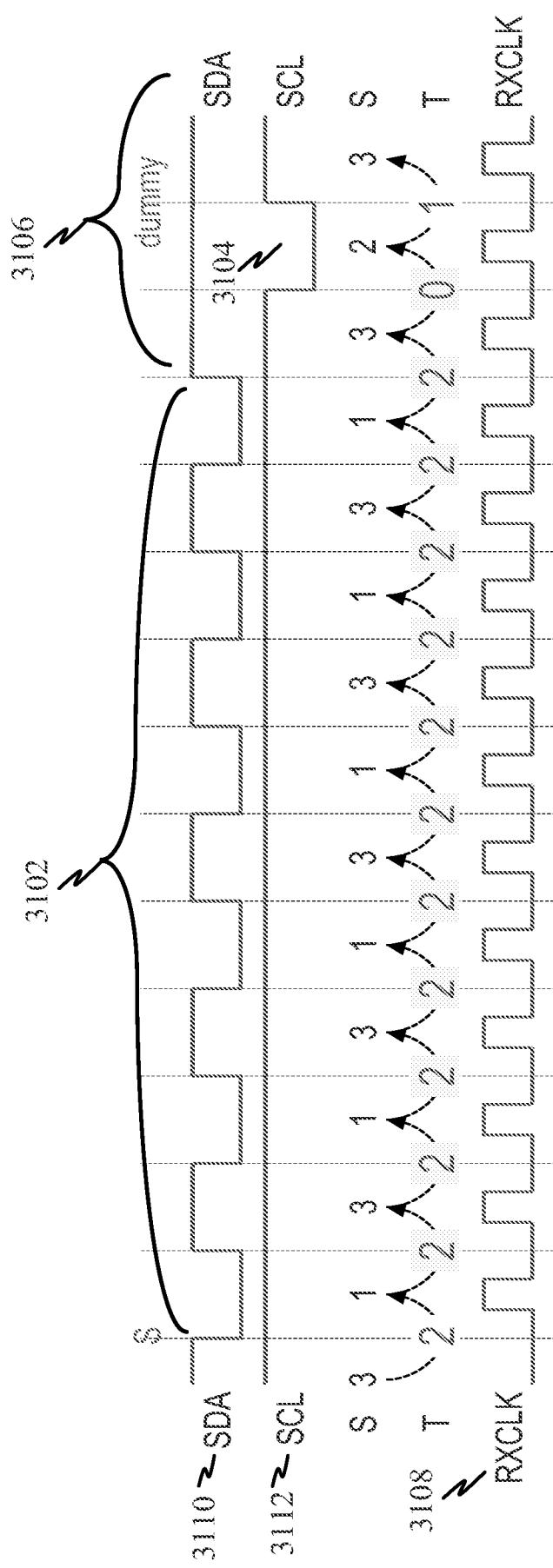

[0060] FIG. 31 illustrates one example of how the heartbeat clock may be transmitted over the SDA line and SCL line of a shared control data bus.

[0061] FIG. 32 illustrates another example of a heartbeat clock may be transmitted over the SDA line and SCL line.

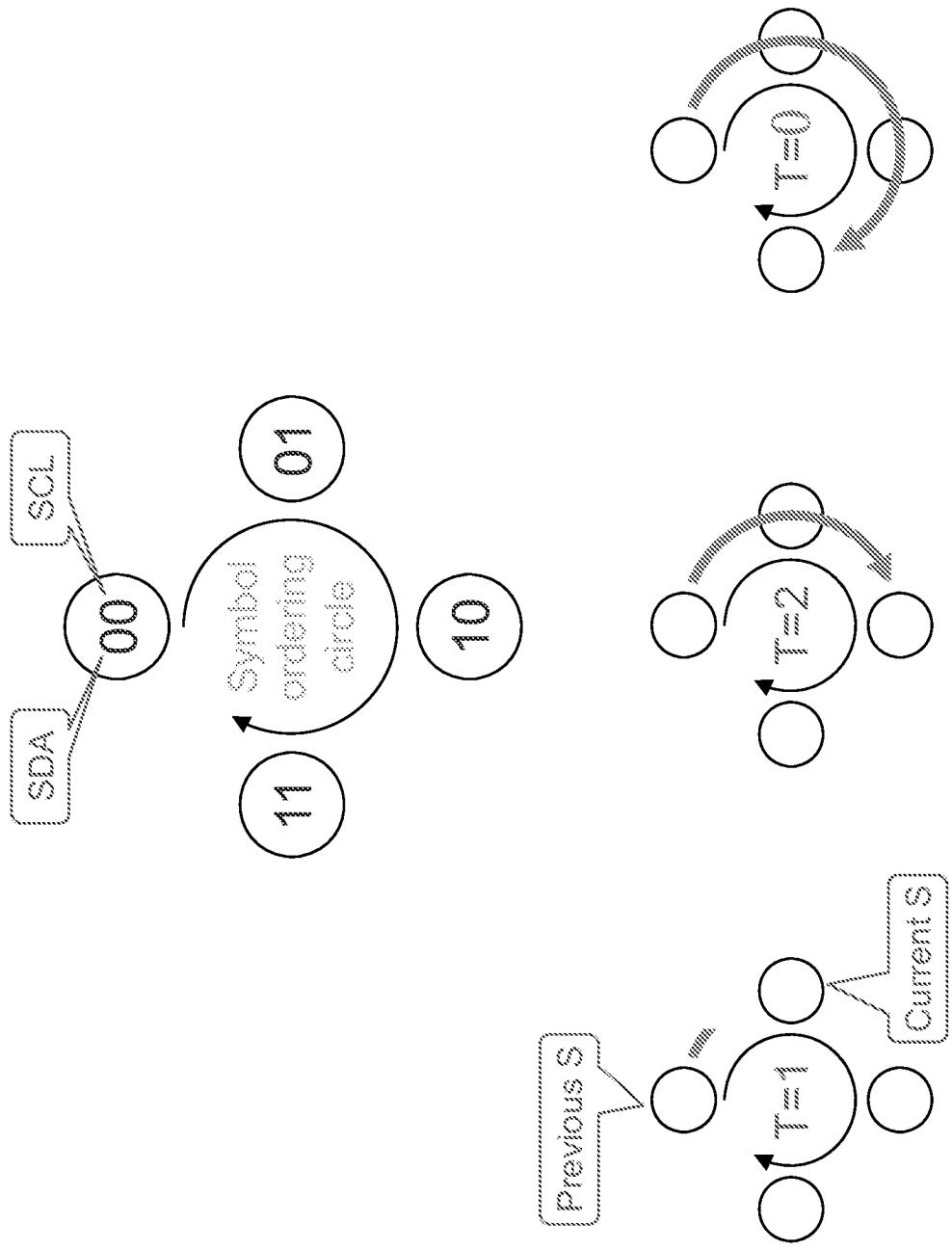

[0062] FIG. 33 illustrates one example of transition number to symbol number conversion.

[0063] FIG. 34 further expands on the symbol number to transition number conversion of FIG. 33.

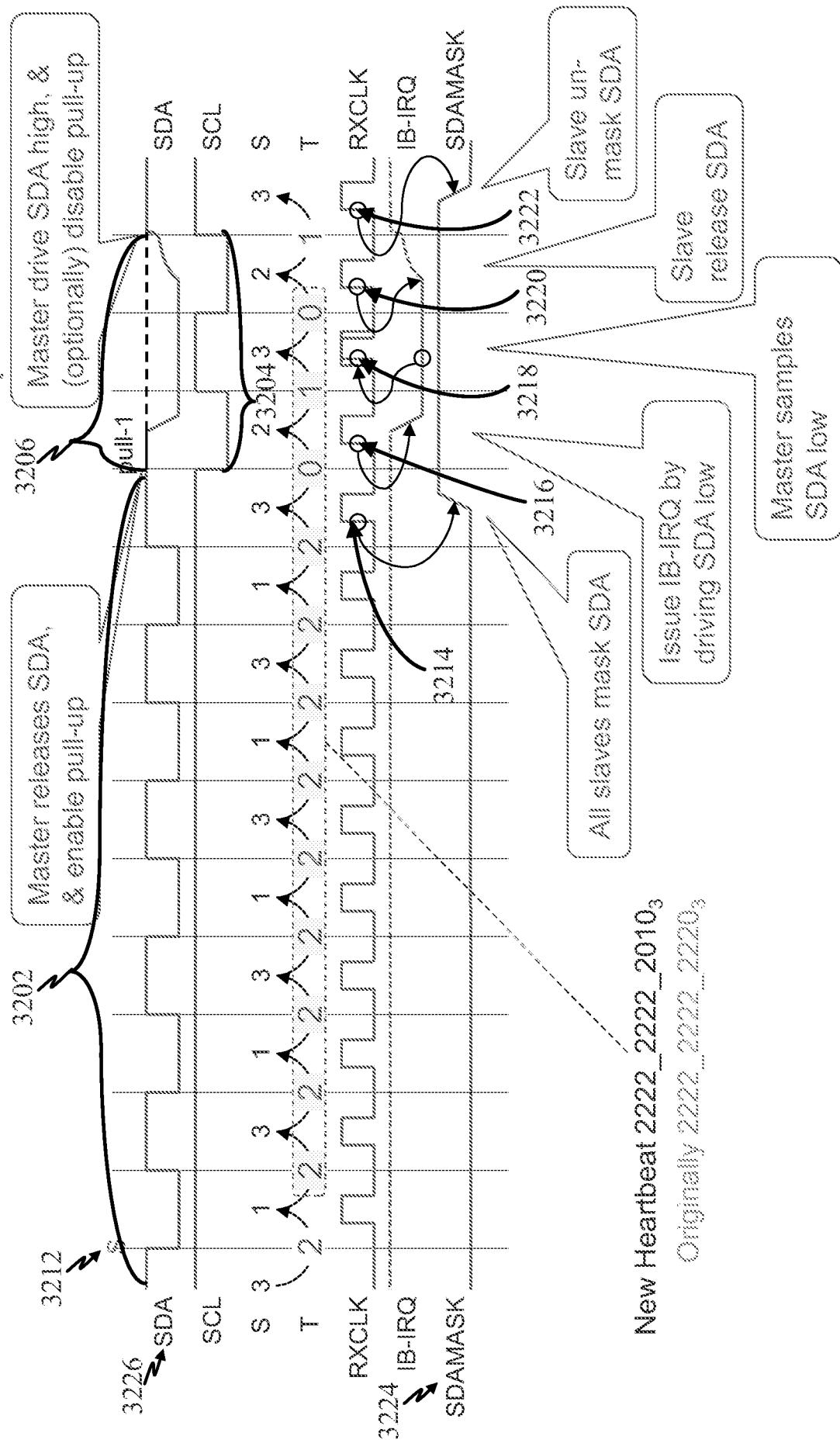

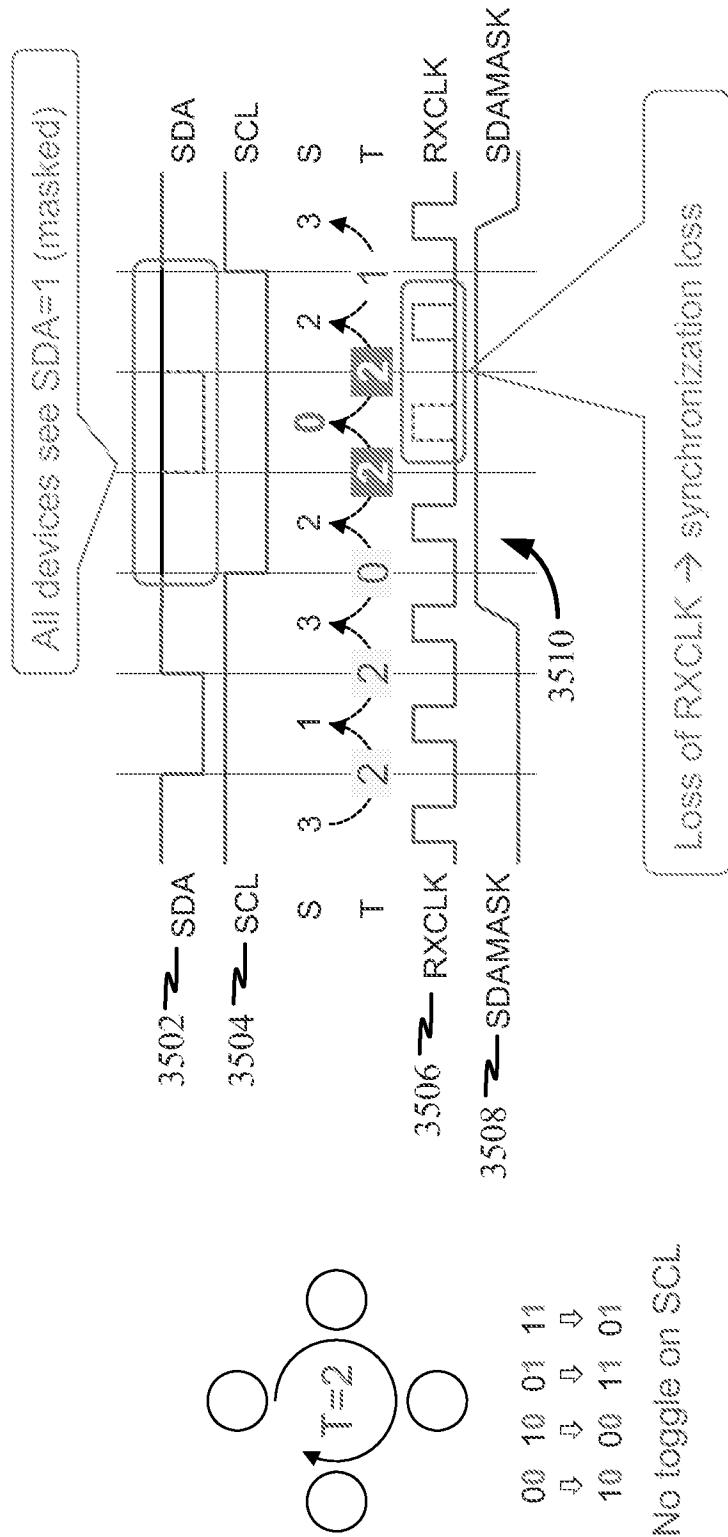

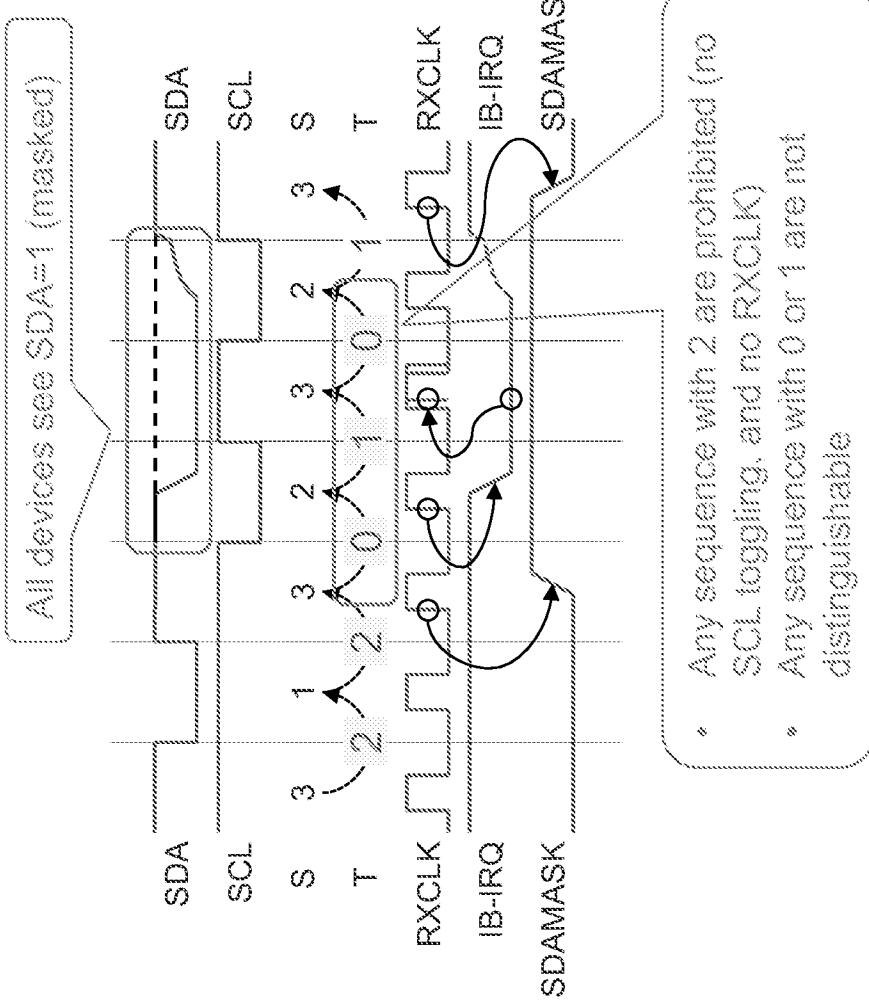

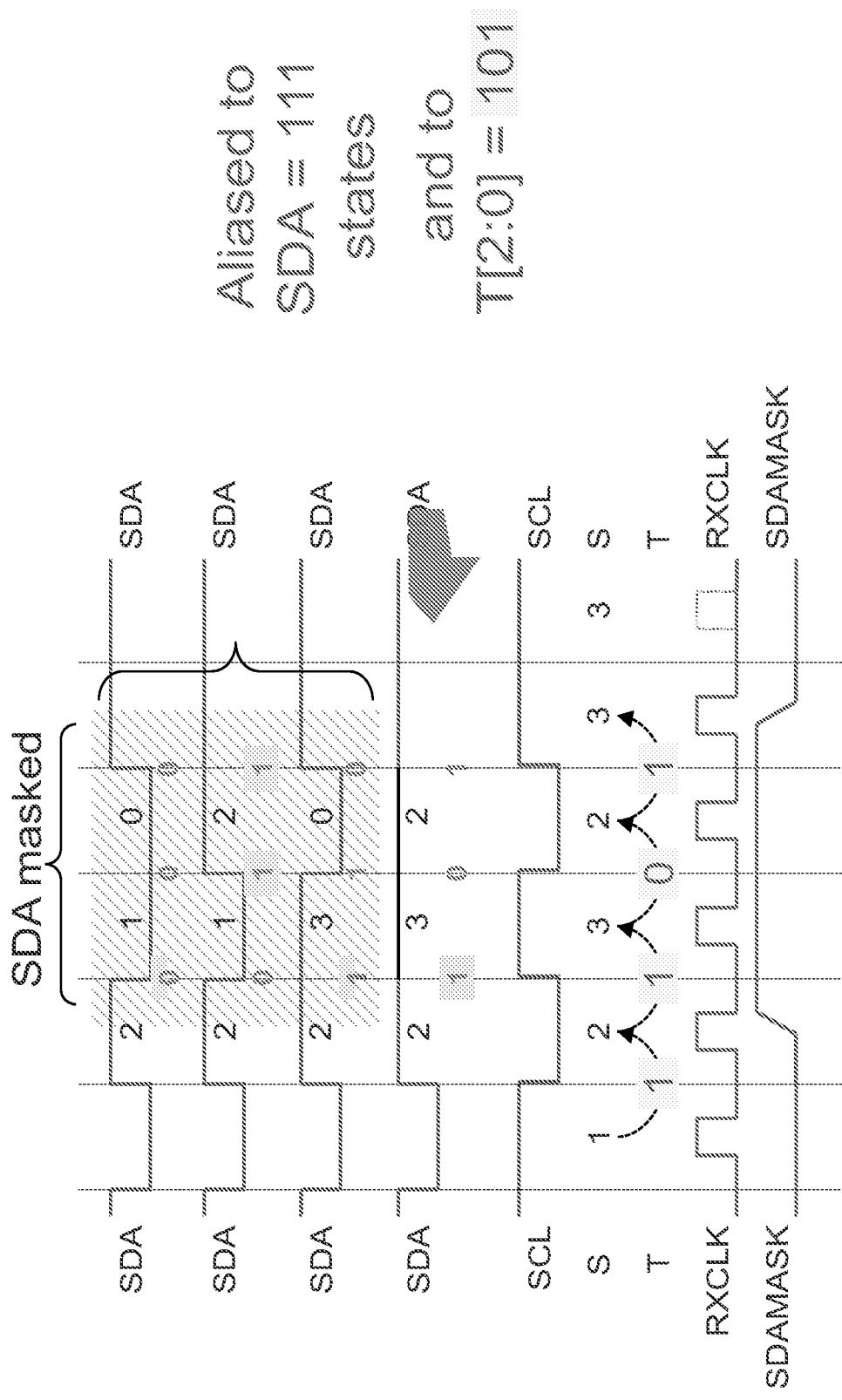

[0064] FIG. 35 illustrates the condition during the in-band IRQ period in which the SDA line is masked.

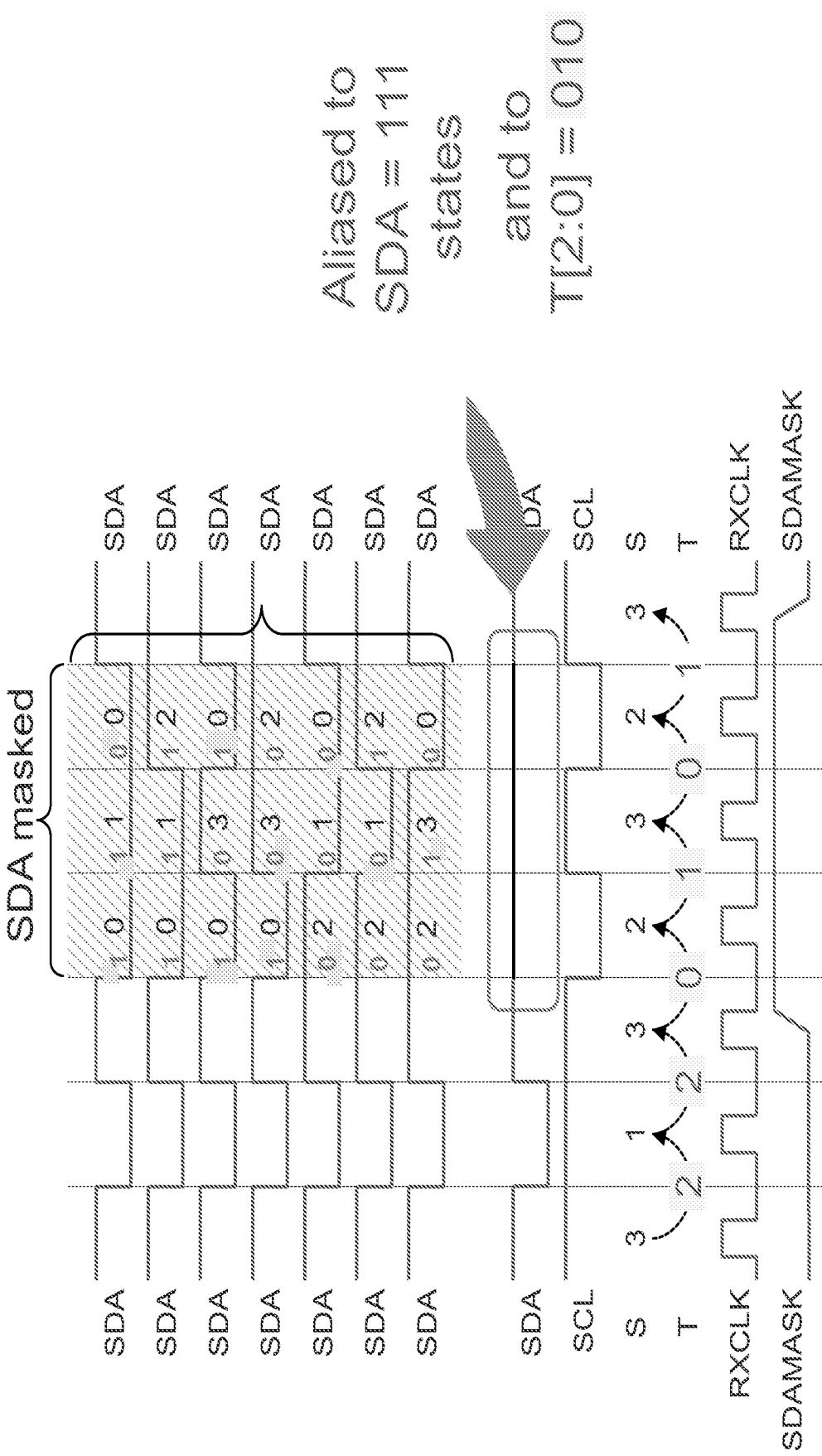

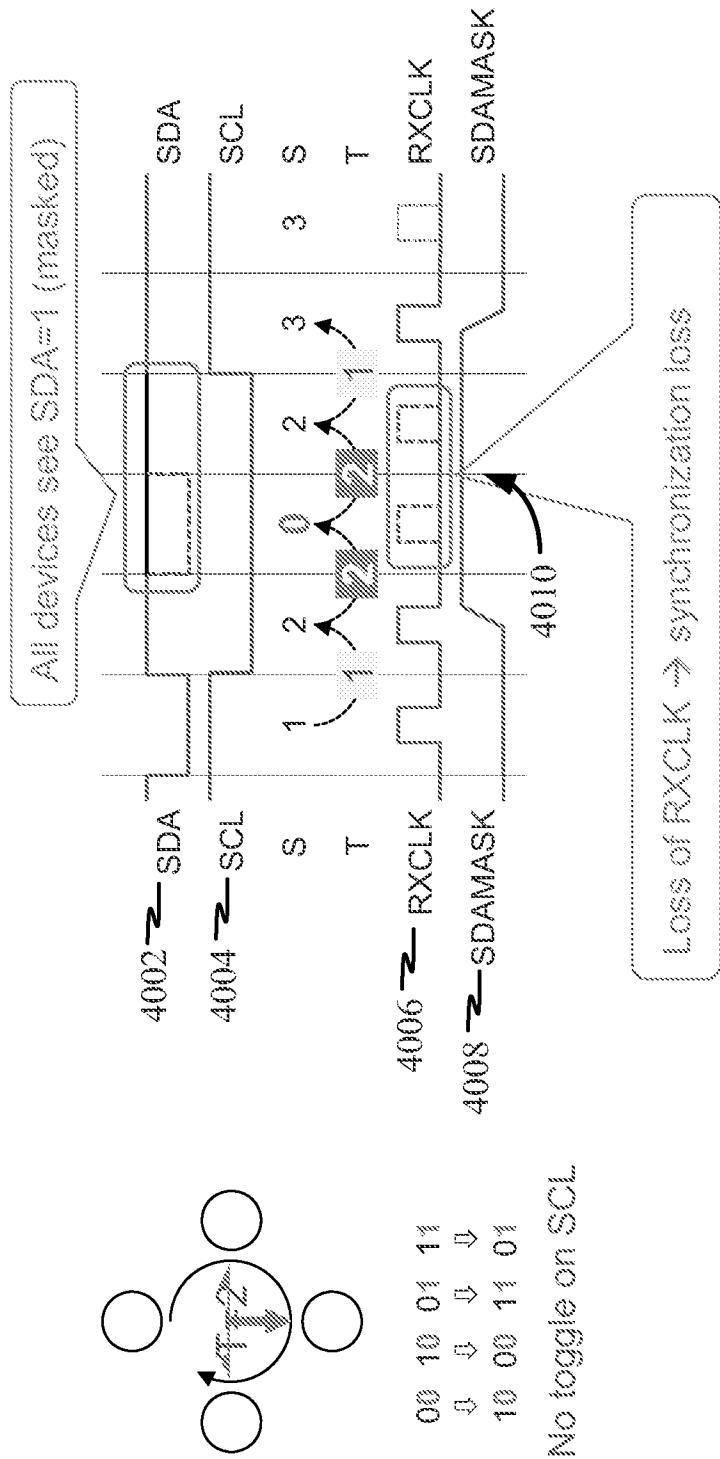

[0065] FIG. 36 illustrates a side-effect of SDA Mask of FIGS. 32 and 35.

[0066] FIG. 37 illustrates that the heartbeat used for in-band IRQs occupies the number space 0x81BD6~0x81BF0 (i.e., 27 addresses) within the ternary number space.

[0067] FIG. 38 illustrates an example of how bit 19 of the ternary number used in FIG. 37 for CCIE mode transmissions may be mapped.

[0068] FIG. 39 illustrates an alternative technique for implementing an in-band IRQ over the control data bus in CCIE mode.

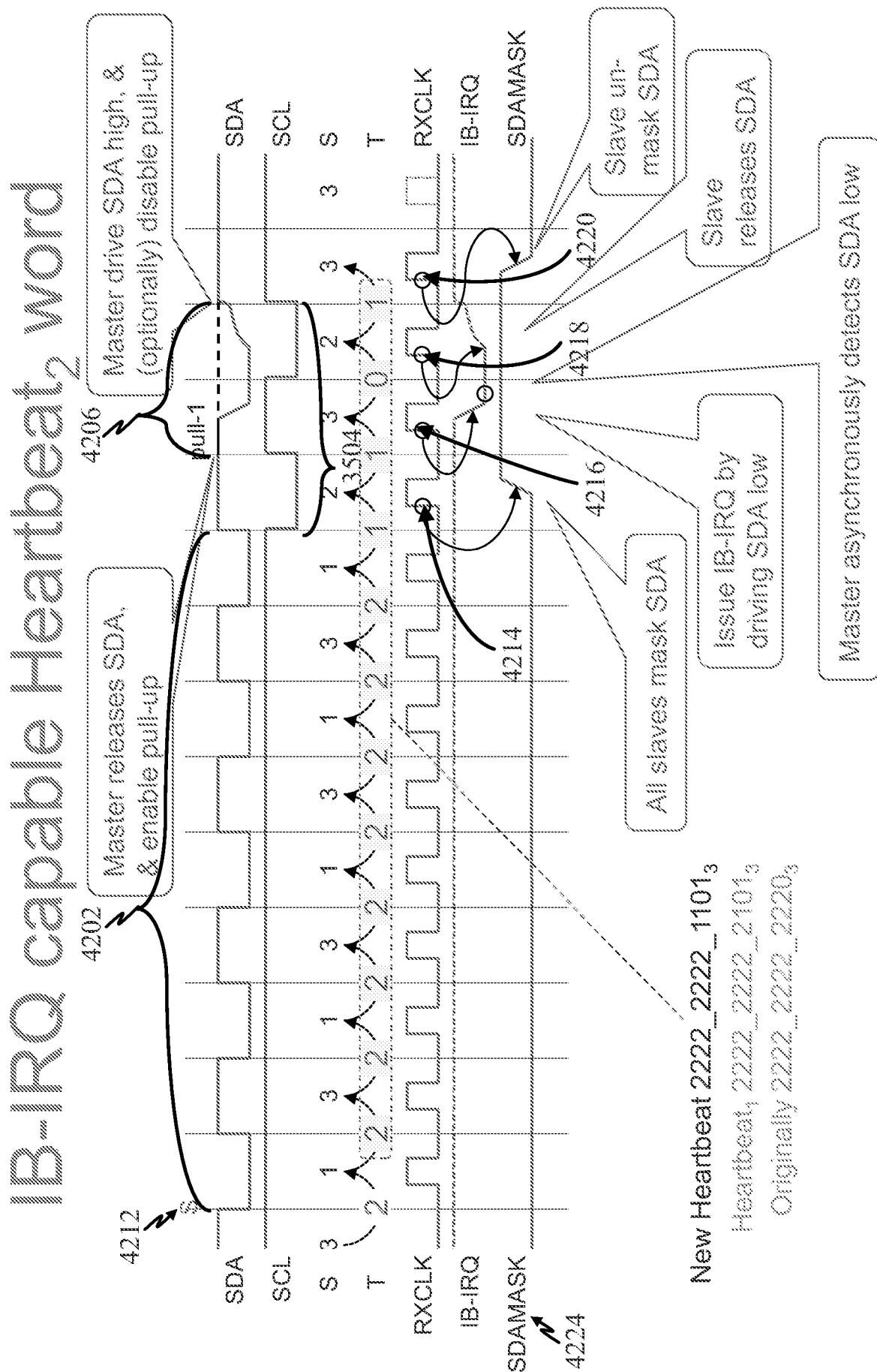

[0069] FIG. 40 illustrates the condition during the in-band IRQ period of FIG. 39 in which the SDA line is masked.

[0070] FIG. 41 illustrates a side-effect of SDA Mask of FIGS. 39 and 40.

[0071] FIG. 42 illustrates that the heartbeat used for in-band IRQs occupies the number space 0x81BBB~0x81BD5 (i.e., 27 addresses) within the ternary number space.

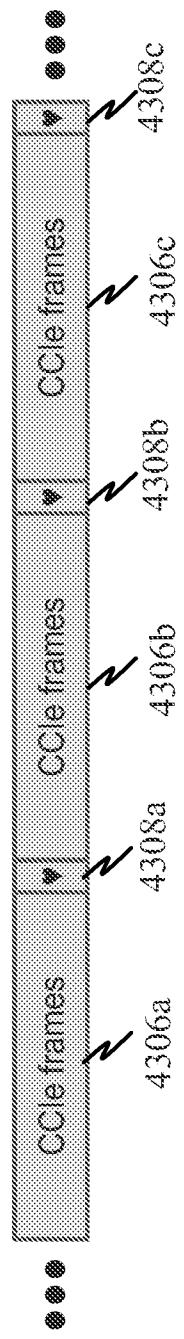

[0072] FIG. 43 illustrates how heartbeats may be transmitted when the master device is active mode and in a power savings mode.

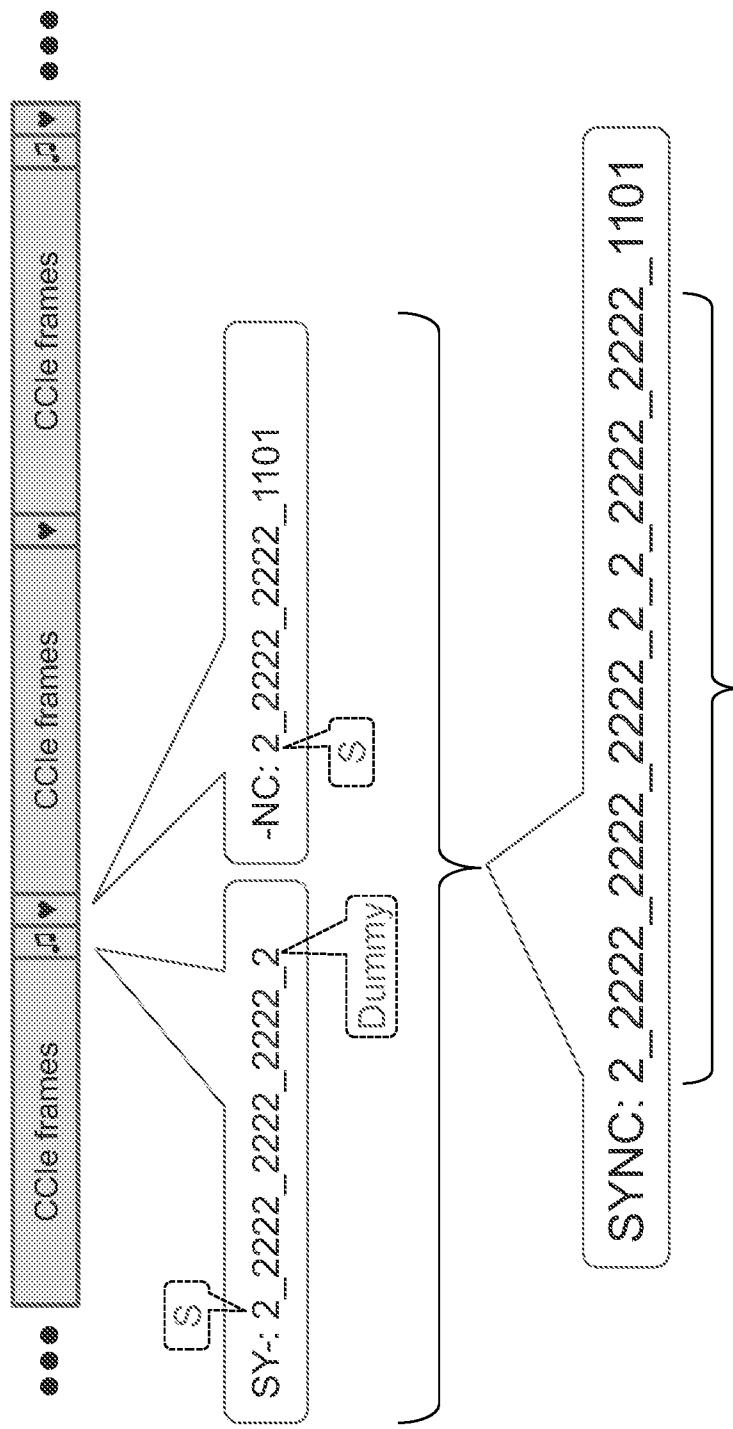

[0073] FIG. 44 illustrates the combination synchronization word and heartbeat.

[0074] FIG. 45 illustrates the synchronization and heartbeat mapping within bit 19 of the CCIE protocol.

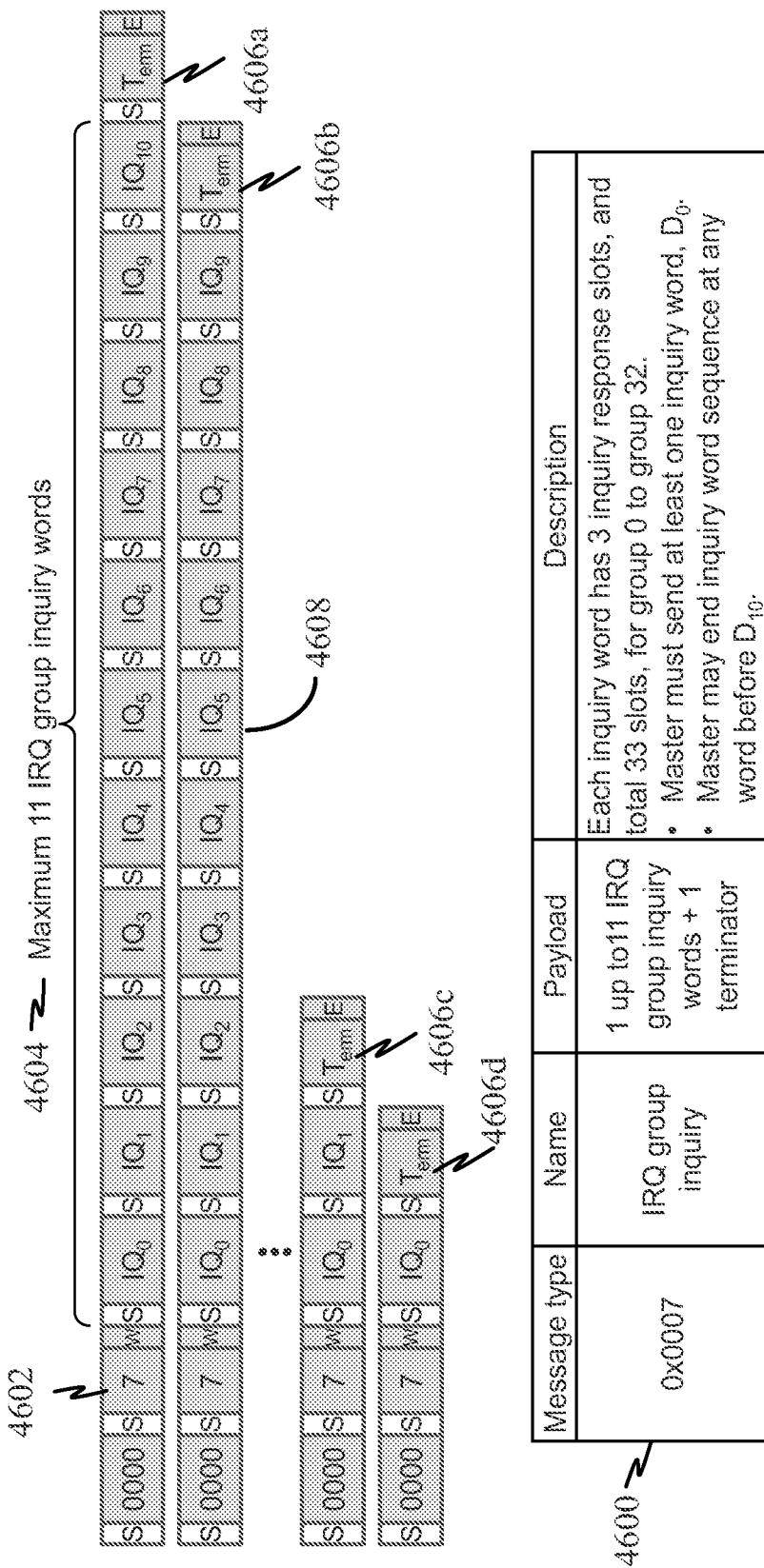

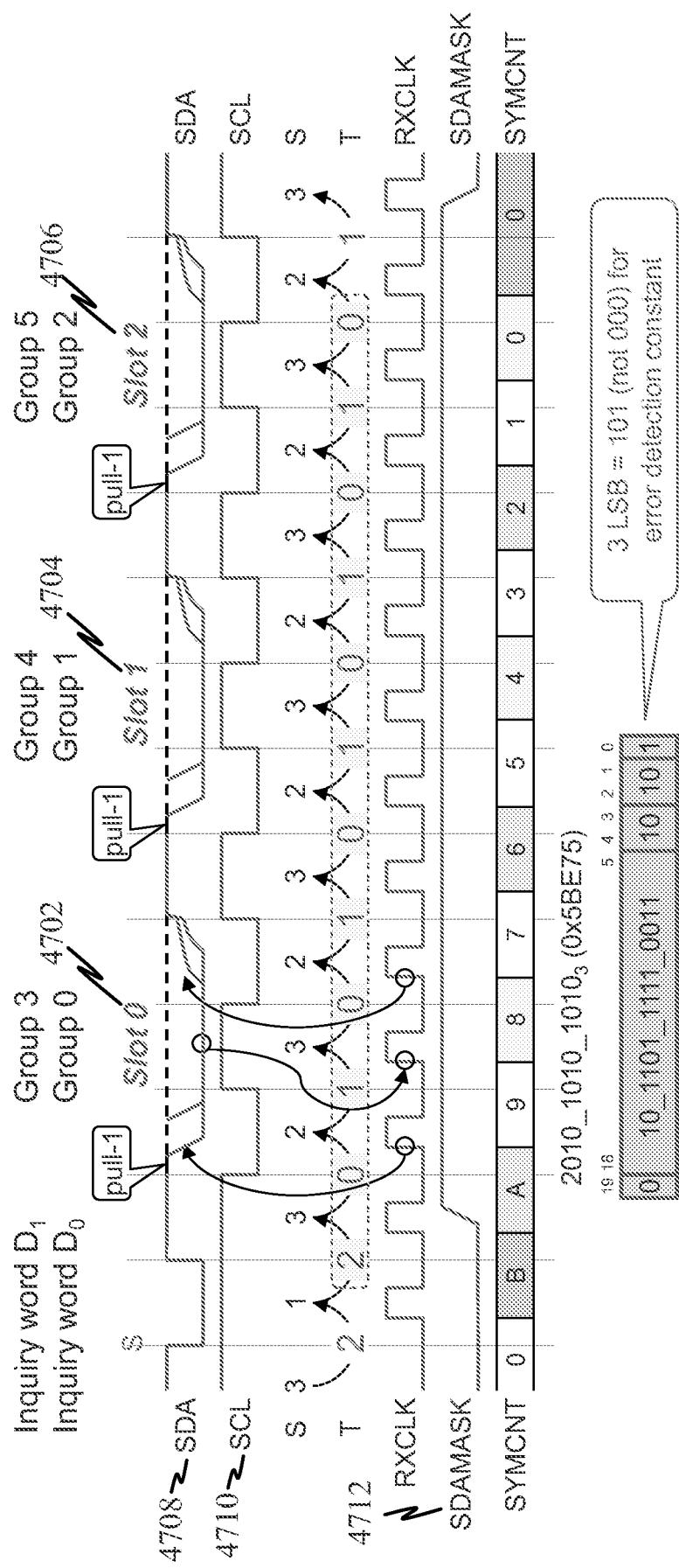

[0075] FIG. 46 illustrates an interrupt group inquiry general call within an exemplary CCIE protocol.

[0076] FIG. 47 illustrates the response to a group inquiry call. In this example, one or more response periods (i.e., inquiry words) may be defined on the SDA line by transferring the heartbeat to the SCL line and using an SDA mask.

**[0077]** FIG. 48 illustrates an exemplary “terminator word” that may be used to indicate the end of an IRQ group inquiry general call to make the length (i.e., word count) of the IRQ group inquiry general call flexible.

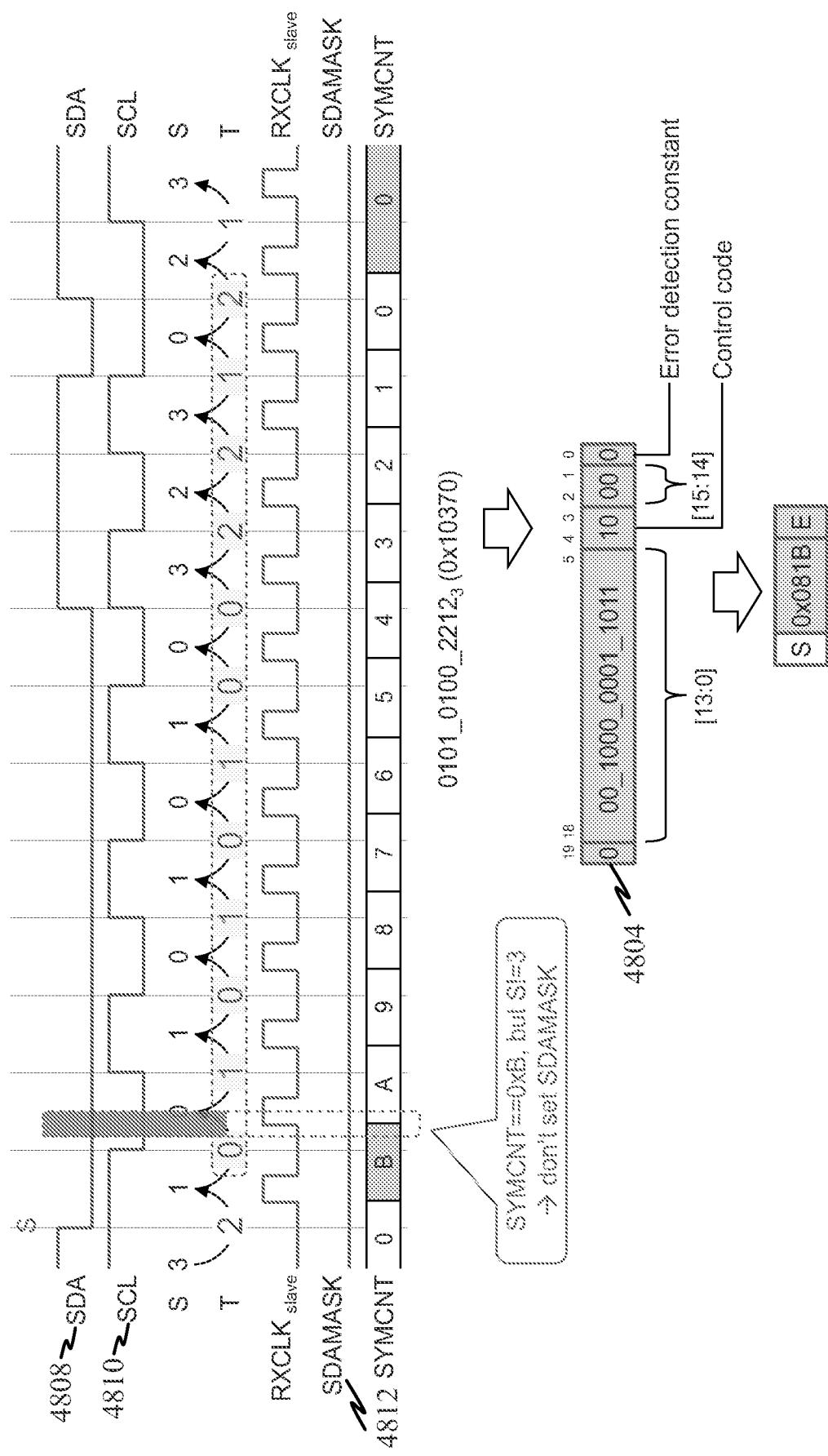

**[0078]** FIG. 49 illustrates one example of how a DDR clock read general call may be implemented

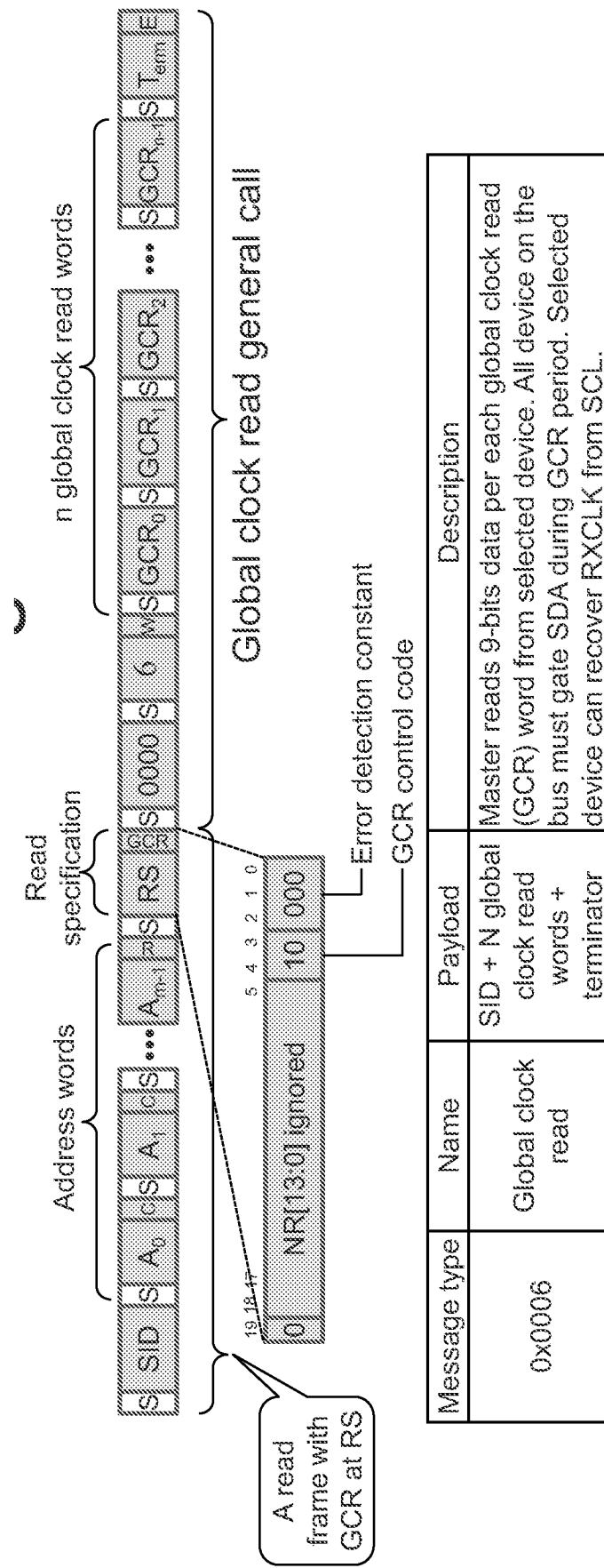

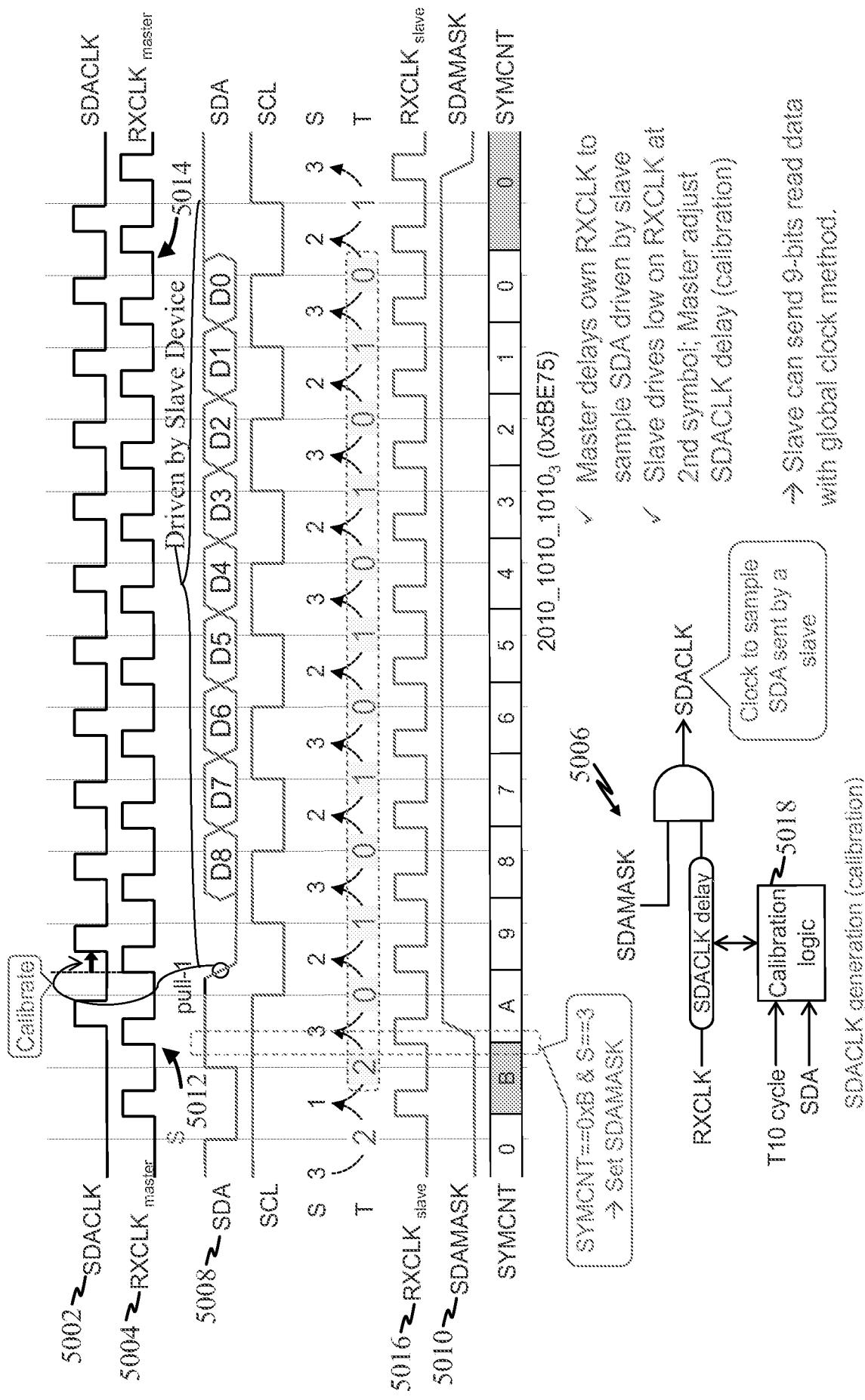

**[0079]** FIG. 50 illustrates an exemplary timing diagram for a global clock read word.

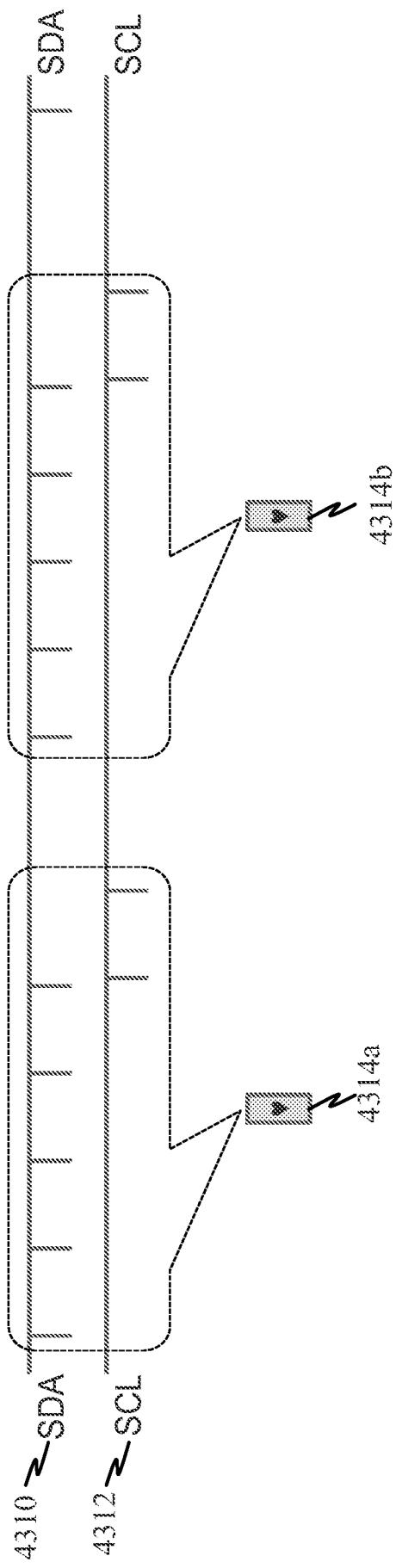

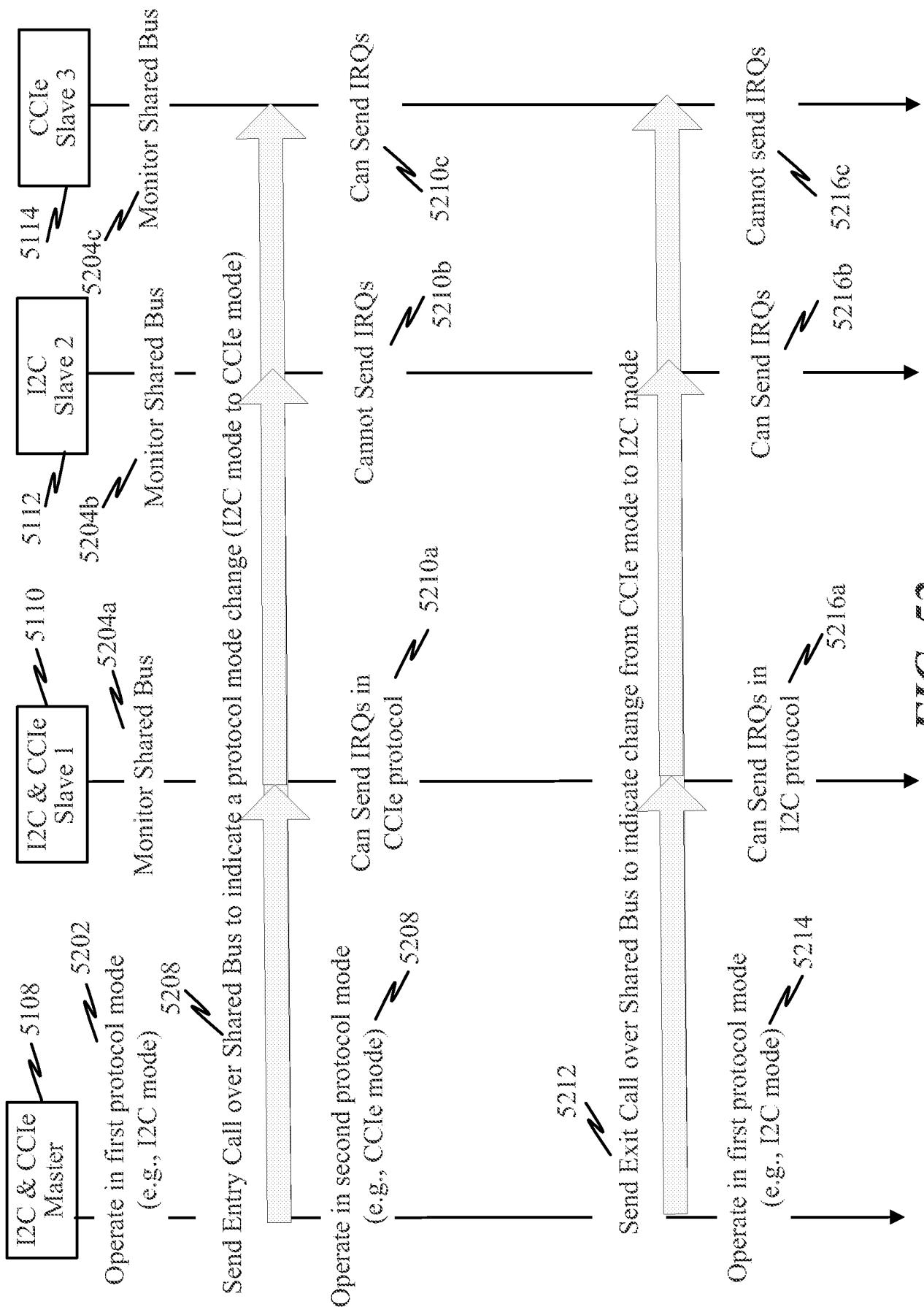

**[0080]** FIG. 51 illustrates the coexistence of I2C-compatible and CCIe-compatible devices on a shared bus within a device, where all master/slave devices use in-band interrupts over the shared bus.

**[0081]** FIG. 52 illustrates the coexistence of the master/slave devices of FIG. 51 over a shared bus

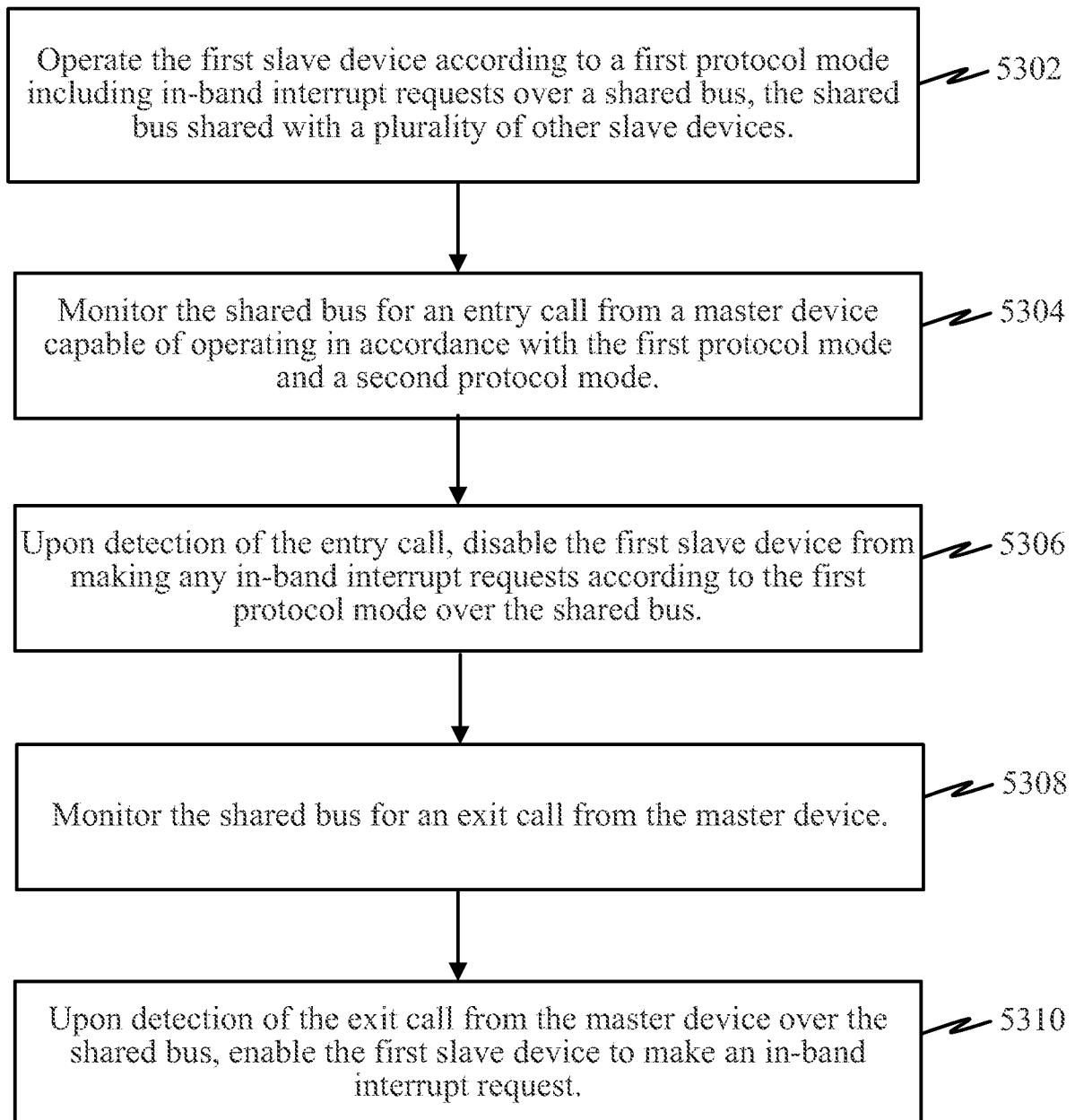

**[0082]** FIG. 53 illustrates a method operational by an I2C-compatible slave device that facilitates coexistence with CCIe-compatible slave devices over a shared bus, where all devices can use in-band interrupts over the shared bus.

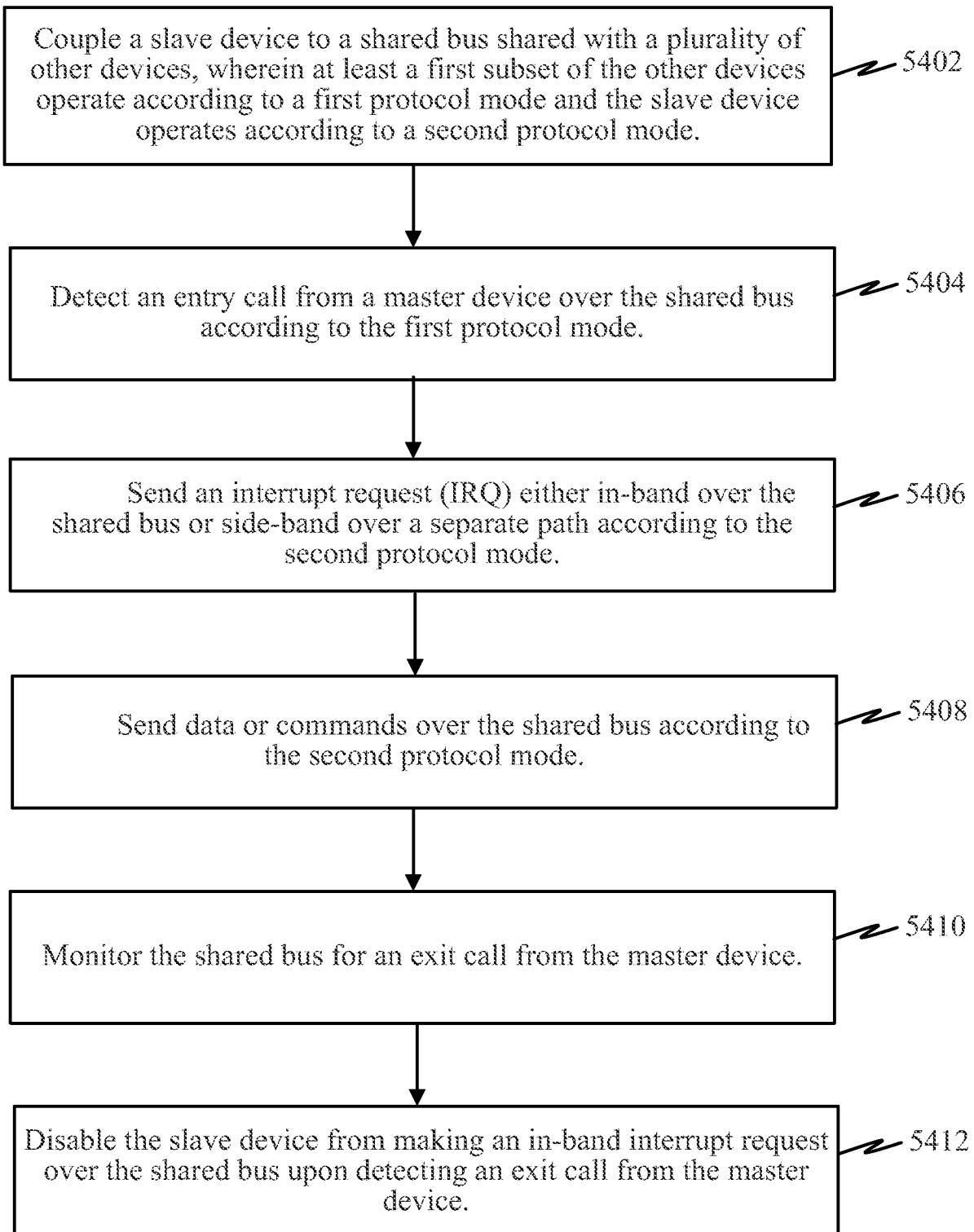

**[0083]** FIG. 54 illustrates a method operational by a CCIe-compatible slave device that facilitates coexistence with I2C-compatible slave devices over a shared bus, where all devices can use in-band interrupts over the shared bus.

**[0084]** FIG. 55 illustrates an exemplary multi-mode master device.

**[0085]** FIG. 56 illustrates an exemplary slave device.

**[0086]** FIG. 57 illustrates an exemplary interrupt request router slave device.

## DETAILED DESCRIPTION

**[0087]** In the following description, specific details are given to provide a thorough understanding of the embodiments. However, it will be understood by one of ordinary skill in the art that the embodiments may be practiced without these specific details. For example, circuits may be shown in block diagrams in order not to obscure the embodiments in unnecessary detail. In other instances, well-known circuits, structures, and techniques may not be shown in detail in order not to obscure the embodiments.

### Overview

**[0088]** A first feature provides a way to concurrently operate devices on a common/shared bus (e.g., a control data bus) according to multiple modes of operation. A plurality of slave devices may be coupled to a control data bus along with at least one

master device that controls access to the control data bus. At least a first slave device may operate in a subset I2C (sI2C) protocol mode of operation and at least a second slave device may operate in a camera control interface extension (CCIE) mode of operation. Note that the use of sI2C mode (e.g., first mode) and CCIE mode (e.g., second mode) are exemplary modes and other operating modes (e.g., for different communication standards). The first slave device (e.g., sI2C-compatible slave device) operating in the sI2C protocol mode (e.g., first mode) may use the control data bus for interrupt requests or IRQs (e.g., referred to as in-band IRQs). In one example, such IRQs may be issued by the first slave device to indicate to the master device that it wishes to use the shared bus. By contrast, the second slave device (CCIE slave device) operates in CCIE mode (e.g., second mode) and uses a dedicated IRQ line for IRQs. In order to maintain the integrity of CCIE communications over the shared bus, the first slave device operating in the sI2C protocol mode disables its IRQ ability (e.g., does not issue in-band IRQs) upon a CCIE communication starting over the shared control data bus. That is, while the shared control data bus is used for CCIE communications, the first slave device operating in the sI2C protocol mode is prevented from sending interrupts over the shared bus.

**[0089]** Although the first slave device operating in the sI2C protocol mode does not understand CCIE communications, entry into the CCIE mode is initiated by the master device operating in the CCIE mode by sending an I2C protocol message over the shared control data bus announcing entry into the CCIE mode. The first slave device, operating in the sI2C protocol mode, understands this CCIE entry announcement and may desist from using the shared control data bus. Additionally, after sending the CCIE entry announcement over the shared control data bus (i.e., a message in the I2C protocol, which the first slave device operating in the sI2C protocol mode understands), the master device operating in the CCIE mode sends an exit/stop message (e.g., in the CCIE protocol and the I2C protocol) announcing an exit or stop from using the shared bus for CCIE communications. The first slave device operating in the sI2C protocol mode disables its own ability to send IRQs over the shared bus while the shared bus is being used for CCIE mode communications.

**[0090]** From the perspective of the first slave device operating in the sI2C protocol mode (e.g., the “sI2C slave device”), the first slave device receives an understandable I2C protocol message announcing entry into the CCIE mode and immediately disables itself from sending in-band IRQs over the shared control data bus. The first slave

device may then receive one or more CCIe communications which the first slave device (which operates in in the sI2C protocol mode) does not understand and/or ignores. Subsequently, the first slave device receives an understandable I2C protocol message announcing an exit or end of the CCIe mode over the shared bus, and the first slave device enables itself to send in-band IRQs. This self-disabling and enabling to send in-band IRQs by sI2C slave devices prevents data collision over the shared control data bus from a sI2C slave device performing an in-band IRQ while a slave device in the CCIe mode is communicating in the CCIe protocol on the same shared control data bus.

**[0091]** A second feature provides for allowing hot plugging (also called hot swapping) of a sI2C slave device onto a CCIe-enabled bus (i.e., the shared control data bus). More generally, this second feature permits a slave device operating according to a first protocol mode (e.g., sI2C compatible communication protocol) to be dynamically plugged or added onto a bus operating according to a different second protocol mode (e.g., CCIe mode). By enabling sI2C slave devices to coexist on a CCIe enabled shared control data bus along with CCIe devices, the hot plug functionality is implemented for devices operating on a CCIe enabled shared bus.

**[0092]** A third feature provides adding an additional way for a sI2C slave device to issue an interrupt (IRQ). In addition to the sI2C slave device using the shared bus (e.g., control data bus) to issue in-band interrupts (IRQs), a separate line (e.g., dedicated IRQ bus or line for sI2C devices) may be utilized to couple the sI2C slave device to an IRQ router CCIe-compatible slave device. The IRQ router CCIe-compatible slave device receives the sI2C protocol interrupts (IRQs) and routes the sI2C protocol IRQ to a CCIe IRQ bus or line. In one example, the sI2C slave device may monitor the shared bus for an entry into the CCIe mode. However, instead of disabling the ability of the sI2C slave device to perform an IRQ, internal logic switches the output of the IRQ from the shared bus to the line coupling the sI2C slave device to the IRQ router CCIe-compatible slave. Subsequently, upon sensing an exit signal while the shared bus is operating according to CCIe mode, the sI2C slave device may again start using the shared bus for issuing in-band IRQs. Accordingly, both sI2C slave devices and slave devices in the CCIe mode can coexist on a CCIe enabled bus without data collisions. The IRQ router CCIe-compatible slave device routes all IRQs received from sI2C slave devices to a dedicated IRQ line or bus operating in the CCIe mode.

**[0093]** A fourth feature provides for sI2C-compatible devices and CCIe-devices to coexist over the same shared bus while both types of devices use in-band interrupt requests (IRQs).

#### **Exemplary Coexistence of Devices Using Different Communication Protocols Over A Shared Bus**

**[0094]** FIG. 1 is a block diagram illustrating a device 102 having a baseband processor 104 and an image sensor 106 and implementing an image data bus 116 and a multi-mode control data bus 108. While FIG. 1 illustrates the multi-mode control data bus 108 within a camera device, it should be clear that this control data bus 108 may be implemented in various different devices and/or systems. Image data may be sent from the image sensor 106 to the baseband processor 104 over an image data bus 116 (e.g., a high speed differential DPHY link). In one example, the control data bus 108 may be an I2C bus comprising two wires, a clock line (SCL) and a serial data line (SDA). The clock line SCL may be used to synchronize all data transfers over the I2C bus (control data bus 108). The data line SDA and clock line SCL are coupled to all devices 112, 114, 118, 122, and 124 on the I2C bus (control data bus 108). Some or all of the devices 112, 114, and 118 may also be coupled with a one line interrupt (IRQ) bus 120. The slave devices 114, 118, 122, and 124 may have different protocol modes (e.g., may operate using different protocols). For example, a first slave device 122 may be a sI2C-compatible slave device (e.g., communicates according to the sI2C protocol), a second slave device 124 may be a CCIe-compatible slave device (e.g., communicates according to the CCIe protocol), and a third slave device 118 may be capable of multi-mode operation (e.g., communicates according to the I2C/sI2C and CCIe protocols). In one example, control data may be exchanged between the baseband processor 104 and the image sensor 106 as well as the slave devices 118, 122, 124 via the shared control data bus 108. The standard clock (SCL) speed for I2C communications/signaling is up to 100KHz. The standard clock SCL speed in I2C fast mode is up to 400KHz, and in I2C fast mode plus (Fm+) it is up to 1 MHz. These operating modes over an I2C bus may be referred to as a camera control interface (CCI) mode when used for camera applications.

**[0095]** According to one aspect, an improved mode of operation (i.e., greater than 1 MHz) may be implemented over the multi-mode control data bus 108 to support camera operation. This improved mode of operation over an I2C bus may be referred to as a

camera control interface extension (CCIE) mode when used for camera applications. In this example, the baseband processor 104 includes a master device/node 112 and the image sensor 106 includes a slave device/node 114, both the master device 112 and slave device 114 may operate according to the camera control interface extension (CCIE) mode over the control data bus 108 without affecting the proper operation of other legacy I2C devices coupled to the control data bus 108. According to one aspect, this improved mode of operation over the control data bus 108 may be implemented without any bridge device between CCIE devices and any legacy I2C slave devices. According to one aspect, legacy I2C devices may operate in a first mode having a first clock, first bus speed, and/or first signal protocol, while CCIE-capable devices may operate in a second mode having a second clock, second bus speed, and/or second protocol. The first clock, first bus speed, and/or first signal protocol may be distinct from the second clock, second bus speed, and/or second protocol. For example, the second clock and/or second bus speed may be faster or have greater speed than the first clock and/or first bus speed, respectively.

**[0096]** According to one aspect, when all slave devices 118 and 124 are CCIE-capable devices there is no need to switch between the first mode and second mode of operation. That is, all signaling and/or communications over the control data bus 108 may be performed according to the second mode (e.g., at a second clock, second bus speed, and/or a second protocol). For example, because the second mode may provide a greater bit rate than the first rate of the first mode, there is no need to switch back and forth between the first mode and second mode. In fact, because legacy devices compatible with the first mode need not be accommodated, a third mode of operation may be implemented which provides a higher/greater bit rate than the second mode.

**[0097]** According to another aspect, at least the first slave device 122 is sI2C compatible to allow the first slave device 122 to be hot pluggable. The sI2C slave device 122 disables its own ability to send in-band IRQs over the control data bus 108 whenever any other device on the control data bus 108 sends a CCIE entry message (in I2C protocol format) over the control data bus 108. The IRQ disabled slave device 122 may be totally disabled or partially disabled. When totally disabled, the sI2C slave device 122 sends no in-band IRQs over the control data bus 108. In some implementations, when partially disabled, rather than sending an in-band IRQ over the control data bus 108, the sI2C slave device 122 may send side-band IRQs over a

connection to an IRQ router CCIe slave device that may serve to route side-band IRQs from the sI2C slave device 122 to a dedicated IRQ bus or line.

**[0098]** FIG. 2 is a block diagram illustrating the exemplary coexistence of I2C mode 202 (e.g., legacy CCI or first mode) and CCIe mode 204 (e.g., second mode) over a shared I2C bus 206 (e.g., control data bus). A master device 208 which manages access to the bus 206 may be capable of operating according to the I2C mode (e.g., first mode) and the CCIe mode (e.g., second mode).

**[0099]** In I2C mode 202, a CCIe-capable master device 208 may support full CCI or I2C Fm+ capability, while a CCIe-capable slave device 210 may not support full I2C capability. In I2C mode, the CCIe master 208 communicates with I2C slaves 210a, 210b, 210c, 210d on the bus 206 using CCI or I2C Fm+ protocol at a maximum of 1Mbps link rate.

**[00100]** Like the CCI standard operation, CCIe operation 204 only supports a single master device operation (e.g., multiple masters are not supported). In CCIe mode 204 (e.g., the bus 206 is being used for CCIe protocol communications), the CCIe master device 208 communicates with only CCIe-capable slave devices 212a and 212b on the control data bus 206, at either 6.4 Mbps or 16.7 Mbps for example.

**[00101]** At a start-up, by default, the bus 206 may operate in legacy I2C mode 202 (e.g., the bus 206 is being used for CCIe protocol communications). When CCIe master 208 wants to access to a CCIe slave 212a and/or 212b, it switches from I2C mode 202 to CCIe mode 204 by means of an I2C general call.

**[00102]** In CCIe mode 204, when CCIe master 208 wants to access the I2C slaves 210a, 210b, 210c, and/or 210d, it switches from CCIe mode 204 back to I2C mode 202 by means of a combination of CCIe “exit” protocol and an I2C general call.

**[00103]** FIG. 3 is a block diagram illustrating the coexistence of I2C mode 302 (i.e., legacy CCI) and CCIe mode 304 over a common I2C bus 306 including one or more sI2C slave devices 308a and 308b, a multi-mode I2C and CCIe master device 304, one or more I2C slave devices 312a and 312b, and one or more CCIe slave devices 310a and 310b. The various features and operations described with respect to FIG. 2 may be applicable with respect to FIG. 3 and is not repeated in the interest of brevity. In one aspect, the sI2C slave devices 308a and 308b are only capable of sI2C protocol mode operation (wherein most, if not all, I2C communications are understandable by the sI2C slave devices 308a and 308b, and few, if any, CCIe communications are understandable by the sI2C slave devices 308a and 308b). That is, the sI2C slave devices 308a and

308b operate in sI2C mode while CCIe slave devices 310a and 310b operate in CCIe mode. The sI2C slave devices 308a and 308b disable their own ability to send IRQs over the control data bus 306 whenever any device sends a CCIe entry message (in I2C protocol format) over the control data bus 306.

### **Exemplary Communication Protocol and Encoding Method for Increasing Bit Rates Over Shared Bus**

**[00104]** FIG. 4 illustrates how a clock may be embedded within data symbols, thereby allowing the use of both I2C wires (i.e., SDA line and SCL line) for data transmissions. In one example, this embedding of the clock may be achieved by transition clock transcoding. For instance, the data 404 to be transmitted over the physical link (wires) is transcoded so that it changes state at every symbol cycle of the transmitted symbols 406. Consequently, the original clock 402 is embedded in the change of symbol states at every symbol cycle. A receiver recovers clock information 408 from the state transition at each symbol (in the transmitted symbols 406) and then reverses the transcoding of the transmitted symbols 406 to obtain the original data 410. This allows both wires of the I2C bus (control data bus 108 in FIG. 1, SDA line and SCL line) to be used to send data information. Additionally, the symbol rate can be doubled since it is no longer necessary to have a setup and hold time between clock and data signals.

**[00105]** FIG. 5 is a block diagram illustrating an exemplary method for transcoding of data bits into transcoded symbols at a transmitter to embed a clock signal within the transcoded symbols. At the transmitter 502, a sequence of data bits 504 are converted into a ternary (base 3) number (i.e., a “transition number”), and the ternary numbers are then converted into (sequential) symbols which are transmitted over the clock line SCL 512 and the data line SDA 514.

**[00106]** In one example, an original 20 bits of binary data is input into a bit-to-transition number converter block 508 to be converted to a 12-digit ternary number. Each digit of a 12-digit ternary number represents a “transition number”. Two consecutive transition numbers may have be the same numbers (i.e., consecutive digits of the ternary number may be the same). Each transition number is converted into a sequential symbol at a transition-to-symbol block 510 such that no two consecutive sequential symbols have the same values. Because a transition is guaranteed at every sequential symbol, such sequential symbol transition may serve to embed a clock signal.

Each sequential symbol 516 is then sent over a two wire physical link (e.g., I2C bus comprising a SCL line 512 and a SDA line 514).

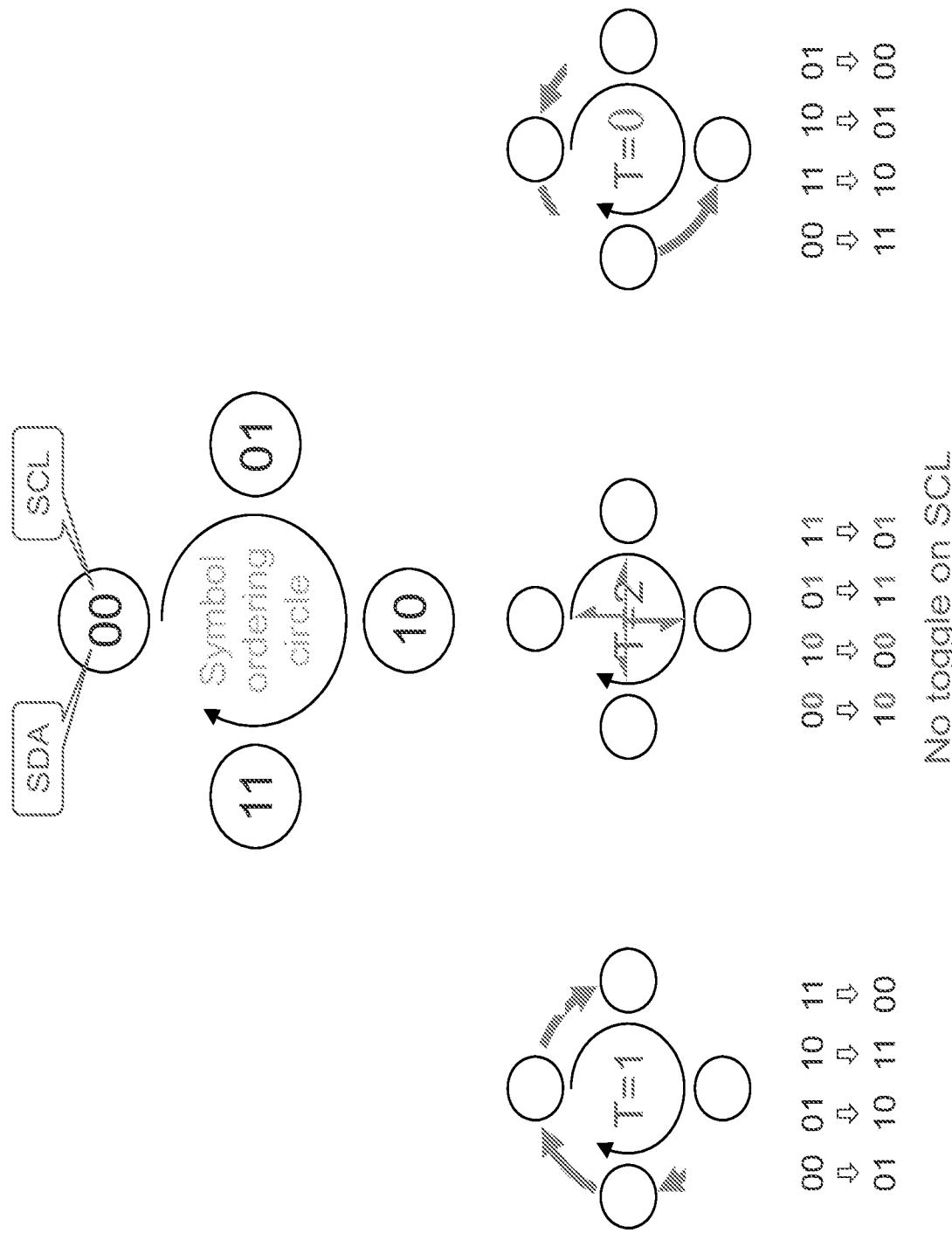

**[00107]** FIG. 6 illustrates an exemplary conversion between transition numbers 602 and sequential symbols 604. An individual digit of ternary number, base-3 number, also referred to as a transition number, can have one of the three (3) possible digits or states, 0, 1, or 2. While the same digit may appear in two consecutive digits of the ternary number, no two consecutive sequential symbols have the same value. The conversion between a transition number and a sequential symbol guarantees that the sequential symbol always changes (from sequential symbol to sequential symbol) even if consecutive transition numbers are the same.

**[00108]** FIG. 7 further illustrates an exemplary conversion between transition numbers and sequential symbols. On the transmitter side (TX: T to S) 702, a transition number (T) may be converted to a sequential symbol (S). For instance, a current sequential symbol (Cs) may be obtained based on a previous sequential symbol (Ps) and a temporary transition number (T<sub>tmp</sub>) that is a function of a current transition number (T). The temporary transition number (T<sub>tmp</sub>) may be obtained by comparing the current transition number T to zero and when T = zero, the temporary transition number (T<sub>tmp</sub>) becomes equal to 3, else (when T not equal zero) T<sub>tmp</sub> becomes equal to T (i.e., T<sub>tmp</sub> = T = 0 ? 3 : T). The current sequential symbol may be obtained as a sum of the current sequential symbol (Cs) plus the previous sequential symbol (Ps) plus the temporary transition number (T<sub>tmp</sub>) (i.e., C<sub>s</sub> = P<sub>s</sub> + T<sub>tmp</sub>).

**[00109]** On the receiver side (RX: S to T) 704 the conversion operation is reversed to obtain a transition number from a current sequential symbol (Cs) and a previous sequential symbol (Ps). A temporary transition number (T<sub>tmp</sub>) may be obtained as the sum of the current sequential symbol (Cs) plus 4 minus the previous symbol (Ps) (i.e., T<sub>tmp</sub> = C<sub>s</sub> + 4 - P<sub>s</sub>). The current transition number (T) is equal to the temporary transition number (T<sub>tmp</sub>), but the temporary transition number (T<sub>tmp</sub>) is compared to three (3) and when T<sub>tmp</sub> = 3, the temporary transition number (T<sub>tmp</sub>) becomes equal to zero (0), else (when T<sub>tmp</sub> not equal 3) T becomes equal to T<sub>tmp</sub> (i.e., T = T<sub>tmp</sub> = 3 ? 0 : T).

**[00110]** A table 706 illustrates the conversion between transition numbers and sequential symbols.

**[00111]** Referring again to FIG. 6, an example of the conversion between transition numbers and sequential symbols is illustrated therein. For example, in a first cycle 606,

the current transition number (Ta) is 2, so  $T_{tmp}$  is also 2, and with the previous sequential symbol  $P_s$  being 1, the new current sequential symbol  $C_s$  is now 3.

**[00112]** In a second cycle 608, the transition number (Tb) is 1. Since the transition number (Tb) is not equal to zero, the temporary transition number  $T_{tmp}$  is equal to the transition number (Tb) value of 1. The current sequential symbol (Cs) is obtained by adding the previous sequential symbol (Ps) value of 3 to the temporary transition number  $T_{tmp}$  of 1. Since the result of the addition operation equals 4, which is greater than 3, the rolled over number 0 becomes the current sequential symbol (Cs).

**[00113]** In a third cycle 610, the current transition number (T) is 1. Because the transition number T is 1, the temporary transition number  $T_{tmp}$  is also 1. The current sequential symbol (Cs) is obtained by adding the previous sequential symbol (Ps) value of 0 to the temporary transition number  $T_{tmp}$  of 1. Since the result of the addition operation equals 1, which is not greater than 3, the current symbol (Cs) is equal to 1.

**[00114]** In a fourth cycle 612, current transition number (T) is 0. Because the transition number T is 0, the temporary transition number  $T_{tmp}$  is 3.

**[00115]** The current sequential symbol (Cs) is obtained by adding the previous sequential symbol (Ps) value of 1 to the temporary transition number  $T_{tmp}$  of 3. Since the result of the addition operation is 4, which is greater than 3, the rolled over number 0 becomes the current sequential symbol (Cs).

**[00116]** Note that even if two consecutive ternary digits Tb and Tc have the same numbers, this conversion guarantees that two consecutive sequential symbols have different state values. Because of this, the guaranteed transition in the sequential symbols 604 may serve to embed a clock signal, thereby freeing the clock line SCL in an I2C bus for data transmissions.

**[00117]** Referring again to FIG. 5, at the receiver 520 the process is reversed to convert the transcoded symbols back to bits and, in the process, a clock signal is extracted from the symbol transition. The receiver 520 receives a sequence of sequential symbols 522 over the two wire physical link (e.g., I2C bus comprising a SCL line 524 and a SDA line 526). The received sequential symbols 522 are input into a clock-data recovery (CDR) block 528 to recover a clock timing and sample the transcoded symbols (S). A symbol-to-transition number converter block 530 then converts the transcoded (sequential) symbols to a transition number, i.e., one ternary digit number. Then, a transition number-to-bits converter 532 converts 12 transition numbers to restore 20 bits of original data from the 12 digit ternary number.

**[00118]** This technique illustrated herein may be used to increase the link rate of a control bus 108 (FIG. 1) beyond what the I2C standard bus provides and is referred hereto as CCIE mode. In one example, a master node/device and/or a slave node/device coupled to the control data bus 108 may implement transmitters and/or receivers that embed a clock signal within symbol transmissions (as illustrated in FIGS. 4 and 5) in order to achieve higher bit rates over the same control data bus than is possible using a standard I2C bus.

#### **Exemplary Method for Supporting I2C, sI2C, and CCIE Devices On A Shared Bus**

**[00119]** One feature provides for implementing a shared bus that supports both I2C devices and CCIE devices at the same time. As noted in FIGS. 1-7, it is possible to embed a clock signal (SCL line for I2C bus) within symbol transitions, thereby allowing the use of a clock line (SCL line) for data transmissions. This may permit, for example, a CCIE mode of operation with higher bit rates than typical I2C mode buses.

**[00120]** However, one challenge is to permit the operation of both legacy I2C-compatible devices and CCIE-compatible devices on the same shared bus at the same time. Some details about the requirements of the I2C protocol and CCIE protocol may be useful in formulating a way to support devices operating according to these modes.

**[00121]** The I2C standard requires that all I2C compatible slave devices must reset their bus logic on receipt of a START condition (e.g., indicated by a high-to-low transition on the SDA line while the SCL line is high on the shared bus).

**[00122]** FIG. 8 illustrates a timing diagram of an I2C one byte write data operation. The I2C master device sends a 7-bit slave ID in the SDA line 802 to indicate which slave device on the I2C bus the master device wishes to access, then one bit to indicate a write operation. Only the slave device whose ID matches with the 7-bit slave ID can cause intended actions. In order for an I2C slave device to detect its own ID, the master device has to send at least 8-bits on the SDA line (or 8 clock pulse on the SCL line 804). Therefore, this can be exploited when operating the shared bus in CCIE mode to prevent legacy I2C slave devices from reacting to any CCIE operations over the shared bus. In particular, if the CCIE protocol sends less than 7-bits between start (S) indicators, then the legacy I2C slave devices (which expect at least 7-bits) treat this as an incomplete slave identifier (SID) and resets its logic.

**[00123]** FIG. 9 illustrates a timing diagram of a sI2C one byte write data operation wherein the most significant bit (MSB) is one (1), in accordance with the sI2C protocol.

In this example, the I2C transmission over the SDA line 902 may include a one (1) in the most significant bit of the slave identifier (SID) 904. The MSB being one (1) allows for hot plugging or swapping of I2C slave devices because a master device can easily know a newly added slave device is a slave device by merely examining the MSB.

**[00124]** FIG. 10 illustrates one example of the CCIe protocol. The blocks indicate CCIe specific timing and signaling as well as legacy I2C timing and signaling. As illustrated in 1002, there are protocols to enter into CCIe mode, and exit from CCIe mode. Once entry to CCIe mode is executed, the shared bus mode stays in CCIe mode until an exit from CCIe mode is executed. In this example, entry into CCIe mode is accomplished by a CCIe mode entry sequence 1004 as part of a general call during I2C mode. To announce entry into CCIe mode to I2C-compatible devices, the master device operating in CCIe mode may send an I2C general call 1030 over the shared bus announcing entry into the CCIe mode 1032. Similarly, to announce the exit 1006 from CCIe mode the master device may send a CCIe mode exit sequence 1034 as part of a general call. These entry/exit sequences 1030 and 1034 within a general call are used by CCIe-enabled devices to switch from I2C mode to CCIe mode and from CCIe mode to I2C mode, respectively. These general calls 1030 and 1034 also allow I2C-only slave devices to know when the shared bus is switching to CCIe mode and withhold issuing interrupts or otherwise transmitting over the shared bus.

**[00125]** A write data protocol 1008 can send an arbitrary number of address words 1014 and data words 1016 to a slave node/device identified by a Slave Identifier (SID) 1018. Similarly, a read data protocol 1010 can read a plurality of data words 1022 from a slave node/device identified by a Slave Identifier (SID), while the number of address words 1020 is still arbitrary.

**[00126]** One last special protocol is the clock data recovery (CDR) calibration 1012, that may be used by the CCIe master device to cause an indicated CCIe device (including the master device itself) to start a sequence to calibrate its clock-data recovery logic to maximize the link rate. For this purpose, the CCIe master device also has to have its own slave ID.

**[00127]** Any CCIe words may be sent in 12-symbols that carry 19-bits information. Except for the CDR calibration protocol 1012, 16 bits of the 19-bits may be data information while 3 bits of the 19-bits are used for other information such as control information.

**[00128]** FIG. 11 illustrates a diagram of an exemplary in-band interrupt signal (IRQ) 1102 sent by a sI2C-compatible slave device over a shared bus. The slave device pulls down or grounds 1106 the SDA line 1104 of a shared bus which a master device detects and then releases the SDA line 1104 to the requesting slave device. The slave device is then able to transmit its IRQ signal 1102. Upon termination of the IRQ signal, the master device may acknowledge receipt of the interrupt signal by holding the SDA line 1104 low for a period of time.

**[00129]** Referring again to FIG. 10, like a I2C-compatible slave device, a sI2C slave device may receive an understandable I2C protocol message 1030 announcing entry into the CCIE mode and immediately disables itself from sending in-band IRQs (i.e., interrupt signals over the shared bus). The sI2C slave device may then receive a CCIE communication 1032 which the sI2C slave device does not understand and ignores. Lastly, the sI2C slave device may receive an understandable I2C protocol message 1034 announcing an exit from the CCIE mode, and the sI2C slave device enables itself for sending in-band IRQs again

**[00130]** FIG. 12 illustrates an additional way of a sI2C slave device to issue an interrupt signal (IRQ) in a mixed protocol mode environment (e.g., where a shared bus can operate according to or dynamically switch between distinct communication protocols). As previously noted, while a shared bus 1204 is managed by a master device 1208 in CCIE mode, sI2C-compatible slave devices 1210a and 1210b may desist from sending or issuing in-band interrupt signals over the shared bus 1204. However, in this alternative approach, these sI2C-compatible slave devices 1210a and 1210b may be coupled to an IRQ router CCIE slave device 1216 via one or more separate lines 1212 and 1214. When the shared bus 1204 is operating in CCIE mode, the sI2C-compatible slave devices 1210 may be configured to send their interrupt signals to the IRQ router CCIE slave device 1216 instead. The IRQ router CCIE slave device 1216 receives the sI2C protocol interrupt signals and routes the interrupt to a CCIE IRQ bus or line 1206 so that they may be processed by the master device 1208. The master device 1208 may then decide whether to switch the shared bus 1204 to I2C mode and grant the requesting I2C-compatible slave device its interrupt request.

**[00131]** Consequently, while the shared bus 1204 may be operating in CCIE mode, instead of the sI2C-compatible slave devices 1210 disabling their ability to issue an interrupt signal (e.g., requesting a service or use of the shared bus 1204), internal logic within each sI2C-compatible slave device 1210 may switch the output of the interrupt

signal from the shared bus 1204 to the separate line 1212 or 1214 coupling the sI2C slave devices 1210 to the IRQ router CCIE slave device 1216. Also, upon detecting an exit code from the CCIE mode over the shared bus 1204, the sI2C-compatible slave devices 1210 switch back to using the shared bus 1204 for issuing interrupt signals. Accordingly, the sI2C-compatible slave devices 1210 and the CCIE-compatible slave devices 1218 can coexist while the shared bus 1204 operates in CCIE mode without data collisions.

#### **Exemplary Single-Mode Slave Device Operating Over A Multi-Mode Shared Control Data Bus**

**[00132]** FIG. 13 illustrates an exemplary slave device 1302 comprising a transmitter and receiver circuit 1306 and a processing/logic circuit 1304. The transmitter and receiver circuit 1306 may be coupled to the processing circuit 1304 to transmit data to and from the processing/logic circuit 1304 and one or more buses. The transmitter and receiver circuit 1306 may be coupled, for example, to a multi-mode shared bus 1320 that may include a first line and a second line. In a first mode of operation (e.g., I2C mode), the transmitter and receiver circuit 1306 may be configured to use the first line for data transmissions and the second line for a first clock signal. In a second mode of operation (e.g., CCIE mode), the transmitter and receiver circuit 1306 may be configured to use both the first line and the second line for data transmissions while embedding a second clock signal within symbol transitions of the data transmissions. The multi-mode shared bus may be an I2C-compatible bus and/or a CCIE-compatible bus. In a third mode of operation, the transmitter and receiver circuit 1306 operate similar to the second mode but without concurrent support for first mode-only legacy devices (e.g., I2C-compatible legacy devices).

**[00133]** The slave device 1302 may coexist with a set of other devices coupled to the multi-mode shared bus 1320 but operates only in the first mode while constantly monitoring at least the first line and/or second line during both the first mode and second mode of operations. In the first mode of operation, the slave device 1302 may transmits data to another device over the first line of the shared bus 1320. In the second mode of operation, the first line and second line of the shared bus 1320 may both transmit data according to the second mode for other devices that support the second mode.

**[00134]** In various examples, the devices coupled to the shared bus 1320 may support multiple different modes of operation (e.g., distinct communication protocols). For example, a first slave device may be a sI2C-compatible slave device, a second slave device may be a CCIE-compatible slave device, and a third slave device may be capable of multiple modes (e.g., I2C-compatible and CCIE-compatible modes).

**[00135]** The first mode of operation may implement a first protocol for data transmissions over the shared bus 1320 and the second mode implements a second protocol for data transmissions over the shared bus 1320.

**[00136]** In one example, the slave device 1302 may be a sI2C-compatible slave device. The processing circuit 1304 may include a shared bus monitoring circuit/module 1310 that, when the shared bus 1320 operates according to the first mode, serves to monitor for communications over the shared bus 1320. When the shared bus 1320 operates according to the second mode, the shared bus monitoring circuit/module 1310 serves to monitor for an exit call/command indicating that the bus is switching back to first mode. An interrupt request generator circuit/module 1312 may serve to generate an interrupt signal. An interrupt request inhibiting circuit/module 1314 may serve to ascertain when the slave device 1302 should withhold from generating and/or issuing an interrupt request. For instance, if the shared bus monitoring circuit/module 1310 detects that the shared bus 1320 is operating according to a second mode, the interrupt request inhibiting circuit/module 1314 may prevent interrupts from being issued over the shared bus 1322.

**[00137]** The transmitter and receiver circuit 1306 may include a clock recover circuit 1308 (to recover a clock signal from the transmitted data). In an optional/alternative approach, an IRQ switching circuit 1316 may allow the slave device 1302 to issue interrupt request to an interrupt router device 1322 over a separate line when the shared bus 1320 operates in the second mode.

**[00138]** FIG. 14 illustrates a method for permitting a single-mode slave device to coexist on a shared data bus that switches between multiple communications modes. The slave device may operate in a first protocol mode that includes in-band interrupt requests over the shared data bus 1402. The slave device may then monitor the shared data bus for an entry call indicating the shared data bus is switching to operate according to a second protocol mode that does not allow for in-band interrupt requests over the shared data bus 1404. Upon detecting the entry call, the slave device disables issuing any in-band interrupt requests over the shared data bus 1406. Optionally, the

slave device may switch to sending interrupt requests to an interrupt request router via a separate line 1408. The slave device may monitor the shared data bus for an exit call from the second protocol mode 1410. Upon receiving the exit call, the slave device enables making in-band interrupt requests over the shared data bus 1412.

### **Coexistent of I2C Slave Devices and Camera Control Interface Extension Devices on a Shared Control Data Bus with In-Band IRQ**

**[00139]** The previous discussion provided for routing IRQs between I2C-compatible slave devices and CCIE-compatible devices using a dedicated interrupt bus. The following discussion provides for I2C-compatible devices and CCIE-compatible devices to both use in-band interrupts over the shared control data bus.

**[00140]** A first feature provides for eliminating dedicated interrupt lines and pins for all devices coupled a shared bus. Instead, all devices use the shared control data bus to issue interrupt requests, thereby allowing slave devices coupled to the shared control data bus to transmit data over the shared control data bus.

**[00141]** A second feature provides for defining an interrupt period within the symbols transmitted over the shared control data bus during which one or more slave devices coupled to the bus can assert an interrupt request on a first line of the bus while a second line of the bus is used by the master device for a heartbeat transmission, where such heartbeat transmission serves to synchronize the one or more slave devices.

**[00142]** A third feature provides for internally masking the first line of the shared bus, at a receiver device during the interrupt period, for purposes of decoding the transcoded data bits received over the shared bus. For instance, the master device and slave devices may mask the first line input to a clock data recovery circuit (CDR) by using a locally (internally) generated mask signal.

**[00143]** A fourth feature provides for a master device to monitor the first line of the shared control data bus during the interrupt period to ascertain whether a slave device has asserted an interrupt request.

**[00144]** A fifth feature provides for a master device, upon detecting an interrupt request over the first line of the shared control data bus, to scan the slave devices over the shared control data bus to identify the asserting/requesting slave device.

### **Interrupt Mechanism Using Dedicated IRQ Line**

**[00145]** FIG. 15 is a block diagram illustrating a system 1502 having a master device 1508 and a plurality of slave devices 1510a-1510e coupled to a shared control data bus 1504 and a shared interrupt bus/request 1506. In one example, the control data bus 1504 may be an I2C bus comprising two wires, a clock line (SCL) and a serial data line (SDA). The clock line SCL may be used to synchronize all data transfers over the I2C bus (control data bus 1504). The data line SDA and clock line SCL are coupled to all devices 1508 and 1510a-1510e on the I2C bus (control data bus 1504). When used in CCIe mode, both the SDA line and SCL line of the control data bus 1504 may be used for data transmissions.

**[00146]** According to one aspect, the shared interrupt bus 1606 may be a single line coupled to the slave devices 1610a-1610e as well as to the master device 1608. This shared interrupt bus 1506 may be pulled up (e.g., pull high) when not in use and may be pulled low (e.g., grounded) when a slave device asserts an interrupt request (IRQ) signal. That is, each slave device 1510a-1510e may independently request access to transmit on the shared control data bus 1504 by sending an IRQ signal (e.g., request) to the master device 1508.

**[00147]** In some examples, the single line IRQ bus may be an asynchronous bus (e.g., unmanaged by a master device or any other device). This means that the slave devices can unilaterally assert an IRQ signal at any time.

**[00148]** In another example, the single line IRQ bus may be dedicated to unidirectional signal transmissions from slave devices to the master device. That is, the single line IRQ bus may be used for only IRQ signals and no other types of signals.

**[00149]** In one example, the control data bus 1504 may be a camera control interface (CCI) or CCI extension compatible bus.

**[00150]** In another example, the control data bus 1504 may be a bidirectional bus between the slave devices and the master device.

**[00151]** FIG. 16 is a block diagram illustrating how the plurality of slave devices 1510a-1510e in FIG. 15 may be logically grouped for purposes of issuing interrupts. In this example, a first plurality of slave devices 1510a and 1510b may be in a first group 1602 and a second plurality of slave devices 1510c and 1510d may be in a second group 1604. Such groupings may be, for example, pre-configured or dynamically defined (e.g., by enumeration) upon boot-up by the master device 1508. Such groupings allow the master device 1508 to more quickly identify which slave device triggered an IRQ signal on the IRQ bus 1506 without unacceptable delays.

**[00152]** Each group of slave devices 1602 and 1604 may have a distinct IRQ signal. For instance, the first group 1602 may use a first signal having a first period, and the second group 1604 may use a second signal having a second period, and so on. For example, the “period” may be a length of time for which the IRQ bus 1506 is pulled low by the asserting slave device. Note that other forms of signal differentiation may be used, e.g., different voltage levels for the IRQ signals used by different groups of slave devices, etc. In one implementation, each “group” may include a single slave device. In other implementations, each “group” may include 2, 3, and/or 4 slave devices or more. The number of slave devices per group may be a function of how long it would take to query and identify an asserting slave device. For instance, if a large number of slave devices coupled to the IRQ bus 1506 have to be queried by the master device 1508, this may cause an unacceptably long delay. Consequently, grouping slave devices and using distinct IRQ signals for each group allows the master device 1508 to identify an asserting slave device in a relatively short period or an acceptable period of time.

**[00153]** The master device 1508 detects the occurrence of an IRQ signal on the shared single line IRQ bus 1506 and queries each slave device in the group to identify which slave device triggered or asserted the IRQ signal. For example, if the IRQ signal identifies a Group-2 1604 slave device, then the master device 1508 may send a register status request (via the control data bus 1504) to a first slave device 1510c within Group-2 1604. If the first slave device 1510c status response indicates that it is not the asserting slave device, then the master device 108 may send another register status request (via the control data bus 1504) to a second slave device 1510d within Group-2 1604. This process is repeated for all slave devices in Group-2 1604 until the slave device that asserted the IRQ signal is identified.

**[00154]** In an alternative approach, the master device 1508 may scan through all slave devices in Group-2 1604 even if the first slave device 1510c is identified the issuer of the IRQ signal. For instance, it is possible that the more than one slave device in the same group issue an IRQ signal at the same time. Consequently, the master device may know all the IRQ requests from devices in group at once and handle them one-by-one. In one implementation, concurrent or overlapping IRQ requests from multiple devices in a single group may be handled by the master device 1608 in order of urgency, importance, and/or priority.

**[00155]** FIG. 17 illustrates a first example of how IRQ signals may be arbitrated over the IRQ line or bus. In this example, different slave device groups 1702 and 1704 may be defined, with each slave device group 1702 and 1704 having interrupts 1706 and 1708 of different widths. When a slave device detects that the IRQN line 1506 low, it waits for the IRQN line 1506 to become high plus minimum bus free time 1702 before asserting IRQN line low. In this example, a first interrupt 1706 is asserted by a slave device within a first group 1702, followed by a second interrupt request 1708 asserted by another slave device within a second group 1704.

**[00156]** FIG. 18 illustrates a second example of how IRQ signals may be arbitrated over the IRQ line or bus 1506. When two slave devices assert IRQN line low (to indicate an interrupt request) at the same time (or overlapping times), the slave group with longest IRQN low period wins. In this example, a first interrupt signal 1806 has been asserted/issued by a first slave device in a first group 1802 while, concurrently or contemporaneously (e.g., overlapping in time), a second slave device in a second group 1804 has asserted/issued a second interrupt signal 1808 over the shared interrupt bus 1506. Because the second interrupt signal 1808 is longer than the first interrupt signal 1806, the first slave device in the first group 1802 loses arbitration. That is, the second interrupt signal 1808 is recognized on the interrupt bus 1506 but not the first interrupt signal 1806. The requesting first slave device can detect a loss of arbitration when it releases the interrupt bus 1506 at the end of the first interrupt signal 1806 but the interrupt bus 1506 remains low (e.g., pull to ground) when it should have returned to high (e.g., pulled high). Consequently, the first slave device reissues its interrupt signal 1810 at a later time (e.g., after the interrupt bus 1506 has been pulled up again for an amount of time 1812 upon the second interrupt signal 1808 ending.

**[00157]** FIG. 19 illustrates a shortest IRQ signal length that may be feasible in one example. This example assumes that, for an interrupt line 1902, a “high” state can be detected when the IRQ signal 1904 is 70% of VDD level (e.g., high state) at latest and a “low” state can be detected when the IRQ signal 1904 is 30% of VDD level at latest. Note that a high or low state maybe detected when the IRQ signal 1902 is anywhere between 30% to 70% of VDD level depending on receiver input levels. Here, TRF max is the maximum fall-rise time and TLOW is the intended low period. The main purpose of the tLOW constraint is so that the master device is able to distinguish between IRQ signals from different groups of slave devices. Additionally, from the master device’s

point of view, the 2TRF max must be less than TLOW (i.e.,  $2TRF\ max < TLOW$ ) so that the IRQ signal 1904 is guaranteed to be detected as low state.

**[00158]** A first IRQ signal length (period)  $tLOW$  is greater than TLOW-TFR and less than  $2TLOW+TFR$  (i.e.,  $TLOW-TFR < tLOW < 2TLOW+TFR$ ). Similarly, a second IRQ signal length (period)  $tLOW'$  is greater than  $2TLOW-TFR$  and less than  $2TLOW+TFR$  (i.e.,  $2TLOW-TFR < tLOW < 2TLOW+TFR$ ).

**[00159]** Note that after a first slave device asserts IRQ signal low, a second slave device may not detect IRQ signal low for a period of time extending TFR max to  $tLOW$  min which must at least TFR max long. Therefore,  $TLOW > 3TFR\ max$ , and  $tLOW\ min > 2TFR\ max$ .

**[00160]** Side-band IRQ (e.g., over a dedicated IRQ bus/line) has a clear advantage over in-band IRQ (e.g., over the shared control data bus) in terms of interrupt latency. Side-band IRQs may be preferable in some implementations that require very short latencies in the detection of interrupt signals.

### **In-Band Interrupt Mechanism Over Shared Bus**

**[00161]** The side-band IRQ method illustrated in FIGS. 15 to 19 requires the use of an extra pin for each slave device and master device. Slave devices in particular are often limited in size/space available and it would be desirable to eliminate the use of side-band interrupts or the requirement of a dedicated interrupt line/bus. Thus, an alternative to side-band IRQ method is sending in-band IRQs over the shared control data bus.

**[00162]** FIG. 20 is a block diagram illustrating an exemplary system 2002 in which the interrupt bus has been eliminated in favor of in-band interrupts. The system 2002 may include a master device 2008 and a plurality of slave devices 2010a-2010e coupled to a shared control data bus 2004. In one example, the control data bus 2004 may be an I2C bus comprising two wires, a clock line (SCL) and a serial data line (SDA). The clock line SCL may be used to synchronize all data transfers over the I2C bus (control data bus 2004). The data line SDA and clock line SCL are coupled to all devices 2008 and 2010a-2010e on the I2C bus (control data bus 2004). Relative to FIGS. 15-16, this system 2002 does not have a separate interrupt line or bus. Instead, interrupts are sent in-band over the shared control data bus 2004.

**[00163]** One feature provides for implementing a shared control data bus that supports both I2C devices and Camera Control Interface extension (CCIE) devices at the same time (e.g., dynamically switch the shared bus between CCIE mode and I2C mode).

#### **Exemplary CCIE and I2C Transmissions Over Shared Bus**

**[00164]** FIG. 21 illustrates an exemplary timing diagram of an I2C one byte write data operation. In this example, the shared control data bus 2004 (FIG. 20) includes a serial data line SDA 2102 and a serial clock line SCL 2104. The transmission scheme illustrated in FIG. 21 may be referred to as “I2C mode”. The SCL line 2104 is used to send a clock from the master device to all slave devices while the SDA line 2102 transmits data bits. An I2C master device sends a 7-bit slave ID 2208 in the SDA line 2102 to indicate which slave device on the I2C bus the master device wishes to access, then one bit to indicate a write operation. Only the slave device whose ID matches with the 7-bit slave ID 2108 can cause intended actions. In order for an I2C slave device to detect its own ID, the master device has to send at least 8-bits on the SDA line (or 8 clock pulses on the SCL line 2104).

**[00165]** The I2C standard requires that all I2C compatible slave devices reset their bus logic on receipt of a START condition 2106 (e.g., indicated by a high-to-low transition on the SDA line while the SCL line is high).

**[00166]** The CCIE protocol uses both the SDA line 2102 and the SCL line 2104 for data transmissions while embedding a clock signal within the data transmissions. For example, data bits may be transcoded into a plurality of symbols which are then transmitted over lines. By embedding the clock signal (SCL line for I2C bus in FIG. 21) within symbol transitions, both the SDA line 2102 and SCL line 2104 may be used for data transmission.

**[00167]** FIG. 22 illustrates an exemplary CCIE transmission in which data bits have been transcoded into twelve symbols for transmission over the SDA line 2102 and the SCL line 2104. The transmission scheme illustrated in FIG. 22 may be referred to as “CCIE mode”.

**[00168]** CCIE mode is source synchronous, driven by push-pull drivers. Whoever sends out data over the shared control data bus also sends out clock information embedded in the data. Consequently, only one device on the control data bus is allowed to drive the bus at any one time.

**[00169]** In order to support both legacy I2C devices and CCIe devices over the same bus, CCIe mode operations use the same START condition 2200, 2202, 2204, which prevents legacy I2C slave devices from reacting to any CCIe operations (e.g., the Start condition during CCIe mode causes the legacy I2C slave devices to reset). In this example, the START condition 2200, 2202, and 2204 (i.e., indicated by a high to low transition on the SDA line 2102 while the SCL line 2104 is high) is detected before a full slave ID (i.e., a full 7 bits) is transmitted, therefore this is an incomplete slave ID (less than 7 bits). If a master device sends 6 SCL pulses then issues a START condition 2200, 2202, or 2204, then all legacy I2C slave devices reset their bus logic before they recognize the data as an I2C Slave ID. Since the 6-bit sequences (e.g., corresponding to every two symbols) are sent between two START conditions 2200, 2202, and 2204, these 6-bit sequences are not decoded as a valid slave ID by any slave devices. Consequently, legacy I2C slave devices will not act upon the incomplete Slave IDs.