(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7500780号

(P7500780)

(45)発行日 令和6年6月17日(2024.6.17)

(24)登録日 令和6年6月7日(2024.6.7)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 9 G | 3/20 (2006.01)  | F I | G 0 9 G | 3/20  | 6 2 2 G |

| G 1 1 C | 19/28 (2006.01) |     | G 1 1 C | 19/28 | 2 3 0   |

| G 0 9 G | 3/36 (2006.01)  |     | G 0 9 G | 3/20  | 6 2 2 D |

|         |                 |     | G 0 9 G | 3/20  | 6 2 2 Q |

|         |                 |     | G 0 9 G | 3/20  | 6 2 1 M |

請求項の数 14 (全23頁) 最終頁に続く

(21)出願番号 特願2022-573280(P2022-573280)

(86)(22)出願日 令和3年12月30日(2021.12.30)

(65)公表番号 特表2023-544940(P2023-544940)

A)

(43)公表日 令和5年10月26日(2023.10.26)

(86)国際出願番号 PCT/CN2021/143379

(87)国際公開番号 WO2023/040125

(87)国際公開日 令和5年3月23日(2023.3.23)

審査請求日 令和4年11月28日(2022.11.28)

(31)優先権主張番号 202111096140.X

(32)優先日 令和3年9月18日(2021.9.18)

(33)優先権主張国・地域又は機関

中国(CN)

(73)特許権者 521141718

惠科股 分 有限公司

H K C C o r p o r a t i o n L i m

i t e d

中華人民共和国広東省深セン市宝安区石

岩街道石龍社区工業二路1号惠科工業園

厂房1棟一層至三層、五至七層，6棟七

層

1 F - 3 F , 5 F - 7 F o f F a

c t o r y B u i l d i n g 1 , 7 F

o f F a c t o r y B u i l d i n g

6 , H u i k e I n d u s t r i

a l 2 n d R o a d , S h i l o n g

C o m m u n i t y , S h i y a n S

最終頁に続く

(54)【発明の名称】 ゲート集積駆動回路、表示パネル及び表示装置

## (57)【特許請求の範囲】

## 【請求項1】

多段接続のゲート集積回路を含むゲート集積駆動回路であって、各段の前記ゲート集積回路は、接続されているゲート集積回路ユニットと信号分割回路とを含み、各段の前記信号分割回路は、隣接する2本の走査線と接続するための第1信号出力端子と第2信号出力端子とを含み、

各段の前記信号分割回路は、前段の前記信号分割回路が output する第1サブ行走査信号と第2サブ行走査信号、及び/又は外部制御信号のうちのいくつかの制御信号によりトリガされて現段の前記ゲート集積回路ユニットが output する行走査信号を第1サブ行走査信号と第2サブ行走査信号に分割して第1信号出力端子、第2信号出力端子、及び後段の前記信号分割回路に出力し、

ここで、各段の前記信号分割回路が output する第1サブ行走査信号の立ち上がりエッジと、各段の前記ゲート集積回路ユニットが output する行走査信号の立ち上がりエッジとが同時にトリガされ、各段の前記信号分割回路が output する第2サブ行走査信号の立ち下がりエッジと、各段の前記ゲート集積回路ユニットが output する行走査信号の立ち下がりエッジとが同時にトリガされ、各段の前記信号分割回路が output する第1サブ行走査信号のハイレベルの長さと、第2サブ行走査信号のハイレベルの長さとが部分的に重ねられており、前記外部制御信号は、多重のクロック信号と、フレーム開始信号と、行走査ハイレベル信号と、行走査ローレベル信号と、第1パルスリセット信号と、第2パルスリセット信号とを含み、

前記第1パルスリセット信号は、第j段の前記信号分割回路に入力されるために使用され、前記第2パルスリセット信号は、第j+1段の前記信号分割回路に入力されるために使用され、ここで、j = 1, 3, ..., n-1であり、

第j段の前記信号分割回路の第1サブ行走査信号の立ち下がりエッジと、前記第1パルスリセット信号の立ち上がりエッジとが同時にトリガされ、第j+1段の前記信号分割回路の第1サブ行走査信号の立ち下がりエッジと、前記第2パルスリセット信号の立ち上がりエッジとが同時にトリガされ、

第1段の前記信号分割回路は、前記フレーム開始信号、前記行走査ハイレベル信号、前記行走査ローレベル信号、前記第1パルスリセット信号、及び現段の前記ゲート集積回路ユニットが出力するプルダウン信号によりトリガされ、現段の前記行走査信号を第1サブ行走査信号と第2サブ行走査信号とに分割して出力し、

第2段の前記信号分割回路は、前記フレーム開始信号、前記行走査ハイレベル信号、前記行走査ローレベル信号、前記第2パルスリセット信号、現段の前記ゲート集積回路ユニットが出力するプルダウン信号、及び第1段の前記信号分割回路が出力する第1サブ行走査信号によりトリガされ、現段の前記行走査信号を第1サブ行走査信号と第2サブ行走査信号とに分割して出力し、

第i段の前記信号分割回路は、前記行走査ハイレベル信号、前記行走査ローレベル信号に対応するパルスリセット信号、現段の前記ゲート集積回路ユニットが出力するプルダウン信号、及び第i-2段の前記信号分割回路が出力する第2サブ行走査信号と第i-1段の前記信号分割回路が出力する第1サブ行走査信号によりトリガされ、現段の前記行走査信号を第1サブ行走査信号と第2サブ行走査信号とに分割して出力し、ここで、i > 3で、iは整数である、

ゲート集積駆動回路。

#### 【請求項2】

前記ゲート集積回路ユニットと前記信号分割回路とが集積化されてゲート集積チップを形成する、

請求項1に記載のゲート集積駆動回路。

#### 【請求項3】

前記ゲート集積チップは、前記クロック信号を受信するためのクロック信号端子と、前記行走査ハイレベル信号を受信するための行走査ハイレベル信号端子と、前記行走査ローレベル信号を受信するための行走査ローレベル信号端子と、入力信号を受信するための第1信号入力端子と、対応する前段が出力する前記第2サブ行走査信号を受信するための第2信号入力端子と、対応する前段が出力する前記第1サブ行走査信号を受信するための第3信号入力端子と、下段の前記ゲート集積チップが出力する行走査信号を受信するための第4信号入力端子と、対応するリセットパルス信号を受信するためのリセットパルス信号端子と、現段の行走査信号を出力するための第1信号出力端子と、現段の前記第1サブ行走査信号を出力するための第2信号出力端子と、現段の前記第2サブ行走査信号を出力するための第3信号出力端子とを含む、

請求項2に記載のゲート集積駆動回路。

#### 【請求項4】

各段の前記信号分割回路は、第1スイッチ回路と、第2スイッチ回路と、プルダウン回路とを含み、

前記第1スイッチ回路の信号出力端子と前記プルダウン回路の第1信号端子とが、前記信号分割回路の第1信号出力端子を構成するように共通に接続され、前記第2スイッチ回路の信号出力端子と前記プルダウン回路の第2信号端子とが、前記信号分割回路の第2信号出力端子を構成するように共通に接続され、前記第1スイッチ回路と前記第2スイッチ回路は、さらに、現段の前記ゲート集積回路ユニットの信号出力端子にそれぞれ接続され、前記プルダウン回路の被制御端子は、現段の前記ゲート集積回路ユニットのプルダウン点に接続され、プルダウン信号を入力し、

前記第1スイッチ回路は、対応するパルスリセット信号、前段の前記信号分割回路が出

10

20

30

40

50

力する第2サブ行走査信号、前記行走査ハイレベル信号、前記行走査ローレベル信号、及び前記フレーム開始信号のうちのいくつかの信号のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、現段の第1サブ行走査信号を出力し、

前記第2スイッチ回路は、前段の前記信号分割回路が出力する第1サブ行走査信号、前記行走査ローレベル信号、及び前記フレーム開始信号のうちのいくつかの信号のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、現段の第2サブ行走査信号を出力し、

前記プルダウン回路は、前記行走査ローレベル信号及び前記プルダウン信号のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、前記第1サブ行走査信号と前記第2サブ行走査信号をプルダウンしてリセットする、

請求項1に記載のゲート集積駆動回路。

**【請求項5】**

前記第1スイッチ回路は、前段の前記信号分割回路が出力する前記第2サブ行走査信号を入力するための第1信号入力端子と、前記パルスリセット信号を入力するための第2信号入力端子と、前記行走査ハイレベル信号を入力するための第3信号入力端子と、前記行走査ローレベル信号を入力するための第4信号入力端子と、現段の前記ゲート集積回路ユニットの信号出力端子を接続するための第5信号入力端子と、を含み、

前記第2スイッチ回路は、前段の前記信号分割回路が出力する前記第1サブ行走査信号を入力するための第1信号入力端子と、前記行走査ローレベル信号を入力するための第2信号入力端子と、現段の前記ゲート集積回路ユニットの信号出力端子を接続するための第3信号入力端子と、を含み、

前記プルダウン回路は、前記行走査ローレベル信号を入力するための第1信号入力端子と、現段の前記ゲート集積回路ユニットのプルダウン点を接続するための第2信号入力端子とを含む、

請求項4に記載のゲート集積駆動回路。

**【請求項6】**

前記第1スイッチ回路は、第1電子スイッチトランジスタと、第2電子スイッチトランジスタと、第3電子スイッチトランジスタと、第1容量と、を含み、

前記第1電子スイッチトランジスタの第1端子は、前記フレーム開始信号、前段の前記信号分割回路が出力する第2サブ行走査信号、及び前記行走査ハイレベル信号のうちの1つの信号を入力するために使用され、前記第1電子スイッチトランジスタの被制御端子は、前記フレーム開始信号又は前段の前記信号分割回路が出力する第2サブ行走査信号を入力するために使用され、前記第1電子スイッチトランジスタの第2端子と、前記第2電子スイッチトランジスタの第1端子と、前記第3電子スイッチトランジスタの被制御端子と、前記第1容量の第1端子とが共通に接続され、前記第2電子スイッチトランジスタの第2端子は、前記行走査ローレベル信号を入力するために使用され、前記第2電子スイッチトランジスタの被制御端子は、対応するパルスリセット信号を入力するために使用され、前記第3電子スイッチトランジスタの第1端子は、現段の前記ゲート集積回路ユニットが出力する行走査信号を入力するために使用され、前記第3電子スイッチトランジスタの第2端子と前記第1容量の第2端子とが、前記第1スイッチ回路の信号出力端子を構成するように共通に接続される、

請求項4に記載のゲート集積駆動回路。

**【請求項7】**

前記第2スイッチ回路は、第4電子スイッチトランジスタと、第5電子スイッチトランジスタと、第6電子スイッチトランジスタと、第2容量と、を含み、

前記第4電子スイッチトランジスタの第1端子は、前記行走査ローレベル信号を入力するために使用され、前記第4電子スイッチトランジスタの第2端子と、前記第5電子スイッチトランジスタの第1端子と、前記第6電子スイッチトランジスタの被制御端子と、前記第2容量の第1端子とが共通に接続され、前記第5電子スイッチトランジスタの第2端子と、前記第5電子スイッチトランジスタの被制御端子と、前記第6電子スイッチトラン

10

20

30

40

50

ジスタの第1端子とが、現段の前記ゲート集積回路ユニットが出力する行走査信号を入力するために共通に接続され、前記第4電子スイッチトランジスタの被制御端子は、前記フレーム開始信号又は前段の前記信号分割回路が出力する第1サブ行走査信号を入力するために使用され、前記第6電子スイッチトランジスタの第2端子と前記第2容量の第2端子とが、前記第2スイッチ回路の信号出力端子を構成するように共通に接続される、

請求項6に記載のゲート集積駆動回路。

【請求項8】

前記プルダウン回路は、第7電子スイッチトランジスタと、第8電子スイッチトランジスタと、を含み、

前記第7電子スイッチトランジスタの第1端子は前記プルダウン回路の第1信号端子を構成し、前記第8電子スイッチトランジスタの第1端子は、前記プルダウン回路の第2信号端子を構成し、前記第7電子スイッチトランジスタの被制御端子と前記第8電子スイッチトランジスタの被制御端子とが、前記プルダウン信号を入力するために共通に接続され、前記第7電子スイッチトランジスタの第2端子と前記第8電子スイッチトランジスタの第2端子とが共通に接続される、

請求項7に記載のゲート集積駆動回路。

【請求項9】

前記信号分割回路は、切り替え回路をさらに含み、前記切り替え回路の第1信号入力端子と、前記第1スイッチ回路の信号出力端子と、前記プルダウン回路の第1信号端子とが共通に接続され、前記切り替え回路の第2信号入力端子と、前記第2スイッチ回路の信号出力端子と、前記プルダウン回路の第2信号端子とが共通に接続され、前記切り替え回路の第3信号入力端子は、現段の前記ゲート集積回路ユニットが出力する行走査信号を入力するために使用され、前記切り替え回路の第1信号出力端子と第2信号出力端子は、前記信号分割回路の第1信号出力端子と第2信号出力端子を構成し、前記切り替え回路の被制御端子は、スイッチ選択信号、前記行走査ハイレベル信号、及び前記行走査ローレベル信号を入力するために使用され、

前記切り替え回路は、前記スイッチ選択信号のハイレベルとローレベル、前記行走査ハイレベル信号、及び前記行走査ローレベル信号によりトリガされてオンオフするために使用され、これにより前記第1サブ行走査信号と前記第2サブ行走査信号を、前記信号分割回路の第1信号出力端子と第2信号出力端子に切り替えて出力するか、或いは、現段の前記ゲート集積回路ユニットが出力する行走査信号を、前記信号分割回路の第1信号出力端子と第2信号出力端子にそれぞれ出力する、

請求項4に記載のゲート集積駆動回路。

【請求項10】

前記スイッチ選択信号がハイレベルである場合、前記切り替え回路の第3信号入力端子は2つの出力信号端子と接続され、

前記スイッチ選択信号がローレベルである場合、前記切り替え回路の第1信号入力端子は自身の第1信号出力端子と接続され、前記切り替え回路の第2信号入力端子は自身の第2信号出力端子と接続される、

請求項9に記載のゲート集積駆動回路。

【請求項11】

前記切り替え回路は、第9電子スイッチトランジスタと、第10電子スイッチトランジスタと、第11電子スイッチトランジスタと、第12電子スイッチトランジスタと、第13電子スイッチトランジスタと、第14電子スイッチトランジスタと、第15電子スイッチトランジスタと、第16電子スイッチトランジスタと、を含み、

前記第9電子スイッチトランジスタの第1端子と被制御端子は、前記行走査ハイレベル信号を入力するために使用され、前記第10電子スイッチトランジスタの第1端子は、前記行走査ローレベル信号を入力するために使用され、前記第9電子スイッチトランジスタの第2端子と、前記第10電子スイッチトランジスタの第2端子と、前記第12電子スイッチトランジスタの被制御端子とが共通に接続され、前記第12電子スイッチトランジ

10

20

30

40

50

タの第1端子は、前記切り替え回路の第1信号入力端子を構成し、前記第12電子スイッチトランジスタの第2端子と前記第11電子スイッチトランジスタの第2端子とが、前記切り替え回路の第1信号出力端子を構成するように共通に接続され、前記第11電子スイッチトランジスタの第1端子と前記第15電子スイッチトランジスタの第1端子とが、前記切り替え回路の第3信号入力端子を構成するように共通に接続され、前記第11電子スイッチトランジスタの被制御端子と、前記第10電子スイッチトランジスタの被制御端子と、前記第15電子スイッチトランジスタの被制御端子と、前記第14電子スイッチトランジスタの被制御端子とが、前記スイッチ選択信号を入力するために共通に接続され、前記第13電子スイッチトランジスタの第1端子と被制御端子は、前記行走査ハイレベル信号を入力するために使用され、前記第14電子スイッチトランジスタの第1端子は、前記行走査ローレベル信号を入力するために使用され、前記第13電子スイッチトランジスタの第2端子と、前記第14電子スイッチトランジスタの第2端子と、前記第16電子スイッチトランジスタの被制御端子とが共通に接続され、前記第16電子スイッチトランジスタの第1端子は、前記切り替え回路の第2信号入力端子を構成し、前記第16電子スイッチトランジスタの第2端子と前記第15電子スイッチトランジスタの第2端子とが、前記切り替え回路の第2信号出力端を構成するように共通に接続される、

請求項9に記載のゲート集積駆動回路。

【請求項12】

アレイ基板と、請求項1に記載のゲート集積駆動回路とを含む表示パネルであって、前記ゲート集積駆動回路は前記アレイ基板の片側又は両側に設けられる、

表示パネル。

【請求項13】

前記アレイ基板は、表示領域と、非表示領域とを含み、非表示領域にはピンパインディング領域と前記ゲート集積駆動回路とが設けられ、前記ゲート集積駆動回路は、前記アレイ基板の前記非表示領域の片側又は両側に設けられる、

請求項12に記載の表示パネル。

【請求項14】

バックライトモジュールと、駆動回路板と、請求項12に記載の表示パネルとを含む表示装置であって、前記バックライトモジュールと前記表示パネルとが対向配置され、前記駆動回路板と前記表示パネルとが電気接続されている、

表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

【関連出願の相互参照】

本願は、2021年09月18日に中国特許庁に提出された、出願番号が202111096140.Xで、発明名称が「GOA駆動回路、表示パネル及び表示装置」の中国特許出願の優先権を主張し、その全内容を引用により本願に組み込んでいる。

【0002】

本願は、表示パネルの技術分野に属し、特に、ゲート集積駆動回路、表示パネル及び表示装置に関するものである。

【背景技術】

【0003】

表示技術の急速な発展に伴い、表示パネルは娯楽、教育、セキュリティなどさまざまな分野で広く応用されている。表示パネル内において、GOA(Gate On Array, ゲート集積)技術とは、ゲート駆動回路(Gate driver IC)をアレイ(Array)基板上に直接作製し、行走査信号を出力することにより表示パネルのプログレッシブ走査を実現する技術である。GOA技術は表示パネルの狭額縫化を実現する主要な技術の1つであり、その上でパネルをさらに狭額縫化するために、GOA回路の信号や素子数を減らすのが一般的である。通常、1つのGOA回路ユニットは、1つのClock信

号を受信し、そしてこの C l o c k 信号の 1 周期を画素行の走査信号として出力するため、額縁の大きさが大きくなり、表示パネルの狭額縁化に不利である。

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 4】

本願の目的は、表示パネルの狭額縁化を実現するためのゲート集積駆動回路を提供することである。

【課題を解決するための手段】

【0 0 0 5】

上述した技術的課題を解決するために、本願の実施例が採用する技術方案は次のとおりである。

10

【0 0 0 6】

本願の実施例の第 1 様では、多段接続のゲート集積回路を含むゲート集積駆動回路であって、各段の前記ゲート集積回路は、接続されているゲート集積回路ユニットと信号分割回路とを含み、各段の前記信号分割回路は、隣接する 2 本の走査線を接続するための第 1 信号出力端子と第 2 信号出力端子とを含み、

各段の前記信号分割回路は、前段の前記信号分割回路が出力する第 1 サブ行走査信号と第 2 サブ行走査信号、及び / 又は外部制御信号のうちのいくつかの制御信号によりトリガされて現段の前記ゲート集積回路ユニットが出力する行走査信号を第 1 サブ行走査信号と第 2 サブ行走査信号に分割して第 1 信号出力端子、第 2 信号出力端子、及び後段の前記信号分割回路に出力し、

20

ここで、各段の前記信号分割回路が出力する第 1 サブ行走査信号の立ち上がりエッジと、各段の前記ゲート集積回路ユニットが出力する行走査信号の立ち上がりエッジとが同時にトリガされ、各段の前記信号分割回路が出力する第 2 サブ行走査信号の立ち下がりエッジと、各段の前記ゲート集積回路ユニットが出力する行走査信号の立ち下がりエッジとが同時にトリガされ、各段の前記信号分割回路が出力する第 1 サブ行走査信号のハイレベルの長さと、第 2 サブ行走査信号のハイレベルの長さとが部分的に重ねられている、ゲート集積駆動回路を提供する。

【0 0 0 7】

オプションとして、前記外部制御信号は、多重のクロック信号と、フレーム開始信号と、行走査ハイレベル信号と、行走査ローレベル信号と、第 1 パルスリセット信号と、第 2 パルスリセット信号と、を含み、

30

前記第 1 パルスリセット信号は、第  $j$  段の前記信号分割回路に入力するために使用され、前記第 2 パルスリセット信号は、第  $j + 1$  段の前記信号分割回路に入力するために使用され、ここで、 $j = 1, 3, \dots, n - 1$  であり、

第  $j$  段の前記信号分割回路の第 1 サブ行走査信号の立ち下がりエッジと、前記第 1 パルスリセット信号の立ち上がりエッジとが同時にトリガされ、第  $j + 1$  段の前記信号分割回路の第 1 サブ行走査信号の立ち下がりエッジと、前記第 2 パルスリセット信号の立ち上がりエッジとが同時にトリガされ、

第 1 段の前記信号分割回路は、前記フレーム開始信号、前記行走査ハイレベル信号、前記行走査ローレベル信号、前記第 1 パルスリセット信号、及び現段の前記ゲート集積回路ユニットが出力するプルダウン信号によりトリガされ、現段の前記行走査信号を第 1 サブ行走査信号と第 2 サブ行走査信号とに分割して出力し、

40

第 2 段の前記信号分割回路は、前記フレーム開始信号、前記行走査ハイレベル信号、前記行走査ローレベル信号、前記第 2 パルスリセット信号、現段の前記ゲート集積回路ユニットが出力するプルダウン信号、及び第 1 段の前記信号分割回路が出力する第 1 サブ行走査信号によりトリガされ、現段の前記行走査信号を第 1 サブ行走査信号と第 2 サブ行走査信号とに分割して出力し、

第  $i$  段の前記信号分割回路は、前記行走査ハイレベル信号、前記行走査ローレベル信号、対応するパルスリセット信号、現段の前記ゲート集積回路ユニットが出力するプルダウン

50

信号、及び第  $i - 2$  段の前記信号分割回路が出力する第 2 サブ行走査信号と第  $i - 1$  段の前記信号分割回路が出力する第 1 サブ行走査信号によりトリガされ、現段の前記行走査信号を第 1 サブ行走査信号と第 2 サブ行走査信号とに分割して出力し、ここで、 $i \geq 3$  で、 $i$  は整数である。

【0008】

オプションとして、前記ゲート集積回路ユニットと前記信号分割回路とが集積化されてゲート集積チップを形成する。

【0009】

オプションとして、前記ゲート集積チップは、前記クロック信号を受信するためのクロック信号端子と、前記行走査ハイレベル信号を受信するための行走査ハイレベル信号端子と、前記行走査ローレベル信号を受信するための行走査ローレベル信号端子と、入力信号を受信するための第 1 信号入力端子と、対応する前段が出力する前記第 2 サブ行走査信号を受信するための第 2 信号入力端子と、対応する前段が出力する前記第 1 サブ行走査信号を受信するための第 3 信号入力端子と、下段の前記ゲート集積チップが出力する行走査信号を受信するための第 4 信号入力端子と、対応するリセットパルス信号を受信するためのリセットパルス信号端子と、現段の行走査信号を出力するための第 1 信号出力端子と、現段の前記第 1 サブ行走査信号を出力するための第 2 信号出力端子と、現段の前記第 2 サブ行走査信号を出力するための第 3 信号出力端子とを含む。

10

【0010】

オプションとして、各段の前記信号分割回路は、第 1 スイッチ回路と、第 2 スイッチ回路と、プルダウン回路とを含み、

20

前記第 1 スイッチ回路の信号出力端子と前記プルダウン回路の第 1 信号端子とが、前記信号分割回路の第 1 信号出力端子を構成するように共通に接続され、前記第 2 スイッチ回路の信号出力端子と前記プルダウン回路の第 2 信号端子とが、前記信号分割回路の第 2 信号出力端子を構成するように共通に接続され、前記第 1 スイッチ回路と前記第 2 スイッチ回路は、さらに、現段の前記ゲート集積回路ユニットの信号出力端子にそれぞれ接続され、前記プルダウン回路の被制御端子は、現段の前記ゲート集積回路ユニットのプルダウン点に接続され、プルダウン信号を入力し、

前記第 1 スイッチ回路は、対応するパルスリセット信号、前段の前記信号分割回路が出力する第 2 サブ行走査信号、前記行走査ハイレベル信号、前記行走査ローレベル信号、及び前記フレーム開始信号のうちのいくつかの信号のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、現段の第 1 サブ行走査信号を出力し、前記第 2 スイッチ回路は、前段の前記信号分割回路が出力する第 1 サブ行走査信号、前記行走査ローレベル信号、及び前記フレーム開始信号のうちのいくつかの信号のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、現段の第 2 サブ行走査信号を出力し、

30

前記プルダウン回路は、前記行走査ローレベル信号及び前記プルダウン信号のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、前記第 1 サブ行走査信号と前記第 2 サブ行走査信号をプルダウンしてリセットする。

【0011】

40

オプションとして、前記第 1 スイッチ回路は、前段の前記信号分割回路が出力する前記第 2 サブ行走査信号を入力するための第 1 信号入力端子と、前記パルスリセット信号を入力するための第 2 信号入力端子と、前記行走査ハイレベル信号を入力するための第 3 信号入力端子と、前記行走査ローレベル信号を入力するための第 4 信号入力端子と、現段の前記ゲート集積回路ユニットの信号出力端子を接続するための第 5 信号入力端子と、を含み、前記第 2 スイッチ回路は、前段の前記信号分割回路が出力する前記第 1 サブ行走査信号を入力するための第 1 信号入力端子と、前記行走査ローレベル信号を入力するための第 2 信号入力端子と、現段の前記ゲート集積回路ユニットの信号出力端子を接続するための第 3 信号入力端子と、を含み、

前記プルダウン回路は、前記行走査ローレベル信号を入力するための第 1 信号入力端子と

50

、現段の前記ゲート集積回路ユニットのプルダウン点を接続するための第2信号入力端子とを含む。

【0012】

オプションとして、前記第1スイッチ回路は、第1電子スイッチトランジスタと、第2電子スイッチトランジスタと、第3電子スイッチトランジスタと、第1容量と、を含み、前記第1電子スイッチトランジスタの第1端子は、前記フレーム開始信号、前段の前記信号分割回路が出力する第2サブ行走査信号、及び前記行走査ハイレベル信号のうちの1つの信号を入力するために使用され、前記第1電子スイッチトランジスタの被制御端子は、前記フレーム開始信号又は前段の前記信号分割回路が出力する第2サブ行走査信号を入力するために使用され、前記第1電子スイッチトランジスタの第2端子と、前記第2電子スイッチトランジスタの第1端子と、前記第3電子スイッチトランジスタの被制御端子と、前記第1容量の第1端子とが共通に接続され、前記第2電子スイッチトランジスタの第2端子は、前記行走査ローレベル信号を入力するために使用され、前記第2電子スイッチトランジスタの被制御端子は、対応するパルスリセット信号を入力するために使用され、前記第3電子スイッチトランジスタの第1端子は、現段の前記ゲート集積回路ユニットが出力する行走査信号を入力するために使用され、前記第3電子スイッチトランジスタの第2端子と前記第1容量の第2端子とが、前記第1スイッチ回路の信号出力端子を構成するように共通に接続される。

10

【0013】

オプションとして、前記第2スイッチ回路は、第4電子スイッチトランジスタと、第5電子スイッチトランジスタと、第6電子スイッチトランジスタと、第2容量と、を含み、前記第4電子スイッチトランジスタの第1端子は、前記行走査ローレベル信号を入力するために使用され、前記第4電子スイッチトランジスタの第2端子と、前記第5電子スイッチトランジスタの第1端子と、前記第6電子スイッチトランジスタの被制御端子と、前記第2容量の第1端子とが共通に接続され、前記第5電子スイッチトランジスタの第2端子と、前記第5電子スイッチトランジスタの被制御端子と、前記第6電子スイッチトランジスタの第1端子とが、現段の前記ゲート集積回路ユニットが出力する行走査信号を入力するために共通に接続され、前記第4電子スイッチトランジスタの被制御端子は、前記フレーム開始信号又は前段の前記信号分割回路が出力する第1サブ行走査信号を入力するために使用され、前記第6電子スイッチトランジスタの第2端子と前記第2容量の第2端子とが、第2スイッチ回路の信号出力端子を構成するように共通に接続される。

20

【0014】

オプションとして、前記プルダウン回路は、第7電子スイッチトランジスタと、第8電子スイッチトランジスタと、を含み、前記第7電子スイッチトランジスタの第1端子は前記プルダウン回路の第1信号端を構成し、前記第8電子スイッチトランジスタの第1端子は、前記プルダウン回路の第2信号端子を構成し、前記第7電子スイッチトランジスタの被制御端子と前記第8電子スイッチトランジスタの被制御端子とが、プルダウン信号を入力するために共通に接続され、前記第7電子スイッチトランジスタの第2端子と前記第8電子スイッチトランジスタの第2端子とが共通に接続される。

30

【0015】

オプションとして、前記信号分割回路は、切り替え回路をさらに含み、前記切り替え回路の第1信号入力端子と、前記第1スイッチ回路の信号出力端子と、前記プルダウン回路の第1信号端子とが共通に接続され、前記切り替え回路の第2信号入力端子と、前記第2スイッチ回路の信号出力端子と、前記プルダウン回路の第2信号端子とが共通に接続され、前記切り替え回路の第3信号入力端子は、現段の前記ゲート集積回路ユニットが出力する行走査信号を入力するために使用され、前記切り替え回路の第1信号出力端子と第2信号出力端子は、前記信号分割回路の第1信号出力端子と第2信号出力端子を構成し、前記切り替え回路の被制御端子は、スイッチ選択信号、前記行走査ハイレベル信号、及び前記行走査ローレベル信号を入力するために使用され、

40

50

前記切り替え回路は、前記スイッチ選択信号のハイレベルとローレベル、前記行走査ハイレベル信号、及び前記行走査ローレベル信号によりトリガされてオンオフするために使用され、これにより前記第1サブ行走査信号と第2サブ行走査信号を、前記信号分割回路の第1信号出力端子と第2信号出力端子に切り替えて出力するか、或いは、現段の前記ゲート集積回路ユニットが出力する行走査信号を、前記信号分割回路の第1信号出力端子と第2信号出力端子にそれぞれ出力する。

【0016】

オプションとして、スイッチ選択信号がハイレベルである場合、前記切り替え回路の第3信号入力端子は2つの出力信号端子と接続され、

スイッチ選択信号がローレベルである場合、前記切り替え回路の第1信号入力端子は自身の第1信号出力端子と接続され、前記切り替え回路の第2信号入力端子は自身の第2信号出力端子と接続される。

【0017】

オプションとして、前記切り替え回路は、第9電子スイッチトランジスタと、第10電子スイッチトランジスタと、第11電子スイッチトランジスタと、第12電子スイッチトランジスタと、第13電子スイッチトランジスタと、第14電子スイッチトランジスタと、第15電子スイッチトランジスタと、第16電子スイッチトランジスタと、を含み、前記第9電子スイッチトランジスタの第1端子と被制御端子は、前記行走査ハイレベル信号を入力するために使用され、前記第10電子スイッチトランジスタの第1端子は、前記行走査ローレベル信号を入力するために使用され、前記第9電子スイッチトランジスタの第2端子と、前記第10電子スイッチトランジスタの第2端子と、前記第12電子スイッチトランジスタの被制御端子とが共通に接続され、前記第12電子スイッチトランジスタの第1端子は、前記切り替え回路の第1信号入力端子を構成し、前記第12電子スイッチトランジスタの第2端子と前記第11電子スイッチトランジスタの第2端子とが、前記切り替え回路の第1信号出力端子を構成するように共通に接続され、前記第11電子スイッチトランジスタの第1端子と前記第15電子スイッチトランジスタの第1端子とが、前記切り替え回路の第3信号入力端子を構成するように共通に接続され、前記第11電子スイッチトランジスタの被制御端子と、前記第10電子スイッチトランジスタの被制御端子と、前記第15電子スイッチトランジスタの被制御端子と、前記第14電子スイッチトランジスタの被制御端子とが、前記スイッチ選択信号を入力するために共通に接続され、前記第13電子スイッチトランジスタの第1端子と被制御端子は、前記行走査ハイレベル信号を入力するために使用され、前記第14電子スイッチトランジスタの第1端子は、前記行走査ローレベル信号を入力するために使用され、前記第13電子スイッチトランジスタの第2端子と、前記第14電子スイッチトランジスタの第2端子と、前記第16電子スイッチトランジスタの被制御端子は、前記切り替え回路の第2信号入力端子を構成し、前記第16電子スイッチトランジスタの第2端子と前記第15電子スイッチトランジスタの第2端子とが、前記切り替え回路の第2信号出力端子を構成するように共通に接続される。

【0018】

本願の実施例の第2態様では、アレイ基板と、上記のゲート集積駆動回路とを含む表示パネルであって、前記ゲート集積駆動回路は前記アレイ基板の片側又は両側に設けられる、表示パネルを提供する。

【0019】

オプションとして、前記アレイ基板は、表示領域と、非表示領域とを含み、非表示領域にはピンバインディング領域と前記ゲート集積駆動回路とが設けられ、前記ゲート集積駆動回路は、アレイ基板の前記非表示領域の片側又は両側に設けられる。

【0020】

本願の実施例の第3態様では、バックライトモジュールと、駆動回路板と、上記の表示パネルとを含む表示装置であって、前記バックライトモジュールと前記表示パネルとが対向配置され、前記駆動回路板と前記表示パネルとが電気接続されている、表示装置を提供す

10

20

30

40

50

る。

【発明の効果】

【0021】

上述したゲート集積駆動回路における多段接続された各ゲート集積回路は、それぞれ、ゲート集積回路ユニットと信号分割回路とを含み、信号分割回路は、表示パネル内の隣接する2本の走査線に接続され、ゲート集積回路ユニットは、原始のゲート集積回路ユニットに従って動作し、出力された行走査信号は、次段のゲート集積回路ユニットへの入力信号とされ、及び、上段のゲート集積回路ユニットのリセット信号とされ、一方、信号分割回路は、現段から出力される行走査信号を第1サブ行走査信号と第2サブ行走査信号とに分割して出力し、2行の画素セルに対する走査駆動を実現し、ゲート集積回路ユニットの素子数を削減し、表示パネルの額縁を節約し、表示パネルの狭額縁化を実現する。

10

【0022】

上記の第2態様及び第3態様の有益な効果は、上記の第1態様に対する説明を参照すればよく、ここでは説明を省略することが理解されたい。

【0023】

本願の実施例に係る技術的解決手段をより明らかにするために、以下は、実施例の説明に使用する必要がある図面を簡単に説明するが、明らかなことに、以下の説明における図面は、本願のいくつかの実施例に過ぎず、当業者であれば、創造的な工夫をせずに、これらの図面により他の図面を取得することができる。

20

【図面の簡単な説明】

【0024】

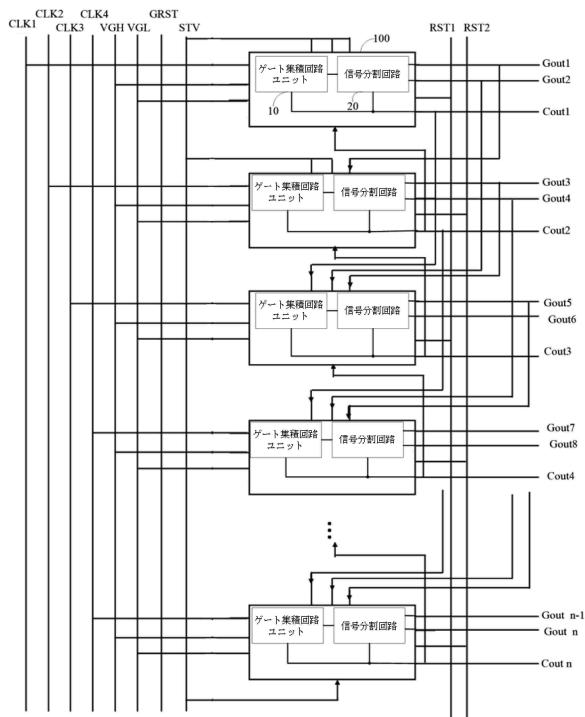

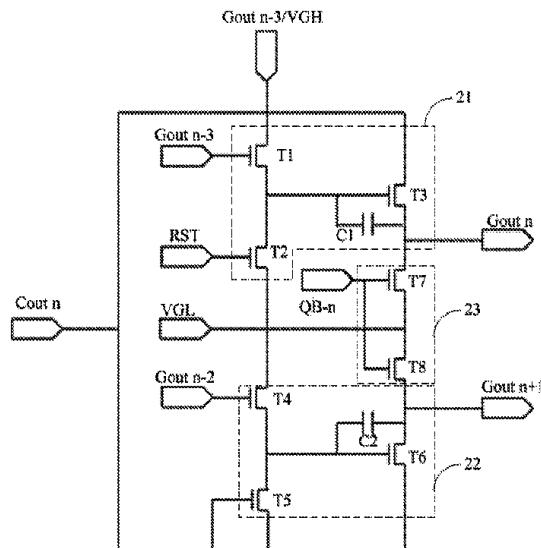

【図1】本願の実施例により提供されるゲート集積駆動回路の第1種類の構成図である。

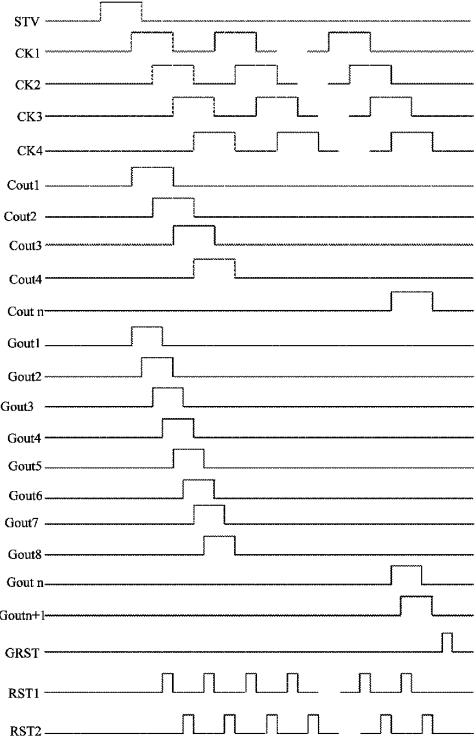

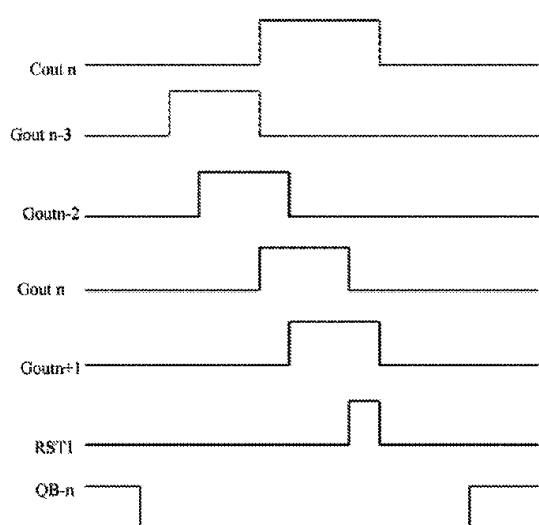

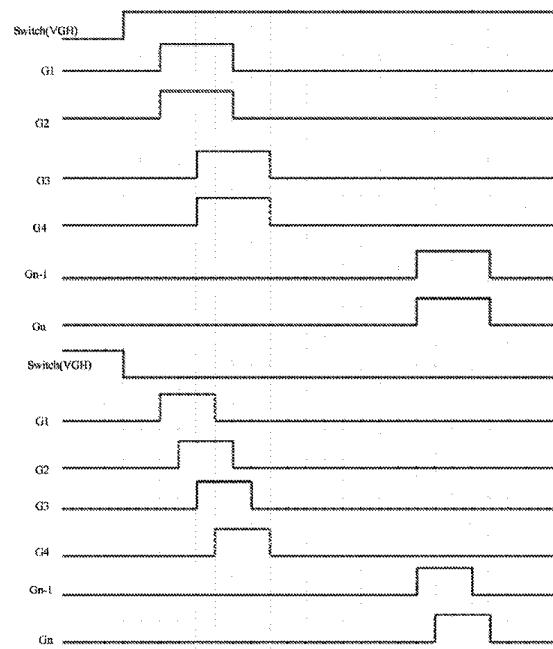

【図2】本願の実施例により提供されるゲート集積駆動回路の波形図である。

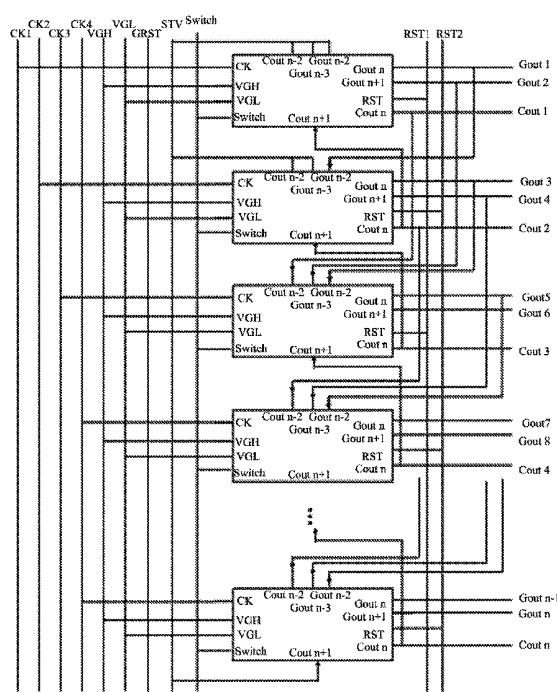

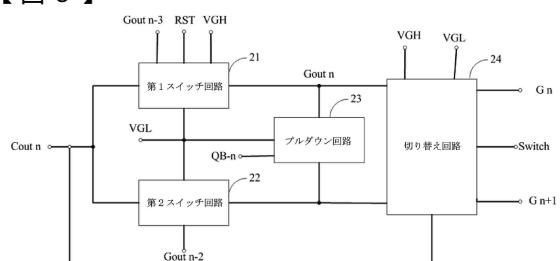

【図3】本願の実施例により提供されるゲート集積駆動回路の第2種類の構成図である。

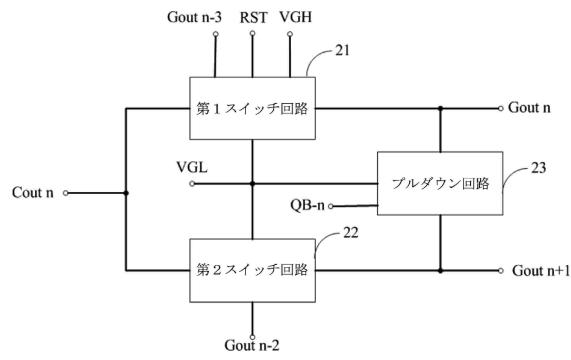

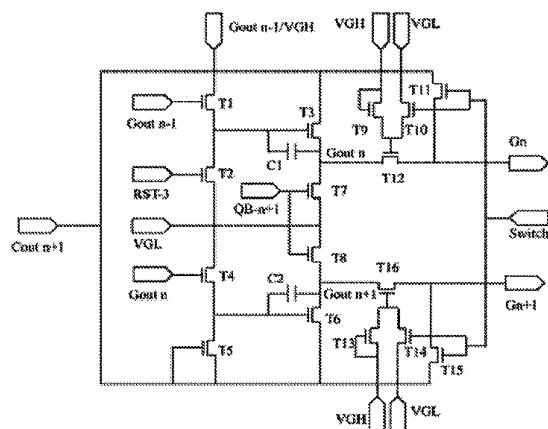

【図4】図1に示したゲート集積駆動回路におけるゲート集積回路の構成図である。

【図5】図4に示したゲート集積回路における信号分割回路の第1種類の構成図である。

【図6】図4に示したゲート集積回路における信号分割回路の第1種類の回路図である。

【図7】図6に示したゲート集積回路における信号分割回路の第1種類の波形図である。

【図8】図4に示したゲート集積回路における信号分割回路の第2種類の構成図である。

【図9】図8に示したゲート集積回路における信号分割回路の第2種類の回路図である。

30

【図10】図9に示すゲート集積回路における信号分割回路の第2種類の波形図である。

【発明を実施するための形態】

【0025】

本願が解決しようとする技術的問題、技術的解決手段及び有益な効果をより分かりやすくするために、以下に添付図面及び実施例を参照しながら、本願について詳しく説明する。ここで説明される具体的な実施例は本願を解釈するためのものに過ぎず、本願を限定するためのものではないことを理解されたい。

【0026】

また、「第1」、「第2」という用語は説明の目的だけに用いられ、比較的重要性を指示又は暗示するか、あるいは示された技術的特徴の数を默示的に指示するためのものと理解してはいけない。したがって、「第1」、「第2」などで限定された特徴は、1つまたは複数の該特徴を明示的または暗黙的に含むことができる。本願の説明において、別途明確かつ具体的な限定がない限り、「複数」とは、二つ以上を意味する。

40

実施例1

【0027】

本願の実施例の第1態様はゲート集積駆動回路を提供し、図1に示すように、ゲート集積駆動回路は多段接続のゲート集積回路100を含み、各段のゲート集積回路100は、接続されているゲート集積回路ユニット10と信号分割回路20とを含み、各段の信号分割回路20は、隣接する2本の走査線を接続するための第1信号出力端子と第2信号出力端子とを含む。

50

各段の信号分割回路 20 は、前段の信号分割回路 20 が output する第 1 サブ行走査信号と第 2 サブ行走査信号、及び / 又は外部制御信号のうちのいくつかの制御信号によりトリガされて現段のゲート集積回路ユニット 10 が output する行走査信号を第 1 サブ行走査信号と第 2 サブ行走査信号に分割して第 1 信号出力端子、第 2 信号出力端子、及び後段の信号分割回路 20 に出力する。

ここで、各段の信号分割回路 20 が output する第 1 サブ行走査信号の立ち上がりエッジと、各段のゲート集積回路ユニット 10 が output する行走査信号の立ち上がりエッジとが同時にトリガされ、各段の信号分割回路 20 が output する第 2 サブ行走査信号の立ち下がりエッジと、各段のゲート集積回路ユニット 10 が output する行走査信号の立ち下がりエッジとが同時にトリガされ、各段の信号分割回路 20 が output する第 1 サブ行走査信号のハイレベルの長さと、第 2 サブ行走査信号のハイレベルの長さとが部分的に重ねられている。

#### 【 0 0 2 8 】

本実施例では、ゲート集積回路 100 は、アレイ基板上のバイニング領域を介して駆動回路板から入力された外部制御信号を受信して行走査信号に変換し、外部制御信号は、多重のクロック信号、フレーム開始信号 STV、行走査ハイレベル信号 VGH、行走査ローレベル信号 VGL、リセット信号 GRSST 等を含む。ゲート集積回路ユニット 10 は、例えば、4T1C のゲート集積回路ユニット 10 又は 8T1C のゲート集積回路ユニット 10 などの原始のゲート集積回路ユニット 10 構造を用いて、そして同様に動作する。ゲート集積駆動回路は、单一又は両側駆動を用いることができ、駆動方式は限定されない。一方、ゲート集積回路ユニット 10 に入力されるクロック信号の数は、4 ウェイ又は 8 ウェイなどをふくんでもよく、具体的な数はゲート集積回路 100 及び内部のゲート集積回路ユニット 10 の構造及び動作要件に応じて決定され、ここでは限定されない。

#### 【 0 0 2 9 】

ゲート集積回路ユニット 10 は、入力されたそのうち 1 パスのクロック信号、フレーム開始信号 STV 等の制御信号に応じて行走査信号を 1 行ずつ output する。一方、本段から出力された行走査信号は、上段のゲート集積回路ユニット 10 のリセット信号とされ、及び対応する下段の入力信号とされ、行同士のゲート集積回路ユニット 10 が相互に影響し、シフトパルス信号を生成する。

#### 【 0 0 3 0 】

一方、本段が出力する行走査信号は、本段の信号分割回路 20 に入力されて信号分割され、そして、2 パスのサブ行走査信号を変換して出力する。2 パスのサブ行走査信号は、最終の行走査信号として出力され、そして、対応する 2 行の画素セルを 1 行ずつ駆動する。一方、2 パスのサブ行走査信号は、それぞれ、次段の信号分割回路 20 及び次々段の信号分割回路 20 の制御信号とされ、各段の信号分割回路 20 が対応して変換分割してシフトパルス信号を生成し、これによりアレイ基板の対応する行の画素セルを駆動する。図 2 に示すように、各ゲート集積回路ユニット 10 は、原始の動作モードで第 1 シフトパルス信号 Cout1 ~ Coutn を出力する。一方、各段の信号分割回路 20 は、受信した前段の信号分割回路 20 から出力された第 1 サブ行走査信号と第 2 サブ行走査信号、及び / 又は外部制御信号のうちのいくつかの制御信号に応じて、第 2 シフトパルス信号 Gout1 ~ Goutn+1 を出力し、原始の单一ゲート集積回路ユニット 10 に基づいて 1 行の画素セルを駆動し、信号分割回路 20 を設置することにより、1 パスのゲート集積回路 100 は 2 行の画素セルを駆動することができ、アレイ基板の行数を変えずに、ゲート集積回路ユニット 10 の素子数を原始の回路に比べて半分にすることができ、表示パネルの額縁を節約し、表示パネルの狭額縁化を実現することができる。

#### 【 0 0 3 1 】

なお、信号分割回路 20 は、各制御信号に応じてシフトされた第 1 サブ行走査信号及び第 2 サブ行走査信号を出力する。各段の信号分割回路 20 が output する第 1 サブ行走査信号の立ち上がりエッジと、各段のゲート集積回路ユニット 10 が output する行走査信号の立ち上がりエッジとが同時にトリガされ、各段の信号分割回路 20 が output する第 2 サブ行走査信号の立ち下がりエッジと、各段のゲート集積回路ユニット 10 が output する行走査信号の立

10

20

30

40

50

ち下がりエッジとが同時にトリガされる。このような設定により、第1サブ行走査信号と第2サブ行走査信号とが原始の行走査信号に同期してシフトして出力することができ、これで各行の画素セルの正常な駆動を保証し、駆動信頼性を向上させることができる。

【0032】

なお、各段の信号分割回路20は、それぞれ異なる駆動制御信号を対応して用いて、第1サブ行走査信号と第2サブ行走査信号とを分割して出力することができ、各段の信号分割回路20が受信した駆動制御信号については特に制限はない。

【0033】

一方、信号分割回路20は、スイッチ構成の異なる分割回路、例えば、シフト回路、タイミング回路等の構成を用いてもよく、その構成は限定されない。

10

【0034】

上述したゲート集積駆動回路を基礎として具体化すると、図1及び図3に示すように、一実施例では、外部制御信号は、多重のクロック信号と、フレーム開始信号STVと、行走査ハイレベル信号VGHと、行走査ローレベル信号VGLと、第1パルスリセット信号RST1と、第2パルスリセット信号RST2と、を含む。

第1パルスリセット信号RST1は、第j段の信号分割回路20に入力されるために使用され、第2パルスリセット信号RST2は、第j+1段の信号分割回路に入力されるために使用され、ここで、 $j = 1, 3, \dots, n - 1$ である。

第j段の信号分割回路20の第1サブ行走査信号の立ち下がりエッジと、第1パルスリセット信号RST1の立ち上がりエッジとが同時にトリガされ、第j+1段の信号分割回路20の第1サブ行走査信号の立ち下がりエッジと、第2パルスリセット信号RST2の立ち上がりエッジとが同時にトリガされる。

20

【0035】

本実施例では、外部クロック信号、行走査ハイレベル信号VGH、行走査ローレベル信号VGL、フレーム開始信号STV、第1パルスリセット信号RST1、及び第2パルスリセット信号RST2は、駆動回路板によりアレイ基板のバインディング領域を介して入力される。図2に示すように、第1パルスリセット信号RST1及び第2パルスリセット信号RST2は、パルス波形であり、そして、奇数段及び偶数段の信号分割回路20の第1サブ行走査信号の立ち下がりエッジ制御を実現するためにそれぞれ用いられる。

30

【0036】

一方、各段の信号分割回路20の駆動方式は、各段のゲート集積回路ユニット10と同様であり、すなわち、第1段のゲート集積回路100の信号分割回路20が、フレーム開始信号STV、行走査ハイレベル信号VGH、行走査ローレベル信号VGL、第1パルスリセット信号RST1、及び現段のゲート集積回路ユニット10から出力されるプルダウン信号QB-nを受信してトリガされ、第1段の第1サブ行走査信号及び第2サブ行走査信号を生成する。第1段の第1サブ行走査信号及び第2サブ行走査信号は、アレイ基板の第1行の画素セル及び第2行の画素セルに入力され、一方、第1段の第1サブ行走査信号は第2段の信号分割回路20に入力され、第1段の第2サブ行走査信号は、第2段の信号分割回路20及び第3段の信号分割回路20の駆動制御信号として、第3段の信号分割回路20に入力される。

40

【0037】

第2段の信号分割回路20は、フレーム開始信号STV、行走査ハイレベル信号VGH、行走査ローレベル信号VGL、第2パルスリセット信号RST2、現段のゲート集積回路ユニット10が出力するプルダウン信号QB-n、及び第1段の信号分割回路20が出力する第1サブ行走査信号によりトリガされ、現段の行走査信号を第1サブ行走査信号と第2サブ行走査信号とに分割して出力する。第2段の第1サブ行走査信号は第3段の信号分割回路20に入力され、第2段の第2サブ行走査信号は、第3段の信号分割回路20及び第4段の信号分割回路20の駆動制御信号として第4段の信号分割回路20に入力される。

【0038】

このようにして、第i段の信号分割回路20は、行走査ハイレベル信号VGH、行走査ロ

50

－レベル信号 V G L、対応するパルスリセット信号、現段のゲート集積回路ユニット 10 が出力するプルダウン信号 Q B - n、及び第 i - 2 段の信号分割回路 20 が出力する第 2 サブ行走査信号と第 i - 1 段の信号分割回路 20 が出力する第 1 サブ行走査信号によりトリガされ、現段の行走査信号を第 1 サブ行走査信号と第 2 サブ行走査信号とに分割して出力し、ここで、i 3 で、i は整数である。そして、最終段の信号分割回路 20 が第 1 サブ行走査信号と第 2 サブ行走査信号とを対応して出力するまで、最終的にシフトパルス信号 G out 1 ~ G out n + 1 を生成して各行に対応する画素セルを駆動する。

#### 【 0 0 3 9 】

図 3 に示すように、出力信号の安定性をさらに向上させるために、一実施例では、ゲート集積回路ユニット 10 は、信号分割回路 20 と集積化されてゲート集積チップを形成する。ゲート集積チップは、クロック信号を受信するためのクロック信号端子 C K と、行走査ハイレベル信号 V G H を受信するための行走査ハイレベル信号端子と、行走査ローレベル信号 V G L を受信するための行走査ローレベル信号端子と、入力信号を受信するための第 1 信号入力端子 C out n - 2 と、対応する前段が出力する第 2 サブ行走査信号を受信するための第 2 信号入力端子 G out n - 3 と、対応する前段が出力する第 1 サブ行走査信号を受信するための第 3 信号入力端子 G out n - 2 と、下段のゲート集積チップが出力する行走査信号を受信するための第 4 信号入力端子 C out n + 1 と、対応するリセットパルス信号を受信するためのリセットパルス信号端子 R S T と、現段の行走査信号を出力するための第 1 信号出力端子 C out n と、現段の第 1 サブ行走査信号を出力するための第 2 信号出力端子 G out n と、現段の第 2 サブ行走査信号を出力するための第 3 信号出力端子 G out n + 1 とを含む。

10

20

30

#### 【 0 0 4 0 】

このうち、第 1 段のゲート集積チップについては、第 1 信号入力端子 C out n - 2、第 2 信号入力端子 G out n - 3、及び第 3 信号入力端子 G out n - 2 には、それぞれフレーム開始信号 S T V が入力される。フレーム開始信号 S T V は、第 1 段のゲート集積チップ内のゲート集積回路ユニット 10 への入力信号として、ゲート集積回路ユニット 10 を介して第 1 段の行走査信号に変換して出力される。一方、フレーム開始信号 S T V、行走査ハイレベル信号 V G H、行走査ローレベル信号 V G L、第 1 パルスリセット信号 R S T 1 は、第 1 段のゲート集積チップ内の信号分割回路 20 の駆動制御信号として、信号分割回路 20 に対してスイッチング制御を行い、そして現段の第 1 サブ行走査信号 G out 1 と第 2 サブ行走査信号 G out 2 とに分割して出力される。

30

#### 【 0 0 4 1 】

第 2 段のゲート集積チップについては、第 1 信号入力端子 C out n - 2 と第 2 信号入力端子 G out n - 3 にはそれぞれフレーム開始信号 S T V が入力され、第 3 信号入力端子 G out n - 2 には、第 1 段のゲート集積チップが出力する第 1 サブ行走査信号が入力される。フレーム開始信号 S T V は、第 2 段のゲート集積チップ内のゲート集積回路ユニット 10 への入力信号として、ゲート集積回路ユニット 10 を介して第 2 段の行走査信号に変換して出力される。一方、フレーム開始信号 S T V、行走査ハイレベル信号 V G H、行走査ローレベル信号 V G L、第 2 パルスリセット信号 R S T 2、及び第 1 段のゲート集積チップが出力する第 1 サブ行走査信号は、第 2 段のゲート集積チップ内の信号分割回路 20 の駆動制御信号として、信号分割回路 20 に対してスイッチング制御を行い、そして現段の第 1 サブ行走査信号 G out 3 と第 2 サブ行走査信号 G out 4 とに分割して出力される。

40

#### 【 0 0 4 2 】

第 3 段及び最終段のゲート集積チップについては、第 1 信号入力端子 C out n - 2 には、第 i - 2 段のゲート集積チップが出力する行走査信号が入力され、第 2 信号入力端子 G out n - 3 には、第 i - 2 段のゲート集積チップが出力する第 2 サブ行走査信号が入力され、第 3 信号入力端子 G out n - 2 には、第 i - 1 段のゲート集積チップが出力する第 1 サブ行走査信号が入力され、第 i - 2 段のゲート集積チップが出力する行走査信号は、現段のゲート集積チップ内のゲート集積回路ユニット 10 への入力信号として、

50

ゲート集積回路ユニット 10 を介して現段の行走査信号に変換して出力される。一方、フレーム開始信号 S T V、行走査ハイレベル信号 V G H、行走査ローレベル信号 V G L、対応するパルスリセット信号、第 i - 2 段のゲート集積チップが出力する第 2 サブ行走査信号、及び第 i - 1 段のゲート集積チップが出力する第 1 サブ行走査信号は、現段のゲート集積チップ内の信号分割回路 20 の駆動制御信号として、信号分割回路 20 に対してスイッチング制御を行い、そして現段の第 1 サブ行走査信号 G out n と第 2 サブ行走査信号 G out n + 1 とに分割して出力される。

#### 【 0 0 4 3 】

上述したゲート集積駆動回路を基礎として最適化及び具体化すると、図 4 と図 5 に示すように、一実施例では、各段の信号分割回路 20 は、第 1 スイッチ回路 21 と、第 2 スイッチ回路 22 と、プルダウン回路 23 とを含む。

10

第 1 スイッチ回路 21 の信号出力端子とプルダウン回路 23 の第 1 信号端子とが、信号分割回路 20 の第 1 信号出力端子を構成するように共通に接続され、第 2 スイッチ回路 22 の信号出力端子とプルダウン回路 23 の第 2 信号端子とが、信号分割回路 20 の第 2 信号出力端子を構成するように共通に接続され、第 1 スイッチ回路 21 と第 2 スイッチ回路 22 は、さらに、現段のゲート集積回路ユニット 10 の信号出力端子にそれぞれ接続され、プルダウン回路 23 の被制御端子は、現段のゲート集積回路ユニット 10 のプルダウン点に接続され、プルダウン信号 Q B - n を入力する。

第 1 スイッチ回路 21 は、対応するパルスリセット信号、前段の信号分割回路 20 が出力する第 2 サブ行走査信号、行走査ハイレベル信号 V G H、行走査ローレベル信号 V G L、及びフレーム開始信号 S T V のうちのいくつかの信号のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、現段の第 1 サブ行走査信号を出力する。

20

第 2 スイッチ回路 22 は、前段の信号分割回路 20 が出力する第 1 サブ行走査信号、行走査ローレベル信号 V G L、及びフレーム開始信号 S T V のうちのいくつかの信号のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、現段の第 2 サブ行走査信号を出力する。

プルダウン回路 23 は、行走査ローレベル信号 V G L 及びプルダウン信号 Q B - n のレベルの組み合わせに応じて、対応するタイミングで対応的にオンオフすることにより、第 1 サブ行走査信号と第 2 サブ行走査信号をプルダウンしてリセットする。

30

#### 【 0 0 4 4 】

本実施例では、第 1 スイッチ回路 21 は、前段の信号分割回路 20 が出力する第 2 サブ行走査信号を入力するための第 1 信号入力端子と、第 2 サブ行走査信号を入力するための第 2 サブ行走査信号と、パルスリセット信号を入力するための第 2 信号入力端子と、行走査ハイレベル信号 V G H を入力するための第 3 信号入力端子と、行走査ローレベル信号 V G L を入力するための第 4 信号入力端子と、現段のゲート集積回路ユニット 10 の信号出力端子を接続するための第 5 信号入力端子と、を含む。第 2 スイッチ回路 22 は、前段の信号分割回路 20 が出力する第 1 サブ行走査信号を入力するための第 1 信号入力端子と、行走査ローレベル信号 V G L を入力するための第 2 信号入力端子と、現段のゲート集積回路ユニット 10 の信号出力端子を接続するための第 3 信号入力端子と、を含む。プルダウン回路 23 は、行走査ローレベル信号 V G L を入力するための第 1 信号入力端子と、現段のゲート集積回路ユニット 10 のプルダウン点を接続するための第 2 信号入力端子とを含む。ここで、現段のゲート集積回路ユニット 10 のプルダウン点は、ゲート集積回路ユニット 10 の P D 点電圧である。

40

#### 【 0 0 4 5 】

具体的には、図 7 に示すように、第 1 スイッチ回路 21 の第 1 信号入力端子がハイレベルである場合、第 1 スイッチ回路 21 がオンし、第 1 スイッチ回路 21 は、現段のゲート集積回路ユニット 10 が出力する行走査信号のローレベルを出力する。第 1 スイッチ回路 21 の第 1 信号入力端子がオフである場合、第 1 スイッチ回路 21 は、内部の容量結合によりオンし続け、第 1 スイッチ回路 21 は、現段のゲート集積回路ユニット 10 が出力する

50

行走査信号のハイレベルを出力する。第2信号入力端子、すなわち、パルスリセット信号がハイレベルである場合、第1スイッチ回路21がオフし、内部の容量結合によりローレベルになるため、第1スイッチ回路21がローレベルを出力し、第1スイッチ回路21は第1サブ行走査信号を表す第1パルス信号を出力する。一方、プルダウン信号Q B - nがハイレベルである場合、プルダウン回路23がオンしてローレベルを出力し、第1サブ行走査信号がローレベルにプルダウンされてリセットする。

【0046】

一方、第2スイッチ回路22の第1信号入力端子がハイレベルである場合、第2スイッチ回路22がオフし、第2スイッチ回路22はローレベルを出力する。第2スイッチ回路22の第1信号入力端子がローレベルである場合、第2スイッチ回路22がオンし、第2スイッチ回路22は、現段のゲート集積回路ユニット10が outputする行走査信号のハイレベルを出力する。第2スイッチ回路22の第3信号入力端子がローレベルである場合、第2スイッチ回路22は内部の容量結合によりローレベルになり、これにより第2サブ行走査信号を表す第2パルス信号を出力する。一方、プルダウン信号Q B - nがハイレベルである場合、プルダウン回路23がオンしてローレベルを出力し、第2サブ行走査信号がローレベルにプルダウンされてリセットする。

10

【0047】

第1スイッチ回路21、第2スイッチ回路22、プルダウン回路23を設置することにより、行走査信号の分割変換が実現され、2バスのシフトされたサブ行走査信号を出力することができ、回路の構成が単純化になる。

20

【0048】

なお、第1スイッチ回路21、第2スイッチ回路22、及びプルダウン回路23は、対応するスイッチ構成を用いてタイミングスイッチ制御を行うことができる。

【0049】

上述した信号分割回路20を基礎として最適化及び具体化すると、図4と図6に示すように、一実施例では、第1スイッチ回路21は、第1電子スイッチトランジスタT1と、第2電子スイッチトランジスタT2と、第3電子スイッチトランジスタT3と、第1容量C1と、を含む。

第1電子スイッチトランジスタT1の第1端子は、フレーム開始信号T1、前段の信号分割回路20が出力する第2サブ行走査信号、及び行走査ハイレベル信号VGHのうちの1つの信号を入力するために使用され、第1電子スイッチトランジスタT1の被制御端子は、フレーム開始信号STV又は前段の信号分割回路20が出力する第2サブ行走査信号を入力するために使用され、第1電子スイッチトランジスタT1の第2端子と、第2電子スイッチトランジスタT2の第1端子と、第3電子スイッチトランジスタT3の被制御端子と、第1容量C1の第1端子とが共通に接続され、第2電子スイッチトランジスタT2の第2端子は、行走査ローレベル信号VGLを入力するために使用され、第2電子スイッチトランジスタT2の被制御端子は、対応するパルスリセット信号を入力するために使用され、第3電子スイッチトランジスタT3の第1端子は、現段のゲート集積回路ユニット10が出力する行走査信号を入力するために使用され、第3電子スイッチトランジスタT3の第2端子と第1容量C1の第2端子とが、第1スイッチ回路21の信号出力端子を構成するように共通に接続される。

30

【0050】

第2スイッチ回路22は、第4電子スイッチトランジスタT4と、第5電子スイッチトランジスタT5と、第6電子スイッチトランジスタT6と、第2容量C2と、を含む。

第4電子スイッチトランジスタT4の第1端子は、行走査ローレベル信号VGLを入力するために使用され、第4電子スイッチトランジスタT4の第2端子と、第5電子スイッチトランジスタT5の第1端子と、第6電子スイッチトランジスタT6の被制御端子と、第2容量C2の第1端子とが共通に接続され、第5電子スイッチトランジスタT5の第2端子と、第5電子スイッチトランジスタT5の被制御端子と、第6電子スイッチトランジスタT6の第1端子とが、現段のゲート集積回路ユニット10が出力する行走査信号を入力

40

50

するために共通に接続され、第4電子スイッチトランジスタT4の被制御端子は、フレーム開始信号STV又は前段の信号分割回路20が出力する第1サブ行走査信号を入力するために使用され、第6電子スイッチトランジスタT6の第2端子と第2容量C2の第2端子とが、第2スイッチ回路22の信号出力端子を構成するように共通に接続される。

【0051】

プルダウン回路23は、第7電子スイッチトランジスタT7と、第8電子スイッチトランジスタT8と、を含む。

第7電子スイッチトランジスタT7の第1端子はプルダウン回路23の第1信号端を構成し、第8電子スイッチトランジスタT8の第1端子は、プルダウン回路23の第2信号端子を構成し、第7電子スイッチトランジスタT7の被制御端子と第8電子スイッチトランジスタT8の被制御端子とが、プルダウン信号QB-nを入力するために共通に接続され、第7電子スイッチトランジスタT7の第2端子と第8電子スイッチトランジスタT8の第2端子とが共通に接続される。

【0052】

本実施例では、図7に示すように、第1電子スイッチトランジスタT1の被制御端子及び第1端子がハイレベルである場合、第1電子スイッチトランジスタT1がオンし、第3電子スイッチトランジスタT3にハイレベルを入力し、第3電子スイッチトランジスタT3がオンし、第3電子スイッチトランジスタT3の第2端子は、現段のゲート集積回路ユニット10が出力する行走査信号のローレベルを出力する。第1電子スイッチトランジスタT1の被制御端子がローレベルである場合、第3電子スイッチトランジスタT3がオフする。第3電子スイッチトランジスタT3の第1端子がハイレベルである場合、第3電子スイッチトランジスタT3は、第1容量C1の容量結合によりオンし続け、そして現段のゲート集積回路ユニット10が出力する行走査信号のハイレベルを出力する。パルスリセット信号がハイレベルである場合、第2電子スイッチトランジスタT2がオンし、行走査ローレベル信号VGLは、第3電子スイッチトランジスタT3に入力され、第3電子スイッチトランジスタT3がオフし、第3電子スイッチトランジスタT3の第2端子が第1容量C1の容量結合によりローレベルになる。プルダウン信号QB-nがハイレベルである場合、第7電子スイッチトランジスタT7がオンし、第7電子スイッチトランジスタT7がローレベルを出力し、これにより第3電子スイッチトランジスタT3の第2端子が出力する第1サブ行走査信号がプルダウンされてリセットする。

【0053】

第4電子スイッチトランジスタT4の被制御端子がハイレベルである場合、第4電子スイッチトランジスタT4がオンし、第6電子スイッチトランジスタT6にローレベルを入力する。行走査信号がローレベルである場合、第5電子スイッチトランジスタT5がオフし、第6電子スイッチトランジスタT6がオフし、第6電子スイッチトランジスタT6はローレベルを出力する。行走査信号がハイレベルである場合、行走査信号と第4電子スイッチトランジスタT4の被制御端子の電圧が部分的に重ねっており、第4電子スイッチトランジスタT4と第5電子スイッチトランジスタT5とが同時に導通される。素子のサイズを調整することにより、第6電子スイッチトランジスタT6はオフ状態を維持する。第4電子スイッチトランジスタT4の被制御端子がローレベルである場合、行走査信号は引き続きハイレベルであり、第6電子スイッチトランジスタT6がオンし、行走査信号のハイレベルを出力する。行走査信号がローレベルに切り替わると、第5電子スイッチトランジスタT5がオフし、第6電子スイッチトランジスタT6の第2端子は、第2容量C2の容量結合によりローレベルになる。プルダウン信号QB-nがハイレベルである場合、第8電子スイッチトランジスタT8がオンし、第8電子スイッチトランジスタT8がローレベルを出力し、これにより第6電子スイッチトランジスタT6の第2端子が出力する第2サブ行走査信号がプルダウンされてリセットする。

【0054】

対称な8本の電子スイッチトランジスタを設置し、そして対応する駆動制御信号を設定することにより、行走査信号の分割が実現され、回路構成が単純化になり、ゲート集積回路

10

20

30

40

50

100の集積設置を容易にするとともに、表示パネルの額縁を節約し、狭額縁化を実現する。

**【0055】**

上述した信号分割回路20を基礎として最適化及び具体化すると、ゲート集積駆動回路の駆動の多様性と異なる分解能を出力することを実現するために、図8に示すように、一実施例では、信号分割回路20は、切り替え回路24をさらに含み、切り替え回路24の第1信号入力端子と、第1スイッチ回路21の信号出力端子と、プルダウン回路23の第1信号端子とが共通に接続され、切り替え回路24の第2信号入力端子と、第2スイッチ回路22の信号出力端子と、プルダウン回路23の第2信号端子とが共通に接続され、切り替え回路24の第3信号入力端子は、現段のゲート集積回路ユニット10が出力する行走査信号を入力するために使用され、切り替え回路24の第1信号出力端子と第2信号出力端子は、信号分割回路20の第1信号出力端子と第2信号出力端子を構成し、切り替え回路24の被制御端子は、スイッチ選択信号Switch、行走査ハイレベル信号VGH、及び行走査ローレベル信号VGLを入力するために使用される。

切り替え回路24は、スイッチ選択信号Switchのハイレベルとローレベル、行走査ハイレベル信号VGH、及び行走査ローレベル信号VGLによりトリガされてオンオフするために使用され、これにより第1サブ行走査信号と第2サブ行走査信号を、信号分割回路20の第1信号出力端子と第2信号出力端子に切り替えて出力するか、或いは、現段のゲート集積回路ユニット10が出力する行走査信号を、信号分割回路20の第1信号出力端子と第2信号出力端子にそれぞれ出力する。

**【0056】**

本実施例では、図3と図8に示すように、外部制御信号はスイッチ選択信号Switchをさらに含み、スイッチ選択信号Switchは2バスの信号を切り替えて出力するために切り替え回路24に入力される。

**【0057】**

具体的には、スイッチ選択信号Switchが第1レベル信号である場合、切り替え回路24の第3信号入力端子は、2つの出力信号端子に接続され、現段のゲート集積回路ユニット10が出力する行走査信号は、信号分割回路20の第1信号出力端子と第2信号出力端子にそれぞれ出力され、それに接続されている隣接する2行の画素セルが同時にオンし、そして同一のデータ信号が入力され、アレイ基板の解像度が低下になる。

**【0058】**

スイッチ選択信号Switchは第1レベル信号と逆極性の第2レベル信号である場合、切り替え回路24の第1信号入力端子は、自身の第1信号出力端子と接続され、切り替え回路24の第2信号入力端子は、自身の第2信号出力端子と接続され、第1スイッチ回路21、第2スイッチ回路22、及びプルダウン回路23により分割出力された第1行走査信号及び第2サブ行走査信号は、信号分割回路20の第1信号出力端子及び第2信号出力端子に出力され、隣接する2行の画素セルは1行ずつオンになり、図10に示すように、一実施例では、第1レベル信号はハイレベルであり、第2レベル信号はローレベルである。

**【0059】**

ここで、切り替え回路24は、制御により入出力を切り替える機能を実現するために、異なるスイッチングデバイスにより構成されてもよく、切り替え回路24の具体的な構成は、必要に応じて設定される。

**【0060】**

上述した信号分割回路20を基礎として最適化及び具体化すると、図9に示すように、一実施例では、切り替え回路24は、第9電子スイッチトランジスタT9と、第10電子スイッチトランジスタT10と、第11電子スイッチトランジスタT11と、第12電子スイッチトランジスタT12と、第13電子スイッチトランジスタT13と、第14電子スイッチトランジスタT14と、第15電子スイッチトランジスタT15と、第16電子スイッチトランジスタT16と、を含む。

第9電子スイッチトランジスタT9の第1端子と被制御端子は、行走査ハイレベル信号V

10

20

30

40

50

G H を入力するために使用され、第 1 0 電子スイッチトランジスタ T 1 0 の第 1 端子は、行走査ローレベル信号 V G L を入力するために使用され、第 9 電子スイッチトランジスタ T 9 の第 2 端子と、第 1 0 電子スイッチトランジスタ T 1 0 の第 2 端子と、第 1 2 電子スイッチトランジスタ T 1 2 の被制御端子とが共通に接続され、第 1 2 電子スイッチトランジスタ T 1 2 の第 1 端は、切り替え回路 2 4 の第 1 信号入力端子を構成し、第 1 2 電子スイッチトランジスタ T 1 2 の第 2 端子と第 1 1 電子スイッチトランジスタ T 1 1 の第 2 端子とが、切り替え回路 2 4 の第 1 信号出力端子を構成するように共通に接続され、第 1 1 電子スイッチトランジスタ T 1 1 の第 1 端子と第 1 5 電子スイッチトランジスタ T 1 5 の第 1 端子とが、切り替え回路 2 4 の第 3 信号入力端子を構成するように共通に接続され、第 1 1 電子スイッチトランジスタ T 1 1 の被制御端子と、第 1 0 電子スイッチトランジスタ T 1 0 の被制御端子と、第 1 5 電子スイッチトランジスタ T 1 5 の被制御端子と、第 1 4 電子スイッチトランジスタ T 1 4 の被制御端子とが、スイッチ選択信号 S w i t c h を入力するために共通に接続され、第 1 3 電子スイッチトランジスタ T 1 3 の第 1 端子と被制御端子は、行走査ハイレベル信号 V G H を入力するために使用され、第 1 4 電子スイッチトランジスタ T 1 4 の第 1 端子は、行走査ローレベル信号 V G L を入力するために使用され、第 1 3 電子スイッチトランジスタ T 1 3 の第 2 端子と、第 1 4 電子スイッチトランジスタ T 1 4 の第 2 端子と、第 1 6 電子スイッチトランジスタ T 1 6 の被制御端子とが共通に接続され、第 1 6 電子スイッチトランジスタ T 1 6 の第 1 端子は、切り替え回路 2 4 の第 2 信号入力端子を構成し、第 1 6 電子スイッチトランジスタ T 1 6 の第 2 端子と第 1 5 電子スイッチトランジスタ T 1 5 の第 2 端子とが、切り替え回路 2 4 の第 2 信号出力端子を構成するように共通に接続される。

#### 【 0 0 6 1 】

図 9 と図 1 0 に示すように、スイッチ選択信号 S w i t c h がハイレベルである場合、第 1 0 電子スイッチトランジスタ T 1 0 と第 1 4 電子スイッチトランジスタ T 1 4 がそれぞれオンし、そして第 1 2 電子スイッチトランジスタ T 1 2 と第 1 6 電子スイッチトランジスタ T 1 6 にローレベルをそれぞれ出力し、第 1 2 電子スイッチトランジスタ T 1 2 と第 1 6 電子スイッチトランジスタ T 1 6 がオフする。第 1 0 電子スイッチトランジスタ T 1 0 と第 1 4 電子スイッチトランジスタ T 1 4 がそれぞれオンするとともに、第 1 1 電子スイッチトランジスタ T 1 1 と第 1 5 電子スイッチトランジスタ T 1 5 もそれぞれオンし、現段のゲート集積回路ユニット 1 0 が出力する行走査信号は、信号分割回路 2 0 の第 1 信号出力端子と第 2 信号出力端子にそれぞれ出力され、それに接続されている隣接する 2 行の画素セルが同時にオンになり、同一のデータ信号が入力され、アレイ基板の解像度が低下になる。

#### 【 0 0 6 2 】

スイッチ選択信号 S w i t c h がローレベルである場合、第 1 0 電子スイッチトランジスタ T 1 0 、第 1 1 電子スイッチトランジスタ T 1 1 、第 1 4 電子スイッチトランジスタ T 1 4 、及び第 1 5 電子スイッチトランジスタ T 1 5 がオフし、第 9 電子スイッチトランジスタ T 9 と第 1 3 電子スイッチトランジスタ T 1 3 をオンし、そして第 1 2 電子スイッチトランジスタ T 1 2 と第 1 6 電子スイッチトランジスタ T 1 6 にハイレベルを入力し、第 1 2 電子スイッチトランジスタ T 1 2 と第 1 6 電子スイッチトランジスタ T 1 6 がオンし、第 1 スイッチ回路 2 1 、第 2 スイッチ回路 2 2 、及びプルダウン回路 2 3 により分割出力された第 1 サブ行走査信号と第 2 サブ行走査信号が信号分割回路 2 0 の第 1 信号出力端子と第 2 信号出力端子に出力され、隣接する 2 行の画素セルが 1 行ずつオンする。

#### 実施例 2

#### 【 0 0 6 3 】

本願は、アレイ基板と、ゲート集積駆動回路とを含む表示パネルをさらに提供し、当該ゲート集積駆動回路の具体的な構造は、本願の別の態様の上記実施例を参照し、本表示パネルは、本願の別の態様の上記した全部実施例のすべての技術的解決手段を採用しているため、本願の別の態様の上記実施例の技術的解決手段によるすべての有益な効果を同様に有し、ここで重複の説明を省略する。ここで、ゲート集積駆動回路はアレイ基板の片側又は

両側に設けられる。

【 0 0 6 4 】

本実施例では、アレイ基板は、表示領域と、非表示領域とを含み、非表示領域にはピンバイディング領域とゲート集積駆動回路とが設けられ、ゲート集積駆動回路は、アレイ基板の非表示領域の片側又は両側に設けられ、表示領域のプログレッシブ走査を行い、データ信号と合わせて表示領域に対するプログレッシブ走査駆動を実現する。

実施例 3

【 0 0 6 5 】

本願は、バックライトモジュールと、駆動回路板と、表示パネルとを含む表示装置をさらに提供し、当該表示パネルの具体的な構造は、本願の別の態様の上記実施例を参照し、本表示装置は、本願の別の態様の上記した全部実施例のすべての技術的解決手段を採用しているため、本願の別の態様の上記実施例の技術的解決手段によるすべての有益な効果を同様に有し、ここで重複の説明を省略する。ここで、バックライトモジュールと表示パネルとが対向配置され、駆動回路板と表示パネルとが電気接続されている。

10

【 0 0 6 6 】

本実施例では、バックライトモジュールは、バックライトを提供するために使用され、駆動回路板は、結晶被覆膜を介して表示パネルに接続され、そして外部からの制御信号を結晶被覆膜の中の駆動チップに入力し、駆動チップは、外部制御信号をデータ信号とゲート集積駆動回路の駆動に必要な制御信号に対応して変換し、ゲート集積駆動回路は、多重のサブ行走査信号からなるシフトパルス信号を変換して出力し、データ信号と合わせて表示領域のプログレッシブ走査駆動を実現する。

20

【 0 0 6 7 】

上記の実施例は本願の技術的解決手段を説明するためのものであり、これを限定するためのものではない。前記の実施例を参照しながら本願を詳細に説明したが、当業者であれば、前記の各実施例に記載された技術的解決手段を変更し、又はその技術特徴の一部を等価的に置き換えることができるることを理解すべきである。これらの変更や置き換えは、対応する技術的解決手段の本質が本願の各実施例の技術的解決手段の要旨及び範囲から逸脱することなく、本願の保護の範囲に含まれるべきである。

30

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

图 2

【図 3】

【図 4】

图 3

50

【図 5】

【図 6】

10

图 6

20

【図 7】

图 7

30

【図 8】

40

50

【図 9】

【図 10】

10

20

30

40

50

## フロントページの続き

## (51)国際特許分類

| F I     |      |         |  |

|---------|------|---------|--|

| G 0 9 G | 3/20 | 6 1 1 F |  |

| G 0 9 G | 3/20 | 6 8 0 G |  |

| G 0 9 G | 3/20 | 6 2 2 E |  |

| G 0 9 G | 3/36 |         |  |

treeet, Baoan District, Shenzhen, China

(74)代理人 100079108

弁理士 稲葉 良幸

(74)代理人 100109346

弁理士 大貫 敏史

(74)代理人 100117189

弁理士 江口 昭彦

(74)代理人 100134120

弁理士 内藤 和彦

(74)代理人 100108213

弁理士 阿部 豊隆

(72)発明者 沈 テイ テイ

中華人民共和国広東省深セン市宝安区石岩街道石龍社区工業二路1号恵科工業園厂房1棟一層至三層、五至七層，6棟七層

(72)発明者 鄭浩旋

中華人民共和国広東省深セン市宝安区石岩街道石龍社区工業二路1号恵科工業園厂房1棟一層至三層、五至七層，6棟七層

審査官 西島 篤宏

(56)参考文献 米国特許出願公開第2017/0193957(US, A1)

米国特許出願公開第2020/0074912(US, A1)

国際公開第2018/193912(WO, A1)

米国特許出願公開第2020/0013474(US, A1)

(58)調査した分野 (Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 1 1 C 1 9 / 2 8