## (12) 特許協力条約に基づいて公開された国際出願

(19) 世界知的所有権機関

国際事務局

(43) 国際公開日

2016年8月18日 (18.08.2016)

W I P O | P C T

(10) 国際公開番号

WO 2016/129463 A1

(51) 国際特許分類 :

G09G 3/30 (2006.01) H01L 51/50 (2006.01)

G09G 3/20 (2006.01)

(74) 代理人 : 島田 明宏 (SHIMADA, Akihiro); 〒6340078 奈良県橿原市八木町1丁目10番3号

萬盛庵ビル 島田特許事務所 Nara (JP).

(21) 国際出願番号 : PCT/JP2016/053 154 (81)

(22) 国際出願日 : 2016年2月3日 (03.02.2016)

(25) 国際出願の言語 : 日本語

(26) 国際公開の言語 : 日本語

(30) 優先権データ : 特願 2015-024601 2015年2月10日 (10.02.2015) JP

(71) 出願人 : シヤープ株式会社 (SHARP KABUSHIKI KAISHA) [JP/JP]; 〒5908522 大阪府堺市堺区匠町1番地 Osaka (JP).

(72) 発明者 : 岸 宣孝 (KISHI, Noritaka), 古川 浩之 (FURUKAWA, Hiroyuki), 乙井 克也 (TOI, Kazuya), 吉山 未来 (YOSHIMAYAMA, Kazuyoshi), 酒井 保 (SAKAI, Tamotsu), 後藤 尚子 (GOTOH, Naoko).

指定国 (表示のない限り、全ての種類の国内保護が可<sup>能</sup>): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, ML, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) 指定国 (表示のない限り、全ての種類の広域保護が可<sup>能</sup>): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), ユーラシア (AM, AZ, BY, KG, KZ, RU, TJ, TM), ヨーロッパ (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR),

[続葉有]

(54) Title: DISPLAY DEVICE AND METHOD FOR DRIVING SAME

(54) 発明の名称 : 表示装置およびその駆動方法

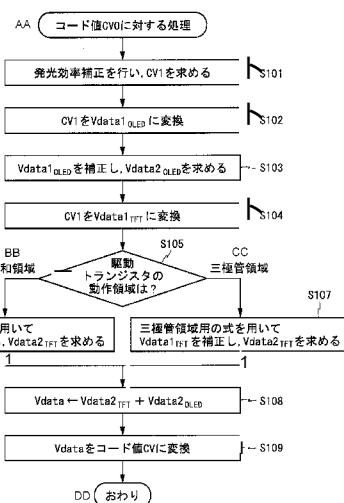

S101 Calculate CV1 by correcting light emission efficiency

S102 Convert CV1 to Vdata<sub>1</sub><sub>OLED</sub>

S103 Calculate Vdata<sub>2</sub><sub>OLED</sub> by correcting Vdata<sub>1</sub><sub>OLED</sub>

S104 Convert CV1 to Vdata<sub>1</sub><sub>TFT</sub>

S105 Which active region drive transistor operating?

S106 Calculate Vdata<sub>2</sub><sub>TFT</sub> by correcting Vdata<sub>1</sub><sub>TFT</sub> using formula for saturation region

S107 Calculate Vdata<sub>2</sub><sub>TFT</sub> by correcting Vdata<sub>1</sub><sub>TFT</sub> using formula for triode region

S108 Convert Vdata to code value CV

AA Processing on code value CV

BB Saturation region

CC Triode region

DD End

(57) Abstract: A current measurement circuit measures a current flowing in a drive transistor when writing a measurement voltage to a pixel circuit by switching through a plurality of measurement voltages, and a current flowing in an organic EL element when writing a measurement voltage to the pixel circuit by switching through another plurality of measurement voltages. A correction unit calculates a threshold voltage and a gain for the drive transistor and the organic EL element in each pixel circuit on the basis of a measured current; determines for each pixel circuit whether the drive transistor should operate in a saturation region or in a triode region on the basis of a video signal; and corrects the video signal in accordance with the active region of the drive transistor. By operating the drive transistor in both the saturation region and the triode region, a power supply voltage decreases to thereby reduce the power consumption of a display device.

(57) 要約: 電流測定回路は、画素回路に複数の測定用電圧を切り替えて書き込んだときに駆動トランジスタを流れる電流と、画素回路に他の複数の測定用電圧を切り替えて書き込んだときに有機EL素子を流れる電流を測定する。補正部は、測定された電流に基づき画素回路ごとに駆動トランジスタと有機EL素子の閾値電圧とゲインを求め、映像信号に基づき画素回路ごとに駆動トランジスタを飽和領域と三極管領域のうちいずれの動作領域で動作させるかを決定し、映像信号に対して駆動トランジスタの動作領域に応じた補正を行う。駆動トランジスタを飽和領域と三極管領域の両方で動作させることにより、電源電圧を小さくし、表示装置の消費電力を削減する。

OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG). 添付公開書類：

- 國際調查報告 (條約第 21 条(3))

## 明 細 書

## 発明の名称：表示装置およびその駆動方法

## 技術分野

[0001] 本発明は、表示装置に関し、特に、有機EL素子などの電気光学素子を含む画素回路を備えた表示装置、および、その駆動方法に関する。

## 背景技術

[0002] 近年、薄型、軽量、高速応答可能な表示装置として、有機EL(Electro Luminescence)表示装置が注目されている。有機EL表示装置は、2次元状に配置された複数の画素回路を備えている。有機EL表示装置の画素回路は、有機EL素子、および、有機EL素子と直列に接続された駆動トランジスタを含んでいる。駆動トランジスタは有機EL素子に流れる電流の量を制御し、有機EL素子は流れる電流の量に応じた輝度で発光する。

[0003] 画素回路内の素子の特性には、製造時にばらつきが発生する。また、画素回路内の素子の特性は、時間の経過と共に変動する。例えば、駆動トランジスタの特性は、発光輝度や発光時間に応じて個別に劣化する。有機EL素子の特性もこれと同様である。このため、駆動トランジスタのゲート端子に同じ電圧を印加しても、有機EL素子の発光輝度にはばらつきが発生する。

[0004] そこで、有機EL表示装置において高画質表示を行うために、有機EL素子や駆動トランジスタの特性のばらつきや変動を補償するように映像信号を補正する方法が知られている。例えば、特許文献1には、有機EL素子に検定電流を流したときの有機EL素子の端子間の電圧を測定し、測定した電圧に基づき映像信号を補正することにより、有機EL素子の特性変動を補償する有機EL表示装置が記載されている。

## 先行技術文献

## 特許文献

[0005] 特許文献1：日本国特開2009—244654号公報

## 発明の概要

## 発明が解決しようとする課題

- [0006] 特許文献 1 に記載の有機 EL 表示装置は、アナログ階調駆動を行う。アナログ階調駆動では、駆動トランジスタのゲート端子に対して、映像信号に応じた多階調の電圧（以下、データ電圧という）が印加される。また、有機 EL 素子の特性にかかわらず、有機 EL 素子に所望の電流を流すために、画素回路に与えられる電源電圧やデータ電圧は駆動トランジスタが飽和領域で動作するように決定される。駆動トランジスタを飽和領域で動作させるためには、ゲート端子に動作範囲内の電圧が印加されているときには、ドレイン－ソース間電圧をオーバードライブ電圧（ゲート－ソース間電圧から閾値電圧を引いた電圧）以上にする必要がある。

- [0007] このようにアナログ階調駆動を行う従来の有機 EL 表示装置では、駆動トランジスタのゲート端子に最大階調に対応した電圧を印加したときでも、駆動トランジスタのドレイン－ソース間電圧をオーバードライブ電圧以上にする必要がある。しかしながら、駆動トランジスタのドレイン－ソース間電圧は、有機 EL 素子の発光に寄与せず、発熱の原因になるだけである。このため、アナログ階調駆動を行う従来の有機 EL 表示装置には、消費電力が大きいという問題がある。

- [0008] これとは別に、駆動トランジスタを三極管領域で動作させる方法として、1 フレーム期間を複数のサブフレーム期間に分割し、各サブフレーム期間において駆動トランジスタのゲート端子に対して、映像信号の各ビットに応じた 2 値の電圧を印加する時分割デジタル階調駆動が知られている。しかしながら、時分割デジタル階調駆動を行う有機 EL 表示装置には、階調数に応じて動作周波数が高くなるので高精細化が困難であるという問題がある。また、時分割デジタル階調駆動を行う有機 EL 表示装置には、表示画面に疑似輪郭が発生し、有機 EL 素子の寿命が短くなるなどの問題もある。

- [0009] それ故に、本発明は、高画質で低消費電力の表示装置を提供することを目的とする。

## 課題を解決するための手段

- [001 0] 本発明の第1の局面は、アクティブマトリクス型の表示装置であって、複数の走査線と複数のデータ線と2次元状に配置された複数の画素回路とを含む表示部と、

前記走査線を駆動する走査線駆動回路と、

前記データ線を駆動するデータ線駆動回路とを備え、

前記画素回路は、電気光学素子と、制御端子を有し、前記電気光学素子と直列に接続された駆動トランジスタとを含み、

前記駆動トランジスタは、前記データ線駆動回路を用いて前記制御端子に印加されたデータ電圧が第1範囲内にあるときは飽和領域で動作し、前記データ電圧が第2範囲内にあるときは三極管領域で動作することを特徴とする。

。

- [001 1] 本発明の第2の局面は、本発明の第1の局面において、

前記表示部の外部に設けられ、前記画素回路について電流または電圧を測定する測定回路と、

前記測定回路で測定された電流または電圧に基づき、前記データ線駆動回路に供給される映像信号に対して補正を行う補正部とをさらに備え、

前記補正部は、前記映像信号に基づき前記画素回路ごとに前記駆動トランジスタを飽和領域および三極管領域のうちいずれの動作領域で動作させるかを決定し、前記映像信号に対して前記駆動トランジスタの動作領域に応じた補正を行うことを特徴とする。

- [001 2] 本発明の第3の局面は、本発明の第2の局面において、

前記補正部は、前記測定回路で測定された電流または電圧に基づき前記画素回路ごとに前記駆動トランジスタと前記電気光学素子の特性を求め、前記映像信号に対して前記駆動トランジスタと前記電気光学素子の特性を用いて前記駆動トランジスタの動作領域に応じた補正を行うことを特徴とする。

- [001 3] 本発明の第4の局面は、本発明の第3の局面において、

前記補正部は、前記映像信号に含まれるコード値に基づき前記駆動トランジスタに印加される第1電圧と前記電気光学素子に印加される第2電圧とを

求め、前記第2電圧に対して前記電気光学素子の特性を用いて補正を行い、前記第1電圧に対して前記駆動トランジスタの特性を用いて前記駆動トランジスタの動作領域に応じた補正を行い、補正後の第1電圧と補正後の第2電圧の和に対応したコード値を求める特徴とする。

[0014] 本発明の第5の局面は、本発明の第4の局面において、前記補正部は、前記第2電圧を補正した後に、前記第1電圧と前記補正後の第2電圧とに基づき前記駆動トランジスタの動作領域を決定することを特徴とする。

[0015] 本発明の第6の局面は、本発明の第2の局面において、前記表示部は、前記画素回路に電源電圧を供給する電源電極をさらに含み、前記電源電圧が印加された非反転入力端子、前記電源電極に接続された反転入力端子、および、前記電源電極に接続された出力端子を有するオペアンプをさらに備える。

[0016] 本発明の第7の局面は、本発明の第2の局面において、前記画素回路に供給される電源電圧のレベルを制御する電源制御部をさらに備える。

[0017] 本発明の第8の局面は、本発明の第2の局面において、前記測定回路は、前記画素回路を流れる電流を測定する電流測定回路であることを特徴とする。

[0018] 本発明の第9の局面は、本発明の第8の局面において、前記電流測定回路は、前記画素回路に複数の測定用電圧を切り替えて書き込んだときに前記駆動トランジスタを流れる電流と、前記画素回路に他の複数の測定用電圧を切り替えて書き込んだときに前記電気光学素子を流れる電流とを測定し、

前記補正部は、前記電流測定回路で測定された電流に基づき、前記画素回路ごとに前記駆動トランジスタの閾値電圧およびゲイン、並びに、前記電気光学素子の閾値電圧およびゲインを求める特徴とする。

[001 9] 本発明の第 10 の局面は、本発明の第 8 の局面において、

前記画素回路は、

前記データ線に接続された第 1 導通端子、前記駆動トランジスタの制御端子に接続された第 2 導通端子、および、前記走査線のうち第 1 走査線に接続された制御端子を有する書き込み制御トランジスタと、

前記データ線に接続された第 1 導通端子、前記駆動トランジスタと前記電気光学素子の接続点に接続された第 2 導通端子、および、前記走査線のうち第 2 走査線に接続された制御端子を有する読み出し制御トランジスタとをさらに含み、

前記電流測定回路は、前記データ線に接続され、前記画素回路と前記データ線を流れる電流を測定することを特徴とする。

[0020] 本発明の第 11 の局面は、本発明の第 8 の局面において、

前記表示部は複数のモニタ線をさらに含み、

前記画素回路は、

前記データ線に接続された第 1 導通端子、前記駆動トランジスタの制御端子に接続された第 2 導通端子、および、前記走査線に接続された制御端子を有する書き込み制御トランジスタと、

前記モニタ線に接続された第 1 導通端子、前記駆動トランジスタと前記電気光学素子の接続点に接続された第 2 導通端子、および、前記走査線に接続された制御端子を有する読み出し制御トランジスタとをさらに含み、

前記電流測定回路は、前記モニタ線に接続され、前記画素回路と前記モニタ線を流れる電流を測定することを特徴とする。

[0021] 本発明の第 12 の局面は、本発明の第 8 の局面において、

前記表示部は電源線を含み、

前記画素回路は、前記データ線に接続された第 1 導通端子、前記駆動トランジスタの制御端子に接続された第 2 導通端子、および、前記走査線に接続された制御端子を有する書き込み制御トランジスタをさらに含み、

前記駆動トランジスタの第 1 導通端子は前記電源線に接続され、

前記電流測定回路は、前記電源線に接続され、前記画素回路と前記電源線を流れる電流を測定することを特徴とする。

[0022] 本発明の第13の局面は、本発明の第2の局面において、

前記測定回路は、前記画素回路内の節点の電圧を測定する電圧測定回路であることを特徴とする。

[0023] 本発明の第14の局面は、本発明の第13の局面において、

前記電圧測定回路は、前記駆動トランジスタに複数の測定用電流を切り替えて流したときの前記駆動トランジスタの一方の導通端子の電圧と、前記電気光学素子に他の複数の測定用電流を切り替えて流したときの前記電気光学素子の一方の端子の電圧とを測定し、

前記補正部は、前記電圧測定回路で測定された電圧に基づき、前記画素回路ごとに前記駆動トランジスタの閾値電圧およびゲイン、並びに、前記電気光学素子の閾値電圧およびゲインを求ることを特徴とする。

[0024] 本発明の第15の局面は、本発明の第14の局面において、

前記画素回路は、

前記データ線に接続された第1導通端子、前記駆動トランジスタの制御端子に接続された第2導通端子、および、前記走査線のうち第1走査線に接続された制御端子を有する書き込み制御トランジスタと、

前記データ線に接続された第1導通端子、前記駆動トランジスタと前記電気光学素子の接続点に接続された第2導通端子、および、前記走査線のうち第2走査線に接続された制御端子を有する読み出し制御トランジスタとをさらに含み、

前記電圧測定回路は、前記データ線に接続され、前記駆動トランジスタと前記電気光学素子の接続点の電圧を測定することを特徴とする。

[0025] 本発明の第16の局面は、複数の走査線と複数のデータ線と2次元状に配置された複数の画素回路とを含む表示部を有するアクティブラトリクス型の表示装置の駆動方法であつて、

前記走査線を駆動するステップと、

前記データ線を駆動するステップとを備え、

前記画素回路は、電気光学素子と、制御端子を有し、前記電気光学素子と直列に接続された駆動トランジスタとを含み、

前記駆動トランジスタは、前記データ線を駆動するステップにおいて前記制御端子に印加されたデータ電圧が第1範囲内にあるときは飽和領域で動作し、前記データ電圧が第2範囲内にあるときは三極管領域で動作することを特徴とする。

[0026] 本発明の第17の局面は、本発明の第16の局面において、

前記表示部の外部において、前記画素回路について電流または電圧を測定するステップと、

測定された電流または電圧に基づき、前記データ線の駆動に用いられる映像信号に対して補正を行うステップとをさらに備え、

前記補正を行うステップは、前記映像信号に基づき前記画素回路ごとに前記駆動トランジスタを飽和領域および三極管領域のうちいずれの動作領域で動作させるかを決定し、前記映像信号に対して前記駆動トランジスタの動作領域に応じた補正を行うことを特徴とする。

## 発明の効果

[0027] 本発明の第1または第16の局面によれば、駆動トランジスタは、データ電圧が第1範囲内にあるときは飽和領域で動作し、データ電圧が第2範囲内にあるときは三極管領域で動作する。したがって、駆動トランジスタに供給される電源電圧を小さくし、低消費電力の表示装置を提供することができる。

[0028] 本発明の第2または第17の局面によれば、映像信号に基づき画素回路ごとに駆動トランジスタの動作領域が決定され、映像信号に対して駆動トランジスタの動作領域に応じた補正が行われる。したがって、駆動トランジスタを飽和領域のみで動作させるときと同様の補正を行いながら、駆動トランジスタに供給される電源電圧を小さくすることができる。これにより、高画質で低消費電力の表示装置を提供することができる。

- [0029] 本発明の第3の局面によれば、駆動トランジスタと電気光学素子の特性を画素回路ごとに求め、これを用いて映像信号を補正することにより、駆動トランジスタと電気光学素子の特性のばらつきや変動を補償し、高画質の表示を行うことができる。

- [0030] 本発明の第4の局面によれば、映像信号に含まれるコード値に基づき駆動トランジスタに印加される電圧と電気光学素子に印加される電圧とを求め、前者の電圧に対して駆動トランジスタの動作領域に応じた補正を行うことができる。

- [0031] 本発明の第5の局面によれば、電気光学素子に印加される電圧を補正した結果に基づき駆動トランジスタの動作領域を決定することにより、駆動トランジスタの動作領域を好適に決定することができる。

- [0032] 本発明の第6の局面によれば、オペアンプを用いて電源電圧を安定化させることにより、駆動トランジスタの動作領域を切り替える場合でも、電源電圧の変動によって表示画面が不安定になることを防止することができる。

- [0033] 本発明の第7の局面によれば、駆動トランジスタに供給される電源電圧を状況に応じて小さくすることにより、表示装置の消費電力をさらに削減することができる。

- [0034] 本発明の第8の局面によれば、画素回路を流れる電流を測定し、測定した電流に基づき映像信号を補正することができる。

- [0035] 本発明の第9の局面によれば、測定用電圧を書き込んだときに駆動トランジスタや電気光学素子を流れる電流を測定し、測定結果に基づき駆動トランジスタと電気光学素子の閾値電圧とゲインを求めることにより、駆動トランジスタと電気光学素子の  $I-V$  特性（電流-電圧特性）を求めることができる。駆動トランジスタと電気光学素子の閾値電圧とゲインを用いて映像信号を補正することにより、高画質の表示を行うことができる。

- [0036] 本発明の第10の局面によれば、画素回路を流れる電流をデータ線に接続された電流測定回路を用いて測定することができる。

- [0037] 本発明の第11の局面によれば、画素回路を流れる電流をモニタ線に接続

された電流測定回路を用いて測定することができる。

[0038] 本発明の第12の局面によれば、画素回路を流れる電流を電源線に接続された電流測定回路を用いて測定することができる。

[0039] 本発明の第13の局面によれば、画素回路内の節点の電圧を測定し、測定した電圧に基づき映像信号を補正することができる。

[0040] 本発明の第14の局面によれば、駆動トランジスタや電気光学素子に測定用電流を流したときに、駆動トランジスタや電気光学素子の端子電圧を測定し、測定結果に基づき駆動トランジスタと電気光学素子の閾値電圧とゲインを求めることにより、駆動トランジスタと電気光学素子の  $I - V$  特性（電流 - 電圧特性）を求めることができる。駆動トランジスタと電気光学素子の閾値電圧とゲインを用いて映像信号を補正することにより、高画質の表示を行うことができる。

[0041] 本発明の第15の局面によれば、画素回路内の節点の電圧をデータ線に接続された電圧測定回路を用いて測定することができる。

## 図面の簡単な説明

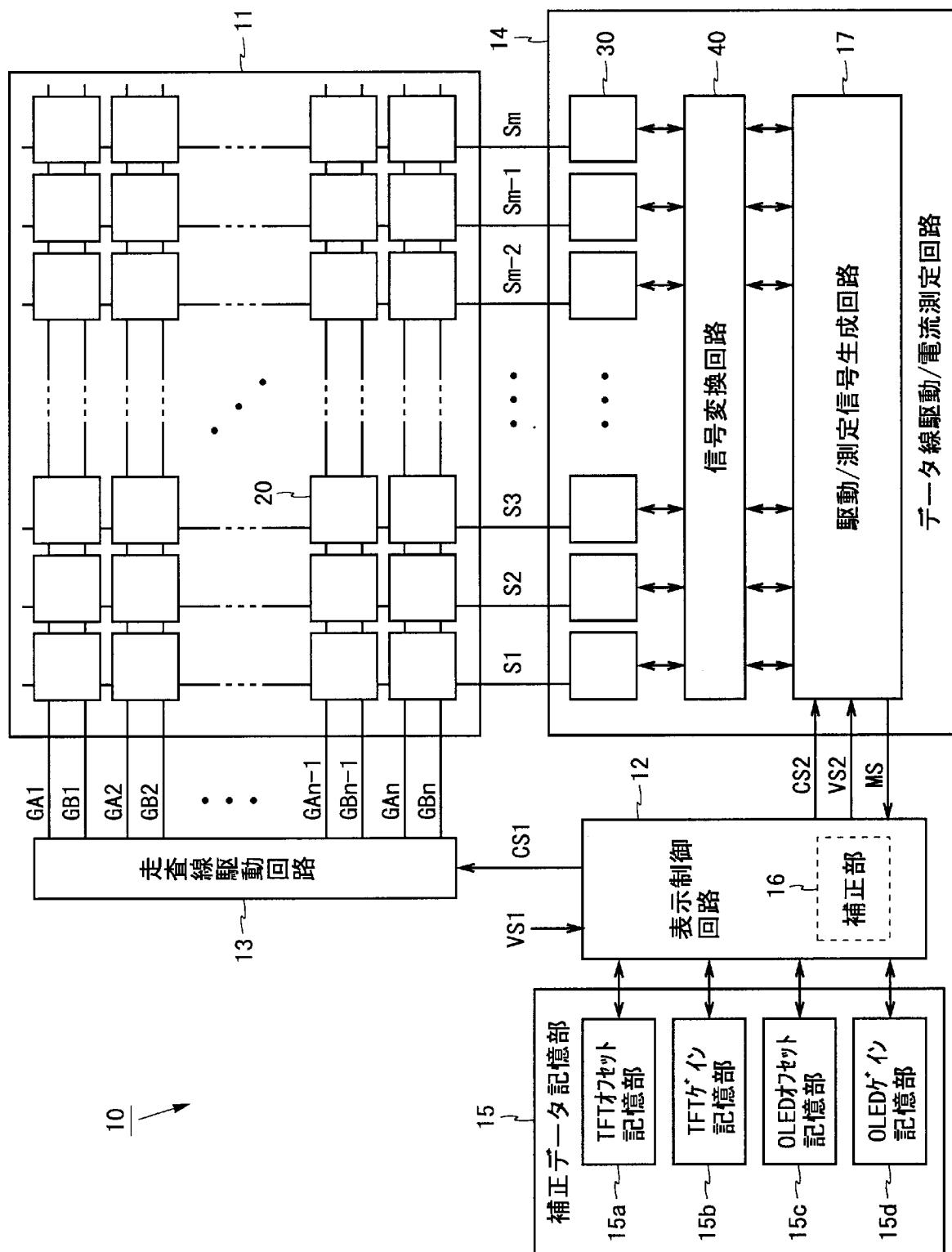

[0042] [図1] 本発明の第1の実施形態に係る表示装置の構成を示すプロック図である。

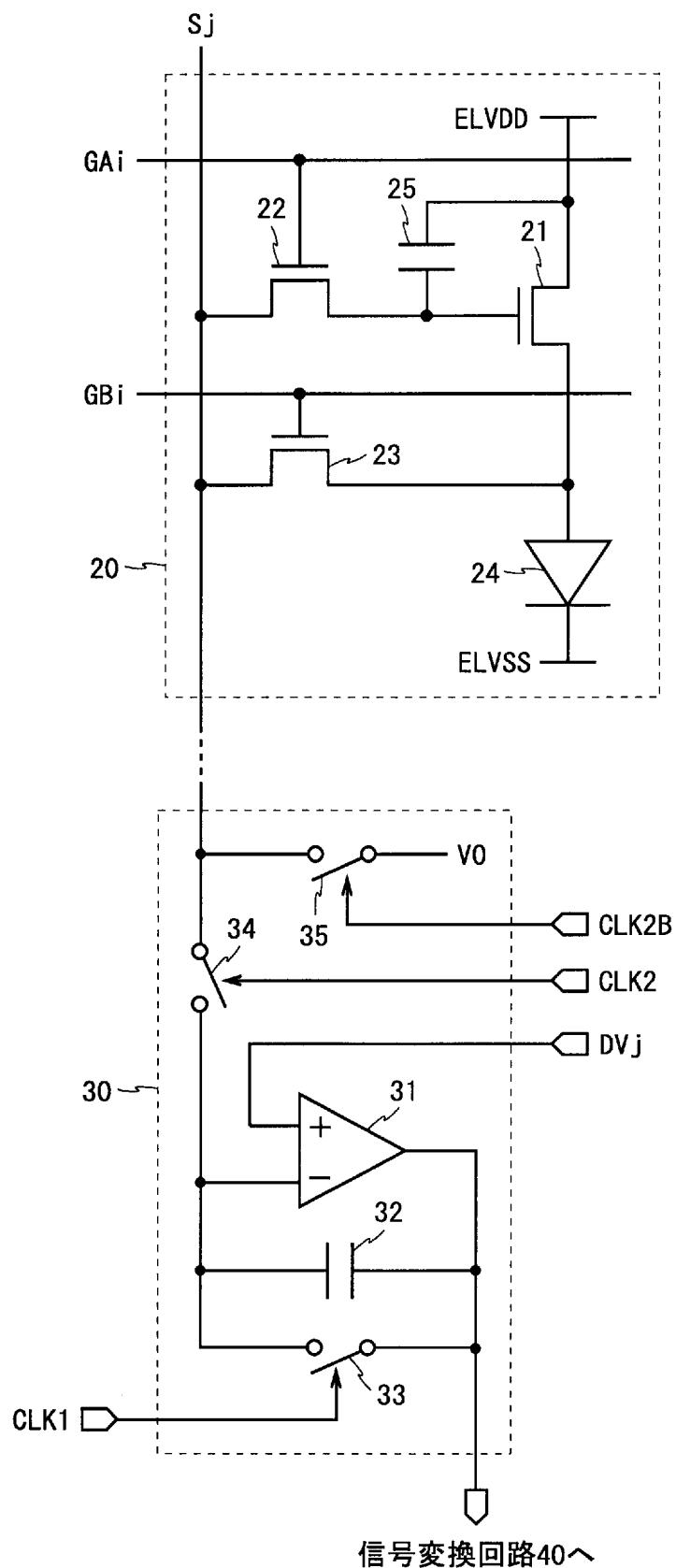

[図2] 図1に示す表示装置の画素回路と出力/測定回路の回路図である。

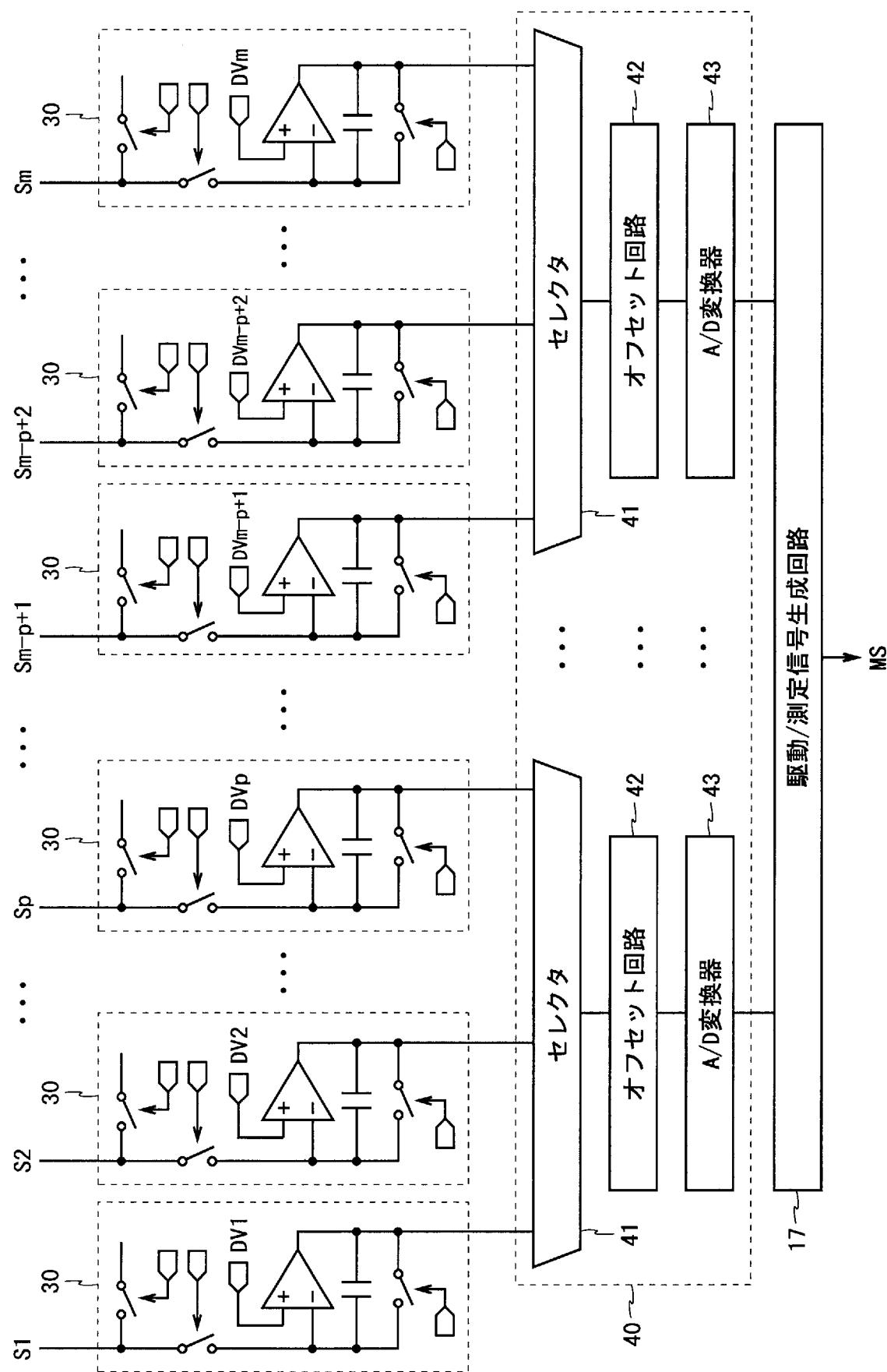

[図3] 図1に示す表示装置の信号変換回路の一部を詳細に示すプロック図である。

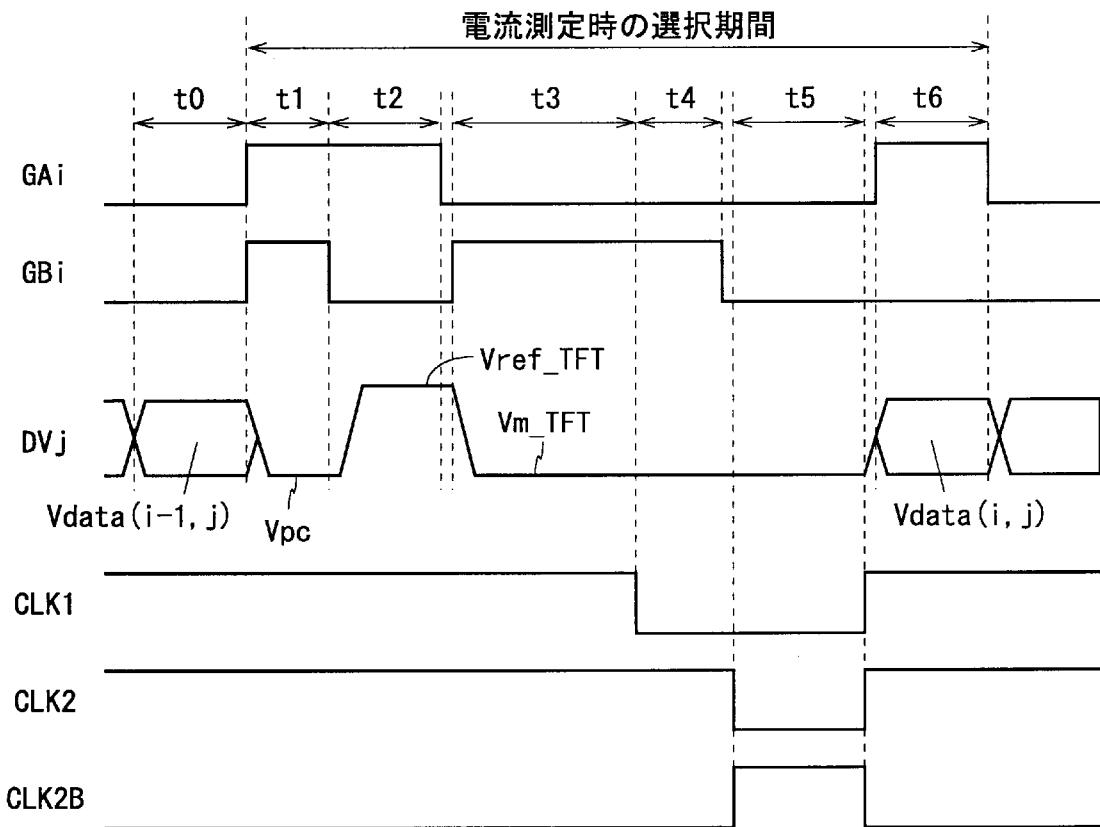

[図4] 図1に示す表示装置の駆動トランジスタの特性検出時のタイミングチャートである。

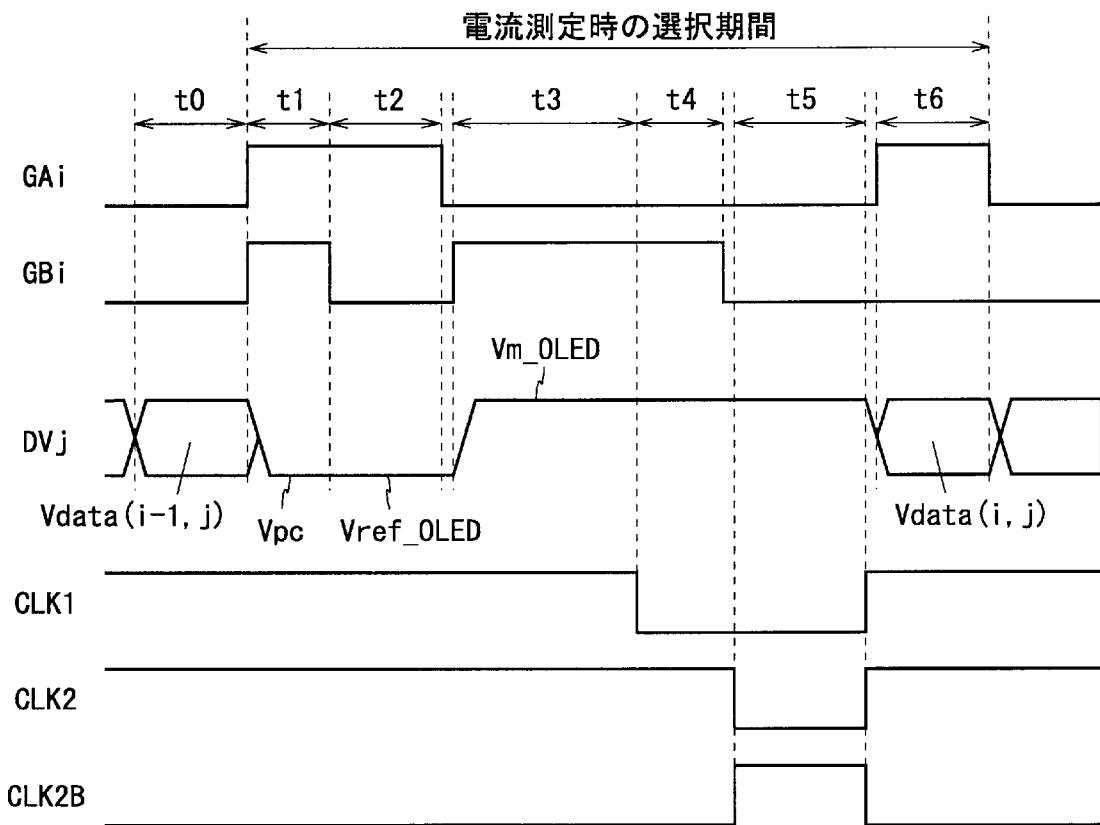

[図5] 図1に示す表示装置の有機EL素子の特性検出時のタイミングチャートである。

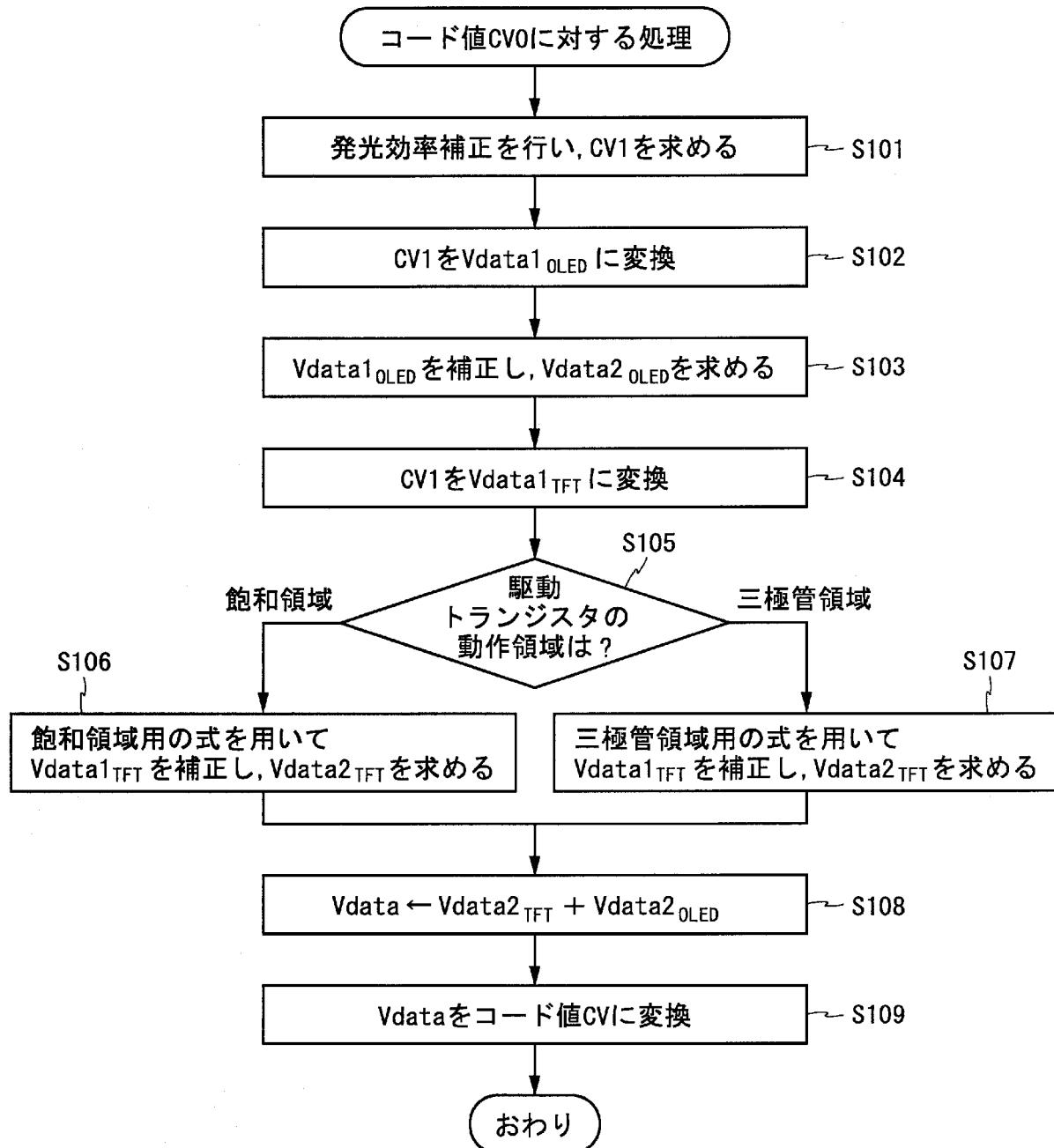

[図6] 図1に示す表示装置における補正処理のフローチャートである。

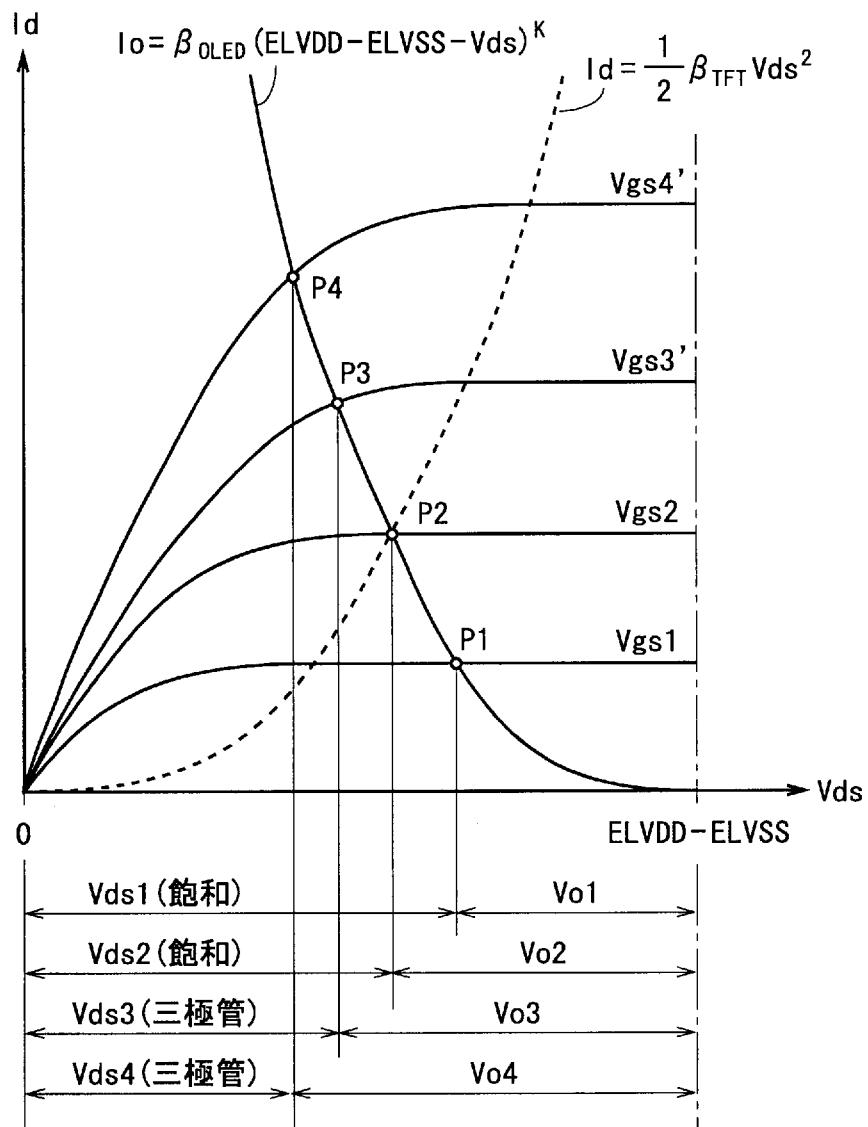

[図7] 従来の表示装置の駆動トランジスタの  $I - V$  特性図である。

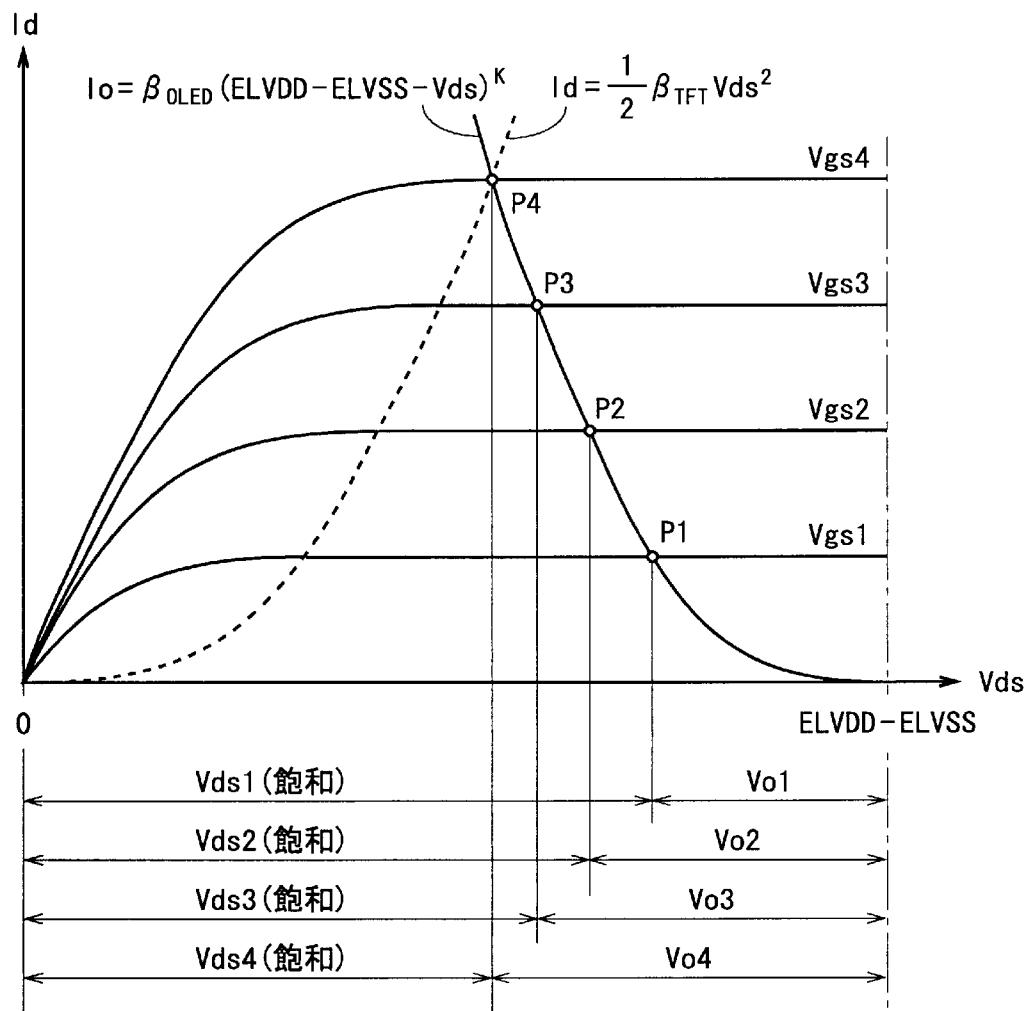

[図8] 図1に示す表示装置の駆動トランジスタの  $I - V$  特性図である。

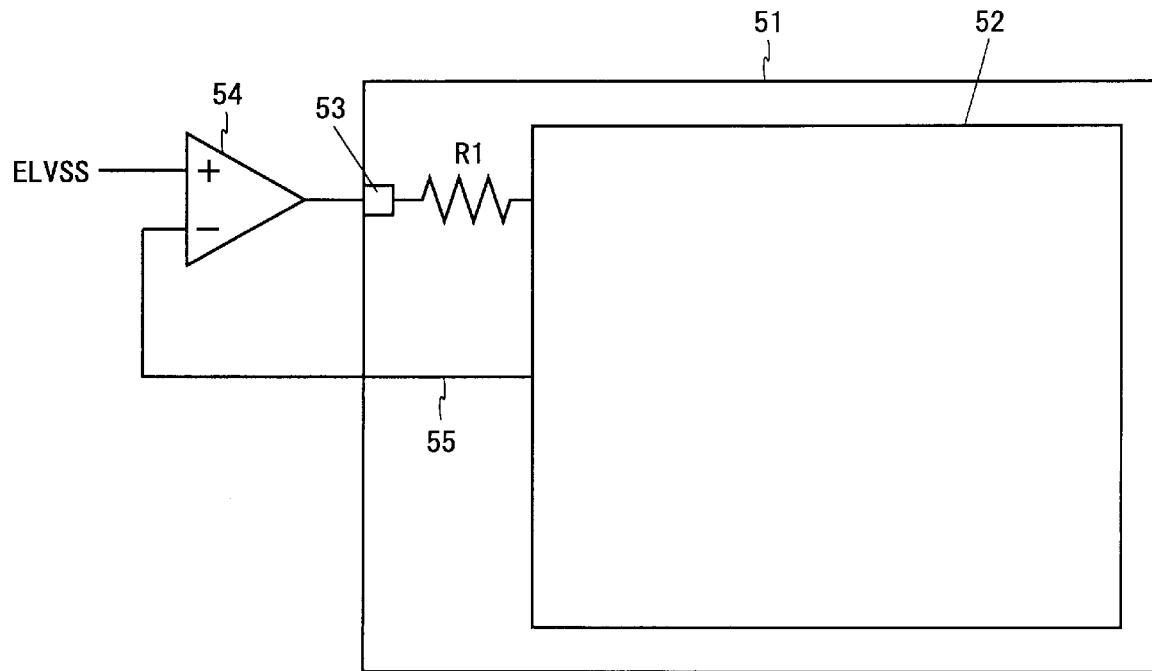

[図9] 本発明の第1の実施形態の変形例に係る表示装置の電源供給回路の構成

を示す図である。

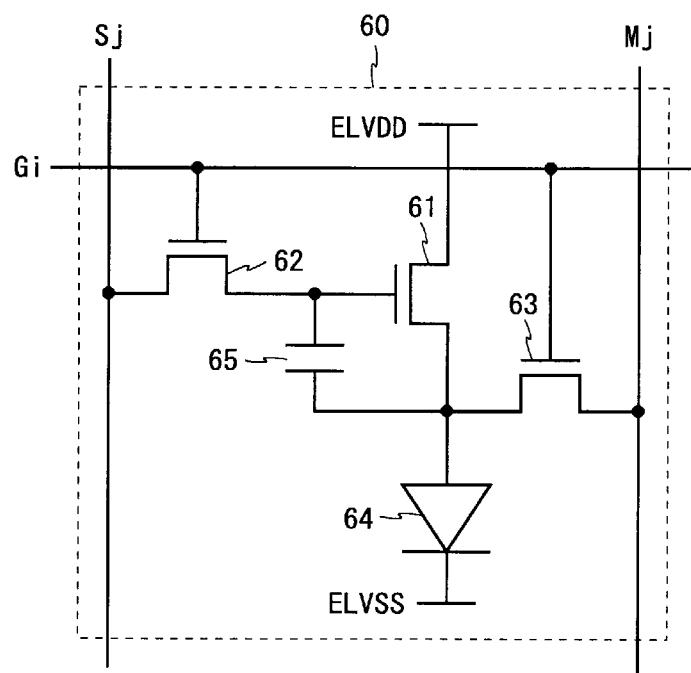

[図10] 本発明の第2の実施形態に係る表示装置の画素回路の回路図である。

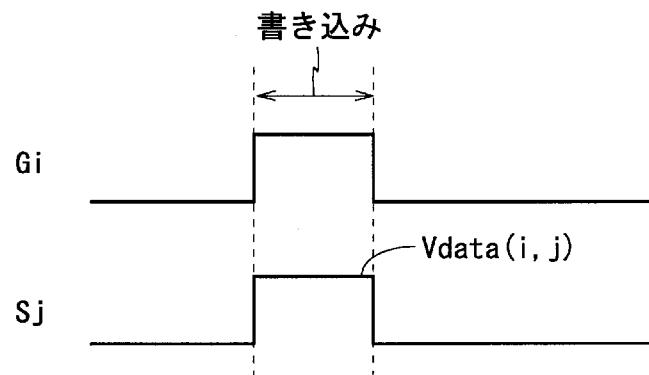

[図11] 本発明の第2の実施形態に係る表示装置のタイミングチャートである。

[図12] 本発明の第3の実施形態に係る表示装置の画素回路と電流測定回路を示す図である。

[図13] 本発明の第4の実施形態に係る表示装置の電源供給回路の構成を示す図である。

[図14] 本発明の第5の実施形態に係る表示装置の構成を示すプロック図である。

[図15] 図14に示す表示装置の画素回路と出力/測定回路の構成を示す図である。

### 発明を実施するための形態

[0043] 以下、図面を参照して、本発明の実施形態に係る表示装置について説明する。本発明の実施形態に係る表示装置は、有機EL素子と駆動トランジスタを含む画素回路を備えたアクティブマトリクス型の有機EL表示装置である。一般に、トランジスタの閾値電圧を $V_{th}$ 、ドレイン-ソース間電圧を $V_{ds}$ 、ゲート-ソース間電圧を $V_{gs}$ としたとき、 $V_{ds} \geq V_{gs} - V_{th}$ を満たす領域を飽和領域、 $V_{ds} < V_{gs} - V_{th}$ を満たす領域を三極管領域（あるいは、線形領域）という。本発明の実施形態に係る表示装置では、画素回路内の駆動トランジスタは、データ電圧が第1範囲内にあるときは飽和領域で動作し、データ電圧が第2範囲内にあるときは三極管領域で動作する。以下の説明では、薄膜トランジスタをTFT（Thin Film Transistor）、有機EL素子をOLED（Organic Light Emitting Diode）ともいう。また、m、nおよびpは2以上の整数、iは1以上n以下の整数、jは1以上m以下の整数であるとする。

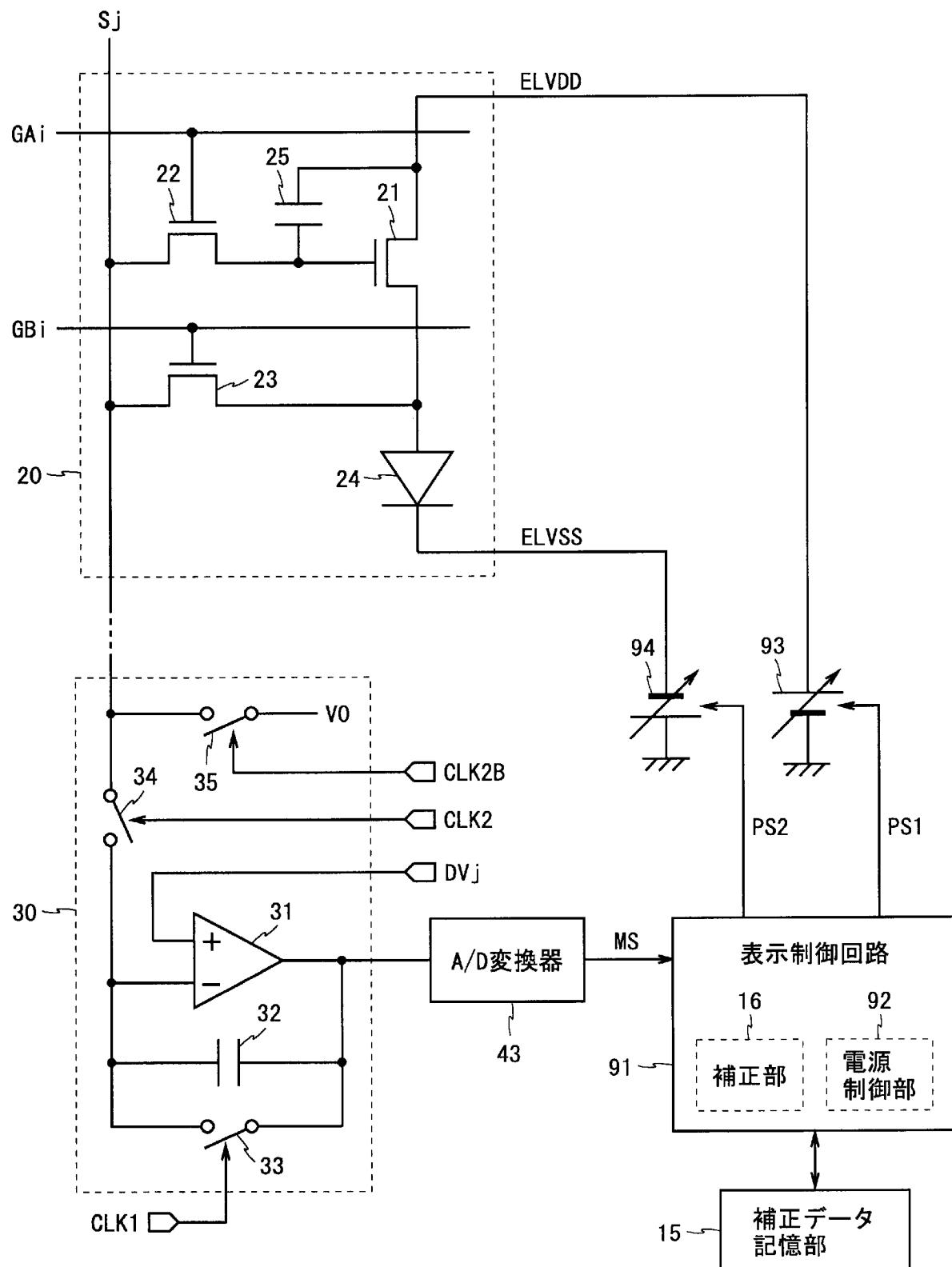

[0044] (第1の実施形態)

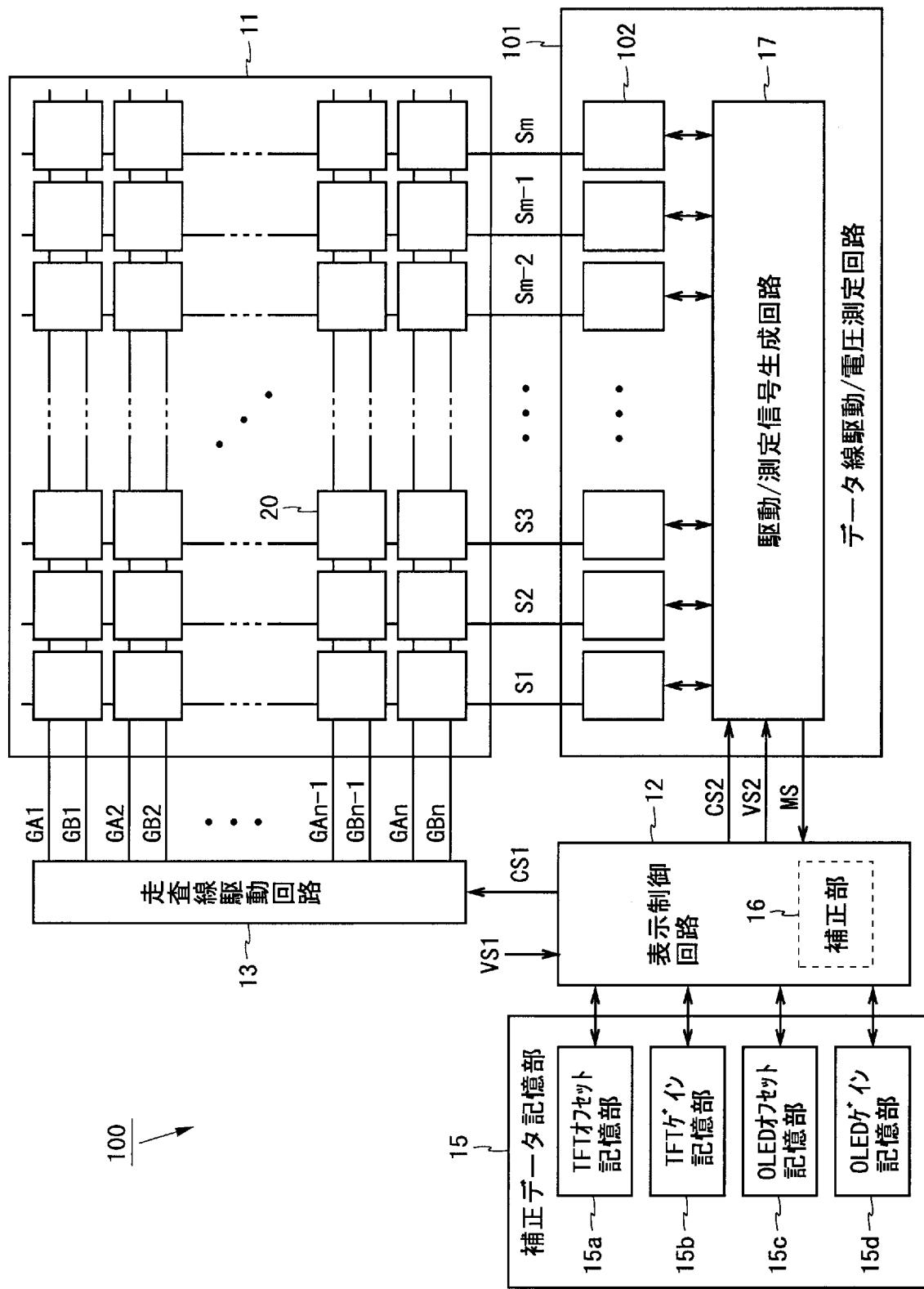

図1は、本発明の第1の実施形態に係る表示装置の構成を示すプロック図

である。図1に示す表示装置10は、表示部11、表示制御回路12、走査線駆動回路13、データ線駆動/電流測定回路(データ線駆動回路と電流測定回路の兼用回路)14、および、補正データ記憶部15を備えている。表示制御回路12は、補正部16を含んでいる。

[0045] 表示部11は、2n本の走査線GA1～GAN、GB1～GBn、m本のデータ線S1～Sm、および、(m×n)個の画素回路20を含んでいる。走査線GA1～GAN、GB1～GBnは、互いに平行に配置される。データ線S1～Smは、互いに平行に、かつ、走査線GA1～GAN、GB1～GBnと直交するように配置される。走査線GA1～GANとデータ線S1～Smは、(m×n)箇所で交差する。(m×n)個の画素回路20は、走査線GA1～GANとデータ線S1～Smの交差点に対応して2次元状に配置される。画素回路20には、図示しない電源線または電源電極を用いてハイレベル電源電圧ELVDDとローレベル電源電圧ELVSSが供給される。

[0046] 表示装置10には、外部から映像信号VS1が入力される。表示制御回路12は、映像信号VS1に基づき、走査線駆動回路13に対して制御信号CS1を出力し、データ線駆動/電流測定回路14に対して制御信号CS2と映像信号VS2を出力する。制御信号CS1には、例えば、ゲートスタートパルスやゲートクロックが含まれる。制御信号CS2には、例えば、ソーススター/パルスやソースクロックが含まれる。映像信号VS2は、補正部16において映像信号VS1に対して後述する補正を行うことにより得られる。

[0047] 走査線駆動回路13とデータ線駆動/電流測定回路14は、表示部11の外部に設けられる。走査線駆動回路13とデータ線駆動/電流測定回路14は、画素回路20に対して映像信号VS2に応じたデータ電圧を書き込む処理と、画素回路20に測定用電圧を書き込んだときに画素回路20を流れる電流を測定する処理とを選択的に行う。以下、前者を「書き込み」、後者を「電流測定」という。

- [0048] 走査線駆動回路 13 は、制御信号 CS 1 に基づき、走査線 GA 1～GA n 、 GB 1～GB n を駆動する。走査線駆動回路 13 は、書き込み時には、走査線 GA 1～GA n の中から 1 本の走査線を順に選択し、選択した走査線に選択電圧（ここでは、ハイレベル電圧）を印加する。これにより、選択された走査線に接続された m 個の画素回路 20 が一括して選択される。

- [0049] データ線駆動/電流測定回路 14 は、駆動/測定信号生成回路（駆動信号と測定信号の生成回路）17、信号変換回路 40、および、m 個の出力/測定回路（出力回路と測定回路の兼用回路）30 を含み、制御信号 CS 2 に基づきデータ線 S 1～S m を駆動する。データ線駆動/電流測定回路 14 は、書き込み時には、映像信号 VS 2 に応じた m 個のデータ電圧をデータ線 S 1～S m にそれぞれ印加する。これにより、選択された m 個の画素回路 20 に m 個のデータ電圧がそれぞれ書き込まれる。

- [0050] 走査線駆動回路 13 とデータ線駆動/電流測定回路 14 の電流測定時の動作については、後述する。データ線駆動/電流測定回路 14 は、画素回路 20 を流れる電流を測定した結果を示すモニタ信号 MS を表示制御回路 12 に対して出力する。

- [0051] 補正部 16 は、モニタ信号 MS に基づき画素回路 20 内の駆動トランジスタと有機 EL 素子の特性を求め、求めた特性を用いて映像信号 VS 1 を補正することにより映像信号 VS 2 を求める。補正データ記憶部 15 は、補正部 16 の作業用メモリである。補正データ記憶部 15 は、TFT オフセット記憶部 15 a、TFT ゲイン記憶部 15 b、OLED オフセット記憶部 15 c、および、OLED ゲイン記憶部 15 d を含んでいる。TFT オフセット記憶部 15 a は、各画素回路 20 について駆動トランジスタの閾値電圧を記憶する。TFT ゲイン記憶部 15 b は、各画素回路 20 について駆動トランジスタのゲインを記憶する。OLED オフセット記憶部 15 c は、各画素回路 20 について有機 EL 素子の閾値電圧を記憶する。OLED ゲイン記憶部 15 d は、各画素回路 20 について有機 EL 素子のゲインを記憶する。

- [0052] 図 2 は、画素回路 20 と出力/測定回路 30 の回路図である。図 2 には、

「行」列目の画素回路 20 と、データ線  $S_j$  に対応した出力/測定回路 30 とが記載されている。図 2 に示すように、「行」列目の画素回路 20 は、トランジスタ 21～23、有機 EL 素子 24、および、コンデンサ 25 を含み、走査線  $G_A$  i、 $G_B$  i とデータ線  $S_j$  に接続される。トランジスタ 21～23 は、N チャネル型 TFT である。

[0053] トランジスタ 21 のドレイン端子には、ハイレベル電源電圧  $ELVDD$  が印加される。トランジスタ 21 のソース端子は、有機 EL 素子 24 のアノード端子に接続される。有機 EL 素子 24 のカソード端子には、ローレベル電源電圧  $ELVSS$  が印加される。トランジスタ 22、23 の一方の導通端子（図 2 では左側の端子）は、データ線  $S_j$  に接続される。トランジスタ 22 の他方の導通端子はトランジスタ 21 のゲート端子に接続され、トランジスタ 22 のゲート端子は走査線  $G_A$  i に接続される。トランジスタ 23 の他方の導通端子はトランジスタ 21 のソース端子と有機 EL 素子 24 のアノード端子に接続され、トランジスタ 23 のゲート端子は走査線  $G_B$  i に接続される。コンデンサ 25 は、トランジスタ 21 のゲート端子とドレイン端子の間に設けられる。トランジスタ 21～23 は、それぞれ、駆動トランジスタ、書き込み制御トランジスタ、および、読み出し制御トランジスタとして機能する。

[0054] データ線  $S_j$  に対応した出力/測定回路 30 は、オペアンプ 31、コンデンサ 32、および、スイッチ 33～35 を含み、データ線  $S_j$  に接続される。スイッチ 34 の一端（図 2 では上端）とスイッチ 35 の一端（図 2 では左端）は、データ線  $S_j$  に接続される。スイッチ 35 の他端には、所定の電圧  $V_O$  が印加される。オペアンプ 31 の非反転入力端子には、データ線  $S_j$  に対応した D/A 変換器（図示せず）の出力信号  $DV_j$  が印加される。オペアンプ 31 の反転入力端子は、スイッチ 34 の他端に接続される。コンデンサ 32 は、オペアンプ 31 の反転入力端子と出力端子との間に設けられる。スイッチ 33 は、コンデンサ 32 と並列に、オペアンプ 31 の反転入力端子と出力端子との間に設けられる。スイッチ 33～35 は、それぞれ、スイッチ

制御信号 C L K 1、C L K 2、C L K 2 B がハイレベルのときにオンする。

スイッチ制御信号 C L K 2 B は、スイッチ制御信号 C L K 2 の否定信号である。

[0055] 図 3 は、信号変換回路 4 0 の一部を詳細に示すプロック図である。図 3 に示すように、m 個の出力/測定回路 3 0 は、m 本のデータ線 S 1～S m に対応して設けられる。データ線 S 1～S m は、p 本ずつ ( $m/p$ ) 個のグループに分類される。信号変換回路 4 0 は、セレクタ 4 1、オフセット回路 4 2、および、六/D 変換器 4 3 を ( $m/p$ ) 個ずつ含んでいる。セレクタ 4 1、オフセット回路 4 2、および、A/D 変換器 4 3 は、データ線の 1 個のグループに対応づけられる。各セレクタ 4 1 の前段には、p 個の出力/測定回路 3 0 が設けられる。 ( $m/p$ ) 個の A/D 変換器 4 3 の後段には、駆動/測定信号生成回路 1 7 が設けられる。

[0056] セレクタ 4 1 は、p 個のオペアンプ 3 1 の出力端子に接続される。セレクタ 4 1 は、p 個のオペアンプ 3 1 の出力信号の中から 1 個のアナログ信号を選択する。オフセット回路 4 2 は、セレクタ 4 1 で選択されたアナログ信号に所定のオフセットを加算する。六/D 変換器 4 3 は、オフセット回路 4 2 から出力されたアナログ信号をデジタル値に変換する。駆動/測定信号生成回路 1 7 は、( $m/p$ ) 個の A/D 変換器 4 3 で求めたデジタル値を一時的に記憶する。各セレクタ 4 1 は、p 個のオペアンプ 3 1 の出力信号を順に選択する。セレクタ 4 1 が p 回の選択を完了したとき、駆動/測定信号生成回路 1 7 には全部で m 個のデジタル値が記憶されている。駆動/測定信号生成回路 1 7 は、表示制御回路 1 2 に対して、m 個のデジタル値を含むモニタ信号 M S を出力する。

[0057] 映像信号 V S 1 を補正して映像信号 V S 2 を求めるために、データ線駆動/電流測定回路 1 4 は、各画素回路 2 0 について 4 種類の電流を測定する。より詳細には、各画素回路 2 0 内のトランジスタ 2 1 の特性を求めるために、データ線駆動/電流測定回路 1 4 は、画素回路 2 0 に第 1 測定用電圧 V m 1 を書き込んだときに画素回路 2 0 から流れ出す電流 I m 1 と、画素回路 2

0 に第 2 測定用電圧  $V_{m2}$  ( $> V_{m1}$ ) を書き込んだときに画素回路 20 から流れ出す電流  $I_{m2}$  とを測定する。また、各画素回路 20 内の有機 EL 素子 24 の特性を求めるために、データ線駆動/ 電流測定回路 14 は、画素回路 20 に第 3 測定用電圧  $V_{m3}$  を書き込んだときに画素回路 20 に流れ込む電流  $I_{m3}$  と、画素回路 20 に第 4 測定用電圧  $V_{m4}$  ( $> V_{m3}$ ) を書き込んだときに画素回路 20 に流れ込む電流  $I_{m4}$  とを測定する。以下、電流  $I_{m1}$ 、 $I_{m2}$  を測定するときを「駆動トランジスタの特性検出時」、電流  $I_{m3}$ 、 $I_{m4}$  を測定するときを「有機 EL 素子の特性検出時」という。

[0058] 走査線駆動回路 13 とデータ線駆動/ 電流測定回路 14 は、1 行分の画素回路 20 に対する書き込み処理と、1 行分の画素回路 20 について 4 種類の電流  $I_{m1} \sim I_{m4}$  のうちいずれかを測定する処理とを行う。例えば、走査線駆動回路 13 とデータ線駆動/ 電流測定回路 14 は、連続した 4 フレーム期間のうち、第 1 ～ 第 4 フレーム期間内の  $i$  番目のライン期間では  $i$  行目の画素回路 20 について電流  $I_{m1} \sim I_{m4}$  をそれぞれ測定し、それ以外のライン期間では 1 行分の画素回路 20 に対する書き込み処理を行ってもよい。

[0059] 図 4 は、駆動トランジスタの特性検出時のタイミングチャートである。図 5 は、有機 EL 素子の特性検出時のタイミングチャートである。図 4 および図 5 において、期間  $t_0$  は ( $i - 1$ ) 行目の画素回路 20 の書き込み時の選択期間であり、期間  $t_1 \sim t_6$  は  $i$  行目の画素回路 20 の電流測定期間の選択期間である。電流測定期間の選択期間には、リセット期間  $t_1$ 、リファレンス電圧書き込み期間  $t_2$ 、測定用電圧書き込み期間  $t_3$ 、電流測定期間  $t_4$ 、A/D 変換期間  $t_5$ 、および、データ電圧書き込み期間  $t_6$  が含まれる。以下、走査線  $GA_i$ 、 $GB_i$  上の信号を走査信号  $GA_i$ 、 $GB_i$ 、データ線  $S_j$  に対応した D/A 変換器の出力信号の電圧を  $DV_j$  という。

[0060] 期間  $t_1$  より前では、走査信号  $GA_i$ 、 $GB_i$  とスイッチ制御信号  $CLK_2$  はローレベル、スイッチ制御信号  $CLK_1$ 、 $CLK_2$  はハイレベルである。期間  $t_0$  では、走査信号  $GA_{i-1}$  (図示せず) はハイレベル、走査信号  $GB_{i-1}$  (図示せず) はローレベル、電圧  $DV_j$  は ( $i - 1$ ) 行目

の画素回路 20 に書き込むべきデータ電圧  $V_{data}(i-1, j)$  になる。

[0061] 期間で1では、走査信号  $GA_i$ 、 $GB_i$  はハイレベル、電圧  $DV_j$  はプリチャージ電圧  $V_{pc}$  になる。プリチャージ電圧  $V_{pc}$  は、トランジスタ 21 がオフするように決定される。特に、プリチャージ電圧  $V_{pc}$  は、駆動トランジスタ (トランジスタ 21) と有機EL素子 24 が共にオフする範囲内で、できるだけ高く決定することが好ましい (理由は後述)。期間で1では、 $i$  行目の画素回路 20 において、トランジスタ 22、23 はオンし、トランジスタ 21 のゲート端子およびソース端子、並びに、有機EL素子 24 のアノード端子にプリチャージ電圧  $V_{pc}$  が印加される。これにより、 $i$  行目の画素回路 20 内のトランジスタ 21 と有機EL素子 24 は初期化される。

[0062] 例えば、 $InGaZnO$  (Indium Gallium Zinc Oxide : インジウム—ガリウム—亜鉛酸化物) などの酸化物半導体を用いてトランジスタ 21 を形成した場合、トランジスタ 21 がヒステリシス特性を有することがある。このような場合にトランジスタ 21 を初期化せずに使用すると、直前の表示状態によって電流測定結果が異なることがある。電流測定時の選択期間の先頭にリセット期間  $t_1$  を設け、リセット期間  $t_1$  においてトランジスタ 21 を初期化することにより、ヒステリシス特性に起因する電流測定結果のばらつきを防止することができる。なお、有機EL素子 24 はヒステリシス特性を有しないので、有機EL素子の特性検出時にはリセット期間  $t_1$  を設ける必要はない。また、表示中ではなく、電源投入直後や表示オフ中に非表示状態で電流を測定する場合には、リセット期間を省略することができる。

[0063] 期間で2では、走査信号  $GA_i$  はハイレベル、走査信号  $GB_i$  はロー レベル、電圧  $DV_j$  はリファレンス電圧 (駆動トランジスタの特性検出時には  $V_{ref\_TFT}$ 、有機EL素子の特性検出時には  $V_{ref\_OLED}$ ) になる。期間  $t_2$  では、 $i$  行」列目の画素回路 20 において、トランジスタ 22 はオンし、トランジスタ 23 はオフし、トランジスタ 21 のゲート端子にはリファレンス電圧  $V_{ref\_TFT}$  または  $V_{ref\_OLED}$  が印加される

。 リファレンス電圧  $V_{ref\_TFT}$  は、期間  $t_3$ 、 $t_4$  においてトランジスタ  $2_1$  がオンする高い電圧に決定される。リファレンス電圧  $V_{ref\_OLED}$  は、期間  $t_3$ 、 $t_4$  においてトランジスタ  $2_1$  がオフする低い電圧に決定される。

[0064] 期間  $t_3$  では、走査信号  $GA_i$  はローレベル、走査信号  $GB_i$  はハイレベル、電圧  $DV_j$  は第 1 ～ 第 4 測定用電圧  $V_{m1} \sim V_{m4}$  のいずれかになる。図 4 に示す  $V_{m\_TFT}$  は第 1 および第 2 測定用電圧  $V_{m1}$ 、 $V_{m2}$  のいずれかを表し、図 5 に示す  $V_{m\_OLED}$  は第 3 および第 4 測定用電圧  $V_{m3}$ 、 $V_{m4}$  のいずれかを表す。期間  $t_3$  では、 $i$  行  $j$  列目の画素回路  $2_0$  において、トランジスタ  $2_2$  はオフし、トランジスタ  $2_3$  はオンし、有機 EL 素子  $2_4$  のアノード端子には第 1 ～ 第 4 測定用電圧  $V_{m1} \sim V_{m4}$  のいずれかが印加される。駆動トランジスタの特性検出時には、トランジスタ  $2_1$  はオンし、電流はハイレベル電源電圧  $ELVDD$  を有する電源線または電源電極からトランジスタ  $2_1$ 、 $2_3$  を通過してデータ線  $S_j$  に流れる。有機 EL 素子の特性検出時には、トランジスタ  $2_1$  はオフし、電流はデータ線  $S_j$  からトランジスタ  $2_3$  と有機 EL 素子  $2_4$  を通過してローレベル電源電圧  $ELVSS$  を有する電源線または電源電極に流れる。期間  $t_3$  の開始からしばらく経つと、データ線  $S_j$  は所定の電圧レベルに充電され、画素回路  $2_0$  からデータ線  $S_j$  に流れ出す電流（あるいは、データ線  $S_j$  から画素回路  $2_0$  に流れ込む電流）は一定になる。

[0065] なお、駆動トランジスタの特性検出時に、期間  $t_2$  におけるトランジスタ  $2_1$  のソース電位が低い場合には、期間  $t_3$  の開始時にトランジスタ  $2_1$  のゲート - ソース間電圧が大きくなり、トランジスタ  $2_1$  に大きな電流が流れ、有機 EL 素子  $2_4$  が発光する。このときの発光を防止するためには、上述したように、駆動トランジスタと有機 EL 素子  $2_4$  が共にオフする範囲内で、期間  $t_1$  で印加するプリチャージ電圧  $V_{pc}$  を高く決定しておけばよい。

[0066] 期間  $t_4$  では、走査信号  $GA_i$ 、 $GB_i$  と電圧  $DV_j$  は期間  $t_3$  と同じレ

ベルを保ち、スイッチ制御信号 C L K 1 はロー レベルになる。期間  $t_4$  では、スイッチ 3 3 はオフし、オペアンプ 3 1 の出力端子と反転入力端子はコンデンサ 3 2 を介して接続される。このとき、オペアンプ 3 1 とコンデンサ 3 2 は積分アンプとして機能する。期間  $t_4$  の終了時におけるオペアンプ 3 1 の出力電圧は、 $i$  行」列目の画素回路 2 0 とデータ線  $S_j$  を流れる電流の量、コンデンサ 3 2 の容量、および、期間  $t_4$  の長さなどによって決まる。

[0067] 期間  $t_5$  では、走査信号  $G A_i$ 、 $G B_i$  とスイッチ制御信号 C L K 1、C L K 2 はロー レベル、スイッチ制御信号 C L K 2 B はハイ レベルになり、電圧  $D V_j$  は期間  $t_3$ 、 $t_4$  と同じレベルを保つ。期間  $t_5$  では、 $i$  行」列目の画素回路 2 0 において、トランジスタ 2 2、2 3 はオフする。また、スイッチ 3 4 がオフし、スイッチ 3 5 がオンするので、データ線  $S_j$  はオペアンプ 3 1 の非反転入力端子から電気的に切り離され、データ線  $S_j$  には電圧  $V_0$  が印加される。オペアンプ 3 1 の非反転入力端子はデータ線  $S_j$  から電気的に切り離されるので、オペアンプ 3 1 の出力電圧は一定になる。期間  $t_5$  において、データ線  $S_j$  を含むグループに対応したオフセット回路 4 2 はオペアンプ 3 1 の出力電圧にオフセットを加算し、当該グループに対応した A/D 変換器 4 3 はオフセット加算後のアナログ信号をデジタル値に変換する（図 3 を参照）。

[0068] 期間  $t_6$  では、走査信号  $G A_i$  はハイ レベル、走査信号  $G B_i$  はロー レベル、電圧  $D V_j$  は  $i$  行」列目の画素回路 2 0 に書き込むべきデータ電圧  $V_{data}(i, j)$  になる。期間  $t_6$  では、 $i$  行」列目の画素回路 2 0 において、トランジスタ 2 2 がオンし、トランジスタ 2 1 のゲート端子にデータ電圧  $V_{data}(i, j)$  が印加される。期間  $t_6$  の終了時に走査信号  $G A_i$  がロー レベルに変化すると、 $i$  行  $j$  列目の画素回路 2 0 内のトランジスタ 2 2 はオフする。これ以降、 $i$  行」列目の画素回路 2 0 において、トランジスタ 2 1 のゲート電圧は、コンデンサ 2 5 の作用によって  $V_{data}(i, j)$  に保たれる。

[0069] 補正部 1 6 は、測定された 4 種類の電流  $I_{m1} \sim I_{m4}$  に基づき、トラン

ジスタ21と有機EL素子24の特性を求める処理を行い、求めた2種類の特性に基づき映像信号VS1を補正する。より詳細には、補正部16は、2種類の電流Im1、Im2に基づき、トランジスタ21の特性として閾値電圧とゲインを求める。トランジスタ21の閾値電圧はTFTオフセット記憶部15aに書き込まれ、トランジスタ21のゲインはTFTゲイン記憶部15bに書き込まれる。また、補正部16は、2種類の電流Im3、Im4に基づき、有機EL素子24の特性として閾値電圧とゲインを求める。有機EL素子24の閾値電圧はOLEDオフセット記憶部15cに書き込まれ、有機EL素子24のゲインはOLEDゲイン記憶部15dに書き込まれる。補正部16は、補正データ記憶部15から閾値電圧とゲインを読み出し、これらを用いて映像信号VS1を補正する。

[0070] まず、トランジスタ21の閾値電圧とゲインを求める処理について説明する。トランジスタ21が飽和領域で動作するとき、トランジスタ21のゲートソース間電圧Vgs、ドレイン電流Id、閾値電圧Vth<sub>TFT</sub>、および、ゲイン $\beta_{TFT}$ の間には、次式(1)が近似的に成立する。

$$Id = (\beta_{TFT}/2) \times (Vgs - Vth_{TFT})^2 \quad \dots (1)$$

[0071] 画素回路20に第1測定用電圧Vm1を書き込んだときのトランジスタ21のゲートソース間電圧をVgsm1、そのときのトランジスタ21のドレイン電流をIm1、画素回路20に第2測定用電圧Vm2を書き込んだときのトランジスタ21のゲートソース間電圧をVgsm2、そのときのトランジスタ21のドレイン電流をIm2とする。式(1)より、電圧Vgsm1と電流Im1の間には次式(2a)が成立し、電圧Vgsm2と電流Im2の間には次式(2b)が成立する。

$$Im1 = (\beta_{TFT}/2) \times (Vgsm1 - Vth_{TFT})^2 \quad \dots (2a)$$

$$Im2 = (\beta_{TFT}/2) \times (Vgsm2 - Vth_{TFT})^2 \quad \dots (2b)$$

式(2a)、(2b)をVth<sub>TFT</sub>と $\beta_{TFT}$ について解くと、次式(3a)、(3b)が得られる。

[数1]

$$V_{th_{TFT}} = - \frac{V_{gsm1} \sqrt{Im2} - V_{gsm2} \sqrt{Im1}}{\sqrt{Im2} - \sqrt{Im1}} \dots (3a)$$

$$\beta_{TFT} = \frac{2(\sqrt{Im2} - \sqrt{Im1})^2}{(V_{gsm2} - V_{gsm1})^2} \dots (3b)$$

[0072] このように電流  $Im1$ 、 $Im2$  を測定し、式 (2a)、(2b) を解くことにより、トランジスタ21の閾値電圧  $V_{th_{TFT}}$  とゲイン  $\beta_{TFT}$  を求め、トランジスタ21のI-V特性を求めることができる。閾値電圧  $V_{th_{TFT}}$  は TFT オフセット記憶部 15a に書き込まれ、ゲイン  $\beta_{TFT}$  は TFT ゲイン記憶部 15b に書き込まれる。

[0073] 次に、有機EL素子24の閾値電圧とゲインを求める処理について説明する。有機EL素子24のアノード—カソード間電圧  $V_o$ 、電流  $I_o$ 、閾値電圧  $V_{th_{0LED}}$ 、および、ゲイン  $\beta_{0LED}$  の間には、次式 (4) が近似的に成立する。ただし、式 (4)において、Kは2以上3以下の定数である。

$$I_o = \beta_{0LED} (V_o - V_{th_{0LED}}) \kappa \dots (4)$$

[0074] 画素回路20に第3測定用電圧  $V_{m3}$  を書き込んだときの有機EL素子24のアノード—カソード間電圧を  $V_{om3}$ 、そのときの有機EL素子24の電流を  $Im3$ 、画素回路20に第4測定用電圧  $V_{m4}$  を書き込んだときの有機EL素子24のアノード—カソード間電圧を  $V_{om4}$ 、そのときの有機EL素子24の電流を  $Im4$  とする。式 (4) より、電圧  $V_{om3}$  と電流  $Im3$  の間には次式 (5a) が成立し、電圧  $V_{om4}$  と電流  $Im4$  の間には次式 (5b) が成立する。

$$Im3 = \beta_{0LED} (V_{om3} - V_{th_{0LED}}) \kappa \dots (5a)$$

$$Im4 = \beta_{0LED} (V_{om4} - V_{th_{0LED}}) \kappa \dots (5b)$$

[0075] 式 (5a)、(5b) を  $V_{th_{0LED}}$  と  $\beta_{0LED}$  について解くと、次式 (6a)、(6b) が得られる。

[数2]

$$V_{th\ OLED} = \frac{V_{om3} \sqrt{Im4} - V_{om4} \sqrt{Im3}}{\sqrt{Im4} - \sqrt{Im3}} \quad \dots \quad (6a)$$

$$\beta_{oLED} = \frac{(\sqrt{Im4} - V_{om3})^K}{(V_{om4} - V_{om3})^K} \quad \dots \quad (6b)$$

[0076] このように電流  $Im3$ 、 $Im4$  を測定し、式 (5a)、(5b) を解くことにより、有機EL素子24の閾値電圧  $V_{th\ OLED}$  とゲイン  $\beta_{oLED}$  を求め、有機EL素子24のI-V特性を求めることができる。閾値電圧  $V_{th\ OLED}$  はOL EDオフセット記憶部15cに書き込まれ、ゲイン  $\beta_{oLED}$  はOLEDゲイン記憶部15dに書き込まれる。

[0077] 図6は、映像信号VS1に対する補正処理のフローチャートである。補正部16は、映像信号VS1に含まれるコード値CV0に対して、トランジスタ21の閾値電圧  $V_{th\ TFT}$ 、トランジスタ21のゲイン  $\beta_{TFT}$ 、有機EL素子24の閾値電圧  $V_{th\ OLED}$  および、有機EL素子24のゲイン  $\beta_{oLED}$  を用いてトランジスタ21の動作領域に応じた補正を行う。以下の処理で用いられる閾値電圧  $V_{th\ TFT}$ 、 $V_{th\ OLED}$  およびゲイン  $\beta_{TFT}$ 、 $\beta_{oLED}$  は、補正データ記憶部15から読み出されたものである。

[0078] 補正部16は、まず、有機EL素子24の発光効率を補正する処理を行う(ステップS101)。具体的には、補正部16は、次式(7)に示す演算を行うことにより、補正後のコード値CV1を求める。

$$CV1 = CV0 \times \alpha \quad \dots \quad (7)$$

ただし、式(7)において、 $\alpha$ は画素回路20ごとに求めた発光効率補正係数を表す。有機EL素子24の発光効率が大きく低下している画素ほど、発光効率補正係数  $\alpha$  は大きな値を有する。なお、 $\alpha$ を計算で求めることもできる。

[0079] 次に、補正部16は、補正後のコード値CV1を有機EL素子24のアノード-カソード間電圧を表す電圧値  $V_{data1\ LED}$  に変換する(ステップS102)。ステップS102における変換は、例えば、予め用意したテーブ

ルを参照する方法や、演算器を用いて演算する方法で行われる。

[0080] 次に、補正部 16 は、電圧値  $V_{data1_{LED}}$  に対して次式 (8) に示す演算を行うことにより、補正後の電圧値  $V_{data2_{LED}}$  を求める (ステップS103)。

$$V_{data2_{LED}} = V_{data1_{LED}} \times B_{0_{LED}} + V_{th_{0_{LED}}} \quad \cdots (8)$$

ただし、有機EL素子 24 のゲインの初期値の平均値を  $\beta_{0_{0_{LED}}}$  としたとき、式 (8) に含まれる  $B_{0_{LED}}$  は次式 (9) で与えられる。

$$B_{0_{LED}} = (\beta_{0_{0_{LED}}} / \beta_{0_{LED}})^{1/K} \quad \cdots (9)$$

[0081] 次に、補正部 16 は、補正後のコード値  $CV_1$  をトランジスタ 21 のゲートソース間電圧を表す電圧値  $V_{data1_{TFT}}$  に変換する (ステップS104)。ステップS104における変換は、ステップS102における変換と同様の方法で行われる。

[0082] 次に、補正部 16 は、電圧値  $V_{data2_{LED}}$ 、 $V_{data1_{TFT}}$  に基づき、トランジスタ 21 を飽和領域と三極管領域のうちいずれの動作領域で動作させるかを決定する (ステップS105)。より詳細には、補正部 16 は、次式 (10) が成立するときには三極管領域と判断し、それ以外のときには飽和領域と判断する。

$$V_{ds} < V_{data1_{TFT}} \times B_{TFT} \quad \cdots (10)$$

ただし、トランジスタ 21 のゲインの初期値の平均値を  $\beta_{0_{TFT}}$  としたとき、式 (10) に含まれる  $B_{TFT}$  は次式 (11) で与えられる。また、式 (10) に含まれる  $V_{ds}$  は、次式 (12) で与えられる。

$$B_{TFT} = \sqrt{(\beta_{0_{TFT}} / \beta_{TFT})} \quad \cdots (11)$$

$$V_{ds} = ELVDD - ELVSS - V_{data2_{LED}} \quad \cdots (12)$$

補正部 16 は、飽和領域と判断したときにはステップS106へ進み、三極管領域と判断したときにはステップS107へ進む。

[0083] 補正部 16 は、ステップS106では、飽和領域用の補正式を用いて電圧値  $V_{data1_{TFT}}$  を補正する。より詳細には、補正部 16 は、電圧値  $V_{da}$

$V_{data1_{TFT}}$  に対して次式 (13) に示す演算を行うことにより、補正後の電圧値  $V_{data2_{TFT}}$  を求める。

$$\begin{aligned} V_{data2_{TFT}} \\ = V_{data1_{TFT}} \times B_{TFT} + V_{th_{TFT}} \cdots (13) \end{aligned}$$

[0084] 補正部 16 は、ステップ S 107 では、三極管領域用の補正式を用いて電圧値  $V_{data1_{TFT}}$  を補正する。より詳細には、補正部 16 は、電圧値  $V_{data1_{TFT}}$  に対して次式 (14) に示す演算を行うことにより、補正後の電圧値  $V_{data2_{TFT}}$  を求める。

$$\begin{aligned} V_{data2_{TFT}} = V_{data1_{TFT}}^2 \times B_{TFT}^2 / 2 V_{ds} \\ + V_{th_{TFT}} + V_{ds} / 2 \cdots (14) \end{aligned}$$

[0085] 補正部 16 は、ステップ S 106 または S 107 を実行した後に、ステップ S 108 へ進む。補正部 16 は、ステップ S 108 では、次式 (15) に従い、ステップ S 103 で求めた補正後の電圧値  $V_{data2_{LED}}$  と、ステップ S 106 または S 107 で求めた補正後の電圧値  $V_{data2_{TFT}}$  とを加算する。これにより、トランジスタ 21 のゲート端子に印加される電圧を表す電圧値  $V_{data}$  が得られる。

$$V_{data} = V_{data2_{TFT}} + V_{data2_{LED}} \cdots (15)$$

[0086] 最後に、補正部 16 は、電圧値  $V_{data}$  を出力コード値 CV に変換する (ステップ S 109)。ステップ S 109 における変換は、ステップ S 102、S 104 における変換と同様の方法で行われる。

[0087] このように補正部 16 は、映像信号 VS1 に含まれるコード値 CV0 に基づきトランジスタ 21 に印加される電圧  $V_{data1_{TFT}}$  と有機EL素子 24 に印加される電圧  $V_{data1_{LED}}$  とを求め、電圧  $V_{data1_{QLED}}$  に対して有機EL素子 24 の閾値電圧  $V_{th}$  謂とゲイン  $\beta_{QLED}$  を用いて補正を行い、電圧  $V_{data1_{TFT}}$  に対してトランジスタ 21 の閾値電圧  $V_{th_{TFT}}$  とゲイン  $\beta_{TFT}$  を用いてトランジスタ 21 の動作領域に応じた補正を行い、補正後の電圧  $V_{data2_{TFT}}$ 、 $V_{data2_{QLED}}$  の和に対応したコード値 CV を求める。また、補正部 16 は、電圧  $V_{data1_{LED}}$  を補正した後に、電圧  $V_{data1_{TFT}}$

と補正後の電圧  $V_{data2_{LED}}$  に基づき駆動トランジスタ 21 の動作領域を決定する。

[0088] 以下、本実施形態に係る表示装置 10 の効果を説明する。ここでは、比較例として、表示装置 10 と同じ構成を有し、駆動トランジスタが飽和領域のみで動作する表示装置を考える。図 7 は、比較例に係る表示装置の駆動トランジスタの I—V 特性図である。図 8 は、表示装置 10 の駆動トランジスタ(トランジスタ 21)の I—V 特性図である。図 7 および図 8 において、横軸は駆動トランジスタのドレイン—ソース間電圧  $V_{ds}$  を表し、縦軸は駆動トランジスタのドレイン電流  $I_d$  を表す。P1～P4 は、それぞれ、第 1～第 4 階調に対応した駆動トランジスタの動作点を表す。

[0089] 図 7 に示す  $V_{gs1} \sim V_{gs4}$  は、それぞれ、比較例に係る表示装置において、第 1～第 4 階調に対応したデータ電圧を駆動トランジスタのゲート端子に印加したときの駆動トランジスタのゲート—ソース間電圧を表す。駆動トランジスタのゲート—ソース間電圧が  $V_{gs1} \sim V_{gs4}$  のとき、有機 EL 素子のアノード—カソード間電圧は  $V_o1 \sim V_o4$  となり、駆動トランジスタのドレイン—ソース間電圧は  $V_{ds1} \sim V_{ds4}$  となる。電圧  $V_{ds1} \sim V_{ds4}$  はいずれもオーバードライブ電圧以上であるので、第 1～第 4 階調のときに駆動トランジスタは飽和領域で動作する。

[0090] 図 8 に示すように、表示装置 10 では、比較例に係る表示装置よりも電源電圧 (ELVDD—ELVSS) が小さく設定されている。図 8 に示す  $V_{gs1}$ 、 $V_{gs2}$ 、 $V_{gs3'}$ 、 $V_{gs4'}$  は、それぞれ、表示装置 10 において、第 1～第 4 階調に対応したデータ電圧を駆動トランジスタのゲート端子に印加したときの駆動トランジスタのゲート—ソース間電圧を表す。駆動トランジスタのゲート—ソース間電圧が  $V_{gs1}$ 、 $V_{gs2}$ 、 $V_{gs3'}$ 、 $V_{gs4'}$  のとき、有機 EL 素子のアノード—カソード間電圧は  $V_o1 \sim V_o4$  となり、駆動トランジスタのドレイン—ソース間電圧は  $V_{ds1} \sim V_{ds4}$  となる。電圧  $V_{ds1}$ 、 $V_{ds2}$  はオーバードライブ電圧以上であるのに対して、電圧  $V_{ds3}$ 、 $V_{ds4}$  はオーバードライブ電圧よりも低い。駆

動トランジスタは、第1および第2階調のときには飽和領域で動作し、第3および第4階調のときには三極管領域で動作する。

[0091] 本実施形態に係る表示装置10では、比較例に係る表示装置よりも電源電圧( $E_{LVD}\_E_{LVS}$ )が小さい。また、補正部16は、映像信号VS1に基づき、駆動トランジスタを飽和領域と三極管領域のうちいずれの動作領域で動作させるかを決定し、映像信号VS1に対して駆動トランジスタの動作領域に応じた補正を行う。したがって、表示装置10によれば、比較例に係る表示装置と同様に高画質の表示を行いながら、駆動トランジスタの消費電力を削減することができる。また、駆動トランジスタの発熱量を削減するので、発熱対策部品(ヒートシンクなど)を簡略化することができる。なお、駆動トランジスタが三極管領域で動作する階調の範囲は、駆動トランジスタの特性などを考慮して決定すればよい。

[0092] 表示装置10では、比較例に係る表示装置と比べて、第3および第4階調を表示するときの駆動トランジスタのゲートソース間電圧を高くする( $V_{gs3'} > V_{gs3}$ 、 $V_{gs4'} > V_{gs4}$ にする)必要がある。駆動トランジスタのゲートソース間電圧 $V_{gs}$ を高くすると、データ線駆動/電流測定回路14の消費電力が増加する。しかしながら、表示装置10では、データ線駆動/電流測定回路14の消費電力よりも、画素回路20の発光時の消費電力のほうが多い。また、電源電圧( $E_{LVD}\_E_{LVS}$ )が小さいほど、画素回路20の発光時の消費電力は小さくなる。したがって、データ線駆動/電流測定回路14における消費電力の増加分よりも多く画素回路20の発光時の消費電力を削減し、表示装置10の消費電力を削減することができる。

[0093] なお、一般に、データ線駆動回路の消費電力は、データ線に印加する電圧の振幅の2乗に比例して増加する。表示装置10では、駆動トランジスタが三極管領域で動作するときには駆動トランジスタのゲートソース間電圧を従来よりも高くするので、データ線駆動/電流測定回路14の消費電力は従来よりも増加する。また、表示装置10では、駆動トランジスタに印加され

る電圧と有機EL素子に印加される電圧の和をデータ電圧として使用する。

このため、データ線駆動/電流測定回路14における階調刻みは、駆動トランジスタに印加される電圧だけをデータ電圧として使用する場合と比べて大きくなる。階調刻みが小さい場合、駆動回路の分解能の制限によって階調反転が発生することがある。

[0094] これらの点を考慮すると、表示装置10では、駆動トランジスタのW/L比を大きく設計し、駆動トランジスタのゲインを大きくして、駆動トランジスタに印加される電圧を小さくすることが好ましい。例えば、駆動トランジスタのゲイン $\beta_{TFT}$ が有機EL素子24のゲイン $\beta_{LED}$ よりも大きくなるように、駆動トランジスタのサイズを決定することが好ましい。これにより、駆動回路の分解能の制限による階調反転を防止し、データ線駆動/電流測定回路14の消費電力の増加を抑制することができる。

[0095] 以上に示すように、本実施形態に係る表示装置10は、複数の走査線GA<sub>1</sub>～GA<sub>n</sub>、GB<sub>1</sub>～GB<sub>n</sub>と複数のデータ線S<sub>1</sub>～S<sub>m</sub>と2次元状に配置された複数の画素回路20とを含む表示部11と、走査線GA<sub>1</sub>～GA<sub>n</sub>、GB<sub>1</sub>～GB<sub>n</sub>を駆動する走査線駆動回路13と、データ線S<sub>1</sub>～S<sub>m</sub>を駆動するデータ線駆動回路(データ線駆動/電流測定回路14の一部)とを備えている。画素回路20は、電気光学素子(有機EL素子24)と、制御端子(ゲート端子)を有し、電気光学素子と直列に接続された駆動トランジスタ(トランジスタ21)とを含んでいる。駆動トランジスタは、データ線駆動回路を用いて制御端子に印加されたデータ電圧が第1範囲(トランジスタ21が飽和領域で動作するように決定された範囲)内にあるときは飽和領域で動作し、データ電圧が第2範囲(トランジスタ21が三極管領域で動作するように決定された範囲)内にあるときは三極管領域で動作する。したがつて、駆動トランジスタに供給される電源電圧を小さくし、低消費電力の表示装置を提供することができる。

[0096] また、表示装置10は、測定回路として、表示部11の外部に設けられ、画素回路20を流れる電流I<sub>m1</sub>～I<sub>m4</sub>を測定する電流測定回路(データ

線駆動/電流測定回路 14 の他の一部)を備え、電流測定回路で測定された電流  $I_{m1} \sim I_{m4}$  に基づき、データ線駆動回路に供給される映像信号  $V_S 1$  に対して補正を行う補正部 16 を備えている。補正部 16 は、映像信号  $V_S 1$  に基づき画素回路 20 ごとに駆動トランジスタを飽和領域と三極管領域のうちいずれの動作領域で動作させるかを決定し、映像信号  $V_S 1$  に対して駆動トランジスタの動作領域に応じた補正を行う。このように表示装置 10 では、映像信号  $V_S 1$  に基づき画素回路 20 ごとに駆動トランジスタの動作領域が決定され、映像信号  $V_S 1$  に対して駆動トランジスタの動作領域に応じた補正が行われる。したがって、駆動トランジスタを飽和領域のみで動作させるときと同様の補正を行いながら、駆動トランジスタに供給される電源電圧を小さくすることができる。これにより、高画質で低消費電力の表示装置を提供することができる。

[0097] また、補正部 16 は、電流測定回路で測定された電流  $I_{m1} \sim I_{m4}$  に基づき画素回路 20 ごとに駆動トランジスタと電気光学素子の特性を求め、映像信号  $V_S 1$  に対して駆動トランジスタと電気光学素子の特性を用いて駆動トランジスタの動作領域に応じた補正を行う。このように駆動トランジスタと電気光学素子の特性を画素回路 20 ごとに求め、これを用いて映像信号  $V_S 1$  を補正することにより、駆動トランジスタと電気光学素子の特性のばらつきや変動を補償し、高画質の表示を行うことができる。

[0098] また、補正部 16 は、映像信号  $V_S 1$  に含まれるコード値  $C_V 0$  に基づき駆動トランジスタに印加される第 1 電圧  $V_{data1_{TFT}}$  と電気光学素子に印加される第 2 電圧  $V_{data1_{LED}}$  とを求める(ステップ S 102、S 104)、第 2 電圧  $V_{data1_{LED}}$  に対して電気光学素子の特性(閾値電圧  $V_{th_{LED}}$  とゲイン  $\beta_{LED}$ )を用いて補正を行い、第 1 電圧  $V_{data1_{TFT}}$  に対して駆動トランジスタの特性(閾値電圧  $V_{th_{TFT}}$  とゲイン  $\beta_{TFT}$ )を用いて駆動トランジスタの動作領域に応じた補正を行い、補正後の第 1 電圧  $V_{data2_{TFT}}$  と補正後の第 2 電圧  $V_{data2_{LED}}$  の和に対応したコード値  $C_V$  を求める。このように映像信号  $V_S 1$  に含まれるコード値  $C_V 0$  に基づき駆動トランジス

タに印加される電圧  $V_{data1_{TFT}}$  と電気光学素子に印加される電圧  $V_{data1_{LED}}$  とを求める、前者の電圧に対して駆動トランジスタの動作領域に応じた補正を行うことができる。

[0099] また、補正部 16 は、第 2 電圧  $V_{data1_{LED}}$  を補正した後に、第 1 電圧  $V_{data1_{TFT}}$  と補正後の第 2 電圧  $V_{data2_{LED}}$  とに基づき駆動トランジスタの動作領域を決定する。このように電気光学素子に印加される電圧を補正した結果  $V_{data2_{LED}}$  に基づき駆動トランジスタの動作領域を決定することにより、駆動トランジスタの動作領域を好適に決定することができる。

[0100] また、電流測定回路は、画素回路 20 に複数の測定用電圧（第 1 および第 2 測定用電圧  $V_{m1}$ 、 $V_{m2}$ ）を切り替えて書き込んだときに駆動トランジスタを流れる電流  $I_{m1}$ 、 $I_{m2}$  と、画素回路 20 に他の複数の測定用電圧（第 3 および第 4 の測定電圧  $V_{m3}$ 、 $V_{m4}$ ）を切り替えて書き込んだときに電気光学素子を流れる電流  $I_{m3}$ 、 $I_{m4}$  とを測定する。補正部 16 は、電流測定回路で測定された電流  $I_{m1} \sim I_{m4}$  に基づき、画素回路 20 ごとに駆動トランジスタの閾値電圧  $V_{th_{TFT}}$  およびゲイン  $\beta_{TFT}$ 、並びに、電気光学素子の閾値電圧  $V_{th_{LED}}$  およびゲイン  $\beta_{LED}$  を求める。このように測定用電圧を書き込んだときに駆動トランジスタや電気光学素子を流れる電流を測定し、測定結果に基づき駆動トランジスタと電気光学素子の閾値電圧とゲインを求めることにより、駆動トランジスタと電気光学素子の  $I-V$  特性を求めることができる。駆動トランジスタと電気光学素子の閾値電圧とゲインを用いて映像信号  $V_S 1$  を補正することにより、高画質の表示を行うことができる。

[0101] また、画素回路 20 は、データ線  $S_j$  に接続された第 1 導通端子、駆動トランジスタの制御端子に接続された第 2 導通端子、および、走査線  $G A 1 \sim G A_n$ 、 $G B 1 \sim G B_n$  のうち第 1 走査線  $G A_i$  に接続された制御端子を有する書き込み制御トランジスタ 22 と、データ線  $S_j$  に接続された第 1 導通端子、駆動トランジスタと電気光学素子の接続点に接続された第 2 導通端子、および、走査線  $G A 1 \sim G A_n$ 、 $G B 1 \sim G B_n$  のうち第 2 走査線  $G B_i$

に接続された制御端子を有する読み出し制御トランジスタ23とを含んでいる。電流測定回路は、データ線Sjに接続され、画素回路20とデータ線Sjを流れる電流を測定する。このように画素回路20を流れる電流をデータ線Sjに接続された電流測定回路を用いて測定することができる。

[01 02] (第1の実施形態の変形例)

第1の実施形態に係る表示装置10では、トランジスタ21の動作領域が切り替えられるので、高画質の表示を行うために電源電圧を一定に保つことが特に要求される。例えば、表示部11を含む表示パネルの陰極に印加されるロー・レベル電源電圧ELVSSが、配線における電圧降下によって変動し、白に近い画面を表示するときと黒に近い画面を表示するときとで異なる場合には、表示画面が不安定になることがある。

[01 03] 図9は、第1の実施形態の変形例に係る表示装置の電源供給回路の構成を示す図である。図9には、表示パネル51内の画素回路(図示せず)にロー・レベル電源電圧ELVSSを供給する回路が記載されている。表示パネル51には、すべての画素回路(図示せず)に共通する陰極52と、ロー・レベル電源電圧ELVSSを供給するためのパッド53が設けられる。表示パネル51の外部には、オペアンプ54が設けられる。オペアンプ54の非反転入力端子には、ロー・レベル電源電圧ELVSSが印加される。オペアンプ54の反転入力端子は、フィードバック線55を介して陰極52に接続される。オペアンプ54の出力端子は、パッド53に接続される。

[01 04] 陰極52にロー・レベル電源電圧ELVSSを印加する場合、陰極52の電圧は、パッド53と陰極52を接続する配線の抵抗R1、および、陰極52自身の抵抗によって低下する。陰極52の抵抗は抵抗R1よりも小さいので、ロー・レベル電源電圧ELVSSが低下する主な原因は抵抗R1である。図9において、フィードバック線55は高いインピーダンスを有するので、フィードバック線55には電流がほとんど流れない。このため、陰極52の電圧を正確に帰還しながらオペアンプ54の出力電圧を陰極52に印加することができる。したがって、表示画面の状態にかかわらず陰極52の電圧を一

定に保ち、トランジスタ21の動作領域を切り替える場合に表示画面が不安定になることを防止することができる。

[01 05] 以上に示すように、本変形例に係る表示装置では、表示部は、画素回路に電源電圧（ロー レベル電源電圧 E L V S S）を供給する電源電極（陰極 52）を含んでいる。表示装置は、電源電圧が印加された非反転入力端子、電源電極に接続された反転入力端子、および、電源電極に接続された出力端子を有するオペアンプ54を備えている。このようにオペアンプ54を用いて電源電圧を安定化させることにより、駆動トランジスタの動作領域を切り替える場合でも、電源電圧の変動によって表示画面が不安定になることを防止することができる。

[01 06] なお、図9では、画素回路にロー レベル電源電圧 E L V S S を供給する陰極52にオペアンプ54を設けることとしたが、画素回路にハイレベル電源電圧 E L V D D を供給する陽極に同様の方法でオペアンプを設けてもよい。

[01 07] (第2の実施形態)

第1の実施形態では、図2に示す画素回路20を備えた表示装置において、駆動トランジスタを飽和領域と三極管領域の両方で動作させる場合について説明した。他の画素回路を備えた表示装置でも、駆動トランジスタを飽和領域と三極管領域の両方で動作させてもよい。第2および第3の実施形態では、他の画素回路を備えた表示装置の例を説明する。

[01 08] 図10は、本発明の第2の実施形態に係る表示装置の画素回路の回路図である。図10には、「i行」列目の画素回路60が記載されている。図10に示すように、「i行」列目の画素回路60は、トランジスタ61～63、有機EL素子64、および、コンデンサ65を含み、走査線G<sub>i</sub>、データ線S<sub>j</sub>、および、モニタ線M<sub>j</sub>に接続される。トランジスタ61～63は、Nチャネル型TFTである。画素回路60は、国際公開第2007/90287号の図22に記載されたものと同じである。

[01 09] トランジスタ61のドレイン端子には、ハイレベル電源電圧 E L V D D が印加される。トランジスタ61のソース端子は、有機EL素子64のアノ-

ト端子に接続される。有機EL素子64のカソード端子には、ロー レベル電源電圧ELVSSが印加される。トランジスタ62の一方の導通端子(図10では左側の端子)はデータ線Sjに接続され、トランジスタ62の他方の導通端子はトランジスタ61のゲート端子に接続される。トランジスタ63の一方の導通端子(図10では右側の端子)はモニタ線Mjに接続され、トランジスタ63の他方の導通端子はトランジスタ61のソース端子と有機EL素子64のアノード端子に接続される。トランジスタ62、63のゲート端子は、走査線Giに接続される。コンデンサ65は、トランジスタ61のゲート端子とソース端子の間に設けられる。トランジスタ61～63は、それぞれ、駆動トランジスタ、書き込み制御トランジスタ、および、読み出し制御トランジスタとして機能する。

[01 10] 本実施形態に係る表示装置は、第1の実施形態に係る表示装置10と同様の構成を有する(図1を参照)。ただし、本実施形態に係る表示装置の表示部は、n本の走査線G1～Gn、m本のデータ線S1～Sm、m本のモニタ線M1～Mm、および、(m×n)個の画素回路60を含んでいる。また、本実施形態に係る表示装置は、データ線駆動/電流測定回路14に代えて、データ線駆動回路と電流測定回路を別個に備えている。データ線駆動回路は、データ線S1～Smに接続され、制御信号CS2と映像信号VS2に基づきデータ線S1～Smを駆動する。電流測定回路は、モニタ線M1～Mmに接続され、画素回路60とモニタ線Mjに流れる電流を測定する。

[01 11] 以下、走査線Gi上の信号を走査信号Giという。書き込み時には、走査信号Giがハイレベルになり、データ線Sjには「i行」列目の画素回路60に書き込むべきデータ電圧Vdata(i,j)が印加される(図11を参照)。駆動トランジスタの特性検出時には、走査信号Giがハイレベルになり、データ線Sjとモニタ線Mjには第1または第2測定用電圧Vm1、Vm2として、トランジスタ61がオンし、有機EL素子64に電流が流れないような電圧が印加される。有機EL素子の特性検出時には、走査信号Giがハイレベルになり、データ線Sjとモニタ線Mjには第3または第4測定

用電圧  $V_{m3}$ 、 $V_{m4}$  として、トランジスタ 6 1 がオフし、有機 EL 素子 6 4 に電流が流れるような電圧が印加される。

[01 12] 本実施形態に係る表示装置でも、第 1 の実施形態と同様に、補正部（図示せず）は、映像信号  $V_{S1}$  に基づき画素回路 6 0 ごとにトランジスタ 6 1 を飽和領域と三極管領域のうちいずれの動作領域で動作させるかを決定し、映像信号  $V_{S1}$  に対してトランジスタ 6 1 の動作領域に応じた補正を行う。ただし、本実施形態に係る表示装置では、駆動トランジスタの特性検出時および有機 EL 素子の特性検出時に、トランジスタ 6 3 がオンし、有機 EL 素子 6 4 のアノード端子の電圧は、モニタ線  $M_j$  に印加される電圧にリセットされる。このため、本実施形態に係る表示装置の補正部は、図 6 に示す補正処理において、ステップ S 10 8 に代えて、ステップ S 10 6 または S 10 7 で求めた補正後の電圧値  $V_{data2_{TF}}$  をそのまま電圧値  $V_{data}$  とするステップを実行すればよい。

[01 13] 以上に示すように、本実施形態に係る表示装置では、表示部は複数のモニタ線  $M_1 \sim M_m$  を含んでいる。画素回路 6 0 は、データ線  $S_j$  に接続された第 1 導通端子、駆動トランジスタ（トランジスタ 6 1）の制御端子（ゲート端子）に接続された第 2 導通端子、および、走査線  $G_i$  に接続された制御端子を有する書き込み制御トランジスタ 6 2 と、モニタ線  $M_j$  に接続された第 1 導通端子、駆動トランジスタと電気光学素子（有機 EL 素子 6 4）の接続点に接続された第 2 導通端子、および、走査線  $G_i$  に接続された制御端子を有する読み出し制御トランジスタ 6 3 を含んでいる。電流測定回路は、モニタ線  $M_1 \sim M_m$  に接続され、画素回路 6 0 とモニタ線  $M_j$  を流れる電流を測定する。このように画素回路 6 0 を流れる電流をモニタ線  $M_j$  に接続された電流測定回路を用いて測定し、第 1 の実施形態に係る表示装置 10 と同様の効果を奏すことができる。

[01 14] （第 3 の実施形態）

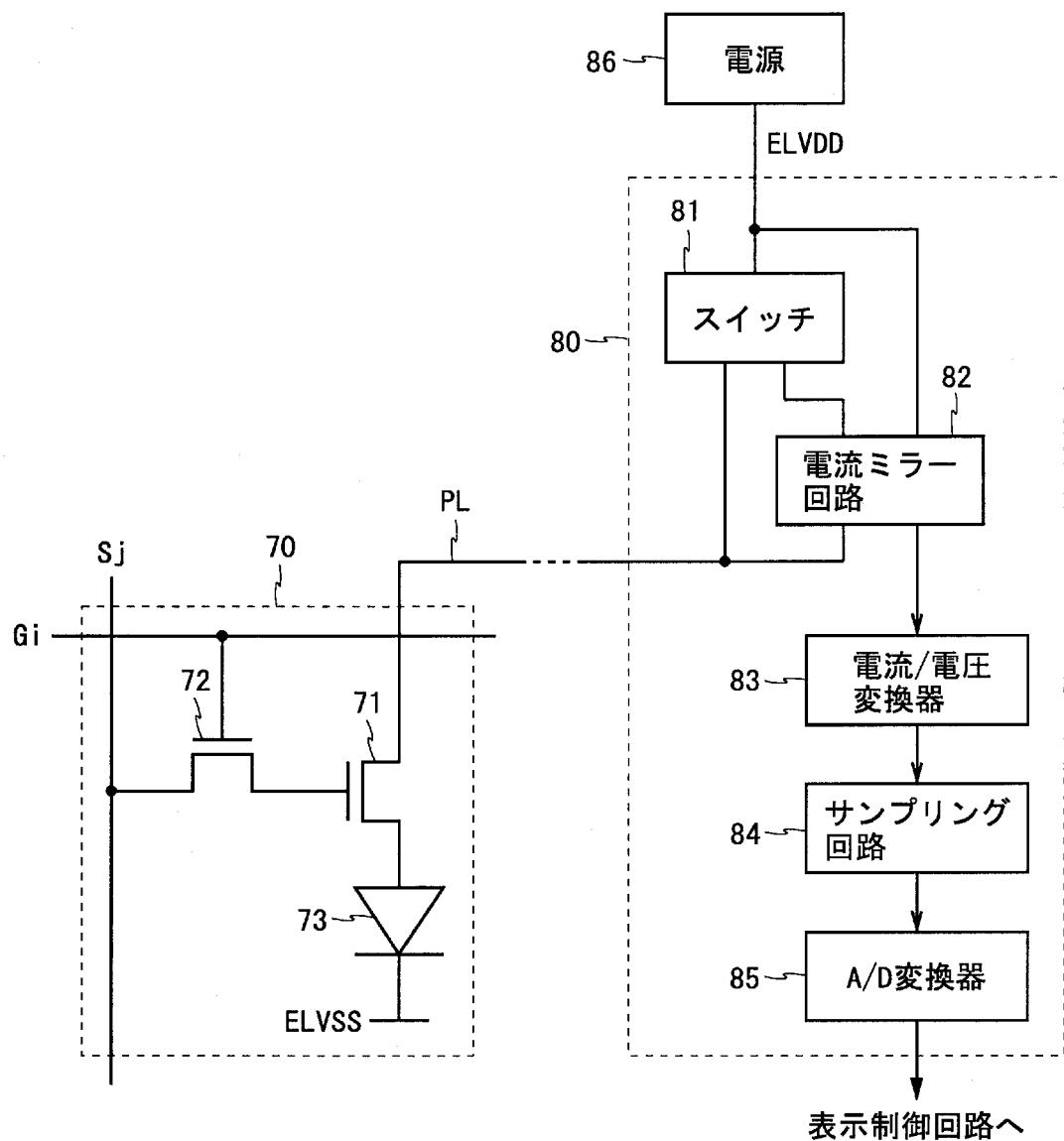

図 12 は、本発明の第 3 の実施形態に係る表示装置の画素回路と電流測定回路を示す図である。図 12 には、「 $i$  行」列目の画素回路 7 0 と電流測定回

路 8 0 が記載されている。図 12 に示す回路は、国際公開第 2010/10

1761 号の図 2 および図 3 に記載された回路から一部の構成要素を省略したものである。

[0115] 図 12 に示すように、「行」列目の画素回路 7 0 は、トランジスタ 7 1、7 2 と有機 EL 素子 7 3 を含み、走査線 G i とデータ線 S j に接続される。トランジスタ 7 1、7 2 は、N チャネル型 TFT である。トランジスタ 7 1 のドレイン端子は、ハイレベル電源電圧 EL V DD を供給する電源線 P L に接続される。トランジスタ 7 1 のソース端子は、有機 EL 素子 7 3 のアノード端子に接続される。有機 EL 素子 7 3 のカソード端子には、ローレベル電源電圧 EL V SS が印加される。トランジスタ 7 2 の一方の導通端子（図 1 2 では左側の端子）はデータ線 S j に接続され、トランジスタ 7 2 の他方の導通端子はトランジスタ 7 1 のゲート端子に接続される。トランジスタ 7 2 のゲート端子は、走査線 G i に接続される。トランジスタ 7 1、7 2 は、それぞれ、駆動トランジスタ、および、書き込み制御トランジスタとして機能する。

[0116] 本実施形態に係る表示装置は、第 1 の実施形態に係る表示装置 1 0 と同様の構成を有する（図 1 を参照）。ただし、本実施形態に係る表示装置の表示部は、n 本の走査線 G 1～G n、m 本のデータ線 S 1～S m、および、（m × n）個の画素回路 7 0 を含んでいる。本実施形態に係る表示装置は、データ線駆動/電流測定回路 1 4 に代えて、データ線駆動回路（図示せず）と電流測定回路 8 0 を別個に備えている。データ線駆動回路は、データ線 S 1～S m に接続され、制御信号 CS 2 と映像信号 VS 2 に基づきデータ線 S 1～S m を駆動する。電流測定回路 8 0 は、電源線 P L に接続され、画素回路 7 0 と電源線 P L に流れる電流を測定する。

[0117] 図 12 に示すように、電流測定回路 8 0 は、スイッチ 8 1、電流ミラー回路 8 2、電流/電圧変換器 8 3、サンプリング回路 8 4、および、A/D 変換器 8 5 を含んでいる。電流測定回路 8 0 には、電源 8 6 からハイレベル電源電圧 EL V DD が供給される。スイッチ 8 1 は、電流測定時以外には電源

線 PL にハイレベル電源電圧 E L V D D を直接印加し、電流測定時には電源線 PL にハイレベル電源電圧 E L V D D を電流ミラー回路 8 2 を介して印加する。

[01 18] 電流ミラー回路 8 2 は、電流測定時に電源線 PL と画素回路 7 0 を流れる電流と同じ量のミラー電流を電流/電圧変換器 8 3 に対して出力する。電流/電圧変換器 8 3 は、電流ミラー回路 8 2 から出力されたミラー電流を電圧に変化する。サンプリング回路 8 4 は、電流/電圧変換器 8 3 の出力信号をサンプリングする。サンプリング回路 8 4 は、例えば、2 個のサンプルホールド回路とオペアンプを含み、相関 2 重サンプリング法を用いて電流/電圧変換器 8 3 の出力信号をサンプリングする。八/D 変換器 8 5 は、サンプリング回路 8 4 の出力信号（アナログ信号）をデジタル信号に変化する。A/D 変換器 8 5 で求めたデジタル信号は、表示制御回路に対して出力される。

[01 19] トランジスタ 7 1 のゲート端子に十分に高い電圧を印加したとき、トランジスタ 7 1 の抵抗は有機 EL 素子 7 3 の抵抗と比べて無視できる程度に小さくなる。したがって、トランジスタ 7 1 のゲート端子に十分に高い電圧を印加したときに測定された電流に基づき、有機 EL 素子 7 3 の特性を求めることができる。また、トランジスタ 7 1 のゲート端子にトランジスタ 7 1 が飽和領域で動作する電圧を印加したときに測定された電流に基づき、トランジスタ 7 1 の特性と有機 EL 素子 7 3 の特性とを加算した特性（以下、合計特性という）を求めることができる。測定した電流に基づく有機 EL 素子 7 3 の特性を合計特性から減算することにより、トランジスタ 7 1 の特性を求めることができる。

[01 20] なお、有機 EL 素子 7 3 の特性の変化がトランジスタ 7 1 の特性の変化と比べて十分に小さい場合には、有機 EL 紴子 7 3 の特性は固定と考えてもよい。この場合、予め固定的に定めた有機 EL 紴子 7 3 の特性を合計特性から減算することにより、トランジスタ 7 1 の特性を求めることができる。

[01 21] 本実施形態に係る表示装置でも、第 1 の実施形態と同様に、補正部（図示せず）は、映像信号 V S 1 に基づき画素回路 7 0 ごとにトランジスタ 7 1 を

飽和領域と三極管領域のうちいずれの動作領域で動作させるかを決定し、映像信号V S 1に対してトランジスタ7 1の動作領域に応じた補正を行う。

[01 22] 以上に示すように、本実施形態に係る表示装置では、表示部は電源線P Lを含んでいる。画素回路7 0は、データ線S jに接続された第1導通端子、駆動トランジスタ(トランジスタ7 1)の制御端子(ゲート端子)に接続された第2導通端子、および、走査線G iに接続された制御端子を有する書き込み制御トランジスタ7 2を含んでいる。駆動トランジスタの第1導通端子は、電源線P Lに接続されている。電流測定回路8 0は、電源線P Lに接続され、画素回路7 0と電源線P Lを流れる電流を測定する。このように画素回路7 0を流れる電流を電源線P Lに接続された電流測定回路8 0を用いて測定し、第1の実施形態に係る表示装置1 0と同様の効果を奏することができる。

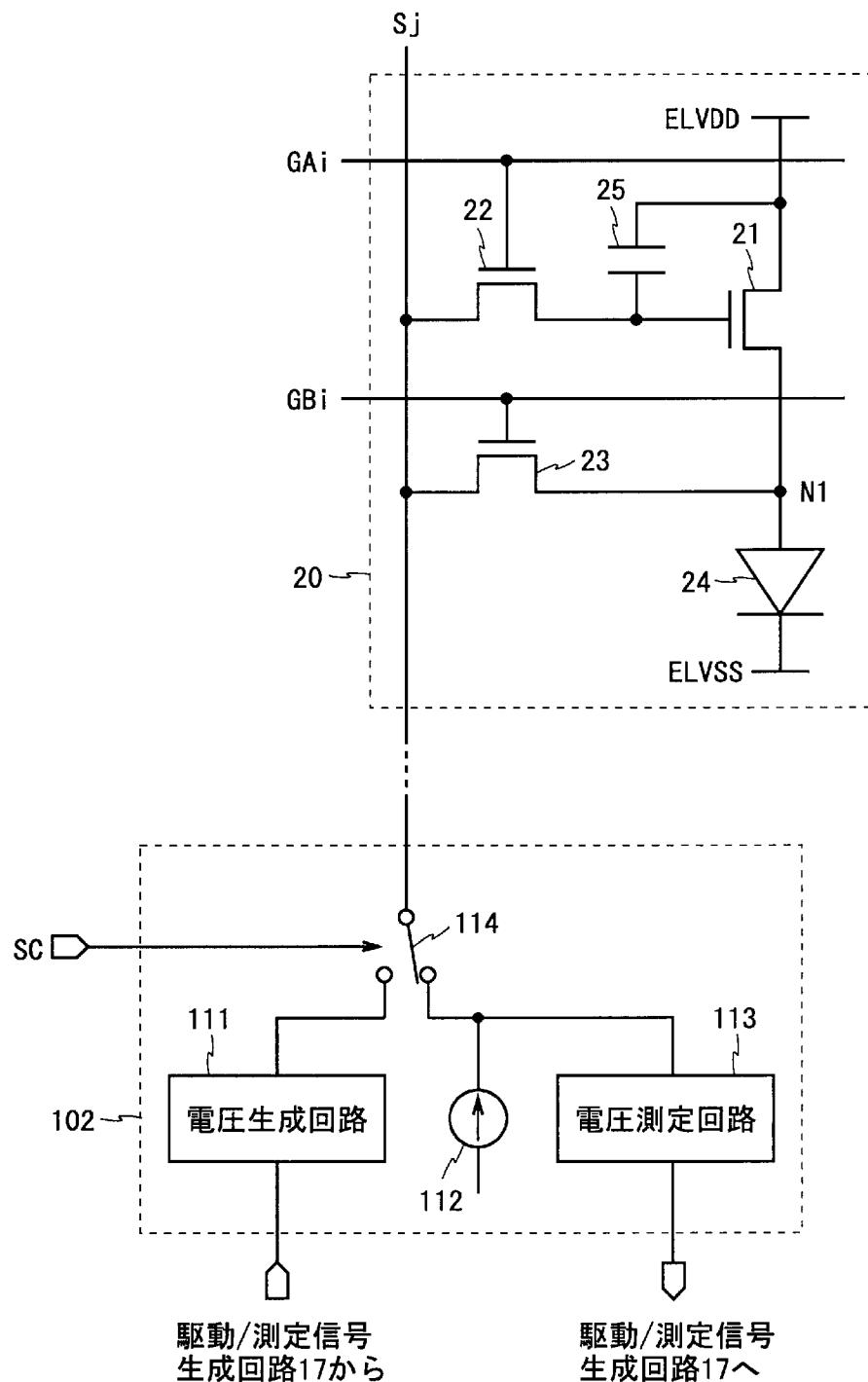

[01 23] (第4の実施形態)

本発明の第4の実施形態に係る表示装置は、第1の実施形態に係る表示装置1 0に電源電圧のレベルを制御する機能を追加したものである。図13は、本発明の第4の実施形態に係る表示装置の電源供給回路の構成を示すプロック図である。なお、図13では、本実施形態の特徴を理解するために必要な構成要素は省略されている。

[01 24] 図13において、可変電源9 3は、画素回路2 0にハイレベル電源電圧E L V D Dを供給する電源である。可変電源9 4は、画素回路2 0にローレベル電源電圧E L V S Sを供給する電源である。可変電源9 3、9 4の出力電圧のレベルは、それぞれ、表示制御回路9 1から出力される制御信号P S 1、P S 2に応じて変化する。

[01 25] 表示制御回路9 1は、第1の実施形態に係る表示制御回路1 2に電源制御部9 2を追加したものである。電源制御部9 2は、制御信号P S 1、P S 2を出力することにより、最大階調のときにデータ線駆動回路の出力振幅が最大となるように、ハイレベル電源電圧E L V D Dとローレベル電源電圧E L V S Sを制御する。また、電源制御部9 2は、ユーザによる明るさ設定や表

示画像の特徴などに応じて、電源電圧 (E L V D D—E L V S S) が小さくなるように、ハイレベル電源電圧 E L V D D とローレベル電源電圧 E L V S S を制御する。例えば、ユーザが画面を暗くすることを選択した場合、電源制御部 9 2 は、ハイレベル電源電圧 E L V D D を低くするか、ローレベル電源電圧 E L V S S を高くするか、あるいは、その両方を行うことにより、電源電圧 (E L V D D—E L V S S) を小さくする。また、静止画を表示しているときに、静止画に含まれる最大階調が表示装置が表示可能な最大階調よりも低い場合にも、電源制御部 9 2 は、同様の方法で電源電圧 (E L V D D—E L V S S) を小さくする。

[01 26] 以上に示すように、本実施形態に係る表示装置は、画素回路 2 0 に供給される電源電圧のレベルを制御する電源制御部 9 2 を備えている。本実施形態に係る表示装置によれば、駆動トランジスタ (トランジスタ 2 1) に供給される電源電圧 (E L V D D—E L V S S) を状況に応じて小さくすることにより、表示装置の消費電力をさらに削減することができる。

[01 27] (第 5 の実施形態)

第 1 ～ 第 4 の実施形態では、画素回路について電流を測定する電流測定回路を備えた表示装置について説明した。第 5 の実施形態では、画素回路について電圧を測定する電圧測定回路を備えた表示装置について説明する。

[01 28] 図 14 は、本発明の第 5 の実施形態に係る表示装置の構成を示すプロック図である。図 14 に示す表示装置 10 0 は、第 5 の実施形態に係る表示装置 10 (図 1) において、データ線駆動/電流測定回路 14 をデータ線駆動/電圧測定回路 (データ線駆動回路と電圧測定回路の兼用回路) 10 1 に置換したものである。データ線駆動/電圧測定回路 10 1 は、駆動/測定信号生成回路 17、および、m 個の出力/測定回路 10 2 を含んでいる。

[01 29] 図 15 は、画素回路 2 0 と出力/測定回路 10 2 の構成を示す図である。図 15 には、「*i* 行」*j* 列目の画素回路 2 0 と、データ線 S<sub>j</sub> に対応した出力/測定回路 10 2 とが記載されている。画素回路 2 0 の構成は、第 1 の実施形態と同じである。以下、トランジスタ 2 1 のソース端子と有機 E L 素子 2 4

のアノード端子が接続された節点をN1という。

- [0130] 出力/測定回路102は、電圧生成回路111、電流源112、電圧測定回路113、および、スイッチ114を含んでいる。スイッチ114の一端は、データ線Sjに接続される。スイッチ114は、スイッチ制御信号SCに従い、データ線Sjを電圧生成回路111に接続するか、電流源112と電圧測定回路113に接続するかを切り替える。

- [0131] 電圧生成回路111は、駆動/測定信号生成回路17から出力されたデジタルデータに基づきデータ電圧を出力するか、リファレンス電圧を出力する。データ線Sjが電圧生成回路111に接続されているとき、電圧生成回路111から出力されたデータ電圧またはリファレンス電圧はデータ線Sjに印加される。データ線Sjが電流源112と電圧測定回路113に接続されているとき、電流源112はデータ線Sjに対して所定量の電流を流し、電圧測定回路113はそのときのデータ線Sjの電圧を測定する。

- [0132] 映像信号VS1を補正して映像信号VS2を求めるために、データ線駆動/電圧測定回路101は、各画素回路20について4種類の電圧を測定する。より詳細には、各画素回路20内のトランジスタ21の特性を求めるために、データ線駆動/電圧測定回路101は、画素回路20にトランジスタ21がオンするリファレンス電圧を書き込み、電流源112から第1測定用電流In1を流したときの節点N1の電圧Vn1と、画素回路20にトランジスタ21がオンする電圧を書き込み、電流源112から第2測定用電流In2(>In1)を流したときの節点N2の電圧Vn2と、画素回路20にトランジスタ21がオフする電圧を書き込み、電流源112から第3測定用電流In3を流したときの節点N1の電圧Vn3と、画素回路20にトランジスタ21がオフする電圧を書き込み、電流源112から第4測定用電流In4を流したときの節点N2の電圧Vn4とを測定する。

- [0133] 走査線駆動回路13とデータ線駆動/電圧測定回路101は、1行分の画素回路20に対する書き込み処理と、1行分の画素回路20について4種類の電圧Vn1～Vn4のうちいずれかを測定する処理とを行う。例えば、走

査線駆動回路 13 とデータ線駆動/電圧測定回路 101 は、連続した 4 フレーム期間のうち、第 1 ～ 第 4 フレーム期間内の i 番目のライン期間では i 行目の画素回路 20 について電圧  $V_{n1} \sim V_{n4}$  をそれぞれ測定し、それ以外のライン期間では 1 行分の画素回路 20 に対する書き込み処理を行ってもよい。

- [0134] 補正部 16 は、測定された 4 種類の電圧  $V_{n1} \sim V_{n4}$  に基づき、トランジスタ 21 と有機 EL 素子 24 の特性を求める処理を行い、求めた 2 種類の特性に基づき映像信号 VS1 を補正する。より詳細には、補正部 16 は、2 種類の電圧  $V_{n1}$ 、 $V_{n2}$  に基づき、トランジスタ 21 の特性として閾値電圧とゲインを求め、2 種類の電圧  $V_{n3}$ 、 $V_{n4}$  に基づき、有機 EL 素子 24 の特性として閾値電圧とゲインを求める。トランジスタ 21 の閾値電圧とゲイン、および、有機 EL 素子 24 の閾値電圧とゲインを求める方法は、第 1 の実施形態と同様である。補正部 16 は、求めた閾値電圧とゲインを補正データ記憶部 15 に書き込み、補正データ記憶部 15 から読み出した閾値電圧とゲインを用いて映像信号 VS1 を補正する。

- [0135] 以上に示すように、本実施形態に係る表示装置 100 は、測定回路として電流測定回路に代えて、表示部 11 の外部に設けられ、画素回路 20 内の節点 N1 の電圧  $V_{n1} \sim V_{n4}$  を測定する電圧測定回路 113 を備え、電圧測定回路 113 で測定された電圧  $V_{n1} \sim V_{n4}$  に基づき、データ線駆動回路（データ線駆動/電圧測定回路 101）に供給される映像信号 VS1 に対して補正を行う補正部 16 を備えている。

- [0136] また、電圧測定回路 113 は、画素回路 20 に複数の測定用電流（第 1 および第 2 測定用電流  $I_{n1}$ 、 $I_{n2}$ ）を切り替えて流したときの駆動トランジスタの一方の導通端子（トランジスタ 21 のソース端子）の電圧  $V_{n1}$ 、 $V_{n2}$  と、画素回路 20 に他の複数の測定用電流（第 3 および第 4 の測定電流  $I_{n3}$ 、 $I_{n4}$ ）を切り替えて流したときの電気光学素子の一方の端子（有機 EL 素子 24 のアノード端子）の電圧  $V_{n3}$ 、 $V_{n4}$  とを測定する。補正部 16 は、電圧測定回路 113 で測定された電圧  $V_{n1} \sim V_{n4}$  に基づき

、画素回路 20 ごとに駆動トランジスタの閾値電圧  $V_{t-h_{TF}}$  およびゲイン  $\beta_{TF}$   $\tau$  、並びに、電気光学素子の閾値電圧  $V_{t-h_{LED}}$  およびゲイン  $\beta_{LED}$  を求める。

[0137] また、画素回路 20 は、データ線  $S_j$  に接続された第 1 導通端子、駆動トランジスタの制御端子に接続された第 2 導通端子、および、走査線  $GA_1 \sim GA_n$ 、 $GB_1 \sim GB_n$  のうち第 1 走査線  $GA_i$  に接続された制御端子を有する書き込み制御トランジスタ 22 と、データ線  $S_j$  に接続された第 1 導通端子、駆動トランジスタと電気光学素子の接続点に接続された第 2 導通端子、および、走査線  $GA_1 \sim GA_n$ 、 $GB_1 \sim GB_n$  のうち第 2 走査線  $GB_i$  に接続された制御端子を有する読み出し制御トランジスタ 23 を含んでいる。電圧測定回路 113 は、データ線  $S_j$  に接続され、駆動トランジスタと電気光学素子の接続点（トランジスタ 21 と有機 EL 素子 24 の接続点）の電圧を測定する。

[0138] 本実施形態に係る表示装置 100 によれば、第 1 の実施形態に係る表示装置 10 と同様の効果を奏すことができる。

[0139] なお、ここまで第 1 ～ 第 5 の実施形態およびその変形例に係る表示装置を説明してきたが、ここまでに説明した表示装置の特徴をその性質に反しない限り任意に組み合わせて、各種の変形例に係る表示装置を構成することができる。例えば、第 2 および第 3 の実施形態に係る表示装置に対して図 9 および図 13 に示す電源供給回路を設けてもよい。

[0140] 以上に示すように、本発明の表示装置によれば、駆動トランジスタを飽和領域と三極管領域の両方で動作させることにより、駆動トランジスタに供給される電源電圧を小さくし、表示装置の消費電力を削減することができる。また、映像信号に基づき画素回路ごとに駆動トランジスタの動作領域を決定し、映像信号に対して駆動トランジスタの動作領域に応じた補正を行うことにより、駆動トランジスタを飽和領域のみで動作させるときと同様の補正を行いながら、駆動トランジスタに供給される電源電圧を小さくし、高画質で低消費電力の表示装置を提供することができる。

## 産業上の利用可能性

[0141] 本発明の表示装置は、高画質で低消費電力であるという特徴を有するので、有機EL表示装置など、電気光学素子を含む画素回路を備えた各種の表示装置に利用することができる。

#### 符号の説明

[0142] 10、100…表示装置

11…●表示部

12、91…表示制御回路

13…●走査線駆動回路

14…●データ線駆動／電流測定回路

15…●補正データ記憶部

16…●補正部

17…●駆動／測定信号生成回路

20、60、70…画素回路

21、61、71…トランジスタ（駆動トランジスタ）

22、62、72…トランジスタ（書き込み制御トランジスタ）

23、63…トランジスタ（読み出し制御トランジスタ）

24、64、73…有機EL素子（電気光学素子）

25、32、65…コンデンサ

30、102…出力／測定回路

31、54…オペアンプ

33～35、114…スイッチ

40…●信号変換回路

51…表示パネル

52…●陰極

80…●電流測定回路

92…●電源制御部

101…●データ線駆動／電圧測定回路

111…電圧生成回路

1 1 2 …電流源

1 1 3 …電圧測定回路

G A 1 ~ G A n 、 G B 1 ~ G B n …走査線

S 1 ~ S m …データ線

M j …モニタ線

P L …電源線

## 請求の範囲

- [請求項1] アクティブマトリクス型の表示装置であつて、

複数の走査線と複数のデータ線と2次元状に配置された複数の画素

回路とを含む表示部と、

前記走査線を駆動する走査線駆動回路と、

前記データ線を駆動するデータ線駆動回路とを備え、

前記画素回路は、電気光学素子と、制御端子を有し、前記電気光学

素子と直列に接続された駆動トランジスタとを含み、

前記駆動トランジスタは、前記データ線駆動回路を用いて前記制御

端子に印加されたデータ電圧が第1範囲内にあるときは飽和領域で動

作し、前記データ電圧が第2範囲内にあるときは三極管領域で動作す

ることを特徴とする、表示装置。

- [請求項2] 前記表示部の外部に設けられ、前記画素回路について電流または電

圧を測定する測定回路と、

前記測定回路で測定された電流または電圧に基づき、前記データ線

駆動回路に供給される映像信号に対して補正を行う補正部とをさらに

備え、

前記補正部は、前記映像信号に基づき前記画素回路ごとに前記駆動

トランジスタを飽和領域および三極管領域のうちいずれの動作領域で

動作させるかを決定し、前記映像信号に対して前記駆動トランジスタ

の動作領域に応じた補正を行うことを特徴とする、請求項1に記載の

表示装置。

- [請求項3] 前記補正部は、前記測定回路で測定された電流または電圧に基づき

前記画素回路ごとに前記駆動トランジスタと前記電気光学素子の特性

を求め、前記映像信号に対して前記駆動トランジスタと前記電気光学

素子の特性を用いて前記駆動トランジスタの動作領域に応じた補正を

を行うことを特徴とする、請求項2に記載の表示装置。

- [請求項4] 前記補正部は、前記映像信号に含まれるコード値に基づき前記駆動

トランジスタに印加される第1電圧と前記電気光学素子に印加される第2電圧とを求める、前記第2電圧に対して前記電気光学素子の特性を用いて補正を行い、前記第1電圧に対して前記駆動トランジスタの特性を用いて前記駆動トランジスタの動作領域に応じた補正を行い、補正後の第1電圧と補正後の第2電圧の和に対応したコード値を求めることを特徴とする、請求項3に記載の表示装置。

[請求項5] 前記補正部は、前記第2電圧を補正した後に、前記第1電圧と前記補正後の第2電圧とに基づき前記駆動トランジスタの動作領域を決定することを特徴とする、請求項4に記載の表示装置。

[請求項6] 前記表示部は、前記画素回路に電源電圧を供給する電源電極をさらに含み、

前記電源電圧が印加された非反転入力端子、前記電源電極に接続された反転入力端子、および、前記電源電極に接続された出力端子を有するオペアンプをさらに備えた、請求項2に記載の表示装置。

[請求項7] 前記画素回路に供給される電源電圧のレベルを制御する電源制御部をさらに備えた、請求項2に記載の表示装置。

[請求項8] 前記測定回路は、前記画素回路を流れる電流を測定する電流測定回路であることを特徴とする、請求項2に記載の表示装置。

[請求項9] 前記電流測定回路は、前記画素回路に複数の測定用電圧を切り替えて書き込んだときに前記駆動トランジスタを流れる電流と、前記画素回路に他の複数の測定用電圧を切り替えて書き込んだときに前記電気光学素子を流れる電流とを測定し、

前記補正部は、前記電流測定回路で測定された電流に基づき、前記画素回路ごとに前記駆動トランジスタの閾値電圧およびゲイン、並びに、前記電気光学素子の閾値電圧およびゲインを求めることが特徴とする、請求項8に記載の表示装置。

[請求項10] 前記画素回路は、

前記データ線に接続された第1導通端子、前記駆動トランジスタ

の制御端子に接続された第2導通端子、および、前記走査線のうち第1走査線に接続された制御端子を有する書き込み制御トランジスタと、

前記データ線に接続された第1導通端子、前記駆動トランジスタと前記電気光学素子の接続点に接続された第2導通端子、および、前記走査線のうち第2走査線に接続された制御端子を有する読み出し制御トランジスタとをさらに含み、

前記電流測定回路は、前記データ線に接続され、前記画素回路と前記データ線を流れる電流を測定することを特徴とする、請求項8に記載の表示装置。

[請求項11]

前記表示部は複数のモニタ線をさらに含み、

前記画素回路は、

前記データ線に接続された第1導通端子、前記駆動トランジスタの制御端子に接続された第2導通端子、および、前記走査線に接続された制御端子を有する書き込み制御トランジスタと、

前記モニタ線に接続された第1導通端子、前記駆動トランジスタと前記電気光学素子の接続点に接続された第2導通端子、および、前記走査線に接続された制御端子を有する読み出し制御トランジスタとをさらに含み、

前記電流測定回路は、前記モニタ線に接続され、前記画素回路と前記モニタ線を流れる電流を測定することを特徴とする、請求項8に記載の表示装置。

[請求項12]

前記表示部は電源線を含み、

前記画素回路は、前記データ線に接続された第1導通端子、前記駆動トランジスタの制御端子に接続された第2導通端子、および、前記走査線に接続された制御端子を有する書き込み制御トランジスタをさらに含み、

前記駆動トランジスタの第1導通端子は前記電源線に接続され、

前記電流測定回路は、前記電源線に接続され、前記画素回路と前記電源線を流れる電流を測定することを特徴とする、請求項8に記載の表示装置。

[請求項13] 前記測定回路は、前記画素回路内の節点の電圧を測定する電圧測定回路であることを特徴とする、請求項2に記載の表示装置。

[請求項14] 前記電圧測定回路は、前記駆動トランジスタに複数の測定用電流を切り替えて流したときの前記駆動トランジスタの一方の導通端子の電圧と、前記電気光学素子に他の複数の測定用電流を切り替えて流したときの前記電気光学素子の一方の端子の電圧とを測定し、

前記補正部は、前記電圧測定回路で測定された電圧に基づき、前記画素回路ごとに前記駆動トランジスタの閾値電圧およびゲイン、並びに、前記電気光学素子の閾値電圧およびゲインを求めるることを特徴とする、請求項13に記載の表示装置。

[請求項15] 前記画素回路は、

前記データ線に接続された第1導通端子、前記駆動トランジスタの制御端子に接続された第2導通端子、および、前記走査線のうち第1走査線に接続された制御端子を有する書き込み制御トランジスタと、

前記データ線に接続された第1導通端子、前記駆動トランジスタと前記電気光学素子の接続点に接続された第2導通端子、および、前記走査線のうち第2走査線に接続された制御端子を有する読み出し制御トランジスタとをさらに含み、

前記電圧測定回路は、前記データ線に接続され、前記駆動トランジスタと前記電気光学素子の接続点の電圧を測定することを特徴とする、請求項14に記載の表示装置。

[請求項16] 複数の走査線と複数のデータ線と2次元状に配置された複数の画素回路とを含む表示部を有するアクティブラリックス型の表示装置の駆動方法であって、

前記走査線を駆動するステップと、

前記データ線を駆動するステップとを備え、

前記画素回路は、電気光学素子と、制御端子を有し、前記電気光学

素子と直列に接続された駆動トランジスタとを含み、

前記駆動トランジスタは、前記データ線を駆動するステップにおいて前記制御端子に印加されたデータ電圧が第1範囲内にあるときは飽和領域で動作し、前記データ電圧が第2範囲内にあるときは三極管領域で動作することを特徴とする、表示装置の駆動方法。

[請求項 17] 前記表示部の外部において、前記画素回路について電流または電圧

を測定するステップと、

測定された電流または電圧に基づき、前記データ線の駆動に用いられる

映像信号に対して補正を行うステップとをさらに備え、

前記補正を行うステップは、前記映像信号に基づき前記画素回路ごとに前記駆動トランジスタを飽和領域および三極管領域のうちいずれの動作領域で動作させるかを決定し、前記映像信号に対して前記駆動トランジスタの動作領域に応じた補正を行うことを特徴とする、請求

項 16 に記載の表示装置の駆動方法。

[図1]

[図2]

[図3]

[図4]

[図5]

[図6]

[図7]

[図8]

[図9]

[図10]

[図11]

[図12]

[図13]

[図14]

[図15]

## INTERNATIONAL

## SEARCH REPORT

International application No.

PCT / JP2 016 / 053154

## A. CLASSIFICATION OF SUBJECT MATTER

G09G3/0 (2006.01)i, G09G3/2 0 (2006.01)i, H01L51/50 (2006.01)i

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G 0 9G3 / 3 0 , G 0 9G3 / 2 0 , H 0 1L5 1 / 5 0

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

|         |         |        |           |           |        |         |        |           |           |

|---------|---------|--------|-----------|-----------|--------|---------|--------|-----------|-----------|

| Jitsuyo | Shinan  | Koho   | 1922-1996 | Jitsuyo   | Shinan | Toroku  | Koho   | 1996-2016 |           |

| Kokai   | Jitsuyo | Shinan | Koho      | 1971-2016 | Toroku | Jitsuyo | Shinan | Koho      | 1994-2016 |

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                       | Relevant to claim No.                    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| X         | J P 2 0 0 7 - 5 3 6 5 8 5 A (Thoms on Licensing) ,<br>1 3 D e cember 2 0 0 7 (1 3 . 1 2 . 2 0 0 7) ,                                                                                                                                     | 1 - 5 , 7 - 8 , 1 0 ,<br>1 3 , 1 6 - 1 7 |

| Y         | paragraphs [0 0 3 1] to [0 0 4 1] ; fig . 4 to 1 2<br>& U S 2 0 0 8 / 0 0 3 0 4 3 8 A I<br>paragraphs [0 0 4 4] to [0 0 5 4] ; fig . 4 to 1 2<br>& W O 2 0 0 5 / 1 0 9 3 8 9 A I & DE 1 0 2 0 0 4 0 2 2 4 2 4 A<br>& C N 1 9 7 7 3 0 2 A | 6 , 9 , 1 1 - 1 2 ,<br>1 4 - 1 5         |

| X         | J P 2 0 0 5 - 3 0 0 9 2 9 A (Sanyo Electric Co . , Ltd .) ,                                                                                                                                                                              | 1 , 1 6                                  |

| Y         | 2 7 October 2 0 0 5 (2 7 . 1 0 . 2 0 0 5) ,<br>paragraphs [0 0 1 4] to [0 0 6 5] ; fig . 1 to 4<br>(Family : none )                                                                                                                      | 2 , 6 - 8 , 1 0 - 1 2 ,<br>1 7           |

| X         | J P 2 0 0 7 - 3 1 6 3 5 6 A (Sony Corp .) ,                                                                                                                                                                                              | 1 , 1 6                                  |

| Y         | 0 6 D e cember 2 0 0 7 (0 6 . 1 2 . 2 0 0 7) ,<br>paragraph [0 0 2 2] ; fig . 5<br>(Family : none )                                                                                                                                      | 2 , 6 - 8 , 1 0 - 1 2 ,<br>1 7           |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents:

"A" document defining the general state of the art which is not considered to be of particular relevance

"E" earlier application or patent but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or other means

"P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&amp;" document member of the same patent family

Date of the actual completion of the international search

2 8 March 2 0 1 6 (2 8 . 0 3 . 1 6)Date of mailing of the international search report

0 5 April 2 0 1 6 (0 5 . 0 4 . 1 6)Name and mailing address of the ISA/

Japan Patent Office

3 - 4 - 3 , Kasumigaseki , Chiyoda-ku ,

Tokyo 1 0 0 - 8 9 1 5 , JapanAuthorized officer

Telephone No.

## INTERNATIONAL SEARCH REPORT

International application No.

PCT / JP2 016 / 053154

## C (Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                 | Relevant to claim No. |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Y         | JP 2010- 281874 A (Cas i o Computer Co . , Ltd . ),<br>16 December 2010 (16.12.2010),<br>paragraphs [0041] to [0069]; fig . 6 to 10<br>(Fami ly: none )                                                                            | 2, 6- , 1 -12,<br>17  |

| Y         | JP 11- 316366 A (Hoshiden Firippusu Di splay<br>Kabushi ki Kai sha ),<br>16 November 1999 (16.11.1999),<br>paragraphs [0016] to [0022]; fig . 1<br>(Fami ly: none )                                                                | 6                     |

| Y         | JP 2011- 169992 A (Cas i o Computer Co . , Ltd . ),<br>01 September 2011 (01.09.2011),<br>paragraphs [0047] to [0094]; fig . 4 to 6<br>(Fami ly: none )                                                                            | 6                     |

| Y         | WO 2010/ 001590 AI (Panas oni c Corp . ),<br>07 January 2010 (07.01.2010),<br>paragraph [0017]<br>& US 2010/ 0214273 AI<br>paragraph [0020]<br>& CN 101960509 A & KR 10- 2011- 0023846 A<br>& JP 5010030 B                         | 9, 14-15              |

| Y         | JP 2009- 8799 A (Sharp Corp . ),<br>15 January 2009 (15.01.2009),<br>paragraphs [0040] to [0064]; fig . 1 to 4<br>(Fami ly: none )                                                                                                 | 11                    |

| Y         | JP 2002- 341825 A (Sharp Corp . ),<br>29 November 2002 (29.11.2002),<br>paragraphs [0025] to [0029]; fig . 1 to 2<br>& US 2003/ 0011314 AI<br>paragraphs [0072] to [0076]; fig . 1 to 2<br>& KR 10- 2002- 0087856 A & CN 1385826 A | 12                    |

| P, A      | WO 2015/ 093097 AI (Sharp Corp . ),<br>25 June 2015 (25.06.2015),<br>ent ire text ; all drawings<br>& TW 201525966 A                                                                                                               | 2-15, 17              |

## A. 発明の属する分野の分類 (国際特許分類 (IPC))

Int.Cl. G09G3/30 (2006. 01) i, G09G3/20 (2006. 01) i, H01L51/50 (2006. 01) i

## B. 調査を行った分野

## 調査を行った最小限資料 (国際特許分類 (IPC))

Int.Cl. G09G3/30, G09G3/20, H01L51/50

## 最小限資料以外の資料で調査を行った分野に含まれるもの

|             |         |

|-------------|---------|

| 日本国実用新案公報   | 1922-19 |

| 日本国公開実用新案公報 | 1971-20 |

| 日本国実用新案登録公報 | 1996-20 |

| 日本国登録実用新案公報 | 1994-20 |

国際調査で使用した電子データベース (データベースの名称、調査に使用した用語)

年

## C. 関連すると認められる文献

| 引用文献の<br>カテゴリ一* | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                         | 関連する<br>請求項の番号                 |

|-----------------|-----------------------------------------------------------------------------------------------------------|--------------------------------|

| X               | JP 2007-536585 A (トムソン ライセンシング) 2007. 12. 13,<br>段落 [0031] — [0041], [図4] — [図12]                         | 1-5, 7-8, 10,<br>13, 16-17     |

| Y               | & US 2008/0030438 A1, [0044] - [0054], 図4 — 図12<br>& WO 2005/109389 A1 & DE 102004022424 A & CN 1977302 A | 6, 9, 11-12, 14<br>-15         |

| X               | JP 2005-300929 A (三洋電機株式会社) 2005. 10. 27,<br>段落 [0014] — [0065], [図1] — [図4]<br>(ファミリーなし)                 | 1, 16<br>2, 6-8, 10-12<br>, 17 |

| Y               |                                                                                                           |                                |

\* c 欄の続きにも文献が列挙されている。

「：パテントファミリーに関する別紙を参照。」

## \* 引用文献のカテゴリ一

「」特に関連のある文献ではなく、一般的技術水準を示すもの

「」国際出願日前の出願または特許であるが、国際出願日以後に公表されたもの

「」優先権主張に疑義を提起する文献又は他の文献の発行日若しくは他の特別な理由を確立するために引用する文献 (理由を付す)

「」口頭による開示、使用、展示等に言及する文献

「」国際出願日前で、かつ優先権の主張の基礎となる出願

## の日の後に公表された文献

「」国際出願日又は優先日後に公表された文献であって出願と矛盾するものではなく、発明の原理又は理論の理解のために引用するもの

「」特に関連のある文献であって、当該文献のみで発明の新規性又は進歩性がないと考えられるもの

「」特に関連のある文献であって、当該文献と他の1以上の文献との、当業者にとって自明である組合せによって進歩性がないと考えられるもの

& 同一パテントファミリー文献

|                                                                         |                                                                   |

|-------------------------------------------------------------------------|-------------------------------------------------------------------|

| 国際調査を完了した日<br>28.03.2016                                                | 国際調査報告の発送日<br>05.04.2016                                          |

| 国際調査機関の名称及びあて先<br>日本国特許庁 (ISA/JP)<br>郵便番号 100-8915<br>東京都千代田区霞が関三丁目4番3号 | 特許庁審査官 (権限のある職員)<br>西島 篤宏<br>電話番号 03-3581-1101 内線 3226<br>2G 9308 |

| c (続き) . 関連すると認められる文献 |                                                                                                                                                                         |                        |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 引用文献の<br>カテゴリー        | 引用文献名 及び一部の箇所が関連するときは、その関連する箇所の表示                                                                                                                                       | 関連する<br>請求項の番号         |

| X                     | JP 2007-316356 A (ソニー株式会社) 2007. 12. 06,<br>段落 [0022], [図5] (ファミリーなし)                                                                                                   | 1, 16                  |

| Y                     | JP 2010-281874 A (カシオ計算機株式会社) 2010. 12. 16,<br>段落 [0041] — [0069], [図6] — [図10]<br>(ファミリーなし)                                                                            | 2, 6-8, 10-12,<br>, 17 |

| Y                     | JP 11-316366 A (ホシデン・フィリップス・ディスプレイ株式会社)<br>1999. 11. 16, 段落 [0016] — [0022], [図1]<br>(ファミリーなし)                                                                          | 6                      |

| Y                     | JP 2011-169992 A (カシオ計算機株式会社) 2011. 09. 01,<br>段落 [0047] — [0094], [図4] — [図6]<br>(ファミリーなし)                                                                             | 6                      |

| Y                     | WO 2010/001590 A1 (パナソニック株式会社) 2010. 01. 07,<br>段落 [0017] & US 2010/0214273 A1, [0020]<br>& CN 101960509 A & KR 10-2011-0023846 A & JP 5010030 B                        | 9, 14-15               |

| Y                     | JP 2009-8799 A (シャープ株式会社) 2009. 01. 15,<br>段落 [0040] — [0064], [図1] — [図4]<br>(ファミリーなし)                                                                                 | 11                     |

| Y                     | JP 2002-341825 A (シャープ株式会社) 2002. 11. 29,<br>段落 [0025] — [0029], [図1] — [図2]<br>& US 2003/0011314 A1, [0072] - [0076], 図1 — 図2<br>& KR 10-2002-0087856 A & CN 1385826 A | 12                     |

| P, A                  | WO 2015/093097 A1 (シャープ株式会社) 2015. 06. 25, 全文, 全図<br>& TW 201525966 A                                                                                                   | 2-15, 17               |