(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-238323

(P2010-238323A)

(43) 公開日 平成22年10月21日(2010.10.21)

| (51) Int.Cl.                  | F 1          | テーマコード (参考) |

|-------------------------------|--------------|-------------|

| <b>G 11 C 19/28</b> (2006.01) | G 11 C 19/28 | D 5 C 080   |

| <b>G 11 C 19/00</b> (2006.01) | G 11 C 19/00 | J 5 C 380   |

| <b>G 09 G 3/20</b> (2006.01)  | G 09 G 3/20  | 6 1 1 A     |

| <b>G 09 G 3/30</b> (2006.01)  | G 09 G 3/20  | 6 7 0 E     |

|                               | G 09 G 3/20  | 6 7 0 J     |

審査請求 未請求 請求項の数 6 O L (全 17 頁) 最終頁に続く

|           |                            |            |                                                                              |

|-----------|----------------------------|------------|------------------------------------------------------------------------------|

| (21) 出願番号 | 特願2009-87287 (P2009-87287) | (71) 出願人   | 000001443<br>カシオ計算機株式会社<br>東京都渋谷区本町1丁目6番2号                                   |

| (22) 出願日  | 平成21年3月31日 (2009.3.31)     | (74) 代理人   | 100095407<br>弁理士 木村 满                                                        |

|           |                            | (72) 発明者   | 山本 卓己<br>東京都八王子市石川町2951番地の5<br>カシオ計算機株式会社八王子技術センター<br>内                      |

|           |                            | F ターム (参考) | 5C080 AA06 AA10 BB05 DD09 DD19<br>DD26 EE29 FF11 FF12 HH10<br>JJ02 JJ03 JJ04 |

|           |                            |            |                                                                              |

最終頁に続く

(54) 【発明の名称】シフトレジスタ及び電子機器

## (57) 【要約】

【課題】シフトレジスタの消費電力を削減するとともに、動作を安定させる。

【解決手段】トランジスタ T13 ~ T16 によって、ノード A の電位 V<sub>a</sub> を反転させてノード B の電位 V<sub>b</sub> とするインバータ INV が構成される。前段のシフト回路から HIGH レベルの入力信号 IN (k) が供給されると、ノード A の電位 V<sub>a</sub> は HIGH レベルとなり、トランジスタ T13 がオンして、ノード B の電位 V<sub>b</sub> は LOW レベルとなる。電流は、電圧 V<sub>HI</sub> のラインから、トランジスタ T14, T15, T13 を経由して、電圧 V<sub>LOW</sub> のアノードライン La へと流れる。電圧 V<sub>HI</sub> が印加される第 2 の端子 P2 とノード B 間の電圧はトランジスタ T14, T15 によって分圧されて、各トランジスタのバイアス電圧が分圧される。従って、第 2 の端子 P2 とノード B 間の抵抗の増加によってインバータ INV に流れる貫通電流が低減されて消費電力が削減されるとともに、トランジスタ T14, T15 の閾値電圧のシフトが抑制されて、シフト回路 21\_k の動作が安定する。

【選択図】図 3

## 【特許請求の範囲】

## 【請求項 1】

縦続接続された複数のシフト回路からなる複数段のシフトレジスタであって、前記各シフト回路は、

前段の出力信号が入力信号として供給される入力端子と、次段の出力信号がリセット信号として供給されるリセット端子と、第1のノードと、を有し、前記入力端子に前記入力信号が供給されたときに前記第1のノードの電位を前記入力信号のレベルに従った電位に設定する入力回路と、

第2のノードと、第1の端子と、第2の端子と、を有し、前記第1のノードの電位が供給され、前記第2のノードの電位を、前記第1のノードの電位を反転した電位とするインバータ回路と、

前記出力信号を出力する出力端子と、第1のクロック信号が供給される第3の端子と、を有し、前記第1のノードの電位と前記第2のノードの電位とが供給され、前記出力信号の電位を、前記第1のクロック信号に基づく電位とする出力回路と、を備え、

前記インバータ回路は、

前記第1の端子と前記第2のノードとの間に電流路が接続され、制御端子に前記第1のノードの電位が供給される第1のトランジスタと、電流路の一端が前記第2のノードに接続される第2のトランジスタと、電流路の一端が前記第2のトランジスタの前記電流路の他端に接続され、電流路の他端が前記第2の端子又は前記第3の端子のいずれか一方に接続される第3のトランジスタと、を備えた、

ことを特徴とするシフトレジスタ。

## 【請求項 2】

前記第2のトランジスタは制御端子が該第2のトランジスタの電流路の他端に接続され、前記第3のトランジスタは制御端子が該第3のトランジスタの電流路の他端に接続されていることを特徴とする請求項1に記載のシフトレジスタ。

## 【請求項 3】

前記インバータ回路は、電流路の一端が前記第2のノードに接続され、前記電流路の他端が前記第2の端子に接続され、制御端子に前記リセット信号が供給されて、前記第2のノードの電位を制御する第4のトランジスタを備えた、

ことを特徴とする請求項1又は2に記載のシフトレジスタ。

## 【請求項 4】

前記第1の端子は一定の基準電位に設定され、前記第2の端子には前記基準電位より高い電位を有する一定の電圧が供給されていることを特徴とする請求項3に記載のシフトレジスタ。

## 【請求項 5】

前記第2の端子には、前記第1のクロック信号に対して逆相の第2のクロック信号が供給されていることを特徴とする請求項3に記載のシフトレジスタ。

## 【請求項 6】

発光素子を備えて行列配置された複数の画素回路と、

請求項1乃至5のいずれか1項に記載のシフトレジスタを含み、当該シフトレジスタに含まれる各シフト回路の出力信号を、行を選択する行選択信号として各行毎に供給し、前記複数の画素回路を行毎に選択する行選択ドライバを備えた、

ことを特徴とする電子機器。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、シフトレジスタ及びこれを備えてなる電子機器に関するものである。

## 【背景技術】

## 【0002】

10

20

30

40

50

電子機器として、TFTを利用したゲートドライバ用シフトレジスタによって、有機EL素子やLCDをアクティブ駆動し、表示する表示装置が開発されている（例えば、特許文献1参照）。

【0003】

具体的には、アクティブ駆動型の表示装置は、行毎に配列された各画素をスイッチする画素回路を選択するゲートドライバを備え、このゲートドライバには、通常、シフトレジスタ回路が用いられる。

【0004】

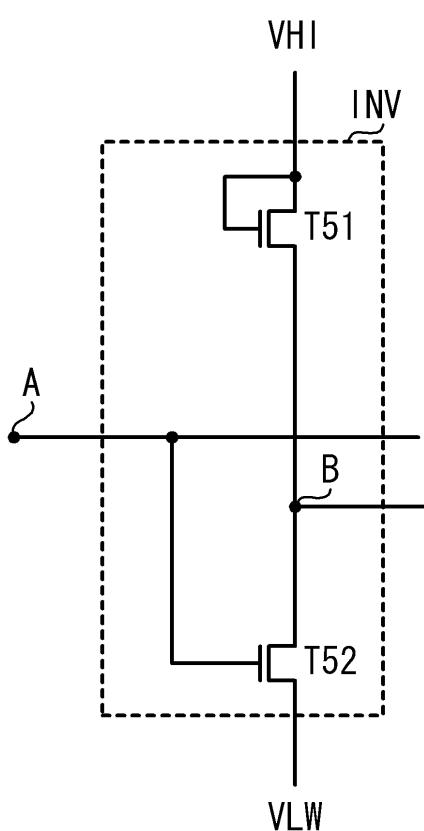

このシフトレジスタ回路は、例えば、各段に、図10に示すようなインバータINVを備えたシフト回路を有し、複数のシフト回路が直列接続されることによって構成される。

10

【0005】

このインバータINVは、トランジスタT51, T52によって構成される。トランジスタT51, T52は、nチャンネル型のFET（Field Effect Transistor；電界効果トランジスタ）によって構成されたポリシリコンまたはアモルファスシリコン薄膜トランジスタ（TFT；Thin Film Transistor）である。

【0006】

インバータINVは、ノードAの電位を反転させ、反転させた電位をノードBの電位とする。

【先行技術文献】

【特許文献】

20

【0007】

【特許文献1】特開2001-052494号公報（第5頁、図4, 5）

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかし、従来のシフト回路では、トランジスタT51, T52がTFTによって構成されているため、インバータINVにHiレベルの入力信号が供給される入力期間と出力期間において、トランジスタT51, T52には、比較的大きなバイアス電圧が印加される。

【0009】

このため、電圧VHIの電源から、このトランジスタT51, T52を経由して電圧VLWの電源に、貫通電流として大きな電流量の電流が流れる。このため、消費電力が増大する。

30

【0010】

また、トランジスタT51, T52は、ゲート-ソース間への電圧印加により経時劣化して、閾値電圧が次第に高くなることが知られている。また、ドレイン-ソース間に過大な電流が流れると、上記の経時劣化が促進されることも知られている。

【0011】

ここで、トランジスタT51が経時劣化して閾値電圧が高くなると、非選択期間において本来HiレベルとなるべきノードBの電圧が低下して、このインバータINVに接続される回路の動作が不安定になってしまう。

40

【0012】

本発明は、このような従来の問題点に鑑みてなされたもので、消費電力を削減するとともに、動作を安定させることが可能なシフトレジスタ及び電子機器を提供することを目的とする。

【課題を解決するための手段】

【0013】

この目的を達成するため、本発明の第1の観点に係るシフトレジスタは、縦続接続された複数のシフト回路からなる複数段のシフトレジスタであって、前記各シフト回路は、

50

前段の出力信号が入力信号として供給される入力端子と、次段の出力信号がリセット信号として供給されるリセット端子と、第1のノードと、を有し、前記入力端子に前記入力信号が供給されたときに前記第1のノードの電位を前記入力信号のレベルに従った電位に設定する入力回路と、

第2のノードと、第1の端子と、第2の端子と、を有し、前記第1のノードの電位が供給され、前記第2のノードの電位を、前記第1のノードの電位を反転した電位とするインバータ回路と、

前記出力信号を出力する出力端子と、第1のクロック信号が供給される第3の端子と、を有し、前記第1のノードの電位と前記第2のノードの電位とが供給され、前記出力信号の電位を、前記第1のクロック信号に基づく電位とする出力回路と、を備え、

前記インバータ回路は、

前記第1の端子と前記第2のノードとの間に電流路が接続され、制御端子に前記第1のノードの電位が供給される第1のトランジスタと、電流路の一端が前記第2のノードに接続される第2のトランジスタと、電流路の一端が前記第2のトランジスタの前記電流路の他端に接続され、電流路の他端が前記第2の端子又は前記第3の端子のいずれか一方に接続される第3のトランジスタと、を備えたことを特徴とする。

#### 【0014】

前記第2のトランジスタは制御端子が該第2のトランジスタの電流路の他端に接続され、前記第3のトランジスタは制御端子が該第3のトランジスタの電流路の他端に接続されてもよい。

#### 【0015】

前記インバータ回路は、電流路の一端が前記第2のノードに接続され、前記電流路の他端が前記第2の端子に接続され、制御端子に前記リセット信号が供給されて、前記第2のノードの電位を制御する第4のトランジスタを備えたものであってもよい。

#### 【0016】

前記第1の端子は一定の基準電位に設定され、前記第2の端子には前記基準電位より高い電位を有する一定の電圧が供給されていてもよい。

#### 【0017】

前記第2の端子には、前記第1のクロック信号に対して逆相の第2のクロック信号が供給されてもよい。

#### 【0018】

本発明の第2の観点に係る電子機器は、

発光素子を備えて行列配置された複数の画素回路と、

上述のシフトレジスタを含み、当該シフトレジスタに含まれる各シフト回路の出力信号を、行を選択する行選択信号として各行毎に供給し、前記複数の画素回路を行毎に選択する行選択ドライバを備えたことを特徴とする。

#### 【発明の効果】

#### 【0019】

本発明によれば、シフトレジスタにおいて、消費電力を削減するとともに、動作を安定させることができる。

#### 【図面の簡単な説明】

#### 【0020】

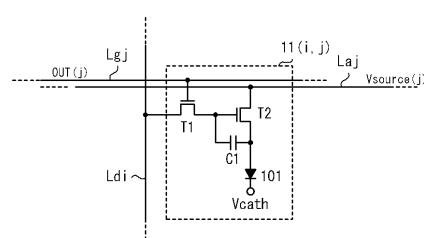

【図1】本発明の第1の実施形態に係る表示装置の構成を示す図であり、(a)は、表示装置の全体構成を示すブロック図であり、(b)は、各画素回路の構成を示す回路図である。

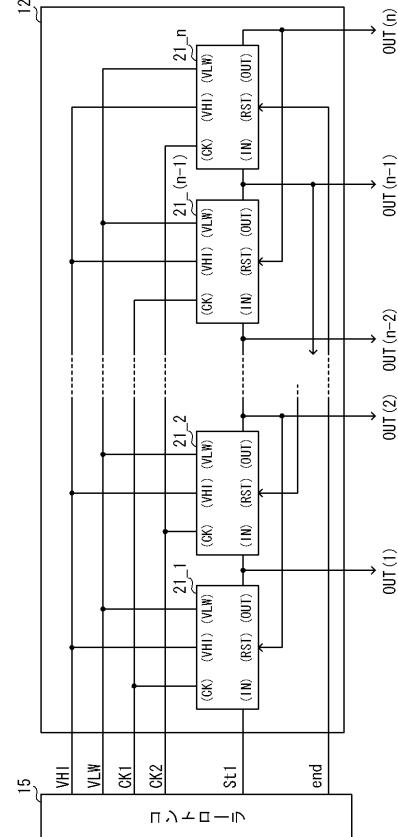

【図2】図1に示すゲートドライバにおけるシフトレジスタの構成を示す図である。

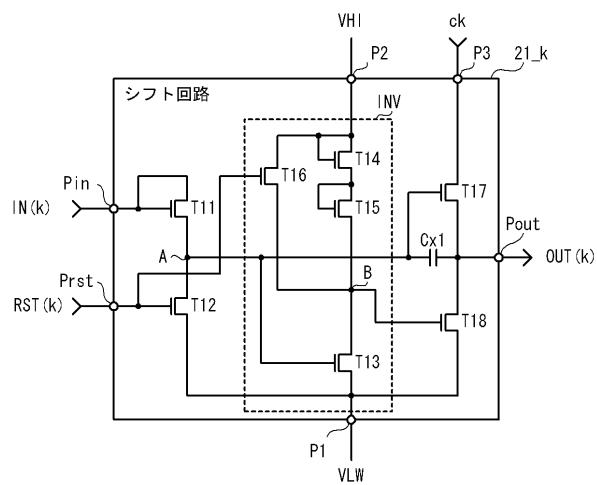

【図3】図2に示す各シフト回路の構成を示す回路図である。

【図4】第1の実施形態に係るシフト回路及びシフトレジスタの動作を説明するためのタイミングチャートである。

【図5】本発明の第2の実施形態に係るシフト回路を示す回路図である。

10

20

30

40

50

【図6】図5に示すシフト回路を備えたシフトレジスタの構成を示す図である。

【図7】図5に示すシフト回路及び図6に示すシフトレジスタの動作を説明するためのタイミングチャートである。

【図8】第2の実施形態におけるシフト回路の変形例を示す回路図である。

【図9】図8に示すシフト回路及びこれを備えるシフトレジスタの動作を説明するためのタイミングチャートである。

【図10】従来のインバータを示す回路図である。

【発明を実施するための形態】

【0021】

以下、本発明の実施形態に係る電子機器を、図面を参照して説明する。尚、本実施形態では、電子機器を、複数の画素を有し、各画素に発光素子として有機エレクトロルミネッセンス素子（以下、「有機EL素子」と略記する）を備えた表示装置として説明する。

【0022】

<第1の実施形態>

本発明の第1の実施形態に係る表示装置の構成を図1に示す。

本実施形態に係る表示装置1は、図1(a)に示すように、n行、m列の複数の画素回路11(i,j)（i=1～m, j=1～n, m, nは、それぞれ、自然数）と、ゲートドライバ（行選択ドライバ）12と、アノードドライバ13と、データドライバ14と、コントローラ15と、を備える。

【0023】

画素回路11(i,j)は、画像の各画素に対応するものであり、行列配置される。この画素回路11(i,j)は、図1(b)に示すように、有機EL素子OLED101と、トランジスタT1, T2と、キャパシタC1と、を有する。

【0024】

キャパシタC1は、トランジスタT2のゲート-ソース間に設けられたキャパシタである。

【0025】

有機EL素子OLED101は、画素電極（アノード電極）、単数或いは複数のキャリア輸送層からなる有機EL層、対向電極が積層された構造を有する表示素子であり、対向電極（カソード電極）にはカソード電位Vcathが印加されている。

【0026】

トランジスタT1, T2は、nチャンネル型のFET(Field Effect Transistor; 電界効果トランジスタ)によって構成されたポリシリコンまたはアモルファスシリコンによって形成されたTFTであり、ドレイン、ソースとゲートを有し、ドレイン-ソース間に半導体層が設けられ、ドレイン-ソース間に所定のバイアス電圧が印加されるとともに、ゲートに閾値電圧より大きい電圧が印加されたとき、半導体層中にチャネルが形成され、このチャネルがドレイン-ソース間の電流路となる。

【0027】

トランジスタT1は、キャパシタC1の一端に、画像データDataの階調を示す階調信号Vdataを印加するためのトランジスタである。各画素回路11(i,j)のトランジスタT1のソースは、トランジスタT2のゲート及びキャパシタC1の一端に接続される。

【0028】

画素回路11(i,1), …, 11(i,n)のトランジスタT1のドレインは、それぞれ、i列目のデータラインLdiに接続される。画素回路11(1,j), …, 11(m,j)の各トランジスタT1のゲートは、それぞれ、第j行目のゲートラインLgjに接続される。

【0029】

そして、それぞれ、ゲートラインLg1, …, LgnにHighレベルの信号が順次出力されると、画素回路11(1,j), …, 11(m,j)の各トランジスタT1はオンし、データラインLd1, …, Ldmにそれぞれ入力された階調信号VdataをトランジスタT2のゲート及びキャパシタC1の一端に出力する。

10

20

30

40

50

## 【0030】

トランジスタ T 2 は、階調信号 V data に基づいた電流量の電流を制御しつつ、有機 E L 素子 O L E D 1 0 1 に供給するトランジスタであり、そのゲートがトランジスタ T 1 のソース及びキャパシタ C 1 の一端に接続され、ドレインは、アノードライン L aj に接続され、ソースがキャパシタ C 1 の他端及び有機 E L 素子 O L E D 1 0 1 のアノードに接続されている。

## 【0031】

ゲートドライバ 1 2 は、行毎に画素回路 1 1 (i, j) を選択するためのドライバである。ゲートドライバ 1 2 は、コントローラ 1 5 から、電圧 V H I , V L W ( V H I > V L W ) が印加され、スタート信号 S t 、クロック信号 C K 1 , C K 2 , e n d 信号が供給されて動作を開始する。

10

## 【0032】

ゲートドライバ 1 2 は、スタート信号 S t が供給されて動作を開始し、クロック信号 C K 1 , C K 2 に従って、出力信号 O U T ( 1 ) ~ ( n ) を、ゲートライン L g1 ~ L gn に、順次、出力する。

## 【0033】

ゲートドライバ 1 2 は、このようにして、画素回路 1 1 (1, 1) ~ 1 1 (m, 1) , . . . , 1 1 (1, n) ~ 1 1 (m, n) を選択する。

## 【0034】

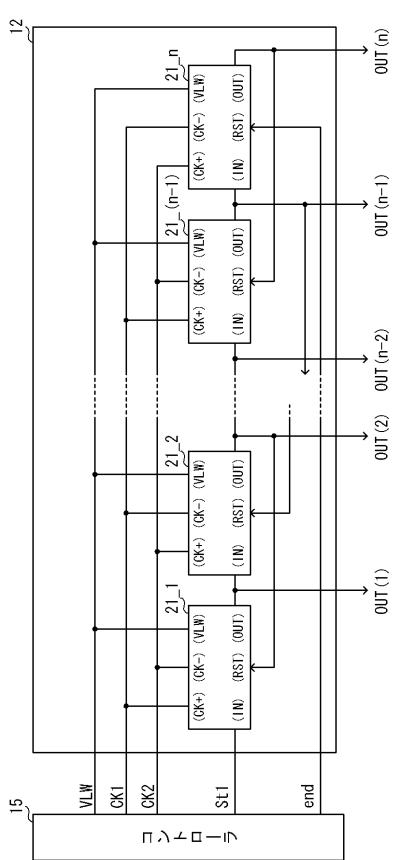

このゲートドライバ 1 2 は、図 2 に示すようなシフトレジスタを有する。なお、ゲートドライバ 1 2 は、シフトレジスタの出力端にバッファが設けられていてもよい。このシフトレジスタは、コントローラ 1 5 から供給されたスタート信号 S t によって動作を開始し、クロック信号 C K 1 , C K 2 に同期させてスタート信号 S t を転送し、出力信号 O U T ( 1 ) ~ O U T ( n ) を順次出力するものである。

20

## 【0035】

シフトレジスタは、第 1 段乃至第 n 段のシフト回路 2 1 \_ 1 ~ 2 1 \_ n を備え、シフト回路 2 1 \_ 1 ~ 2 1 \_ n が直列に接続されている。

## 【0036】

シフト回路 2 1 \_ 1 ~ 2 1 \_ n は、入力信号 I N ( スタート信号 S t を含む ) とクロック信号 C K 1 又は C K 2 とが供給され、供給された入力信号 I N をクロック信号 C K 1 又は C K 2 に従ってシフトし、シフトした信号を出力信号 O U T ( k ) ( k = 1 ~ n ) として出力するものである。

30

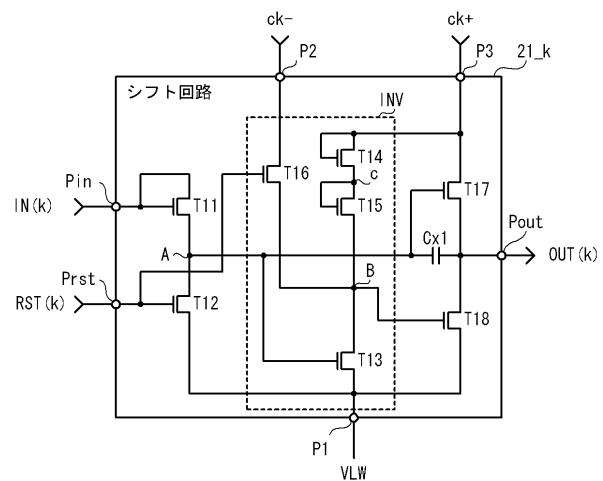

## 【0037】

シフト回路 2 1 \_ k ( k = 1 ~ n ) は、図 3 に示すように、入力端子 P in と、出力端子 P out と、リセット端子 P rst と、電圧端子として機能する第 1 の端子 P 1 と、電圧端子として機能する第 2 の端子 P 2 と、クロック端子として機能する第 3 の端子 P 3 と、を有している。

## 【0038】

入力端子 P in は、入力信号 I N ( k ) が供給される端子である。シフト回路 2 1 \_ 1 の入力端子 P in には、コントローラ 1 5 からスタート信号 S t が入力信号 I N ( 1 ) として供給される。

40

## 【0039】

出力端子 P out は、出力信号 O U T ( k ) を出力する端子であり、ゲートライン L gk に接続されている。シフト回路 2 1 \_ 2 ~ 2 1 \_ n の入力端子 P in は、それぞれ、前段のシフト回路 2 1 \_ 1 ~ 2 1 \_ ( n - 1 ) の出力端子 P out に接続される。

## 【0040】

リセット端子 P rst は、リセット信号 R S T ( k ) が供給される端子である。シフト回路 2 1 \_ 1 ~ 2 1 \_ ( n - 1 ) のリセット端子 P rst は、それぞれ、次段のシフト回路 2 1 \_ 2 ~ 2 1 \_ n の出力端子 P out に接続され、出力信号 O U T ( 2 ) ~ O U T ( n ) がリセット信号 R S T ( 1 ) ~ R S T ( n - 1 ) として供給される。また、シフト回路 2 1 \_ n に

50

は、コントローラ15からe n d信号が供給される。

【0041】

第3の端子P3は、クロック信号(第1のクロック信号)CK1又はCK2が供給される端子であり、奇数段であるシフト回路21\_kの第3の端子P3には、コントローラ15から、クロック信号CK1が供給される。

【0042】

また、偶数段であるシフト回路21\_(k+1)の第3のクロック端子P3には、コントローラ15から、クロック信号CK2が供給される。

【0043】

第2の端子P2は、電圧VHIが印加される端子であり、第1の端子P1は、基準電圧としての電圧VLWが印加される端子である。 10

【0044】

このシフト回路21\_kは、トランジスタT11～T18を備えている。トランジスタT11～T18は、nチャンネル型のFETによって構成されたトランジスタである。

【0045】

このトランジスタT11～T18は、単結晶シリコントランジスタでもよく、また画素回路11(i,j)と一緒に構成されるためにポリシリコンFTやアモルファスシリコンFT(a-FT)によって構成されてもよい。

【0046】

トランジスタT11～T18は、ドレイン、ソースとゲートを有し、ドレイン-ソース間には半導体層が設けられ、ドレイン-ソース間に所定のバイアス電圧が印加されるとともに、ゲートに閾値電圧より大きい電圧が印加されたとき、半導体層中にチャネルが形成され、このチャネルがドレイン-ソース間の電流路となる。 20

【0047】

トランジスタT11は、入力端子Pinに供給された入力信号IN(k)の信号レベルに従って、ノードAの電位Vaを決定するためのトランジスタである。このトランジスタT11のゲートとドレインとは、入力端子Pinに接続される。ノードAは、信号出力端としてのトランジスタT11のソースに接続された接続点である。

【0048】

トランジスタT12は、リセット端子Prstに供給されたHighレベルのリセット信号RST(k)でシフト回路21\_kをリセットするためのトランジスタである。 30

【0049】

このトランジスタT12のゲートは、リセット端子Prstに接続され、ドレインは、トランジスタT11のソースとノードAとに接続され、ソースは、第1の端子P1に接続される。トランジスタT11、T12は入力回路に相当する。

【0050】

トランジスタT13～T16は、ノードAの電位を反転するインバータINVを構成するトランジスタである。インバータINVはインバタ回路に相当する。

【0051】

トランジスタT13は、ノードAの電位Vaに従って、ノードBの電位Vbをコントロールするためのトランジスタである。このトランジスタT13のゲートは、ノードAに接続され、電流上流端としてのドレインは、ノードBに接続され、電流下流端としてのソースは第1の端子P1に接続される。ノードBはトランジスタT15のソースとトランジスタT13のドレインとの接続点である。 40

【0052】

トランジスタT14、T15は、ダイオード接続されて抵抗として機能する半導体素子であり、トランジスタT14のドレインとゲートとは、第2の端子P2に接続される。トランジスタT14は、電圧VHIが印加されて、電流量を制限しつつトランジスタT15、T13に電流を供給する。

【0053】

またトランジスタ T 1 5 のゲートとドレインとは、トランジスタ T 1 4 のソースに接続され、ソースはノード B に接続される。トランジスタ T 1 5 は、トランジスタ T 1 4 と直列に接続されて、電流下流端としてのソースがノード B に接続されて、第 2 の端子 P 2 とノード B 間の電圧を分圧するトランジスタである。

【 0 0 5 4 】

このように、電圧 V H I が印加される第 2 の端子 P 2 とノード B 間との間にダイオード接続されたトランジスタ T 1 4 、 T 1 5 が直列接続されるため、各トランジスタ T 1 4 、 T 1 5 のバイアス電圧が分圧（ストレス電圧が分散）される。また、これにより、第 2 の端子 P 2 とノード B 間の抵抗値が従来の構成に比べて増加して、貫通電流の電流値が従来の構成に比べて減少する。

10

【 0 0 5 5 】

トランジスタ T 1 6 は、ノード B の電位 V b の立ち上がり速度の低下を抑制するためのトランジスタである。トランジスタ T 1 6 がトランジスタ T 1 4 、 T 1 5 と並列に接続されるように、トランジスタ T 1 6 のドレインはトランジスタ T 1 4 のドレイン（及びゲート）に接続されるとともに第 2 の端子 P 2 に接続され、ソースはノード B に接続される。

【 0 0 5 6 】

また、トランジスタ T 1 6 のゲートは、リセット端子 P r s t に接続され、トランジスタ T 1 6 は、リセット信号 R S T ( k ) の信号レベルに従って、ノード B の電位をコントロールする。

20

【 0 0 5 7 】

尚、このトランジスタ T 1 6 は、 H i g h レベルのリセット信号 R S T ( k ) で動作するため、リセット信号 R S T ( k ) の立ち上がりの際に、過渡的にしか電圧ストレス（ゲート - ソース間電圧）を受けないため、比較的劣化が少ない素子である。

【 0 0 5 8 】

このトランジスタ T 1 3 ~ T 1 6 によって構成されるインバータ I N V により、ノード A の電位 V a 、ノード B の電位 V b は相補的に H i g h ( オンレベル ) 、 L o w ( オフレベル ) にスイッチされ、一方が H i g h であれば、他方が L o w となる。

30

【 0 0 5 9 】

尚、トランジスタ T 1 3 ~ T 1 6 のトランジスタサイズは、チャネル長が互いに同じ値である場合、チャネル幅も互いに同じ値に設定してよい。これに対し、図 1 0 に示す従来のインバータ I N V では、電圧 V H I と電圧 V L W との間に接続されているトランジスタは、トランジスタ T 5 1 、 T 5 2 の 2 つであり、ノード B の電圧を低下させるため、トランジスタ T 5 1 、 T 5 2 のトランジスタサイズを、チャネル長を同じとして、チャネル幅を、例えば 1 : 3 程度にする必要があった。

【 0 0 6 0 】

しかし、図 3 に示すインバータ I N V では、トランジスタ T 1 5 が介挿されているため、トランジスタ T 1 3 のトランジスタサイズを T 1 4 、 T 1 5 と同程度に小さくしてもノード B の電位 V b を充分に低下させることができる。

【 0 0 6 1 】

また、ダイオード接続されたトランジスタ T 5 1 を備える従来の構成に比べて、 T 1 6 があることによってノード B の電圧の立ち上がりが速められているため、トランジスタ T 1 4 、 T 1 5 のトランジスタサイズを T 5 1 のトランジスタサイズより小さくすることができる。以上により、従来の構成に対してトランジスタが 2 つ増加されているものの、各トランジスタの大きさを比較的小さくすることが出来て、回路面積の増加を抑えることができる。

40

【 0 0 6 2 】

トランジスタ T 1 7 は、クロック信号 C K 1 がドレインに供給され、ノード A の電位 V a に従ってオン、オフし、オンしたときに、クロック信号 C K 1 に同期して、シフト信号としての出力信号 O U T ( k ) として出力するトランジスタである。

【 0 0 6 3 】

50

このトランジスタ T 1 7 のゲートは、ノード A に接続され、ドレインは、第 3 の端子 P 3 に接続され、ソースは出力端子 P out に接続される。このトランジスタ T 1 7 のゲート - ソース間には、ブートストラップ効果をもたらすためのキャパシタ C x1 が接続される。

【0064】

トランジスタ T 1 8 は、ノード B の電位 Vb に従ってオン、オフし、第 k 行の画素回路 1 1 (i, k) の非選択期間にオンして出力信号 OUT (k) を基準電圧としての電圧 V LW に固定して出力信号 OUT (k) を安定させるためのトランジスタである。

【0065】

トランジスタ T 1 8 のゲートは、ノード B に接続され、ドレインは、トランジスタ T 1 7 のソースと出力端子 P out とに接続され、ソースは、第 1 の端子 P 1 に接続される。トランジスタ T 1 7 、 T 1 8 は出力回路に相当する。

【0066】

図 1 (a) , (b) に戻り、アノードドライバ 1 3 は、アノードドライイン La(1) ~ La(n) に、それぞれ、電圧 VL 又は VH の信号 V source(1) ~ V source(n) を出力するドライバである。アノードドライバ 1 3 は、それぞれ、アノードドライイン Laj (j = 1 ~ n) を介して、各画素回路 1 1 (i, j) のトランジスタ T 3 のドレインに接続される。

【0067】

アノードドライバ 1 3 は、コントローラ 1 5 から供給されたスタート信号 S t により動作を開始し、コントローラ 1 5 から供給されたクロック信号 CK 1 に従って動作する。

【0068】

そして、アノードドライバ 1 3 は、電圧 VL 又は VH の電圧信号 V source(1) ~ V source(n) を出力する。電圧 VL は、書き込み処理時等において、各画素回路 1 1 (i, j) の有機 EL 素子 O LED 1 0 1 を非発光状態にするための電圧である。

【0069】

本実施形態では、有機 EL 素子 O LED 1 0 1 のカソード電圧 V cath が 0 V に設定され、電圧 VL は、0 V 、もしくは 0 V より低い電位に設定される。また、電圧 VH は、各画素回路 1 1 (i, j) の有機 EL 素子 O LED 1 0 1 を発光状態にするための電圧であり、例えば、+ 1 5 V に設定される。

【0070】

データドライバ 1 4 は、画素回路 1 1 (i, j) の各キャパシタ C 1 に供給された画像データ Data に基づく表示信号の階調信号 V data を書き込むドライバである。

【0071】

データドライバ 1 4 は、コントローラ 1 5 から画像データ Data が供給され、この画像データ Data に基づいて、行毎の階調信号 V data を生成する。

【0072】

データドライバ 1 4 は、生成した階調信号 V data を、それぞれ、データライン L d1 ~ L dm を介して、ゲートドライバ 1 2 が選択した第 j 行の画素回路 1 1 (1, j) ~ 1 1 (m, j) に供給する。

【0073】

コントローラ 1 5 は、ゲートドライバ 1 2 、データドライバ 1 4 を制御するものであり、CPU (Central Processing Unit) 、ROM (Read Only Memory) , RAM (Random Access Memory) 、等を備える (いずれも図示せず)。

【0074】

コントローラ 1 5 は、シフト回路 2 1 \_ 1 ~ 2 1 \_ n のうち奇数段にクロック信号 CK 1 を出力し、偶数段にクロック信号 CK 2 を出力した状態で、動作を開始させるスタート信号 S t をゲートドライバ 1 2 の初段のシフト回路 2 1 \_ 1 に供給する。コントローラ 1 5 は、このようにして、ゲートドライバ 1 2 に動作を開始させる。

【0075】

また、コントローラ 1 5 は、ゲートドライバ 1 2 に、最終段のシフト回路 2 1 \_ n のリセット信号 R S T (n) として end 信号を供給する。

10

20

30

40

50

## 【0076】

コントローラ15は、データドライバ14にスタート信号St及び画像データData、クロック信号CK1等を供給する。

## 【0077】

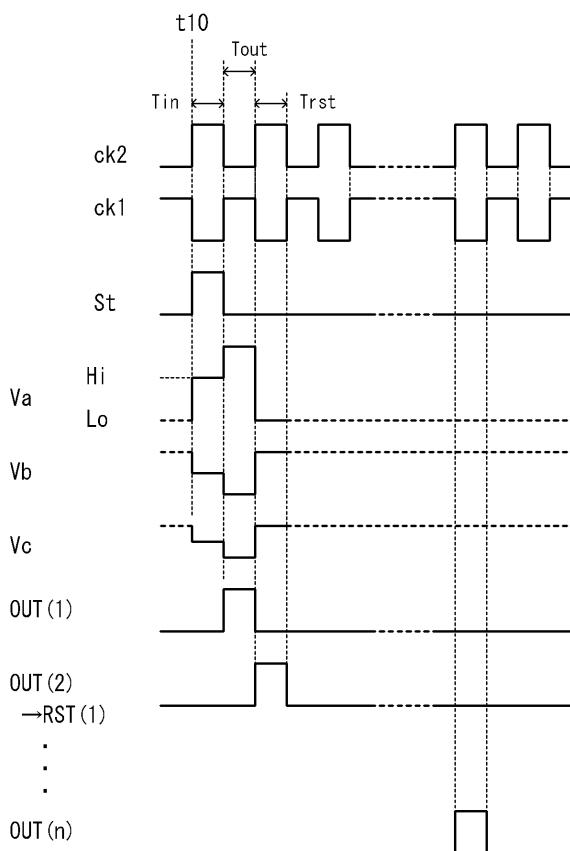

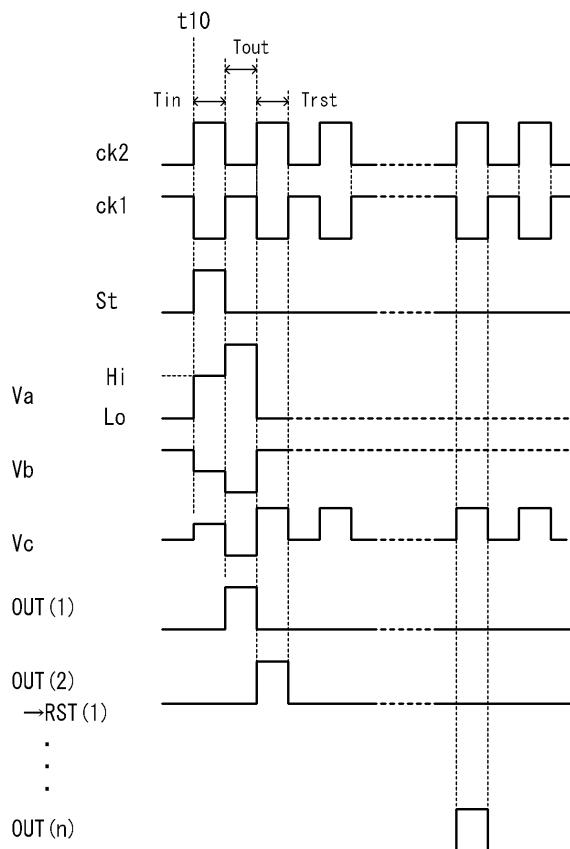

次に本実施形態に係る表示装置1の動作を説明する。図4は、ゲートドライバ12におけるシフト回路21\_k及びシフトレジスタの動作を説明するためのタイミングチャートである。なお、Va、Vb、Vcは初段のシフト回路21\_1のノードA、B、Cの電位を示す。

## 【0078】

図4に示すように、コントローラ15は、位相が180°異なるクロック信号CK1、CK2とHighレベルのスタート信号Stとをゲートドライバ12に供給する。 10

## 【0079】

クロック信号CK1がLowレベルになる時刻t10において、このHighレベルのスタート信号Stは、第1段のシフト回路21\_1の入力端子Pinに、入力信号IN(1)として供給される。

## 【0080】

このHighレベルのスタート信号Stが供給される期間を入力期間Tinとして、シフト回路21\_1のトランジスタT11は、この入力期間Tinにおいて、オンする。

## 【0081】

トランジスタT11がオンすると、ノードAの電位Vaは、Highレベルとなり、トランジスタT13も、ゲートにHighレベルの信号が供給されてオンする。 20

## 【0082】

トランジスタT13がオンすると、トランジスタT14、T15は、ダイオード接続されているために、電流が、電圧VHIのラインから、第2の端子P2、トランジスタT14、T15、T13の各ドレイン-ソース、第1の端子P1を経由して、電圧VLWのラインへと流れる。

## 【0083】

電流がこのように流れ、ノードBの電位Vbは、図4に示すように、入力期間TinにおいてLowレベルになり、トランジスタT18はオフする。

## 【0084】

しかし、トランジスタT14、T15は、抵抗素子として機能し、流れる電流の電流量は、トランジスタT14、T15によって制限され、トランジスタT13の発熱量も低減される。また、トランジスタT14、T15のドレイン-ソース間に印加される電圧は、(VHI - VLW) / 3となり、従来と比較して減少する。 30

## 【0085】

図4に示すように、入力期間Tin経過後、クロック信号CK1がHighレベルになる出力期間Toutにおいて、入力信号IN(1)がLowレベルとなり、トランジスタT11はオフする。

## 【0086】

ノードAの電位Vaは、トランジスタT11がオフしても、トランジスタT17、T18がオフしているため、Highレベルに保持されている。 40

## 【0087】

この出力期間Toutにおいて、クロック信号CK1がHighレベルになると、キャパシタCx1のブーストアップ効果により、ノードAの電位Vaは、さらに上昇し、トランジスタT17は、確実にオンする。

## 【0088】

トランジスタT17がオンすると、シフト回路21\_1は、出力端子Poutから、Highレベルの出力信号OUT(1)を出力する。

## 【0089】

このHighレベルの出力信号OUT(1)は、ゲートラインLg1に出力されるととも

50

に、シフト回路 21\_2 に、入力信号 IN(2) として供給される。

【0090】

シフト回路 21\_2 は、この入力信号 IN(2) をクロック信号 CK2 に同期してシフトし、High レベルの出力信号 OUT(2) を出力する。

【0091】

この High レベルの出力信号 OUT(2) は、High レベルのリセット信号 RST(1) として、シフト回路 21\_1 のリセット端子 Prst に供給される。

【0092】

この High レベルのリセット信号 RST(1) が供給されると、トランジスタ T12 がオンする。トランジスタ T12 がオンすると、ノード A の電位 Va は Low レベルに立ち下がる。

【0093】

ノード A の電位 Va が Low レベルに立ち下がると、トランジスタ T13 がオフし、ノード B の電位 Vb は High レベルとなる。

【0094】

また、High レベルのリセット信号 RST(1) が供給されると、トランジスタ T16 もオンする。

【0095】

第 2 の端子 P2 と第 1 の端子 P1 との間には、トランジスタ T15 が介挿されているため、トランジスタ T16 がなければ、トランジスタ T15 の寄生容量により、ノード B の電位 Vb の立ち上がり速度は、従来と比較して、遅くなる。

【0096】

しかし、シフト回路 21\_1 には、トランジスタ T16 が備えられ、トランジスタ T16 がオンすることにより、第 2 の端子 P2 とノード B との間が短絡され、電位 Vb の立ち上がり速度の遅れは解消され、ノード B の電位 Vb は、素早く High レベルとなる。

【0097】

ノード B の電位 Vb が High レベルになることにより、トランジスタ T18 はオンし、出力信号 OUT(1) は、Low レベルに立ち下がる。

【0098】

同様に、シフト回路 21\_k (k = 2 ~ n) は、それぞれ、クロック信号 CK1, CK2 に同期させて、シフト回路 21\_(k-1) から出力された出力信号 OUT(k-1) を入力信号 IN(k) として、この入力信号 IN(k) をシフトする。そして、シフト回路 21\_k は、シフトした信号を出力信号 OUT(k) として出力する。

【0099】

ゲートドライバ 12 は、シフト回路 21\_1 の High レベルの出力信号 OUT(1) をゲートライン Lg1 に出力する。画素回路 11(1,1) ~ 11(m,1) の各トランジスタ T1 は、この High レベルの出力信号 OUT(1) によりオンする。

【0100】

データドライバ 14 は、この期間において、データライン Ld1 ~ Ldm を介して、ゲートドライバ 12 が選択した画素回路 11(1,1) ~ 11(m,1) に階調信号 Vdata を供給する。

【0101】

画素回路 11(1,1) ~ 11(m,1) の各キャパシタ C1 には、各トランジスタ T1 を介して、この階調信号 Vdata が書き込まれる。

【0102】

同様にして、ゲートドライバ 12 は、シフト回路 21\_2, ..., 21\_n の High レベルの出力信号 OUT(2) ~ OUT(n) を、順次、ゲートライン Lg2, ..., Lgn に出力する。

【0103】

ゲートライン Lg2, ..., Lgn に、順次、High レベルの出力信号 OUT(1) が供給されると、画素回路 11(1,2) ~ 11(m,2), ..., 11(1,n) ~ 11(m,n) が選択さ

10

20

30

40

50

れる。

【0104】

データドライバ14は、供給された画像データに基づく階調信号Vdataを、それぞれ、データラインLd1～Ldmに印加し、選択された画素回路11(1,2)～11(m,2), . . . , 11(1,n)～11(m,n)の各キャパシタC1に階調信号Vdataを書き込む。

【0105】

このようにして書き込み動作が完了すると、コントローラ15は、発光動作を制御する。

【0106】

アノードドライバ13は、電圧VH(=+15V)の信号Vsource(1)～Vsource(n)を、アノードラインLa(1)～La(n)に出力する。 10

【0107】

アノードラインLa(1)～La(n)の電圧がVHになると、各画素回路11(i,j)のトランジスタT2は、各キャパシタC1が保持した電圧をゲート電圧Vgsとして、このゲート電圧Vgsに対応する電流を有機EL素子OLED101に供給する。

【0108】

そして、各有機EL素子OLED101は、この電流が流れることにより、この電流の電流値に対応する輝度で発光する。

【0109】

以上説明したように、本実施形態によれば、インバータINVのトランジスタT14とノードBとの間にトランジスタT15が接続され、電圧VHIと電圧VLWとの間のバイアス電圧を分圧するようにした。 20

【0110】

従って、各トランジスタT13～T15のバイアス電圧は分散されるため、入力期間Tinと出力期間Toutにおいて、トランジスタT14、T15の各々に印加されるバイアス電圧を従来の構成の場合に対してほぼ半減させることができ、電流を大幅に低減することができる。

【0111】

また、このため、トランジスタT14、T15の劣化による閾値Vthシフトの発生を抑制することができる。 30

【0112】

また、トランジスタT14、T15と並列に、トランジスタT16が接続されることにより、トランジスタT15を介挿したことによるノードBの電位Vbの立ち上がり速度の遅れを防止することができる。

【0113】

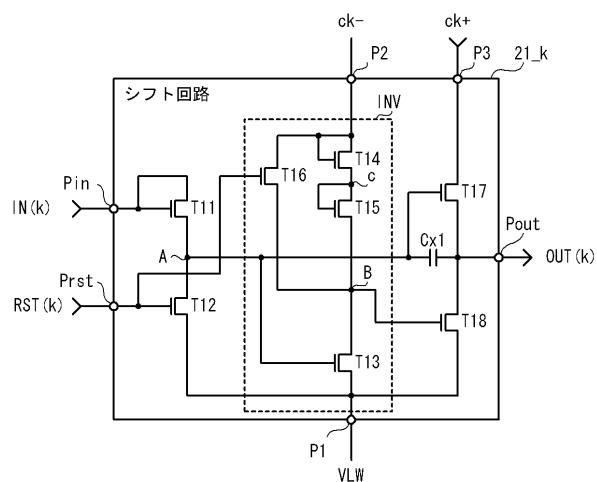

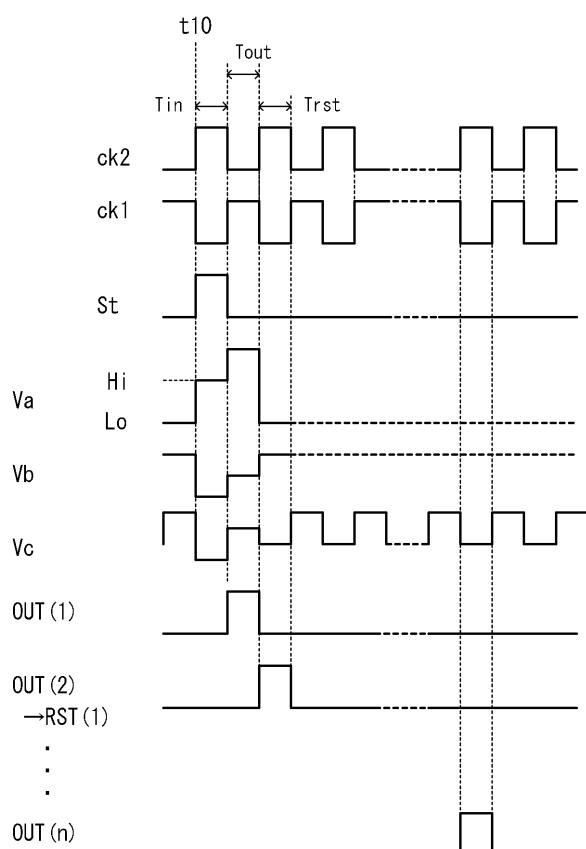

<第2の実施形態>

次に、本発明の第2の実施形態に係るシフト回路の構成を図5に示す。

上記第1の実施形態では、シフト回路21\_kにおいて、トランジスタT14のドレインに接続される第2の端子P2に一定の電圧値を有する電圧VHIを印加するようにした。しかし、インバータINVのトランジスタT14のドレインには、図4に示した出力期間Toutには電圧VHIが印加されていなくても、シフト回路21\_kは実質的に同様に動作する。 40

【0114】

そこで、本第2の実施形態は、図5に示すように、第2の端子P2に、電圧VHIに代えて、第3の端子P3に印加されるクロック信号(正相のクロック信号(第1のクロック信号)CK+とする)に対して逆相のクロック信号(第2のクロック信号)CK-を供給するようにしたものである。

【0115】

この場合、ゲートドライバ12は、図6に示すように、すべてのシフト回路21\_1～21\_nに、クロック信号CK1, CK2を供給する。奇数段のシフト回路21\_kには、 50

クロック信号CK1, CK2が、それぞれ、正相及び逆相のクロック信号CK+, CK-として供給され、偶数段のシフト回路21\_kには、クロック信号CK1, CK2が、それぞれ、逆相及び正相のクロック信号CK-, CK+として供給される。

【0116】

ここで、本実施形態におけるシフト回路21\_k及びシフトレジスタの動作は、図7に示すように、ノードCの電位であるVc以外は図4に示した動作と同じとなる。

【0117】

ノードCの電位Vcは、第2の端子P2に逆相のクロック信号CK-が印加されるために、初段のシフト回路21\_1においては、クロック信号CK2に対応して変化する。

【0118】

このようにすることにより、電圧VHIを使用しないため、電圧VHIのラインの配線が不要となり、回路面積を縮小することができる。また、トランジスタT14、T15に印加されるバイアス電圧を低減することができるとともに、トランジスタT14、T15にバイアス電圧が印加される期間を入力期間Tinのみとし、出力期間ToutにはトランジスタT14、T15にバイアス電圧が印加されないため、バイアス電圧が印加される期間を短縮して、トランジスタT14、T15の劣化を更に抑制することができる。

【0119】

さらに、第2の端子P2に逆相のクロック信号CK-を供給することにより、出力期間Toutにおいて、インバータINVに電流が供給されなくなるため、消費電流を低減させることができる。

【0120】

次に、本実施形態の変形例について説明する。上記図5に示した構成においては、第2の端子P2にトランジスタT16のドレインとトランジスタT14のドレインとが接続されていたが、図8に示すように、第2の端子P2にはトランジスタT16のドレインのみを接続し、第3の端子P3にトランジスタT13のドレインとトランジスタT17のドレインとを接続するようにしてもよい。

【0121】

ここで、本実施形態におけるシフト回路21\_k及びシフトレジスタの動作も、図9に示すように、ノードB、Cの電位であるVb、Vc以外は図4に示した動作と同じとなる。

【0122】

スタート信号Stが供給されたときトランジスタT16はオフ状態であり、トランジスタT13、T14もオフ状態であるため、ノードBの電位Vbは、入力期間Tinに電圧VLW近いLowレベルになり、出力期間Toutにおいて、第3の端子P3にHighレベルのクロック信号が印加されて、そのLowレベルが上昇する。そして、ノードCの電位Vcは、このノードBの電位Vbの変化に応じた変化をする。

【0123】

この場合においても、電圧VHIを使用しないため、電圧VHIのラインの配線が不要となり、回路面積を縮小することができる。また、トランジスタT14、T15に印加されるバイアス電圧を低減することができるとともに、トランジスタT14、T15にバイアス電圧が印加される期間を出力期間Toutのみとし、入力期間TinにはトランジスタT14、T15にバイアス電圧が印加されないため、バイアス電圧が印加される期間を短縮して、トランジスタT14、T15の劣化を更に抑制することができる。

【0124】

なお、上記実施形態では、電子機器を、有機EL素子を備えた表示装置として説明した、しかし、電子機器は、このものに限られるものではなく、発光素子を備えたものであれば、本実施形態に限定されるものではない。また、電子機器は、例えば、液晶素子を備えた液晶表示装置であってもよい。

【符号の説明】

【0125】

1 . . . 表示装置、11 . . . 画素回路、12 . . . ゲートドライバ、13 . . . アノ

10

20

30

40

50

ードライバ、14···データドライバ、15···コントローラ、21\_k (k; 1~n)···シフト回路、101···有機EL素子OLED、T1, T2, T11~T18···トランジスタ、C1···キャパシタ、INV···インバータ

【図1】

(a)

(b)

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

## フロントページの続き

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|--------------|---------|--------------|

|              | G 0 9 G | 3/20 6 2 2 E |

|              | G 0 9 G | 3/20 6 4 1 C |

|              | G 0 9 G | 3/20 6 2 4 B |

|              | G 0 9 G | 3/30 J       |

|              | G 0 9 G | 3/30 H       |

|              | G 0 9 G | 3/20 6 1 1 J |

F ターム(参考) 5C380 AA01 AB06 AB22 AB23 BA01 BA05 BA11 BA40 BD10 CA04

CA08 CA12 CB01 CC02 CC27 CC33 CC41 CC62 CD012 CF07

CF10 CF43 CF46 CF62 DA02 DA06 GA14