(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4825429号 (P4825429)

(45) 発行日 平成23年11月30日(2011.11.30)

(24) 登録日 平成23年9月16日 (2011.9.16)

(51) Int.Cl. F 1

HO1L 21/822 (2006.01) HO1L 27/04 M HO1L 27/04 (2006.01) HO1L 27/04 V HO3K 19/0175 (2006.01) HO3K 19/00 1O1F

請求項の数 7 (全 13 頁)

(21) 出願番号 特願2005-40974 (P2005-40974) (22) 出願日 平成17年2月17日 (2005. 2. 17)

(65) 公開番号 特開2006-228972 (P2006-228972A) (43) 公開日 平成18年8月31日 (2006. 8. 31)

審査請求日 平成19年12月11日 (2007.12.11)

||(73)特許権者 308014341

富士通セミコンダクター株式会社

神奈川県横浜市港北区新横浜二丁目10番

23

||(74)代理人 100070150

弁理士 伊東 忠彦

|(72)発明者 小林 広之

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

||(72)発明者 内田 敏也

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 須原 宏光

最終頁に続く

## (54) 【発明の名称】半導体装置

#### (57)【特許請求の範囲】

### 【請求項1】

動作時に外部から設定される第1の信号を受け取る端子と、

動作時と非動作時とに関わらず固定的に設定状態を保持し該設定状態に応じた第2の信号を出力する記憶部と、

該端子と該記憶部の出力とに結合され該第1の信号と該第2の信号とに応じた駆動能力で出力信号を出力する出力ドライバ部

#### を含み、

該第1の信号は該半導体装置に接続される伝送線の負荷に応じて設定される信号であり、該記憶部の該設定状態は該出力ドライバ部の信号駆動能力の試験結果に応じて設定される信号であることを特徴とする半導体装置。

10

## 【請求項2】

該第1の端子は、該半導体装置の外部から供給される該第1の信号を受け取ることを特徴とする請求項1記載の半導体装置。

#### 【請求項3】

動作時に外部から設定されるレジスタ部を更に含み、該端子は該レジスタ部から該第1の信号を受け取ることを特徴とする請求項1記載の半導体装置。

#### 【請求項4】

該記憶部はヒューズの切断 / 非切断により該設定状態を保持する R O M 回路であることを特徴とする請求項 1 記載の半導体装置。

### 【請求項5】

該出力ドライバ部は該出力信号を出力する複数の出力トランジスタを含み、該第1の信号と該第2の信号とに応じた個数の該出力トランジスタを駆動することを特徴とする請求項1記載の半導体装置。

## 【請求項6】

<u>該</u>出力ドライバ部は該出力信号を出力する複数の出力トランジスタを含み、該第1の信号と該第2の信号とに応じた個数の該出力トランジスタを駆動し、

該複数の出力トランジスタはゲート幅の異なる出力トランジスタを含み、該第 1 の信号に応じた個数の同一ゲート幅の該出力トランジスタを駆動するとともに、該第 2 の信号に応じて異なるゲート幅の該出力トランジスタを駆動することを特徴とする<u>請求項 1 記載の</u>半導体装置。

### 【請求項7】

<u>該</u>出力ドライバ部は該出力信号を出力する複数の出力トランジスタを含み、該第1の信号と該第2の信号とに応じた個数の該出力トランジスタを駆動し、

該複数の出力トランジスタはゲート幅の異なる出力トランジスタを含み、該第2の信号に応じた個数の同一ゲート幅の該出力トランジスタを駆動するとともに、該第1の信号に応じて異なるゲート幅の該出力トランジスタを駆動することを特徴とする<u>請求項1記載の</u>半導体装置。

【発明の詳細な説明】

### 【技術分野】

[00001]

本発明は一般に半導体装置に関し、詳しくは信号駆動能力を調整可能な出力回路を備えた半導体装置に関する。

#### 【背景技術】

#### [0002]

半導体装置のチップ間の伝送速度を上げるために信号周波数を高くすると、伝送線において信号のオーバーシュート・アンダーシュート、リンギング、反射等が生じ、高速で確実なデータ転送の妨げとなる。これらの影響を削減するためには、半導体装置から信号を送出する信号駆動能力と伝送負荷とを適合させ、インピーダンスマッチングをとる必要がある。

## [0003]

しかし半導体装置の信号駆動能力に合わせるように伝送線を設計してシステムを構成することは困難である。半導体装置でシステムを構成する場合、その構成に応じて伝送線の負荷は異なってしまう。しかし高速で確実なデータ伝送を実現するためには、伝送線の負荷が小さい場合にはそれに応じて信号駆動能力を小さくし、伝送線の負荷が大きい場合にはそれに応じて信号駆動能力を大きくすることが必要である。従って、伝送負荷に応じて信号駆動能力を調整できる機能を半導体装置に設けることが好ましい。

## [0004]

半導体装置に信号駆動能力を調整する機能を設けた構成が、特許文献1乃至3に開示される。特許文献1では、出力バッファに出力電流制御回路としてセレクタを設け、外部から供給する制御信号により出力電流制御回路を制御して、出力電流をシステムに適応した値に調整する。特許文献2では、サイズが異なる複数のトランジスタを並列接続して出力バッファ回路を構成し、各トランジスタのオン/オフをコントロールすることで出力バッファ回路のインピーダンスを調整する。特許文献3では、出力バッファに含まれる第1および第2の電流駆動ユニットを、製造プロセスの後工程において選択的に動作状態もしくは非動作状態に設定し、出力バッファの電流駆動能力を調整する。

【特許文献1】特開平5-206829号公報

【特許文献2】特開2002-111474号公報

【特許文献3】特開2002-300023号公報

#### 【発明の開示】

20

10

40

30

#### 【発明が解決しようとする課題】

### [0005]

半導体装置においては、製造時のプロセス条件に応じて、その動作特性にバラツキが生じることは避けられない。その結果、半導体装置の信号駆動能力が、チップ間で2倍程度異なってしまう場合がある。この場合、半導体装置に信号駆動能力の調整機能が設けられているとしても、その機能が有効に働かないという問題がある。

#### [0006]

例えば、システム側で25%、50%、75%、及び100%の信号駆動能力を選択可能であり、伝送負荷に応じて50%の能力を選ぶとする。このときチップ間で信号駆動能力に2倍のバラツキがあるとすると、ある半導体チップで信号駆動能力を50%に設定しても、実際には100%の信号駆動能力に相当する大きさ、或いは25%の信号駆動能力に相当する大きさになってしまう可能性がある。従って、システムのコントローラ側において伝送負荷に適した選択をしても、期待した通りの信号駆動能力を確保することができない場合がある。このために、信号駆動能力のバラツキを考慮したシステム設計をする必要が生じ、周波数の上限を決めてしまう1つの要因になっている。

#### [0007]

以上を鑑みて、本発明は、製造バラツキに影響を受けることなく所望の信号駆動能力を 実現可能な半導体装置を提供することを目的とする。

#### 【課題を解決するための手段】

## [0008]

本発明による半導体装置は、動作時に外部から設定される第1の信号を受け取る端子と、動作時と非動作時とに関わらず固定的に設定状態を保持し該設定状態に応じた第2の信号を出力する記憶部と、該端子と該記憶部の出力とに結合され該第1の信号と該第2の信号とに応じた駆動能力で出力信号を出力する出力ドライバ部を含み、該第1の信号は該半導体装置に接続される伝送線の負荷に応じて設定される信号であり、該記憶部の該設定状態は該出力ドライバ部の信号駆動能力の試験結果に応じて設定される信号であることを特徴とする。

#### 【発明の効果】

## [0009]

本発明の少なくとも1つの実施例によれば、半導体装置においては、実装時にシステムからの指示により信号駆動能力を設定可能とすることにより、システムの伝送線の負荷に応じて信号駆動能力を調整可能とするとともに、工場出荷時等に行う試験結果に応じたヒューズ設定により信号駆動能力を設定可能とすることにより、製造バラツキに影響されない所望の信号駆動能力を実現することができる。これにより、半導体装置の製造バラツキ及びシステム構成に影響されること無く、高速で確実なチップ間のデータ転送を実現することができる。

## 【発明を実施するための最良の形態】

#### [ 0 0 1 0 ]

以下に、本発明の実施例を添付の図面を用いて詳細に説明する。

## [0011]

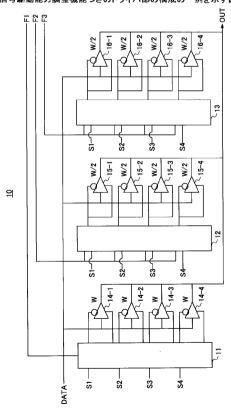

図1は、本発明による半導体装置に搭載される信号駆動能力調整機能つきのドライバ部の構成の一例を示す図である。図1のドライバ部10は、ドライバ選択駆動ユニット11乃至13、第1のドライバ14-1乃至14-4、第2のドライバ15-1乃至15-4、及び第3のドライバ16-1乃至16-4を含む。図1の例では、4つのドライバを含むセットが3セット設けられているが、ドライバ数及びセット数は特定の数に限定されるものではなく、複数のドライバを含む複数のセットが設けられていればよい。

#### [0012]

図 1 の例において、第 1 のドライバ 1 4 - 1 乃至 1 4 - 4 は例えば、第 2 のドライバ 1 5 - 1 乃至 1 5 - 4 及び第 3 のドライバ 1 6 - 1 乃至 1 6 - 4 の 2 倍の信号駆動能力を有する。これは例えば、第 1 のドライバ 1 4 - 1 乃至 1 4 - 4 をゲート幅Wの出力トランジ

10

20

30

40

スタで構成し、第2のドライバ15-1乃至15-4及び第3のドライバ16-1乃至16-4をゲート幅W/2の出力トランジスタで構成することにより実現される。

#### [0013]

ドライバ選択駆動ユニット11乃至13は、第1のドライバ14-1乃至14-4、第2のドライバ15-1乃至15-4、及び第3のドライバ16-1乃至16-4のうちで、信号F1乃至F3及び信号S1乃至S4により選択されたドライバのみを駆動する。選択的に駆動されたドライバの各々は、入力されるデータ信号DATAに応じた出力信号を出力する。更に、複数のドライバの出力信号が1つに纏められ、出力信号OUTとなる。このような選択的なドライバ駆動により、データ信号DATAに応じた出力信号OUTを、所望の信号駆動能力で駆動することができる。

[0014]

具体的には、ドライバ選択駆動ユニット11は、信号F1がアサートされると、信号S1乃至S4に応じて対応する第1のドライバ14-1乃至14-4を駆動する。同様に、ドライバ選択駆動ユニット12は、信号F2がアサートされると、信号S1乃至S4に応じて対応する第2のドライバ15-1乃至15-4を駆動する。ドライバ選択駆動ユニット13は、信号F3がアサートされると、信号S1乃至S4に応じて対応する第3のドライバ16-1乃至16-4を駆動する。

#### [0015]

例えばドライバ選択駆動ユニット11の場合には、信号F1がアサートされない限り、第1のドライバ14-1乃至14-4は駆動されない。信号F1がアサートされるときには、信号S1乃至S4のアサートに応じて、対応する第1のドライバ14-1乃至14-4が駆動される。論理としては、信号S1乃至S4の各々と信号F1のANDを取ることにより、第1のドライバ14-1乃至14-4を駆動する信号を生成すればよい。信号F2及びF3についても同様である。

[0016]

信号F1乃至F3は、半導体装置の工場出荷時等にヒューズを切断/非切断することにより決定される信号レベルを有する。信号S1乃至S4は、半導体装置を実装した状態でシステムからの設定により決定される信号レベルを有する。

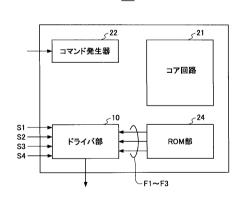

### [0017]

図2は、本発明による半導体装置の構成の一例を示す図である。図2の半導体装置20は、ドライバ部10、コア回路21、コマンド発生器22、レジスタ23、及びROM部24を含む。コア回路21は、半導体装置20の主要な機能を実現するための回路部分であり、例えば半導体装置20が半導体記憶装置である場合には、メモリアレイ、デコーダ、センスアンプ等の部分に相当する。このコア回路21から出力されるデータが、図1に示されるドライバ部10に供給される。またドライバ部10は、ROM部(ヒューズ回路)24から信号F1乃至F3を供給され、レジスタ23から信号S1乃至S4を供給されてよい。

[0018]

ROM部24は、内部にヒューズを含み、半導体装置20の工場出荷時等にこれらのヒューズを切断/非切断することにより、信号F1乃至F3の信号レベルが決定される。レジスタ23は半導体装置20の外部からの設定信号を受け取り、この設定信号に応じて信号S1乃至S4がレジスタ23に設定される。具体的には、例えばレジスタ設定コマンドを外部からコマンド発生器22に入力すると、コマンド発生器22がレジスタ23に信号ラッチ指示を供給する。レジスタ23は、信号ラッチ指示に応じて、設定信号を内部に取り込みラッチする。

## [0019]

上述のように信号 S 1 乃至 S 4 は、システム実装後にシステムからの指示等により設定される信号である。この信号 S 1 乃至 S 4 に応じて、信号駆動能力を例えば 2 5 % から 1 0 0 % の間で調整する。

## [0020]

10

20

30

図3は、信号S1万至S4と信号駆動能力との関係を示す図である。図3に示されるように、信号S1、S2、S3、及びS4が、それぞれHIGH、LOW、LOW、LOWであれば、25%の信号駆動能力が達成される。これは、例えばドライバ選択駆動ユニット11の場合であれば、信号S1のアサート(HIGH)状態に応答して、第1のドライバ14-1を駆動することにより実現される。また信号S1、S2、S3、及びS4が、それぞれHIGH、HIGH、LOW、LOWであれば、50%の信号駆動能力が達成される。これは、例えばドライバ選択駆動ユニット11の場合であれば、信号S1及び信号S2のアサート(HIGH)状態に応答して、第1のドライバ14-1及び14-2を駆動することにより実現される。信号駆動能力が75%及び100%の場合についても、同様にしてドライバを選択的に駆動することにより、所望の信号駆動能力が実現される。

[0021]

以下に、半導体装置の工場出荷時等にヒューズを切断/非切断することにより制御される信号F1乃至F3の信号レベル決定方法について説明する。

#### [0022]

半導体装置の製造工程後、工場出荷時等に、試験等によりドライバ部10の信号駆動能力を測定する。例えば、製造工程が終了した時点で、第1のドライバ14-1乃至14-4と第2のドライバ15-1乃至15-4とを駆動して、信号駆動能力を測定する。測定した信号駆動能力が所定の信号駆動能力に略等しいと判断すると、信号F1及びF2がアサート状態となり信号F3がネゲート状態となるように、ROM部24のヒューズの切断/非切断を行う。また測定した信号駆動能力が所定の信号駆動能力よりも低すぎると判断すると、信号F1乃至F3の全てがアサート状態となるように、ROM部24のヒューズの切断/非切断を行う。また測定した信号駆動能力が所定の信号駆動能力よりも高すぎると判断すると、信号F1がアサート状態となり信号F2及びF3がネゲート状態となるように、ROM部24のヒューズの切断/非切断を行う。

[0023]

即ち、信号駆動能力が高すぎも低すぎもしない場合には、例えば第1のドライバ14‐1乃至14‐4及び第2のドライバ15‐1乃至15‐4のみを駆動対象とするようにヒューズ設定する。また信号駆動能力が低すぎる場合には、例えば第1のドライバ14‐1乃至14‐4、第2のドライバ15‐1乃至15‐4、及び第3のドライバ16‐1乃至16‐4を駆動対象とするようにヒューズ設定する。またプロセスバラツキにより信号駆動能力が高すぎる場合には、例えば第1のドライバ14‐1乃至14‐4のみを駆動対象とするようにヒューズ設定する。なお更に信号駆動能力を低くしたい場合には、例えば第2のドライバ15‐1乃至15‐4のみを駆動対象とするように設定すればよい。このように、ドライバのトランジスタのゲート幅により信号駆動能力を調整してもよい。

[0024]

このように本発明による半導体装置においては、実装時にシステムからの指示により信号駆動能力を設定可能とすることにより、システムの伝送線の負荷に応じて信号駆動能力を調整可能とするとともに、工場出荷時等に行う試験結果に応じたヒューズ設定により信号駆動能力を設定可能とすることにより、製造バラツキに影響されない所望の信号駆動能力を実現することができる。これにより、半導体装置の製造バラツキ及びシステム構成に影響されること無く、高速で確実なチップ間のデータ転送を実現することができる。

[0025]

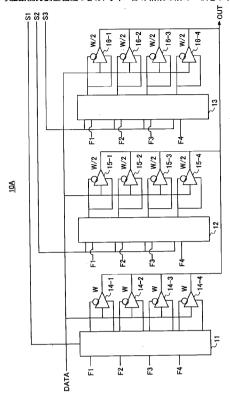

図4は、本発明による半導体装置に搭載される信号駆動能力調整機能つきのドライバ部の構成の別の一例を示す図である。図4において、図1と同一の構成要素は同一の番号で参照し、その説明は省略する。

## [0026]

図4の回路構成は図1の回路構成と同一である。但し、図4の構成においては、図1の場合と比較して、レジスタ23からの信号の位置とROM部24からの信号の位置とを交換してある。即ち、図1でレジスタ23からの信号S1乃至S4が入力されていた位置には、図4においてROM部24からの信号F1乃至F4が入力される。また図1でROM

10

20

30

40

10

20

30

40

50

部24からの信号F1乃至F3が入力されていた位置には、図4においてレジスタ23からの信号S1乃至S3が入力される。

#### [0027]

信号F1乃至F4は、半導体装置の工場出荷時等にヒューズを切断/非切断することにより決定される信号レベルを有する。信号S1乃至S3は、半導体装置を実装した状態でシステムからの設定により決定される信号レベルを有する。

#### [0028]

このように、ヒューズ設定により1セットあたり4つのドライバ(例えば4つの第1のドライバ14-1乃至14-4)のうちの所定数を駆動するように制御し、またシステムからの指定に基づき3つのセットのうちの所定のものを駆動するように構成してもよい。即ち、ヒューズ設定による信号とシステム設定による信号との両方に応じて信号駆動能力を設定可能であればよく、バッファ選択機構の具体的な構成について限定される必要はない。

## [0029]

図5は、本発明による半導体装置の構成の別の一例を示す図である。図5において、図2と同一の構成要素は同一の番号で参照し、その説明は省略する。

#### [0030]

図5の半導体装置20Aは、ドライバ部10、コア回路21、コマンド発生器22、及びROM部24を含む。図2の半導体装置20と比較して、図5の半導体装置20Aにおいてはレジスタ23が取り除かれている。ドライバ部10は、レジスタ23から信号S1乃至S4を受け取るのではなく、半導体装置20Aの外部から直接に信号S1乃至S4を受け取る。尚、レジスタ23を経由してS1乃至S4を受け取ることも可能である。なおROM部(ヒューズ回路)24から信号F1乃至F3を供給される点は、図2の構成と同様である。

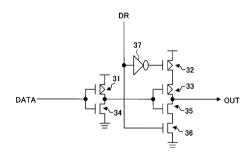

#### [0031]

図 6 は、ドライバの回路構成の一例を示す図である。図 6 に示されるドライバが、第 1 のドライバ 1 4 - 1 乃至 1 4 - 4、第 2 のドライバ 1 5 - 1 乃至 1 5 - 4、及び第 3 のドライバ 1 6 - 1 乃至 1 6 - 4 として用いられる。

### [0032]

図6のドライバは、PMOSトランジスタ31乃至33、NMOSトランジスタ34乃至36、及びインバータ37を含む。図1及び図4の回路では、データ信号DATAと同論理の出力信号OUTを出力する構成となっているので、図6のドライバは、PMOSトランジスタ31及びNMOSトランジスタ34からなるインバータと、PMOSトランジスタ33及びNMOSトランジスタ35からなるインバータとの2段構成となっている。ドライバがデータ信号DATAの反転信号を出力する構成でよいのであれば、PMOSトランジスタ31及びNMOSトランジスタ34からなるインバータ部分は不要である。

## [0033]

駆動信号 D R が H I G H の場合、 P M O S トランジスタ 3 2 及び N M O S トランジスタ 3 6 が導通する。従って、 P M O S トランジスタ 3 3 及び N M O S トランジスタ 3 5 からなるインバータに電源が供給され、ドライバが駆動されることになる。駆動信号 D R が L O W の場合には、 P M O S トランジスタ 3 2 及び N M O S トランジスタ 3 6 が非導通となり、ドライバは駆動されない。

### [0034]

駆動信号 D R は、図 1 又は図 4 に示されるドライバ選択駆動ユニット 1 1 乃至 1 3 から供給される信号である。例えばドライバ選択駆動ユニット 1 1 の場合には、前述のように、信号 S 1 乃至 S 4 の各々と信号 F 1 との A N D を取ることにより、第 1 のドライバ 1 4 - 1 乃至 1 4 - 4 を駆動する駆動信号 D R を生成すればよい。ドライバ選択駆動ユニット 1 2 及び 1 3 の場合も同様である。

#### [0035]

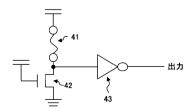

図7は、ROM部24に含まれるヒューズ回路の一例を示す図である。図7のヒューズ

10

20

30

40

50

回路は、ヒューズ41、NMOSトランジスタ42、及びインバータ43を含む。NMOSトランジスタ42は、ソース・ドレイン間が高抵抗で導通状態となるように設定される。ヒューズ41が非切断の状態では、インバータ43の入力がHIGHとなり、ヒューズ回路の出力はLOWとなる。ヒューズ41が切断された状態では、インバータ43の入力がLOWとなり、ヒューズ回路の出力はHIGHとなる。このようにしてヒューズの切断/非切断に応じた信号を供給することができる。

#### [0036]

図 7 の構成では、ヒューズが非切断の場合、ヒューズに常時電流が流れることになる。 従ってヒューズの数が大きくなると、消費電流が大きくなってしまう。

#### [0037]

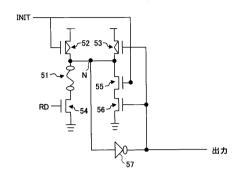

図8は、ROM部24に含まれるヒューズ回路の別の一例を示す図である。図8のヒューズ回路は、ヒューズ51、PMOSトランジスタ52及び53、NMOSトランジスタ54乃至56、及びインバータ57を含む。

## [0038]

電源投入直後(又はリセット直後)の状態では、初期設定信号INITがLOWであり、PMOSトランジスタ52は導通状態、NMOSトランジスタ55は非導通状態である。またヒューズ状態読み込み信号RDはLOWに設定され、NMOSトランジスタ54は非導通状態にある。従って、ヒューズ51の状態に関わらず、ノードNの電位はHIGHである。従ってインバータ57の出力はLOWとなる。

## [0039]

電源投入後(又はリセット後)所定の時間が経過すると、初期設定信号INITがHIGHになる。これによりPMOSトランジスタ52は非導通状態、NMOSトランジスタ55は導通状態となる。従って、PMOSトランジスタ53及びNMOSトランジスタ56からなるインバータとインバータ57とで構成されるラッチは、ノードNの電位がHIGHである状態をラッチして保持することになる。

#### [0040]

その後ヒューズ状態読み込み信号RDがHIGHになると、ヒューズ51の状態に応じて、ノードNの電位が異なる。ヒューズ51が切断されているときには、ノードNの電位はHIGHのままであり、ヒューズ回路の出力はLOWに設定される(LOWのままである)。ヒューズ51が非切断のときには、ノードNの電位はLOWになり、ヒューズ回路の出力はHIGHに設定される。このようにしてヒューズの切断/非切断に応じた信号を供給することができる。図8の構成では、動作時にヒューズに電流が流れないので、消費電流を削減することができる。

### [0041]

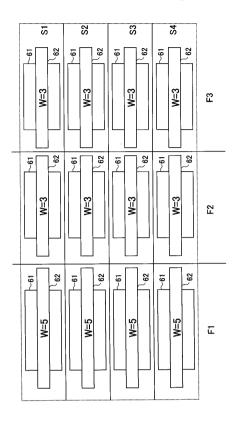

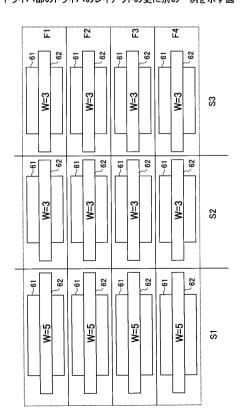

図9は、ドライバ部のドライバのレイアウトの一例を示す図である。図9において、ソース及びドレインを構成する拡散領域61とゲート62とで、ドライバの一部をなすトランジスタを構成する。図9の例では、トランジスタが縦3列、横4行に配置されている。

#### [0042]

左列のトランジスタ、中央列のトランジスタ、右列のトランジスタは、ゲート幅Wの比率が、5:3:3になっている。これらのトランジスタ列が、ヒューズ設定による製造バラツキ補正用の信号 F1乃至 F3に割当てられる。また図面上から第1行乃至第4行のトランジスタが、システム設定による伝送線負荷との整合用の信号 S1乃至 S4に割当てられる。

## [0043]

このように図9の構成では、ヒューズ設定による製造バラツキ補正についてはゲート幅の異なるトランジスタを選択することにより信号駆動能力の調整を行い、システム設定による伝送線負荷との整合についてはゲートの本数(トランジスタの個数)を選択することにより信号駆動能力の調整を行う。

#### [0044]

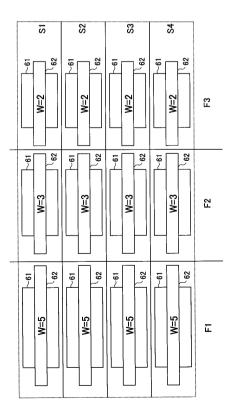

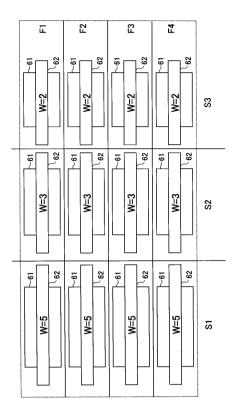

図10は、ドライバ部のドライバのレイアウトの別の一例を示す図である。図10にお

いて、ソース及びドレインを構成する拡散領域 6 1 とゲート 6 2 とで、ドライバの一部をなすトランジスタを構成する。図 1 0 の例では、トランジスタが縦 3 列、横 4 行に配置されている。

#### [0045]

左列のトランジスタ、中央列のトランジスタ、右列のトランジスタは、ゲート幅Wの比率が、5:3:2になっている。これらのトランジスタ列が、ヒューズ設定による製造バラツキ補正用の信号 F1乃至 F3に割当てられる。また図面上から第1行乃至第4行のトランジスタが、システム設定による伝送線負荷との整合用の信号 S1乃至 S4に割当てられる。

#### [0046]

図10の構成では、各列のトランジスタのゲート幅を全て異ならせることで、製造バラツキ補正に対して、よりきめ細かな信号駆動能力の調整が可能になる。即ち、ゲート幅Wが相対的に5、3、及び2のドライバを組み合わせることで、相対的な信号駆動能力を2、3、5、7(=5+2)、8(=5+3)、10(=5+3+2)に設定することが可能になる。

#### [0047]

図11は、ドライバ部のドライバのレイアウトの更に別の一例を示す図である。図11の構成は、図9に示す構成と同様であるが、左列のトランジスタ、中央列のトランジスタ、右列のトランジスタがそれぞれ、システム設定による伝送線負荷との整合用の信号S1乃至S3に割当てられる。また図面上から第1行乃至第4行のトランジスタが、ヒューズ設定による製造バラツキ補正用の信号F1乃至F4に割当てられる。即ち、図9のレイアウトが図1の構成に対応するのに対して、図11のレイアウトは図4の構成に対応することになる。

#### [0048]

このように図11の構成では、ヒューズ設定による製造バラツキ補正についてはゲートの本数(トランジスタの個数)を選択することにより信号駆動能力の調整を行い、システム設定による伝送線負荷との整合についてはゲート幅の異なるトランジスタを選択することにより信号駆動能力の調整を行う。

### [0049]

図12は、ドライバ部のドライバのレイアウトの更に別の一例を示す図である。図12 において、トランジスタの配置及び信号駆動能力調整用の信号の割当てについては、図1 1の構成と同様である。但し、左列のトランジスタ、中央列のトランジスタ、及び右列のトランジスタのゲート幅Wの比率が、5:3:2になっている。

### [0050]

このように図12の構成では、各列のトランジスタのゲート幅を全て異ならせることで、システム設定による伝送線負荷との整合に対して、よりきめ細かな信号駆動能力の調整が可能になる。即ち、ゲート幅Wが相対的に5、3、及び2のドライバを組み合わせることで、相対的な信号駆動能力を2、3、5、7(=5+2)、8(=5+3)、10(=5+3+2)に設定することが可能になる。

#### [0051]

以上、本発明を実施例に基づいて説明したが、本発明は上記実施例に限定されるものではなく、特許請求の範囲に記載の範囲内で様々な変形が可能である。

#### [0052]

例えば上記説明では、ROM部24はヒューズの切断/非切断によりプログラムされるものとしたが、ヒューズを使用することなく、例えば不揮発にプログラム可能な記憶素子を用いてもよい。本発明を実施するためには、ROM部24は、工場出荷時等に固定的に信号の状態を設定可能な素子であればよい。

### 【図面の簡単な説明】

#### [0053]

【図1】本発明による半導体装置に搭載される信号駆動能力調整機能つきのドライバ部の

10

20

30

40

構成の一例を示す図である。

- 【図2】本発明による半導体装置の構成の一例を示す図である。

- 【図3】信号S1乃至S4と信号駆動能力との関係を示す図である。

- 【図4】本発明による半導体装置に搭載される信号駆動能力調整機能つきのドライバ部の 構成の別の一例を示す図である。

- 【図5】本発明による半導体装置の構成の別の一例を示す図である。

- 【図6】ドライバの回路構成の一例を示す図である。

- 【図7】ROM部に含まれるヒューズ回路の一例を示す図である。

- 【図8】ROM部に含まれるヒューズ回路の別の一例を示す図である。

- 【図9】ドライバ部のドライバのレイアウトの一例を示す図である。

- 【図10】ドライバ部のドライバのレイアウトの別の一例を示す図である。

- 【図11】ドライバ部のドライバのレイアウトの更に別の一例を示す図である。

- 【図12】ドライバ部のドライバのレイアウトの更に別の一例を示す図である。

### 【符号の説明】

## [0054]

- 10 ドライバ部

- 11乃至13 ドライバ選択駆動ユニット

- 14-1乃至14-4 第1のドライバ

- 15-1乃至15-4 第2のドライバ

- 16-1乃至16-4 第3のドライバ

- 2 1 コア回路

- 22 コマンド発生器

- 23 レジスタ

- 2 4 R O M 部

### 【図1】

#### 本発明による半導体装置に搭載される 信号駆動能力調整機能つきのドライバ部の構成の一例を示す図

## 【図2】

## 本発明による半導体装置の構成の一例を示す図

<u>20</u>

| フマンド発生器 | コア回路 | ファロ路 | ファロカロ | ファロカロ

20

## 【図3】

信号S1乃至S4と信号駆動能力との関係を示す図

|    | 25% | 50% | 75% | 100% |  |

|----|-----|-----|-----|------|--|

| S1 | Н   | Н   | Н   | Н    |  |

| S2 | L   | Н   | Н   | Н    |  |

| S3 | L   | L   | Н   | Н    |  |

| S4 | L   | L   | L   | Н    |  |

【図4】

本発明による半導体装置に搭載される 信号駆動能力調整機能つきのドライバ部の構成の別の一例を示す図

## 【図5】

本発明による半導体装置の構成の別の一例を示す図 20A

## 【図6】

ドライバの回路構成の一例を示す図

## 【図7】

ROM部に含まれるヒューズ回路の一例を示す図

## 【図8】

ROM部に含まれるヒューズ回路の別の一例を示す図

【図9】

ドライバ部のドライバのレイアウトの一例を示す図

## 【図10】

ドライバ部のドライバのレイアウトの別の一例を示す図

【図11】

ドライバ部のドライバのレイアウトの更に別の一例を示す図

# 【図12】

## ドライバ部のドライバのレイアウトの更に別の一例を示す図

## フロントページの続き

(56)参考文献 特開平11-185479(JP,A)

特開2002-300023(JP,A)

特開平05-211432(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 1 L 2 7 / 0 4

H01L 21/822

H03K 19/0175

G11C 11/40