(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-332694

(P2006-332694A)

(43) 公開日 平成18年12月7日(2006.12.7)

(51) Int.CI.

H01L 21/60 (2006.01)

F 1

H01L 21/92 602D

H01L 21/92 604B

H01L 21/92 604Q

テーマコード(参考)

審査請求 有 請求項の数 8 O L (全 21 頁)

|            |                                   |                                                                                                       |

|------------|-----------------------------------|-------------------------------------------------------------------------------------------------------|

| (21) 出願番号  | 特願2006-200592 (P2006-200592)      | (71) 出願人 506285002<br>メジカ・コーポレーション<br>台湾 シンチュー, パーク・セカンド・<br>ロード, ナンバー 47, サイエンスペ<br>ースド・インダストリアル・パーク |

| (22) 出願日   | 平成18年7月24日 (2006.7.24)            | (74) 代理人 100089705<br>弁理士 松本 一夫                                                                       |

| (62) 分割の表示 | 特願2002-56997 (P2002-56997)<br>の分割 | (74) 代理人 100140109<br>弁理士 小野 新次郎                                                                      |

| 原出願日       | 平成14年3月4日 (2002.3.4)              | (74) 代理人 100075270<br>弁理士 小林 泰                                                                        |

|            |                                   | (74) 代理人 100080137<br>弁理士 千葉 昭男                                                                       |

|            |                                   | (74) 代理人 100096013<br>弁理士 富田 博行                                                                       |

最終頁に続く

(54) 【発明の名称】半導体表面上に金属バンプを形成する方法

## (57) 【要約】

【課題】 本発明は、半導体表面上に金属バンプを形成する方法を提供する。

【解決手段】 パシベーション層中に作製された導体パッドに対する開口を含んだパシベーション層上にバリヤー層を付着させる。導体パッドと整列していて、導体パッドの表面にはほぼ等しい直径を有していて、バリヤー層をオーバーレイする3つの金属層のカラムを形成させる。カラムを構成する3つの金属層は、バリヤー層と接触している層から始まって、ピラー金属層、アンダーバンプ金属層、およびはんだ金属層をこの順序にて含む。ピラー金属層の直径を減少させ、パシベーション層の表面からバリヤー層を選択的に除去し、その後にはんだ金属のリフロー処理を行って、本発明のはんだバンプを完成させる。

【選択図】 図1

## 従来技術

**【特許請求の範囲】****【請求項 1】**

半導体表面上に金属バンプを形成するための方法であって、

半導体表面を供給する工程；

導体パッドに対する開口を設けたパシベーション層をその上に有する、前記半導体表面を覆う導体パッドを供給する工程、このときパシベーション層の表面を覆うように、および前記開口中にバリヤー層が付着されている；

フォトレジスト層を、前記バリヤー層を覆うように付着させる工程；

前記フォトレジスト中に、導体パッドと整列したピラー開口を形成する工程；

前記ピラー開口中にピラー金属の層を付着させる工程；

アンダーバンプ金属の層を、前記ピラー金属を覆うように付着させる工程；

はんだ金属の層を、前記アンダーバンプ金属を覆うように付着させる工程；

フォトレジスト層を除去する工程；

ピラー金属層の直径を減少させる工程；

バリヤー層をエッチングする工程； および

はんだ金属をリフローして前記金属バンプを形成する工程；

を含む前記方法。

**【請求項 2】**

前記バリヤー層が、約 500 ~ 2000 オングストロームの厚さに、さらに好ましくは約 1000 オングストロームの厚さに施されたチタンを含む、請求項 1 記載の方法。

20

**【請求項 3】**

前記フォトレジスト層が、約 100 ~ 200  $\mu\text{m}$  の厚さに、さらに好ましくは約 150  $\mu\text{m}$  の厚さに施される、請求項 1 記載の方法。

**【請求項 4】**

前記ピラー金属層が、約 10 ~ 100  $\mu\text{m}$  の厚さに、さらに好ましくは約 50  $\mu\text{m}$  の厚さに施された銅を含む、請求項 1 記載の方法。

**【請求項 5】**

前記アンダーバンプ金属層が、約 1 ~ 10  $\mu\text{m}$  の厚さに、さらに好ましくは約 4  $\mu\text{m}$  の厚さに施されたニッケルを含む、請求項 1 記載の方法。

30

**【請求項 6】**

前記はんだ金属層が、約 30 ~ 100  $\mu\text{m}$  の厚さに、さらに好ましくは約 50  $\mu\text{m}$  の厚さに施されたはんだを含む、請求項 1 記載の方法。

**【請求項 7】**

半導体表面；

前記半導体表面を覆う誘電体層；

第 1 の材料で造られた、前記誘電体層を覆う導体パッド；

前記導体パッドと整列した開口を有する、前記誘電体層を覆うパシベーション層；

前記パシベーション層中に造られた前記開口を含む、前記誘電体層を覆うように付着させたバリヤー層； および

導体パッドと整列していて、導体パッドの表面エリアにほぼ等しい直径を有していて、バリヤー層と接触しているある層からはじまっている、ピラー金属層、アンダーバンプ金属層、およびはんだ金属層の 3 つの金属層で構成されるスタック；

を含み、このとき

前記ピラー金属の直径が適度の量だけ減少されており；

前記バリヤー層が、等方性エッチング法または異方性エッチング法を使用して除去されており； そして

前記はんだ金属がリフローされている；

金属バンプ接点。

**【請求項 8】**

前記バリヤー層が、約 500 ~ 2000 オングストロームの厚さに、さらに好ましくは

50

約 1 0 0 0 オングストロームの厚さに施されたチタンまたは銅を含む、請求項 7 記載の金属バンプ接点。

【請求項 9】

前記フォトレジスト層が、約 1 0 0 ~ 2 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 1 5 0  $\mu\text{m}$  の厚さに施される、請求項 7 記載の金属バンプ接点。

【請求項 10】

前記ピラー金属層が、約 1 0 ~ 1 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 5 0  $\mu\text{m}$  の厚さに施された銅を含む、請求項 7 記載の金属バンプ接点。

【請求項 11】

前記アンダーバンプ金属層が、約 1 ~ 1 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 4  $\mu\text{m}$  の厚さに施されたニッケルを含む、請求項 7 記載の金属バンプ接点。 10

【請求項 12】

前記はんだ金属層が、約 3 0 ~ 1 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 5 0  $\mu\text{m}$  の厚さに施されたはんだを含む、請求項 7 記載の金属バンプ接点。

【請求項 13】

半導体表面を供給し、導体パッドに対する開口を設けたパシベーション層をその上に有する、前記半導体表面を覆う導体パッドを供給する工程；

前記パシベーション層中に造られた開口を含んだバリヤー材料層を、前記パシベーション層の表面を覆うように付着させる工程；

金属の付着を妨げる材料の層を、バリヤー層の表面を覆うように付着させる工程； 20

金属の付着を妨げる材料の層をパターン焼き付け及びエッチングし、金属の付着を妨げる材料層中に、導体パッドと整列していて、導体パッドの表面エリアにほぼ等しい直径を有する開口を造る工程；

導体パッドと整列している表面エリア上のバリヤー層表面を部分的に露出させる工程；

ピラー金属の層を、バリヤー層の露出表面を覆うように付着させる工程；

アンダーバンプメタラージ (UBM) の層を、ピラー金属層の表面を覆うように付着させる工程；

バンプ金属の層を、UBM 層の表面を覆うように付着させる工程；

金属の付着を妨げる材料の層をバリヤー層の表面上から取り除く工程；

ピラー金属の層をエッチングし、ピラー材料の直径を適度の量だけ減少させる工程； 30

等方性エッチング法または異方性エッチング法を使用して、前記パシベーション層の表面から前記バリヤー層を除去する工程； および

前記はんだ金属をリフローして金属バンプを形成する工程；

を含む、半導体表面上に金属バンプを形成する方法。

【請求項 14】

前記バリヤー層が、約 5 0 0 ~ 2 0 0 0 オングストロームの厚さに、さらに好ましくは約 1 0 0 0 オングストロームの厚さに施されたチタンまたは銅を含む、請求項 1 3 記載の方法。

【請求項 15】

前記フォトレジスト層が、約 1 0 0 ~ 2 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 1 5 0  $\mu\text{m}$  の厚さに施される、請求項 1 3 記載の方法。 40

【請求項 16】

前記ピラー金属層が、約 1 0 ~ 1 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 5 0  $\mu\text{m}$  の厚さに施された銅を含む、請求項 1 3 記載の方法。

【請求項 17】

前記アンダーバンプ金属層が、約 1 ~ 1 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 4  $\mu\text{m}$  の厚さに施されたニッケルを含む、請求項 1 3 記載の方法。

【請求項 18】

前記はんだ金属層が、約 3 0 ~ 1 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 5 0  $\mu\text{m}$  の厚さに施されたはんだを含む、請求項 1 3 記載の方法。 50

**【請求項 19】**

バリヤー層の露出表面に対してその場でのスパッタクリーンを行う工程をさらに含み、このとき前記追加工程は、前記ピラー金属層を付着させる工程の前に行う、請求項13記載の方法。

**【請求項 20】**

金属の付着を妨げる前記材料がフォトレジストを含む、請求項13記載の方法。

**【請求項 21】**

半導体表面上に金属バンプを形成するための方法であって、

表面もしくは表面上に導体パッドが設けられている半導体表面を供給する工程、このとき前記導体パッドは、下側に存在する誘電体層上に位置しており、前記支持体の表面もしくは表面上における電気接点の少なくとも1個所と電気的に接触している；

10

表面層としてのバリヤー層を有する、前記金属バンプのためのベース層を供給する工程；

ピラー金属層、アンダーバンプ金属層、およびはんだ金属層の3つの連続した層を含む、前記金属バンプのためのカラムを供給する工程； および

前記金属バンプを供給する工程；

を含む前記方法。

**【請求項 22】**

金属バンプのためのベース層を供給する前記工程が、

前記導体パッドの表面を含めて、導体パッドの下側に存在する前記誘電体層の表面を覆うようにパシベーション層を付着させる工程；

20

前記パシベーション層をパターン焼き付け及びエッチングし、前記パシベーション層に開口を作製し、そして前記導体パッドの表面を部分的に露出させる工程、このとき前記パシベーション層において作製された前記開口は、前記導体パッドの表面エリアより適度の量だけ小さい； および

前記パシベーション層において作製された開口を含めて、前記パシベーション層の表面を覆うようにバリヤー材料の層を付着させる工程；

を含む、請求項21記載の方法。

**【請求項 23】**

前記金属バンプのためのカラムを供給する前記工程が、

金属の付着を妨げる材料の層を、バリヤー層の表面を覆うように付着させる工程；

金属の付着を妨げる材料の層をパターン焼き付け及びエッチングし、導体パッドと整列していて、導体パッドの表面にほぼ等しい直径を有する開口を、金属の付着を妨げる材料の層において作製し、そして導体パッドと整列している表面エリア上のバリヤー層の表面を部分的に露出させる工程；

ピラー金属の層を、バリヤー層の露出表面を覆うように付着させる工程；

アンダーバンプメタラージ(UBM)の層を、ピラー金属層の表面を覆うように付着させる工程；

バンプ金属の層を、UBM層の表面を覆うように付着させる工程；

金属の付着を妨げる材料の層をバリヤー層の表面上から取り除く工程；

ピラー金属層をエッチングし、ピラー金属の直径を適度の量だけ減少させる工程； および

40

等方性エッチング法または異方性エッチング法を使用して、前記パシベーション層の表面から前記バリヤー層を取り除く工程；

を含む、請求項21記載の方法。

**【請求項 24】**

金属バンプを供給する前記工程が、前記はんだ金属をリフローして金属バンプを形成する工程を含む、請求項21記載の方法。

**【請求項 25】**

前記バリヤー層が、約500～2000オングストロームの厚さに、さらに好ましくは

50

約 1 0 0 0 オングストロームの厚さに施されたチタンまたは銅を含む、請求項 2 1 記載の方法。

【請求項 2 6】

前記フォトレジスト層が、約 1 0 0 ~ 2 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 1 5 0  $\mu\text{m}$  の厚さに施される、請求項 2 1 記載の方法。

【請求項 2 7】

前記ピラー金属層が、約 1 0 ~ 1 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 5 0  $\mu\text{m}$  の厚さに施された銅を含む、請求項 2 1 記載の方法。

【請求項 2 8】

前記アンダーバンプ金属層が、約 1 ~ 1 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 4  $\mu\text{m}$  の厚さに施されたニッケルを含む、請求項 2 1 記載の方法。 10

【請求項 2 9】

前記はんだ金属層が、約 3 0 ~ 1 0 0  $\mu\text{m}$  の厚さに、さらに好ましくは約 5 0  $\mu\text{m}$  の厚さに施されたはんだを含む、請求項 2 1 記載の方法。

【請求項 3 0】

前記半導体表面が、半導体基板、プリント回路基板、フレックス回路、金属化基板、ガラス基板、および半導体素子実装支持体からなる表面群から選択される、請求項 2 1 記載の方法。

【請求項 3 1】

前記半導体基板が、半導体基板、セラミック基板、ガラス基板、ガリウムヒ素基板、シリコン・オン・インシュレータ (S O I) 基板、シリコン・オン・サファイア (S O S) 基板からなる基板群から選択される、請求項 3 0 記載の方法。 20

【請求項 3 2】

前記導体パッドが、アルミニウム、銅、またはこれらの化合物を含む、請求項 2 1 記載の方法。

【請求項 3 3】

バリヤー層の露出表面に対してその場でのスパッタクリーンを行う工程をさらに含み、このとき前記追加工程は、前記ピラー金属層を付着させる工程の前に行う、請求項 2 3 記載の方法。

【請求項 3 4】

金属の付着を妨げる前記材料がフォトレジストを含む、請求項 2 3 記載の方法。 30

【請求項 3 5】

ピラー金属層の直径を減少させる前記工程が、直径を 0 . 2  $\mu\text{m}$  より多く減少させることを含む、請求項 1 記載の方法。

【請求項 3 6】

前記アンダーバンプ金属と前記ピラー金属を熱的に酸化する追加工程をさらに含み、このとき前記追加工程は、はんだ金属をリフローして前記金属バンプを形成する工程の前に行う、請求項 1 記載の方法。

【請求項 3 7】

前記ピラー金属の直径が適度の量だけ減少されている、すなわち 0 . 2  $\mu\text{m}$  より多く減少されている、請求項 7 記載の金属バンプ接点。 40

【請求項 3 8】

前記はんだ金属をリフローする前に、前記アンダーバンプ金属と前記ピラー金属が酸化されている、請求項 7 記載の金属バンプ接点。

【請求項 3 9】

ピラー金属の直径を適度な量だけ減少させる前記工程が、直径を 0 . 2  $\mu\text{m}$  より多く減少させることを含む、請求項 1 3 記載の方法。

【請求項 4 0】

前記アンダーバンプ金属と前記ピラー金属を熱的に酸化する追加工程をさらに含み、このとき前記追加工程は、はんだ金属をリフローして金属バンプを形成する工程の前に行う 50

、請求項 1 3 記載の方法。

【請求項 4 1】

ピラー金属の直径を適度の量だけ減少させる前記工程が、直径を  $0.2 \mu m$  より多く減少させることを含む、請求項 2 3 記載の方法。

【請求項 4 2】

前記アンダーバンプ金属と前記ピラー金属を熱的に酸化する追加工程をさらに含み、このとき前記追加工程は、はんだ金属をリフローして金属バンプを形成する工程の前に行う、請求項 2 4 記載の方法。

【請求項 4 3】

前記バリヤー層を覆うようにシード層を付着させることに関して、前記パシベーション層の表面を覆うように及び開口中に前記バリヤー層を付着させた後に前記シード層を付着させる、請求項 1 記載の方法。 10

【請求項 4 4】

前記バリヤー層を覆うようにシード層を付着させた、請求項 7 記載の金属バンプ接点。

【請求項 4 5】

前記バリヤー層の表面を覆うようにシード層を付着させることに関して、前記パシベーション層の表面を覆うようにバリヤー材料の層を付着させた後に前記シード層を付着させる、請求項 1 3 記載の方法。

【請求項 4 6】

前記バリヤー層の表面を覆うようにシード層を付着させるという追加工程に関して、前記パシベーション層の表面を覆うようにバリヤー材料の層を付着させた後に前記シード層を付着させる、請求項 2 2 記載の方法。 20

【発明の詳細な説明】

【発明の開示】

【0 0 0 1】

発明の属する技術分野

本発明は集積回路素子の製造に関し、さらに詳細には、信頼性の高い微細ピッチのはんだバンプを低成本で作製する方法に関する。

【0 0 0 2】

従来の技術

半導体素子の実装については、長年にわたって、半導体素子の機能サイズのさらなる減少（素子性能の向上と素子製造コストの減少という二重の要件によって促される）に重点が置かれている。こうした傾向に基づいて半導体素子密度の大幅な増大がもたらされており、素子またはパッケージの I / O 能力に益々重点が置かれるようになっている。従って、集積回路と他の回路もしくはシステム部品とを接続する金属接続物がより一層重要なになってきており、半導体素子のさらなる小型化と相俟って、回路の性能に対して益々好ましくない影響を及ぼすようになっている。金属相互接続物の寄生容量と抵抗が増大すると、チップの性能が大幅に低下することがある。この点に関して最も重要なのは、電源バス（power bus）もしくは接地バス（ground bus）に沿っての電圧低下、および臨界信号路（critical signal paths）の RC 遅延である。より幅広の金属線を使用することによって抵抗を少なくしようとすると、これら金属線の容量がより高くなる。 40

【0 0 0 3】

こうした実装上の問題を解決するためにとられているアプローチの 1 つは、相互接続ワイヤ用に低抵抗の金属（たとえば銅）を開発することであるが、信号線間に低誘電率の材料が使用されている。I / O 能力の問題を解決するための他のアプローチは、適切な製造コストでチップを相互接続する高信頼性の方法をもたらすようなチップ実装技術を設計することである。こうしたことからフリップ・チップ・パッケージが開発された。

【0 0 0 4】

フリップ・チップ技術により、チップの A1 パッド上にバンプ（一般には Pb / Sn は 50

んだ)が作製され、パッケージ媒体(package media)(通常は、セラミックまたはプラスチックをベースとしている)にパンプが直接相互接続される。フリップ・チップは、最短路を介して、表を下にしてパッケージ媒体に接合される。これらの技術は、単一チップの実装だけでなく、複数チップ又は集積されたレベルの実装(パッケージがより大きい)にも、および幾つかのチップを収容してより大きな機能ユニットを形成するより高度な基板にも適用することができる。

#### 【0005】

いろいろなI/O相互接続物を使用するフリップ・チップ技術は、パッケージに対する極めて低いインダクタンスの相互接続と相俟って、素子への最も高い密度の相互接続を達成するという利点を有する。しかしながら、予備試験可能性(pre-testability)、接合後の目視検査、およびはんだバンプの疲労を防止するための熱膨張係数(CTE)の整合などが、まだ課題として残っている。幾つかのパッケージと一緒に実装する場合(たとえば、プラスチック基板へのセラミックパッケージの表面実装など)、CTEが不整合であると、はんだ-鉛接合部に対して大きな熱応力を引き起こすことがあり、従って温度サイクル操作によるはんだ疲労によって接合部の破壊が起こることがある。

#### 【0006】

従来技術の基板実装は、セラミックとプラスチックのフリップ・チップ実装を使用する。セラミック基板の実装は高コストであり、全体としてのパッケージの性能を制約することがわかっている。最近では、プラスチック基板のフリップ・チップ実装が見られるようになり、このタイプの実装が設計の大きな流れとなっていて、大量のフリップ・チップ・パッケージの製造においてしばしば使用されている。プラスチック基板のフリップ・チップ・パッケージは、低密度のフリップ・チップ集積回路(I/C)に使用されると充分に機能を果たす。I/Cから出ているピンの数が多い場合(すなわち350ピンを越える場合)、あるいはI/Cから出ているピンの数が350ピンより少ないが、必要とされる全体としてのパッケージサイズが小さい場合、プラスチックのフリップ・チップ構造物は複雑かつ高コストになる。このことは、プラスチックのフリップ・チップ・パッケージを製造するのに使用される多層構造物に対してトレースすることができる。この多層構造物を使用すると、一般には2~3ミルの範囲のパッケージ線密度が得られる。この線密度は、単層内のパッケージに対してチップI/Oからはんだボールまでファンアウト(fan out)を達成するには充分とは言えず、従って多層アプローチが求められることになる。多層アプローチは比較的厚い(50~75μm)誘電体層を使用し、これらの層は、プラスチックのフリップ・チップ・パッケージが実装されるラミネート基板の熱膨張係数(CTE)よりかなり高いCTEを有する。こうしたCTEの差を和らげるために、全体としてのパッケージを(熱的および機械的に)バランスさせなければならず、従ってさらなる材料と、これらの材料を施すためのさらなるプロセス工程が使用され、このためボール・グリッド・アレイ(Ball Grid Array)パッケージのコストが増し、いろいろ問題が生じる。

#### 【0007】

半導体素子を製造する上での、素子と素子機能(device features)とを相互接続する技術が、今日のようなサブミクロン素子の時代においても依然として続いている課題である。こうした目的に対してボンドパッドとはんだバンプがしばしば使用されており、従って、単純で、信頼性が高くて、そして低成本のボンドパッドとはんだバンプを製造することに継続的な努力が注がれている。

#### 【0008】

ボンドパッドは一般に、素子エレメントを結びつけるために、またダイの露出接点区域をもたらすために使用される。これらの接点区域は、ダイに対して外部の部品にダイを結びつけるのに適切である。たとえば、ボンドワイヤの一端が半導体ダイのボンドパッドに結びつけられ、そしてボンドワイヤの他端がプリント回路基板の一部に結びつけられる。従来技術に対しては、ボンドパッドの信頼性を高めつつ製造プロセスが単純化できるよう、ボンドパッドの製造面での改良が絶えず求められている。

10

20

30

40

50

## 【0009】

ボンドパッドに一般的に使用される材料としては、タンゲステンやアルミニウム等の金属材料があるが、ドーピング量の多いポリシリコンも材料を接触させるのに使用することができる。ボンドパッドは半導体素子の上表面に形成され、このとき導電性材料が絶縁性的誘電体層中に埋め込まれることが多い。ポリシリコンをボンドパッド材料として使用する場合、N-領域と接触させるためのn-型ドーパントをポリシリコンにドーピングすることができるが、P-領域と接触させるためのp-型ドーパントをポリシリコンにドーピングすることもできる。こうしたドーピングというアプローチにより、ドーパントの相互拡散とマイグレーションが防止される。ボンドパッドのエリアに対しては低い接触抵抗が必要とされるが、湿気や化学溶媒の吸収の防止、薄いフィルムの接着特性、離層、および亀裂についての検討がボンドパッドの作製に対しては重要である。

## 【0010】

アルミニウムボンドパッドを作製するのに使用される従来の加工シーケンスは、半導体表面（一般にはシリコン単結晶基板の表面）からスタートする。半導体表面を覆うようにイントラメタル誘電体（Intra Metal Dielectric）（IMD）の層を付着させ、IMD層の表面を覆うように金属（一般にはアルミニウム）の層を付着させる。金属の層をパターン焼き付けし、一般にはフォトレジスト層および写真平板法とエッチング法の従来法を使用してエッティングする。この方法でボンドパッドを作製した後、IMDの層を覆うようにパシベーション層を付着させる。再び写真平板法とエッティング法を使用して、ボンドパッドと整列した開口をパシベーション層中に作製する。

## 【0011】

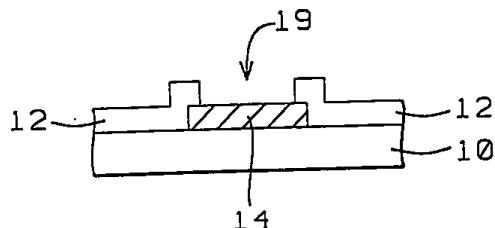

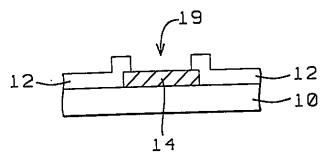

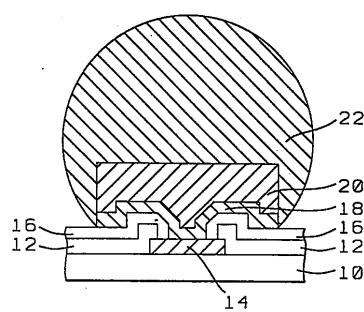

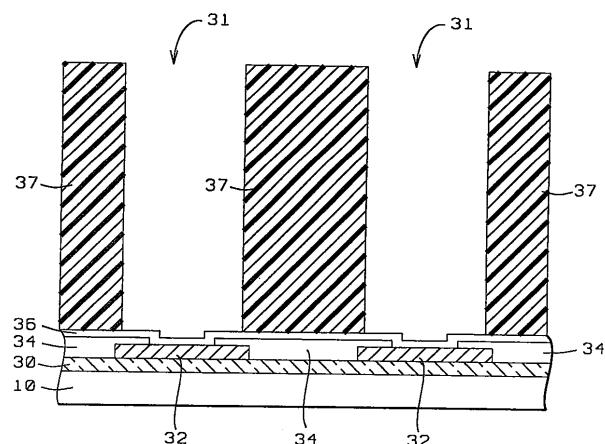

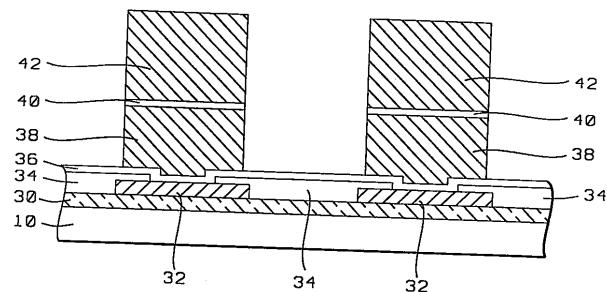

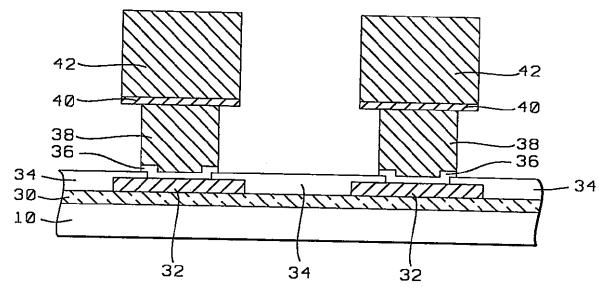

次に、導体パッド(contact pad)上にはんだバンプを作製するのに使用される従来法について説明する。図1～4は、相互接続バンプを作製するのに使用される方法の1つの例をしている。半導体表面10に金属導体パッド14が設けられており、半導体表面10はパシベーション層12で保護されている。パシベーション層12に開口19が造られており、金属導体パッド14の表面が、この開口19を通して露出されている。図2では、パシベーション層12の表面を覆うように誘電体層16を付着させている。誘電体層16をパターン焼き付け及びエッティングし、これによって金属パッド14と整列していて、金属パッド14の表面を部分的に露出させる開口21を誘電体層16に作製する。一般にはアンダーバンプメタラージ(UBM)を使用して、誘電体層16を覆うように金属層18を作製し、このとき金属層18は、開口21の内部で金属パッド14の表面と接触している。金属パッド14の上に位置する金属層18の区域は、プロセシングにおける後の段階で、相互接続バンプが造られる台座(pedestal)を形成する。この台座はさらに、フォトレジストもしくは誘電体物質を含有する1つ以上の層の付着とパターン焼き付けによって垂直方向に延ばすことができる（これらの追加層は図2には示されていない）。これらの層は本質的に層16の形状を有しており、幾つかある最終的な加工工程のうちの、相互接続バンプの形成のために施される工程時において除去される。

## 【0012】

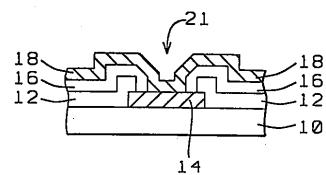

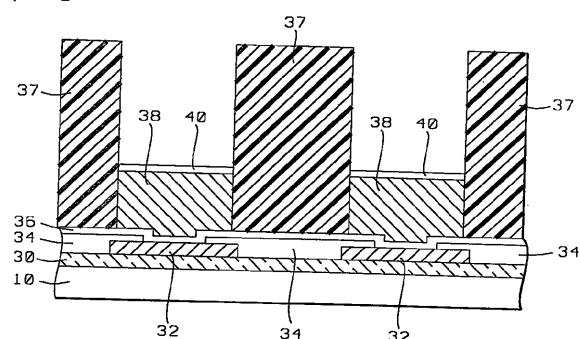

フォトレジスト層（図示せず）を付着させ、パターン焼き付けし、エッティングし、これによって導体パッド14と整列した開口を作製する。次いで、図3におけるたとえば銅やニッケルの金属層20（作製しようとする相互接続バンプの台座の一體部分を形成する）を、フォトレジスト層に作製された、また金属層18の表面上において作製された開口において電気メッキし、これによりメッキ工程時において層18が下側電極として機能する。従来技術での使用における層20は約1～10μmの厚さを有しており、通常の厚さは約5μmである。最後に、層20の表面にはんだ層22を電気メッキする。次いで、パターン焼き付けされたフォトレジスト層を除去する。

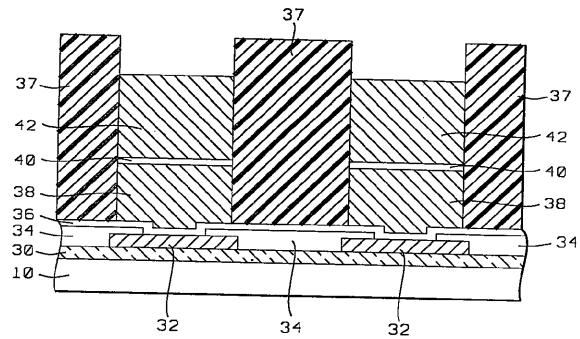

## 【0013】

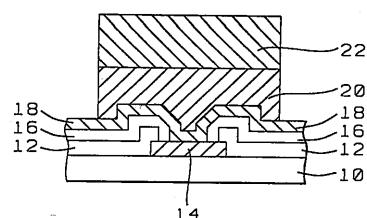

金属層18をエッティングし（図4）、相互接続バンプのための台座のみを所定の場所に残す。このエッティングプロセス時に、付着させた層20と22がマスクとして機能する。前記のように、図2における台座のさらなる造形のために誘電体層またはフォトレジスト

10

20

30

40

50

層の追加層が付着されている場合、これらの層もこの時点において除去される。

【0014】

はんだペースト又ははんだフラックス（図示せず）をはんだ層22に施し、通常は窒素雰囲気下でリフロー表面にてはんだ22を溶融し、これにより球状の相互接続バンプ22（図4に示す）が作製される。

【0015】

相互接続バンプの台座をさらに造形するのに使用できる誘電体層またはフォトレジスト層の上記追加層の他に、相互接続バンプの作製を目的としている応用の多くは、バリヤー層として機能するか、あるいは他の特定の目的（たとえば、種々のオーバーレイ層の接着性の改良、または隣接層間の物質の拡散防止）を有する金属層を利用する。これらの層はまとまって図4の層18を形成し、上記から明らかなように、作製されるバンプの形状に對して影響を及ぼし、従ってしばしばボール・リミティング・メタル（B a l l L i m i t i n g M e t a l）（BLM）層と呼ばれる。しばしば使用されるBLM層は、クロム、銅、および金の連続したオーバーレイ層であり、このときクロムは、下側に存在するアルミニウム導体パッドとの接着性を高めるのに使用されており、銅層は、下側層へのはんだ物質の拡散を防ぐよう機能しており、そして金層は、銅層の表面の酸化を防ぐよう機能している。BLM層は、図2～4における層18である。

10

【0016】

素子密度を上げると、作製された半導体素子の一部である部品とエレメントの接近度が増す。こうした接近度の増大は、半導体素子のエレメント間のスペーシングまたは“ピッチ”的減少をもたらす。最先端の技術は約200μmのピッチを有するはんだバンプを使用し、素子密度のさらなる増大に対して制約を及ぼす。信頼性という点において、はんだバンプのピッチをさらに減少させる上で制約を受ける（従って、はんだバンプに対して比較的大きなボールサイズが要求されるということである）。このようにはんだボールが比較的大きいと、はんだボールのピッチのさらなる減少が制約を受ける。

20

【0017】

多くの用途において、はんばバンプは、I/Oボンドパッドと基板すなわちプリント回路基板との間の相互接続物として使用されている。大きなはんだボールは高いスタンドオフをもたらす。なぜなら、高いスタンドオフのはんだボールは、より良好な熱的性能を有するからである（CTEの不整合を防止するのがより容易になり、従ってはんだボールに及ぼす熱応力が少なくなる）。従って、相互接続の信頼性を保持するためには、大きなはんだボールが必要とされる。ソフトエラー（soft error）（電気的または機能的なエラー）が起こるのを防ぐために低アルファ（low-alpha）のはんだが施され、これにより不注意なメモリ・ディスチャージ（memory discharge）や不正確な電圧セッティング（1または0）が起こる可能性が取り除かれる。

30

【0018】

Dassらによる米国特許第6,162,652号は、ボンドパッドの表面にはんだバンプを付着させることを含めて、集積回路素子を試験することについて開示している。

Farnsworthらによる米国特許第5,756,370号は、試験用半導体ダイとの一時的な接続を形成させるための規格適合の接点システム、および柔軟な接点システムを製造するための方法を開示している。

40

【0019】

Hubackerによる米国特許第5,554,940号は、接点バンプが取り付けられている半導体素子の精確な検査、および周辺テストパッドの形成について開示している。

【0020】

Seppalaによる米国特許第5,665,639号、Ohsawaによる米国特許第6,051,450号、およびLinによる米国特許第5,882,957号は、関連したバンププロセス（bump process）を開示している。

【0021】

50

Chao らによる米国特許第 5,633,535 号は、乾式レジストを使用するペデスタルプロセス (pedestal process) を開示している。

Lin による米国特許第 6,103,552 号は、はんだバンプの形成を含むウェハースケールの実装を達成するための方法とパッケージを開示している。

#### 【0022】

##### 発明の要旨

本発明の主要な目的は、微細ピッチのはんだバンプを作製する方法を提供することにある。

#### 【0023】

本発明の他の目的は、より小さなはんだバンプを作製する方法、そしてさらに、微細ピッチのはんだバンプの作製を可能にする方法を提供することにある。 10

本発明のさらに他の目的は、はんだバンプの高さを増大させることによる、高信頼性の微細ピッチのはんだバンプを作製するための原価効率の良い方法を提供することにある。この目的は、はんだバンプの信頼性が、はんだボールと下側に存在する基板との間の距離の 2 乗に比例して向上する、という考え方に基づいている。

#### 【0024】

本発明のさらに他の目的は、はんだバンプを作製する原価効率の良い方法を提供することにある。こうした原価効率の良い方法は、標準的なはんだ材料を使用することによって、そしてそれと共に高コストの“低 - はんだ”の必要性をなくすことによって達成される。 20

#### 【0025】

本発明のさらに他の目的は、メモリー製品に及ぼすアルファ効果を少なくすることによって微細ピッチはんだバンプを作製する、原価効率の良い方法を提供することにある。

本発明のさらに他の目的は、はんだバンプ作製プロセスが完了した後のフラックスの清浄操作が容易なはんだバンプ作製法を提供することにある。

#### 【0026】

本発明のさらに他の目的は、アンダーフィルの簡単な施しを可能にするはんだバンプ作製法を提供することにある。

本発明の方法によれば、半導体表面上に導体パッドを形成し、これに誘電体の層がオーバーレイしている。導体パッドを保護するために、誘電体層を覆うようにパシベーション層を付着させ、導体パッドの表面を部分的に露出させる開口をパシベーション層中に作製する。パシベーション層中に作製した開口を含めて、パシベーション層を覆うようにバリヤー層を付着させる。バリヤー層をオーバーレイしていく、導体パッドと整列していく、導体パッドの表面にはほぼ等しい直径を有する 3 つの金属層のカラムを形成する。これら 3 つの金属層は連続していく、バリヤー層と接触している層から始めて、ピラー金属の層、アンダーバンプ金属の層、およびはんだ金属の層で構成されている。ピラー金属層の直径を減少させ、はんだ金属のリフローにより本発明のはんだバンプの形成が完了した後に、パシベーション層の表面からバリヤー層を選択的に除去する。 30

#### 【0027】

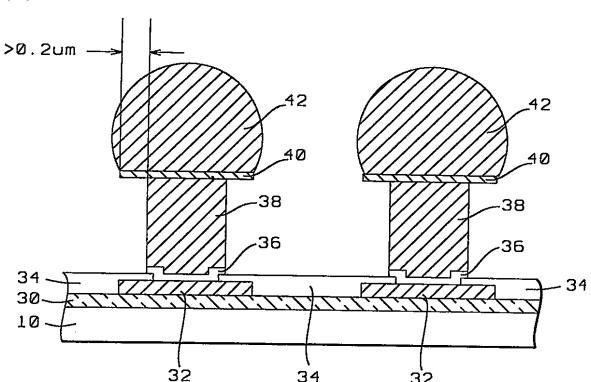

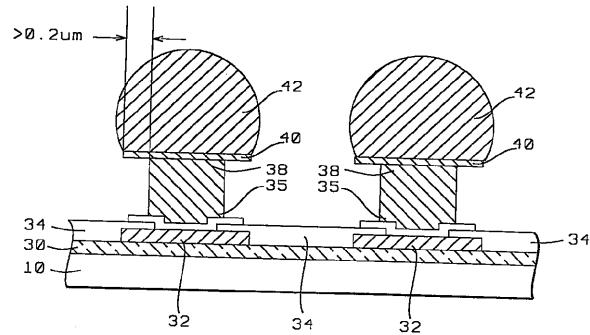

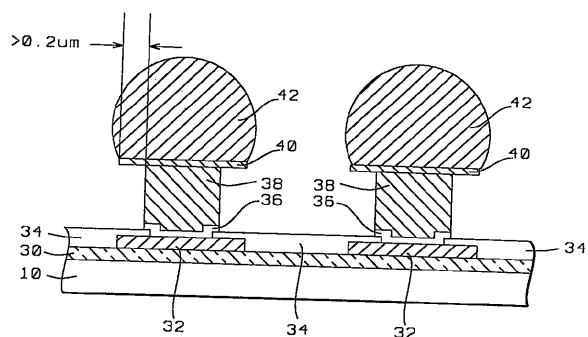

##### 好ましい態様の説明

図 5 を参照すると、第 1 のプロフィールを有する本発明の完成はんだバンプの断面が示されている。“プロフィール”とは、はんだバンプ作製における最終工程のうちの一工程時に、バリヤー金属の層がエッチングされるときの違いを表わしている。 40

#### 【0028】

本発明のはんだバンプの第 1 のプロフィールに対しては、露出バリヤー金属の等方性エッチングが行われ、露出バリヤー金属が除去される（但し、このバリヤー金属が本発明のピラー金属の下側に存在している場合は除く）。

#### 【0029】

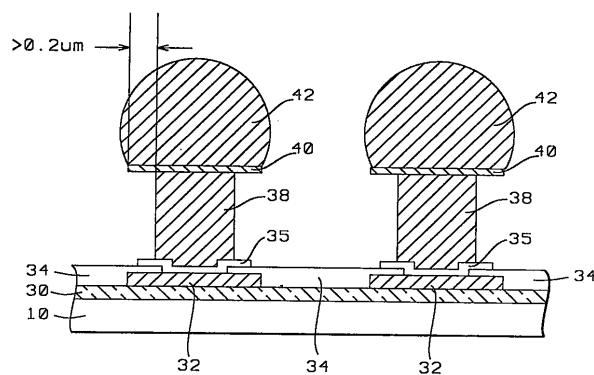

本発明のはんだバンプの第 2 のプロフィールに対しては、露出バリヤー金属の異方性エッチングが行われ、露出バリヤー金属が除去される（但し、このバリヤー金属が、はんだ

バンプのリフロー前に、はんだバンプによって異方性エッチングから遮蔽されている場合は除く)。

### 【0030】

図5において断面で示されているのは、本発明のはんだバンプの第1のプロフィールであり、このはんだバンプのエレメントは以下の通りである：

- 10、その上にはんだバンプが作製される半導体表面であって、一般にはシリコン半導体基板の表面である；

- 30、半導体表面10を覆うように付着させた誘電体層；

- 32、誘電体層30の表面上に作製された導体パッド；

- 34、誘電体層30の表面を覆うように付着させた、パターン焼き付けされたパシベーション層； パシベーション層34に開口が造られていて、導体パッド32の表面を部分的に露出させている；

- 36、等方的にエッチングされたバリヤー金属層； このバリヤー金属層は等方的にエッチングされているので、バリヤー金属は、パシベーション層34の表面から完全に除去されている(但し、オーバーレイしているはんだバンプのピラー金属(38)によってバリヤー金属が被覆されている場合は除く)；

- 38、はんだバンプのピラー金属；

- 40、はんだバンプのピラー金属38をオーバーレイするように作製されたアンダーバンプ金属の層；

- 40、はんだ金属。

10

20

20

### 【0031】

図6にて断面で示されているのは、本発明のはんだバンプの第2のプロフィールであり、このはんだバンプのエレメントは、異方的にエッチングされた層35(バリヤー金属層)が、異方性エッチングの特質により、図6の断面にて示すようにピラー金属38に対して突き出している、という点を除けば、本発明のはんだバンプの第1のプロフィールについて記載したエレメントと同じである。

### 【0032】

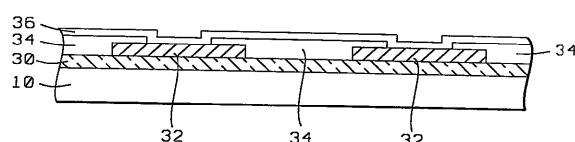

図7～16は、図5と6にて断面で示されているはんだバンプが得られる、本発明のプロセスの詳細を示している。

図7は、基板10の表面上部分の断面を示している。以下にエレメントについて記載する：

- 10、シリコン基板であり、その表面上に金属導体パッド32が作製されている；

- 30、基板10の表面を覆うように付着させた誘電体層；

- 32、金属導体パッド、一般にはアルミニウムを含み、誘電体層30の表面上に作製される；

- 34、誘電体層30の表面を覆うように付着させたパシベーション層であり、金属導体パッド32と整列していて、導体パッド32の表面を部分的に露出させている開口がパシベーション層34に作製されている；

- 36、パシベーション層34の表面を覆うように作製されたバリヤー金属層であって、パシベーション層34に作製されている開口を含み、下側に存在する導体パッド32と接触している。

### 【0033】

層30に対する誘電体材料としては、一般的に使用されている誘電体材料〔たとえば、二酸化ケイ素(ドーピングされている場合と、そうでない場合)、オキシ窒化ケイ素、パリレン、ポリイミド、スピノンガラス(spin-on-glass)、プラズマ酸化物、またはLPCVD酸化物など〕のいずれも使用することができる。本発明の誘電体層30の付着に対して使用される材料は上記材料に限定されず、当業界において広く使用されている誘電体のいずれも使用できる。

### 【0034】

金属導体パッド32の作製に対しては、たとえばアルミニウム-銅材料(アルミニウム

30

40

50

導体パッド作製用)を供給源として使用し、約100~400 の温度および約1~100ミリトルの圧力にて約10~400 sccmの流量で約400~11000 オングストロームの厚さに金属rfスパッタリングするという従来法を使用することができる。金属層を付着させた後、パターン焼き付けとエッチングを行ってアルミニウム導体パッド32を作製しなければならない。このパターン焼き付けとエッチングでは、従来の写真平板法、従来のパターン焼き付け法、および従来のエッチング法が使用される。Al-Cuの付着層は、Cl<sub>2</sub>/Arをエッチング液として使用して、50~200 の温度にて、Cl<sub>2</sub>に対しては約20 sccmの、Arに対しては1000 sccmのエッチング液流量にて、約50ミリトル~約10トルの圧力にて、30~200秒のエッチング時間でエッチングすることができる。

10

## 【0035】

代表的なアプリケーションでは、半導体素子もしくは半導体基板における導線(conducting lines)の種々の層の表面上に化学蒸着(CVD)法を使用して絶縁層(たとえば、酸化ケイ素や酸素含有ポリマー)を付着させて、導電性の相互接続線を互いに隔離する。相互接続線のパターン焼き付け層上にさらに絶縁層を付着させることができ、絶縁層に金属バイアスが造られた状態で相互接続線の連続層間の電気的接触が確立される。チップに対する電気的接触は一般に、相互接続金属線のパターン焼き付けレベルとの電気的インターフェースを形成するボンディング・パッドまたは導体パッドによって確立される。信号線と電源/接地線は、ボンディング・パッドまたは導体パッドに接続することができる。ボンディング・パッドまたは導体パッドをチップの表面上に作製した後、ボンディング・パッドの表面を覆うようにパシベーション層を付着させることによってボンディング・パッドまたは導体パッドを不動態化し、電気的に絶縁する。パシベーション層は、CVDによって付着される酸化ケイ素/窒化ケイ素(SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>)を含有してよい。このパシベーション層をパターン焼き付け及びエッチングして、パシベーション層にボンディング・パッドまたは導体パッドのための開口を作製し、その後に第2の比較的厚いパシベーション層を付着させて、さらなる絶縁、ならびに湿気や汚染物からの、またチップ集成時における機械的損傷からのチップ表面のさらなる保護を果たすことができる。

20

## 【0036】

パシベーション層の作製に対しては種々の材料が使用されている。パシベーション層は、CVDによって付着させた酸化ケイ素/窒化ケイ素(SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>)を含有してよく、感光性ポリイミドの層であってもよく、あるいは窒化チタンを含んでもよい。パシベーション層に対して使用されることの多い他の材料はリンをドーピングした二酸化ケイ素であり、一般には、低温CVD法を使用して、アルミニウム相互接続物の最終層上に付着させる。近年、パシベーション層の作製に対しては、感光性ポリイミドが使用されることが多い。従来のポリイミドは、半導体素子構造物におけるアプリケーションに対して多くの優れた特性を有する。感光性ポリイミドはこれらの同じ特性を有するが、これに加えて、フォトレジストマスクのようにパターン焼き付けすることができ、またパターン焼き付けとエッチングの後に、表面上に残存してパシベーション層として機能することもできる。一般には、表面の接着性を向上させ、緊張状態を低下させるために、たとえば従来のフォトレジスト・スピinn・コーティングによって、先ず最初に前駆体層を付着させる。低温でのプリベーク(pre-bake)の後に、たとえばステップアンドリピート式投影露光装置と光源としての紫外線とを使用して、この前駆体を露出させる。このようにして露出させた前駆体の部分に対して架橋反応を起こさせ、これによって、露出していない区域(架橋していない区域)がボンディング・パッド上に残る。引き続き行われる現像操作において、露出していないポリイミド前駆体層(ボンディング・パッド上)が溶解され、これによってボンディング・パッド上に開口が得られる。熱キュラーの最終工程を施すことにより、ポリイミドの耐久性高品質パシベーション層が残る。

30

## 【0037】

パシベーション層34を付着させるための本発明の好ましい材料はプラズマ・エンハン

40

50

スト窒化ケイ素 (P E S i<sub>3</sub>N<sub>4</sub>) であり、P E C V D 技術を使用して、約 350 ~ 450 の温度および約 2.0 ~ 2.8 トルの圧力にて、約 8 ~ 12 秒の継続時間で付着させる。P E S i<sub>3</sub>N<sub>4</sub> の層 32 は、約 200 ~ 800 オングストロームの厚さに付着させることができる。

#### 【0038】

次いで、P E S i<sub>3</sub>N<sub>4</sub> の層 34 をパターン焼き付け及びエッチングして、下側に存在する導体パッド 32 にオーバーレイしていて且つ整列している開口を層 34 中に作製する。

#### 【0039】

パシベーション層 34 のエッチングは、乾式エッチングプロセスに従って、A r / C F<sub>4</sub> をエッチング液として使用し、約 120 ~ 160 の温度および約 0.30 ~ 0.40 トルの圧力にて約 33 ~ 39 秒行うことができる。10

#### 【0040】

パシベーション層 34 のエッチングはさらに、乾式エッチングプロセスに従って、H e / N F<sub>3</sub> をエッチング液として使用し、約 80 ~ 100 の温度および約 1.20 ~ 1.30 トルの圧力にて約 20 ~ 30 秒行うことができる。

#### 【0041】

バリヤー層 (たとえば層 36) は通常、周囲の誘電体層およびシリコン層への相互接続金属の拡散を防ぐために使用される。相互接続金属のための銅を 1 つの例として使用することによって、バリヤー層のための材料を選択する上で適用される考え方の幾つかが明らかになる。銅は比較的コストが低く、抵抗率が低いけれども、二酸化ケイ素やケイ素中への拡散係数が比較的大きく、従って一般には相互接続金属としては使用されない。銅は、相互接続物から二酸化ケイ素の層中に拡散することがあり、従って誘電体が導電性になり、二酸化ケイ素層の絶縁耐力が低下する。銅の相互接続物は、少なくとも 1 つの拡散バリヤーによって封入して、二酸化ケイ素層への拡散を防止しなければならない。窒化ケイ素は銅に対する拡散バリヤーであるが、従来技術によれば、相互接続物は二酸化ケイ素と比較して高い誘電率を有するので、相互接続物が窒化ケイ素層の上に存在すべきではないとされている。誘電率が高いと、相互接続物と基板との間にキャパシタンスの所望の増大を引き起こす。20

#### 【0042】

典型的な拡散バリヤー層は、窒化ケイ素、ホスホシリケートガラス (P S G) 、オキシ窒化ケイ素、アルミニウム、酸化アルミニウム (A l<sub>x</sub>O<sub>y</sub>) 、タンタル、T i / T i N 、T i / W 、ニオブ、またはモリブデンを含有してよく、T i N から形成されるのがさらに好ましい。バリヤー層はさらに、オーバーレイしているタングステン層の密着性を向上させるのにも使用することができる。30

#### 【0043】

バリヤー層の厚さは約 500 ~ 2000 オングストロームであるのが好ましく、約 300 オングストロームであるのがさらに好ましく、r f スパッタリングを使用して付着させることができる。

#### 【0044】

バリヤー層 36 を作製した後、ウェハーの表面を覆うようにしてシード層 (図 7 には示されていない) をプランケット付着させることができる。ウェハーの表面上に付着させるシード層に対しては、従来の金属シード材料のいずれも使用することができる。金属シード層は、スパッター・チャンバーまたはイオンメタルプラズマ (I M P) チャンバーを約 0 ~ 300 の温度および約 1 ~ 100 ミリトルの圧力にて使用し、たとえば銅または銅合金を供給源として約 10 ~ 400 s c c m の流量にて使用して (前述) 、そしてアルゴンを周囲ガスとして使用して付着させることができる。40

#### 【0045】

図 8 は、バリヤー層 36 の表面上にフォトレジスト層 37 を付着させた後の基板の断面を示している。フォトレジスト層 37 をパターン焼き付け及びエッチングし、フォトレジ

スト層 37 に開口 31 を作製する。開口 31 は、バリヤー層 36 の表面を部分的に露出させる。フォトレジスト層 37 は、通常は約 100 ~ 200 μm の厚さに、さらに好ましくは約 150 μm の厚さに施す。

#### 【 0 0 4 6 】

フォトレジスト層 37 は、通常は約 100 ~ 200 μm の厚さに、さらに好ましくは約 150 μm の厚さに施す。フォトレジスト層 37 の付着と現像に対して使用される方法は従来の写真平板法を使用する。写真平板は広く使用されている方法であり、該方法によれば、フォトレジスト層に対してスピニングし、フォトレジストをパターンに従って露出させるよう所望のパターンを有するフォトマスクを通してフォトレジスト上に光を投射し、フォトレジストを現像し、現像されていないフォトレジストを洗い落とし、そしてプラズマエッチングして、フォトレジストが洗い落とされた区域を清浄にすることによって、パターン焼き付けされた層が形成される。露出されたレジストを可溶性にして（ポジティブ・ワーキング）洗い落とすこともできるし、あるいは不溶性にして（ネガティブ・ワーキング）パターンを形成させることもできる。10

#### 【 0 0 4 7 】

付着させたフォトレジスト層 37 に対し、パターン焼き付けとエッチングの前にキュアーまたはプリベークして、フォトレジスト層 37 の表面をさらに硬化させることができる。。

#### 【 0 0 4 8 】

フォトレジスト層 37 は、O<sub>2</sub> プラズマを施し、次いで H<sub>2</sub>SO<sub>4</sub> 溶液、H<sub>2</sub>O<sub>2</sub> 溶液、および NH<sub>4</sub>OH 溶液を使用して湿潤ストリッピングすることによってエッチングすることができる。フォトレジストを他の手段によってストリッピングした後には、硫酸 (H<sub>2</sub>SO<sub>4</sub>) および H<sub>2</sub>SO<sub>4</sub> と他の酸化剤 [たとえば過酸化水素 (H<sub>2</sub>O<sub>2</sub>)]との混合物が広く使用されている。ストリッピングしようとするウエハーを混合物中に約 100 ~ 約 150 の温度で 5 ~ 10 分浸漬し、脱イオン水を使用して清浄化処理し、そして乾燥窒素によって乾燥することができる。強くポストベークされたレジストを残留物が残らないよう除去するには、無機レジストストリッパー (たとえば硫酸混合物) が極めて有効である。これらは有機ストリッパーより有効であり、浸漬時間を長くするほど、より清浄で且つより残留物の少ない表面を得ることができる。20

#### 【 0 0 4 9 】

フォトレジスト層 37 はさらに、プラズマ酸素アッシングと慎重なウェット・クリーニングを使用して部分的に除去することもできる。酸素プラズマアッシングは、フォトレジストを高度に酸化された環境 (たとえば酸素プラズマ) において加熱することであり、これによりフォトレジストが容易に除去されるアッシュに転化される。酸素プラズマアッシングの後に、フッ化水素酸の 200 : 1 希釀溶液中にて 90 秒ネイティブ・オキシド・ディップ (native oxide dip) を行うことができる。30

#### 【 0 0 5 0 】

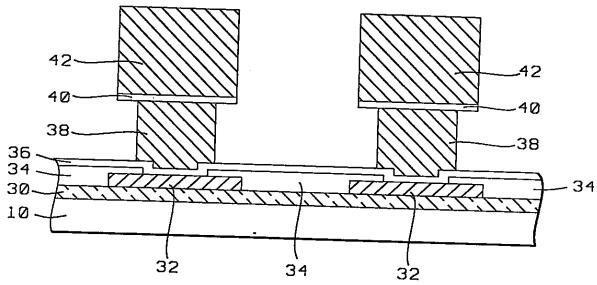

図 9 は、フォトレジスト層 37 中に作製されている開口 31 によって拘束されるピラー金属層 38 をバリヤー材料層 36 の表面上に付着 (電気メッキにより) させた後の、基板 10 の断面を示している。金属層 38 (これらの層が本発明のはんだバンプの完成構造物において果たす役割から見て、この金属はピラー金属と呼ばれる) の表面上に、アンダーバンプ金属の層 40 が電気メッキ等の付着法を使用して付着されている。40

#### 【 0 0 5 1 】

層 36 はチタンまたは銅を含むのが好ましく、約 500 ~ 2000 オングストロームの厚さに付着させるのが好ましく、約 1000 オングストロームの厚さに付着させるのがさらに好ましい。

#### 【 0 0 5 2 】

層 38 は銅を含むのが好ましく、約 10 ~ 100 μm の厚さに施すのが好ましく、約 50 μm の厚さに施すのがさらに好ましい。

層 40 はニッケルを含むのが好ましく、約 1 ~ 10 μm の厚さに施すのが好ましく、約 50

4 μmの厚さに施すのがさらに好ましい。

【0053】

図10は、本発明のプロセスが、フォトレジスト層37中に作製されている開口31によって拘束されるはんだ金属の電気メッキ層42を、アンダーバンプ金属(UBM)層40の表面上にさらに有している場合の断面を示している。

【0054】

UBM層40(一般にはニッケルであって、厚さは約1~10μm)は、ピラー金属層38を覆うように電気メッキする。バンプ金属(一般にははんだ)の層42は、UBM層40と接触している状態にて約30~100μmの厚さに、さらに好ましくは約50μmの厚さに電気メッキして作製する。電気メッキした金属の層38、40、および42は、フォトレジスト層37中に作製されている開口31に中心を置いている。

10

【0055】

図11に示されている断面においては、パターン焼き付けされたフォトレジスト層37がバリヤー層36の表面上から除去された状態が示されている。フォトレジスト層を除去するための前述の方法とプロセシング条件を、図11の断面にて示されているような層37の除去のためにも適用することができる。本発明ではさらに、図12の断面にて示すように、ピラー金属材料に対して選択的な湿式化学エッティング法または等方性乾式エッティング法を使用してピラー金属38の部分エッティングを行う。言うまでもないことであるが、エッティングパラメーター(このうちエッティング時間が最も有益である)を調節することによって、ピラー金属層38の直径を所望する殆どいかなる値にも減少させることができる。ピラー金属層38の直径が減少される程度に対して及ぼされる制約は、湿式エッティングプロセスによって及ぼされることはなく、金属バンプの信頼性および機能性に対しては問題が生じる。ピラー金属層38の残留直径があまりにも小さいと、はんだバンプの堅牢性に影響を及ぼし、また金属バンプの抵抗を増大させるという影響を及ぼすことがある。

20

【0056】

はんだ金属がリフローされる前の本発明の最終的な2つのプロセシング工程が図13と図14の断面に示されており、バリヤー層36の露出表面のエッティングに影響を及ぼす。等方性エッティングを使用して(図13)、露出されたバリヤー層が完全に除去される。異方性エッティングを使用して(図14)、はんだ金属のカラム42の存在によって、バリヤー層のエッティングが部分的に妨げられる。

30

【0057】

ピラー38のアンダーカット形状により、引き続き行われるはんだリフロー時におけるピラー38とUBM層40のウェッティングが防止される、と考えられる。さらに、空気に露出されることによって、ピラー38とUBM層40のサイドウォールが酸化され、従って引き続き行われるはんだリフロー時におけるこれら表面のウェッティングが防止される、と考えられる。必要に応じて、ピラー38とUBM層40のサイドウォールは、たとえば約240°のリフロー温度未満での熱酸化(たとえば約125°における酸素雰囲気での加熱)によってさらに酸化してもよい。

【0058】

図15と図16は、はんだ金属がリフローされた後の、本発明のはんだバンプの最終的な断面を示している。図15は図13に、そして図16は図14に対応しており、図13と図14を使用して説明されたバリヤー層36のエッティングに関係している。図15における断面で示されているエッティングされたバリヤー材料層36は、図13において示されているエッティングされたバリヤー材料層に対応している、という点に留意しなければならない。図16と図14との間に同じ対応が存在する。

40

【0059】

金属バンプの作製に対して使用される上記のプロセシング工程(電気メッキ工程)は、フォトレジスト層の付着後にこのフォトレジスト層をキュアまたはプリベークする工程で補足することができる。

【0060】

10

20

30

40

50

本発明を要約すると以下のようになる：

- ・本発明の準備にあたって、半導体表面を供給し、半導体表面上に誘電体層を付着させ、誘電体層上に導体パッドを供給し、導体パッドが露出表面を有し、前記導体パッドの表面を含めた半導体表面上にパシベーション層を付着させ、パシベーション層に対しパターン焼き付けとエッチングを施し、これによりパシベーション層中に開口を作製し、導体パッドの表面を部分的に露出させ、パシベーション層中の開口を導体パッドに関して中心に配置する。

#### 【0061】

- ・本発明は、パシベーション層の表面上に付着させたバリヤー層からスタートしており、パシベーション層中に作製されている開口を通して導体パッドと接触している。

10

- ・バリヤー層の表面上にフォトレジスト層を付着させる。

#### 【0062】

- ・フォトレジスト層に対しパターン焼き付けとエッチングを施してフォトレジスト層を貫く開口を作製し、このフォトレジスト中の開口を、導体パッドに関して整列させて中心に置くようとする。

#### 【0063】

- ・ピラー金属層、アンダーバンプ金属層、およびはんだ金属層をこの順序にて、フォトレジスト層中に作製されている開口によって拘束される状態で付着させる。

- ・パターン焼き付けされたフォトレジスト層をバリヤー層の表面から除去する。

#### 【0064】

- ・ピラー金属層をエッチングし、ピラー金属の直径を減少させる。

- ・等方性エッチングまたは異方性エッチングを使用してバリヤー層をエッチングする。

- ・はんだ金属をリフローする。

20

#### 【0065】

本発明は以下のようない点をもたらす。

- ・信頼性を高める上でボールの高さが極めて重要なポイントである。パッケージのオーバーレイ層間の熱的不整合を防止するために（たとえば、半導体素子と下側に存在するプリント回路基板など）、オーバーレイしているエレメント間の距離を増大させることが重要である。本発明では、こうしたことが達成される。

30

#### 【0066】

- ・はんだボールがより大きくなると（より良好な熱的性能又はより高い信頼性を得るために）ピッチが増大し、この点は、最新技術に基づく設計要件とは相容れない。

- ・高さを与えることなく小さなはんだボールが使用される場合、小さな隙間をアンダーフィルするのが極めて困難である。

#### 【0067】

- ・本発明を使用すると、はんだが半導体素子から比較的離れた個所にて除去され、このことは低 - はんだを施す必要がないということを意味している（ - 粒子はメモリー物品においてソフト上のエラーを生じ、鉛は、腐食すると - 粒子を放出することが知られている）。

40

#### 【0068】

- ・ピラー金属に関しては、良好な導電性と延性を有する金属（たとえば銅）を選択する必要がある。これは、熱応力の影響を弱めることによって改良された熱的性能を得るためのものである。

#### 【0069】

- ・本発明のはんだバンプのピラーの高さが重要であり、高いスタンドオフという目的を達成するために約 10 ~ 100 μm でなければならない。

- ・アンダーバンプ金属層のために使用される金属は、はんだリフロー時にオーバーレイしているはんだに対して良好な接着性を有していなければならないが、あまりにも早く溶解してはならず、また早く溶解した場合にははんだに対するバリヤーを形成しなければならない、という点において重要である。さらに、UBM 金属は、空気にさらされると保護

50

酸化物層を形成することがあり、従ってリフロープロセス時において、UBM金属の周りでのピラー金属に対するはんだウェッティングが妨げられる。従ってUBM金属にはニッケルが好みしい。

【0070】

幾つかの特定の実施態様に関して本発明を説明してきたが、本発明がこれらの実施態様に限定されることはない。本発明の精神を逸脱することなく種々の変形や改良形が可能であることは、当業者にとっては言うまでもないことである。従って、特許請求の範囲の範囲内に含まれるこのような全ての変形や改良形も本発明に含まれるものとする。

【図面の簡単な説明】

【0071】

【図1】図1は、導体パッドが作製されている表面上での半導体表面の断面を示しており、半導体表面がパターン焼き付けされたパシベーション層で被覆されている。図1は、電気的接触のポイントにオーバーレイするはんだバンプを作製する従来技術の方法を示している。

【図2】図2は、パターン焼き付けされた誘電体層と金属層が半導体表面上に作製された後の、図1の断面を示している。図2は、電気的接触のポイントにオーバーレイするはんだバンプを作製する従来技術の方法を示している。

【図3】図3は、バンプ金属の層とはんだ化合物を選択的に付着させた後の、図2の断面を示している。図3は、電気的接触のポイントにオーバーレイするはんだバンプを作製する従来技術の方法を示している。

【図4】図4は、過剰の層を半導体表面から除去した後の、またはなどをリフローして相互接続バンプを形成させた後の断面を示している。図4は、電気的接触のポイントにオーバーレイするはんだバンプを作製する従来技術の方法を示している。

【図5】図5は、本発明の完成したはんだバンプの断面を示している。

【図6】図6は、本発明の完成したはんだバンプの断面を示している。

【図7】図7は、誘電体層が付着されていて、金属パッドが作製されていて、パシベーション層が付着およびパターン焼き付けされていて、そしてバリヤー材料層が付着されている状態の半導体表面の断面を示している。

【図8】図8は、パターン焼き付けされたフォトレジスト層を図7の構造物上に作製した後の断面を示している。

【図9】図9は、ピラー金属層を金属パッドと整列させて作製し、アンダーバンプ金属をピラー金属の表面上に付着させた後の断面を示している。

【図10】図10は、はんだ金属をアンダーバンプ金属上に電気メッキした後の断面を示している。

【図11】図11は、パターン焼き付けされたフォトレジスト層を表面から除去した後の断面を示している。

【図12】図12は、ピラー金属の直径を減少させた後の断面を示している。

【図13】図13は、等方性エッティングを使用してバリヤー層をエッティングして第1のプロフィールを作製した後の断面を示している。

【図14】図14は、異方性エッティングまたはRIEを使用してバリヤー層をエッティングして第2のプロフィールを作製した後の断面を示している。

【図15】図15は、第1のプロフィールのはんだ金属をリフローした後の断面を示している。

【図16】図16は、第2のプロフィールのはんだ金属をリフローした後の断面を示している。

10

20

30

40

【図1】

従来技術

【図2】

従来技術

【図3】

従来技術

【図4】

従来技術

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

【図13】

【図14】

【図16】

【図15】

**【手続補正書】**

【提出日】平成18年8月23日(2006.8.23)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

基板；

前記基板を覆うパッド；および

前記パッドを覆うバンプ

を含む回路構成要素であって、前記バンプが、

前記パッドを覆う第一の金属層；

前記第一の金属層を覆う銅層、ここで、前記銅層は10～100μmの厚さを有する；

前記銅層を覆う第二の金属層；および

前記第二の金属層を覆うはんだ層

を含む、前記回路構成要素。

**【請求項2】**

前記第二の金属層がニッケルを含む、請求項1記載の回路構成要素。

**【請求項3】**

前記はんだ層が30～100μmの厚さを有する、請求項1記載の回路構成要素。

**【請求項4】**

前記第二の金属層が1～10μmの厚さを有する、請求項1記載の回路構成要素。

**【請求項5】**

前記第一の金属層がチタンを含む、請求項1記載の回路構成要素。

**【請求項6】**

前記第一の金属層が500～2000オングストロームの厚さを有する、請求項1記載の回路構成要素。

**【請求項7】**

前記第二の金属層の端と前記銅層の端との間の距離が0.2μmより大きい、請求項1記載の回路構成要素。

**【請求項8】**

前記基板を覆う絶縁層を更に含み、前記第一の金属層が、前記絶縁層中の開口により露出された前記パッドを覆う、請求項1記載の回路構成要素。

## フロントページの続き

(74)代理人 100123548

弁理士 平山 晃二

(72)発明者 ジン - ユアン・リー

台湾シン - チュー , アン - ホー・ストリート , レイン 4 , ナンバー 11

(72)発明者 ムウ・シュン・リン

台灣シン - チュー , ジンサン・テンス・ストリート 28

(72)発明者 チン - チエン・ファン

台灣シン - チュー , クアンファ・セヴンス・ストリート 38 - 24 , 11エフ - 1