(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5435640号

(P5435640)

(45) 発行日 平成26年3月5日(2014.3.5)

(24) 登録日 平成25年12月20日(2013.12.20)

(51) Int.Cl.

F 1

H01L 27/146 (2006.01)

H01L 27/14 A

H04N 5/369 (2011.01)

H04N 5/335 690

H04N 5/374 (2011.01)

H04N 5/335 740

請求項の数 6 (全 7 頁)

(21) 出願番号 特願2009-551287 (P2009-551287)

(86) (22) 出願日 平成20年2月29日 (2008.2.29)

(65) 公表番号 特表2010-520614 (P2010-520614A)

(43) 公表日 平成22年6月10日 (2010.6.10)

(86) 國際出願番号 PCT/IB2008/001791

(87) 國際公開番号 WO2008/125986

(87) 國際公開日 平成20年10月23日 (2008.10.23)

審査請求日 平成23年2月28日 (2011.2.28)

(31) 優先権主張番号 11/713,301

(32) 優先日 平成19年3月1日 (2007.3.1)

(33) 優先権主張国 米国(US)

(73) 特許権者 510051299

タイ, ヒョク ナム

シンガポール国 730409 シンガポール, #13-109, ウードランズ ストリート 41, ブロック 409

(74) 代理人 100091683

弁理士 ▲吉▼川 俊雄

(72) 発明者 テー, ヒョク, ナム

シンガポール共和国, 730409 シンガポール, ブロック 409, ウッドランズ ストリート 41, #13-109

審査官 石坂 博明

最終頁に続く

(54) 【発明の名称】画素間分離されたイメージセンサ

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のフォトダイオードが低濃度にドープされたp型基板に配置されている画素アレイを有するイメージセンサであって、

上記フォトダイオードは、

上記基板における中濃度にドープされたp型の第1の領域と、

上記第1の領域に隣接し、上記第1の領域に対する第1の横位置に配置され、上記基板における低濃度にドープされたn型の第2の領域と、

上記第1の領域の下で、上記第2の領域と他のフォトダイオードの第2の領域との間に、

上記第1の領域に対する第2の横位置に配置され、上記基板における中濃度にドープされたp型のバリア領域とを含み、

上記第1の横位置は、上記画素アレイの中心と上記画素アレイの外側領域との間で変動し、

上記バリア領域は、中性領域を含み、

上記中性領域は、上記第2の領域から上記中性領域に延びる空乏領域が、他のフォトダイオードの第2の領域から上記中性領域に延びる他の空乏領域と繋がることを阻止することを特徴とするイメージセンサ。

## 【請求項 2】

上記第2の横位置が上記画素アレイの中心と上記画素アレイの外側領域との間で変動することを特徴とする請求項1に記載のイメージセンサ。

**【請求項 3】**

上記第2の領域と上記他のフォトダイオードの第2の領域とが上記第1の領域よりも深い深度を有することを特徴とする請求項2に記載のイメージセンサ。

**【請求項 4】**

複数のフォトダイオードが配置されている画素アレイを含むイメージセンサを形成するための方法であって、

低濃度にドープされたp型基板を提供する工程と、

上記基板に中濃度にドープされたp型の第1の領域を形成する工程と、

上記基板に低濃度にドープされたn型の第2の領域を形成する工程と、

上記基板に中濃度にドープされたp型のバリア領域を形成する工程により上記フォトダイオードを形成し、10

上記第2の領域は、上記第1の領域に隣接し、上記第1の領域に対する第1の横位置に配置され、

上記バリア領域は、上記第2の領域と他のフォトダイオードの第2の領域との間で、上記第1の領域の下方に配置され、上記第1の領域に対する第2の横位置に配置され、

上記第1の横位置が、上記画素アレイの中心と上記画素アレイの外側領域との間で変動し、10

上記のバリア領域は、中性領域を有し、

上記中性領域は、上記第2の領域から上記中性領域に延びる空乏領域が、他のフォトダイオードの第2の領域から上記中性領域に延びる他の空乏領域と繋がることを阻止することを特徴とする方法。20

**【請求項 5】**

上記第2の横位置が上記画素アレイの中心と上記画素アレイの外側領域との間で変動することを特徴とする請求項4に記載の方法。

**【請求項 6】**

上記第2の領域と上記他のフォトダイオードの第2の領域が上記第1の領域よりも深い深度を有することを特徴とする請求項4に記載の方法。

**【発明の詳細な説明】****【発明の詳細な説明】****【0001】**30**[発明の背景]****[発明の分野]**

ここに開示する主題は、該して、半導体イメージセンサの分野に関するものである。

**【0002】****[背景情報]**

デジタルカメラおよびデジタルビデオカメラといった写真機材は、電子イメージセンサを含み、電子イメージセンサはそれぞれ、静止画像に処理するため、または、ビデオ画像に処理するための光を捕獲する。これらの電子イメージセンサは、典型的には、何百万もの光捕獲素子、例えばフォトダイオードを含む。フォトダイオードは、二次元の画素アレイに配置されている。40

**【0003】**

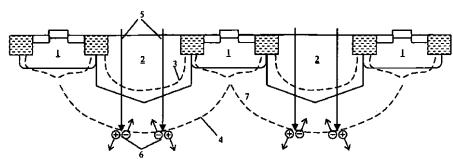

図1は、従来技術の画素アレイ内の画素を示す拡大した断面図である。前記画素は、第1の型の材料から構成される、典型的にはp型の第1の領域と、第2の型の材料から構成される、典型的にはn型の第2の領域とを含む。第1の領域1および第2の領域2は、フォトダイオードのpn接合を形成する。前記pn接合に逆バイアスを印加して、破線3と破線4との間に空乏領域を形成する。入射光線5の光子が吸収されて、電子正孔対6を生成する。電子が移動して電流を生成する。最終的にこの電流は感知されると共に処理されて、イメージセンサによって検出される画像を再生する。

**【0004】**

比較的長い波長の光が、フォトダイオードの中に深く浸透する。その結果、空乏領域の50

外縁に電子が形成される。空乏領域は広がって、領域 7 にほぼ繋がることが可能である。空乏領域同士が繋がると、隣接し合うフォトダイオードを電子的に容量結合させる。光を受けるフォトダイオードの電圧が変化すると、隣接する、光を受けないフォトダイオードの電圧は変動し得る。このため、前記の隣接するフォトダイオードにおいて、正確な光の感知は行われない。空乏領域の横方向の広がりが、隣接する空乏領域に影響を与えることを最小限に抑える画素構造を提供することが望まれている。

#### 【0005】

##### [発明の概要]

フォトダイオードアレイを有するイメージセンサであり、各フォトダイオードは、第 1 の型の材料から構成される第 1 の領域と、第 2 の型の材料から構成される第 2 の領域とを有する。第 1 の領域と第 2 の領域との間には、分離領域が位置している。第 2 の領域は、上記フォトダイオードアレイのコーナー領域において、分離領域からオフセットして配置されている。10

##### [図面の簡単な説明]

図 1 は、従来技術のイメージセンサを示す図である。

#### 【0006】

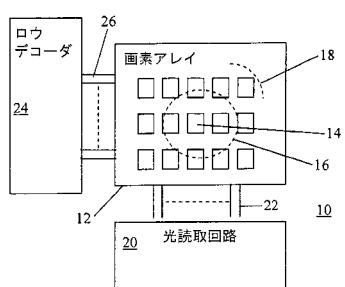

図 2 は、イメージセンサを概略的に示す図である。

#### 【0007】

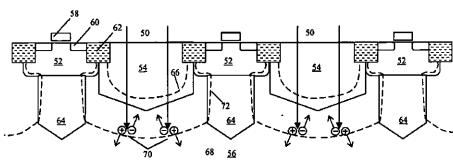

図 3 は、イメージセンサの複数のフォトダイオードを示す図である。

#### 【0008】

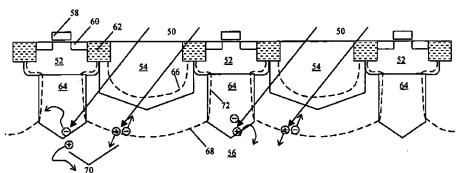

図 4 は、イメージセンサの画素アレイのコーナー領域におけるフォトダイオードを示す図である。20

#### 【0009】

図 5 は、オフセットして配置されたバリア領域を有する、コーナー領域におけるフォトダイオードを示す図である。

#### 【0010】

図 6 は、オフセットして配置された n 型領域を有する、コーナー領域におけるフォトダイオードを示す図である。

##### [詳細な説明]

#### 【0011】

複数のフォトダイオードを有するイメージセンサを開示する。各フォトダイオードは、第 1 の型の材料から構成される第 1 の領域と、第 2 の型の材料から構成される第 2 の領域とを有する。フォトダイオードはまた、第 1 の領域と第 2 の領域との間に分離領域を有する。フォトダイオードはアレイ状に配置されている。このアレイのコーナー領域において、第 2 の領域は、より多くの入射光線の光子を捕獲するために、分離領域に対してオフセットして配置されている。30

#### 【0012】

参照番号を用いて図面をより具体的に参照する。図 2 は、イメージセンサ 10 を示す図である。イメージセンサ 10 は、複数の個々のフォトダイオード 14 を含むフォトダイオードアレイ 12 を有する。フォトダイオード 14 は、典型的には、ロウおよびカラムから成る二次元のアレイに配置されている。フォトダイオードアレイ 12 は、中心領域 16 およびコーナー領域 18 を有する。40

#### 【0013】

フォトダイオードアレイ 12 は、典型的には、複数の導電トレース 22 によって光読取回路 20 に接続されている。フォトダイオードアレイ 12 は、導電トレース 26 によって、ロウデコーダ 24 に接続されている。ロウデコーダ 24 は、フォトダイオードアレイ 12 の個々のロウを選択することができる。その後、光読取回路 20 が、選択されたロウ内の特定の個別のカラムを読み取ることが可能である。ロウデコーダ 24 および光読取回路 20 を共に用いて、フォトダイオードアレイ 12 内の個々のフォトダイオード 14 の読み取りを行うことができる。フォトダイオード 14 から読み取られたデータは、ブ

50

ロセッサ(図示しない)等の他の回路によって処理されて、画像表示を生成する。

**【0014】**

Tayに付与された米国特許第6,795,117号に開示された対応するイメージセンサおよびイメージセンサシステムと同一に、または類似して、イメージセンサ10および他の回路を構成、構造化、および、動作させてもよい。米国特許第6,795,117号を本願に引用して援用する。

**【0015】**

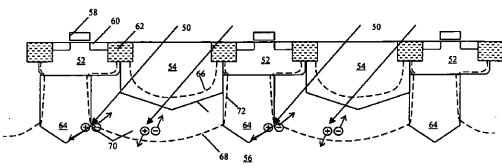

図3は、複数のフォトダイオード50を示す図である。各フォトダイオード50は、第1の型の材料から構成される第1の領域52と、第2の型の材料から構成される第2の領域54とを含む。一例として、第1の材料は中間ドープされたp型材料であってよく、第2の領域52は低濃度にドープされたn型材料であってよい。第1の領域50および第2の領域52は、基板56上に形成される。基板56は、低濃度にドープされたp型材料から構成されていてよい。

**【0016】**

各フォトダイオード50は、ゲート58と、第1の領域52に隣接して形成されたソースパッドまたはドレインパッド60とをさらに有していてよい。ゲート58は、高濃度にドープされたn型ポリシリコン材料から構成されていてよい。ソース/ドレインパッド60は、高濃度にドープされたn型材料から構成されていてよい。n型のソース/ドレインパッド60は、分離領域62によって、n型の第2の領域54から分離されていてよい。

**【0017】**

各第1の領域52には、バリア領域64が隣接している。バリア領域64は、中濃度にドープされたp型材料から構成されていてよい。フォトダイオード50に逆バイアスを印加して、一般的には線66および線68の内部に空乏領域を生成する。光の比較的長い波長における光の吸収および電子正孔対70の形成は、空乏領域の底部において生じる。一例として、650ナノメートルよりも長い波長の光は、空乏領域の底部において吸収され易い。

**【0018】**

バリア領域64は、空乏領域が破線72によって示される水平方向に横に広がることを妨げる。これによって、空乏領域同士が繋がることが阻止されると共に、隣接し合うフォトダイオードにおいて誤った電圧変動が生じることが阻止される。図3に示したように、バリア領域64は、第2の領域52と同じだけ深く広がっていてよい。一例として、前記バリア領域は、2~4μm間の深度を有していてよい。

**【0019】**

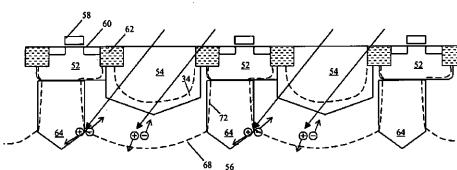

図4に示すように、画素アレイのコーナー領域18に位置する画素の場合、光線は斜めにフォトダイオードに浸透する。この角度は30度であってよい。入射光線は材料に吸収され、第2の領域の外部、かつ隣接するフォトダイオードに近接して電子正孔対70を形成することが可能である。自由電子が、隣接するフォトダイオードに移動して、結果として光検出は不正確になる。

**【0020】**

図5は、バリア領域64が第1の領域52に対してオフセットして配置された一実施形態を示す図である。オフセットして配置されたバリア領域64は、入射光線が材料に吸収された地点から隣接するフォトダイオードまでの長い経路を生成している。このオフセットは、光が垂直方向にフォトダイオードに浸透する画素アレイの中心から、光が大きな角度をなして浸透する画素アレイの外側の画素まで変動し得る。このオフセットは、画素アレイの中心から画素アレイの外側領域まで徐々に拡大し得る。オフセットによって、空乏領域が入射光線の方向に横に広がることが可能である。一例として、バリア領域は、最外部の画素において最大0.5μmだけオフセットされていてよい。

**【0021】**

図6は、バリア領域64および第2の領域54の両方が分離領域62に対してオフセットして配置された一実施形態を示す図である。オフセットして配置された第2の領域54

10

20

30

40

50

は、入射光線の方向に整列しており、より多くの光子を捕獲する。第2の領域のオフセットは、光が垂直方向にフォトダイオードに浸透する画素アレイの中心から、光が大きな角度をなして浸透する画素アレイの外側の画素まで変動し得る。このオフセットは、画素アレイの中心から画素アレイの外側領域まで徐々に拡大し得る。一例として、バリア領域64および第2の領域54は、最外部の画素において最大0.5 μmだけオフセットされていてよい。

#### 【0022】

上記フォトダイオードは、公知のCMOS製造技術を用いて構成することが可能である。バリア領域64を基板56の上に形成してよい。第1の領域52をバリア領域64の上に形成し、ゲート58およびパッド60を領域52の上に形成してもよい。第2の領域54を基板56上に形成してもよい。形成の順番は、イメージセンサを作成するために用いられるプロセスに応じて変化し得る。10

#### 【0023】

特定の典型的な実施形態について記載すると共に、添付の図面に図示してきたが、当業者は様々な他の変形を行うことが可能であるため、このような実施形態は、単に説明のためにあって本発明の範囲を制限するものでないこと、および、本発明は、図示すると共に説明した特定の構造および構成に制限されるものでないことは明らかであろう。

#### 【図面の簡単な説明】

#### 【0024】

【図1】図1は、従来技術のイメージセンサを示す図である。20

【図2】図2は、イメージセンサを概略的に示す図である。

【図3】図3は、イメージセンサの複数のフォトダイオードを示す図である。

【図4】図4は、イメージセンサの画素アレイのコーナー領域におけるフォトダイオードを示す図である。

【図5】図5は、オフセットして配置されたバリア領域を有する、コーナー領域におけるフォトダイオードを示す図である。

【図6】図6は、オフセットして配置されたn型領域を有する、コーナー領域におけるフォトダイオードを示す図である。

【図1】

FIG. 1 Prior Art

【図2】

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

---

フロントページの続き

(56)参考文献 特開平11-284168(JP,A)

特開平11-274456(JP,A)

特開平11-233747(JP,A)

特開2006-024907(JP,A)

特開2004-134790(JP,A)

特表2003-507902(JP,A)

特開2006-279048(JP,A)

特開2006-216577(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/339、27/14、

27/144-27/148、29/762

H04N 5/335-5/378