(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5491077号

(P5491077)

(45) 発行日 平成26年5月14日 (2014.5.14)

(24) 登録日 平成26年3月7日 (2014.3.7)

(51) Int.Cl.

F 1

H01L 27/146 (2006.01)

H01L 27/14

A

H01L 21/768 (2006.01)

H01L 21/90

N

H01L 23/532 (2006.01)

請求項の数 6 (全 18 頁)

(21) 出願番号

特願2009-137721 (P2009-137721)

(22) 出願日

平成21年6月8日 (2009.6.8)

(65) 公開番号

特開2010-283307 (P2010-283307A)

(43) 公開日

平成22年12月16日 (2010.12.16)

審査請求日

平成24年6月7日 (2012.6.7)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】半導体装置、及び半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部を含む半導体基板と、

前記半導体基板の上に配された多層配線構造と、

を備え、

前記多層配線構造は、

複数の第1の導電ラインと、

前記複数の第1の導電ラインを覆う絶縁膜と、

前記複数の第1の導電ラインと交差するように前記絶縁膜の上に配された第2の導電ラインと、

を含み、

前記絶縁膜は、前記複数の第1の導電ラインと前記第2の導電ラインとが交差する複数の領域における少なくとも一部の領域にギャップを有し、前記光電変換部の上にギャップを有さず、

前記第2の導電ラインに沿った方向における前記ギャップの幅は、前記第1の導電ラインの幅以下である

ことを特徴とする半導体装置。

## 【請求項 2】

前記第1の導電ラインに沿った方向における前記ギャップの幅は、前記第2の導電ラインの幅以下である

10

20

ことを特徴とする請求項 1 に記載の半導体装置。

【請求項 3】

半導体基板を有する半導体装置の製造方法であって、

前記半導体基板の上方に複数の第 1 の導電ラインを形成する第 1 の工程と、

前記複数の第 1 の導電ラインを覆うように絶縁膜を形成する第 2 の工程と、

前記絶縁膜に前記複数の第 1 の導電ラインの上面の一部を露出する複数の溝をそれぞれ

前記第 1 の導電ラインの幅以下の幅で形成する第 3 の工程と、

前記複数の溝のそれぞれに第 1 の絶縁体を埋め込む第 4 の工程と、

前記絶縁膜及び前記第 1 の絶縁体の上に、前記複数の第 1 の導電ラインと交差するよう

に第 2 の導電ラインを形成する第 5 の工程と、

前記第 5 の工程の後に、前記第 1 の絶縁体を前記複数の溝のそれから除去する第 6

の工程と、

前記第 6 の工程の後に、前記複数の溝内の前記第 1 の導電ラインと前記第 2 の導電ライ

ンとが交差する複数の領域における少なくとも一部の領域をギャップとして残すように、

前記複数の溝のそれぞれにおける前記半導体基板の表面に垂直な方向から見た場合に前記

第 2 の導電ラインが重ならない部分に第 2 の絶縁体を埋め込む第 7 の工程と、

を含み、

前記第 2 の導電ラインに沿った方向における前記ギャップの幅は、前記第 1 の導電ライ

ンの幅以下である

ことを特徴とする半導体装置の製造方法。

【請求項 4】

前記第 6 の工程では、前記第 1 の絶縁体の上面のうち前記半導体基板の表面に垂直な方

向から見た場合に前記第 2 の導電ラインが重ならない部分が露出した状態で、前記第 1 の

絶縁体の前記絶縁膜及び前記第 2 の導電ラインに対するエッチング選択比が高くなる条件

で等方性エッチングを行うことにより、前記第 1 の絶縁体を前記複数の溝のそれから

除去する

ことを特徴とする請求項 3 に記載の半導体装置の製造方法。

【請求項 5】

前記第 5 の工程は、

前記絶縁膜及び前記第 1 の絶縁体の上に第 2 の絶縁膜を形成する工程と、

前記第 2 の絶縁膜に、前記複数の第 1 の導電ラインと交差するよう第 2 の溝を形成す

る工程と、

前記第 2 の溝に導電体を埋め込むことにより、前記第 2 の溝に対応した前記第 2 の導電

ラインを形成する工程と、

を含み、

前記第 6 の工程は、

前記第 1 の絶縁体の上面のうち前記半導体基板の表面に垂直な方向から見た場合に前記

第 2 の導電ラインが重ならない部分を露出するように複数の穴を前記第 2 の絶縁膜に形成

する工程と、

前記絶縁膜及び前記第 2 の導電ラインに対する前記第 1 の絶縁体のエッチング選択比が

高くなる条件で前記複数の穴を介して等方性エッチングを行うことにより、前記第 1 の絶

縁体を前記複数の溝のそれから除去する工程と、

を含み、

前記第 7 の工程では、

前記複数の穴を介して前記複数の溝のそれぞれに前記第 2 の絶縁体を埋め込む

ことを特徴とする請求項 3 に記載の半導体装置の製造方法。

【請求項 6】

前記半導体装置は、光電変換装置を含み、

前記半導体基板は、光電変換部を含む

ことを特徴とする請求項 3 から 5 のいずれか 1 項に記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体装置、及び半導体装置の製造方法に関する。

**【背景技術】****【0002】**

半導体装置における微細化の進展は著しい。微細化に伴い、配線層の多層化も進展している。多層配線構造では、層間絶縁膜を介した上下のライン間に寄生する静電容量（以下、ライン間容量とよぶ）が問題となっている。また、撮像センサ、とくにCMOS型撮像センサでは、画素ピッチが縮小された際に光学的な特性を劣化させないために、各画素における光電変換素子の受光面から光電変換素子の上方におけるマイクロレンズまでの距離を縮小する必要がある。これに伴い、光電変換素子とマイクロレンズとの間に配される層間絶縁膜も薄膜化するので、ライン間容量が増加する。

10

**【0003】**

それに対して、特許文献1には、第1層配線4の周囲に空間6を形成することが記載されている（特許文献1の図1参照）。具体的には、第1層配線4を形成した後、第1層配線4を覆うようにSiN膜1を形成し、さらにSiN膜1を覆うようにSiO<sub>2</sub>膜2を形成する。そして、SiO<sub>2</sub>膜2における第1層配線4の上方の部分に小孔7を形成した後、小孔7を通してCF<sub>4</sub>/O<sub>2</sub>混合ガスを用いたドライエッ칭により第1層配線4の周囲に空間6を形成する。そして、SiO<sub>2</sub>膜2を覆うようにスピノングラス膜9を塗布し焼結する。このとき、スピノングラス膜3は、表面張力が高いため、小孔7から空間6中へ浸入しない。これにより、第1層配線4の周囲に空間6を保持した状態で小孔7を塞ぐことが可能になる。特許文献1によれば、このように第1層配線4の周囲に空間6を形成することにより、配線間容量の大幅な低減化を実現できるとされている。

20

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開平5-36841号公報****【発明の概要】****【発明が解決しようとする課題】**

30

**【0005】**

特許文献1の図1には、第1層配線3と第1層配線8とを接続する第2層配線5の周囲にも空間6を形成することが示されている。ここで、第2層配線5の長さが長くなると、空間6の長さも長くなるので、特許文献1の図1に示された配線構造の機械的強度が低下する。これにより、以降の工程でCMP（Chemical Mechanical Polishing：化学的機械的研磨法）を施すと配線構造が変形もしくは破断する可能性がある。

**【0006】**

本発明の目的は、半導体装置において、多層配線構造におけるライン間容量を低減しながら、多層配線構造の機械的強度の低下を抑制することにある。

40

**【課題を解決するための手段】****【0007】**

本発明の1つの側面に係る半導体装置は、光電変換部を含む半導体基板と、前記半導体基板の上に配された多層配線構造とを備え、前記多層配線構造は、複数の第1の導電ラインと、前記複数の第1の導電ラインを覆う絶縁膜と、前記複数の第1の導電ラインと交差するように前記絶縁膜の上に配された第2の導電ラインと、を含み、前記絶縁膜は、前記複数の第1の導電ラインと前記第2の導電ラインとが交差する複数の領域における少なくとも一部の領域にギャップを有し、前記光電変換部の上にギャップを有さず、前記第2の導電ラインに沿った方向における前記ギャップの幅は、前記第1の導電ラインの幅以下であることを特徴とする。

50

## 【発明の効果】

## 【0008】

本発明によれば、半導体装置において、多層配線構造におけるライン間容量を低減しながら、多層配線構造の機械的強度の低下を抑制することができる。

## 【図面の簡単な説明】

## 【0009】

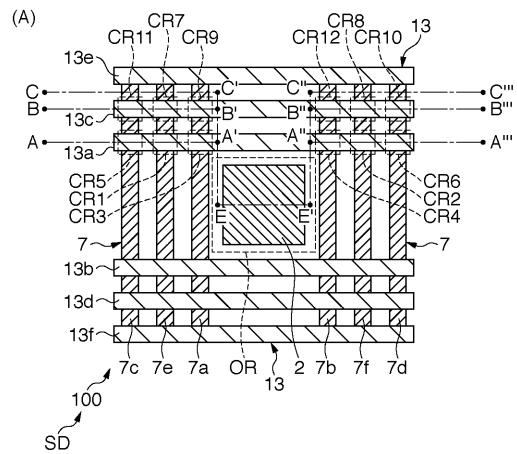

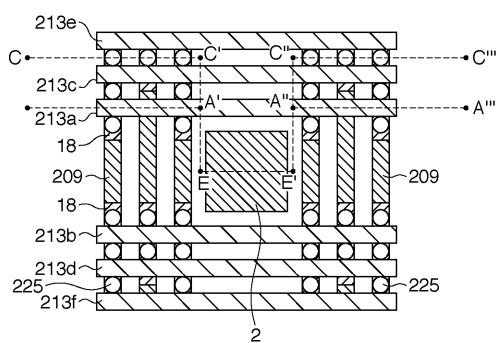

【図1】第1実施形態に係る半導体装置SDの構成を示す図。

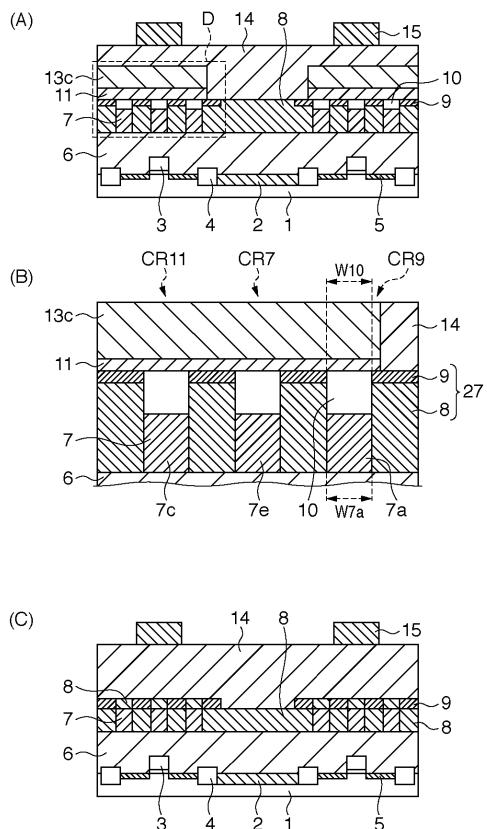

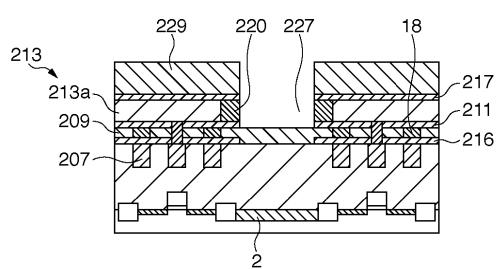

【図2】第1実施形態に係る半導体装置SDの構成を示す図。

【図3】第1実施形態に係る半導体装置SDの製造方法を示す図。

【図4】第1実施形態に係る半導体装置SDの製造方法を示す図。

10

【図5】第1実施形態に係る半導体装置SDの製造方法を示す図。

【図6】第1実施形態に係る半導体装置SDの製造方法を示す図。

【図7】第1実施形態に係る半導体装置SDの製造方法を示す図。

【図8】第1実施形態に係る半導体装置SDの製造方法を示す図。

【図9】第1実施形態に係る半導体装置SDの製造方法を示す図。

【図10】第1実施形態に係る半導体装置SDの製造方法を示す図。

【図11】第1実施形態に係る半導体装置SDの製造方法を示す図。

【図12】第1実施形態における光電変換装置を適用した撮像システムの構成図。

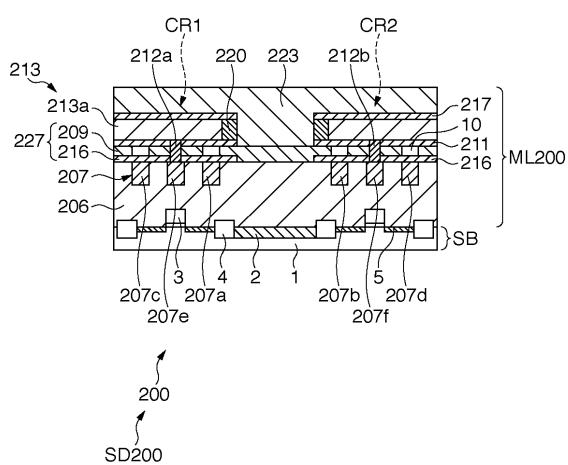

【図13】第2実施形態に係る半導体装置SD200の構成を示す図。

20

【図14】第2実施形態に係る半導体装置SD200の製造方法を示す図。

【図15】第2実施形態に係る半導体装置SD200の製造方法を示す図。

【図16】第2実施形態に係る半導体装置SD200の製造方法を示す図。

【図17】第2実施形態に係る半導体装置SD200の製造方法を示す図。

【図18】第2実施形態に係る半導体装置SD200の製造方法を示す図。

【図19】第2実施形態に係る半導体装置SD200の製造方法を示す図。

【図20】第2実施形態に係る半導体装置SD200の製造方法を示す図。

【図21】第2実施形態に係る半導体装置SD200の製造方法を示す図。

## 【発明を実施するための形態】

## 【0010】

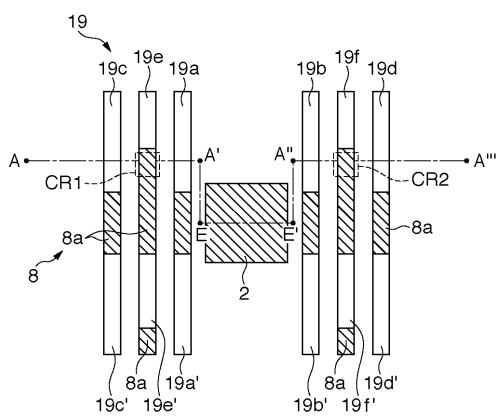

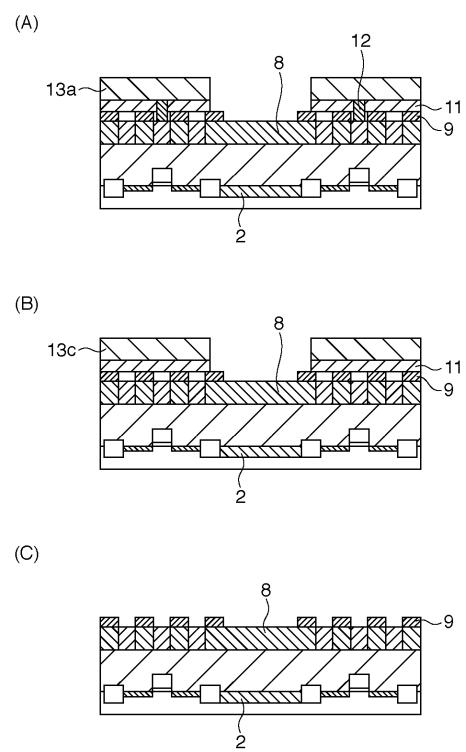

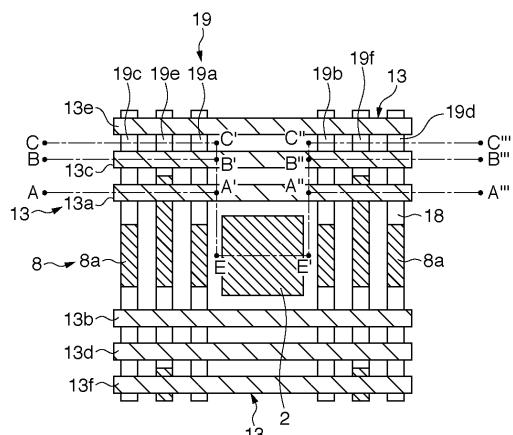

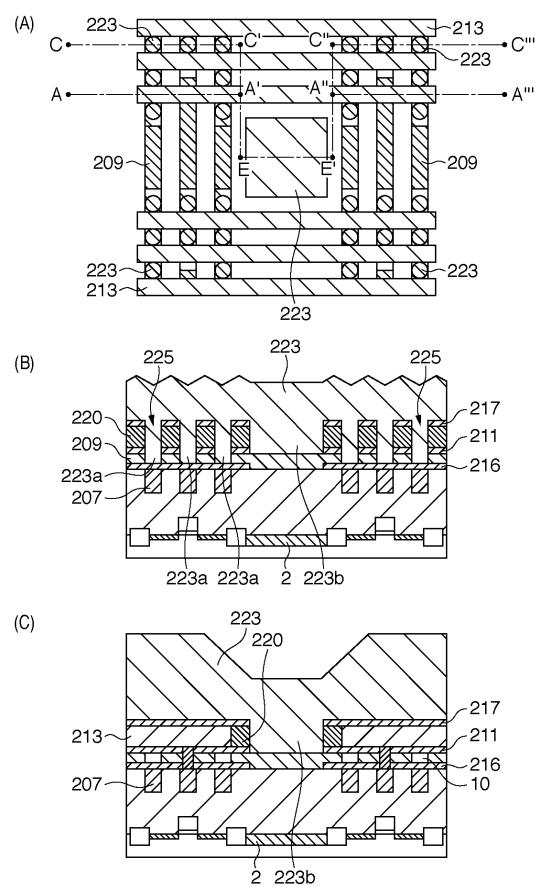

以下、本発明の第1実施形態に係る半導体装置SDの構成について、図1及び図2を用いて説明する。半導体装置SDは、光電変換装置100を含む。半導体装置SDの光電変換装置100における配線構造を上面から見た模式図を図1(A)に示す。図1(B)は、図1(A)の(A-A', E-E', A''-A''')断面を示す図である。図1(B)では、便宜的に、A-A'断面とE-E'断面とA''-A'''断面とを繋げて示している。図2(A)は、図1(A)の(B-B', E-E', B''-B''')断面を示す図である。図2(A)では、便宜的に、B-B'断面とE-E'断面とB''-B'''断面とを繋げて示している。図2(C)は、図1(A)の(C-C', E-E', C''-C''')断面を示す図である。図2(C)では、便宜的に、C-C'断面とE-E'断面とC''-C'''断面とを繋げて示している。

30

## 【0011】

半導体装置SDの光電変換装置100は、半導体基板SB及び多層配線構造MLを備える。半導体基板SBのウエル領域1には、複数の光電変換部2が2次元状に配されている。各光電変換部2は、光に応じた電荷を発生させる。光電変換部2は、例えば、フォトダイオードである。半導体基板SBのウエル領域1には、MOSトランジスタにおけるソース電極又はドレイン電極となる拡散層5が配されている。また、半導体基板SBには、素子分離部4が配されている。素子分離部4は、半導体基板SBにおけるアクティブ領域を規定するとともに、複数の光電変換部2を電気的に分離したり、複数のMOSトランジスタを電気的に分離したりする。

40

## 【0012】

多層配線構造MLは、半導体基板SBの上に配されており、次の構成要素を含む。MO

50

Sトランジスタにおけるゲート電極3は、半導体基板SBの表面における2つの拡散層（ソース電極及びドレイン電極）5の上に配されている。ゲート電極3は、例えば、ポリシリコンで形成されており、ライン（ポリシリコンライン）とすることもできる。絶縁膜6は、半導体基板SB及びゲート電極3を覆っており、その上面が平坦化されている。第1の配線層7は、絶縁膜6の上に配されている。第1の配線層7は、例えば、アルミニウムを主成分とする金属又は金属間化合物で形成されている。第1の配線層7は、複数の第1の導電ライン7a～7fを含む。複数の第1の導電ライン7a～7fのうち第1の導電ライン7aと第1の導電ライン7bとは、それぞれ、光電変換部2の上方における開口領域ORを規定する。絶縁膜8は、第1の配線層7における複数の第1の導電ライン7a～7fを覆っている。絶縁膜9は、絶縁膜8を覆っている。絶縁膜9は、絶縁膜8の研磨に対して耐性を有しており、第1の導電ライン上の層間絶縁膜を研磨・平坦化する際に研磨停止層としての役割を果たす。絶縁膜9は、複数の第1の導電ライン7a～7fのそれぞれの上方に位置する開口と光電変換部2の上方に位置する開口とを有する。絶縁膜9は、絶縁膜8、絶縁膜11と比較して屈折率が高く、それらとの界面における光の反射を低減する役目を果たす。絶縁膜11は、絶縁膜9を覆っている。第2の配線層13は、絶縁膜8、絶縁膜9、及び絶縁膜11の上に配されている。第2の配線層13は、例えば、アルミニウムを主成分とする金属又は金属間化合物で形成されている。第2の配線層13は、複数の第2の導電ライン13a～13fを含む。複数の第2の導電ライン13a～13fのうち第2の導電ライン13aと第2の導電ライン13bとは、それぞれ、光電変換部2の上方における開口領域ORを規定する。複数の第2の導電ライン13a～13fのそれぞれは、半導体基板SBの表面SBaに垂直な方向から透視した場合に複数の第1の導電ライン7a～7fのそれぞれと交差するように伸びている。絶縁膜14は、絶縁膜8、絶縁膜9、絶縁膜11、及び第2の配線層13を覆っており、その上面が平坦化されている。第3の配線層15は、絶縁膜14の上に配されている。

#### 【0013】

ここで、図1(A)、(B)及び図2(A)に示すように、複数の交差する領域CR1～CR12のうち交差する領域CR1、CR2には、プラグ12a及び12bが配されている。プラグ12aは、第1の導電ライン7eと第2の導電ライン13aとを電気的に接続する役割を果たす。プラグ12bは、第1の導電ライン7fと第2の導電ライン13aとを電気的に接続する役割を果たす。プラグ12a、12bは、例えば、タングステンを主成分とする金属又は金属間化合物で形成されている。複数の交差する領域CR1～CR12のうち残りの交差する領域CR3～CR12には、エアギャップ10が設けられている。すなわち、絶縁膜8及び絶縁膜9は、複数の交差する領域CR3～CR12のそれにエアギャップ10を有する。エアギャップ10は、第1の導電ラインと第2の導電ラインとが交差していない領域に設けられていない。エアギャップ10は、真空空間をなしで、あるいは、空気が満たされている。これにより、エアギャップ10の誘電率は、約1であり、絶縁膜（例えば、SiO<sub>2</sub>）又はSiNの誘電率より大幅に低減されている。すなわち、第1の導電ラインと第2の導電ラインとの間ににおける寄生容量であるライン間容量が大きな箇所にエアギャップ10を設け、ライン間容量が小さな箇所にエアギャップ10を設けないようにするので、ライン間容量を効果的にかつ効率的に低減することができる。ここで、エアギャップ10に関する構成を、図2(B)を用いて詳細に説明する。図2(B)は、図2(A)の断面における領域Dを拡大した図である。第1の導電ライン7aと第2の導電ライン13cとの交差する領域CR9に設けられたエアギャップ10における第2の導電ライン13cに沿った方向の幅W10は、第1の導電ライン7aの幅W7a以下である。また、図示しないが、エアギャップ10における第1の導電ライン7aに沿った方向の幅は、第2の導電ライン13cの幅以下である。これに応じて、エアギャップ10の4つの側方では、支柱27が絶縁膜6と絶縁膜11との間を支えている。支柱27には、絶縁膜8及び絶縁膜9が含まれている。これにより、エアギャップ10の周囲における機械的強度、すなわち、多層配線構造MLの機械的強度の低下が抑制されている。このように、本実施形態では、半導体装置SDにおいて、多層配線構造MLにおける

10

20

30

40

50

るライン間容量を低減しながら、多層配線構造M Lの機械的強度の低下を抑制することができる。なお、上記では、光電変換装置1 0 0を中心説明しているため、絶縁膜9が光電変換部2の上方に開口を有するものとしているが、光電変換装置以外の半導体装置の場合にはこの構成は不要である。

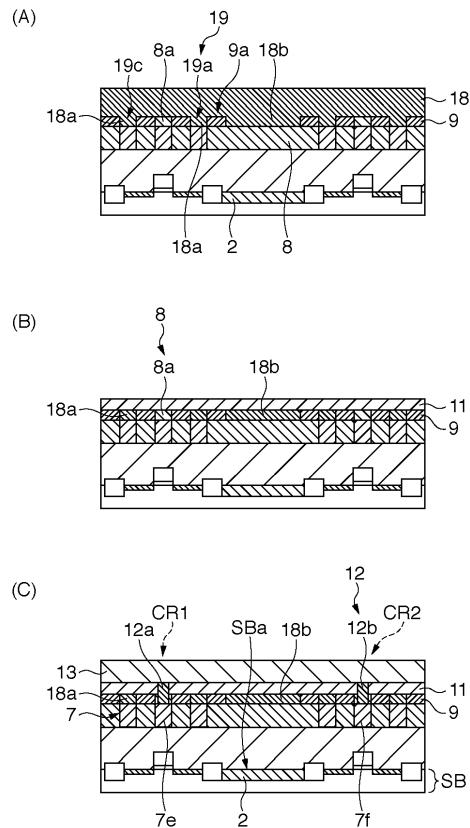

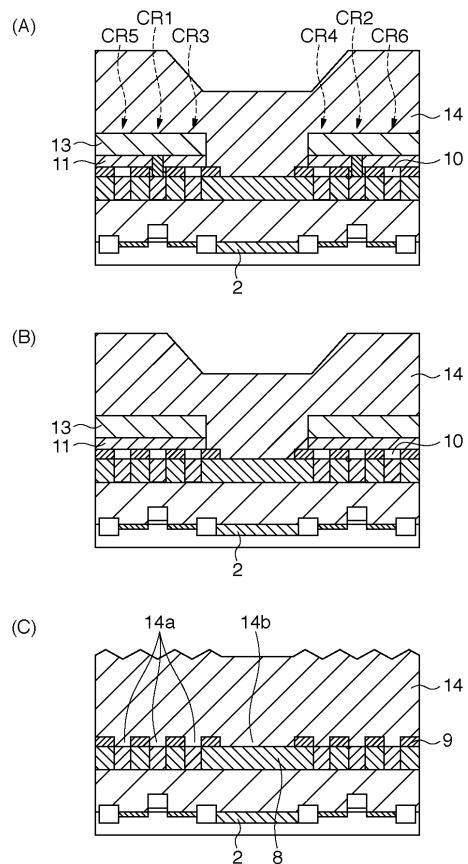

【0014】

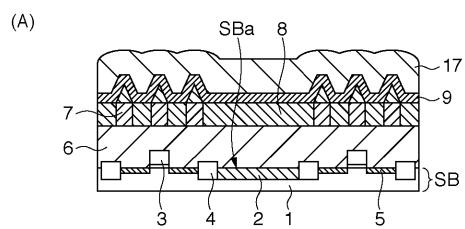

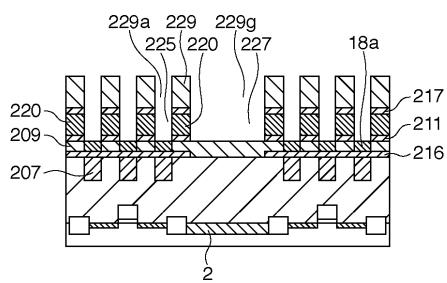

次に、本発明の第1実施形態に係る半導体装置S Dの製造方法について、図3～図11を用いて説明する。図3、4、6に示す断面は、図1(B)の断面に対応した断面である。図5は、図4の工程における平面図である。図7(A)～(C)に示す断面は、それぞれ、図1(B)、図2(A)、(C)の断面に対応した断面である。図8は、図7の工程における平面図である。図9(A)～(C)に示す断面は、それぞれ、図1(B)、図2(A)、(C)の断面に対応した断面である。図10は、図9の工程における平面図である。図11(A)～(C)に示す断面は、それぞれ、図1(B)、図2(A)、(C)の断面に対応した断面である。

【0015】

図3(A)の工程では、半導体基板S Bに素子分離部4を形成した後に、半導体基板S Bの表面S B aにおける素子分離部4により規定されたアクティブ領域の上に、ゲート電極3を形成する。そして、ゲート電極3をマスクとして半導体基板S Bにイオン注入を行うことにより、半導体基板S Bのウエル領域1(アクティブ領域)に光電変換部2及び拡散層5を形成する。ゲート電極3と拡散層5とはM O Sトランジスタを構成する。その後、半導体基板S B及びゲート電極3を覆うように絶縁膜6を形成する。C M P法を用いて絶縁膜6を研磨することにより、絶縁膜6の上面を平坦化する。次いで、例えば拡散層5の表面を露出するように、絶縁膜6にスルーホール(図示せず)を形成し、そのスルーホールに金属(例えばタンゲステン)を埋め込むことにより、プラグ(図示せず)を形成する。そして、絶縁膜6の上に金属積層膜(例えば、T i N膜/A 1 C u合金膜/T i N膜の積層膜)における各膜をスパッタリング法により順次成膜した後、フォトリソグラフィー工程とドライエッティング工程とを経て第1の配線層7のパターンを形成する。すなわち、半導体基板S Bの上方に複数の第1の導電ライン7 a～7 fを形成する(第1の工程)。次に、高密度プラズマC V D法を用いて第1の配線層7(複数の第1の導電ライン7 a～7 f)を覆うように絶縁膜8を形成する(第2の工程)。絶縁膜8は、例えばS i O<sub>2</sub>で形成する。その後、プラズマC V D法を用いて、絶縁膜8を覆うように絶縁膜9を形成する。絶縁膜9は、例えばS i Nで形成する。続いて、プラズマC V D法を用いて、絶縁膜9を覆うように絶縁膜17を形成する。絶縁膜17は、研磨の犠牲膜となるべき膜である。絶縁膜17は、例えばS i O<sub>2</sub>で形成する。

【0016】

図3(B)の工程では、C M P法を用いて、絶縁膜9の上面9 aが露出するまで、絶縁膜17、絶縁膜9、及び絶縁膜8を研磨する。これにより、絶縁膜8における第1の導電ラインの上に位置する部分8 aを第1の導電ラインの幅以下の幅で露出させる。言い換えると、絶縁膜9における第1の導電ラインの上に位置する(スリット状の)開口9 bを第1の導電ラインの幅以下の幅で形成する。それとともに、絶縁膜8における部分8 aの表面8 a 1と絶縁膜9の上面9 aとを含む平坦な上面を得る。絶縁膜9(例えばS i N膜)の研磨速度は、絶縁膜17(例えばS i O<sub>2</sub>膜)の研磨速度の1/3以下である。すなわち、絶縁膜9は、絶縁膜17の研磨に対して耐性を有する。このため、絶縁膜9は研磨停止層として機能するので、絶縁膜8を過度に研磨することなくかつ第1の導電ラインを研磨することなく絶縁膜17を選択的に研磨して平坦化処理を終了することができる。絶縁膜9の膜厚は、研磨停止層として機能するのに十分な膜厚の下限値以上でありかつその上面9 aと同じ高さに上記の部分8 aが位置するような膜厚の上限値以下である。なお、図3(A)に示すように研磨前は第1の導電ラインの上部に絶縁膜8及び絶縁膜9が凸形状に形成されているが、その凸形状の部分は研磨の過程で除去され平坦化後に残らない。

【0017】

図3(C)の工程では、フォトリソグラフィー工程を経て、絶縁膜9の上にエッティング

10

20

30

40

50

マスク 2 8 を形成する。エッティングマスク 2 8 は、光電変換部 2 の上方の領域に開口 2 8 g を有し、溝 1 9 ( 図 5 参照 ) を形成すべき領域に開口 2 8 a ~ 2 8 d を有する。一方、エッティングマスク 2 8 は、溝 1 9 を形成すべきでない領域 ( 図 5 における部分 8 a 参照 ) を覆っている。エッティングマスク 2 8 は、例えば、フォトレジスト樹脂で形成する。

【 0 0 1 8 】

図 4 の工程では、エッティングマスク 2 8 と上記の研磨された絶縁膜 9 とをマスクとして絶縁膜 8 における第 1 の配線の上の部分 8 a をエッティングする。各溝の幅が各第 1 の配線の幅以下になるように、絶縁膜 8 に複数の第 1 の配線 7 a ~ 7 f を露出する複数の溝 1 9 a ~ 1 9 f ' ( 図 5 参照 ) を形成する ( 第 3 の工程 )。各溝 1 9 a ~ 1 9 f ' は、その一部分がエアギャップ 1 0 になるべき溝である。図 4 及び図 5 に示されるように、複数の溝 1 9 a ~ 1 9 f ' は、複数の第 1 の配線 7 a ~ 7 f のうち後述のプラグ 1 2 a , 1 2 b ( 図 6 ( C ) 参照 ) が配されるべき領域 C R 1 , C R 2 を除いた領域における複数の第 1 の配線 7 a ~ 7 f の上に形成される。上記のように、各溝 1 9 a ~ 1 9 f ' の幅は各第 1 の配線 7 a ~ 7 f の幅以下である。ここで、例えば、絶縁膜 8 が S i O <sub>2</sub> で形成されている場合、S i O <sub>2</sub> が選択的にエッティングされるエッティングガス ( 例えば、C <sub>4</sub> F <sub>8</sub> + C O + A r + O <sub>2</sub> ) を用いてドライエッティングを実施する。この場合、絶縁膜 9 に対する絶縁膜 8 のエッティング選択比 ( エッティング速度比 ) が大きくなる。すなわち、絶縁膜 9 は、絶縁膜 8 のエッティングに対して耐性を有する。これにより、絶縁膜 8 における第 1 の配線の上に位置する部分 8 a の膜厚が絶縁膜 9 の膜厚に比べて厚くても、絶縁膜 8 を選択的にエッティングすることができる。その後、エッティングマスク 2 8 を介して絶縁膜 9 が選択的にエッティングされる条件でドライエッティングを実施する。例えば、絶縁膜 9 が S i N で形成されている場合、S i N が選択的にエッティングされるエッティングガス ( 例えば、C H <sub>2</sub> F <sub>2</sub> + C O + O <sub>2</sub> ) を用いてドライエッティングを実施する。これにより、絶縁膜 9 における光電変換部 2 の上方に位置した部分 9 g ( 図 3 ( C ) 参照 ) を除去する。

【 0 0 1 9 】

なお、図 4 の工程では、エッティングマスク 2 8 ( 図 3 ( C ) 参照 ) を介してドライエッティングを実施することにより、絶縁膜 9 における部分 9 g と絶縁膜 8 における部分 8 a を同時に除去しても良い。例えば、S i O <sub>2</sub> が選択的にエッティングされるエッティングガス ( 例えば、C <sub>4</sub> F <sub>8</sub> + C O + A r + O <sub>2</sub> ) と S i N が選択的にエッティングされるエッティングガス ( 例えば、C H <sub>2</sub> F <sub>2</sub> + C O + O <sub>2</sub> ) との混合ガスを用いてドライエッティングを実施する。これにより、絶縁膜 8 が S i O <sub>2</sub> で形成され、絶縁膜 9 が S i N で形成されている場合、絶縁膜 9 に対する絶縁膜 8 のエッティング選択比 ( エッティング速度比 ) が 1 に近くなる。この場合でも、エッティングの異方性が高ければ、絶縁膜 8 における部分 8 a の除去とエアギャップ 1 0 になるべき溝 1 9 の形成とを同時に達成することができる。これにより、光電変換部 2 上に残存する研磨停止層 ( 絶縁膜 9 ) を除去する工程と溝 1 9 を形成する工程とを共通化できる。

【 0 0 2 0 】

図 6 ( A ) の工程では、プラズマ C V D 法を用いて、複数の溝 1 9 a ~ 1 9 f ' のそれぞれに有機系絶縁体 ( 第 1 の絶縁体 ) 1 8 a を埋め込むとともに絶縁膜 9 の開口 9 c に有機系絶縁体 1 8 b を埋め込む。また、絶縁膜 9 を覆うように、有機系絶縁膜 1 8 を形成する ( 第 4 の工程 )。有機系絶縁体 1 8 a 及び有機系絶縁体 1 8 b と有機系絶縁膜 1 8 とは、連続的に形成される。有機系絶縁体 1 8 a 及び有機系絶縁体 1 8 b と有機系絶縁膜 1 8 とは、例えば、S i O C で形成される。

【 0 0 2 1 】

図 6 ( B ) の工程では、C M P 法を用いて、絶縁膜 9 の上面 9 a が露出するまで、有機系絶縁膜 1 8 、絶縁膜 9 、及び絶縁膜 8 を研磨する。これにより、有機系絶縁膜 1 8 が除去され、有機系絶縁体 1 8 a が複数の溝 1 9 a ~ 1 9 f ' の中に残り、有機系絶縁体 1 8 b が開口 9 c の中に残った状態になる。このとき、絶縁膜 8 の研磨速度と絶縁膜 9 の研磨速度とが、それぞれ、有機系絶縁膜 1 8 の研磨速度の 1 / 5 以下である。すなわち、絶縁膜 9 は、有機系絶縁膜 1 8 の研磨に対して耐性を有する。このため、絶縁膜 9 は研磨停

止層として機能するので、有機系絶縁体 18 a 及び有機系絶縁体 18 b を残しながら有機系絶縁膜 18 を選択的に研磨して平坦化処理を終了することができる。続いて、プラズマ CVD 法を用いて、絶縁膜 8 、絶縁膜 9 、及び有機系絶縁体 18 a を覆うように、絶縁膜 11 を形成する。絶縁膜 11 は、例えば、 $\text{SiO}_2$  で形成する。

【 0022 】

図 6 ( C ) の工程では、例えば領域 C R 1 , C R 2 における第 1 の導電ライン 7 e , 7 f の表面を露出するように、絶縁膜 8 及び絶縁膜 11 にスルーホール ( 図示せず ) を形成する。そのスルーホールに埋め込まれるとともに絶縁膜 11 を覆うように金属層を形成する。金属層は、例えばタンゲステンで形成する。そして、絶縁膜 11 の表面が露出されるまで金属層を研磨することにより、プラグ 12 a , 12 b を形成する。このとき、絶縁膜 11 における表面近傍の部分も研磨される。その後、絶縁膜 11 の上に金属積層膜 ( 例えば、 $\text{TiN}$  膜 /  $\text{AlCu}$  合金膜 /  $\text{TiN}$  膜の積層膜 ) における各膜をスパッタリング法により順次成膜する。

【 0023 】

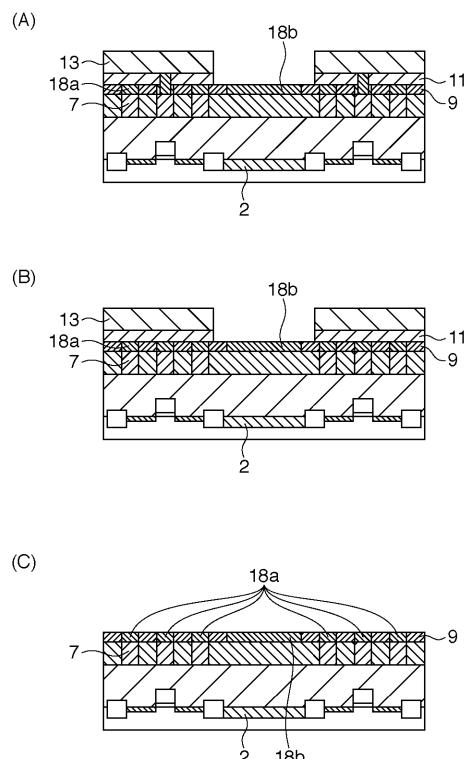

図 7 ( A ) ~ ( C ) は、同じ工程における断面を示す。図 7 の工程では、フォトリソグラフィー工程とドライエッチング工程とを経て絶縁膜 11 と金属積層膜とをパターニングすることにより、第 2 の配線層 13 のパターンを形成する。すなわち、絶縁膜 8 、有機系絶縁体 18 a 、及び絶縁膜 11 の上に、複数の第 1 の導電ライン 7 a ~ 7 f と交差するように複数の第 2 の導電ライン 13 a ~ 13 f を形成する ( 第 5 の工程 ) 。有機系絶縁体 18 a の上面の一部を覆うように複数の第 2 の導電ライン 13 a ~ 13 f を形成する。このとき、図 7 ( C ) 及び図 8 に示すように、ドライエッチング工程におけるオーバーエッチング処理にて、第 2 の導電ラインを配しない領域の絶縁膜 11 も除去し、有機系絶縁体 18 a を露出させる。第 2 の導電ラインを配しない領域は、図 1 に示す開口領域 OR を含む。一方、図 7 ( A ) 、 ( B ) 及び図 8 に示すように、ドライエッチング工程において第 2 の導電ラインがマスクとして機能するため、第 2 の導電ラインを配する領域の絶縁膜 11 は除去されずに残っており有機系絶縁体 18 a を覆っている。

【 0024 】

図 9 ( A ) ~ ( C ) は、同じ工程における断面を示す。図 9 の工程では、有機系絶縁体 18 a の絶縁膜 8 、絶縁膜 9 、及び第 2 の導電ラインのそれぞれに対するエッチング選択比が高くなる条件で等方性エッチングを行うことにより、有機系絶縁体 18 a を複数の溝 19 a ~ 19 f ' から除去する ( 第 6 の工程 ) 。有機系絶縁体 18 a の上面のうち半導体基板 SB の表面 SB a に垂直な方向から見た場合に第 2 の導電ラインが重ならない部分が露出した状態で等方性エッチングを行うことにより、有機系絶縁体 18 a を複数の溝 19 a ~ 19 f ' のそれぞれから除去する。有機系絶縁体 18 a の絶縁膜 8 、絶縁膜 9 、及び第 2 の導電ラインのそれぞれに対するエッチング選択比は、例えば  $\text{CF}_4 + \text{O}_2$  をエッチングガスとして用いた場合、1 / 20 である。このため、有機系絶縁体 18 a を選択的にエッチングすることができる。また、ドライエッチングが等方性であるため、図 9 ( A ) 、 ( B ) に示すように、第 2 の導電ライン 13 a , 13 c の下にある有機系絶縁体 18 a も、回り込むエッチングガス ( 例えば  $\text{CF}_4 + \text{O}_2$  ) によって効果的に除去される。

【 0025 】

なお、有機系絶縁体 18 a を等方性ドライエッチングにより除去するために、有機系絶縁体 18 a を露出させる工程を第 2 の配線層 13 のパターニングのためのドライエッチング時のオーバーエッチングを利用して実施することができる。この場合、有機系絶縁体 18 a を露出させる工程と第 2 の配線層 13 をパターニングする工程とを共通化することができる。

【 0026 】

図 11 ( A ) ~ ( C ) は、同じ工程における断面を示す。図 11 の工程では、高密度プラズマ CVD 法を用いて、複数の溝 19 a ~ 19 f ' における半導体基板の表面に垂直な方向から見た場合に第 2 の導電ライン 13 a ~ 13 f に重ならない部分に絶縁体 ( 第 2 の絶縁体 ) 14 a を埋め込む ( 図 11 ( C ) 参照 ) 。また、複数の第 2 の導電ライン 13 a

10

20

30

40

50

~13fを覆うように絶縁膜14を形成する。絶縁体14aと絶縁膜14とは、連続的に形成される。絶縁膜14は、例えば、SiO<sub>2</sub>で形成される。すなわち、複数の溝19a~19f'内(溝内)の複数の第1の導電ラインと第2の導電ラインとの交差する複数の領域における一部の領域をエアギャップ10として残すように、複数の溝19a~19f'に絶縁体(第2の絶縁体)14aを埋め込む。このとき、複数の溝19a~19f'のそれぞれにおける半導体基板SBの表面SBaに垂直な方向から見た場合に第2の導電ラインが重ならない部分に第2の絶縁体を埋め込む(第7の工程)。例えば、図11(A)、(B)に示すように、複数の交差する領域CR1~CR12(図1参照)のうち、交差する領域CR1, CR2にプラグ12a、12bが配され、残りの複数の交差する領域CR3~CR12のそれぞれにエアギャップ10が形成されている。このとき、各第2の導電ラインの下にある空間にはCVDガスが回り込み難いために、真空空間をなしている、あるいは、空気が満たされている状態を保持したままのエアギャップ10が第2の導電ラインの幅以下の幅で形成される。すなわち、エアギャップ10における第1の導電ラインに沿った方向の幅が第2の導電ラインの幅以下になるように、エアギャップ10は形成される。一方、エアギャップ10における第2の導電ラインに沿った方向の幅は、図4の工程で各溝の幅が各第1の導電ラインの幅以下になるように形成されていることに応じて、第1の導電ラインの幅以下になっている。次に、CMP法を用いて、絶縁膜14を研磨することにより絶縁膜14の上面を平坦化する。次いで、例えば第2の導電ラインの表面を露出するように、絶縁膜14にスルーホール(図示せず)を形成し、そのスルーホールに金属(例えばタンクスチタン)を埋め込むことにより、プラグ(図示せず)を形成する。その後、絶縁膜14の上に金属積層膜(例えば、TiN膜/A1Cu合金膜/TiN膜の積層膜)における各膜をスパッタリング法により順次成膜し、その後にフォトリソグラフィー工程とドライエッチング工程とを経て第3の配線層(図示せず)のパターンを形成する。

#### 【0027】

ここで、図2(B)に示すように、第2の配線層13と絶縁膜6との間は、絶縁膜11を介して、絶縁膜8と絶縁膜9とに含まれる支柱27によって支えられる構造になっている。このため、第2の配線層13が図2(B)における横方向に長くなった場合でも、多層配線構造MLの全体としての機械的強度は保持され、後の工程におけるCMP等による応力がかかった場合にも多層配線構造MLが破壊されにくい。また、第1の導電ラインと第2の導電ラインとの交差する領域(例えば、交差する領域CR3~CR12)にエアギャップ10が設けられているので、第1の導電ラインと第2の導電ラインとのライン間容量が低減されている。このように、本実施形態に係る製造方法によれば、多層配線構造MLにおけるライン間容量を低減しながら、多層配線構造MLの機械的強度の低下を抑制することができる半導体装置SDを得ることができる。

#### 【0028】

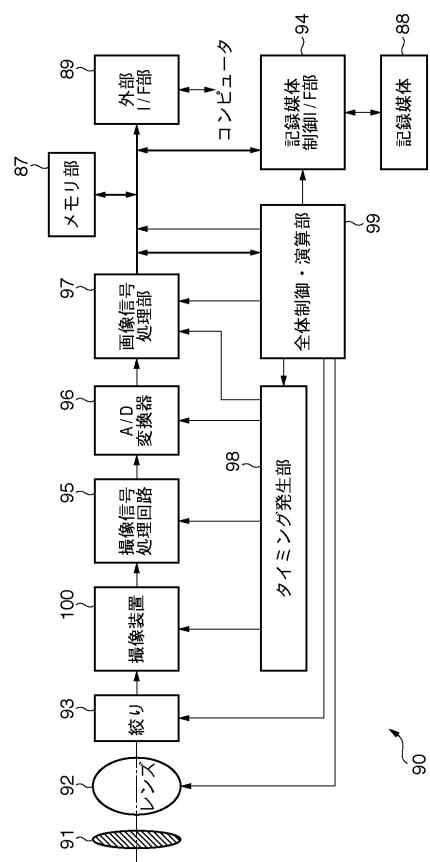

次に、本発明の光電変換装置を適用した撮像システムの一例を図12に示す。撮像システム90は、図12に示すように、主として、光学系、撮像装置86及び信号処理部を備える。光学系は、主として、シャッター91、レンズ92及び絞り93を備える。撮像装置86は、光電変換装置100を含む。信号処理部は、主として、撮像信号処理回路95、A/D変換器96、画像信号処理部97、メモリ部87、外部I/F部89、タイミング発生部98、全体制御・演算部99、記録媒体88及び記録媒体制御I/F部94を備える。なお、信号処理部は、記録媒体88を備えなくても良い。シャッター91は、光路上においてレンズ92の手前に設けられ、露出を制御する。レンズ92は、入射した光を屈折させて、撮像装置86の光電変換装置100の撮像面に被写体の像を形成する。絞り93は、光路上においてレンズ92と光電変換装置100との間に設けられ、レンズ92を通過後に光電変換装置100へ導かれる光の量を調節する。撮像装置86の光電変換装置100は、光電変換装置100の撮像面に形成された被写体の像を画像信号に変換する。撮像装置86は、その画像信号を光電変換装置100から読み出して出力する。撮像信号処理回路95は、撮像装置86に接続されており、撮像装置86から出力された画像信

10

20

30

40

50

号を処理する。A/D変換器96は、撮像信号処理回路95に接続されており、撮像信号処理回路95から出力された処理後の画像信号（アナログ信号）を画像信号（デジタル信号）へ変換する。画像信号処理部97は、A/D変換器96に接続されており、A/D変換器96から出力された画像信号（デジタル信号）に各種の補正等の演算処理を行い、画像データを生成する。この画像データは、メモリ部87、外部I/F部89、全体制御・演算部99及び記録媒体制御I/F部94などへ供給される。メモリ部87は、画像信号処理部97に接続されており、画像信号処理部97から出力された画像データを記憶する。外部I/F部89は、画像信号処理部97に接続されている。これにより、画像信号処理部97から出力された画像データを、外部I/F部89を介して外部の機器（パソコン等）へ転送する。タイミング発生部98は、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97に接続されている。これにより、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97へタイミング信号を供給する。そして、撮像装置86、撮像信号処理回路95、A/D変換器96及び画像信号処理部97がタイミング信号に同期して動作する。全体制御・演算部99は、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94に接続されており、タイミング発生部98、画像信号処理部97及び記録媒体制御I/F部94を全体的に制御する。記録媒体88は、記録媒体制御I/F部94に取り外し可能に接続されている。これにより、画像信号処理部97から出力された画像データを、記録媒体制御I/F部94を介して記録媒体88へ記録する。以上の構成により、光電変換装置100において良好な画像信号が得られれば、良好な画像（画像データ）を得ることができる。

10

20

#### 【0029】

次に、本発明の第2実施形態に係る半導体装置SD200を、図13～図21を用いて説明する。以下では、第1実施形態と異なる部分を中心に説明する。

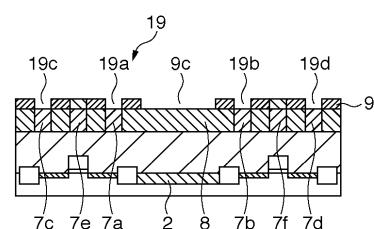

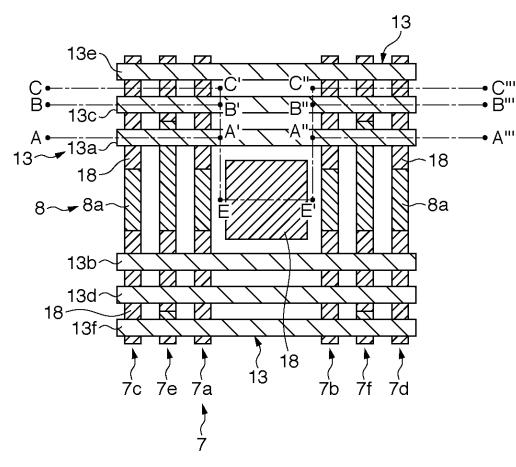

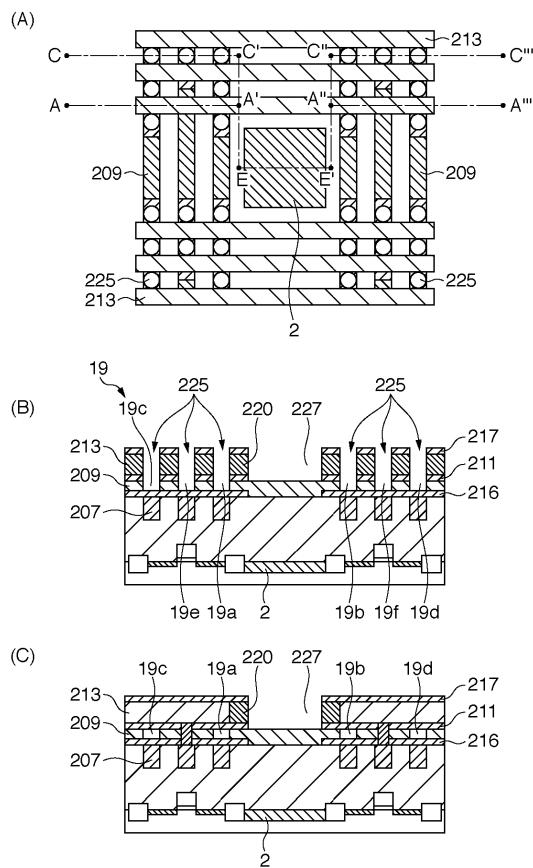

#### 【0030】

図13に示すように、半導体装置SD200は、光電変換装置200を含む。図13は、半導体装置SD200における図1(B)の断面に対応する断面を示す図である。半導体装置SD200の光電変換装置200は、多層配線構造ML200を備える。多層配線構造ML200は、デュアルダマシン構造を有している。多層配線構造ML200は、次の構成要素を含む点で第1実施形態と異なる。第1の配線層207は、絶縁膜206の中に配されている。第1の配線層207は、例えば、銅を主成分とする金属又は金属間化合物で形成されている。第1の配線層207における複数の第1の導電ライン207a～207fは、それぞれ、シングルダマシン法にて、絶縁膜206に形成された溝に埋め込まれている。拡散抑制膜（拡散バリア膜）216は、第1の配線層207を覆っている。拡散抑制膜216は、第1の配線層207の材料（例えば銅）が絶縁膜209中へ拡散することを抑制する。第2の配線層213は、絶縁膜220の中に配されている。第2の配線層213は、例えば、銅を主成分とする金属又は金属間化合物で形成されている。第2の配線層213における複数の第2の導電ライン213a～213fは、デュアルダマシン法にて、絶縁膜220に形成された溝に上記の材料が埋め込まれることにより形成されている。絶縁膜211は、デュアルダマシン法における第2の導電ラインを埋め込むための溝を形成するエッチングを行う際のエッチング停止層としての役割を果たす。拡散抑制膜（拡散バリア膜）217は、第2の配線層213を覆っている。拡散抑制膜217は、第2の配線層213の材料（例えば銅）が絶縁膜223中へ拡散することを抑制する。拡散抑制膜216、絶縁膜211、及び拡散抑制膜217は、それぞれ、光電変換部2の上方に位置する部分に開口を有する。

30

40

#### 【0031】

ここで、複数の交差する領域CR1～CR12（図1(A)、(B)及び図2(A)参照）のうち交差する領域CR1、CR2には、プラグ212a及び212bが配されている。プラグ212a及び212bは、それぞれ、例えば、銅を主成分とする金属又は金属間化合物で形成されている。プラグ212a及び212bは、デュアルダマシン法にて、絶縁膜211、絶縁膜209、及び拡散抑制膜216に形成された穴に上記の材料が埋め

50

込まれることにより形成されている。一方、複数の交差する領域 C R 1 ~ C R 1 2 のうち残りの交差する領域 C R 3 ~ C R 1 2 にエアギャップ 1 0 が設けられている点は、第 1 実施形態と同様である。エアギャップ 1 0 の 4 つの側方では、支柱 2 2 7 が絶縁膜 2 0 6 と絶縁膜 2 1 1 との間を支えている。支柱 2 2 7 は、拡散抑制膜 2 1 6 及び絶縁膜 2 0 9 に含まれている。

#### 【 0 0 3 2 】

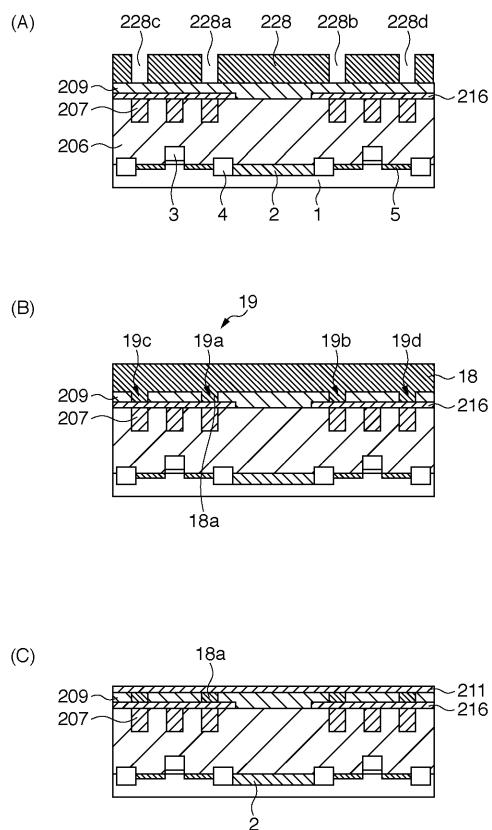

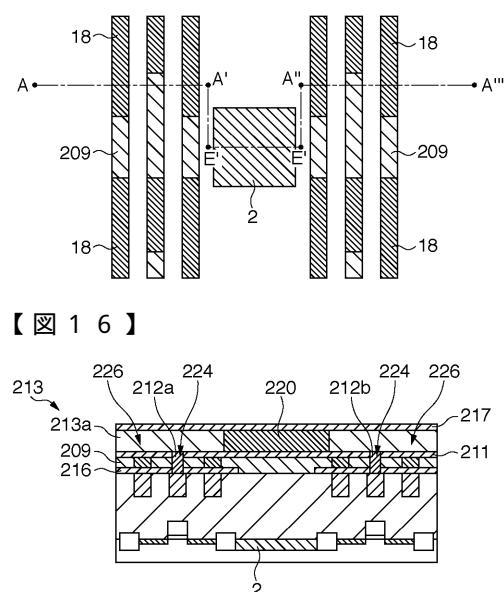

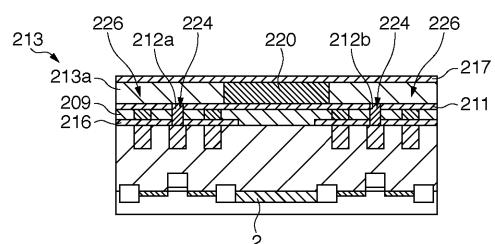

また、半導体装置 S D 2 0 0 の製造方法が、図 1 4 ~ 図 2 1 に示すように、次の点で第 1 実施形態と異なる。図 1 4 、 1 6 に示す断面は、図 1 ( B ) の断面に対応した断面である。図 1 5 は、図 1 4 ( C ) の工程における平面図である。図 1 8 、 1 9 に示す断面は、それぞれ、図 2 ( C ) 、図 1 ( B ) の断面に対応した断面である。図 1 7 は、図 1 8 、 1 9 の工程における平面図である。図 2 0 ( B ) 、 ( C ) に示す断面は、それぞれ、図 2 ( C ) 、図 1 ( B ) の断面に対応した断面である。図 2 0 ( A ) は、図 2 0 ( B ) 、 ( C ) の工程における平面図である。図 2 1 ( B ) 、 ( C ) に示す断面は、それぞれ、図 2 ( C ) 、図 1 ( B ) の断面に対応した断面である。図 2 1 ( A ) は、図 2 1 ( B ) 、 ( C ) の工程における平面図である。

#### 【 0 0 3 3 】

図 1 4 ( A ) の工程では、絶縁膜 2 0 6 の上面を平坦化した後、ダマシン法により第 1 の配線層 2 0 7 を形成する。すなわち、第 1 の配線層 2 0 7 の材料（例えば、銅を主成分とする金属又は金属間化合物）を埋め込むための溝を絶縁膜 2 0 6 に形成し、その材料をその溝に埋め込むことにより、第 1 の配線層 2 0 7 を形成する。その後、プラズマ C V D 法を用いて、第 1 の配線層 2 0 7 を覆うように、拡散抑制膜 2 1 6 を形成する。拡散抑制膜 2 1 6 は、例えば、S i N で形成する。その後に、フォトリソグラフィー工程を経て、拡散抑制膜 2 1 6 における光電変換部 2 の上方に位置した部分をドライエッチング法により除去する。次に、プラズマ C V D 法を用いて、絶縁膜 2 0 6 及び拡散抑制膜 2 1 6 を覆うように絶縁膜 2 0 9 を形成する。絶縁膜 2 0 9 は、例えば、S i O<sub>2</sub> で形成する。そして、絶縁膜 2 0 9 の上面に生じた段差を C M P 法にて研磨して平坦化する。そして、フォトリソグラフィー工程を経て、絶縁膜 2 0 9 の上にエッチングマスク 2 2 8 を形成する。エッチングマスク 2 2 8 は、溝 1 9 ( 図 5 参照 ) を形成すべき領域に開口 2 2 8 a ~ 2 2 8 d を有する。

#### 【 0 0 3 4 】

図 1 4 ( B ) の工程では、エッチングマスク 2 2 8 ( 図 1 4 ( A ) 参照 ) を介して絶縁膜 2 0 9 における第 1 の導電ラインの上の部分をエッチングする。これにより、各溝の幅が各第 1 の導電ラインの幅以下になるように、絶縁膜 2 0 9 に複数の溝 1 9 a ~ 1 9 f ' ( 図 5 参照 ) を形成する点は、第 1 実施形態と同様である。その後、図 6 ( A ) の工程と同様の処理を行う。

#### 【 0 0 3 5 】

図 1 4 ( C ) の工程では、図 6 ( B ) の工程と同様の平坦化処理を行う。これにより、図 1 5 に示すように、有機系絶縁体 1 8 a を露出させる。続いて、プラズマ C V D 法を用いて、絶縁膜 2 0 9 及び有機系絶縁体 1 8 a を覆うように、絶縁膜 2 1 1 を形成する。絶縁膜 2 1 1 は、例えば、S i N で形成する。絶縁膜 2 1 1 は、デュアルダマシン法における第 2 の導電ラインを埋め込むための穴を形成するエッチングを行う際のエッチング停止層としての役割を果たす。

#### 【 0 0 3 6 】

図 1 6 の工程では、プラズマ C V D 法を用いて、絶縁膜（第 2 の絶縁膜）2 2 0 を絶縁膜 2 1 1 の上に形成する。フォトリソグラフィー工程を経て、デュアルダマシン法におけるプラグ 2 1 2 a , 2 1 2 b を埋め込むための第 1 の穴 2 2 4 を絶縁膜 2 2 0 、絶縁膜 2 1 1 、絶縁膜 2 0 9 、及び絶縁膜 2 1 6 に形成する。また、フォトリソグラフィー工程を経て、デュアルダマシン法における第 2 の導電ラインを埋め込むための第 2 の溝 2 2 6 を絶縁膜 2 2 0 に形成する。その後、T a 膜と導電体シード膜とをスパッタリング法により形成し、メッキ法による導電体の埋め込みを第 1 の穴 2 2 4 及び第 2 の溝 2 2 6 に対して

行う。導電体は、例えば、銅を主成分とする金属又は金属間化合物で形成する。そして、C M P 法による研磨・平坦化を行うことにより、プラグ 212 と第 2 の溝 226 に対応した第 2 の配線層 213 とを形成する。次に、プラズマ C V D 法を用いて、第 2 の配線層 213 及び絶縁膜 220 を覆うように拡散抑制膜 217 を形成する。拡散抑制膜 217 は、例えば、S i N で形成する。

【 0037 】

図 18 及び図 19 は、同じ工程における断面を示す。図 18 及び図 19 の工程では、フォトリソグラフィー工程を経て、拡散抑制膜 217 の上にエッチングマスク 229 を形成する。エッチングマスク 229 は、光電変換部 2 の上方の領域に開口 229g を有し、有機系絶縁体 18a を露出するための後述の第 2 の穴 225 を形成すべき領域に開口 229a を有する。エッチングマスク 229 と第 2 の導電ラインとをマスクとして散抑制膜 217、絶縁膜 220、及び絶縁膜 211 をエッチングする。これにより、有機系絶縁体 18a の上面のうち半導体基板の表面 S B a に垂直な方向から見た場合に第 2 の導電ラインが重ならない部分を露出するように複数の第 2 の穴 225 を、拡散抑制膜 217、絶縁膜 220、及び絶縁膜 211 に形成する(図 17 参照)。このとき、拡散抑制膜 217、絶縁膜 220、及び絶縁膜 211 のそれぞれにおける光電変換部 2 の上方に位置した部分も除去されて、第 3 の溝 227 が形成される。

【 0038 】

図 20 (A) ~ (C) は、同じ工程における平面図及び断面図を示す。図 20 の工程では、有機系絶縁体 18a の拡散抑制膜 217、絶縁膜 220、絶縁膜 211、及び絶縁膜 209 のそれぞれに対するエッチング選択比が高くなる条件で第 2 の穴 225 を介して等方性エッチングを行う。これにより、有機系絶縁体 18a を複数の溝 19a ~ 19f'(図 5 参照) から除去する。このとき、拡散抑制膜 216 と絶縁膜 209 とは、それぞれ、有機系絶縁体 18a の等方性ドライエッチングに対し高い耐性を有しているため。有機系絶縁体 18a を選択的にエッチングすることが容易である(図 20 (B) 参照)。また、ドライエッチングが等方性であるため、第 2 の配線層 213 の下にある有機系絶縁体 18a は、回り込むエッチングガスによって除去される(図 20 (C) 参照)。

【 0039 】

図 21 の工程では、高密度プラズマ C V D 法を用いて、絶縁体(第 2 の絶縁体) 223a を複数の第 2 の穴 225 に埋め込むとともに絶縁体 223b を第 3 の溝 227 に埋め込む。また、拡散抑制膜 217 を覆うように絶縁膜 223 を形成する。すなわち、複数の溝 19a ~ 19f' における第 1 の導電ラインと第 2 の導電ラインとの交差する複数の領域における一部の領域をエアギャップ 10 として残すように、複数の第 2 の穴 225 を介して複数の溝 19a ~ 19f' に絶縁体 223a を埋め込む。このとき、各第 2 の導電ラインの下にある空間には C V D ガスが回り込み難いために、真空空間をなしている、あるいは、空気が満たされている状態を保持したままのエアギャップ 10 が第 2 の導電ラインの幅以下の幅で形成される。すなわち、エアギャップ 10 における第 1 の導電ラインに沿った方向の幅が第 2 の導電ラインの幅以下になるように、エアギャップ 10 は形成される。一方、エアギャップ 10 における第 2 の導電ラインに沿った方向の幅は、図 14 (B) の工程で各溝の幅が各第 1 の導電ラインの幅以下になるように形成されていることに応じて、第 1 の導電ラインの幅以下になっている。

【 0040 】

なお、半導体装置の製造方法において、エッチング停止層および拡散抑制膜のそれぞれにおける光電変換部の上方に位置する部分を除去する処理を、エアギャップを形成する工程を利用して実施することができる。このため、エッチング停止層および拡散抑制膜の部分を除去する処理とエアギャップを形成する処理とを別の工程で行う場合に比べて、工程数を削減できる。

【 図 1 】

【 図 2 】

【図3】

(B) A cross-sectional diagram of a layered structure. The layers are labeled 8a1, 8a, 9b, 9a, 8, and 9. The structure consists of a top layer 9 with a hatched pattern, followed by a layer 8, a layer 9a, a layer 9b, a layer 8a, and a bottom layer 8a1. The bottom layer 8a1 is supported by a series of rectangular blocks.

【 図 4 】

【 図 5 】

【図6】

【 四 7 】

【 図 8 】

【 四 9 】

【図10】

### 【図11】

【図 1 2】

### 【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

---

フロントページの続き

(72)発明者 青木 武志

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 今井 聖和

(56)参考文献 米国特許第06211561(US, B1)

特開平11-330232(JP, A)

特開2003-078015(JP, A)

特開2007-184788(JP, A)

国際公開第2007/020688(WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H01L 21/768

H01L 23/532