## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-165222 (P2004-165222A)

(43) 公開日 平成16年6月10日(2004.6.10)

| (51) Int.C1. <sup>7</sup> | F I        |   | テーマコード(参考) |

|---------------------------|------------|---|------------|

| HO1L 21/3205              | HO1L 21/88 | K | 5FO33      |

| HO1L 21/768               | HO1L 21/90 | Α |            |

|                           | HO1L 21/88 | M |            |

審査請求 未請求 請求項の数 11 OL (全 29 頁)

|           |                              |               | - 1 - 114 - 4 - |                |      |      |      |      |

|-----------|------------------------------|---------------|-----------------|----------------|------|------|------|------|

| (21) 出願番号 | 特願2002-326048 (P2002-326048) | (71) 出願人      | 0000058         | 321            |      |      |      |      |

| (22) 出願日  | 平成14年11月8日 (2002.11.8)       |               | 松下電器産業株式会社      |                |      |      |      |      |

|           |                              |               | 大阪府             | 9門真市大字門真1006番地 |      |      |      |      |

|           |                              | (74) 代理人      | 1000818         | 100081813      |      |      |      |      |

|           |                              |               | 弁理士             | 早瀬             | 憲一   |      |      |      |

|           |                              | (72) 発明者      | 山本              | <b>明広</b>      |      |      |      |      |

|           |                              |               |                 | 門真市大           | 字門真  | 100  | 6番地  | 松下   |

|           |                              | 電器産業株式会社内     |                 |                |      |      |      |      |

|           |                              | <br> F ターム (参 |                 | 3 HH11         | JJ01 | JJ11 | KK11 | LL08 |

|           |                              |               | •) 0100         | MMO2           | PP15 | PP27 | PP28 | PP33 |

|           |                              |               |                 | QQ00           | QQ09 | QQ10 | QQ11 | QQ37 |

|           |                              |               |                 | QQ48           | QQ73 | QQ89 | QQ90 | QQ91 |

|           |                              |               |                 |                |      |      |      |      |

|           |                              |               |                 | RR01           | RR06 | SS11 | WW03 | XX00 |

|           |                              |               |                 | XX01           | XX09 | XX16 | XX18 |      |

|           |                              |               |                 |                |      |      |      |      |

(54) 【発明の名称】半導体装置の製造方法

## (57)【要約】

【課題】デュアルダマシンプロセスにおいて銅ヒロックを有する配線上にSiN膜を形成すると不均一な膜厚となり、工程中のSiN膜破れに起因する物理的化学的ダメージを配線に与えてしまうのを防止できる半導体装置の製造方法を得る。

【解決手段】下地配線である第1配線25の形成後にアニールを行い、銅ヒロック26を意図的に発生させ、CMP法により研磨除去する。その後、SiN膜27を形成することにより、銅ヒロックの発生を防ぎ、SiN膜27の均一な膜厚を確保し、工程中のSiN膜27破れを防ぎ、第1配線25に対する物理的化学的ダメージを最低限に抑制する。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項1】

半導体基板上に第1の配線を形成する工程と、

該第1の配線にヒロックを発生させる処理を行うヒロック発生工程と、

該ヒロック発生工程により発生したヒロックを研磨により除去し、前記第 1 の配線の表面を平坦化する処理と、

前記第1の配線上を含む前記半導体基板上に絶縁膜を形成し、該絶縁膜に前記第1の配線が露出するようにヴィア形状を形成し、該ヴィア形状の内部に配線材料膜を埋め込む、ことを特徴とする半導体装置の製造方法。

# 【請求項2】

10

半導体基板上に形成した第1の絶縁膜に、該絶縁膜と表面が同一になるように埋め込まれた第1の配線を形成する工程と、

該 第 1 の 配 線 に ヒ ロ ッ ク を 発 生 さ せ る 処 理 を 行 う ヒ ロ ッ ク 発 生 工 程 と 、

該ヒロック発生工程により発生したヒロックを研磨により除去し、前記第 1 の配線の表面を平坦化する工程と、

前記第1の配線上を含む前記半導体基板上に第2の絶縁膜を形成し、該第2の絶縁膜に前記第1の配線が露出するようにヴィア形状を形成し、該ヴィア形状の内部に配線材料膜を埋め込み、研磨により不要な配線材料膜を除去してヴィアおよび第2の配線を形成する工程とを含む、

ことを特徴とする半導体装置の製造方法。

20

30

50

#### 【請求項3】

半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝の内部を含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、平坦化して第1の配線を形成する工程と、

該 第 1 の 配 線 が 形 成 さ れ た 半 導 体 基 板 に 対 し ア ニ ー ル を 行 う ア ニ ー ル 工 程 と 、

該 ア ニ ー ル に よ り 前 記 第 1 の 配 線 上 に 発 生 し た ヒ ロ ッ ク を 研 磨 し 、 平 坦 化 す る 工 程 と 、

該平坦化された前記第1の配線上にSiN膜を形成する工程と、

該SiN膜上に第2の絶縁膜を形成する工程と、

該第2の絶縁膜に対しヴィア形状形成用フォトレジストマスクを用いて前記第1の配線に相当する位置にヴィア形状を形成する工程と、

前記第2の絶縁膜に対し配線溝形成用フォトレジストマスクを用いて前記ヴィア形状の上部を含む第2の配線溝を形成する工程と、

前記ヴィア形状底部のSiN膜を除去する工程と、

前記ヴィア形状の内部および前記第2の配線溝の内部を含む前記第2の絶縁膜上に第2の 銅膜を形成する工程と、

該第2の銅膜を研磨、平坦化しヴィアと第2の配線とを形成する工程とを含む、

ことを特徴とする半導体装置の製造方法。

### 【請求項4】

請求項3記載の半導体装置の製造方法において、

前記アニール工程は、酸素を抑制した雰囲気で前記第1の配線から銅ヒロックが発生する 40 温度と時間の条件の下でアニール処理を行う、

ことを特徴とする半導体装置の製造方法。

## 【請求項5】

請求項3記載の半導体装置の製造方法において、

前記SiN膜を形成する工程は、前記ヴィア形成時及び前記第2の配線溝形成時のヴィア 底部において、SiN膜が残存するような膜厚の形成を行う、

ことを特徴とする半導体装置の製造方法。

## 【請求項6】

半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝を含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、

平坦化して第1の配線を形成する工程と、

該第1の配線が形成された半導体基板に対し酸素プラズマ処理を行う工程と、

該 酸 素 プラ ズマ 処 理 に よ り 前 記 第 1 の 配 線 に 発 生 し た ヒ ロ ッ ク を 研 磨 し 、 平 坦 化 す る 工 程

該平坦化された前記第1の配線上にSiN膜を形成する工程と、

該SiN膜トに第2の絶縁膜を形成する工程と、

該 第 2 の 絶 縁 膜 に 対 し ヴ ィ ア 形 状 形 成 用 フ ォ ト レ ジ ス ト マ ス ク を 用 い て 前 記 第 1 の 配 線 に 相当する位置にヴィア形状を形成する工程と、

前 記 第 2 の 絶 縁 膜 に 対 し 配 線 溝 形 成 用 フ ォ ト レ ジ ス ト マ ス ク を 用 い て 前 記 ヴ ィ ア 形 状 の 上 部を含む第2の配線溝を形成する工程と、

前記ヴィア形状底部のSiN膜を除去する工程と、

前記ヴィア形状の内部および前記第2の配線溝の内部を含む前記第2の絶縁膜上に第2の 銅膜を形成する工程と、

該第2の銅膜を研磨、平坦化しヴィアと第2の配線とを形成する工程とを含む、

ことを特徴とする半導体装置の製造方法。

### 【請求項7】

請求項6記載の半導体装置の製造方法において、

前記酸素プラズマ処理工程は、基板温度が120°C以下となる条件の下で行う、

ことを特徴とする半導体装置の製造方法。

## 【請求項8】

半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、 該第1の配線溝を含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、 平坦化して第1の配線を形成する工程と、

該 第 1 の 配 線 が 形 成 さ れ た 半 導 体 基 板 に 対 し ア ン モ ニ ア プ ラ ズ マ 処 理 を 行 う 工 程 と 、

該 ア ン モ ニ ア プ ラ ズ マ 処 理 に よ り 前 記 第 1 の 配 線 に 発 生 し た ヒ ロ ッ ク を 研 磨 し 、 平 坦 化 す る工程と、

該平坦化された前記第1の配線上にSiN膜を形成する工程と、

該SiN膜上に第2の絶縁膜を形成する工程と、

該 第 2 の 絶 縁 膜 に 対 し ヴ ィ ア 形 状 形 成 用 フ ォ ト レ ジ ス ト マ ス ク を 用 い て 前 記 第 1 の 配 線 に 相当する位置にヴィア形状を形成する工程と、

前 記 第 2 の 絶 縁 膜 に 対 し 配 線 溝 形 成 用 フ ォ ト レ ジ ス ト マ ス ク を 用 い て 前 記 ヴ ィ ア 形 状 の 上 部を含む第2の配線溝を形成する工程と、

前記ヴィア形状底部のSiN膜を除去する工程と、

前記ヴィア形状および前記第2の配線溝の内部を含む前記第2の絶縁膜上に第2の銅膜を 形成する工程と、

該 第 2 の 銅 膜 を 研 磨 、 平 坦 化 し ヴ ィ ア と 第 2 配 線 と を 形 成 す る 工 程 と を 含 む 、

ことを特徴とする半導体装置の製造方法。

### 【請求項9】

請求項8記載の半導体装置の製造方法において、

前 記 ア ン モ ニ ア プ ラ ズ マ 処 理 工 程 は 基 板 温 度 が 1 2 0 。 C 以 下 の 条 件 の 下 で 行 う 、

ことを特徴とする半導体装置の製造方法。

### 【請求項10】

半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、 該第1の配線溝の内部を含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を 研磨、平坦化して第1の配線を形成する工程と、

該第1の配線上にSiC膜を形成する工程と、

該SiC膜上に第2の絶縁膜を形成する工程と、

該 第 2 の 絶 縁 膜 に 対 し ヴ ィ ア 形 状 形 成 用 フ ォ ト レ ジ ス ト マ ス ク を 用 い て 前 記 第 1 の 配 線 に 相当する位置にヴィア形状を形成する工程と、

前記第2の絶縁膜に対し配線溝形成用フォトレジストマスクを用いて前記ヴィア形状の上

10

20

30

40

部を含む第2の配線溝を形成する工程と、

前記ヴィア形状底部のSiC膜を除去する工程と、

前記ヴィア形状および前記第2の配線溝の内部を含む前記第2の絶縁膜上に銅膜を形成する工程と、

該銅膜を研磨、平坦化しヴィアと第2配線とを形成する工程とを含む、

ことを特徴とする半導体装置の製造方法。

## 【請求項11】

請求項10記載の半導体装置の製造方法において、

前記SiC膜を形成する工程は、前記ヴィア形成時及び前記第2の配線溝形成時のヴィア底部において、SiC膜が残存するような膜厚の形成を行う、

ことを特徴とする半導体装置の製造方法。

### 【発明の詳細な説明】

## [0001]

【発明の属する技術分野】

本発明は、半導体装置の製造方法に関するものであり、特に配線材料として銅を用いたデュアルダマシンプロセスの改良を図ったものに関する。

### [0002]

## 【従来の技術】

近年、配線抵抗を低くするために、配線材料として銅を用いた半導体装置が求められている。特に銅配線を有する半導体装置の製造方法としてデュアルダマシンプロセスが用いられている。

### [0003]

デュアルダマシンプロセスは、絶縁膜に配線溝および下層配線との接続を行うための接続孔を形成した後、その絶縁膜上、配線溝および接続孔内に配線形成用の主導電層を堆積し、さらに、その主導電層を、例えば、CMP(Chemical Mechanical Polishing:化学的機械的研磨)法等によって配線溝および接続孔内のみに残されるように研磨することにより、配線溝および接続孔内に埋め込み配線を形成するものである。

## [0004]

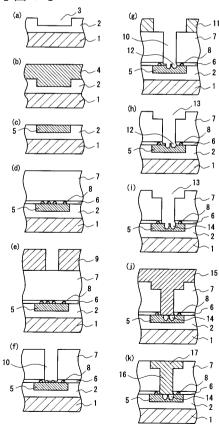

以下、この従来例による半導体装置の製造方法について、図面を参照しながら説明する。 図8は従来例における半導体装置の製造方法の工程断面図を示す。この従来の半導体装置 の製造方法は、図8(a)ないし(k)の各工程からなる。

### [0005]

図9は従来例における半導体装置の製造方法の工程を示すフローチャートであり、図8の工程断面図の(a)ないし(k)の工程に対応する処理工程901ないし912を示している。

### [0006]

図8において、1は半導体基板、2は半導体基板1上に形成された絶縁膜、3は絶縁膜2の表面に形成された第1配線溝、4は第1配線溝3内を含む絶縁膜2の表面を覆うように形成された銅膜、5は第1配線溝3内に形成された第1配線、6は第1配線5上を含む絶縁膜上2に形成された5iN膜、7は5iN膜6上に形成された絶縁膜、8は銅膜5から発生した銅ヒロックであり、5iN膜6中に侵入している。9は絶縁膜7上に形成されたヴィア形状形成用フォトレジストマスク、10は5iN膜6及び絶縁膜7に形成されたヴィア形状、11は絶縁膜7上に形成された第2配線溝形成用フォトレジストマスク、12は第1配線5の表面に発生したボイド、13は絶縁膜7の表面に形成された第2配線溝11の底面の第1配線5の露出部を覆うとともにヴィア形状10内を充填するように絶縁膜7上に形成された銅膜、16は絶縁膜7内に形成されたヴィア、17は絶縁膜7の第2配線溝13内に形成された第2配線

## [0007]

40

10

20

以下、図8の各工程断面図について説明する。

図 8 ( a ) は半導体基板 1 上に絶縁膜 2 を形成し、絶縁膜 2 の表面に第 1 配線溝 3 を形成した直後の工程断面図である。この段階は図 9 の処理工程 9 0 1 に対応する。

### [0008]

図8(b)はスパッタリング法及びメッキ法により第1配線溝3内を含む絶縁膜2の表面全面に銅膜4を形成した直後の工程断面図である。この段階は図9の処理工程902に対応する。

## [0009]

図8(c)はCMP法により銅膜4及び絶縁膜2を研磨、平坦化し、洗浄し、絶縁膜2と表面が同一となるように第1配線5を形成した直後の工程断面図である。この段階は図9の処理工程903に対応する。

#### [ 0 0 1 0 ]

図8(d)は第1配線5上を含む絶縁膜2上に、CVD法によりSiN膜6及び絶縁膜7をこの順で形成した直後の工程断面図であり、第1配線5からSiN膜6中へ銅ヒロック8が侵入している。この段階は図9の処理工程904および905に対応する。

#### [0011]

図 8 ( e ) はリソグラフィ法により絶縁膜 7 上にヴィア形状形成用フォトレジストマスク 9 を形成した直後の工程断面図である。この段階は図 9 の処理工程 9 0 6 に対応する。

#### [0012]

図8(f)はフォトレジストマスク9を用いたドライエッチング法によりSiN膜6及び 絶縁膜7にヴィア形状10を形成し、アッシング及び洗浄によりヴィア形状形成用フォト レジストマスク9を除去した直後の工程断面図である。この段階は図9の処理工程907 に対応する。

## [0013]

図 8 (g)はリソグラフィ法により、絶縁膜7上に開口を有する第2配線溝形成用フォトレジストマスク11を形成した直後の工程断面図である。フォトレジストマスク11はヴィア形状10を含む領域に開口を有しており、第1配線5中にはボイド12が発生している。この段階は図9の処理工程908に対応する。

## [0014]

図8(h)はフォトレジストマスク11を用いたドライエッチング法によりヴィア形状10の上部を含む絶縁膜7の表面の一部に第2配線溝13を形成し、アッシング及び洗浄により第2配線溝形成用フォトレジストマスク11を除去した直後の工程断面図である。この段階は図9の処理工程909に対応する。

## [0015]

図8(i)はドライエッチング法によりSiN膜6をエッチングし、洗浄した直後の工程断面図である。第1銅配線5中には侵食部14が形成されている。この段階は図9の処理工程910に対応する。

## [0016]

図8(j)はスパッタリング法及びメッキ法によりヴィア形状 1 0 内および第 1 銅配線 5 の露出した表面および第 2 配線溝 1 3 内を含む絶縁膜 7 上全面に銅膜 1 5 を形成した直後の工程断面図である。この段階は図 9 の処理工程 9 1 1 に対応する。

### [0017]

図8(k)はCMP法により銅膜15及び絶縁膜7を研磨、平坦化し、洗浄し、ヴィア形状10内を銅膜により充填したヴィア16と、絶縁膜7と表面が同一の第2配線17とを形成した直後の工程断面図である。この段階は図9の処理工程912に対応する。

## [0018]

従来の半導体装置の製造方法は以上のような工程を有しており、配線材料として銅を用いた配線を形成することができ、配線の低抵抗化を実現した半導体装置を製造することができる。

## [0019]

40

10

20

この従来方法においては、絶縁膜に形成された溝などの内部に導電膜を埋め込んだ後、絶縁膜上の不要な導電膜を除去するダマシン法を用いて第1銅配線を形成し、その後、ダマシン法と同様の工程によりヴィアおよび配線を同時に形成するデュアルダマシン法によりヴィア及び第2銅配線を形成している。

#### [0020]

このようにダマシン法を用いて第1銅配線を形成する点を示すものとして、例えば特許文献1がある。また、ダマシン法を用いて第1銅配線を形成した後、デュアルダマシン法によりヴィア及び第2銅配線を形成する点を示すものとして、例えば特許文献2がある。

#### [0021]

### 【特許文献1】

特開2001-53076号公報(第4頁、第8-9頁、第7図、第8図、第10図)

### 【特許文献2】

特開 2 0 0 1 - 2 9 1 7 2 0 号公報 ( 第 4 頁、第 1 0 頁、第 2 4 頁 - 第 2 5 頁、第 4 図、 第 6 6 図 - 第 7 7 図 )

### [0022]

### 【発明が解決しようとする課題】

しかしながら、上記従来例では、第1配線 5 から S i N 膜 6 中へ銅ヒロック 8 が侵入することにより(図 8 ( e ) 参照)、部分的に S i N 膜 6 が薄膜化し、後の工程であるヴィア形状 1 0 を形成するためのドライエッチング工程(図 8 ( f ) 参照)から、ヴィア形状 1 0 底部の S i N 膜 6 を除去するためのドライエッチング工程前までの工程を経る間に S i N 膜 6 の薄膜化した部分が破れ、第1配線 5 が部分的に露出し、第1配線 5 に意図せぬダメージが与えられ、ボイド 1 2 を発生させ(図 8 ( g ) 参照)、それを基点として第1配線 5 に侵食部 1 4 を発生させてしまう(図 8 ( i ) 参照)。

### [ 0 0 2 3 ]

その後、ヴィア16と第2配線17とを形成すれば(図8(k)参照)、半導体装置の製造方法としての一連の工程は終了する。しかしながら、このような従来方法で製造した半導体装置では、第1配線5と第2配線17との間にヴィア16を介する電流を通電させたとき、ヴィア抵抗の異常な上昇や断線などの信頼性不良を発生させてしまうおそれがある

## [0024]

本発明は上記の課題に鑑みてなされたもので、第1配線5への工程中のダメージを極力低減し、ヴィア抵抗の異常な上昇や配線の信頼性不良を防ぐことが可能な半導体装置を製造できる半導体装置の製造方法を提供することを目的としている。

## [0025]

## 【課題を解決するための手段】

この課題を達成するために、本発明の請求項1に係る半導体装置の製造方法においては、 半導体基板上に第1の配線を形成する工程と、該第1の配線にヒロックを発生させる処理 を行うヒロック発生工程と、該ヒロック発生工程により発生したヒロックを研磨により除 去し、前記第1の配線の表面を平坦化する処理と、前記第1の配線上を含む前記半導体基 板上に絶縁膜を形成し、該絶縁膜に前記第1の配線が露出するようにヴィア形状を形成し 、該ヴィア形状の内部に配線材料膜を埋め込むようにしたものである。

### [0026]

本発明では、第1の配線形成後に、意図的にヒロックを発生させる工程を追加し、さらに発生したヒロックを研磨除去する。このため、その後の絶縁膜を形成する工程でヒロックが発生することはなく、絶縁膜下にバリア層を形成しておく場合に、バリア層を均一な膜厚に形成することができ、その後の工程でバリア層が意図せぬ破れを起こすことが無く、第1の配線へのダメージを最小限に抑えることが可能となり、第1の配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置を製造することが可能となる。

## [ 0 0 2 7 ]

50

10

20

30

30

40

50

本発明の請求項2に係る半導体装置の製造方法においては、半導体基板上に形成した第1の絶縁膜に、該絶縁膜と表面が同一になるように埋め込まれた第1の配線を形成する工程と、該第1の配線にヒロックを発生させる処理を行うヒロック発生工程と、該ヒロック発生工程により発生したヒロックを研磨により除去し、前記第1の配線の表面を平坦化する工程と、前記第1の配線上を含む前記半導体基板上に第2の絶縁膜を形成し、該第2の絶縁膜に前記第1の配線が露出するようにヴィア形状を形成し、該ヴィア形状の内部に配線材料膜を埋め込み、研磨により不要な配線材料膜を除去してヴィアおよび第2の配線を形成する工程とを含むようにしたものである。

[ 0 0 2 8 ]

本発明では、第1の配線形成後に、意図的にヒロックを発生させる工程を追加し、さらに発生したヒロックを研磨除去する。このため、その後の絶縁膜を形成する工程でヒロックが発生することはなく、第2の絶縁膜下にバリア層を形成しておく場合に、バリア層を均一な膜厚に形成することができ、その後の工程でバリア層が意図せぬ破れを起こすことが無く、第1の配線へのダメージを最小限に抑えることが可能となり、第1の配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置を製造することが可能となる。

[0029]

[0030]

本発明では、第1の配線形成後にアニール工程を追加し、意図的に銅ヒロックを発生させる。さらに発生した銅ヒロックをCMP法によって研磨除去する。このため、その後のSiN膜や絶縁膜を形成する工程では銅ヒロックが発生することはなく、SiN膜を均一な膜厚に形成することができる。従って、その後の工程でSiN膜が意図せぬ破れを起こすことが無く、第1の配線へのダメージを最小限に抑えることが可能となり、第1の配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置を製造することが可能となる。

[0031]

また、本発明の請求項4に係る半導体装置の製造方法によれば、請求項3記載の半導体装置の製造方法において、前記アニール工程は、酸素を抑制した雰囲気で前記第1の配線から銅ヒロックが発生する温度と時間の条件の下でアニール処理を行うようにしたものである。

[0032]

本発明では、第1の配線形成後に追加したアニール工程において、銅ヒロックを十分発生 させるため、以降の工程においてヒロックが発生することがなくなる。

[0033]

また、本発明の請求項 5 に係る半導体装置の製造方法によれば、請求項 3 記載の半導体装置の製造方法において、前記 S i N 膜を形成する工程は、前記ヴィア形成時及び前記第 2 の配線溝形成時のヴィア底部において、 S i N 膜が残存するような膜厚の形成を行うよう

にしたものである。

#### [ 0 0 3 4 ]

本発明では、第2の絶縁膜下に形成するSiN膜として、ヴィア形成時及び第2の配線溝形成時に行う処理を経ても残存できる厚さのものを形成しておくため、これらの工程を経た後でもSiN膜が確実に残存する。

#### [0035]

また、本発明の請求項6に係る半導体装置の製造方法によれば、半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝を形成して第1の配線溝を形成して第1の配線流域では、該第1の配線が形成された半導体基板に対し酸素プラズマ処理を形成された半導体基板に対しで、該では、立て変により前記第1の配線に発生したヒロックを研磨し、平均に第2の絶縁膜を形成する工程と、該第2の絶縁膜に対しヴィア形状形成用フォトレジスクを用いて前記第1の配線に付って形状を形成する工程と、前記第2の絶縁膜に対しでは、で形状の上で、前記第2の絶縁膜に対し配線溝形成用フォトレジスクを用いて前記ヴィア形状の上の上でが、前記第2の配線溝を形成する工程と、前記ヴィア形状底部のSiN膜を除去する工程との記算でである。である。である。

## [0036]

本発明では、第1の配線形成後に酸素プラズマ処理工程を追加し、意図的に銅ヒロック及び酸化銅層を発生させる。さらに発生した銅ヒロック及び酸化銅層をCMP法によって研磨除去する。その後、SiN膜や絶縁膜を形成する工程では銅ヒロックが発生することはなく、SiN膜は均一な膜厚に形成することができる。従って、その後の工程でSiN膜が意図せぬ破れを起こすことが無く、第1の配線へのダメージを最小限に抑えることが可能となり、第1の配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができる。

### [0037]

また、本発明の請求項 7 に係る半導体装置の製造方法によれば、請求項 6 記載の半導体装置の製造方法において、前記酸素プラズマ処理工程は、基板温度が 1 2 0 ° C 以下となる条件の下で行うようにしたものである。

## [0038]

本発明では、第1の配線形成後に追加した酸素プラズマ処理工程において、銅ヒロックを十分発生させるため、以降の工程においてヒロックが発生することがなくなる。酸素プラズマ中(酸化雰囲気中)で銅ヒロック発生処理を行うことにより、比較的低温、短時間でヒロックを発生させることができる。

### [0039]

また、本発明の請求項8に係る半導体装置の製造方法によれば、半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝を含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、平坦化して第1の配線を形成する工程と、該第1の配線が形成された半導体基板に対しアンモニアプラズマ処理により前記第1の配線に発生したヒロックを研でし、平坦化する工程と、該平坦化された前記第1の配線上にSiN膜を形成する工程と、該第2の絶縁膜に対しでする工程と、該第2の絶縁膜に対しずィア形状を形成する工程と、前記第2の絶縁膜に対し配線溝形成用フォトレジストマスクを用いて前記第1の配線に相当する位置にヴィア形状を形成する下程と、前記第2の配線溝を形成する工程と、前記ヴィア形状および前記第2の配線溝の内部を含む前記第2の絶縁膜上に第2の銅膜を形成する工程と、該第2の銅膜を研磨、平坦化しヴィアと第2配線とを形成する工程とを含むようにしたものである。

20

30

30

40

50

#### [0040]

本発明では、第1配線形成後にアンモニアプラズマ処理工程を追加し、意図的に銅ヒロックを発生させる。さらに発生した銅ヒロックをCMP法によって研磨除去する。このため、その後のSiN膜や絶縁膜を形成する工程では銅ヒロックが発生することはなく、SiN膜を均一な膜厚に形成することができる。従って、その後の工程でSiN膜が意図せぬ破れを起こすことが無く、第1配線へのダメージを最小限に抑えることが可能となり、第1配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置を製造することが可能となる。

## [0041]

また、本発明の請求項9に係る半導体装置の製造方法によれば、請求項8記載の半導体装置の製造方法において、前記アンモニアプラズマ処理工程は基板温度が120°C以下の条件の下で行うようにしたものである。

### [0042]

本発明では、第1の配線形成後に追加したアンモニアプラズマ処理工程において、銅ヒロックを十分発生させるため、以降の工程においてヒロックが発生することがなくなる。アンモニアプラズマ中(還元雰囲気中)で銅ヒロック発生処理を行うことにより、比較的低温、短時間でヒロックを発生させることができる。

### [0043]

また、本発明の請求項10に係る半導体装置の製造方法によれば、半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝の内部を含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、平坦化して第1の配線を形成する工程と、該第1の配線上にSiC膜を形成する工程と、該SiC膜上に第2の絶縁膜を形成する工程と、該第2の絶縁膜に対しヴィア形状形成用フォトレジストマスクを用いて前記第1の配線に相当する位置にヴィア形状を形成する工程と、前記第2の絶縁膜に対し配線溝形成用フォトレジストマスクを用いて前記ヴィア形状の上部を含む第2の紀線溝を形成する工程と、前記ヴィア形状底部のSiC膜を除去する工程と、前記ヴィア形状および前記第2の配線溝の内部を含む前記第2の絶縁膜上に銅膜を形成する工程と、該銅膜を研磨、平坦化しヴィアと第2配線とを形成する工程とを含むようにしたものである。

### [0044]

本発明では、第1配線形成後にSiC膜を形成し、その後絶縁膜を形成する。SiC膜はSiN膜に比べて硬度が高いために銅ヒロック発生を抑制することができ、SiC膜は均一な膜厚に形成することができる。従って、その後の工程でSiC膜が意図せぬ破れを起こすことが無く、第1配線へのダメージを最小限に抑えることが可能となり、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置を製造することが可能となる

## [0045]

また、本発明の請求項11に係る半導体装置の製造方法によれば、請求項10記載の半導体装置の製造方法において、前記SiC膜を形成する工程は、前記ヴィア形成時及び前記第2の配線溝形成時のヴィア底部において、SiC膜が残存するような膜厚の形成を行うようにしたものである。

## [0046]

本発明では、第2の絶縁膜の下に形成するSiC膜として、ヴィア形成時及び第2の配線 溝形成時に行う処理によっても残存できる厚さのものを形成しておくため、これらの工程 を経た後でもSiC膜が確実に残存する。

## [0047]

### 【発明の実施の形態】

## (実施の形態1)

この実施の形態1は、請求項1ないし5の発明に対応するもので、第1配線を形成後、アニール処理によりこの第1配線に意図的にヒロックを発生させ、これをСMP法で除去し

た後、デュアルダマシン法を行うようにしたもので、意図的にヒロックを発生させたためにヒロック除去後の工程で第1配線にヒロックが発生することがなく、第1配線へのダメージを最小限に抑えることが可能となり、第1配線の侵食を防ぐことが可能となり、ヴィア抵抗の安定化や配線の信頼性を確保することができるようにしたものである。

[0048]

以下、本発明の実施の形態 1 における半導体装置の製造方法について、図面を参照しながら説明する。

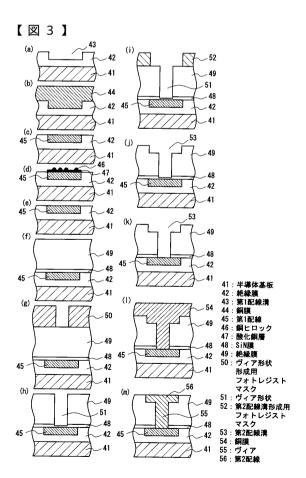

図1は本発明の実施の形態1による半導体装置の製造方法の工程断面図を示す。

[0049]

図 2 は本発明の実施の形態 1 による半導体製造方法の工程フローチャートであり、図 1 の工程断面図の(a)ないし(m)の工程に対応する処理工程 2 0 1 ないし 2 1 4 を示している。

[0050]

図1において、21は半導体基板、22は半導体基板21上に形成された絶縁膜、23は絶縁膜22の表面に形成された第1配線溝、24は第1配線溝23内を含む絶縁膜22の表面を覆うように形成された銅膜、25は第1配線溝23内に形成された第1配線、26は第1配線25上を含む絶縁膜22上に形成された5iN膜、28は5iN膜27上に形成された絶縁膜、29は絶縁膜28上に形成されたヴィア形状形成用フォトレジストマスク、30は5iN膜27及び絶縁膜28に形成されたヴィア形状形成用フォトレジストマスク、30は5iN膜27及び絶縁膜28に形成されたヴィア形状、31は絶縁膜28上に形成された第2配線溝形成用フォトレジストマスク、32は絶縁膜28の表面に形成された第2配線溝形成用フォトレジストマスク、32は絶縁膜28の表面に形成された第2配線溝、33はヴィア形状30底面の第1配線25の露出部を覆うとともにヴィア形状30内を充填するように絶縁膜28上に形成された銅膜、34は絶縁膜28内に形成されたヴィア、35は絶縁膜28の第2配線溝32内に形成された第2配線である。

[0051]

以下では図1の各工程断面図について説明する。

図1(a)は半導体基板21上に絶縁膜22を形成し、絶縁膜22の表面に第1配線溝23を形成した直後の工程断面図である。この段階は図2の処理工程201に対応し、成膜装置およびエッチング装置により実現される。

[ 0 0 5 2 ]

図 1 ( b ) はスパッタリング法及びメッキ法により第 1 配線溝 2 3 内を含む絶縁膜 2 2 の表面全面に銅膜 2 4 を形成した直後の工程断面図である。この段階は図 2 の処理工程 2 0 2 に対応し、スパッタリング装置およびメッキ装置により実現される。

[0053]

図1(c)はCMP法により銅膜24及び絶縁膜22を研磨、平坦化し、洗浄し、絶縁膜22と表面が同一となるように第1配線25を形成した直後の工程断面図である。この段階は図2の処理工程203に対応し、CMP装置および洗浄装置により実現される。

[0054]

図 1 ( d ) はアニール工程により第 1 配線 2 5 上に銅ヒロック 2 6 を意図的に発生させた直後の工程断面図である。この段階は図 2 の処理工程 2 0 4 に対応し、アニール装置により実現される。

[0055]

図 1 ( e )は C M P 法により銅ヒロック 2 6 を研磨、平坦化し、洗浄した直後の工程断面図である。この段階は図 2 の処理工程 2 0 5 に対応し、 C M P 装置および洗浄装置により実現される。

[0056]

図1(f)はCVD法により第1配線25上を含む絶縁膜22上全面にSiN膜27及び 絶縁膜28をこの順で形成した直後の工程断面図である。この段階は図2の処理工程20 6および207に対応し、成膜装置により実現される。

[0057]

50

40

10

20

図 1 ( g )はリソグラフィ法により絶縁膜 2 8 上にヴィア形状形成用フォトレジストマスク 2 9 を形成した直後の工程断面図である。この段階は図 2 の処理工程 2 0 8 に対応し、レジスト成膜装置およびリソグラフィ装置により実現される。

[0058]

図 1 ( h ) はフォトレジストマスク 2 9 を用いたドライエッチング法により S i N 膜 2 7 及び絶縁膜 2 8 にヴィア形状 3 0 を形成し、アッシング及び洗浄によりヴィア形状形成用フォトレジストマスク 2 9 を除去した直後の工程断面図である。この段階は図 2 の処理工程 2 0 9 に対応し、ドライエッチング装置,アッシング装置および洗浄装置により実現される。

[0059]

図 1 ( i ) はリソグラフィ法により絶縁膜 2 8 上に第 2 配線溝形成用フォトレジストマスク 3 1 を形成した直後の工程断面図である。フォトレジストマスク 3 1 はヴィア形状 3 0 を含む領域に開口を有している。この段階は図 2 の処理工程 2 1 0 に対応し、レジスト成膜装置およびリソグラフィ装置により実現される。

[0060]

図1( j )はフォトレジストマスク31を用いたドライエッチング法により絶縁膜28の表面の一部に第2配線溝32を形成し、アッシング及び洗浄により第2配線溝形成用フォトレジストマスク31を除去した直後の工程断面図である。この段階は図2の処理工程211に対応し、ドライエッチング装置,アッシング装置および洗浄装置により実現される

[0061]

図 1 ( k )はドライエッチング法によりSiN膜27をエッチングし、洗浄した直後の工程断面図である。この段階は図 1 の処理工程212に対応し、ドライエッチング装置および洗浄装置により実現される。

[0062]

図 1 (1)はスパッタリング法及びメッキ法によりヴィア形状 3 0 内および第 1 配線 2 5 の露出した表面および第 2 配線溝 3 2 内を含む絶縁膜 2 8 上全面に第 2 の銅膜 3 3 を形成した直後の工程断面図である。この段階は図 2 の処理工程 2 1 3 に対応し、スパッタリング装置およびメッキ装置により実現される。

[0063]

図 1 (m)は CMP法により銅膜 3 3 及び絶縁膜 2 8 を研磨、平坦化し、洗浄し、ヴィア形状 3 0 内を銅膜により充填したヴィア 3 4 と、絶縁膜 2 8 と表面が同一の第 2 配線 3 5 とを形成した直後の工程断面図である。この段階は図 2 の処理工程 2 1 4 に対応し、 CMP装置および洗浄装置により実現される。

[0064]

次に、本実施の形態1において、半導体製造装置により実行される、半導体装置の製造方法について説明する。

図1(a)ないし図1(c)は半導体基板21上の絶縁膜22の表面の一部に形成された配線溝23に埋め込まれた第1配線25を形成する工程である。

[0065]

これは従来の図8(a)ないし図8(c)と同様、半導体基板21上に絶縁膜22を形成し、絶縁膜22の表面に第1配線溝23を形成し、スパッタリング法及びメッキ法により第1配線溝23内を含む絶縁膜22の表面全面に銅膜24を形成し、CMP法により銅膜24及び絶縁膜22を研磨、平坦化し、洗浄し、絶縁膜22と表面が同一となるように第1配線25を形成する、というものである。

[0066]

図1(c)の工程断面図に示された半導体基板に対して酸素濃度を抑制した雰囲気中で150°C程度のアニールを120分程度行うと、銅ヒロック26が第1配線25上に発生する(図1(d)参照)。これは第1配線25が熱的なストレスを与えられることにより、銅原子が移動し、銅のグレイン成長が促進されることに起因すると考えられる。銅ヒロ

10

20

40

30

30

40

50

ックはランダムに発生し、その高さは 5 0 ~ 1 0 0 n m 程度である。第 1 配線 2 5 の配線 膜厚は350nm程度に設定している。銅のグレイン成長を促進させるためにはさらなる 高温でのアニールを行うことが望ましいが、例えば400°C程度の高温で処理すると、 1 0 p p m 程 度 の 微 量 な 酸 素 濃 度 を 有 す る 雰 囲 気 中 で も 第 1 配 線 2 5 上 に 酸 化 銅 が 形 成 さ れてしまう。このため、アニール装置の酸素濃度抑制能力の制約上、または生産性を考慮 し、 1 5 0 ° C 程度かつ 1 2 0 分程度の熱処理を行うことが合理的である。また、アニー ルの雰囲気として窒素を用いたが、銅に対して不活性なガスであれば窒素ガス以外を用い ても良い。要は、酸化銅形成を抑制しながら、銅ヒロックを意図的に発生させることが肝 要である。その後、CMP法により銅ヒロック26を研磨し、洗浄し、第1配線25を平 坦化する。この状態では第1配線に再度熱処理を加えても、銅原子が移動することは無い 。すなわち銅のグレイン成長は飽和状態にある。従って、第1配線25は銅ヒロックの存 在しない図1(e)の状態になる。次に、図1(f)のようにCVD法によりSiN膜2 7 及び絶縁膜 2 8 を形成する。この C V D 法による S i N 膜 2 7 及び絶縁膜 2 8 の形成時 には最高到達温度が400°C程度まで半導体基板21の温度が上昇する。従来例ではこ の 熱 ス ト レ ス が 図 8 ( c ) に 示 す 第 1 配 線 5 に 与 え ら れ る と 、 銅 原 子 が 移 動 し 銅 の グ レ イ ン 成 長 が 促 進 さ れ 、 図 8 ( d ) に 示 す よ う な 銅 ヒ ロ ッ ク 8 が S i N 膜 6 へ と 侵 入 し て しま う。しかしながら、本実施の形態1では、この熱ストレスが図1( e )に示す第1配線 2 5に与えられたとしても、銅原子が移動することは無く、銅のグレイン成長が促進されず 、もはや銅ヒロックは発生しない。このため、SiN膜27は所望の均一な膜厚を有する ことができ、図1(f)のようになる。

[0067]

SiN膜27の膜厚は配線間容量を低減させるために可能な限り薄膜化することが望まれ ているが、その後のヴィア形成や第2配線溝形成のためのドライエッチング工程やアッシ ングや洗浄で第1配線が露出しないような膜厚に設定することが重要である。本実施の形 態 1 ではSiN膜27の膜厚を150nmと設定した。また、絶縁膜28の膜厚を800 n m とした。従来例の図8(e)に示すようなSiN膜6の膜厚が不均一な状態でヴィア 形 状 1 0 形 成 や 第 2 配 線 溝 1 3 形 成 の た め の ド ラ イ エ ッ チ ン グ を 施 す と 、 S i N 膜 6 が 部 分 的 に 破 れ 、 レ ジ ス ト マ ス ク 除 去 時 の ア ッ シ ン グ や 洗 浄 、 リ ソ グ ラ フ ィ 時 の 現 像 液 な ど に より、第1配線5に物理的、化学的なダメージが複数回与えられ、ボイド12や侵食部1 4 を発生させてしまう。しかしながら、本実施の形態 1 では、図 1 ( h ) に示すヴィア形 状30はSiN膜27中まで到達しているが、SiN膜27を貫通することはなく、第1 配線25が露出することは無い。SiN膜27のエッチング量はヴィア形状30形成のた めのドライエッチング時のオーバーエッチング量によって決まるが、フロロカーボン系の ガスを用い、絶縁膜に対するSiN膜選択比を十分に確保した条件を用い、40nm程度 のエッチング量に抑制している。また本実施の形態1の図1(j)に示す第2配線溝32 形成後のヴィア形状 3 0 の底部は S i N 膜 2 7 中まで到達しているが、第 1 配線 2 5 が露 出することは無い。SiN膜27のエッチング量は第2配線溝32形成のためのドライエ ッチング量と、絶縁膜に対するSiN膜選択比から決まるが、フロロカーボン系のガスを 用い、絶縁膜に対するSiN膜選択比を確保した条件を用い、80nm程度のエッチング 量に抑制している。第2配線溝32形成後のヴィア形状30の底部のSiN膜27は合計 120nm程度がエッチングされ、30nmが残るように設計されている。そして、図1 ( k )に示すようにフロロカーボン系のガスを用いたドライエッチング法により、ヴィア 形状 3 0 底部の S i N 膜 2 7 をエッチングすることにより、 初めて第 1 配線 2 5 が露出す る。その後、洗浄を施し、図1(1)に示すようにスパッタリング法及びメッキ法を用い て 銅 膜 3 3 を 形 成 す る 。 こ の 間 、 第 1 配 線 2 5 へ の ダ メ ー ジ は 従 来 例 に 比 べ て 最 小 限 に 抑 えることができる。その後、図1(m)に示すようにCMP法により銅膜33を研磨、平 坦化し、洗浄し、ヴィア34及び第2配線35を形成する。

[0068]

これにより、第 1 配線 2 5 及びヴィア 3 4 及び第 2 配線 3 5 はボイドや侵食の無い配線となり、ヴィア抵抗の安定化や配線の信頼性を確保することができる。

#### [0069]

このように、本実施の形態1によれば、第1の銅配線を絶縁膜と表面が同一となるように埋め込んで形成した後、意図的にアニール工程を行うことで銅ヒロックを発生させ、この銅ヒロックをCMP法により、研磨し平坦化した後に、デュアルダマシン法により、第1,第2の銅配線を互いに接続するヴィアと第2の銅配線とを形成するようにしたので、デュアルダマシン法を実施する際に第1の銅配線にヒロックが発生することはもはや無く、デュアルダマシン法を実施する際に形成するSiN層に銅ヒロックが侵入し、一部でSiN層が薄膜化するために、第1の銅配線の一部が露出し、ヴィア形状形成時のドライエッチングで意図しないダメージを受け、第1の銅配線に侵食部が生じてしまう、というおそれがなくなり、ヴィア抵抗の異常や断線などの信頼性不良が発生する不具合をなくすことができる。

[0070]

(実施の形態2)

この実施の形態 2 は、請求項 1 , 2 , 6 , 7 の発明に対応するもので、第 1 配線を形成後、酸素プラズマ処理によりこの第 1 配線に意図的にヒロックを発生させ、これを C M P 法で除去した後、デュアルダマシン法を行うようにしたもので、意図的にヒロックを発生させたためにヒロック除去後の工程で第 1 配線にヒロックが発生することがなく、第 1 配線へのダメージを最小限に抑えることが可能となり、第 1 配線の侵食を防ぐことが可能となり、ヴィア抵抗の安定化や配線の信頼性を確保することができるようにしたものである。

[0071]

以下、本発明の実施の形態 2 における半導体装置の製造方法について、図面を参照しながら説明する。

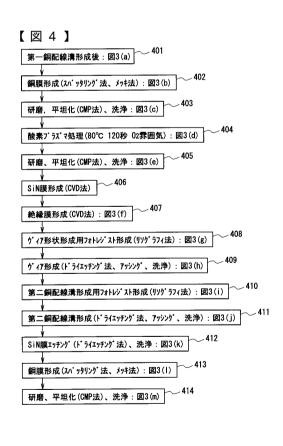

図3は本発明の実施の形態2による半導体装置の製造方法の工程断面図を示す。

[ 0 0 7 2 ]

図4は本発明の実施の形態2による半導体装置の製造方法の工程フローチャートであり、図3の工程断面図の(a)ないし(m)の工程に対応する処理工程401ないし414を示している。

[0073]

図3において、41は半導体基板、42は半導体基板41上に形成された絶縁膜、43は絶縁膜42の表面に形成された第1配線溝、44は第1配線溝43内を含む絶縁膜42の表面を覆うように形成された銅膜、45は第1配線溝43内に形成された第1配線、46は第1配線45の表面に発生した銅ヒロック、47は第1配線45上に形成された酸化銅層、48は第1配線45上を含む絶縁膜42上に形成されたSiN膜、49はSiN膜48上に形成された絶縁膜、50は絶縁膜49上に形成されたヴィア形状形成用フォトレジストマスク、51はSiN膜48及び絶縁膜49に形成されたヴィア形状、52は絶縁膜49の表面に形成された第2配線溝形成用フォトレジストマスク、53は絶縁膜49の表面に形成された第2配線溝形成用フォトレジストマスク、53は絶縁膜49の表面に形成された第2配線溝が51底面の第1配線45の露出部を覆うとともにヴィア形状51内を充填するように絶縁膜49の第2配線溝53内に形成された第2配線である。

[ 0 0 7 4 ]

以下では図3の各工程断面図について説明する。

図3(a)は半導体基板41上に絶縁膜42を形成し、絶縁膜42の表面に第1配線溝43を形成した直後の工程断面図である。この段階は図4の処理工程401に対応し、成膜装置およびエッチング装置により実現される。

[0075]

図 3 ( b )はスパッタリング法及びメッキ法により第 1 配線溝 4 3 内を含む絶縁膜 4 2 の表面全面に銅膜 4 4 を形成した直後の工程断面図である。この段階は図 4 の処理工程 4 0 2 に対応し、スパッタリング装置およびメッキ装置により実現される。

[0076]

20

30

図3(c)はCMP法により銅膜44及び絶縁膜42を研磨、平坦化し、洗浄し、絶縁膜42と表面が同一になるように第1配線45を形成した直後の工程断面図である。この段階は図4の処理工程403に対応し、CMP装置および洗浄装置により実現される。

[0077]

図3 (d)は酸素プラズマ処理により第1配線45上に銅ヒロック46及び酸化銅層47が発生した直後の工程断面図である。この段階は図4の処理工程404に対応し、プラズマ処理装置により実現される。

[0078]

図3(e)はCMP法により銅ヒロック46及び酸化銅層47を研磨、平坦化し、洗浄した直後の工程断面図である。この段階は図4の処理工程405に対応し、CMP装置および洗浄装置により実現される。

[0079]

図3(f)はCVD法により第1配線45上を含む絶縁膜42上全面にSiN膜48及び 絶縁膜49をこの順で形成した直後の工程断面図である。この段階は図4の処理工程40 6および407に対応し、成膜装置により実現される。

[0080]

図3(g)はリソグラフィ法により絶縁膜49上にヴィア形状形成用フォトレジストマスク50を形成した直後の工程断面図である。この段階は図4の処理工程408に対応し、レジスト成膜装置およびリソグラフィ装置により実現される。

[0081]

図3(h)はフォトレジストマスク50を用いたドライエッチング法によりSiN膜48及び絶縁膜49にヴィア形状51を形成し、アッシング及び洗浄によりヴィア形状形成用フォトレジストマスク50を除去した直後の工程断面図である。この段階は図4の処理工程409に対応し、ドライエッチング装置,アッシング装置および洗浄装置により実現される。

[0082]

図3(i)はリソグラフィ法により絶縁膜49上に第2配線溝形成用フォトレジストマスク52を形成した直後の工程断面図である。フォトレジストマスク52はヴィア形状51を含む領域に開口を有している。この段階は図4の処理工程410に対応し、レジスト成膜装置およびリソグラフィ装置により実現される。

[0083]

図 3 ( j )はフォトレジストマスク 5 2 を用いたドライエッチング法により絶縁膜 4 9 の表面の一部に第 2 配線溝 5 3 を形成し、アッシング及び洗浄により第 2 配線溝形成用フォトレジストマスク 5 2 を除去した直後の工程断面図である。この段階は図 4 の処理工程 4 1 1 に対応し、ドライエッチング装置,アッシング装置および洗浄装置により実現される

[0084]

図3(k)はドライエッチング法によりSiN膜48をエッチングし、洗浄した直後の工程断面図である。この段階は図4の処理工程412に対応し、ドライエッチング装置および洗浄装置により実現される。

[ 0 0 8 5 ]

図3(1)はスパッタリング法及びメッキ法によりヴィア形状51内および第1配線45の露出した表面および第2配線溝53内を含む絶縁膜49上全面に第2の銅膜54を形成した直後の工程断面図である。この段階は図4の処理工程413に対応し、スパッタリング装置およびメッキ装置により実現される。

[0086]

図3(m)はCMP法により銅膜54及び絶縁膜49を研磨、平坦化し、洗浄し、ヴィア形状51内を銅膜により充填したヴィア55と、絶縁膜49と表面が同一の第2配線56とを形成した直後の工程断面図である。この段階は図3の処理工程414に対応し、CMP装置および洗浄装置により実現される。

20

10

30

40

30

50

### [0087]

次に、本実施の形態2において、半導体製造装置により実行される、半導体装置の製造方法について説明する。

図3(a)ないし図3(c)は半導体基板41上の絶縁膜42の表面の一部に形成された配線溝43に埋め込まれた第1配線45を形成する工程である。

#### [0088]

これは従来の図8(a)ないし図8(c)と同様、半導体基板41上に絶縁膜42を形成し、絶縁膜42の表面に第1配線溝43を形成し、スパッタリング法及びメッキ法により第1配線溝43内を含む絶縁膜42の表面全面に銅膜44を形成し、CMP法により銅膜44及び絶縁膜42を研磨、平坦化し、洗浄し、絶縁膜42と表面が同一となるように第1配線45を形成する、というものである。

#### [0089]

図3(c)の工程断面図に示された半導体基板に対して酸素雰囲気中、80°C程度の基 板温度、120秒程度のプラズマ処理を行うと、銅ヒロック46及び酸化銅層47が第1 配 線 4 5 上に発生する(図 3 ( d )参照)。これは第 1 配 線 4 5 が熱的なストレスを与え ら れ る こ と に よ り 、 銅 原 子 が 移 動 し 、 銅 の グ レ イ ン 成 長 が 促 進 さ れ る こ と と 、 酸 素 ラ ジ カ ルと銅原子の反応により酸化銅が生成されることに起因する。銅ヒロックはランダムに発 生し、その高さは50~100nm程度である。酸化銅層は本実施の形態2の酸素プラズ マ処理では30nm以下である。本実施の形態2では酸素プラズマ処理時の基板温度を8 0 ° C に 設 定 し た が 、 銅 ヒ ロ ッ ク の 発 生 状 況 か ら 勘 案 す る と プ ラ ズ マ 照 射 に よ る 温 度 上 昇 により第1配線45は80°C以上に上昇していることが考えられる。第1配線45の配 線膜厚は 3 5 0 n m 程度に設定している。その後、CMP法により銅ヒロック 4 6 及び酸 化銅層47を研磨し、洗浄し、第1配線45を平坦化する。この状態では第1配線に再度 熱 処 理 を 加 え て も 、 銅 原 子 は 移 動 す る こ と が 無 い 。 す な わ ち 銅 の グ レ イ ン 成 長 は 飽 和 状 態 にある。従って、第1配線45は銅ヒロックの存在しない図3(e)の状態になる。次に 、 図 3 ( f )のように C V D 法により S i N 膜 4 8 及び絶縁膜 4 9 を形成する。この C V D 法による S i N 膜 4 8 及び絶縁膜 4 9 の形成時には最高到達温度が 4 0 0 ° C 程度まで 半導体基板 4 1 の温度が上昇する。従来例ではこの熱ストレスが図 8 ( c ) に示す第 1 配 線5に与えられると、銅原子が移動し銅のグレイン成長が促進され、図8(d)に示すよ うな銅ヒロック8がSiN膜6へと侵入してしまう。しかしながら、本実施の形態2では 、 こ の 熱 ス ト レ ス が 図 3 ( e ) に 示 す 第 1 配 線 4 5 に 与 え ら れ た と し て も 、 銅 原 子 が 移 動 することは無く、銅のグレイン成長が促進されず、もはや銅ヒロックは発生しない。この ため、SiN膜48は所望の均一な膜厚を有することができ、図3(f)のようになる。

## [0090]

SiN膜48の膜厚は配線間容量を低減させるために可能な限り薄膜化することが望まれ て い る が 、 そ の 後 の ヴ ィ ア 形 成 や 第 2 配 線 溝 形 成 の た め の ド ラ イ エ ッ チ ン グ 工 程 や ア ッ シ ン グ や 洗 浄 で 第 1 配 線 が 露 出 し な い よ う な 膜 厚 に 設 定 す る こ と が 重 要 で あ る 。 本 実 施 の 形 態 2 ではSiN膜 4 8の膜厚を150nmと設定した。また、絶縁膜49の膜厚を800 n m とした。従来例の図 8 ( e )に示すような S i N 膜 6 の膜厚が不均一な状態でヴィア 形 状 1 0 形 成 や 第 2 配 線 溝 1 3 形 成 の た め の ド ラ イ エ ッ チ ン グ を 施 す と 、 S i N 膜 6 が 部 分的に破れ、レジストマスク除去時のアッシングや洗浄、リソグラフィ時の現像液などに より、 第 1 配 線 5 に 物 理 的 、 化 学 的 な ダ メ ー ジ が 複 数 回 与 え ら れ 、 ボ イ ド 1 2 や 侵 食 部 1 4 を発生させてしまう。しかしながら、本実施の形態 2 では、図 3 ( h )に示すヴィア形 状 5 1 は S i N 膜 4 8 中まで到達しているが、 S i N 膜 4 8 を貫通することはなく、第 1 配線45が露出することは無い。SiN膜48のエッチング量はヴィア形状51形成のた めのドライエッチング時のオーバーエッチング量によって決まるが、フロロカーボン系の ガスを用い、絶縁膜に対するSiN膜選択比を十分に確保した条件を用い、40nm程度 のエッチング量に抑制している。また本実施の形態2の図3(j)に示す第2配線溝53 形 成 後 の ヴィ ア 形 状 5 1 の 底 部 は S i N 膜 4 8 中 ま で 到 達 し て い る が 、 第 1 配 線 4 5 が 露 出することは無い。SiN膜48のエッチング量は第2配線溝53形成のためのドライエ

20

30

40

50

ッチング量と、絶縁膜に対するSiN膜選択比から決まるが、フロロカーボン系のガスを用い、絶縁膜に対するSiN膜選択比を確保した条件を用い、80nm程度のエッチング量に抑制している。第2配線溝53形成後のヴィア形状51の底部のSiN膜48は合計120nm程度エッチングされ、30nmが残るように設計されている。そして、図3(k)に示すようにフロロカーボン系のガスを用いたドライエッチング法により、ヴィア形状51底部のSiN膜48をエッチングすることにより、初めて第1配線45が露出する。その後、洗浄を施し、図3(1)に示すようにスパッタリング法及びメッキ法を用いて銅膜54を形成する。この間、第1配線45へのダメージは従来例に比べて最小限に抑えることができる。その後、図3(m)に示すようにCMP法により銅膜54を研磨、平坦化し、洗浄し、ヴィア55及び第2配線56を形成する。

[0091]

これにより、第1配線45及びヴィア55及び第2配線56はボイドや侵食の無い配線となり、ヴィア抵抗の安定化や配線の信頼性を確保することができる。

[0092]

このように、本実施の形態 2 によれば、第 1 の銅配線を絶縁膜と表面が同一となるように埋め込んで形成した後、意図的に酸素プラズマ処理を行うことで銅ヒロックを発生させ、この銅ヒロックを C M P 法により、研磨し平坦化した後に、デュアルダマシン法により、第 1 ,第 2 の銅配線を互いに接続するヴィアと第 2 の銅配線とを形成するようにしたので、デュアルダマシン法を実施する際に第 1 の銅配線にヒロックが発生することはもはや無く、デュアルダマシン法を実施する際に形成する S i N 層に銅ヒロックが侵入し、一部でSiN層が薄膜化するために、第 1 の銅配線の一部が露出し、ヴィア形状形成時のドライエッチングで意図しないダメージを受け、第 1 の銅配線に侵食部が生じてしまう、というおそれがなくなり、ヴィア抵抗の異常や断線などの信頼性不良が発生する不具合をなくすことができる。

[0093]

(実施の形態3)

この実施の形態 3 は、請求項 1 , 2 , 8 , 9 の発明に対応するもので、第 1 配線を形成後、アンモニアプラズマ処理によりこの第 1 配線に意図的にヒロックを発生させ、これを C M P 法で除去した後、デュアルダマシン法を行うようにしたもので、意図的にヒロックを発生させたためにヒロック除去後の工程で第 1 配線にヒロックが発生することがなく、第 1 配線へのダメージを最小限に抑えることが可能となり、第 1 配線の侵食を防ぐことが可能となり、ヴィア抵抗の安定化や配線の信頼性を確保することができるようにしたものである。

[0094]

以下、本発明の実施の形態3における半導体装置の製造方法について、図面を参照しながら説明する。

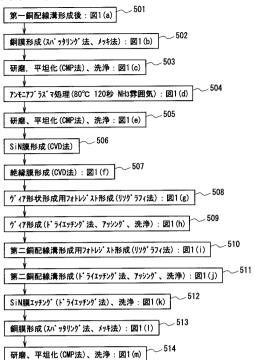

図1は本発明の実施の形態3による半導体装置の製造方法の工程断面図を示す。

[0095]

図5は本発明の実施の形態3による半導体装置の製造方法の工程フローチャートであり、図1の工程断面図の(a)ないし(m)の工程に対応する処理工程501ないし514を示している。

[0096]

実施の形態1で述べたように、図1において、21は半導体基板、22は半導体基板21上に形成された絶縁膜、23は絶縁膜22の表面に形成された第1配線溝、24は第1配線溝23内を含む絶縁膜22の表面を覆うように形成された銅膜、25は第1配線溝23内に形成された第1配線、26は第1配線25の表面に発生した銅ヒロック、27は第1配線25上を含む絶縁膜22上に形成されたSiN膜、28はSiN膜27上に形成されため線膜、29は絶縁膜27上に形成されたヴィア形状形成用フォトレジストマスク、30はSiN膜27及び絶縁膜28に形成されたヴィア形状、31は絶縁膜28上に形成された第2配線溝形成用フォトレジストマスク、32は絶縁膜28の表面に形成された第2

配線溝、33はヴィア形状30底面の第1配線25の露出部を覆うとともにヴィア形状30内を充填するように絶縁膜28上に形成された銅膜、34は絶縁膜28内に形成されたヴィア、35は絶縁膜28の第2配線溝32内に形成された第2配線である。

[0097]

以下では図1の各工程断面図について説明する。

図1(a)は半導体基板21上に絶縁膜22を形成し、絶縁膜22の表面に第1配線溝23を形成した直後の工程断面図である。この段階は図5の処理工程501に対応し、成膜装置およびエッチング装置により実現される。

[0098]

図1(b)はスパッタリング法及びメッキ法により第1配線溝23内を含む絶縁膜22の表面全面に銅膜24を形成した直後の工程断面図である。この段階は図5の処理工程502に対応し、スパッタリング装置およびメッキ装置により実現される。

[0099]

図1(c)はCMP法により銅膜24及び絶縁膜22を研磨、平坦化し、洗浄し、絶縁膜22と表面が同一となるように第1配線25を形成した直後の工程断面図である。この段階は図5の処理工程503に対応し、CMP装置および洗浄装置により実現される。

[ 0 1 0 0 ]

図 1 ( d ) はアンモニアプラズマ処理により第 1 配線 2 5 上に銅ヒロック 2 6 を意図的に発生させた直後の工程断面図である。この段階は図 5 の処理工程 5 0 4 に対応し、プラズマ処理装置により実現される。

[ 0 1 0 1 ]

図 1 ( e )は C M P 法により銅ヒロック 2 6 を研磨、平坦化し、洗浄した直後の工程断面図である。この段階は図 5 の処理工程 5 0 5 に対応し、 C M P 装置および洗浄装置により実現される。

[0102]

図1(f)はCVD法により第1配線25上を含む絶縁膜22上全面にSiN膜27及び 絶縁膜28をこの順で形成した直後の工程断面図である。この段階は図5の処理工程50 6および507に対応し、成膜装置により実現される。

[0103]

図 1 (g)はリソグラフィ法により絶縁膜 2 8 上にヴィア形状形成用フォトレジストマスク 2 9 を形成した直後の工程断面図である。この段階は図 5 の処理工程 5 0 8 に対応し、レジスト成膜装置およびリソグラフィ装置により実現される。

[0104]

図 1 ( h ) はフォトレジストマスク 2 9 を用いたドライエッチング法により S i N 膜 2 7 及び絶縁膜 2 8 にヴィア形状 3 0 を形成し、アッシング及び洗浄によりヴィア形状形成用フォトレジストマスク 2 9 を除去した直後の工程断面図である。この段階は図 5 の処理工程 5 0 9 に対応し、ドライエッチング装置,アッシング装置および洗浄装置により実現される。

[0105]

図 1 ( i ) はリソグラフィ法により絶縁膜 2 8 上に第 2 配線溝形成用フォトレジストマスク 3 1 を形成した直後の工程断面図である。フォトレジストマスク 3 1 はヴィア形状 3 0 を含む領域に開口を有している。この段階は図 5 の処理工程 5 1 0 に対応し、レジスト成膜装置およびリソグラフィ装置により実現される。

[0106]

図 1 ( j ) はフォトレジストマスク 3 1 を用いたドライエッチング法により絶縁膜 2 8 中の表面の一部に第 2 配線溝 3 2 を形成し、アッシング及び洗浄により第 2 配線溝形成用フォトレジストマスク 3 1 を除去した直後の工程断面図である。この段階は図 5 の処理工程 5 1 1 に対応し、ドライエッチング装置,アッシング装置および洗浄装置により実現される。

[0107]

50

40

20

30

40

50

図 1 ( k ) はドライエッチング法によりSiN膜27をエッチングし、洗浄した直後の工程断面図である。この段階は図5の処理工程512に対応し、ドライエッチング装置および洗浄装置により実現される。

[0108]

図1(1)はスパッタリング法及びメッキ法によりヴィア形状30内および第1配線25の露出した表面および第2配線溝32内を含む絶縁膜28上全面に第2の銅膜33を形成した直後の工程断面図である。この段階は図5の処理工程513に対応し、スパッタリング装置およびメッキ装置により実現される。

[0109]

図1(m)はCMP法により銅膜33及び絶縁膜28を研磨、平坦化し、洗浄し、ヴィア形状30内を銅膜により充填したヴィア34と、絶縁膜28と表面が同一の第2配線35とを形成した直後の工程断面図である。この段階は図5の処理工程514に対応し、CMP装置および洗浄装置により実現される。

[ 0 1 1 0 ]

次に、本実施の形態3において、半導体製造装置により実行される、半導体装置の製造方法について説明する。

図1(a)ないし図1(c)は半導体基板21上の絶縁膜22の表面の一部に形成された配線溝23に埋め込まれた第1配線25を形成する工程である。

[0111]

これは従来の図8(a)ないし図8(c)と同様、半導体基板21上に絶縁膜22を形成し、絶縁膜22の表面に第1配線溝23を形成し、スパッタリング法及びメッキ法により第1配線溝23内を含む絶縁膜22の表面全面に銅膜24を形成し、CMP法により銅膜24及び絶縁膜22を研磨、平坦化し、洗浄し、絶縁膜22と表面が同一となるように第1配線25を形成する、というものである。

[0112]

図1(c)の工程断面図に示された半導体基板に対してアンモニア雰囲気中、80°C程 度の基板温度、 1 2 0 秒程度のプラズマ処理を行うと、銅ヒロック 2 6 が第 1 配線 2 5 上 に発生する(図1(d)参照)。これは第1配線25が熱的なストレスを与えられること により、銅原子が移動し、銅のグレイン成長が促進されることに起因すると考えられる。 銅ヒロックはランダムに発生し、その高さは50~100nm程度である。第1配線25 の 配 線 膜 厚 は 3 5 0 n m 程 度 に 設 定 し て い る 。 プ ラ ズ マ 処 理 時 の 雰 囲 気 と し て ア ン モ ニ ア を 用 い た の は プ ラ ズ マ 中 で 分 解 し た 水 素 原 子 に よ る 還 元 雰 囲 気 の 中 で 、 銅 ヒ ロ ッ ク を 意 図 的に発生させることを目的としている。その後、CMP法により銅ヒロック26を研磨し 洗浄し、第1配線25を平坦化する。この状態では第1配線に再度熱処理を加えても、 銅原子が移動することは無い。すなわち銅のグレイン成長は飽和状態にある。従って、第 1 配線 2 5 は銅ヒロックの存在しない図 1 ( e ) の状態になる。次に、図 1 ( f ) のよう に C V D 法により S i N 膜 2 7 及び絶縁膜 2 8 を形成する。この C V D 法による S i N 膜 27及び絶縁膜28の形成時には最高到達温度が400°C程度まで半導体基板21の温 度が上昇する。従来例ではこの熱ストレスが図 8 ( c )に示す第 1 配線 5 に与えられると 、 銅 原 子 が 移 動 し 銅 の グ レ イ ン 成 長 が 促 進 さ れ 図 8 ( d ) に 示 す よ う な 銅 ヒ ロ ッ ク 8 が S iN膜6へと侵入してしまう。しかしながら、本実施の形態3では、この熱ストレスが図 1(e)に示す第1配線25に与えられたとしても、銅原子が移動することは無く、銅の グレイン成長が促進されず、もはや銅ヒロックは発生しない。このため、SiN膜27は 所望の均一な膜厚を有することができ、図1(f)のようになる。

[0113]

SiN膜 2 7 の膜厚は配線間容量を低減させるために可能な限り薄膜化することが望まれているが、その後のヴィア形成や第 2 配線溝形成のためのドライエッチング工程やアッシング工程や洗浄工程で第 1 配線が露出しないような膜厚に設定することが重要である。本実施の形態 3 ではSiN膜 2 7 の膜厚を 1 5 0 n m と設定した。また、絶縁膜 2 8 の膜厚を 8 0 0 n m とした。従来例の図 8 ( e )に示すようなSiN膜 6 の膜厚が不均一な状態

30

40

50

でヴィア形状10形成や第2配線溝13形成のためのドライエッチングを施すと、SiN 膜 6 が 部 分 的 に 破 れ 、 レ ジ ス ト マ ス ク 除 去 時 の ア ッ シ ン グ や 洗 浄 、 リ ソ グ ラ フ ィ 時 の 現 像 液などにより、第1配線5に物理的、化学的なダメージが複数回与えられ、ボイド12や 侵食部14を発生させてしまう。しかしながら、本実施の形態3では、図1(h)に示す ヴィア形状30はSiN膜27中まで到達しているが、SiN膜27を貫通することはな く、 第 1 配 線 2 5 が 露 出 す る こ と は 無 い 。 S i N 膜 2 7 の エ ッ チ ン グ 量 は ヴ ィ ア 形 状 3 0 形成のためのドライエッチング時のオーバーエッチング量によって決まるが、フロロカー ボン系のガスを用い、絶縁膜に対するSiN膜選択比を十分に確保した条件を用い、40 n m 程 度 の エ ッ チ ン グ 量 に 抑 制 し て い る 。 ま た 本 実 施 の 形 態 3 の 図 1 ( i )に 示 す 第 2 配 線 溝 3 2 形 成 後 の ヴィ ア 形 状 3 0 の 底 部 は S i N 膜 2 7 中 ま で 到 達 し て い る が 、 第 1 配 線 25が露出することは無い。SiN膜27のエッチング量は第2配線溝32形成のための ドライエッチング量と、絶縁膜に対するSiN膜選択比から決まるが、フロロカーボン系 のガスを用い、絶縁膜に対するSiN膜選択比を確保した条件を用い、80nm程度のエ ッチング量に抑制している。 第 2 配線溝 3 2 形成後のヴィア形状 3 0 の底部の S i N 膜 2 7 は合計120nm程度がエッチングされ、30nmが残るように設計されている。そし て、図1(k)に示すようにフロロカーボン系のガスを用いたドライエッチング法により . ヴィア形状30底部のSiN膜27をエッチングすることにより、初めて第1配線25 が露出する。その後、洗浄を施し、図1(1)に示すようにスパッタリング法及びメッキ 法を用いて銅膜33を形成する。この間、第1配線25へのダメージは従来例に比べて最 小限に抑えることができる。その後、図1(m)に示すようにCMP法により銅膜33を 研磨、平坦化し、洗浄し、ヴィア34及び第2配線35を形成する。

[0114]

これにより、第1配線25及びヴィア34及び第2配線35はボイドや侵食の無い配線となり、ヴィア抵抗の安定化や配線の信頼性を確保することができる。

[ 0 1 1 5 ]

このように、本実施の形態 3 によれば、第 1 の銅配線を絶縁膜と表面が同一となるように埋め込んで形成した後、意図的にアンモニアプラズマ処理を行うことで銅ヒロックを発生させ、この銅ヒロックを C M P 法により、研磨し平坦化した後に、デュアルダマシン法により、第 1 ,第 2 の銅配線を互いに接続するヴィアと第 2 の銅配線とを形成するようにしたので、デュアルダマシン法を実施する際に第 1 の銅配線にヒロックが発生することはもはや無く、デュアルダマシン法を実施する際に形成する S i N 層に銅ヒロックが侵入し、一部で S i N 層が薄膜化するために、第 1 の銅配線の一部が露出し、ヴィア形状形成時のドライエッチングで意図しないダメージを受け、第 1 の銅配線に侵食部が生じてしまう、というおそれがなくなり、ヴィア抵抗の異常や断線などの信頼性不良が発生する不具合をなくすことができる。

[0116]

(実施の形態4)

この実施の形態 4 は、請求項 1 0 , 1 1 の発明に対応するもので、第 1 配線を形成後、バリア層として S i C 膜を第 1 配線上全面に形成し、その後デュアルダマシン法を行うようにしたもので、バリア層の材質を硬質なものに変更したために、その後の工程で第 1 配線にヒロックが発生することがなく、第 1 配線へのダメージを最小限に抑えることが可能となり、第 1 配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができるようにしたものである。

[0117]

以下、本発明の実施の形態 4 による半導体装置の製造方法について、図面を参照しながら 説明する。

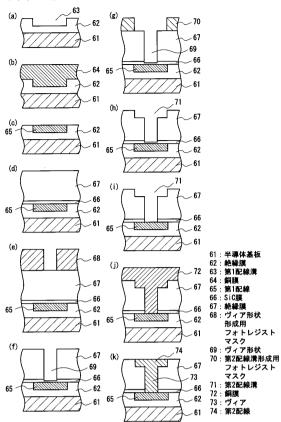

図6は本発明の実施の形態4における半導体装置の製造方法の工程断面図を示す。

[0118]

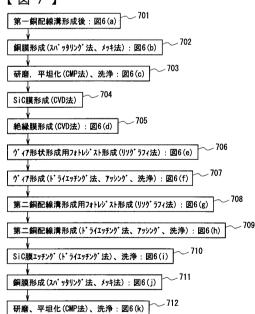

図 7 は本発明の実施の形態 4 における半導体装置の製造方法の工程フローチャートであり、図 6 の工程断面図の(a)ないし(k)の工程に対応する処理工程 7 0 1 ないし 7 1 2

30

40

50

(20)

を示す。

[0119]

図6において、61は半導体基板、62は半導体基板61上に形成された絶縁膜、63は絶縁膜62の表面に形成された第1配線溝、64は第1配線溝63内を含む絶縁膜62の表面を覆うように形成された銅膜、65は第1配線溝63内に形成された第1配線、66は第1配線65上を含む絶縁膜62上に形成されたSiN膜、67はSiN膜66上に形成された絶縁膜、68は絶縁膜67上に形成されたヴィア形状形成用フォトレジストマスク、69はSiN膜66及び絶縁膜67に形成されたヴィア形状、70は絶縁膜67上に形成された第2配線溝形成用フォトレジストマスク、71は絶縁膜67の表面に形成された第2配線溝、72はヴィア形状69底面の第1配線65の露出部を覆うとともにヴィア形状69内を充填するように絶縁膜67上に形成された銅膜、73は絶縁膜67内に形成されたヴィア、74は絶縁膜67の第2配線溝71内に形成された第2配線である。

[ 0 1 2 0 ]

以下では図6の各工程断面図について説明する。

図 6 ( a ) は半導体基板 6 1 上に絶縁膜 6 2 を形成し、絶縁膜 6 2 の表面に第 1 配線溝 6 3 を形成した直後の工程断面図である。この段階は図 7 の処理工程 7 0 1 に対応し、成膜装置およびエッチング装置により実現される。

[0121]

図 6 ( b ) はスパッタリング法及びメッキ法により第 1 配線溝 6 3 内を含む絶縁膜 6 2 の表面全面に銅膜 6 4 を形成した直後の工程断面図である。この段階は図 7 の処理工程 7 0 2 に対応し、スパッタリング装置およびメッキ装置により実現される。

[ 0 1 2 2 ]

図6(c)はCMP法により銅膜64及び絶縁膜62を研磨、平坦化し、洗浄し、絶縁膜62と表面が同一となるように第1配線65を形成した直後の工程断面図である。この段階は図7の処理工程703に対応し、CMP装置および洗浄装置により実現される。

[0123]

図 6 ( d )は C V D 法により S i C 膜 6 6 及び絶縁膜 6 7 を形成した直後の工程断面図である。この段階は図 7 の処理工程 7 0 4 および 7 0 5 に対応し、成膜装置により実現される。

[ 0 1 2 4 ]

図6(e)はリソグラフィ法により絶縁膜67上にヴィア形状形成用フォトレジストマスク68を形成した直後の工程断面図である。この段階は図7の処理工程706に対応し、レジスト成膜装置およびリソグラフィ装置により実現される。

[0125]

図 6 ( f ) はドライエッチング法によりSiC膜66及び絶縁膜67中にヴィア形状69を形成し、アッシング及び洗浄によりヴィア形状形成用フォトレジストマスク68を除去した直後の工程断面図である。この段階は図7の処理工程707に対応し、ドライエッチング装置,アッシング装置および洗浄装置により実現される。

[0126]

図 6 (g)はリソグラフィ法により絶縁膜 6 7 上に第 2 配線溝形成用フォトレジストマスク 7 0 を形成した直後の工程断面図である。フォトレジストマスク 7 0 はヴィア形状 6 9 を含む領域に開口を有している。この段階は図 7 の処理工程 7 0 8 に対応し、レジスト成膜装置およびリソグラフィ装置により実現される。

[0127]

図 6 ( h ) はドライエッチング法により絶縁膜 6 7 の表面の一部に第 2 配線溝 7 1 を形成し、アッシング及び洗浄により第 2 配線溝形成用フォトレジストマスク 7 0 を除去した直後の工程断面図である。この段階は図 7 の処理工程 7 0 9 に対応すし、ドライエッチング装置 , アッシング装置および洗浄装置により実現される。

[0128]

図6(i)はドライエッチング法によりSiC膜66をエッチングし、洗浄した直後のエ

20

30

50

程断面図である。この段階は図7の処理工程710に対応し、ドライエッチング装置および洗浄装置により実現される。

### [0129]

図 6 ( j ) はスパッタリング法及びメッキ法によりヴィア形状 6 9 内および第 1 配線 6 5 の露出した表面および第 2 配線溝 7 1 内を含む絶縁膜 6 7 上全面に第 2 の銅膜 7 2 を形成した直後の工程断面図である。この段階は図 7 の処理工程 7 1 1 に対応し、スパッタリング装置およびメッキ装置により実現される。

## [0130]

図 6 ( k ) は C M P 法により 銅膜 7 2 及び絶縁膜 6 7 を研磨、平坦化し、洗浄し、ヴィア 7 3 と第 2 配線 7 4 を形成した直後の工程断面図である。この段階は図 7 の処理工程 7 1 2 に対応し、 C M P 装置および洗浄装置により実現される。

#### [ 0 1 3 1 ]

次に、本実施の形態4において、半導体製造装置により実行される、半導体装置の製造方法について説明する。

図 6 ( a ) ないし図 6 ( c ) は半導体基板 6 1 上の絶縁膜 6 2 の表面の一部に形成された 配線溝 6 3 に埋め込まれた第 1 配線 6 5 を形成する工程である。

## [0132]

これは従来の図8(a)ないし図8(c)と同様、半導体基板61上に絶縁膜62を形成し、絶縁膜62の表面に第1配線溝63を形成し、スパッタリング法及びメッキ法により第1配線溝63内を含む絶縁膜62の表面全面に銅膜64を形成し、CMP法により銅膜64及び絶縁膜62を研磨、平坦化し、洗浄し、絶縁膜62と表面が同一となるように第1配線65を形成する、というものである。

## [0133]

図6(c)の工程断面図に示された半導体基板に対してCVD法によりSiC膜66及び絶縁膜67を形成する(図6(d)参照)。このCVD法によるSiC膜66及び絶縁膜67の形成時には最高到達温度が400°C程度まで半導体基板61の温度が上昇する。従来例ではこの熱ストレスが図8(c)に示す第1配線5に与えられると、銅原子が移動し銅のグレイン成長が促進され、図8(d)に示すような銅ヒロック8がSiN膜6へと侵入してしまう。しかしながら、本実施の形態4では、この熱ストレスが図6(c)に示す第1配線65に与えられたとしても、SiC膜66自体の硬度が高いために銅原子が移動することは無く、銅のグレイン成長が促進されず、銅ヒロックは発生しない。このため、SiC膜66は所望の均一な膜厚を有することができ、図6(d)のようになる。

### [0134]

SiC膜66の膜厚は配線間容量を低減させるために可能な限り薄膜化することが望まれ ているが、その後のヴィア形成や第2配線溝形成のためのドライエッチング工程やアッシ ン グ 工 程 や 洗 浄 工 程 で 第 1 配 線 が 露 出 し な い よ う な 膜 厚 に 設 定 す る こ と が 重 要 で あ る 。 本 実 施 の 形 態 4 で は S i C 膜 6 6 の 膜 厚 を 1 5 0 n m と 設 定 し た 。 ま た 、 絶 縁 膜 6 7 の 膜 厚 を800nmとした。従来例の図8(e)に示すようなSiN膜6の膜厚が不均一な状態 でヴィア形状10形成や第2配線溝13形成のためのドライエッチングを施すと、SiN 膜 6 が 部 分 的 に 破 れ 、 レ ジ ス ト マ ス ク 除 去 時 の ア ッ シ ン グ や 洗 浄 、 リ ソ グ ラ フ ィ 時 の 現 像 液などにより、第1配線5に物理的、化学的なダメージが複数回与えられ、ボイド12や 侵食部14を発生させてしまう。しかしながら、本実施の形態4では、図6(f)に示す ヴィア形状69はSiC膜66中まで到達しているが、SiC膜66を貫通することはな く、 第 1 配 線 6 5 が 露 出 す る こ と は 無 い 。 S i C 膜 6 6 の エ ッ チ ン グ 量 は ヴ ィ ア 形 状 6 9 形成のためのドライエッチング時のオーバーエッチング量によって決まるが、フロロカー ボン系のガスを用い、絶縁膜に対するSiC膜選択比を十分に確保した条件を用い、40 n m 程 度 の エ ッ チ ン グ 量 に 抑 制 し て い る 。 ま た 本 実 施 の 形 態 4 の 図 6 ( h ) に 示 す 第 2 配 線 溝 7 1 形 成 後 の ヴィ ア 形 状 6 9 の 底 部 は S i C 膜 6 6 中 ま で 到 達 し て い る が 、 第 1 配 線 6 5 が露出することは無い。 S i C 膜 6 6 のエッチング量は第 2 配線溝 7 1 形成のための ドライエッチング量と、絶縁膜に対するSiC膜選択比から決まるが、フロロカーボン系

20

30

50

のガスを用い、絶縁膜に対するSiC膜選択比を確保した条件を用い、80nm程度のエッチング量に抑制している。第2配線溝71形成後のヴィア形状69の底部のSiC膜66は合計120nm程度エッチングされ、30nm残るように設計されている。そして、図6(i)に示すようにフロロカーボン系のガスを用いたドライエッチング法により、ヴィア形状69底部のSiC膜66をエッチングすることにより、初めて第1配線65が露出する。その後、洗浄を施し、図6(j)に示すようにスパッタリング法及びメッキ法を用いて銅膜72を形成する。この間、第1配線65へのダメージは従来例に比べて最小限に抑えることができる。その後、図6(k)に示すようにCMP法により銅膜72を研磨、平坦化し、洗浄し、ヴィア73及び第2配線74を形成する。

## [ 0 1 3 5 ]

これにより、第1配線65及びヴィア73及び第2配線74はボイドや侵食の無い配線となり、ヴィア抵抗の安定化や配線の信頼性を確保することができる。

### [0136]

このように、本実施の形態4によれば、第1の銅配線を絶縁膜と表面が同一となるように埋め込んで形成した後、バリア層としてSiN膜よりも硬質なSiC膜を第1配線上に形成し、その後デュアルダマシン法により、第1,第2の銅配線を互いに接続するヴィアと第2の銅配線とを形成するようにしたので、デュアルダマシン法を実施する際に第1の銅配線にヒロックが発生することはもはや無く、バリア層としてSiN膜を形成する場合の問題である、デュアルダマシン法を実施する際に形成するSiN層に銅ヒロックが侵入し、一部でSiN層が薄膜化するために、第1の銅配線の一部が露出し、ヴィア形状形成時のドライエッチングで意図しないダメージを受け、第1の銅配線に侵食部が生じてしまう、というおそれがなくなり、ヴィア抵抗の異常や断線などの信頼性不良が発生する不具合をなくすことができる。

### [0137]

なお、本件の特許請求の範囲に示された発明は上記各実施の形態で説明した態様に限られるものではない。

例えば、第 1 配線はその形成後にデュアルダマシン法を実行する際にヒロックが生じ、これが原因となって自身に浸食部が生じるものであれば、銅以外の配線材料で形成するものであってもよい。また、第 1 配線はダマシン法以外の方法で形成するものであってもよい

## [0138]

## 【発明の効果】

以上のように、本発明の請求項1に係る半導体装置の製造方法によれば、半導体基板上に第1の配線を形成する工程と、該第1の配線にヒロックを発生させる処理を行うヒロック発生工程と、該ヒロック発生工程により発生したヒロックを研磨により除去し、前記第1の配線の表面を平坦化する処理と、前記第1の配線上を含む前記半導体基板上に絶縁膜を形成し、該絶縁膜に前記第1の配線が露出するようにヴィア形状を形成し、該ヴィア形状の内部に配線材料膜を埋め込むようにしたので、意図的に発生させたヒロックを研磨除状の内部に配線材料膜を形成する場合にヒロックが発生することはなく、バリヤ層や絶縁膜を形成する場合にヒロックが発生することはなく、バリヤ層は均一な膜厚に形成することができる。このため、その後の工程でバリヤ層が意図せぬ破れを起こすことが無く、第1配線へのダメージを最小限に抑えることが可能となり、第1配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置の製造方法が得られる効果がある。

# [0139]

また、本発明の請求項2に係る半導体装置の製造方法によれば、半導体基板上に形成した第1の絶縁膜に、該絶縁膜と表面が同一になるように埋め込まれた第1の配線を形成する工程と、該第1の配線にヒロックを発生させる処理を行うヒロック発生工程と、該ヒロック発生工程により発生したヒロックを研磨により除去し、前記第1の配線の表面を平坦化する工程と、前記第1の配線上を含む前記半導体基板上に第2の絶縁膜を形成し、該第2の絶縁膜に前記第1の配線が露出するようにヴィア形状を形成し、該ヴィア形状の内部に

20

30

40

50

配線材料膜を埋め込み、研磨により不要な配線材料膜を除去してヴィアおよび第2の配線を形成する工程とを含むようにしたので、意図的に発生させたヒロックを研磨除去した後に、バリヤ層や絶縁膜を形成する場合にヒロックが発生することはなく、バリヤ層は均一な膜厚に形成することができる。このため、その後の工程でバリヤ層が意図せぬ破れを起こすことが無く、第1配線へのダメージを最小限に抑えることが可能となり、第1配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置の製造方法が得られる効果がある。

## [0140]

ま た 、 本 発 明 の 請 求 項 3 に 係 る 半 導 体 装 置 の 製 造 方 法 に よ れ ば 、 半 導 体 基 板 上 の 第 1 の 絶 縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝の内部を 含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、平坦化して第1の 配 線 を 形 成 す る 工 程 と 、 該 第 1 の 配 線 が 形 成 さ れ た 半 導 体 基 板 に 対 し ア ニ ー ル を 行 う ア ニ ールエ程と、該アニールにより前記第1の配線上に発生したヒロックを研磨し、平坦化す る工程と、該平坦化された前記第 1 の配線上に S i N 膜を形成する工程と、該 S i N 膜上 に 第 2 の 絶 縁 膜 を 形 成 す る 工 程 と 、 該 第 2 の 絶 縁 膜 に 対 し ヴィ ア 形 状 形 成 用 フ ォ ト レ ジ ス トマスクを用いて前記第 1 の配線に相当する位置にヴィア形状を形成する工程と、前記第 2 の 絶 縁 膜 に 対 し 配 線 溝 形 成 用 フォト レ ジ スト マ ス ク を 用 い て 前 記 ヴィ ア 形 状 の 上 部 を 含 む 第 2 の 配 線 溝 を 形 成 す る 工 程 と 、 前 記 ヴ ィ ア 形 状 底 部 の S i N 膜 を 除 去 す る 工 程 と 、 前 記 ヴィ ア 形 状 の 内 部 お よ び 前 記 第 2 の 配 線 溝 の 内 部 を 含 む 前 記 第 2 の 絶 縁 膜 上 に 第 2 の 銅 膜 を 形 成 す る 工 程 と 、 該 第 2 の 銅 膜 を 研 磨 、 平 坦 化 し ヴ ィ ア と 第 2 の 配 線 と を 形 成 す る 工 程とを含むようにしたので、アニール工程により意図的に銅ヒロックを発生させた後のS i N 膜 や 絶 縁 膜 を 形 成 す る 工 程 で 銅 ヒ ロ ッ ク が 発 生 す る こ と が な く 、 S i N 膜 は 均 一 な 膜 厚に形成することができる。このため、その後の工程でSiN膜が意図せぬ破れを起こす ことが無く、第1の配線へのダメージを最小限に抑えることが可能となり、第1の配線の 侵 食 を 防 ぐ こ と が で き 、 ヴ ィ ア 抵 抗 の 安 定 化 や 配 線 の 信 頼 性 を 確 保 す る こ と が で き る 半 導 体装置の製造方法が得られる効果がある。

## [ 0 1 4 1 ]

また、本発明の請求項4に係る半導体装置の製造方法によれば、請求項3記載の半導体装置の製造方法において、前記アニール工程は、酸素を抑制した雰囲気で前記第1の配線から銅ヒロックが発生する温度と時間の条件の下でアニール処理を行うようにしたので、第1の配線形成後に追加したアニール工程において、銅ヒロックが発生しつくしているため、以降の工程においてヒロックが発生することを確実に抑えることができる半導体装置の製造方法が得られる効果がある。

## [0142]

また、本発明の請求項5に係る半導体装置の製造方法によれば、請求項3記載の半導体装置の製造方法において、前記SiN膜を形成する工程は、前記ヴィア形成時及び前記第2の配線溝形成時のヴィア底部において、SiN膜が残存するような膜厚の形成を行うようにしたので、ヴィア形成時及び第2の配線溝形成時に行う処理によっても残存できる厚さのものを予め形成しているため、これらの工程を経た後でもSiN膜が確実に残存することが可能な半導体装置の製造方法が得られる効果がある。

## [ 0 1 4 3 ]

また、本発明の請求項6に係る半導体装置の製造方法によれば、半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝を含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、平坦化して第1の配線を形成する工程と、該第1の配線が形成された半導体基板に対し酸素プラズマ処理を行う工程と、該酸素プラズマ処理により前記第1の配線に発生したヒロックを研磨し、平坦化する工程と、該平坦化された前記第1の配線上にSiN膜を形成する工程と、該SiN膜上に第2の絶縁膜を形成する工程と、該第2の絶縁膜に対しヴィア形状形成用フォトレジストマスクを用いて前記第1の配線に相当する位置にヴィア形状を形成する工程と、前記第2の絶縁膜に対し配線溝形成用フォトレジストマスクを用いて前記ヴィア形状の上部を含

20

30

40

50

む第2の配線溝を形成する工程と、前記ヴィア形状底部のSiN膜を除去する工程と、前記ヴィア形状の内部および前記第2の配線溝の内部を含む前記第2の絶縁膜上に第2の銅膜を形成する工程と、該第2の銅膜を研磨、平坦化しヴィアと第2の配線とを形成する工程とを含むようにしたので、酸素プラズマ処理により意図的に銅ヒロックを発生させた後のSiN膜や絶縁膜を形成する工程で銅ヒロックが発生することがなく、SiN膜は均一な膜厚に形成することができる。このため、その後の工程でSiN膜が意図せぬ破れを起こすことが無く、第1の配線へのダメージを最小限に抑えることが可能となり、第1の配線の侵食を防ぐことができ、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置の製造方法が得られる効果がある。

## [0144]

また、本発明の請求項7に係る半導体装置の製造方法によれば、請求項6記載の半導体装置の製造方法において、前記酸素プラズマ処理工程は、基板温度が120°C以下となる条件の下で行うようにしたので、第1の配線形成後に追加した酸素プラズマ処理工程において、銅ヒロックが発生しつくしているため、以降の工程においてヒロックが発生するのをなくすことが可能な半導体装置の製造方法が得られる効果がある。

#### [0145]

また、本発明の請求項8に係る半導体装置の製造方法によれば、半導体基板上の第1の絶 縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝を含む前 記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、平坦化して第1の配線を 形 成 す る 工 程 と 、 該 第 1 の 配 線 が 形 成 さ れ た 半 導 体 基 板 に 対 し ア ン モ ニ ア プ ラ ズ マ 処 理 を 行う 工 程 と 、 該 ア ン モ ニ ア プ ラ ズ マ 処 理 に よ り 前 記 第 1 の 配 線 に 発 生 し た ヒ ロ ッ ク を 研 磨 し、平坦化する工程と、該平坦化された前記第1の配線上にSiN膜を形成する工程と、 該SiN膜上に第2の絶縁膜を形成する工程と、該第2の絶縁膜に対しヴィア形状形成用 フ ォ ト レ ジ ス ト マ ス ク を 用 い て 前 記 第 1 の 配 線 に 相 当 す る 位 置 に ヴ ィ ア 形 状 を 形 成 す る 工 程 と 、 前 記 第 2 の 絶 縁 膜 に 対 し 配 線 溝 形 成 用 フ ォ ト レ ジ ス ト マ ス ク を 用 い て 前 記 ヴ ィ ア 形 状の上部を含む第2の配線溝を形成する工程と、前記ヴィア形状底部のSiN膜を除去す る工程と、前記ヴィア形状および前記第2の配線溝の内部を含む前記第2の絶縁膜上に第 2の銅膜を形成する工程と、該第2の銅膜を研磨、平坦化しヴィアと第2配線とを形成す る工程とを含むようにしたので、アンモニアプラズマ処理工程により意図的に銅ヒロック を発生させた後のSiN膜や絶縁膜を形成する工程で銅ヒロックが発生することがなく、 SiN膜は均一な膜厚に形成することができる。このため、その後の工程でSiN膜が意 図せぬ破れを起こすことが無く、第1の配線へのダメージを最小限に抑えることが可能と なり、 第 1 の配 線 の 侵 食 を 防 ぐこ と が で き 、 ヴ ィ ア 抵 抗 の 安 定 化 や 配 線 の 信 頼 性 を 確 保 す ることができる半導体装置の製造方法が得られる効果がある。

## [0146]

また、本発明の請求項9に係る半導体装置の製造方法によれば、請求項8記載の半導体装置の製造方法において、前記アンモニアプラズマ処理工程は基板温度が120°C以下の条件の下で行うようにしたので、第1の配線形成後に追加したアンモニアプラズマ処理工程において、銅ヒロックが発生しつくしているため、以降の工程においてヒロックが発生するのをなくすことが可能な半導体装置の製造方法が得られる効果がある。

## [0147]

また、本発明の請求項10に係る半導体装置の製造方法によれば、半導体基板上の第1の絶縁膜の表面に、配線が埋め込まれるべき第1の配線溝を形成し、該第1の配線溝の内部を含む前記第1の絶縁膜上に第1の銅膜を形成し、該第1の銅膜を研磨、平坦化して第1の配線を形成する工程と、該第1の配線上にSiC膜を形成する工程と、該SiC膜上に第2の絶縁膜を形成する工程と、該第2の絶縁膜に対しヴィア形状形成用フォトレジストマスクを用いて前記第1の配線に相当する位置にヴィア形状を形成する工程と、前記第2の絶縁膜に対し配線溝形成用フォトレジストマスクを用いて前記ヴィア形状の上部を含む第2の配線溝を形成する工程と、前記ヴィア形状底部のSiC膜を除去する工程と、前記ヴィア形状および前記第2の配線溝の内部を含む前記第2の絶縁膜上に銅膜を形成する工

程と、該銅膜を研磨、平坦化しヴィアと第2配線とを形成する工程とを含むようにしたので、SiC膜はSiN膜に比べて硬度が高いために銅ヒロックの発生を抑制することができ、SiC膜は均一な膜厚に形成することができる。このため、その後の工程でSiC膜が意図せぬ破れを起こすことが無く、第1配線へのダメージを最小限に抑えることが可能となり、ヴィア抵抗の安定化や配線の信頼性を確保することができる半導体装置の製造方法が得られる効果がある。

#### [ 0 1 4 8 ]

また、本発明の請求項11に係る半導体装置の製造方法によれば、請求項10記載の半導体装置の製造方法において、前記SiC膜を形成する工程は、前記ヴィア形成時及び前記第2の配線溝形成時のヴィア底部において、SiC膜が残存するような膜厚の形成を行うようにしたので、第2の絶縁膜の下に形成するSiC膜として、ヴィア形成時及び第2の配線溝形成時に行う処理によっても残存できる厚さのものを予め形成しているため、これらの工程を経た後でもSiC膜が確実に残存する半導体装置の製造方法が得られる効果がある。

【図面の簡単な説明】

- 【図1】本発明の実施の形態1および3における半導体製造方法の工程断面図である。

- 【図2】本発明の実施の形態1における半導体製造方法の工程フローチャートを示す図である。

- 【図3】本発明の実施の形態2における半導体製造方法の工程断面図である。

- 【図4】本発明の実施の形態2における半導体製造方法の工程フローチャートを示す図である。

- 【図 5 】本発明の実施の形態 3 における半導体製造方法の工程フローチャートを示す図である。

- 【図6】本発明の実施の形態4における半導体製造方法の工程断面図である。

- 【 図 7 】 本 発 明 の 実 施 の 形 態 4 に お け る 半 導 体 製 造 方 法 の 工 程 フ ロ ー チ ャ ー ト を 示 す 図 で あ る 。

- 【図8】従来例における半導体製造方法の工程断面図である。

- 【 図 9 】 従 来 例 に お け る 半 導 体 製 造 方 法 の 工 程 フ ロ ー チ ャ ー ト を 示 す 図 で あ る

【符号の説明】

- 1 半導体基板

- 2 絶縁膜

- 3 第 1 配 線 溝

- 4 銅膜

- 5 第1配線

- 6 SiN膜

- 7 絶縁膜

- 8 銅ヒロック

- 9 ヴィア形状形成用フォトレジストマスク

- 10 ヴィア形状

- 1 1 第 2 配 線 溝 形 成 用 フォトレジストマスク

- 12 ボイド

- 1 3 第 2 配 線 溝

- 1 4 侵食部

- 15 銅膜

- 16 ヴィア

- 17 第2配線

- 2 1 半導体基板

- 2 2 絶縁膜

- 2 3 第 1 配 線 溝

- 2 4 銅膜

30

20

40

20

30

- 2 5 第 1 配 線 2 6 銅ヒロック 2 7 SiN膜 2 8 絶縁膜 2 9 ヴィア形状形成用フォトレジストマスク 3 0 ヴィア形状 3 1 第2配線溝形成用フォトレジストマスク 3 2 第2配線溝 3 3 銅膜 3 4 ヴィア 3 5 第 2 配線 4 1 半導体基板

- 4 2

絶縁膜

4 3

第 1 配線溝

4 4

銅膜

4 5

第 1 配線

- 4 6 銅ヒロック 4 7 酸化銅層 4 8 SiN膜

- 4 9 絶縁膜 5 0 ヴィア形状形成用フォトレジストマスク 5 1 ヴィア形状

- 5 2

第 2 配 線 溝 形 成 用 フォト レジストマスク

5 3

第 2 配 線 溝

- 5 4 銅膜

- 5 5 ヴィア

- 5 6 第 2 配 線 6 1 半 導 体 基 板

- 6 2 絶縁膜

- 6 3 第 1 配 線 溝

- 6 4 銅膜

- 6 5 第 1 配 線

- 6 6 S i C 膜

- 6 7 絶縁膜

- 68 ヴィア形状形成用フォトレジストマスク

- 6 9 ヴィア形状

- 70 第2配線溝形成用フォトレジストマスク

- 7 1 第 2 配 線 溝

- 7 2 銅膜

- 73 ヴィア

- 7 4 第 2 配 線

# 【図5】

## 【図6】

## 【図7】

## 【図8】

# 【図9】