(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2024-44051

(P2024-44051A)

(43)公開日 令和6年4月2日(2024.4.2)

(51)国際特許分類

G 0 6 F 12/06 (2006.01)

G 0 6 F 12/00 (2006.01)

F I

G 0 6 F 12/06

G 0 6 F 12/0012/06

12/005 5 0 A

5 9 7 U

テーマコード(参考)

5 B 1 6 0

審査請求 未請求 請求項の数 20 O L (全21頁)

(21)出願番号

(22)出願日特願2022-149365(P2022-149365)

令和4年9月20日(2022.9.20)(71)出願人

(74)代理人

(72)発明者

(72)発明者

F ターム(参考) 318010018

キオクシア株式会社

東京都港区芝浦三丁目1番21号

110003708

弁理士法人鈴榮特許総合事務所

庄野 温夫

東京都港区芝浦三丁目1番21号 キオ

クシア株式会社内

岩崎 清隆

東京都港区芝浦三丁目1番21号 キオ

クシア株式会社内

5B160 CA15 CD04 CD12

(54)【発明の名称】 メモリシステム

## (57)【要約】

【課題】データ転送の期間を短縮する。

【解決手段】実施形態のメモリシステムは、複数のメモリパッケージと、前記複数のメモリパッケージのそれぞれに設けられた複数のメモリダイと、前記複数のメモリダイのそれぞれに設けられ、データをそれぞれ記憶する複数のプレーンと、を含む不揮発性メモリと、ラウンドロビン処理に基づいて、前記不揮発性メモリからデータをリードするメモリコントローラと、を含み、前記メモリコントローラは、前記複数のプレーンの中から次のサイクルにおいてデータ転送を実行するプレーンを選択する時、データ転送中のプレーンが属するメモリパッケージと異なるメモリパッケージに属するプレーンを、前記ラウンドロビン処理によって、選択する。

【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

複数のメモリパッケージと、前記複数のメモリパッケージのそれぞれに設けられた複数のメモリダイと、前記複数のメモリダイのそれぞれに設けられ、データをそれぞれ記憶する複数のプレーンと、を含む不揮発性メモリと、

ラウンドロビン処理に基づいて、前記不揮発性メモリからデータをリードするメモリコントローラと、

を具備し、

前記メモリコントローラは、前記複数のプレーンの中から次のサイクルにおいてデータ転送を実行するプレーンを選択する時、データ転送中のプレーンが属するメモリパッケージと異なるメモリパッケージに属するプレーンを、前記ラウンドロビン処理によって、選択する、

メモリシステム。

**【請求項 2】**

前記メモリコントローラは、前記ラウンドロビン処理において、

前記複数のメモリパッケージのうち1つのメモリパッケージを、データ転送の可否を判断する対象に設定し、

前記対象に設定されたメモリパッケージがデータ転送を可能であるか否か判断し、

前記対象に設定されたメモリパッケージがデータ転送を可能でない場合、前記対象に設定されたメモリパッケージを、変え、

前記対象に設定されたメモリパッケージがデータ転送を可能である場合、前記対象に設定されたメモリパッケージの前記複数のメモリダイのうち1つのメモリダイを、データ転送の可否を判断する対象に設定し、

前記対象に設定されたメモリダイがデータ転送を可能であるか否か判断し、

前記対象に設定されたメモリダイがデータ転送を可能でない場合、前記対象に設定されたメモリダイを、変え、

前記対象に設定されたメモリダイがデータ転送を可能である場合、前記対象に設定されたメモリダイの前記複数のプレーンのうち1つのプレーンを、データ転送の可否を判断する対象に設定し、

前記対象に設定されたプレーンがデータ転送を可能でない場合、前記対象に設定されたプレーンを、変え、

前記対象に設定されたプレーンがデータ転送を可能である場合、前記対象に設定されたプレーンから前記データをリードする、

請求項1に記載のメモリシステム。

**【請求項 3】**

前記複数のメモリパッケージのそれぞれのデータ転送の可否を示す第1の情報をそれぞれ記憶する複数の第1のレジスタと、前記複数のメモリダイのそれぞれのデータ転送の可否を示す第2の情報をそれぞれ記憶する複数の第2のレジスタと、前記複数のプレーンのそれぞれのデータ転送の可否を示す第3の情報をそれぞれ記憶する複数の第3のレジスタと、を含む記憶部を、

さらに具備する請求項2に記載のメモリシステム。

**【請求項 4】**

前記複数の第1のレジスタのそれぞれの値は、前記複数の第2のレジスタの論理和演算の値に基づいて設定され、

前記複数の第2のレジスタのそれぞれの値は、前記複数の第3のレジスタの論理和演算の値に基づいて設定される、

請求項3に記載のメモリシステム。

**【請求項 5】**

前記メモリコントローラは、

複数の識別番号のそれぞれを、前記複数のプレーンのそれぞれに割り当て、

10

20

30

40

50

前記メモリコントローラは、前記ラウンドロビン処理において、

前記複数の識別番号のうち1つを、データ転送の可否を判断する対象に設定し、

前記設定された識別番号が割り当てられたプレーンがデータ転送可能であるか判断し、

前記設定された識別番号が割り当てられたプレーンがデータ転送を可能でない場合、前記設定された識別番号を変え、

前記設定された識別番号が割り当てられたプレーンがデータ転送を可能である場合、前記設定された識別番号が割り当てられたプレーンからデータをリードする、

請求項1に記載のメモリシステム。

#### 【請求項6】

前記複数の識別番号のうち、データ転送の可否の判断の対象の識別番号を記憶する第1のレジスタと、前記複数のプレーンのそれぞれのデータ転送の可否を示す第1の情報を記憶する第2のレジスタと、を含む記憶部を、

さらに具備する請求項5に記載のメモリシステム。

#### 【請求項7】

前記複数のプレーンのそれぞれのリード期間の終了を検出する第1の検出部を、さらに具備する

請求項1に記載のメモリシステム。

#### 【請求項8】

前記ラウンドロビン処理による前記複数のプレーンのそれぞれからのデータ転送のタイミングを制御するスケジューラを、

さらに具備する

請求項1に記載のメモリシステム。

#### 【請求項9】

前記不揮発性メモリは、NANDフラッシュメモリである、

請求項1に記載のメモリシステム。

#### 【請求項10】

複数のメモリパッケージと、前記複数のメモリパッケージのそれぞれに設けられた複数のメモリダイと、前記複数のメモリダイのそれぞれに設けられ、データをそれぞれ記憶する複数のプレーンと、を含む不揮発性メモリと、

ラウンドロビン処理に基づいて、前記不揮発性メモリからデータをリードするメモリコントローラと、

を具備し、

前記メモリコントローラは、

前記複数のメモリパッケージのうち1つのメモリパッケージを、データ転送の可否を判断する対象に設定し、

前記対象に設定されたメモリパッケージがデータ転送を可能であるか否か判断し、

前記対象に設定されたメモリパッケージがデータ転送を可能でない場合、前記対象に設定されたメモリパッケージを、変え、

前記対象に設定されたメモリパッケージがデータ転送を可能である場合、前記対象に設定されたメモリパッケージの前記複数のメモリダイのうち1つのメモリダイを、データ転送の可否を判断する対象に設定し、

前記対象に設定されたメモリダイがデータ転送を可能であるか否か判断し、

前記対象に設定されたメモリダイがデータ転送を可能でない場合、前記対象に設定されたメモリダイを、変え、

前記対象に設定されたメモリダイがデータ転送を可能である場合、前記対象に設定されたメモリダイの前記複数のプレーンのうち1つのプレーンを、データ転送の可否を判断する対象に設定し、

前記対象に設定されたプレーンがデータ転送を可能でない場合、前記対象に設定されたプレーンを、変え、

10

20

30

40

50

前記対象に設定されたプレーンがデータ転送を可能である場合、前記対象に設定されたプレーンから前記データをリードする、

メモリシステム。

**【請求項 1 1】**

前記複数のメモリパッケージのそれぞれのデータ転送の可否を示す第1の情報をそれぞれ記憶する複数の第1のレジスタと、前記複数のメモリダイのそれぞれのデータ転送の可否を示す第2の情報をそれぞれ記憶する複数の第2のレジスタと、前記複数のプレーンのそれぞれのデータ転送の可否を示す第3の情報をそれぞれ記憶する複数の第3のレジスタと、を含む記憶部を、

さらに具備する請求項10に記載のメモリシステム。

10

**【請求項 1 2】**

前記複数の第1のレジスタのそれぞれの値は、前記複数の第2のレジスタの論理和演算の値に基づいて設定され、

前記複数の第2のレジスタのそれぞれの値は、前記複数の第3のレジスタの論理和演算の値に基づいて設定される、

請求項11に記載のメモリシステム。

20

**【請求項 1 3】**

前記複数のプレーンのそれぞれのリード期間の終了を検出する第1の検出部を、さらに具備する

請求項10に記載のメモリシステム。

20

**【請求項 1 4】**

前記ラウンドロビン処理による前記複数のプレーンのそれぞれからのデータ転送のタイミングを制御するスケジューラを、

さらに具備する

請求項10に記載のメモリシステム。

30

**【請求項 1 5】**

前記不揮発性メモリは、NANDフラッシュメモリである、

請求項10に記載のメモリシステム。

**【請求項 1 6】**

複数のメモリパッケージと、前記複数のメモリパッケージのそれぞれの複数のメモリダイと、前記複数のメモリダイのそれぞれに設けられ、データをそれぞれ記憶する複数のプレーンと、を含む不揮発性メモリと、

ラウンドロビン処理に基づいて、前記不揮発性メモリからデータをリードするメモリコントローラと、

を具備し、

前記メモリコントローラは、

複数の識別番号のそれぞれを、前記複数のプレーンのそれぞれに割り当て、

前記メモリコントローラは、前記ラウンドロビン処理において、

前記複数の識別番号のうち1つを、データ転送の可否を判断する対象に設定し、

前記設定された識別番号が割り当てられたプレーンがデータ転送可能であるか判断し

40

、前記設定された識別番号が割り当てられたプレーンがデータ転送を可能でない場合、前記設定された識別番号を変え、

前記設定された識別番号が割り当てられたプレーンがデータ転送を可能である場合、前記設定された識別番号が割り当てられたプレーンからデータをリードする、

メモリシステム。

**【請求項 1 7】**

前記複数の識別番号のうち、データ転送の可否の判断の対象の識別番号を記憶する第1のレジスタと、前記複数のプレーンのそれぞれのデータ転送の可否を示す第1の情報を記憶する第2のレジスタと、を含む記憶部を、

50

さらに具備する請求項 1 6 に記載のメモリシステム。

【請求項 1 8】

前記複数のプレーンのそれぞれのリード期間の終了を検出する第 1 の検出部を、

さらに具備する

請求項 1 6 に記載のメモリシステム。

【請求項 1 9】

前記ラウンドロビン処理による前記複数のプレーンのそれぞれからのデータ転送のタイミングを制御するスケジューラを、

さらに具備する

請求項 1 6 に記載のメモリシステム。

10

【請求項 2 0】

前記不揮発性メモリは、NAND フラッシュメモリである、

請求項 1 6 に記載のメモリシステム。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

実施形態は、メモリシステムに関する。

【背景技術】

【0 0 0 2】

データを不揮発に記憶することが可能なNAND型フラッシュメモリが知られている。

20

【先行技術文献】

【特許文献】

【0 0 0 3】

【特許文献 1】米国特許出願公開第 2015 / 0212732 号明細書

【特許文献 2】米国特許出願公開第 2019 / 0214087 号明細書

【特許文献 3】米国特許出願公開第 2022 / 0084568 号明細書

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 4】

データ転送の期間を短縮する。

30

【課題を解決するための手段】

【0 0 0 5】

実施形態のメモリシステムは、複数のメモリパッケージと、複数のメモリパッケージのそれぞれに設けられた複数のメモリダイと、複数のメモリダイのそれぞれに設けられ、データをそれぞれ記憶する複数のプレーンと、を含む不揮発性メモリと、ラウンドロビン処理に基づいて、不揮発性メモリからデータをリードするメモリコントローラと、を含み、メモリコントローラは、複数のプレーンの中から次のサイクルにおいてデータ転送を実行するプレーンを選択する時、データ転送中のプレーンが属するメモリパッケージと異なるメモリパッケージに属するプレーンを、ラウンドロビン処理によって、選択する。

【図面の簡単な説明】

40

【0 0 0 6】

【図 1】実施形態の情報処理システムの構成を示す図。

【図 2】第 1 の実施形態のメモリシステムの不揮発性メモリの構成を示す図。

【図 3】第 1 の実施形態のメモリシステムのメモリコントローラの構成を示す図。

【図 4】第 1 の実施形態のメモリシステムの機能構成を示す図。

【図 5】第 1 の実施形態のメモリシステムの動作を示すフローチャート。

【図 6】第 1 の実施形態のメモリシステムの効果を説明するための図。

【図 7】第 2 の実施形態のメモリシステムの機能構成を示す図。

【図 8】第 2 の実施形態のメモリシステムの動作を示すフローチャート。

【発明を実施するための形態】

50

## 【0007】

図1乃至図8を参照して、実施形態のメモリシステムについて、説明する。

## 【0008】

以下、図面を参照しながら、本実施形態について詳細に説明する。以下の説明において、同一の機能及び構成を有する要素については、同一符号を付す。また、以下の各実施形態において、末尾に区別化のための数字／英字を伴った参照符号を付された構成要素（例えば、回路、配線、各種の電圧及び信号など）が、相互に区別されなくとも良い場合、末尾の数字／英字が省略された記載（参照符号）が用いられる。

## 【0009】

（実施形態）

10

（1）第1の実施形態

（a）構成

（a-1）情報処理システム1の構成

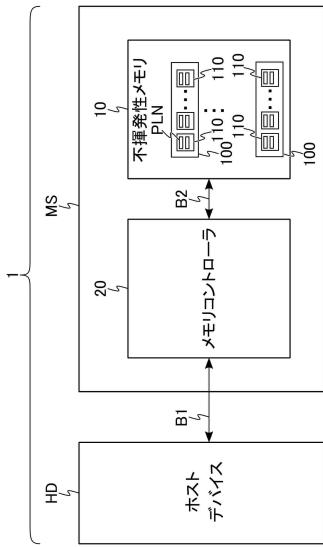

図1は、本実施形態の情報処理システム1の構成の一例を示すブロック図である。

## 【0010】

情報処理システム1は、ホストデバイスHD及びメモリシステムMSを含む。

## 【0011】

ホストデバイスHDは、パーソナルコンピュータ、携帯情報端末、サーバなどの電子機器である。

## 【0012】

メモリシステムMSは、メモリカード、SSD (solid state drive)などの半導体ストレージデバイスである。メモリシステムMSは、不揮発性メモリ10、及びメモリコントローラ20を含む。

20

## 【0013】

不揮発性メモリ10は、データを不揮発に記憶するメモリデバイスである。本実施形態において、不揮発性メモリ10は、例えば、NAND型フラッシュメモリである。但し、不揮発性メモリ10は、NOR型フラッシュメモリ、MRAM (Magneto-resistive Random Access Memory)、PRAM (Phase change Random Access Memory)、ReRAM (Resistive Random Access Memory)、FeRAM (Ferroelectric Random Access Memory)でもよい。不揮発性メモリ10は、複数のメモリパッケージ100を含む。複数のメモリパッケージ100のそれぞれは、複数のメモリダイ（メモリチップ）110を含む。複数のメモリダイ110のそれぞれは、複数のプレーンPLNを含む。本実施形態において、データを不揮発性メモリ10に記憶させる（書き込む）ことを、“不揮発化”ともよぶ。

30

## 【0014】

メモリコントローラ20は、不揮発性メモリ10を制御する制御装置である。メモリコントローラ20は、例えば、SoC (System On a Chip)として構成される半導体集積回路である。メモリコントローラ20は、ホストデバイスHDから受けた命令（要求）に基づいて不揮発性メモリ10を制御して、データのリード動作、ライト動作、及びイレース動作などを実行する。メモリコントローラ20は、複数の不揮発性メモリ10を一括で管理してもよい。メモリコントローラ20は、バスB1を介してホストデバイスHDに接続される。不揮発性メモリ10は、バスB2を介して、メモリコントローラ20に接続される。なお、ホストデバイスHDとメモリコントローラ20とは、ネットワークを介して接続されてもよい。

40

## 【0015】

（a-2）メモリシステムMSのハードウェア構成

（a-2-1）不揮発性メモリ10のハードウェア構成

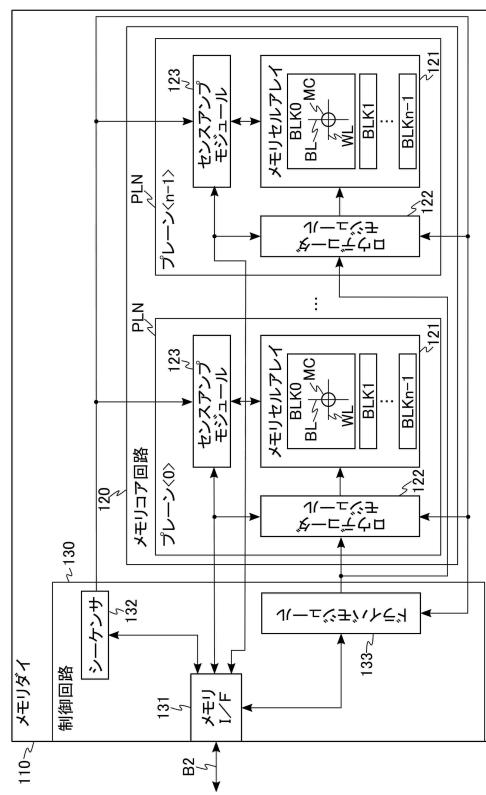

図2は、本実施形態の不揮発性メモリ10のハードウェア構成の一例を示すブロック図である。

## 【0016】

50

不揮発性メモリ 10 の或るメモリパッケージ 100において、各メモリダイ110は、例えば、複数のプレーン PLN、及び制御回路 130 を含む。

【0017】

複数のプレーン PLN のそれぞれは、互いに独立に且つ並列（同時）に動作し得る回路である。複数のプレーン PLN の集合は、メモリコア回路 120 ともよばれる。

【0018】

制御回路 130 は、複数のプレーン PLN の動作を制御する複数の回路の集合である。

【0019】

各プレーン PLN は、メモリセルアレイ 121、ロウデコーダモジュール 122、及びセンスアンプモジュール 123 を含む。

10

【0020】

メモリセルアレイ 121 は、複数のメモリセル MC の集合を含む記憶回路である。複数のメモリセル MC は、二次元に配置されてもよいし、三次元に配置されてもよい。

【0021】

ロウデコーダモジュール 122 は、ロウアドレスをデコードするデコーダである。ロウデコーダモジュール 122 は、デコード結果に基づいてメモリセルアレイ 121 のロウ（1つのブロック BLK）を選択する。ロウデコーダモジュール 122 は、選択したブロック BLK に設けられた複数の配線（ワード線 WL 及びビット線 BL）に、電圧をそれぞれ転送する。

20

【0022】

センスアンプモジュール 123 は、リード動作時、ビット線 BL の電圧に基づいて、選択されたブロック BLK から読み出されたデータをセンスするセンス回路である。センスアンプモジュール 123 は、リード動作時、読み出されたデータを、制御回路 130 を介してメモリコントローラ 20 に送信する。センスアンプモジュール 123 は、ライト動作時、メモリセル MC に書き込むデータに応じた電圧を各ビット線 BL に印加し得る。

【0023】

メモリセルアレイ 121 は、複数のブロック BLK (BLK0 ~ BLKn-1) を含む。n は、自然数である。ブロック BLK は、例えば、データのイレース単位として使用される。ブロック BLK は、複数のページを含む。ページは、データのリードの単位である。また、ページは、データのライトの単位である。ページは、例えば、1つのワード線 WL に接続された複数のメモリセル MC によって記憶されるデータに対応する。なお、1つのワード線 WL に接続された複数のメモリセル MC は、各メモリセル MC が記憶するデータのビット数に応じて、複数のページのデータを記憶し得る。

30

【0024】

ブロック BLK は、複数のメモリセル MC と、複数のビット線 BL と、複数のワード線 WL とを含む。各メモリセル MC は、少なくとも1ビットデータを不揮発に記憶する。各メモリセル MC は、1つのビット線 BL と1つのワード線 WL とに関連付けられる。各メモリセル MC は、ワード線 WL を識別するアドレスと、ビット線 BL を識別するアドレスと、に基づいて識別される。

40

【0025】

制御回路 130 は、メモリインターフェース（メモリ I/F）131、シーケンサ 132、及びドライバモジュール 133 を含む。

【0026】

メモリ I/F 131 は、バス B2 を介してメモリコントローラ 20 に接続されるハードウェアインターフェースである。メモリ I/F 131 は、不揮発性メモリ 10 とメモリコントローラ 20 との間のインターフェース規格に従った通信を行う。メモリ I/F 131 がサポートするインターフェース規格は、例えば、NANDインターフェース規格である。例えば、メモリ I/F 131 は、ロウアドレスを各ロウデコーダモジュール 122 に送る。メモリ I/F 131 は、リード動作時、読み出されたデータをセンスアンプモジュール 123 のそれから受ける。メモリ I/F 131 は、ライト動作時、データを或るセ

50

ンスアンプモジュール 123 に送る。

【0027】

シーケンサ 132 は、メモリダイ 110 の全体の動作を制御する制御回路である。シーケンサ 132 は、メモリ I/F 131 を介して受け取ったコマンドに基づいてドライバモジュール 133、複数のロウデコーダモジュール 122、及び複数のセンスアンプモジュール 123 などを制御して、リード動作、ライト動作、及びイレース動作などを実行する。

【0028】

ドライバモジュール 133 は、リード動作、ライト動作、及びイレース動作などに用いられる電圧を生成する回路である。ドライバモジュール 133 は、複数の信号線を介してロウデコーダモジュール 122 のそれぞれに接続される。ドライバモジュール 133 は、メモリ I/F 131 を介して受け取ったアドレスに基づいて、複数のワード線 WL 及び複数のビット線 BL に対応する複数の信号線の各々に印加する電圧を変更し得る。

【0029】

不揮発性メモリ 10 のメモリ空間において、メモリパッケージ 100 の識別番号（アドレス値）は、メモリ空間における上層のアドレスの階層に相当する。プレーン PLN の識別番号（アドレス）は、メモリ空間における下層のアドレスの階層に相当する。メモリダイ 110 の識別番号（アドレス）は、メモリ空間におけるメモリパッケージ 100 の階層とプレーン PLN の階層との間の中層のアドレスの階層に相当する。

【0030】

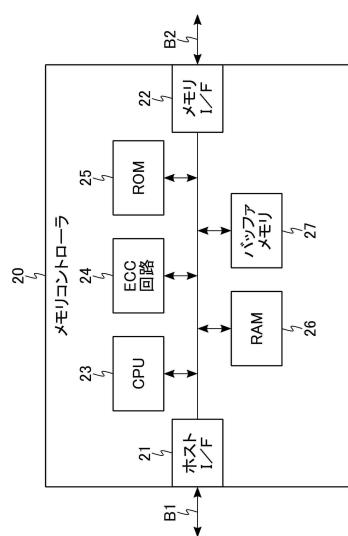

（a-2-2）メモリコントローラ 20 のハードウェア構成

図 3 は、本実施形態のメモリコントローラ 20 のハードウェア構成の一例を示すブロック図である。

【0031】

本実施形態のメモリコントローラ 20 は、ホストインターフェース（ホスト I/F）21、メモリインターフェース（メモリ I/F）22、CPU（Central Processing Unit）23、ECC（Error Correction Code）回路 24、ROM（Read Only Memory）25、RAM（Random Access Memory）26、及びバッファメモリ 27 を含む。

【0032】

ホスト I/F 21 は、バス B 1 を介してホストデバイス HD に接続されるハードウェアインターフェースである。ホスト I/F 21 は、ホストデバイス HD とメモリコントローラ 20 との間のインターフェース規格に従った通信を行う。ホスト I/F 21 がサポートするインターフェース規格は、SATA（Serial Advanced Technology Attachment）、PCIe<sup>TM</sup>（PCI Express）などである。

【0033】

メモリ I/F 22 は、バス B 2 を介して不揮発性メモリ 10 に接続されるハードウェアインターフェースである。メモリ I/F 22 は、不揮発性メモリ 10 とメモリコントローラ 20 との間のインターフェース規格に従った通信を行う。メモリ I/F 22 がサポートするインターフェース規格は、例えば、NAND インターフェース規格である。

【0034】

CPU 23 は、プロセッサである。CPU 23 は、メモリコントローラ 20 の全体の動作を制御する。CPU 23 は、ホスト I/F 21 を介して受けたライト要求に従って、データの書き込みをメモリ I/F 22 を介して不揮発性メモリ 10 に指示する。CPU 23 は、ホスト I/F 21 を介して受けたリード要求に従って、データの読み出しをメモリ I/F 22 を介して不揮発性メモリ 10 に指示する。

【0035】

ECC 回路 24 は、ECC 処理を実行する回路である。ECC 処理は、データの符号化及び復号化を含む。ECC 回路 24 は、不揮発性メモリ 10 に書き込むデータを符号化する。ECC 回路 24 は、不揮発性メモリ 10 から読み出されたデータを復号する。

10

20

30

40

50

## 【0036】

R O M 2 5 は、不揮発性メモリである。R O M 2 5 は、例えば、E E P R O M <sup>TM</sup> (E lectrically Erasable Programmable Read-Only Memory) である。R O M 2 5 は、ファームウェアなどのプログラムを記憶する。例えば、後述されるメモリコントローラ20の動作は、C P U 2 3 がR O M 2 5 のファームウェアを実行することにより実現される。

## 【0037】

R A M 2 6 は、揮発性メモリである。R A M 2 6 は、例えば、D R A M (Dynamic R andom Access Memory) やS R A M (Static Random Access Memory) である。R A M 2 6 は、C P U 2 3 の作業領域として使用される。R A M 2 6 は、論理アドレスと物理アドレスとを関連付けるルックアップテーブル (L U T) などの管理テーブルを記憶する。管理テーブルは、メモリシステムM S のシステムデータの一種である。L U T は、"アドレス変換テーブル" や、"論理アドレス / 物理アドレス変換テーブル" とよばれてもよい。

## 【0038】

バッファメモリ27は、揮発性メモリである。バッファメモリ27は、D R A M (Dynamic Random Access Memory) やS R A M (Static Random Access Memory) などである。バッファメモリ27は、ホストI / F 2 1 を介して受けたデータや、メモリI / F 2 2 を介して受けたデータを一時的に記憶する。バッファメモリ27は、メモリコントローラ20に外部接続されてもよい。

10

20

30

40

50

## 【0039】

(a - 2 - 3) 不揮発性メモリ10及びメモリコントローラ20の機能構成

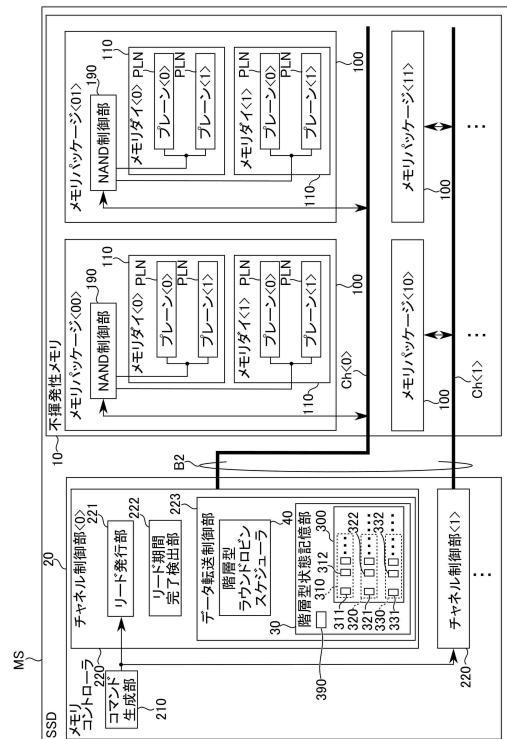

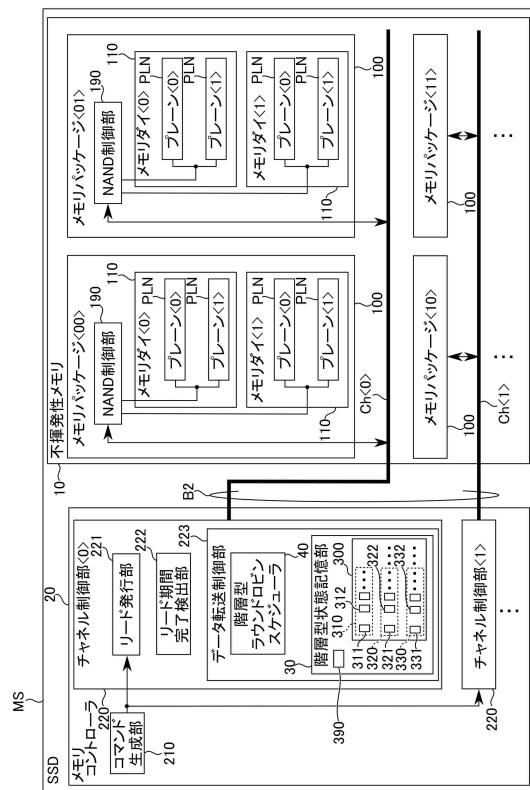

図4は、本実施形態のメモリシステムM S における、不揮発性メモリ10及びメモリコントローラ20の機能構成の一例を示すブロック図である。

## 【0040】

上述のように、不揮発性メモリ10は、複数のメモリパッケージ100を含む。複数のメモリパッケージ100のそれぞれは、チャネルC h (C h 0, C h 1, ...)を介して、メモリコントローラ20に接続される。或る個数(例えば、2つ)のメモリパッケージ100が、1つのチャネルC h に接続される。複数のチャネルC h の集合が、バスB 2 である。

## 【0041】

各メモリパッケージ100は、複数のメモリダイ110およびN A N D 制御部190を含む。1つのメモリパッケージは、例えば、2つのメモリダイ110を含む。但し、メモリパッケージ100が含むメモリダイ110の数は、3以上でもよい。

## 【0042】

各メモリダイ110は、複数のプレーンP L N を含む。1つのメモリダイ110は、例えば、2つのプレーンP L N を含む。但し、メモリダイ110のプレーンP L N の数は、3以上でもよい。プレーンP L N のそれぞれは、互いに独立に、コマンドに応じた動作シーケンスを実行する。

## 【0043】

N A N D 制御部190は、複数のメモリダイ110の制御回路130の集合を示す機能ブロックである。N A N D 制御部190は、メモリパッケージ100の複数のプレーンP L N の各種の動作を制御する。N A N D 制御部190は、リード動作において、プレーンP L N から読み出されたデータを、メモリコントローラ20に送る。N A N D 制御部190は、ライト動作において、不揮発性メモリ10に書き込まれるデータを、プレーンP L N に送る。

## 【0044】

メモリコントローラ20は、コマンド生成部210、及び複数のチャネル制御部220を含む。

## 【0045】

コマンド生成部 210 は、コマンドを生成する機能ブロックである。

【0046】

チャネル制御部 220 のそれぞれは、複数のチャネル Ch のうち対応する 1 つを制御する機能ブロックである。

【0047】

チャネル制御部 220 は、リード発行部 221、リード期間終了検出部 222、及びデータ転送制御部 223 を含む。

【0048】

リード発行部 221 は、コマンドに基づいて、チャネル Ch に属する複数のメモリパッケージ 100 のそれぞれに、リードコマンドを発行する。

10

【0049】

リード期間終了検出部 222 は、複数のプレーン PLN の中からリード期間が終了したプレーン PLN を検出する。リード期間は、プレーン PLN のリード動作が開始されてから完了するまでの期間である。リード期間が終了したプレーン PLN は、リード動作におけるデータ転送が可能なプレーン PLN、或いは、データ転送の指示を待っているプレーン PLN である。例えば、リード期間終了検出部 222 は、各種の機能に基づいて、NAND 制御部 190 を介して、メモリパッケージ 100 の動作状態、メモリダイ 110 の動作状態、及びプレーン PLN の動作状態を、モニタできる。リード期間終了検出部 222 は、モニタ結果に基づいて、リード期間が終了したプレーン（データ転送が可能なプレーン）PLN を検出する。例えば、リード期間終了検出部 222 は、リード期間が終了したプレーン PLN を、後述の階層型状態記憶部 30 に通知する。

20

【0050】

データ転送制御部（データアウト制御部ともよばれる）223 は、ラウンドロビン処理によって、各メモリパッケージ 100 のプレーン PLN から読み出されたデータの転送（データの出力）の順序を制御する。データ転送制御部 223 は、データ転送の可能な複数のプレーン PLN の中から次のサイクルにおいてデータ転送を実行するプレーン PLN を選択する時、現在データ転送中のプレーン PLN が属するメモリパッケージ 100（又はメモリダイ 110）と異なるメモリパッケージ 100（又はメモリダイ 110）に属するプレーン PLN を、ラウンドロビン処理によって、優先的に選択する。データ転送制御部 223 は、例えば、ソフトウェア、ハードウェア、又は、ソフトウェアとハードウェアとの組み合わせによって、構成される。

30

【0051】

データ転送制御部 223 は、階層型状態記憶部 30、及び階層型ラウンドロビンスケジューラ 40 を含む。

【0052】

階層型状態記憶部 30 は、複数のメモリパッケージ 100 を含む階層、複数のメモリダイ 110 を含む階層、及び複数のプレーン PLN を含む階層のそれぞれにおける、各階層のデータ転送に関する各種の情報を記憶する。例えば、階層型状態記憶部 30 は、リード期間終了検出部 222 からの通知に基づいて、各メモリパッケージ 100 のリード期間の終了の状態（データ転送の可否、データ転送待ち）、各メモリダイ 110 のリード期間の終了の状態、及びプレーン PLN のリード期間の終了の状態を、記憶する。ここで、リード動作の終了の状態は、リード期間が終了したか否かに応じて、プレーンから読み出されたデータを、メモリコントローラ 20 に転送可能な状態を示す。また、階層型状態記憶部 30 は、記憶している情報を、チャネル制御部 220 及び／又は階層型ラウンドロビンスケジューラ 40 に送ることができる。

40

【0053】

階層型ラウンドロビンスケジューラ（ラウンドロビン制御部ともよばれる）40 は、ラウンドロビン処理のための各種の処理の実行タイミング、各種の動作の実行期間、及び各種の設定を、制御する。例えば、階層型ラウンドロビンスケジューラ 40 は、階層型状態記憶部 30 の情報に基づいて、データ転送の可能なメモリパッケージ 100、データ転送

50

の可能なメモリダイ110、及びデータ転送の可能なプレーンPLNを階層的に探索する。階層型ラウンドロビンスケジューラ40は、ラウンドロビン処理による探索結果に基づいて、データ転送を可能なプレーンPLNを、検知する。階層型ラウンドロビンスケジューラ40は、検知結果に基づいて、データ転送を実行するプレーンPLNを選択する。階層型ラウンドロビンスケジューラ40は、選択されたプレーンPLNからのデータ転送を、制御する。

#### 【0054】

階層型状態記憶部30は、レジスタ領域300及び論理演算部390を含む。

#### 【0055】

レジスタ領域300は、情報を記憶する。

10

#### 【0056】

論理演算部390は、レジスタ322, 332の値の論理演算（例えば、OR演算）を実行する。論理演算部390は、データ転送制御部223の構成要素として、階層型状態記憶部30の外部に設けられてもよい。

#### 【0057】

レジスタ領域300は、チャネル対応部310を含む。

#### 【0058】

チャネル対応部310は、不揮発性メモリ10とメモリコントローラ20との間の対応するチャネルChに対して設けられている。チャネル対応部310は、ラウンドロビン処理における、対応するチャネルChの複数のメモリパッケージ100のデータ転送可能状態に関する情報を記憶する。

20

#### 【0059】

チャネル対応部310は、レジスタ311、複数のレジスタ312及び複数のメモリパッケージ対応部320を含む。

#### 【0060】

レジスタ311は、対応するチャネルChのメモリパッケージ100の階層において、複数のメモリパッケージ100のうちどのメモリパッケージ100が、ラウンドロビン処理におけるモニタ対象のメモリパッケージ100であるかを示す情報（例えば、メモリパッケージ100の識別番号又はアドレス値）を、記憶する。

30

#### 【0061】

複数のレジスタ312のそれぞれは、メモリパッケージ100の階層において、対応するメモリパッケージ100がリード期間を終了しているか否か（データ転送を可能であるか否か）を示す情報を、記憶する。

#### 【0062】

例えば、或るメモリパッケージ100が、データ転送を不可能な状態である場合（メモリパッケージ100の複数のメモリダイ110が、リード期間が終了したプレーンPLNを含まない状態である場合）、そのメモリパッケージ100に対応するレジスタ312は、第1の値（N）を記憶する。第1の値は、例えば、1ビットのデータである。1ビットのデータは、“0”データ又は“1”データを意味する。

40

#### 【0063】

また、例えば、或るメモリパッケージ100が、データ転送を可能な状態である場合（メモリパッケージ100の少なくとも1つのメモリダイ110が、リード期間が終了したプレーンPLNを含む状態である場合）、そのメモリパッケージ100に対応するレジスタ312は、第1の値と異なる第2の値（Y）を記憶する。第2の値は、例えば、1ビットのデータである。1ビットのデータは、“0”データ又は“1”データを意味する。

#### 【0064】

さらに、例えば、或るメモリパッケージ100に関するレジスタ312の値は、そのメモリパッケージ100に属するメモリダイ110に関する複数のレジスタ322の値の論理演算の結果に基づいて、決定される。複数のレジスタ322の値に対して実行される論理演算は、例えば、論理和演算（OR演算）である。

50

**【 0 0 6 5 】**

複数のメモリパッケージ対応部 320 は、チャネル Ch に属する複数のメモリパッケージ 100 にそれぞれ対応する。複数のメモリパッケージ対応部 320 のそれぞれは、ラウンドロビン処理における、対応するメモリパッケージ 100 の複数のメモリダイ 110 のデータ転送可能状態に関する情報を記憶する。

**【 0 0 6 6 】**

各メモリパッケージ対応部 320 は、レジスタ 321 及び複数のレジスタ 322 を含む。

**【 0 0 6 7 】**

レジスタ 321 は、対応するメモリパッケージ 100 のメモリダイ 110 の階層において、複数のメモリダイ 110 のうちどのメモリダイ 110 が、ラウンドロビン処理におけるモニタ対象のメモリダイ 110 であるかを示す情報（例えば、メモリダイ 110 の識別番号又はアドレス値）を、記憶する。

**【 0 0 6 8 】**

複数のレジスタ 322 のそれぞれは、メモリダイ 110 の階層において、対応するメモリダイ 110 がリード期間を終了しているか否かを示す情報を、記憶する。

**【 0 0 6 9 】**

例えば、或るメモリダイ 110 が、データ転送を不可能な状態である場合（リード期間が終了したプレーン PLN を含まない状態である場合）、そのメモリダイ 110 に対応するレジスタ 322 は、第 3 の値（N）を記憶する。第 3 の値は、例えば、1 ビットのデータである。

**【 0 0 7 0 】**

また、例えば、或るメモリダイ 110 が、データ転送を可能な状態である場合（リード期間が終了したプレーン PLN を含む状態である場合）、そのメモリダイ 110 に対応するレジスタ 322 は、第 3 の値と異なる第 4 の値（Y）を記憶する。第 4 の値は、例えば、1 ビットのデータである。

**【 0 0 7 1 】**

さらに、例えば、或るメモリダイ 110 に関するレジスタ 322 の値は、そのメモリダイ 110 に属するプレーン PLN に関する複数のレジスタ 332 の値の論理演算の結果に基づいて、決定される。複数のレジスタ 332 の値に対して実行される論理演算は、例えば、論理和演算（OR 演算）である。

**【 0 0 7 2 】**

各メモリパッケージ対応部 320 は、複数のメモリダイ対応部 330 を含む。

**【 0 0 7 3 】**

複数のメモリダイ対応部 330 は、メモリパッケージ 100 に属する複数のメモリダイ 110 にそれぞれ対応する。複数のメモリダイ対応部 330 のそれぞれは、ラウンドロビン処理における、対応するメモリダイ 110 の複数のプレーン PLN のデータ転送可能状態に関する情報を記憶する。

**【 0 0 7 4 】**

各メモリダイ対応部 330 は、レジスタ 331 及び複数のレジスタ 332 を含む。

**【 0 0 7 5 】**

レジスタ 331 は、対応するメモリダイ 110 のプレーン PLN の階層において、複数のプレーン PLN のうちどのプレーン PLN が、ラウンドロビン処理におけるモニタ対象のプレーン PLN であるかを示す情報（例えば、プレーン PLN の識別番号又はアドレス値）を、記憶する。

**【 0 0 7 6 】**

複数のレジスタ 332 のそれぞれは、プレーン PLN の階層において、対応するプレーン PLN がリード期間を終了しているか否かを示す情報を、記憶する。

**【 0 0 7 7 】**

例えば、或るプレーン PLN が、データ転送を不可能な状態である場合（リード期間が

10

20

30

40

50

終了していない状態である場合) そのプレーン P L N に対応するレジスタ 332 は、第 5 の値 (N) を記憶する。第 5 の値は、例えば、1 ビットのデータである。

【0078】

また、例えば、或るプレーン P L N が、データ転送を可能な状態である場合 (リード期間が終了している状態である場合)、そのプレーン P L N に対応するレジスタ 332 は、第 5 の値と異なる第 6 の値 (Y) を記憶する。第 6 の値は、例えば、1 ビットのデータである。

【0079】

さらに、例えば、或るプレーン P L N のリード期間 (t R) が終了した場合、そのプレーン P L N に対応するレジスタ 332 の値は、第 5 の値から第 6 の値へ変わる。レジスタ 332 が第 6 の値を有している場合、そのレジスタ 332 に対応するプレーン P L N は、データ転送を待っている状態 (データ転送を可能である状態) を示す。データ転送可能なプレーン P L N のデータ転送が完了した場合、そのプレーン P L N に対応するレジスタ 332 の値は、第 6 の値から第 5 の値へ変わる。

【0080】

(b) 動作

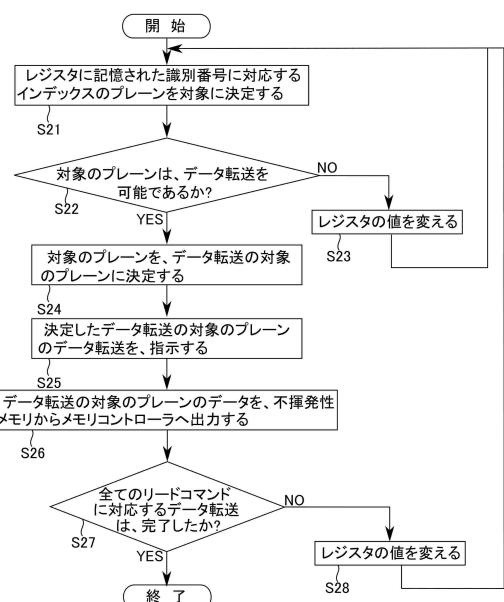

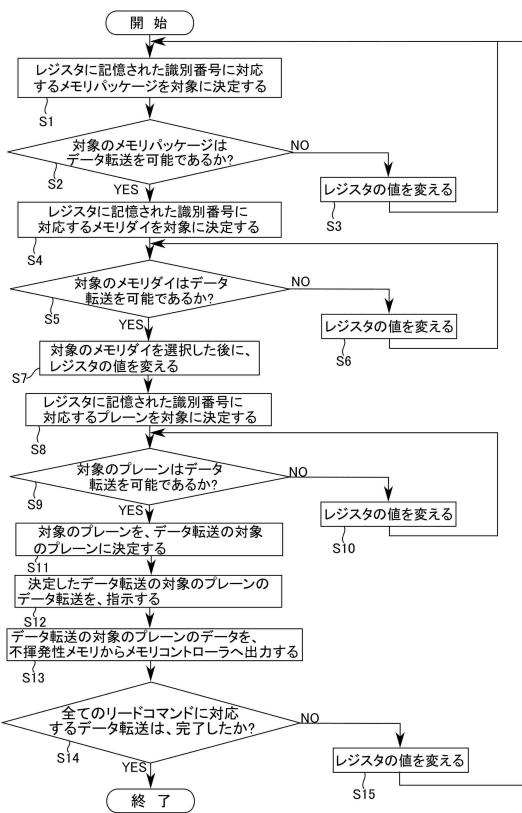

図 5 は、第 1 の実施形態のメモリシステム M S の動作を示すフローチャートである。

【0081】

メモリコントローラ 20 は、不揮発性メモリ 10 からの複数のデータ転送のために、ラウンドロビン処理を実行する。

【0082】

メモリコントローラ 20 のデータ転送制御部 223 は、複数のメモリパッケージ 100 のリード期間の終了の状態 (データ転送の可否)、複数のメモリダイ 110 のリード期間の終了の状態、及び複数のプレーン P L N のリード期間の終了の状態を、階層型状態記憶部 30 の情報 (データ) に基づいて、階層型ラウンドロビンスケジューラ 40 によって、対応するメモリパッケージ 100 のメモリ空間を階層的にモニタする。

【0083】

ここでは、1 つのチャネル C h (例えば、チャネル C h <0>) に関するチャネル制御部 220 及びメモリパッケージ 100 のラウンドロビン処理及びデータ転送について、説明する。

【0084】

データ転送の開始のタイミング又は或るプレーン P L N からのデータ転送中において、階層型ラウンドロビンスケジューラ 40 は、レジスタ 311 に記憶された識別番号に対応するメモリパッケージ 100 を対象に決定する (S1)。レジスタ 311 に識別番号が記憶されてない場合、階層型ラウンドロビンスケジューラ 40 は、チャネル C h <0> に属する或る識別番号 (i 番) のメモリパッケージ 100 を対象に決定する。i は、0 以上の整数である。例えば、或るメモリパッケージ 100 のデータ転送が実行中である場合、データ転送を実行中のメモリパッケージ 100 と異なるメモリパッケージ 100 が、対象となる。レジスタ 311 に識別番号が記憶されてない場合、階層型ラウンドロビンスケジューラ 40 は、対象のメモリパッケージ 100 の識別番号を、レジスタ 311 に記憶させる。

【0085】

階層型ラウンドロビンスケジューラ 40 は、対象のメモリパッケージ 100 が、データ転送を可能な状態であるか否か、判断する (S2)。対象のメモリパッケージ 100 がデータ転送を可能な状態であるか否かの情報は、対応するレジスタ 312 に記憶される。

【0086】

対象のメモリパッケージ 100 が、データ転送を可能な状態でない場合 (S2 NO)、階層型ラウンドロビンスケジューラ 40 は、レジスタ 311 の値を、インクリメント (1 の加算) 又はデクリメント (1 の減算) する (S3)。これによって、階層型ラウンドロビンスケジューラ 40 は、レジスタ 311 の値を変える。その後、階層型ラウンドロビ

10

20

30

40

50

ンスケジューラ 4 0 は、 S 1 の処理を行う。

【 0 0 8 7 】

対象のメモリパッケージ 1 0 0 が、データ転送を可能な状態である場合 ( S 2 Y E S ) 、階層型ラウンドロビンスケジューラ 4 0 は、対象のメモリパッケージ 1 0 0 に属する複数のメモリダイ 1 1 0 のうち、レジスタ 3 2 1 に記憶された識別番号に対応するメモリダイ 1 1 0 を対象に決定する ( S 4 ) 。レジスタ 3 2 1 に識別番号が記憶されてない場合、階層型ラウンドロビンスケジューラ 4 0 は、或る識別番号 ( j 番目 ) のメモリダイ 1 1 0 を対象に決定する。 j は、 0 以上の整数である。レジスタ 3 2 1 に識別番号が記憶されてない場合、階層型ラウンドロビンスケジューラ 4 0 は、対象のメモリダイ 1 1 0 の識別番号を、レジスタ 3 2 1 に記憶させる。

10

【 0 0 8 8 】

階層型ラウンドロビンスケジューラ 4 0 は、対象のメモリダイ 1 1 0 が、データ転送を可能な状態であるか否か、判断する ( S 5 ) 。対象のメモリダイ 1 1 0 がデータ転送を可能な状態であるか否かの情報は、対応するレジスタ 3 2 2 に記憶される。

【 0 0 8 9 】

対象のメモリダイ 1 1 0 が、データ転送を可能な状態でない場合 ( S 5 N O ) 、階層型ラウンドロビンスケジューラ 4 0 は、レジスタ 3 2 1 の値を、インクリメント又はデクリメントする ( S 6 ) 。これによって、階層型ラウンドロビンスケジューラ 4 0 は、レジスタ 3 2 1 の値を変える。その後、階層型ラウンドロビンスケジューラ 4 0 は、 S 4 の処理を行う。

20

【 0 0 9 0 】

対象のメモリダイ 1 1 0 が、データ転送を可能な状態である場合 ( S 5 Y E S ) 、階層型ラウンドロビンスケジューラ 4 0 は、対象のメモリダイ 1 1 0 を選択した後に、レジスタ 3 2 1 の値を、インクリメント又はデクリメントする ( S 7 ) 。このように、階層型ラウンドロビンスケジューラ 4 0 は、レジスタ 3 2 1 の値を変える。これによって、複数のリード動作が連続して実行される状況下にあっても、同じ識別番号を有するメモリダイ 1 1 0 が連続して選択されるのを、抑制できる。

【 0 0 9 1 】

階層型ラウンドロビンスケジューラ 4 0 は、選択したメモリダイ 1 1 0 に属する複数のプレーン P L N のうち、レジスタ 3 3 1 に記憶された識別情報に対応するプレーン P L N を対象に決定する ( S 8 ) 。レジスタ 3 3 1 に識別情報が記憶されてない場合、階層型ラウンドロビンスケジューラ 4 0 は、或る識別番号 ( k 番目 ) のプレーン P L N を対象に決定する。 k は、 0 以上の整数である。レジスタ 3 3 1 に識別情報が記憶されてない場合、階層型ラウンドロビンスケジューラ 4 0 は、対象のプレーン P L N の識別番号を、レジスタ 3 3 1 に記憶させる。

30

【 0 0 9 2 】

階層型ラウンドロビンスケジューラ 4 0 は、対象のプレーン P L N が、データ転送を可能な状態であるか否か、判断する ( S 9 ) 。対象のプレーン P L N がデータ転送を可能な状態であるか否かの情報は、対応するレジスタ 3 3 2 に記憶される。

40

【 0 0 9 3 】

対象のプレーン P L N が、データ転送を可能な状態でない場合 ( S 9 N O ) 、階層型ラウンドロビンスケジューラ 4 0 は、レジスタ 3 3 1 の値を、インクリメント又はデクリメントする ( S 1 0 ) 。これによって、階層型ラウンドロビンスケジューラ 4 0 は、レジスタ 3 3 1 の値を変える。その後、階層型ラウンドロビンスケジューラ 4 0 は、 S 8 の処理を行う。

【 0 0 9 4 】

対象のプレーン P L N が、データ転送を可能な状態である場合 ( S 9 Y E S ) 、階層型ラウンドロビンスケジューラ 4 0 は、対象のプレーン P L N を、データ転送の対象のプレーン P L N に決定する ( S 1 1 ) 。階層型ラウンドロビンスケジューラ 4 0 は、データ転送の対象のプレーン P L N を決定した後に、レジスタ 3 3 1 の値を変更してもよい。こ

50

れによって、複数のリード動作が連続して実行される状況下にあっても、同じ識別番号を有するプレーンPLNが連続して選択されるのを、抑制できる。

【0095】

階層型ラウンドロビンスケジューラ40は、決定したデータ転送の対象のプレーンPLNに対するデータ転送を、データ転送制御部223に指示する(S12)。

【0096】

データ転送を指示されると、データ転送制御部223は、不揮発性メモリ10に、データ転送の対象のプレーンPLNのデータを、メモリコントローラ20へ出力させる(S13)。データは、NAND制御部190及びチャネルChを介して、メモリコントローラ20に出力される。データ転送の対象のプレーンPLNのデータ転送が完了した後、データ転送の対象のプレーンPLNに対応するレジスタ332には、データ転送を不可能な状態を示す情報が記憶される。

【0097】

データ転送の対象のプレーンPLNのデータ転送が完了した後、階層型ラウンドロビンスケジューラ40は、全てのリードコマンドに対応するデータの転送が完了した否か、確認する(S14)。

【0098】

全てのリードコマンドに対するデータの転送が完了していない場合(S13 NO)、階層型ラウンドロビンスケジューラ40は、レジスタ311の値を、インクリメント又はデクリメントする(S15)。その後、階層型ラウンドロビンスケジューラ40は、S1の処理を行う。

【0099】

全てのリードコマンドに対するデータの転送が完了している場合(S13 YES)、メモリコントローラ20は、図5に示す一連の処理を、終了する(終了)。

【0100】

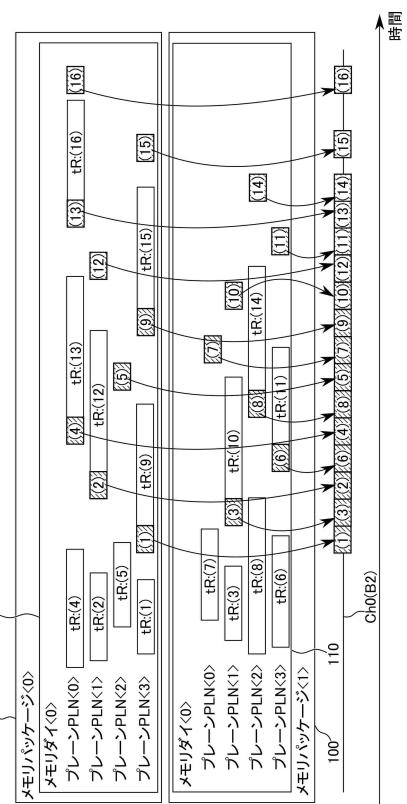

図6は、本実施形態のメモリシステムMSにおける、データ転送の順序の制御にラウンドロビン処理を用いたデータ転送処理を、模式的に示す図である。図6において、2つのメモリパッケージ100が並列にデータ転送を実行する例が示されている。図6において、“(1),(2),(3),…,(15),(16)”は、リード期間の終了の順序を示している。

【0101】

ラウンドロビン処理によるデータ転送の順序の制御によって、複数のメモリパッケージ100のそれぞれから、データ(複数のデータアイテム)が、チャネルCh(バスB2)に出力される。

【0102】

本実施形態において、或るメモリパッケージ100のプレーンPLNの先行するデータ転送が完了する時点において、データ転送が可能な1以上のプレーンPLNの中から、先行するデータ転送を実行するメモリパッケージ100と異なるメモリパッケージ100のプレーンPLNが、選択される。

【0103】

それゆえ、本実施形態において、各メモリパッケージ100内のデータのリード期間tRの終了の順に依存せずに、リード期間tRが終了したプレーンPLNのデータ転送が、2つのメモリパッケージ100から交互に実行される。連続する2つのデータ転送が、互いに異なるメモリパッケージ100において実行される場合、データ出力待ち時間tWHR2は、発生しない。

【0104】

この結果として、本実施形態のメモリシステムMSは、データ転送間の待ち時間tWHR2の発生を抑制できる。

【0105】

それゆえ、本実施形態のメモリシステムMSは、複数のデータ転送の完了までの期間を

10

20

30

40

50

短縮できる。

【0106】

1つのメモリパッケージ100の複数のメモリダイ110が、ラウンドロビン処理によって設定された順序に基づくデータ転送によって、並列にデータを転送する場合、先行するデータ転送を実行するメモリダイ110と異なるメモリダイ110のプレーンPLNが、次のデータ転送の対象として選択される。或るメモリダイ110の先行のデータ転送の完了の後、異なるメモリダイ110のデータ転送が、選択されたプレーンPLNによって実行される。

【0107】

(c) 効果

第1の実施形態のメモリシステムMSは、メモリパッケージ100毎及びメモリダイ110毎に、前回のサイクルのデータ転送に続くデータ転送の対象となるメモリパッケージ100、メモリダイ110及びプレーンPLNを、ラウンドロビン処理によって、巡回して探索する。これによって、第1の実施形態のメモリシステムMSは、データ転送を実行可能なプレーンPLNが、一定の巡回の回数のうちにデータ転送の対象として選択することを、保証できる。したがって、第1の実施形態のメモリシステムMSは、データ転送のレイテンシの上限を保証できる。

10

【0108】

(d) まとめ

ラウンドロビン処理によって、データの転送可能な単位が、メモリパッケージ100、メモリダイ110及びプレーンPLNの順に階層的に探索される場合、異なる識別番号を有する複数のメモリパッケージ100及び/又は異なる識別番号を有するメモリダイ110が、データ転送の対象として、順次(交互に)選択される傾向を有する。それゆえ、同じ識別番号を有するメモリパッケージ100及び/又は同じ識別番号を有するメモリダイ110からの連続したデータ転送は、比較的回避され得る。この結果として、第1の実施形態のメモリシステムMSにおいて、複数のデータ転送間の待ち時間の発生が、抑制される。したがって、第1の実施形態のメモリシステムMSは、データ転送のための時間を、短縮できる。第1の実施形態のメモリシステムMSは、データ転送を効率化できる。第1の実施形態のメモリシステムMSは、メモリシステムの性能を向上できる。

20

【0109】

30

(2) 第2の実施形態

(a) 構成

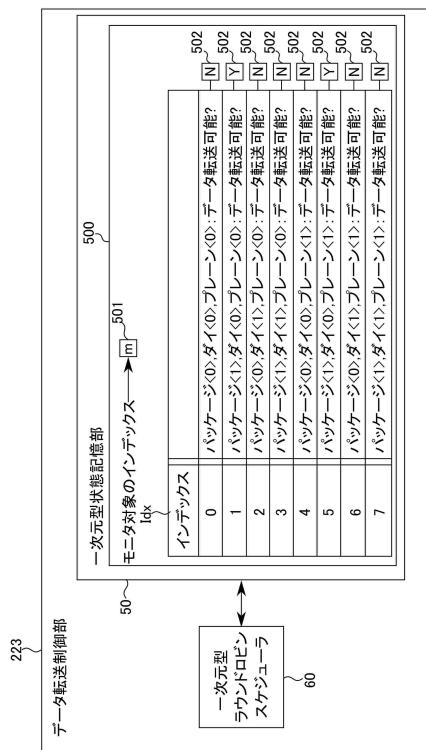

図7は、第2の実施形態に係るメモリシステムMSの構成を模式的に示す図である。

【0110】

第2の実施形態において、インデックス(識別番号)Idxが、データ出力の対象の最小単位のそれぞれに割り当てられる。例えば、不揮発性メモリ10に含まれる複数のプレーンPLNのそれぞれが、データ出力の対象の最小単位である。

【0111】

図7の例において、不揮発性メモリ10において、1つのチャネルChに、2つのメモリパッケージ100が属する。1つのメモリパッケージ100は、2つのメモリダイ110を含む。1つのメモリダイ110は、2つのプレーンPLNを含む。

40

【0112】

この場合において、以下のように、インデックスIdxは、データ転送単位である複数のプレーンPLNのそれぞれに対して、割り当てられる。

【0113】

“0”のインデックスIdxが、“0”の識別番号のメモリパッケージ100及び“0”の識別番号のメモリダイ110に属する“0”的プレーンPLNに、割り当てられる。

【0114】

“1”的インデックスIdxが、“1”的識別番号のメモリパッケージ100及び“0”的識別番号のメモリダイ110に属する“0”的プレーンPLNに、割り当てられる。

50

## 【 0 1 1 5 】

“ 2 ” のインデックス  $I_{d \times}$  が、 “ 0 ” の識別番号のメモリパッケージ 1 0 0 及び “ 1 ” の識別番号のメモリダイ 1 1 0 に属する “ 0 ” のプレーン P L N に、割り当てられる。

## 【 0 1 1 6 】

“ 3 ” のインデックス  $I_{d \times}$  が、 “ 1 ” の識別番号のメモリパッケージ 1 0 0 及び “ 1 ” の識別番号のメモリダイ 1 1 0 に属する “ 0 ” のプレーン P L N に、割り当てられる。

## 【 0 1 1 7 】

“ 4 ” のインデックス  $I_{d \times}$  が、 “ 0 ” の識別番号のメモリパッケージ 1 0 0 及び “ 0 ” の識別番号のメモリダイ 1 1 0 に属する “ 1 ” のプレーン P L N に、割り当てられる。

## 【 0 1 1 8 】

“ 5 ” のインデックス  $I_{d \times}$  が、 “ 1 ” の識別番号のメモリパッケージ 1 0 0 及び “ 0 ” の識別番号のメモリダイ 1 1 0 に属する “ 1 ” のプレーン P L N に、割り当てられる。

## 【 0 1 1 9 】

“ 6 ” のインデックス  $I_{d \times}$  が、 “ 0 ” の識別番号のメモリパッケージ 1 0 0 及び “ 1 ” の識別番号のメモリダイ 1 1 0 に属する “ 1 ” のプレーン P L N に、割り当てられる。

## 【 0 1 2 0 】

“ 7 ” のインデックス  $I_{d \times}$  が、 “ 1 ” の識別番号のメモリパッケージ 1 0 0 及び “ 1 ” の識別番号のメモリダイ 1 1 0 に属する “ 1 ” のプレーン P L N に、割り当てられる。

## 【 0 1 2 1 】

隣り合う 2 つのインデックス  $I_{d \times}$  のそれぞれは、互いに異なる識別番号のメモリパッケージ 1 0 0 に関連付けられている。

## 【 0 1 2 2 】

例えば、複数のインデックス  $I_{d \times}$  の配列は、プレーン P L N の番号が最上位の桁、メモリパッケージ 1 0 0 の番号が最下位の桁、メモリダイ 1 1 0 の番号がプレーン P L N の番号の桁とメモリパッケージ 1 0 0 の番号の桁との間の桁とした数値に基づいて、設定される。

## 【 0 1 2 3 】

このように、1 つのメモリパッケージ 1 0 0 内のプレーン P L N の数に応じて、8 つのインデックス  $I_{d \times}$  が、データ転送に関するラウンドロビン処理のために、設定される。

## 【 0 1 2 4 】

本実施形態において、データ転送制御部 2 2 3 は、一次元型状態記憶部 5 0 及び一次元型ラウンドロビンスケジューラ 6 0 を含む。

## 【 0 1 2 5 】

一次元型状態記憶部 5 0 は、レジスタ領域 5 0 0 を含む。レジスタ領域 5 0 0 は、複数のレジスタ 5 0 1, 5 0 2 を含む。レジスタ 5 0 1 は、モニタ対象のインデックス  $I_{d \times}$  の値 (m) を、記憶する。m は、0 以上の整数である。

## 【 0 1 2 6 】

複数のレジスタ 5 0 2 のそれぞれは、対応するインデックス  $I_{d \times}$  に対応するプレーン P L N がデータの転送を可能であるか否かの状態を示す値を、記憶する。レジスタ 5 0 2 の値は、例えば、リード期間終了検出部 2 2 2 によって、制御される。

## 【 0 1 2 7 】

レジスタ 5 0 2 は、対応するインデックス  $I_{d \times}$  のプレーン P L N のリード期間が終了していない状態 (データ転送が可能でない状態) である場合、第 7 の値 (N) を記憶する。第 7 の値は、1 ビットのデータ (“ 0 ” データ又は “ 1 ” データ) である。

## 【 0 1 2 8 】

レジスタ 5 0 2 は、対応するインデックス  $I_{d \times}$  のプレーン P L N のリード期間が終了している状態 (データ転送が可能な状態、データ転送が待機の状態) である場合、第 7 の値と異なる第 8 の値 (Y) を記憶する。第 8 の値は、1 ビットのデータ (“ 0 ” データ又は “ 1 ” データ) である。

## 【 0 1 2 9 】

10

30

40

50

一次元型ラウンドロビンスケジューラ（ラウンドロビン制御部）60は、モニタ対象のインデックス $Id_x$ の値を、レジスタ501に設定する。

【0130】

一次元型ラウンドロビンスケジューラ60は、複数のレジスタ502の値に基づいて、モニタ対象のインデックス $Id_x$ に対応するプレーンPLNがデータ転送を可能であるか否か、モニタする。

【0131】

例えば、一次元型ラウンドロビンスケジューラ60は、不揮発性メモリ10の各プレーンからのデータ転送を制御できる。

【0132】

（b）動作

図8は、第2の実施形態に係るメモリシステムMSの動作を示すフローチャートである。

【0133】

データ転送の開始のタイミング又は或るプレーンPLNからのデータ転送中、一次元型ラウンドロビンスケジューラ60は、レジスタ501に記憶された識別番号に対応するインデックス $Id_x$ のプレーンPLNを対象に決定する（S21）。

【0134】

一次元型ラウンドロビンスケジューラ60は、対象のプレーンPLNが、データ転送可能であるか否か、判断する（S22）。

【0135】

対象のプレーンPLNが、データ転送可能でない場合（S22 NO）、一次元型ラウンドロビンスケジューラ60は、レジスタ501の値を、インクリメント又はデクリメントによって、変える（S23）。その後、一次元型ラウンドロビンスケジューラ60は、S21の処理を行う。

【0136】

対象のプレーンPLNが、データ転送可能である場合（S22 YES）、一次元型ラウンドロビンスケジューラ60は、対象のプレーンPLNを、データ転送の対象のプレーンPLNに決定する（S24）。

【0137】

一次元型ラウンドロビンスケジューラ60は、決定したデータ転送の対象のプレーンPLNのデータ転送を、データ転送制御部223に指示する（S25）。

【0138】

データ転送が指示されると、データ転送制御部223は、不揮発性メモリ10に、データ転送の対象のプレーンPLNのデータを、メモリコントローラ20へ出力させる（S26）。

【0139】

データ転送の対象のプレーンPLNのデータ転送が完了した後、一次元型ラウンドロビンスケジューラ60は、全てのリードコマンドに対するデータの転送が完了しているか否か、確認する（S27）。

【0140】

全てのリードコマンドに対するデータの転送が完了していない場合（S27 NO）、一次元型ラウンドロビンスケジューラ60は、レジスタ501の値を、変える（S28）。その後、一次元型ラウンドロビンスケジューラ60は、S21の処理を行う。

【0141】

全てのリードコマンドに対するデータの転送が完了している場合（S27 YES）、メモリコントローラ20は、図8に示される一連の処理を、終了する（終了）。

【0142】

（c）まとめ

第2の実施形態のメモリシステムMSにおいて、不揮発性メモリ10のデータ転送は、

10

20

30

40

50

それぞれ異なるインデックス  $I_{d \times}$  が割り当てられたプレーン  $P_L N$  の単位で、管理される。これによって、第 2 の実施形態のメモリシステム  $M_S$  は、不揮発性メモリ 10 からの複数のデータ転送の順序を、比較的容易に制御できる。

#### 【 0 1 4 3 】

第 2 の実施形態のメモリシステム  $M_S$  において、複数のプレーン  $P_L N$  は、インデックス  $I_{d \times}$  の数に応じた或るサイクルで、探索される。したがって、第 2 の実施形態において、複数のプレーン  $P_L N$  のそれぞれは、データの転送対象として、確実に選択され得る。したがって、第 2 の実施形態のメモリシステム  $M_S$  は、データ転送のレイテンシの上限を保証できる。

#### 【 0 1 4 4 】

第 2 の実施形態のメモリシステム  $M_S$  は、ラウンドロビン処理による探索の階層の一次元化によって、モニタ対象の識別番号を記憶するレジスタ 501 の数を、削減できる。この結果として、第 2 の実施形態において、状態記憶部 50 のレジスタ領域 500 のサイズが、縮小され得る。

#### 【 0 1 4 5 】

第 2 の実施形態のメモリシステム  $M_S$  は、第 1 の実施形態と実質的に同じ効果を得ることができる。第 2 の実施形態のメモリシステム  $M_S$  は、データ転送のための時間を、短縮できる。第 2 の実施形態のメモリシステム  $M_S$  は、メモリシステムの性能を向上できる。

#### 【 0 1 4 6 】

##### ( 3 ) その他

実施形態は例示であり、発明の範囲はそれらに限定されない。

#### 【 符号の説明 】

#### 【 0 1 4 7 】

1 ... 情報処理システム

H D ... ホストデバイス

M S ... メモリシステム

1 0 0 ... メモリパッケージ

1 1 0 ... メモリダイ

P L N ... プレーン

2 2 2 ... リード期間終了検出部

2 2 3 ... データ転送制御部

3 0 ... 階層型状態記憶部

3 1 1 , 3 1 2 , 3 2 1 , 3 2 2 , 3 3 1 , 3 3 2 ... レジスタ

4 0 ... 階層型ラウンドロビンスケジューラ

5 0 ... 一次元型状態記憶部

5 0 1 , 5 0 2 ... レジスタ

6 0 ... 一次元型ラウンドロビンスケジューラ

10

20

30

40

50

【図面】

【図1】

【図3】

【図2】

10

20

【図4】

30

40

50

【 図 5 】

〔 図 6 〕

【 図 7 】

〔 四 8 〕