(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6576926号

(P6576926)

(45) 発行日 令和1年9月18日(2019.9.18)

(24) 登録日 令和1年8月30日(2019.8.30)

(51) Int.Cl.

F 1

|             |           |            |      |

|-------------|-----------|------------|------|

| HO1L 29/06  | (2006.01) | HO1L 29/78 | 652P |

| HO1L 29/78  | (2006.01) | HO1L 29/78 | 653A |

| HO1L 21/336 | (2006.01) | HO1L 29/78 | 658F |

|             |           | HO1L 29/78 | 658A |

|             |           | HO1L 29/06 | 301F |

請求項の数 13 (全 11 頁) 最終頁に続く

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2016-539924 (P2016-539924)  |

| (86) (22) 出願日      | 平成26年12月3日 (2014.12.3)        |

| (65) 公表番号          | 特表2017-504964 (P2017-504964A) |

| (43) 公表日           | 平成29年2月9日 (2017.2.9)          |

| (86) 國際出願番号        | PCT/EP2014/076443             |

| (87) 國際公開番号        | W02015/090971                 |

| (87) 國際公開日         | 平成27年6月25日 (2015.6.25)        |

| 審査請求日              | 平成29年12月1日 (2017.12.1)        |

| (31) 優先権主張番号       | 13197534.4                    |

| (32) 優先日           | 平成25年12月16日 (2013.12.16)      |

| (33) 優先権主張国・地域又は機関 | 歐州特許庁 (EP)                    |

早期審査対象出願

前置審査

最終頁に続く

(54) 【発明の名称】半導体装置のエッジ終端および対応する製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体パワーデバイスを製造する方法であつて、

前記半導体パワーデバイスは、

第1導電型のドリフト層を含む半導体基板(6)を備え、前記半導体基板(6)は、アクティプセルエリア(3)と、基板エッジまでのエッジ終端エリア(4)とを有し、

前記方法は、

前記第1導電型と異なる第2導電型の複数の表面ガードリング(10)を形成する第1のステップを含み、前記複数の表面ガードリングは、前記エッジ終端エリア(4)の表面上において互いに分離されており、

基板材料を除去することにより、前記エッジ終端エリア(4)の前記半導体基板(6)の表面から下方に延在する複数の終端トレンチ(40)を形成する第2のステップを含み、前記複数の終端トレンチ(40)は、各表面ガードリング(10)が、隣接する終端トレンチ(40)の、基板エッジに向かって前記終端トレンチ(40)の側のみに接し、かつ、前記ドリフト層が、前記終端トレンチ(40)の、アクティプセルエリア(3)に向かって前記終端トレンチ(40)の側に接するように、形成され、それにより、前記ドリフト層は前記複数の終端トレンチ(40)を分離し、

各終端トレンチ(40)の底部に隣接する基板材料内に前記第2導電型の埋込みガードリング(41)を形成する第3のステップと、

各終端トレンチ(40)を誘電材料または導電材料で充填する第4のステップと、

10

20

終端レンチ(40)ごとに、各終端レンチ(40)の上面の一部および前記終端レンチに接する表面ガードリング(10)の上面の全体ならびに前記ドリフト層の上面の一部を接触により覆うように、フィールドプレート(11)を形成する第5のステップとを含む、方法。

**【請求項2】**

前記第5のステップは、前記ドリフト層の表面上において、前記表面ガードリングを超えるように基板エッジの側に延在するフィールドプレート(11)を形成するステップをさらに含む、請求項1に記載の方法。

**【請求項3】**

前記第1のステップを前記第2のステップよりも前に実行して、前記複数の終端レンチ(40)各々について、前記第2のステップで除去された基板材料が、前記表面ガードリング(10)のうちの1つの一部を含むようにする、請求項1~2のいずれか一項に記載の方法。 10

**【請求項4】**

前記アクティブセルエリア(3)は、複数のレンチ-ゲート装置セル(30、31、33)を含み、

前記第2のステップは、前記レンチ-ゲート装置セル(30、31、33)のレンチ(30)を、前記終端レンチ(40)と同一の1つまたは複数の製造プロセス中に形成することを含む、請求項1~3のいずれか一項に記載の方法。

**【請求項5】**

前記アクティブセルエリア(3)は、複数のアクティブ装置セル(20、21、23、24)を含み、前記アクティブ装置セルは各々ボディ領域(20)を含み、

前記第1のステップは、前記アクティブ装置セル(20、21、23、24)の前記ボディ領域(20)を、前記表面ガードリング(10)と同一の1つまたは複数の製造プロセス中に形成することを含む、請求項1~4のいずれか一項に記載の方法。 20

**【請求項6】**

終端レンチ(40)ごとに、各終端レンチ(40)の一部および前記終端レンチに接する表面ガードリング(10)の上に、フィールドプレート(11)を形成する第5のステップをさらに含み、

各アクティブ装置セル(20、21、23、24)は、ゲート接続(23)およびパワー接続(24)のうちの少なくとも一方を含み、

前記第5のステップは、前記ゲート接続(23)および前記パワー接続(24)のうちの少なくとも一方を、前記フィールドプレート(11)と同一の1つまたは複数の製造プロセス中に形成することを含む、請求項4または5に記載の方法。 30

**【請求項7】**

終端レンチ(40)ごとに、各終端レンチ(40)の一部および前記終端レンチに接する表面ガードリング(10)の上に、フィールドプレート(11)を形成する第5のステップをさらに含み、前記フィールドプレート(11)は、前記ドリフト層の表面上において、前記表面ガードリングを超えるように基板エッジの側に延在し、

各アクティブ装置セル(20、21、23、24)は、ゲート接続(23)およびパワー接続(24)のうちの少なくとも一方を含み、

前記第5のステップは、前記ゲート接続(23)および前記パワー接続(24)のうちの少なくとも一方を、前記フィールドプレート(11)と同一の1つまたは複数の製造プロセス中に形成することを含む、請求項4または5に記載の方法。 40

**【請求項8】**

第1導電型のドリフト層を含む半導体基板(6)を備えた半導体パワー装置であって、前記半導体基板(6)は、アクティブセルエリア(3)と、基板エッジまでのエッジ終端エリア(4)とを有し、

前記エッジ終端エリア(4)は、

前記第1導電型と異なる第2導電型の複数の表面ガードリング(10)を含み、前記複 50

数の表面ガードリング(10)は、前記エッジ終端エリア(4)の表面に配置され、互いに分離されており、

前記エッジ終端エリア(4)の前記半導体基板(6)の表面から下方に延在し、誘電材料または導電材料で充填された複数の終端トレンチ(40)を含み、各表面ガードリング(10)が、隣接する終端トレンチ(40)の、基板エッジに向かって前記終端トレンチ(40)の側のみに接し、かつ、前記ドリフト層が、前記終端トレンチ(40)の、アクティブセルエリア(3)に向かって前記終端トレンチ(40)の側に接し、それにより、前記ドリフト層は前記複数の終端トレンチ(40)を分離し、

複数の埋込みガードリング(41)を含み、各埋込みガードリング(41)は、前記半導体基板(6)内において前記終端トレンチ(40)のうちの1つの底部に隣接するように配置されており、10

少なくとも1つのフィールドプレート(11)が、終端トレンチ(40)の上面の一部および前記終端トレンチに接する表面ガードリング(10)の上面の全体ならびに前記ドリフト層の上面の一部を接触により覆うように配置されている、半導体パワー装置。

#### 【請求項9】

前記少なくとも1つのフィールドプレート(11)は、前記ドリフト層の表面上において、前記表面ガードリングを超えるように基板エッジの側に延在する、請求項8に記載の半導体パワー装置。

#### 【請求項10】

前記アクティブセルエリア(3)は、複数のトレンチ-ゲート装置セル(30、31、33)を含み、20

前記終端トレンチ(40)は、前記トレンチ-ゲート装置セル(30、31、33)のトレンチ(30)と同一の材料で充填されている、請求項8～9のいずれか一項に記載の半導体パワー装置。

#### 【請求項11】

前記アクティブセルエリア(3)は、複数のアクティブ装置セル(20、21、23、24)を含み、前記アクティブ装置セルは各々、第2導電型のボディ領域(20)を含み、

前記表面ガードリング(10)のドーピング濃度プロファイルは、前記アクティブ装置セル(20、21、23、24)の前記ボディ領域(20)と同一である、請求項8～10のいずれか一項に記載の半導体パワー装置。30

#### 【請求項12】

少なくとも1つのフィールドプレート(11)が終端トレンチ(40)および前記終端トレンチに接する表面ガードリング(10)の上に配置されており、

各アクティブ装置セル(20、21、23、24)は、ゲート接続(23)およびパワー接続(24)のうちの少なくとも一方を含み、

前記終端トレンチ(40)、前記表面ガードリング(10)および前記フィールドプレート(11)は、前記アクティブ装置セル(20、21、23、24)の前記ゲート接続(23)および前記パワー接続(24)のうちの少なくとも一方と同一の材料を含む、請求項11に記載の半導体パワー装置。40

#### 【請求項13】

前記少なくとも1つのフィールドプレート(11)は、前記ドリフト層の表面上において、前記表面ガードリングを超えるように基板エッジの側に延在している、請求項12に記載の半導体パワー装置。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置の終端配置に関し、排他的にではないが具体的には、何百または何千ボルトの逆電圧に耐えることが求められる、ダイオード、トランジスタ、または絶縁ゲートバイポーラトランジスタ(insulated gate bipolar transistor)(IGBT)等

の高電圧 (high voltage) (H V) 半導体装置の終端配置に関する。

**【背景技術】**

**【0 0 0 2】**

**発明の背景**

高電圧半導体装置は一般的に、この装置を周囲の基板からおよび / または装置のパッケージから電気的に分離する終端領域を含む。終端領域によって、確実に半導体装置のアクティブエリアを高電圧から保護するとともに半導体装置の装置耐圧ができる限り高くなるようにしなければならない。

**【0 0 0 3】**

D M O S F E T または I G B T 等の高電圧装置の場合、低濃度でドープされたドリフト領域を、装置の最大限の定格電圧を得るために重要である、力線または電位線の最適分布を保証するように、終端させることがある。有効であるためには、このような終端エリアが、装置の内部 (アクティブ) エリアよりも高い耐圧能力を有することが好ましいはずである。

**【0 0 0 4】**

電気的な終端は、誘電材料によっておよび / または逆バイアスされた p n 接合によって得ることができる。誘電体分離の場合、シリコンの酸化物等の誘電絶縁体材料を使用してもよく、その場合の電気的終端は、装置のアクティブエリアを囲む終端エリアに、酸化物で充填されたトレンチを形成することによって得てもよい。このような終端トレンチは、基板本体全体において横方向に電位線または力線を分布させるのに有効であろうが、表面における電荷と電位の分布は相対的に未制御の状態のままになる場合がある。

**【0 0 0 5】**

代わりに接合分離終端を用いてもよい。この場合、逆バイアスされた p n 接合によって、終端エリア全体を通る力線または電位線の必要な分布が得易くなる。たとえばドリフト領域とは逆のドーピングがなされた表面ガードリングを用いることにより、終端エリアの、基板の表面近傍において、電位を分布させてよい。しかしながら、このような終端配置は、基板本体の中の、表面近傍における、電位線の密集を防止するには、効果が低い。さらに、このような先行技術の終端配置では、一般的に、特別の製造ステップおよび / またはマスクが必要であるか、または、製造プロセスによって、終端要素の形状および / または構成が制限される場合があるか、いずれかである。

**【0 0 0 6】**

U S 2 0 0 8 / 0 4 2 1 7 2 A 1 は、連続した 1 つの p ドープ層によって囲まれた、アクティブセルエリアのトレンチゲートと、終端エリアの終端トレンチゲートとを含む、先行技術の M O S トランジスタに言及している。

**【0 0 0 7】**

U S 2 0 0 9 / 0 9 0 9 6 8 A 1 には、終端領域にある、フィールドプレート電極によって覆われた p ガードリングを有する、先行技術の M O S 装置が記載されている。

**【発明の概要】**

**【課題を解決するための手段】**

**【0 0 0 8】**

本発明の目的は、先行技術の終端配置の短所のうちの少なくともいくつかを克服することである。そのために、本発明は、請求項 1 に記載の製造方法および請求項 6 に記載の半導体装置を予測する。本発明の他の変形は従属請求項 2 ~ 5 および 7 ~ 1 1 に記載されている。

**【0 0 0 9】**

終端トレンチと埋込みガードリングの製造を、表面ガードリングの製造と組合わせることによって、必要な追加の製造プロセスの量を最小にしつつ、優れた終端効率 (すなわち終端エリアの低減および / または耐圧の増大) を得ることが可能である。終端トレンチおよび / または表面ガードリング上にフィールドプレートを加えることによって、終端効率をさらに改善してもよい。

10

20

30

40

50

**【0010】**

終端トレンチと、この終端トレンチに接する、深い場所にある埋込みガードリングとを配置することによって、電界を、終端エリア内において、このような埋込み終端トレンチよりも下の、浅い場所で維持し、電界の電位線がアクティブエリアから横方向外向きに案内されるようにして、耐圧を高める。表面ガードリングが、終端トレンチの、基板のエッジ側の側面に接しているので、電界はさらにアクティブエリアから外向きの方向に拡大するが、それでもなお、外側から2番目の終端トレンチの前で効率的に終端される、すなわち、電界が良好に制御されて終端されるが、それでも横方向の短い距離の中に納まっている。

**【0011】**

ドリフト層が、各終端トレンチの、アクティブセルエリア側の側面に接しており、かつ、表面ガードリングが、基板エッジ側のみに配置されていることで、電界が、それを超えた領域で、すなわち終端トレンチの外側（基板のエッジ側）で終端するようになると、重要である。終端トレンチの、アクティブセルエリア側の側面に、表面ガードリングがあると、電位線をアクティブセルエリアから遠ざかる方向に導くという効果が損なわれるであろう。

**【0012】**

代表的な実施形態において、終端トレンチを表面ガードリングに接続するフィールドプレートの存在は、アクティブセルエリアからの、短いが制御された側方距離の中で、電界を終端させる効果に寄与し、基板の表面を保護する。

**【発明の効果】****【0013】**

このように、本発明の半導体装置によって、小さな距離の中で電界を効率的に終端させる装置を得ることができ、それにより、装置をより確実に動作させることができるとともに、先行技術の装置よりも小型になるように設計することができる、すなわち終端エリア（終端エリアの横方向の拡がり）を低減することができる。

**【0014】**

次に、添付の図面を参照しながら本発明についてより詳細に説明する。

**【図面の簡単な説明】****【0015】**

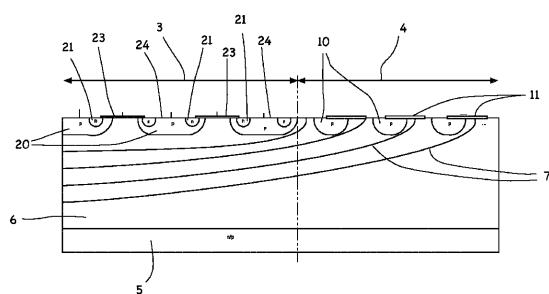

【図1】先行技術において周知の、p リングとフィールドプレートを用いてnチャネルDMOS 装置を終端させる例の概略断面図を示す。

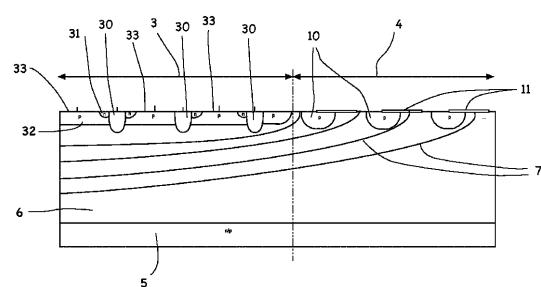

【図2】先行技術において周知の、p リングとフィールドプレートを用いてトレンチゲートnチャネル装置を終端させる例の概略断面図を示す。

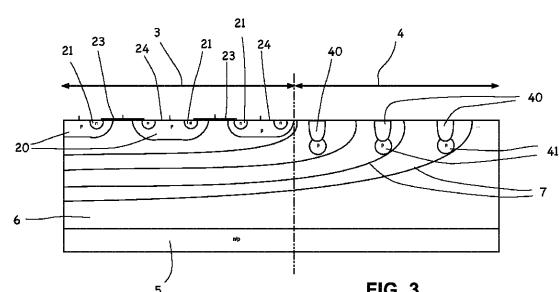

【図3】先行技術において周知の、トレンチと埋込みp リングを用いてnチャネルDMOS 装置を終端させる例の概略断面図を示す。

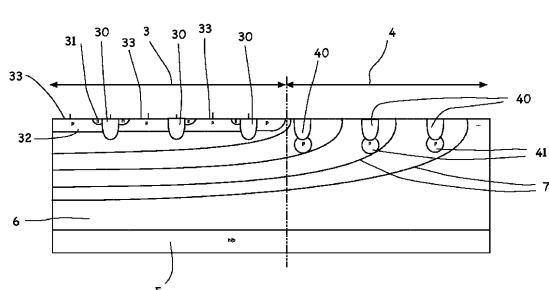

【図4】先行技術において周知の、トレンチと埋込みp リングを用いてトレンチゲートnチャネル装置を終端させる例の概略断面図を示す。

【図5】本発明に従う、トレンチと埋込みガードリングと表面ガードリングとを用いてnチャネルDMOS 装置を終端させる例の概略断面図を示す。

【図6】本発明に従う、トレンチと埋込みガードリングと表面ガードリングとを用いてトレンチゲートnチャネル装置を終端させる例の概略断面図を示す。

【図7】本発明に従う、トレンチと埋込みガードリングと表面ガードリングとを用いてnチャネルDMOS 装置を終端させる例の概略断面図を示す。

【図8】本発明に従う、終端させた一般的な装置の一例の概略平面図を示す。

**【発明を実施するための形態】****【0016】**

なお、図面は、本発明の基礎をなす特定の原理の理解を助けるために設けられており、保護を求める範囲の限定を示唆するものと解釈されてはならない。2つ以上の図面において用いられている同一の参照符号は、同一または対応する特徴を示すことを意図している

10

20

30

40

50

。しかしながら、異なる参照符号が用いられていても、これらの参照符号が示す特徴の違いを示すものと解釈されなければならない。

#### 【0017】

##### 発明の詳細な説明

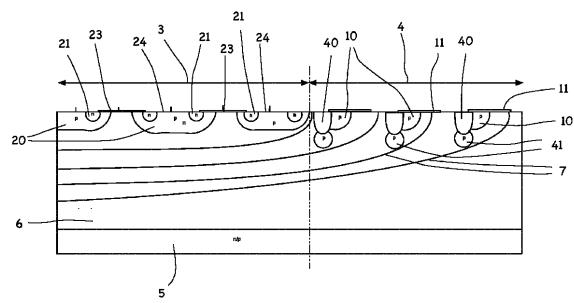

図1は、先行技術において周知の、nチャネル空乏MOSFETまたはIGBTの断面図の一例を示す。アクティブセルエリア3は、パワーMOSFETまたはIGBTセルのアレイを含み、各セルは、2つのnドープ領域21（すなわち第1導電型）とpドープボディ（ウェル）領域20との間に形成された2つのpn接合を取り囲むpドープボディ領域20（すなわち第2導電型）を有する。2つのゲート接続23（この例の場合は近くのセルによって共有される）は、pn接合からドリフト領域6に入り装置基板6（nドリフト層の形態）を通ってドレイン／カソード層5（nチャネルDMOSFETの場合はnドープ、またはnチャネルIGBTの場合はpドープ）に入る電流の流れを制御するために、設けられている。電力はエミッタ／アノードコンタクト24を介して各装置セルに供給される。

#### 【0018】

図1はまた、エッジ終端エリア4全体に分布させたガードリング10とフィールドプレート11とを用いてMOSFETまたはIGBTを如何にして終端し得るかを示す。電位線7がアクティブエリア3のエッジの周囲に集中することを、基板材料の表面に形成したpドープガードリング10を含めることによって、防止することができる。各ガードリング10は、弱くドープされたpn接合を、低濃度でpドープされたガードリング10と、低濃度でnドープされたドリフト領域6との間に形成する。各ガードリング10は、逆バイアス条件下で、アクティブエリア3内の高電荷密度が、終端エリア4を通して減少してゼロになるまで、順次電位が低くなるよう、空乏層を、他のガードリング10を超えて、基板6のエッジに向かって拡大させることにより、基板表面において密集する電界の量を減じる役割を果たす。フィールドプレート11は、表面近くで電位をより均一的に分散させることにより、電位線の集中（「密集」）を回避する役割を果たす。

#### 【0019】

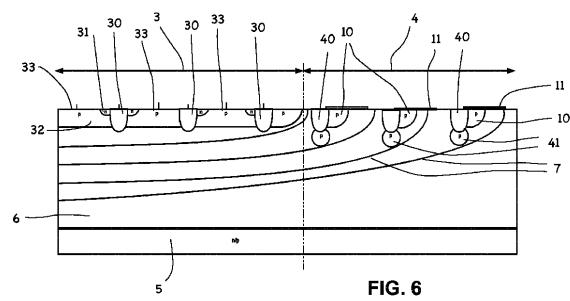

図2は、nチャネルトレンチゲートMOSFETまたはIGBTの断面図を示す。図1に示された装置と同様、この装置のアクティブセルエリア3は、基板6の終端エリア4によって拡大している。終端エリア4は、終端エリア4の表面および表面近くにあるドリフト層材料6を部分的に置換えたものである表面pリング（ガードリング）10を用いる。フィールドプレート11は、pリング10各々のエッジにも加えられる。図1の装置の例と同様、ガードリング10およびフィールドプレート11は、電位線7を偏向させて、終端エリア4の表面領域に電位線が集中するのを防止する役割を果たす。

#### 【0020】

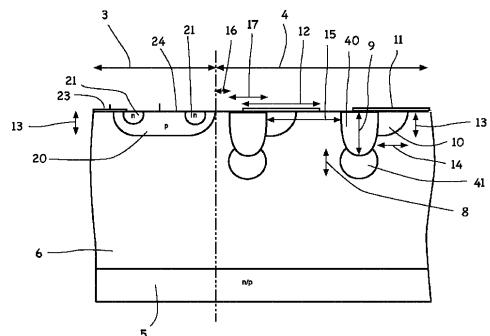

図3および図4はそれぞれ、図1および図2に示されている装置と同様の装置を示すが、図3および図4では、図1および図2の表面pリング10の代わりに終端トレンチ40を用いて終端している。各終端トレンチ40は、酸化シリコン等の誘電材料またはポリシリコン等の導電材料で充填してもよい。pドープ領域41を、各終端トレンチ40の端もしくは先端にまたは端もしくは先端近くに形成して、終端トレンチ40の端の周りの電位線の偏向を改善してもよい。深いまたは埋込みガードリング41とも呼ばれる深いpドープ領域41は、図1および図2を参照しながら説明した表面ガードリング10の有効な代替物として知られている。

#### 【0021】

なお、図1～図4を参照しながら説明した装置は、専用のpn接合がオフ状態で空乏化することによりオフ状態電圧に耐える、空乏モード装置である。言い換えると、この空乏領域が、pドープ領域とnドープ領域を互いに分離する。

#### 【0022】

図5は、本発明のMOSFETの第1の実施形態を示す。低濃度でnドープされた領域6の部分を「ドリフト領域」、「低濃度ドープ領域」または「逆電圧サポート領域」と呼

10

20

30

40

50

ぶ場合がある。最初に基板のnドープ濃度を低くして作ったパワーデバイスの場合、最終的に得られるパワーデバイスのドリフト層6は、製造工程でドープ濃度が修正されなかつた層になるであろう。典型的に、ドリフト層6は常に低いドープ濃度を有する。ここで、ドリフト層6のドープ濃度が実質的に一定であることは、ドープ濃度がドリフト層6全体において実質的に均一であることを意味するが、これは、たとえばエピタキシャル成長プロセスにおける変動が原因で、ドリフト層内のドープ濃度が約1～5倍変動する可能性があることを除外している。最終的なドリフト層の厚みおよびドープ濃度を用途の要求に応じて選択する。ドリフト層6の典型的なドープ濃度は、 $5 \times 10^{12} \text{ cm}^{-3}$  と  $5 \times 10^{14} \text{ cm}^{-3}$  の間である。

## 【0023】

10

しかしながら、本発明の実施はこのような装置に限定される訳ではない。他の可能性は、たとえば、終端を必要とする超接合(super junction)(SJ)または他の種類の装置での使用である。SJ装置では、ドリフト領域は一般的に、交互に置かれた高濃度でドープされたp層とn層に置換えられ、これは、電荷の相互補償において、オフ状態で完全に空乏化することができ装置全体の高電圧をサポートすることができる。

## 【0024】

同様に、図面は1つの特定のドープ方式(たとえばnチャネルMOSFET)を示しているが、当然ながら他の(たとえば逆)ドープ方式を用いることも可能である。

## 【0025】

20

図5および図6は、本発明の原理を利用した終端配置の一例を示す。図5および図6に示される装置のアクティブエリア3は、それぞれ図1および図2または図3および図4のアクティブエリアに対応する。基板6は(n-)ドープされたドリフト層を含む。アクティブセルエリアにおいて、装置は、基板の両側の第1の主面と第2の主面上の主電気コンタクトを含む。基板6は、横方向において(すなわち上記主面に平行な面において)終端エリア4によって囲まれたアクティブセルエリア3を含む。終端エリア4は基板のエッジ(基板の側面)まで延びている。

## 【0026】

一方、終端エリア4において、図5および図6に示される装置は、終端トレンチ40の原理を、埋込みガードリング41および表面ガードリング10の変形と、組合せている。このガードリングは、ドリフト層と異なる導電型を有する。この例では、ガードリングはpドープされている。図5に示す装置例および図6に示す装置例いずれにおいても、終端エリア4は終端トレンチ40と埋込みガードリング41とを含み、これによって、電位線7を、横方向においてアクティブエリア3から外側に向かう方向に導くことで、第1の終端効果をもたらす。各終端トレンチ40には、外側に隣接している表面ガードリング10がある。この表面ガードリング10は、終端トレンチ40の外側に接することにより、電位線7を導く。そうでなければこの電位線7は図3および図4に示されるように終端トレンチの周りでカーブし、各終端トレンチ40の外側近くにおいて局所的に集中する電位線7を形成してこれらの電位線をさらに終端トレンチ40の下にpドープ埋込みガードリング41が存在していることで、電界の一部を装置のシリコン内に放出し、それによって耐圧が増加する。終端トレンチ40は、たとえば酸化物またはポリシリコンで充填してもよい。各終端トレンチ40に隣接する終端エリア4の表面は、表面のpリング10を終端トレンチ40の外側に対して整列させることにより、高電界から保護される状態に保たれる。表面をさらに、各表面pリング(10)のエッジにフィールドプレート(たとえば誘電酸化物)を形成することによって保護してもよい。

30

## 【0027】

40

終端トレンチ40は、その埋込みpリング41および表面pリング10(第2導電型のリング)とともに、自己整合方式で作ってもよい。nドープ基板6を設けてもよい。たとえば、最初に表面pリング10を基板6に(たとえば注入と拡散によって)形成し、次に終端トレンチ40を、エッチングするか、そうでなければ、終端トレンチのうちの1つの

50

外側のエッジが（アクティブセルエリア3から外側方向にあるエッジ、すなわち基板エッジ側）接触している表面pリングの内側部分（アクティブセルエリア3側）と交差するよう、形成してもよい。終端トレンチ40を、従来のやり方で、基板材料を除去することによって形成してもよい。終端トレンチ40を形成したら、終端トレンチ40の下に、埋込みpリング41を、各終端トレンチ40の底部に隣接する領域41内の基板ボディに対する注入（ドーピング）によって形成してもよい。有利なのは、必要なプロセス工程の数および／または必要なマスクの数が、終端エリア4の表面pリング10と、pウェルボディ20またはボディ32を、同じマスクを用い同じドーピングプロセスで形成することで、減じられることである。よって、図5に示される装置の例の場合、同一のマスクとプロセスを、終端エリア4内の表面pリング10にのみ使用するのではなく、アクティブエリア内の装置セルボディ（pウェル）領域20にも使用するように、有利に製造方法を構成すればよい。加えて、図6に示される装置の例の製造プロセスにおいて、1つのマスクおよび／またはプロセスを、終端エリア4の表面pリング10とアクティブエリア3のpボディ層32の形成に、有利に使用してもよい。

#### 【0028】

表面フィールドプレート11も形成してもよい。表面フィールドプレート11は、各終端トレンチ40の一部または全体を覆うとともにこのトレンチに隣接する表面ガードリング10を覆い、終端トレンチ40を分離するドリフト領域6（nドープ領域、すなわち第1導電型と異なる第2導電型）の表面上で、表面がガードリング10を超えて延在している。終端エリア4上の電界分布は、終端トレンチ40、表面pリング10、および埋込みpリング41の寸法と間隔を適切に選択することによって制御してもよい。

#### 【0029】

図7は、終端トレンチ40、埋込みpリング41、表面pリング10、およびフィールドプレート11のいくつかの寸法の例を示す。図7には2つの終端トレンチ40しか示されていないが、終端エリア4全体に分布している終端トレンチの数は遥かに多く、たとえば15または20以上である場合があることが、理解されるはずである。

#### 【0030】

一例として、アクティブエリア3のエッジと第1の終端トレンチ40との間の距離16は、たとえば5μmと10μmの間（たとえば7μm）であってもよい。メサ幅15（すなわち隣合う終端トレンチ40間の分離距離）は、たとえば7～20μmであってもよく、アクティブエリア3から離れる方向に増していくてもよい。トレンチ深さ9は、4μmと7μmの間（たとえば5.2μm）であってもよく、トレンチ幅17は、たとえば製造プロセスが許容する最小幅と4μmの間（たとえば1.2μm）であってもよい。埋込みpリング41のピークドープ濃度は、 $10^{16} \text{ cm}^{-3}$ と $10^{18} \text{ cm}^{-3}$ の間（たとえば $10^{17} \text{ cm}^{-3}$ ）であってもよく、ドープ深さ2μmの場所におけるドープ濃度が $10^{15} \text{ cm}^{-3}$ と $10^{16} \text{ cm}^{-3}$ の間（たとえば $5 \times 10^{15} \text{ cm}^{-3}$ ）であってもよい。深いpリング（埋込みガードリング）41の高さ8は、2μmと5μmの間（たとえば3～4μm）であってもよい。表面pリング（ガードリング）10の横方向の範囲は1μmと5μmの間であってもよく、好ましくは1μmと2μmの間、たとえば1.5μmであってもよい。一方、表面pリング（ガードリング）10の縦方向の範囲（深さ）は、アクティブエリア3内の装置セルのpウェル（ボディ領域）20の深さと実質的に同一であることが好ましい。同様に、表面pリング（ガードリング）10のドーピング濃度は、アクティブエリア3内の装置セルのpウェル20のドーピング濃度と実質的に同一であることが好ましい。これらの好ましい寸法を有する装置の場合、フィールドプレートの幅12は、たとえば3μmと8μmの間であってもよく、より好ましくは4μmと6μmの間（たとえば4.5μm）であってもよい。ガードリング／トレンチ／フィールドプレート終端を、注入、拡散、エッチング、および再充填等の標準的な装置処理技術を用いて作ってもよい。表面ガードリング10、深いガードリング41、フィールドプレート11、および酸化物／ポリシリコンで充填されたトレンチ40の寸法と距離を、必要な逆耐圧に適したものとなるように変化させてもよい。

10

20

30

40

50

## 【0031】

表面のリング終端および深いリング終端と、誘電ノトレーニング終端と、フィールドプレートとを組合わせることにより、5 kV、6 kVまたはそれ以上の逆電圧に耐えることが要求されることがある高電圧装置における有効な接合終端を必要とする終端エリアの面積を、大幅に減じる。電圧がより低い場合（たとえば1.3 kV）、本明細書に記載の終端により、終端エリアの径方向の最小範囲が30%以上減じられることがわかっている。

## 【0032】

図8は、終端トレーニング40およびフィールドプレート11を含む終端エリアを簡略化した例の概略平面図を示す。見えていないのは、表面ガードリング10（フィールドプレート11によって遮られている）と埋込みガードリング41（終端トレーニング40の下にある）である。上記終端配置を現実的に実施する場合、終端構造体（終端トレーニング40、埋込みガードリング41、表面ガードリング10、およびフィールドプレート11）の数は、図8に示される2個よりも遥かに多いであろう。

10

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図7】

FIG. 7

【図6】

FIG. 6

【図8】

FIG. 8

---

フロントページの続き

(51)Int.Cl.

F I

|        |       |      |

|--------|-------|------|

| H 01 L | 29/06 | 301G |

| H 01 L | 29/06 | 301V |

(72)発明者 ウドレア，フローリン

イギリス、シィ・ビィ・2 0・アール・ビィ ケンブリッジ、バブラハム・ロード、23

(72)発明者 ニストル，ユリアン

スイス、ツェー・ハー - 8166 ニーダーベニンゲン、マンムートベーク、3

(72)発明者 ラヒモ，ムナフ

スイス、ツェー・ハー - 5619 ウエツビル、バッハベーク、10

(72)発明者 コルバーシェ，キアラ

スイス、ツェー・ハー - 8962 ベルクディーティコン、エアレンシュトラーセ、7

審査官 恩田 和彦

(56)参考文献 特開2009-088345 (JP, A)

米国特許出願公開第2001/0035561 (US, A1)

特開2008-103683 (JP, A)

特開2007-173319 (JP, A)

特開2007-109712 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 06

H 01 L 21 / 336

H 01 L 29 / 78