(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5111954号

(P5111954)

(45) 発行日 平成25年1月9日(2013.1.9)

(24) 登録日 平成24年10月19日(2012.10.19)

(51) Int.Cl.

F 1

H01L 21/683 (2006.01)

H01L 21/68

R

H02N 13/00 (2006.01)

H02N 13/00

D

B23Q 3/15 (2006.01)

B23Q 3/15

D

請求項の数 5 (全 13 頁)

(21) 出願番号

特願2007-165465 (P2007-165465)

(22) 出願日

平成19年6月22日 (2007.6.22)

(65) 公開番号

特開2009-4649 (P2009-4649A)

(43) 公開日

平成21年1月8日 (2009.1.8)

審査請求日

平成22年3月16日 (2010.3.16)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 宮澤 昌邦

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 大沼 崇

長野県長野市小島田町80番地 新光電氣

工業株式会社内

(72) 発明者 小野 雅史

長野県長野市小島田町80番地 新光電氣

工業株式会社内

最終頁に続く

(54) 【発明の名称】 静電チャック及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

アルミナと、第1のフラックスと、を含有したセラミック基体と、

前記セラミック基体に内蔵された静電電極と、

前記セラミック基体に内蔵された、アルミナを主成分とし第2のフラックスを含むセラ

ミック材と、を備え、

前記セラミック材は、前記セラミック基体と前記静電電極の両面との間に、前記セラミ

ック基体及び前記静電電極の両面と接触するように配置され、

前記セラミック材の前記静電電極と接触する部分を除く外周部分及び前記静電電極は前

記セラミック基体に覆われ、

前記セラミック材に含まれる前記第2のフラックスの含有率は、前記セラミック基体に

含まれる前記第1のフラックスの含有率よりも高いことを特徴とする静電チャック。

## 【請求項 2】

前記第1のフラックスの含有率は、前記第2のフラックスを含有した前記セラミック材

に比べて、前記セラミック基体がプラズマによる損傷を受けにくい値であることを特徴と

する請求項1記載の静電チャック。

## 【請求項 3】

前記第1のフラックス及び前記第2のフラックスは、酸化珪素、炭酸カルシウム、及び

酸化マグネシウムのうち、少なくともいずれか1種を含むことを特徴とする請求項1又は

2記載の静電チャック。

**【請求項 4】**

前記セラミック基体に含まれる前記第1のフラックスの含有率は、1重量%以下であることを特徴とする請求項1ないし3のうち、いずれか一項記載の静電チャック。

**【請求項 5】**

積層された複数のグリーンシートを焼成することにより形成されるセラミック基体と、前記セラミック基体に内蔵され、導電性ペーストを焼成することにより形成される静電電極と、を備え、

前記セラミック基体に含まれるフラックスの含有率を、プラズマにより前記セラミック基体が損傷を受けにくい値とした静電チャックの製造方法であって、

前記複数のグリーンシートは、少なくとも第1のグリーンシートと、第2のグリーンシートとを有し、10

前記第1及び第2のグリーンシートは、アルミナと、第1のフラックスと、を含み、

前記第1のグリーンシートに、アルミナを主成分とし第2のフラックスを含んだ第1のアルミナペーストを形成する第1のアルミナペースト形成工程と、

前記第1のアルミナペーストに、前記導電性ペーストを形成する導電性ペースト形成工程と、

前記導電性ペーストと対向する部分の前記第2のグリーンシートに、アルミナを主成分とし前記第2のフラックスを含んだ第2のアルミナペーストを形成する第2のアルミナペースト形成工程と、20

前記第2のアルミナペーストと前記導電性ペーストとが接触するように、前記第1のアルミナペースト及び前記導電性ペーストが形成された前記第1のグリーンシートと、前記第2のアルミナペーストが形成された前記第2のグリーンシートとを積層させる積層工程と、

前記積層工程後に、前記第1のアルミナペースト及び前記導電性ペーストが形成された前記第1のグリーンシートと、前記第2のアルミナペーストが形成された前記第2のグリーンシートとが積層された構造体を焼成する焼成工程と、を含み、

前記焼成工程では、前記第1のアルミナペースト及び前記第2のアルミナペーストの前記導電性ペーストと接触する部分を除く外周部分及び前記導電性ペーストが前記第1のグリーンシート又は前記第2のグリーンシートに覆われ、

前記第1及び第2のアルミナペーストに含まれる前記第2のフラックスの含有率を前記第1及び第2のグリーンシートに含まれる前記第1のフラックスの含有率よりも高くしたことを特徴とする静電チャックの製造方法。30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、静電チャック及びその製造方法に係り、特にセラミック基体に含まれるフラックスの含有率をプラズマによりセラミック基体が損傷を受けにくい値とした静電チャック及びその製造方法に関する。

**【背景技術】****【0002】**

従来、ICやLSI等の半導体装置を製造する際に使用される成膜装置（例えば、CVD装置やPVD装置等）やプラズマエッティング装置は、半導体基板（具体的には、例えば、シリコンウエハ）を処理室内に精度良く保持するためのステージを有する。このようなステージとして、例えば、静電チャックが適用されている。静電チャックは、セラミック及びフラックスよりなるセラミック基体と、セラミック基体に内蔵された静電電極とを有する。

**【0003】**

近年、成膜装置として高密度プラズマを用いた成膜装置（例えば、ECR（Electric Cyclotron Resonance）装置）及びプラズマエッティング装置において、静電チャックを使用した場合、プラズマにより、セラミック基体に含まれるフラックスがエッティングされてセ40

50

セラミック基体が損傷してしまうという問題があった。

【0004】

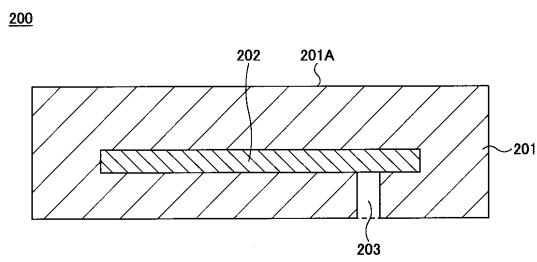

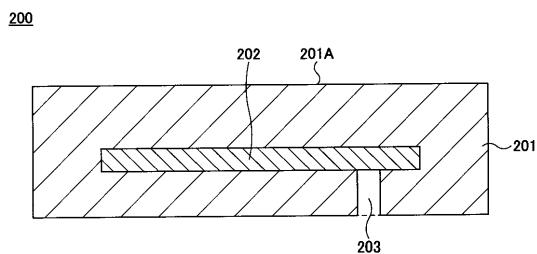

このような問題を解決可能な静電チャックとして、図1に示すような静電チャック200がある。

【0005】

図1は、従来の静電チャックの断面図である。

【0006】

図1を参照するに、従来の静電チャック200は、セラミック基体201と、静電電極202とを有する。セラミック基体201は、静電電極202を内蔵するためのものである。セラミック基体201は、半導体基板が載置される基板載置面201Aと、静電電極202を露出する開口部203とを有する。開口部203は、図示していない給電端子を挿入するための挿入口である。給電端子(図示せず)は、静電電極202に給電するための端子である。セラミック基体201は、アルミナの含有率が99重量% (残りの1重量%以下がフラックス)以上のグリーンシートを積層し、焼成することで形成する。セラミック基体201を形成する際に用いられるグリーンシートは、一般的なグリーンシートよりもアルミナの含有率の高いグリーンシートである。一般的なグリーンシートのアルミナの含有率は、96重量%程度である。

【0007】

このように、アルミナの含有率の高いグリーンシート(アルミナの含有率が99重量%以上)を用いてセラミック基体201を形成することにより、セラミック基体201に含まれるフラックスの含有率が低くなるため、セラミック基体201がプラズマにより損傷することを抑制できる。

【0008】

静電電極202は、セラミック基体201に内蔵されている。静電電極202は、静電力によりセラミック基体201の基板載置面201Aに半導体基板を固定するための電極である。静電電極202は、導電性ペースト(例えば、Wペースト)を焼成することにより形成できる。

【0009】

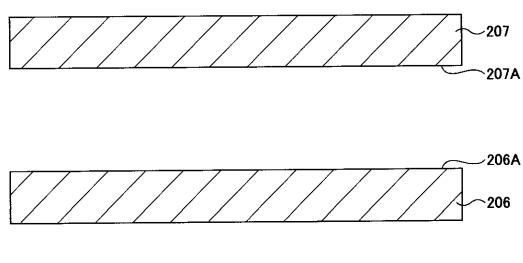

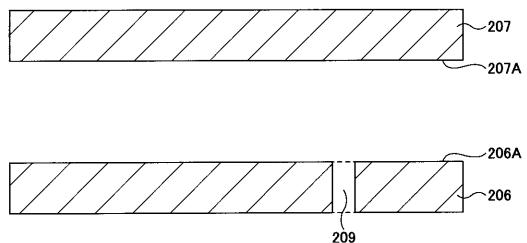

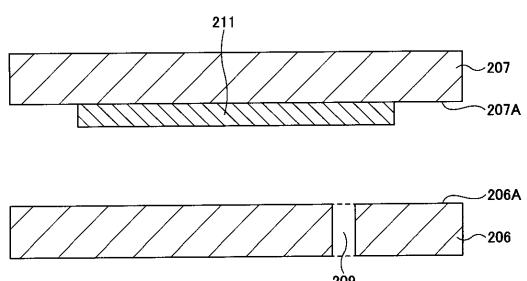

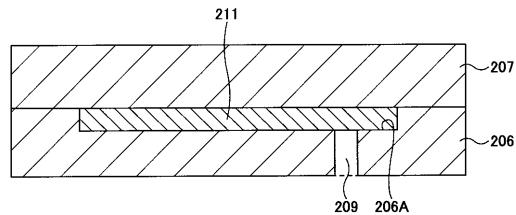

図2～図6は、従来の静電チャックの製造工程を示す図である。図2～図6において、図1に示す従来の静電チャック200と同一構成部分には同一符号を付す。

【0010】

図2～図6を参照して、従来の静電チャック200の製造方法について説明する。始めに、図2に示す工程では、アルミナの含有率が99重量% (残りの1重量%以下がフラックス)以上のグリーンシート206, 207を準備する。

【0011】

次いで、図3に示す工程では、グリーンシート206に貫通穴209を形成する。貫通穴209は、後述する図5に示す構造体を焼成することにより、図1に示す開口部203となる穴である。

【0012】

次いで、図4に示す工程では、グリーンシート207の面207Aに、導電性ペースト211(例えば、Wペースト)を形成する。次いで、図5に示す工程では、グリーンシート206の面206Aが導電性ペースト211と接触するように、グリーンシート206上にグリーンシート207を積層させる。

【0013】

次いで、図6に示す工程では、図5に示す構造体を焼成する。これにより、セラミック基体201と、静電電極202とを有した静電チャック200が製造される(例えば、特許文献1参照。)。

【特許文献1】特開平11-312729号公報

【発明の開示】

【発明が解決しようとする課題】

10

20

30

40

50

**【0014】**

しかしながら、従来の静電チャック200では、アルミナ含有率の高いグリーンシート206, 207を用いてセラミック基体201を形成していたため、グリーンシート206, 207に含まれるフラックスの含有率が低くなり、セラミック基体201に含まれるフラックスの含有量が少なくなってしまう。これにより、セラミック基体201と静電電極202との接合部におけるフラックスによるアンカー効果が小さくなるため、セラミック基体201と静電電極202との間の接合強度が低下するという問題があった。このような問題が発生した場合、セラミック基体201から静電電極202が剥がれる虞がある。

**【0015】**

そこで本発明は、プラズマによる損傷を受けにくいセラミック基体と静電電極との間の接合強度を向上させることのできる静電チャック及びその製造方法を提供することを目的とする。

**【課題を解決するための手段】****【0016】**

本発明の一観点によれば、アルミナと、第1のフラックスと、を含有したセラミック基体と、前記セラミック基体に内蔵された静電電極と、前記セラミック基体に内蔵された、アルミナを主成分とし第2のフラックスを含むセラミック材と、を備え、前記セラミック材は、前記セラミック基体と前記静電電極の両面との間に、前記セラミック基体及び前記静電電極の両面と接触するように配置され、前記セラミック材の前記静電電極と接触する部分を除く外周部分及び前記静電電極は前記セラミック基体に覆われ、前記セラミック材に含まれる前記第2のフラックスの含有率は、前記セラミック基体に含まれる前記第1のフラックスの含有率よりも高いことを特徴とする静電チャックが提供される。

**【0017】**

本発明によれば、セラミック基体と静電電極との間に、第2のフラックスを含み、セラミック基体及び静電電極と接触するセラミック材を設けると共に、セラミック材に含まれる第2のフラックスの含有率をセラミック基体に含まれる第1のフラックスの含有率よりも高くすることにより、プラズマによる損傷を受けにくいセラミック基体を用いた場合であっても、セラミック材と接触する部分のセラミック基体及び静電電極に第2のフラックスが移動するため、セラミック材とセラミック基体及び静電電極との間において十分なアンカー効果を発生させることが可能となる。これにより、セラミック基体と静電電極との間の接合強度を向上させることができる。

**【0018】**

本発明の他の観点によれば、積層された複数のグリーンシートを焼成することにより形成されるセラミック基体と、前記セラミック基体に内蔵され、導電性ペーストを焼成することにより形成される静電電極と、を備え、前記セラミック基体に含まれるフラックスの含有率を、プラズマにより前記セラミック基体が損傷を受けにくい値とした静電チャックの製造方法であって、前記複数のグリーンシートは、少なくとも第1のグリーンシートと、第2のグリーンシートとを有し、前記第1及び第2のグリーンシートは、アルミナと、第1のフラックスと、を含み、前記第1のグリーンシートに、アルミナを主成分とし第2のフラックスを含んだ第1のアルミナペーストを形成する第1のアルミナペースト形成工程と、前記第1のアルミナペーストに、前記導電性ペーストを形成する導電性ペースト形成工程と、前記導電性ペーストと対向する部分の前記第2のグリーンシートに、アルミナを主成分とし前記第2のフラックスを含んだ第2のアルミナペーストを形成する第2のアルミナペースト形成工程と、前記第2のアルミナペーストと前記導電性ペーストとが接触するように、前記第1のアルミナペースト及び前記導電性ペーストが形成された前記第1のグリーンシートと、前記第2のアルミナペーストが形成された前記第2のグリーンシートとを積層させる積層工程と、前記積層工程後に、前記第1のアルミナペースト及び前記導電性ペーストが形成された前記第1のグリーンシートと、前記第2のアルミナペーストが形成された前記第2のグリーンシートとが積層された構造体を焼成する焼成工程と、を

10

20

30

40

50

含み、前記焼成工程では、前記第1のアルミナペースト及び前記第2のアルミナペーストの前記導電性ペーストと接触する部分を除く外周部分及び前記導電性ペーストが前記第1のグリーンシート又は前記第2のグリーンシートに覆われ、前記第1及び第2のアルミナペーストに含まれる前記第2のフラックスの含有率を前記第1及び第2のグリーンシートに含まれる前記第1のフラックスの含有率よりも高くしたことを特徴とする静電チャックの製造方法が提供される。

### 【0019】

本発明によれば、第1のグリーンシートに設けられた第1のアルミナペーストに導電性ペーストを形成し、第2のアルミナペーストと導電性ペーストとが接触するように、第1のアルミナペースト及び導電性ペーストが形成された第1のグリーンシートと、第2のアルミナペーストが形成された第2のグリーンシートとを積層し、その後、積層された構造体を焼成すると共に、第1及び第2のアルミナペーストに含まれる第2のフラックスの含有率を第1及び第2のグリーンシートに含まれる第1のフラックスの含有率よりも高くすることにより、第1のアルミナペーストと第1のグリーンシート及び導電性ペーストとの間、及び第2のアルミナペーストと第2のグリーンシート及び導電性ペーストとの間において十分なアンカー効果を発生させることができるとなるため、プラズマによる損傷を受けにくいセラミック基体と静電電極との間の接合強度を向上させることができる。

### 【発明の効果】

### 【0020】

本発明によれば、プラズマによる損傷を受けにくいセラミック基体と静電電極との間の接合強度を向上させることができる。

### 【発明を実施するための最良の形態】

### 【0021】

次に、図面に基づいて本発明の実施の形態について説明する。

### 【0022】

#### (実施の形態)

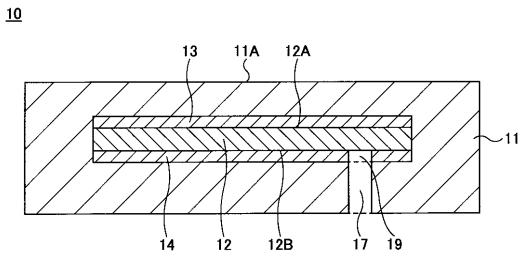

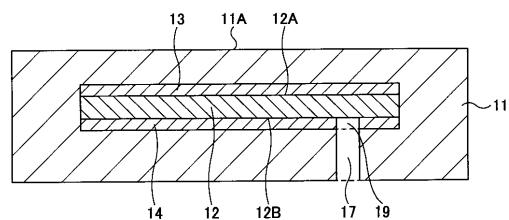

図7は、本発明の実施の形態に係る静電チャックの断面図である。

### 【0023】

図7を参照するに、本実施の形態の静電チャック10は、セラミック基体11と、静電電極12と、セラミック材13, 14とを有する。

### 【0024】

セラミック基体11は、基板(例えば、半導体基板や液晶パネル等)を載置する基板載置面11Aと、図示していない給電端子(静電電極12に給電するための端子)の一部が挿入される開口部17とを有する。セラミック基体11は、静電電極12及びセラミック材13, 14を内蔵している。セラミック基体11は、例えば、アルミナ及び第1のフラックス等から構成することができる。第1のフラックスは、例えば、酸化珪素、炭酸カルシウム、酸化マグネシウム等により構成されている。第1のフラックスの含有率は、セラミック基体がプラズマによる損傷を受けにくい値とされている。セラミック基体11に含まれるアルミナの含有率は、99重量%以上(第1のフラックスの含有率は0重量%よりも高く1重量%以下)となるように設定されている。

### 【0025】

このように、アルミナの含有率が99重量%以上とされたセラミック基体11を用いることにより、セラミック基体11に含まれるフラックスの含有率がかなり低くなる(第1のフラックスの含有率は0重量%よりも高く1重量%以下)ため、プラズマ雰囲気で静電チャック10を使用した場合、プラズマによりセラミック基体11が損傷することを防止できる。

### 【0026】

静電電極12は、単極電極であり、セラミック基体11に内蔵されている。静電電極12の面12Aには、セラミック材13が設けられている。また、静電電極12の面12B

10

20

30

40

50

には、セラミック材 14 が設けられている。例えば、基板載置面 11A に載置された基板（図示せず）がマイナスに帯電させられた際、静電電極 12 は、プラスの電位に帯電させることで、基板載置面 11A に基板を固定するための電極である。静電電極 12 は、例えば、導電性ペースト（具体的には、W ペースト）を焼成することにより形成できる。静電電極 12 の厚さは、例えば、20 μm とすることができます。

#### 【0027】

セラミック材 13 は、静電電極 12 の面 12A を覆うように設けられている。セラミック材 13 は、基板載置面 11A 側に位置する部分のセラミック基体 11 と、静電電極 12 との間に配置されている。セラミック材 13 は、基板載置面 11A 側に位置する部分のセラミック基体 11 及び静電電極 12 と接触している。

10

#### 【0028】

セラミック材 13 は、例えば、アルミナ及び第 2 のフラックス等から構成することができる。セラミック材 13 に含まれる第 2 のフラックスの含有率は、セラミック基体 11 に含まれる第 1 のフラックスの含有率よりも高くなるように設定されている。具体的には、第 1 のフラックスの含有率が 0 重量% よりも高く 1 重量% 以下の場合、第 2 のフラックスの含有率は、例えば、4 重量% 以上 10 重量% 以下とすることができます。

#### 【0029】

このように、基板載置面 11A 側に位置する部分のセラミック基体 11 と静電電極 12 の面 12A との間に、第 2 のフラックスを含み、セラミック基体 11 及び静電電極 12 と接触するセラミック材 13 を設けると共に、セラミック材 13 に含まれる第 2 のフラックスの含有率をセラミック基体 11 に含まれる第 1 のフラックスの含有率よりも高くすることにより、セラミック材 13 に含まれる第 2 のフラックスがセラミック基体 11 及び静電電極 12 に移動して、セラミック基体 11 及び静電電極 12 とセラミック材 13 との間ににおいて十分なアンカー効果を発生させることができるとなる。これにより、セラミック基体 11 と静電電極 12 との間の接合強度を向上させることができる。セラミック材 13 の厚さは、例えば、10 μm とすることができます。

20

#### 【0030】

セラミック材 14 は、静電電極 12 の面 12B を覆うように設けられている。セラミック材 14 は、基板載置面 11A とは反対側に位置する部分のセラミック基体 11 と、静電電極 12 との間に配置されている。セラミック材 14 は、基板載置面 11A とは反対側に位置する部分のセラミック基体 11 及び静電電極 12 と接触している。セラミック材 14 は、静電電極 12 の面 12B の一部を露出する開口部 19 を有する。開口部 19 は、セラミック基体 11 に形成された開口部 17 と対向するように配置されている。

30

#### 【0031】

セラミック材 14 は、例えば、アルミナ及び第 2 のフラックス等から構成することができる。セラミック材 14 に含まれる第 2 のフラックスの含有率は、セラミック基体 11 に含まれる第 1 のフラックスの含有率よりも高くなるように設定されている。具体的には、第 1 のフラックスの含有率が 0 重量% よりも高く 1 重量% 以下の場合、第 2 のフラックスの含有率は、例えば、4 重量% 以上 10 重量% 以下とすることができます。

#### 【0032】

40

このように、基板載置面 11A とは反対側に位置する部分のセラミック基体 11 と静電電極 12 の面 12B との間に、第 2 のフラックスを含み、セラミック基体 11 及び静電電極 12 と接触するセラミック材 14 を設けると共に、セラミック材 14 に含まれる第 2 のフラックスの含有率をセラミック基体 11 に含まれる第 1 のフラックスの含有率よりも高くすることにより、セラミック材 14 に含まれる第 2 のフラックスがセラミック基体 11 及び静電電極 12 に移動して、セラミック基体 11 及び静電電極 12 とセラミック材 14 との間ににおいて十分なアンカー効果を発生させることができるとなる。これにより、セラミック基体 11 と静電電極 12 との間の接合強度を向上させることができる。セラミック材 14 の厚さは、例えば、10 μm とすることができます。

#### 【0033】

50

本実施の形態の静電チャックによれば、プラズマによる損傷を受けにくいセラミック基体11と静電電極12との間に、第2のフラックスを含み、セラミック基体11及び静電電極12と接触するセラミック材13，14を設けると共に、セラミック材13，14に含まれる第2のフラックスの含有率（具体的には、4重量%以上10重量%以下）をセラミック基体11に含まれる第1のフラックスの含有率（具体的には、0重量%よりも高く1重量%以下）よりも高くすることにより、セラミック材13，14とセラミック基体11及び静電電極12との間ににおいて十分なアンカー効果を発生させることが可能となるため、プラズマによる損傷を受けにくいセラミック基体11と静電電極12との間の接合強度を向上させることができる。

## 【0034】

10

また、アルミナが含まれたセラミック基体11を用いる場合において、セラミック材13，14にアルミナを含ませることにより、セラミック基体11とセラミック材13，14との密着性を向上させることができる。

## 【0035】

なお、セラミック基体11に含まれる第1のフラックスの含有率よりも高い値の範囲内で、セラミック材13に含まれる第2のフラックスの含有率とセラミック材14に含まれる第2のフラックスの含有率とを異なる値としてもよい。

## 【0036】

また、第1及び第2のフラックスは、酸化珪素、炭酸カルシウム、及び酸化マグネシウムのうち、少なくともいずれか一種を含んでおればよい。

20

## 【0037】

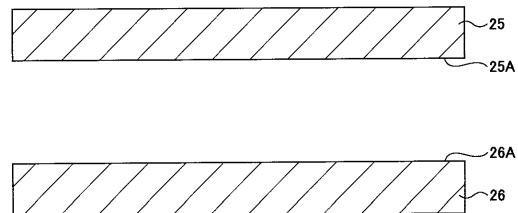

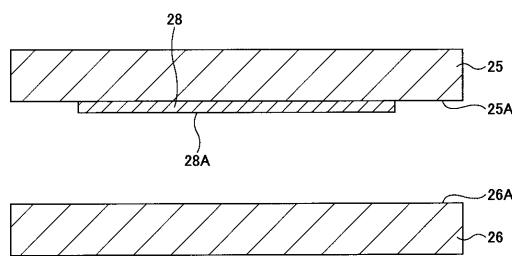

図8～図14は、本発明の実施の形態に係る静電チャックの製造工程を示す図である。図8～図14において、本実施の形態の静電チャック10と同一構成部分には同一符号を付す。

## 【0038】

図8～図14を参照して、本実施の形態の静電チャック10の製造方法について説明する。始めに、図8に示す工程では、第1のグリーンシート25と、第2のグリーンシート26とを準備する。第1及び第2のグリーンシート25，26は、アルミナ、第1のフラックス、バインダー、及び可塑材等から構成されている。第1及び第2のグリーンシート25，26に含まれるアルミナの含有率は、99重量%以上（第1のフラックスの含有率が1重量%以下）とされている。第1及び第2のグリーンシート25，26に含まれる第1のフラックスは、酸化珪素、炭酸カルシウム、及び酸化マグネシウム等により構成されている。バインダーは、有機物の接合剤である。可塑材は、第1及び第2のグリーンシート25，26に柔軟性を持たせるための材料である。可塑材としては、例えば、ポリエチレングリコールやジブチルフタレート等を用いることができる。

30

## 【0039】

第1のグリーンシート25の厚さは、例えば、1.2mmとすることができる。また、第2のグリーンシート26の厚さは、例えば、1.2mmとすることができる。第1及び第2のグリーンシート25，26は、所望の厚さとなるように、それぞれ複数のグリーンシートを積層させた構成としてもよい。第1及び第2のグリーンシート25，26は、先に説明したセラミック基体11（図2参照）の母材である。第1及び第2のグリーンシート25，26は、焼成されることにより、セラミック基体11となる。

40

## 【0040】

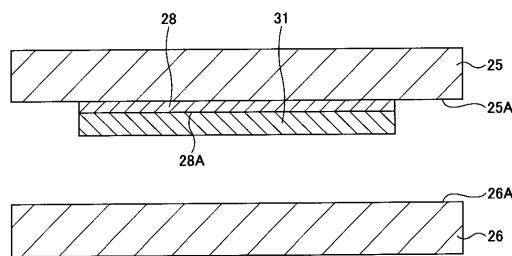

次いで、図9に示す工程では、第1のグリーンシート25の面25Aに、第1のアルミナペースト28を形成する（第1のアルミナペースト形成工程）。具体的には、印刷法により、第1のアルミナペースト28を形成する。

## 【0041】

第1のアルミナペースト28は、アルミナと、第2のフラックスとを含んだ構成とされている。第1のアルミナペースト28に含まれる第2のフラックスの含有率は、第1及び第2のグリーンシート25，26に含まれる第1のフラックスの含有率よりも高くなるよ

50

うに設定されている。具体的には、第1のフラックスの含有率が0%重量よりも高く1%重量以下の場合、第2のフラックスの含有率は、例えば、4重量%以上10重量%以下とすることができます。第1のアルミナペースト28の厚さは、例えば、10μmとすることができます。第1のアルミナペースト28は、先に説明したセラミック材13(図7参照)の母材となるものである。第1のアルミナペースト28は、焼成されることにより、セラミック材13となる。

#### 【0042】

次いで、図10に示す工程では、第1のアルミナペースト28の面28Aを覆うように、導電性ペースト31を形成する(導電性ペースト形成工程)。具体的には、印刷法により、導電性ペースト31を形成する。導電性ペースト31としては、例えば、Wペーストを用いることができる。導電性ペースト31の厚さは、例えば、20μmとすることができます。導電性ペースト31は、焼成することにより、先に説明した静電電極12(図7参照)となる。

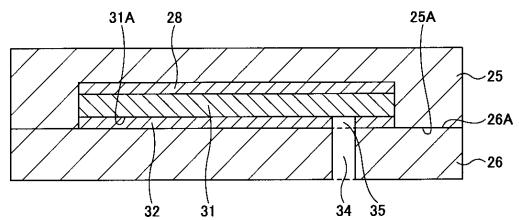

#### 【0043】

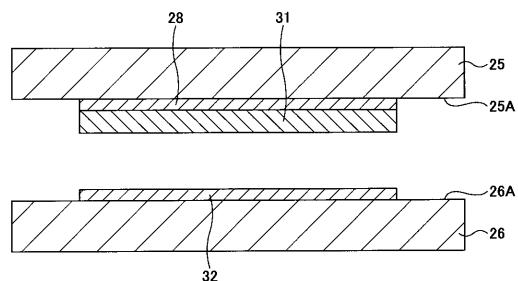

次いで、図11に示す工程では、第2のグリーンシート26の面26Aに、第2のアルミナペースト32を形成する(第2のアルミナペースト形成工程)。具体的には、印刷法により、第2のアルミナペースト32を形成する

第2のアルミナペースト32は、アルミナと、第2のフラックスとを含んだ構成とされている。第2のアルミナペースト32に含まれる第2のフラックスの含有率は、第1及び第2のグリーンシート25, 26に含まれる第1のフラックスの含有率よりも高くなるように設定されている。具体的には、第1のフラックスの含有率が0%重量よりも高く1%重量以下の場合、第2のフラックスの含有率は、例えば、4重量%以上10重量%以下とすることができます。第2のアルミナペースト32の厚さは、例えば、10μmとすることができます。第2のアルミナペースト32は、先に説明したセラミック材14(図7参照)の母材となるものである。第2のアルミナペースト32は、焼成されることにより、セラミック材14となる。

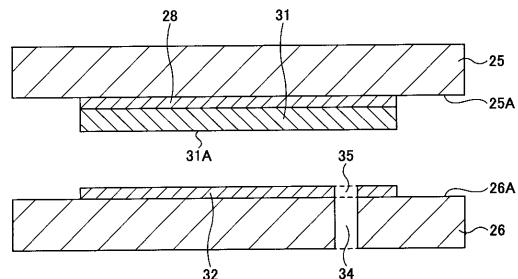

#### 【0044】

次いで、図12に示す工程では、第2のグリーンシート26に貫通穴34と、第2のアルミナペースト32に貫通穴35とを同時に形成する。貫通穴34は、焼成されることにより、先に説明した開口部17(図2参照)となるものである。また、貫通穴35は、焼成されることにより、先に説明した開口部19(図2参照)となるものである。

#### 【0045】

次いで、図13に示す工程では、第2のアルミナペースト32と導電性ペースト31の面31Aとが接触するように、第1のアルミナペースト28及び導電性ペースト31が形成された第1のグリーンシート25と、第2のアルミナペースト32が形成された第2のグリーンシート26とを圧力を印加しながら積層する(積層工程)。

#### 【0046】

次いで、図14に示す工程では、図13に示す構造体を焼成する(焼成工程)。これにより、セラミック基体11と、静電電極12と、セラミック材13, 14とを備えた静電チャック10が製造される。焼成温度は、例えば、1550、焼成時間は、例えば、60時間とすることができます。

#### 【0047】

本実施の形態の静電チャックの製造方法によれば、第1のグリーンシート25に設けられた第1のアルミナペースト28に導電性ペースト31を形成し、第2のアルミナペースト32と導電性ペースト31が接触するように、第1のアルミナペースト28及び導電性ペースト31が形成された第1のグリーンシート25と、第2のアルミナペースト32が形成された第2のグリーンシート26とを積層し、その後、積層された構造体を焼成すると共に、第1のアルミナペースト28に含まれる第2のフラックスの含有率及び第2のアルミナペースト32に含まれる第2のフラックスの含有率を第1及び第2のグリーンシート25, 26に含まれる第1のフラックスの含有率よりも高くすることにより、第1の

10

20

30

40

50

アルミナペースト 28 と第1のグリーンシート 25 及び導電性ペースト 31との間、及び第2のアルミナペースト 32 と第2のグリーンシート 26 及び導電性ペースト 31との間ににおいて十分なアンカー効果を発生させることが可能となるため、プラズマによる損傷を受けにくいセラミック基体 11 と静電電極 12との間の接合強度を向上させることができる。

#### 【0048】

なお、第1のアルミナペースト 28 に含まれる第2のフラックスの含有率と第2のアルミナペースト 32 に含まれる第2のフラックスの含有率とを異ならせててもよい。

#### 【0049】

以上、本発明の好ましい実施の形態について詳述したが、本発明はかかる特定の実施の形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。 10

#### 【産業上の利用可能性】

#### 【0050】

本発明は、セラミック基体に含まれるフラックスの含有率を、プラズマによりセラミック基体が損傷を受けにくいような値とした静電チャック及びその製造方法に適用できる。

#### 【図面の簡単な説明】

#### 【0051】

【図1】従来の静電チャックの断面図である。

【図2】従来の静電チャックの製造工程を示す図（その1）である。 20

【図3】従来の静電チャックの製造工程を示す図（その2）である。

【図4】従来の静電チャックの製造工程を示す図（その3）である。

【図5】従来の静電チャックの製造工程を示す図（その4）である。

【図6】従来の静電チャックの製造工程を示す図（その5）である。

【図7】本発明の実施の形態に係る静電チャックの断面図である。

【図8】本発明の実施の形態に係る静電チャックの製造工程を示す図（その1）である。

【図9】本発明の実施の形態に係る静電チャックの製造工程を示す図（その2）である。

【図10】本発明の実施の形態に係る静電チャックの製造工程を示す図（その3）である。

。

【図11】本発明の実施の形態に係る静電チャックの製造工程を示す図（その4）である 30

。

【図12】本発明の実施の形態に係る静電チャックの製造工程を示す図（その5）である。

。

【図13】本発明の実施の形態に係る静電チャックの製造工程を示す図（その6）である。

。

【図14】本発明の実施の形態に係る静電チャックの製造工程を示す図（その7）である。

。

#### 【符号の説明】

#### 【0052】

10 静電チャック

40

11 セラミック基体

11A 基板載置面

12 静電電極

12A, 12B, 25A, 25B, 26A, 28A, 31A 面

13, 14 セラミック材

17, 19 開口部

25 第1のグリーンシート

26 第2のグリーンシート

28 第1のアルミナペースト

31 導電性ペースト

50

3 2 第 2 のアルミナペースト

3 4 , 3 5 貫通穴

【図 1】

従来の静電チャックの断面図

【図 2】

従来の静電チャックの製造工程を示す図(その1)

【図 3】

従来の静電チャックの製造工程を示す図(その2)

【図 4】

従来の静電チャックの製造工程を示す図(その3)

【図5】

従来の静電チャックの製造工程を示す図(その4)

【図6】

従来の静電チャックの製造工程を示す図(その5)

【図7】

本発明の実施の形態に係る静電チャックの断面図

【図8】

本発明の実施の形態に係る静電チャックの製造工程を示す図(その1)

【図9】

本発明の実施の形態に係る静電チャックの製造工程を示す図(その2)

【図10】

本発明の実施の形態に係る静電チャックの製造工程を示す図(その3)

【図11】

本発明の実施の形態に係る静電チャックの製造工程を示す図(その4)

【図12】

本発明の実施の形態に係る静電チャックの製造工程を示す図(その5)

## 【図13】

本発明の実施の形態に係る静電チャックの製造工程を示す図(その6)

## 【図14】

本発明の実施の形態に係る静電チャックの製造工程を示す図(その7)

10

---

フロントページの続き

審査官 川東 孝至

(56)参考文献 米国特許第06272002(US, B1)

特開2003-152064(JP, A)

特開2005-343733(JP, A)

特開2002-170870(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/67 - 21/687

B23Q 3/15

H02N 13/00