(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4077890号

(P4077890)

(45) 発行日 平成20年4月23日(2008.4.23)

(24) 登録日 平成20年2月8日(2008.2.8)

(51) Int.Cl.

F 1

G02B 26/08 (2006.01)

G02B 26/08

E

G09G 3/34 (2006.01)

G09G 3/34

Z

H04N 9/30 (2006.01)

H04N 9/30

請求項の数 2 (全 12 頁)

(21) 出願番号 特願平8-108007

(22) 出願日 平成8年4月26日(1996.4.26)

(65) 公開番号 特開平8-304720

(43) 公開日 平成8年11月22日(1996.11.22)

審査請求日 平成15年4月15日(2003.4.15)

(31) 優先権主張番号 429388

(32) 優先日 平成7年4月26日(1995.4.26)

(33) 優先権主張国 米国(US)

(73) 特許権者 590000879

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国テキサス州ダラス、ノース

セントラルエクスプレスウェイ 135

OO

(74) 代理人 100066692

弁理士 浅村 皓

(74) 代理人 100072040

弁理士 浅村 肇

(74) 代理人 100091339

弁理士 清水 邦明

(74) 代理人 100094673

弁理士 林 銘三

最終頁に続く

(54) 【発明の名称】イメージディスプレイシステムにおけるアーチファクト低減方法

## (57) 【特許請求の範囲】

## 【請求項 1】

多数のメモリ多重化空間光変調器(SLM)を有するイメージディスプレイシステムにおけるアーチファクト低減方法であって、前記SLMは独立に制御可能な複数のピクセル素子を含み、各SLMは対応する相対的な位置にピクセル素子を有し、各SLMは異なるカラーを表わすピクセルデータに基づいて像をディスプレイし、該像は像平面で結合され、各SLMに対するピクセル素子は多重リセットグループに割り当てられ、一つのリセットグループの各ピクセル素子は、SLMに対するリセットグループの全てに共通のメモリにおける対応するメモリセルに結合されており、

各SLMに対し、第1リセットグループのピクセル素子に関連するあるビットウェートのピクセルデータをメモリからロードするステップと、ここで、前記多数のSLMの各々に対する前記第1リセットグループは、他のSLMの前記第1リセットグループに対して使用されたピクセルの組と異なる相対位置を有するピクセルの組を含む；

前記関連するメモリセルからのデータに応答して、各SLMに対する前記第1リセットグループのピクセル素子の状態を制御するステップと；

各SLMに対する前記第1リセットグループに対するピクセル素子の状態に応答して像をディスプレイするステップと；

前記リセットグループを変えながら、前記ロードするステップと、制御するステップと、ディスプレイするステップとを各リセットグループと前記ピクセルデータの各ビットウェートに対して繰り返すステップと、

10

20

を含むアーチファクト低減方法。

【請求項 2】

多数のメモリ多重化空間光変調器( SLM )を有するイメージディスプレイシステムにおけるアーチファクト低減方法であって、前記 SLM は独立に制御可能な複数のピクセル素子を含み、各 SLM は多数のローに配列されたピクセル素子を含み、各 SLM は異なるカラーを表わすピクセルデータに基づいて像をディスプレイし、該像は像平面で結合され、各 SLM に対するピクセル素子のローは多重リセットグループに割り当てられ、一つのリセットグループのピクセル素子の各ローは、 SLM に対するリセットグループの全てに共通のメモリにおける対応するメモリセルのグループに結合されている、イメージディスプレイシステムにおけるアーチファクト低減方法は、

10

各 SLM に対し、第 1 リセットグループのピクセル素子に関連するあるビットウェートのピクセルデータをメモリからロードするステップと、ここで、前記多数の SLM の各々に対する前記第 1 リセットグループは、他の SLM の前記第 1 リセットグループに対して使用されたピクセルのローと異なる相対位置を有するピクセル素子のローの組を含む；

前記関連するメモリセルからのデータに応答して、各 SLM に対する前記第 1 リセットグループのピクセル素子の状態を制御するステップと；

各 SLM に対する前記第 1 リセットグループに対するピクセル素子の状態に応答して像をディスプレイするステップと；

前記リセットグループを変えながら、前記ロードするステップと、制御するステップと、ディスプレイするステップとを各リセットグループと前記ピクセルデータの各ビットウェートに対して繰り返すステップと、

を含むアーチファクト低減方法。

20

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明はイメージディスプレイシステムに関し、特に 1 個以上の空間光変調器を使用してカラーディスプレイを発生するディスプレイシステムにおけるアーチファクト低減方法に関する。

【0002】

【従来の技術】

30

空間光変調器( SLM : spatial light modulator )に基づいたイメージディスプレイシステムが陰極線管に基づいたイメージディスプレイシステムに代わるものとして次第に使用されつつある。イメージディスプレイ応用に使用される SLM は像平面へ光を放出もししくは反射するピクセル発生素子アレイである。画素と識別して、ピクセル発生素子自体を“ピクセル”と呼ぶことが多い。1 つの画素を発生するのに SLM アレイの 2 つ以上のピクセルを使用できることが判れば、この用語は前後関係から自明である。

【0003】

デジタルマイクロミラーデバイス( DMD : digital micro-mirror device )は SLM の 1 種である。 DMD は数百乃至数千個の小さな傾斜ミラーのアレイを有している。傾斜できるようにするために、各ミラーは支柱に載置された 1 個以上のヒンジに取り付けられ、下層の制御回路から空隙により間隔がとられている。制御回路は静電力を与え、それにより各ミラーは選択的に傾斜する。各ミラー素子により 1 画素の強度が与えられる。

40

【0004】

所与の時間にどのピクセルをオンオフするかによって像が画定されるように、 DMD のミラー素子を個別にアドレスすることができる。 DMD のミラー素子をアドレスするためには、各ミラー素子はアドレス信号のオンオフ状態を決定する少しのデータを記憶するメモリセルと連絡されている。ミラー素子が像平面へ光を反射するか否かを示すハイもしくはロー信号により各ミラー素子がアドレスされる点でアドレッシングはバイナリである。ミラー素子の DMD アレイ周辺のデータローディング回路を介してメモリセル内に入力データを記憶することにより DMD は“ロード”される。

50

## 【0005】

ピクセルデータは空間“ビットプレーン (bit-plane)”フォーマットでDMDのメモリセルへ送られる。このフォーマットでは各フレームに対してデータはピクセル毎ではなく全ピクセルのビットウェイト (bit-weight) により配置される。このフォーマットでは1フレーム期間中に、各々がそのミラー素子のnビットピクセル値の異なるビットウェイトを表す、連続アドレス信号により各ミラー素子をアドレスすることによりグレイスケール像を発生することができる。アドレッシングに使用されるビットのビットウェイトが上位であるほど、ミラー素子がオンのままでされる時間が長くなる。最も明るい強度に対しては、ミラー素子はアドレスされる度にオンとされる。これは本質的にパルス幅変調であり、多くのバリエーションが可能である。連続するフレームに対するデータによりDMDを再アドレスすることにより移動像を発生することができる。

10

## 【0006】

カラーイメージに対する1つの方法は、各原色 (R, G, B) について1個ずつの、3個のDMDを使用することである。各DMDの対応するピクセルからの光は観察者が所望のカラーを知覚するように収束される。もう1つの方法は1個のDMDと原色区画を有するカラーホイール (color wheel) を使用することである。さまざまなカラーに対するデータがカラーホイールへシーケンスされ同期化されて目の中でシーケンシャルな像が連続するカラー像へ統合されるようにされる。第3の方法では2個のDMDが使用され、一方は2色間の切り替えに使用され、他方は第3色を表示するのに使用される。

20

## 【0007】

## 【発明が解決しようとする課題】

どんなディスプレイシステムでもそうであるが、DMDベースディスプレイシステムからの像の品質はアーチファクトを解消することにより改善される。潜在的なアーチファクトには観察者がまばたきしたり、目を動かしたり、目の前で手を振ったりした時にフラッシュや筋として現れる一時的な輪郭線が含まれる。もう1つのアーチファクトは動き輪郭線であり、それは移動物体を目で追っている時に疑似輪郭線として現れる。疑似輪郭線は急峻なエッジにおけるゴースト像もしくは緩やかに変化する領域におけるアーチファクト輪郭線である。メモリ多重化として知られるデータローディング法を使用するDMDディスプレイシステムに特有な他種のアーチファクトもある。

## 【0008】

30

## 【課題を解決するための手段】

本発明の1つの特徴は多数のメモリ多重化空間光変調器 (SLM) を有するイメージディスプレイシステム内のアーチファクト低減方法である。この種のシステムでは、各SLMは異なるカラーを表すデータに基づいた像を同時にディスプレイし、像は像平面において結合される。SLMは“対応する”SLMロー (row) を有し、それは対応するロー位置を有するローである。メモリ多重化のために、SLMのローはリセットグループ内で接続されている。各リセットグループは各SLMのいくつかのローからなり、対応するSLMローは同じリセットグループ内には無い。SLMへデータをローディングする間に、第1のリセットグループにはピクセルデータの、あるビットウェイトを有するデータがロードされる。このデータは、次のリセットグループにピクセルデータの、あるビットウェイトを有するデータがロードされる間に、ディスプレイされる。これらのローディングおよびディスプレイステップは各リセットグループおよびピクセルデータの各ビットウェイトに対して繰り返される。

40

## 【0009】

本発明の利点はリセットグループが対応するSLMローを含んでいないため、スプリットリセット構成の周期性によるアーチファクトが低減されることである。例えば、スプリットリセット構成が水平であれば、水平線構造を知覚する傾向が少なくなる。

## 【0010】

本発明は1個のSLMを使用してカラーホイールを介したさまざまなカラーの像を逐次表示するシングルSLMシステムにも有用である。この場合、1組のSLMローしかない。

50

1つのカラーに対するリセットグループは別のカラーに対するリセットグループとは異なるローを有している。

【0011】

【発明の実施の形態】

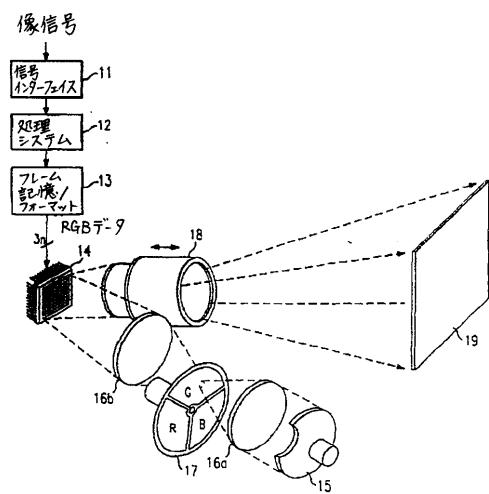

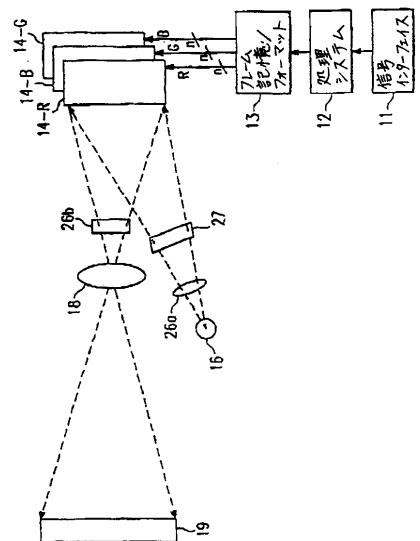

図1および図2は、それぞれ、SLMに基づくカラーディスプレイシステム10および20のブロック図である。システム10はカラーホイールを介したさまざまなカラーの像を逐次ディスプレイする1個のSLMを使用している。システム20は3個のSLMを使用し、その各々が像の異なるカラーに対するデータを同時にディスプレイする。後記するように、カラーディスプレイがシステム10のように逐次与えられるかシステム20のように同時に与えられるかに拘わらず、各システムは多数のデータチャネルを有し、各チャネルが異なるカラー用とされている。一般的に、本発明はさまざまなチャネルのデータのタイミングを変えてディスプレイされる像内のアーチファクトを低減するものである。

10

【0012】

例えば、システム10のSLM14およびシステム20のSLM14はDMD型SLMである。後記するように、本発明ではメモリ多重化SLMが使用される。SLMがDMDである場合には、リセットされるまでオンもしくはオフ位置に設定されたままとされる傾斜ミラーのラッチング特性によりこのメモリ多重化が可能とされる。この特性により、1組のミラー素子が既に設定されている時にもう1組のミラー素子を関連するメモリセルへロードすることができる。これによりミラー素子はメモリセルを共有することができる。

20

【0013】

システム10やシステム20が受信するイメージ信号はデジタル信号もしくは後にデジタル形式に変換されるアナログ信号とすることができる。例えば、入信号は放送されたテレビジョン信号のようなアナログ信号と考えることができる。

【0014】

図1および図2には、主画面処理にとって重要な構成要素しか示されていない。同期化およびオーディオ信号の処理やクローズドキャプショニング(closed captioning)等の機能に使用される他の構成要素は示されていない。

【0015】

システム10およびシステム20は“フロントエンド”構成要素と同じような構成を有し、DMD14へデジタル像データを与えるための、信号インターフェイス11、処理システム12、およびフレームメモリ13、を含む。これらの構成要素についてはシステム10およびシステム20に対して共通に検討し、DMD14および2つのシステムの関連する光学系については別々に検討する。システム10およびシステム20を共通に検討する場合には、DMDはシステム10の1個のDMDもしくはシステム20の多数のDMD14を表す。

30

【0016】

信号インターフェイス11はアナログ入力信号を受信し、ビデオ信号、同期信号、およびオーディオ信号に分離する。信号インターフェイス11は、それぞれ、信号をピクセルデータへ変換しクロミナンスデータから輝度データを分離する、A/Dコンバータおよびカラーセパレータを含んでいる。別の実施例では、カラー分離はA/D変換を行う前にアナログフィルタを使用して行われる。

40

【0017】

プロセッサシステム12はさまざまなピクセル処理タスクを実施することによりディスプレイするピクセルデータを準備する。プロセッサシステム12は処理中にピクセルデータを格納する、フィールドおよびラインバッファ等の、さまざまなメモリデバイスを含んでいる。

【0018】

プロセッサシステム12により代表的に実施される1つのタスクはインターレースされたデータの前進走査変換であり、インターレースされたデータの各フィールドが完全なフレームへ変換される。他の処理タスクはスケーリング、色空間変換、もしくはガンマ補正で

50

ある。色空間変換中に、輝度およびクロミナンスデータはRGBデータへ変換される。DMD14の線形特性によりガンマ補償は不要となるためガンマ補正によりガンマ補償されたデータは逆補償される。

【0019】

実施例では、プロセッサシステム12は前進走査変換およびスケーリング等の計算処理タスクを実施する“走査線ビデオプロセッサ”を含んでいる。このデバイスはテキサスインスツルメンツ社から市販されており、ピクセルデータのラインバイライン処理を行うことができる。

【0020】

フレームメモリ13はプロセッサシステム12から処理されたピクセルデータを受信する。フレームメモリ13は、入力もしくは出力において、データを“ビットプレーン”フォーマットへ変換し、ビットプレーンデータをDMDへ送る。従来の技術で検討したように、ビットプレーンフォーマットはピクセルデータがビットウェートにより再構成されるフォーマットである。これによりDMD14の各ピクセルはある時間の1ビットデータの値に応答してオンオフすることができる。

10

【0021】

代表的なディスプレイシステム10では、フレームメモリ13は“ダブルバッファ”メモリであり、少なくとも2つのディスプレイフレームに対する容量を有することを意味する。一方のディスプレイフレームに対するバッファへ書き込んでいる間に他方のディスプレイフレームに対するバッファをDMD14へ読み出すことができる。2個のバッファは“ピンポン”式に制御してDMD14は連続的にデータを得ることができる。

20

【0022】

従来の技術で前記したように、DMD14は各ミラー素子のオンオフ状態を有する2進デバイスである。データの各ビットに対するビットプレーンはパルス幅変調シーケンスによりロードされディスプレイされる。nビットピクセルデータに対しては、フレーム期間当たりnビットプレーンがある。フレーム期間中に、観察者は2進データを統合してそのフレームの像のさまざまな強度を知覚する。

【0023】

次に図1およびシステム10を参照して、DMD14へのRGBデータの各フレームへ一時に1つのカラーが与えられ、データの各フレームがレッド、ブルー、およびグリーンのデータセグメントへ分割されるようにされる。各セグメントのディスプレイ時間はフレーム毎に1回転するカラーフォイール17に同期化され、DMD14が適切な時間にカラーフォイール17を介した1つのカラーに対するデータを表示するようされる。したがって、各カラー(R, GおよびB)に対するデータチャネルは各フレームがさまざまなカラーに対するシーケンシャルデータを有するよう時間多重化される。

30

【0024】

シーケンシャルカラーシステム10に対して、光源15から集光レンズ16aを介して白色光が送られ、それは回転するカラーフォイール17上的一点へ収束される。第2のレンズ16bによりカラー光線はDMDのミラーアレイのサイズへ適合される。DMDからの反射光により画面19上に像が投影される。投影レンズ18はさまざまな画面サイズに調整される。

40

【0025】

図2およびシステム20を参照して、R, GおよびBデータについて1つづつの3つの異なるデータパスに沿って3個のDMD14へデータが与えられる。光源16から集光レンズ26aを介して白色光が送られ、それはカラーフィルタ27を介して収束される。各カラーフィルタ26は異なるカラーの光(R, GおよびB)をDMD14へ与え、そのカラーに対するデータがディスプレイされる。フィルタ26bによりDMD14からの像が再結合されて投影レンズ18上へ収束され、画面19へ像が収束される。システム20の1つのバリエーションでは1個の大型DMDが各カラーに対する領域を有している。

【0026】

50

システム10およびシステム20のようなシーケンシャルカラーおよびマルチDMDシステムの両方に対する包括的な説明がテキサスインスツルメンツ社が譲り受けたいくつかの特許および特許出願に記載されている。それには米国特許第5,079,544号“標準独立デジタル化ビデオシステム”、米国特許第5,233,385号“白色光強化カラーフィールドシーケンシャル投影”、米国特許出願第07/678,761号“パルス幅変調ディスプレイシステムに使用するDMDアーキテクチャおよびタイミング”、米国特許出願第08/147,249号“デジタルテレビジョンシステム”、および米国特許出願第08/146,385号“DMDディスプレイシステム”が含まれる。これらの各特許および特許出願がここに組み入れられている。

## 【0027】

10

本発明の特徴はビットプレーンディスプレイにより遷移エネルギー変化が生じることを認識することである。ビットプレーンディスプレイでは、特別なデータシーケンスによりピクセルの各ビットウェートについてディスプレイ時間の順序、すなわちディスプレイ時間のセグメント、が指定される。単純な例として、8ビットピクセルデータに対するシーケンスは7,6,5,4,3,2,1,0とることができ、各ビットウェートに対するディスプレイ時間はフレーム中に順次短くなる。1つのビットレベルからもう1つのビットレベルへの遷移毎に遷移エネルギーが関連している。高い遷移エネルギーはアーチファクトとして知覚することができる。

## 【0028】

20

ピークエネルギーレベルを低減する1つの方法はビットウェートを“分割”して各高いビットウェートに対するディスプレイ時間が連続的ではなくフレーム期間中にセグメント化されることである。例えば、最上位ビットに対するディスプレイ時間は2つの部分へ分割することができる。次に、最上位ビット(MSB)に対するデータがフレーム期間中に2度ディスプレイされ、その各オン時間は総MSB時間の半分である。

## 【0029】

図3に前記したビット分割方法の替わりとしてもしくはそれを補足するために使用することができるディスプレイシーケンス方法を示す。この方法ではアーチファクトを低減するように遷移エネルギーが分散される。

## 【0030】

30

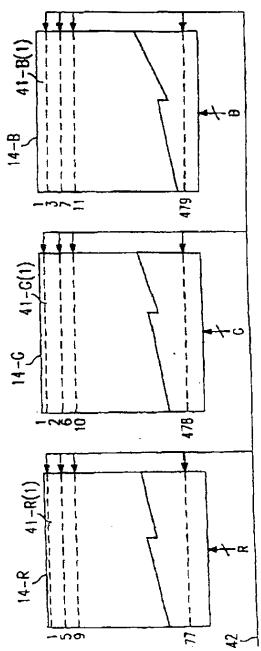

図3の例では、この方法はシステム20等のマルチSLMシステムに実施される。各DMD14はレッド、グリーン、もしくはブルーデータを受信し、したがって各々がDMD14-R、14-G、もしくは14-Bとして示されている。

## 【0031】

40

図3のDMD14は各々がメモリ多重化されている。前記したように、これは多数のミラー素子に同じメモリセルからデータがロードされることを意味する。メモリセルを共有する各ミラー素子が異なるリセット線に接続されている。全体DMDに対して、メモリセル当たりミラー素子と同数のリセット線がある。特定のリセット線に接続されたミラー素子は“リセットグループ”である。動作について、ミラー素子のリセットグループに対する全メモリセルにデータがロードされた後で、これらのミラー素子の状態はそのリセット線上のリセット信号に応答して変化する。メモリの多重化とそれに伴う“スプリット-リセット”データローディング方式についてはテキサスインスツルメンツ社が譲り受け参照としてここに組み入れられている米国特許出願第08/300/356号“空間光変調器用ピクセル制御回路”に記載されている。

## 【0032】

ここに記載する例では、メモリ多重化はロー( row ) (水平の)によるものであり1つのメモリセルからのミラー素子のファンアウトは4である。したがって、ミラー素子の連続する4ロー毎に1ローのメモリセルが共有される。メモリセルを共有する4ローのミラー素子は1“ブロック”のミラー素子である。480ローのミラー素子を有するDMD14は120のブロック41を有する。各ブロック41は4ローを有し、それらはメモリセルの同じローからデータを受信する。

50

## 【0033】

代表的なメモリ多重化構成と同様に、各ローは4本のリセット線の1本に接続されている。図4には、1本のリセット線42しか示されていないが4本のリセット線がある。リセット線42は3個のDMD14の全ブロックの第1ローを含むリセットグループに接続される。したがって、リセットグループは全DMD14のロー数の1/4を含んでいる。

## 【0034】

リセットグループへのデータは1タイムスライス中にロードされる。次のリセットグループへのデータがロードされている間に、第1のリセットグループのミラー素子はリセット信号に応答してオンオフされる。

## 【0035】

より詳細には、フレームのデータローディング中に、同じブロックロー番号を有するローからなるリセットグループがフレーム期間のタイムスライス中にビットウェートによりロードされる。“タイムスライス”はフレーム期間の一部であり、最下位ビットに対するディスプレイ期間である場合が多い。タイムスライスは短すぎて余分なタイムスライスが許されない場合もあるが、一般的には、最下位ビットの持続時間により決定される。

10

## 【0036】

1フレームのデータをローディングしてメモリ多重化システム20上へディスプレイする1例として、第1のリセットグループのビットnがロードされ、次に第2のリセットグループのビットnがロードされ、次に第3のリセットグループのビットnがロードされ、次に第4のリセットグループのビットnがロードされる。次に、第1のリセットグループのビットn-1がロードされ、次に第2のリセットグループのビットn-1がロードされ、以下全リセットグループの全ビットウェートがロードされるまで続けられる。各リセットグループ/ビットウェイトに対するデータがロードされると、前のリセットグループ/ビットウェイトデータがディスプレイされる。この例では、ビットウェートは各リセットグループに対して同じ順序に従うが、これは要求されているわけではない。事実、リセットグループの中では、さまざまなビットウェートシーケンスが有利である。このようにして、各フレーム期間中に、全DMDローがそれらのリセットグループを介して、またそのフレームに対するデータの全ビットウェートがロードされてディスプレイされる。

20

## 【0037】

システム20等のメモリ多重化ディスプレイシステムに対しては、画像品質を最適化する特殊なローディングおよびディスプレイパターンが開発されている。図3の例では、次のようなパターンとすることができます。

30

リセットグループ1、ビットウェートシーケンスa

リセットグループ2、ビットウェートシーケンスb

リセットグループ3、ビットウェートシーケンスc

リセットグループ4、ビットウェートシーケンスd

前記したように、ローディングおよびディスプレイング中に、各シーケンスのビットウェートはリセットグループ間で変更される。

## 【0038】

図3のDMD14が“対応する”ローを有しており、各DMD14の第nローが各DMD14についてその同じ位置にある。したがって、“1”とマークされた各DMD14の第1のDMDローがディスプレイされるデータの第1ローを受信する。これら3つのローは対応するローである。同様に、480ロー像に対する、各DMD14の第480番ローはディスプレイされるデータの最終ローを受信する。これらの3つの第480番ローは対応するローである。

40

## 【0039】

図からお判りのように、DMD14のDMDローとそのブロックロー間の連関はDMD14間で垂直にオフセットされている。すなわち、DMD14の所与の1組の対応するローに対して、各DMDローは異なるブロックローと連関されている。例えば、DMD14-Rの第1のローはブロック41-R(1)の第1のローと連関されている。しかしながら

50

、 D M D 1 4 - G の第 1 のローはブロック 4 1 - G ( 1 ) の第 4 ローに対応している。 D M D 1 4 - B の第 1 のローはブロック 4 1 - B ( 1 ) の第 3 ローに対応している。

#### 【 0 0 4 0 】

前記したことと一貫して、第 1 のリセットグループに対しては、連関する D M D ローは D M D 1 4 - R の 1 , 5 , 9 . . . 4 7 7 ロー、 D M D 1 4 - G の 2 , 6 , 1 0 , . . . 4 7 8 ロー、および D M D 1 4 - B の 3 , 7 , 1 1 , . . . 4 7 9 ローである。各リセットパターンは同様なパターンで接続されており、 D M D ローは対応する D M D ローと同じリセットグループ内には無いように接続されている。

#### 【 0 0 4 1 】

前記したように、ディスプレイはミラー素子のリセットグループをローディングしかつリセットすることにより発生される。特定のリセットグループがディスプレイされると、連関する D M D ローは対応しない。例えば、リセット線 4 2 に接続されたリセットグループがディスプレイされる場合、ディスプレイされる D M D ローは D M D 1 4 - R の 1 , 5 , 9 , . . . 4 7 7 ロー、 D M D 1 4 - G の 2 , 6 , 1 0 , . . . 4 7 8 ロー、および D M D 1 4 - B の 3 , 7 , 1 1 , . . . 4 7 9 ローである。

#### 【 0 0 4 2 】

対応する D M D ローとリセットグループ間の連関が非均一であるため、各カラーに対するデータは同じパターンに従うことができる。しかしながら、各カラーに対する遷移時間が異なるため遷移ピークが低減される。

#### 【 0 0 4 3 】

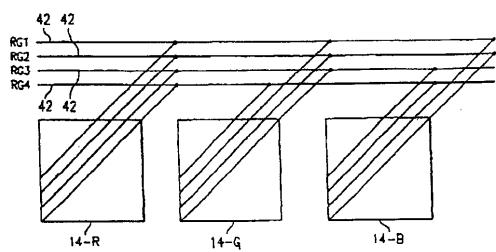

対応する D M D ローを異なるリセットグループと連関させる前記方法は水平メモリ多重化 D M D 1 4 に向けられたものであるが、同じ概念を他のメモリ多重化構成に応用することができる。例えば、メモリ多重化は対角とすることができます。水平メモリ多重化の場合のように、各メモリセルのファンアウトは 1 組の垂直に連続するミラー素子である。しかしながら、ブロックローは対角線に沿っており、ブロックロー  $n$  に対するデータは D M D ロー 1 のピクセル 1 、 D M D ロー 2 のピクセル 4 、 D M D ロー 3 のピクセル 3 、および D M D ロー 4 のピクセル 2 等に対するデータを含むことがある。  $n$  ローを有する D M D に対しては、  $2 n - 1$  のブロックローがある。対角メモリ多重化についてはここに組み入れられている米国特許出願第 0 8 / 3 0 0 , 3 5 6 号に詳細に記載されている。

#### 【 0 0 4 4 】

図 4 は本発明に従って対角分割リセットを行うように構成された 3 個の S L M の  $8 \times 8$  ピクセル部を示す。異なるリセットグループに対して 1 本づつの 4 本のリセット線 4 2 がある。 S L M 1 4 の対応する 4 組の対角ローが示されている。各 D M D 1 4 の対応する対角ローはさまざまなりセットグループと連関されている。

#### 【 0 0 4 5 】

同じ概念が 2 個の D M D しかないシステムに応用される。さらに、システム 1 0 等のシングル D M D システムに対しては、 D M D ローとリセットグループ間の対応はカラー毎にシフトさせて図 3 の方法のシーケンシャルバージョンを実現することができる。各カラーに対して、リセットグループを再構成してさまざまな S L M ローを含む用にすることができる。目の積分 ( eye's integration ) はフレーム期間内のエネルギーの積分に基づいているため、フレーム期間内でエネルギーレベルを適切に分散させることによりアーチファクトを低減することができる。

#### 【 0 0 4 6 】

特定の実施例について本発明を説明してきたが、本明細書は制約的意味合いを有するものではない。当業者であれば他の実施例だけでなく開示された実施例のさまざまな改良が容易にお判りと思われる。したがって、発明の真の範囲内に入る改良は全て特許請求の範囲に入るものとする。

#### 【 0 0 4 7 】

以上の説明に関して更に以下の項を開示する。

( 1 ) . 多数のメモリ多重化空間光変調器 ( S L M ) を有し、各 S L M が異なるカラーを

10

20

30

40

50

表すピクセルデータに基づいた像をディスプレイし、像は像平面において結合されるイメージディスプレイシステムにおけるアーチファクト低減方法であって、該方法は、前記ＳＬＭ内に対応するロー位置を有する前記ＳＬＭのローを識別して対応するＳＬＭローを識別するステップと、各リセットグループが前記各ＳＬＭのいくつかのローからなりしかも対応するＳＬＭローが同じリセットグループ内には無いようにリセットグループ内で前記各ＳＬＭのローを接続するステップと、前記ピクセルデータの、あるビットウェイトを有するデータを第1のリセットグループへロードするステップと、前記第1のリセットグループへロードされた前記データをディスプレイするステップと、前記リセットグループ間で交互に各リセットグループおよび前記ピクセルデータの各ビットウェイトについて前記ローディングステップおよび前記ディスプレイステップを繰り返すステップとからなるアーチファクト低減方法。10

## 【0048】

(2). 第1項記載の方法であって、前記対応するローの各ローが異なるリセットグループ内にあるアーチファクト低減方法。

## 【0049】

(3). 第1項記載の方法であって、前記繰り返しステップは前記ビットウェイトがさまざまなりセットグループに対してさまざまな順序でロードされるように実施されるアーチファクト低減方法。

## 【0050】

(4). 第1項記載の方法であって、前記ローディングステップおよび前記ディスプレイステップはフレーム期間の2つの連続するタイムスライス内で実施され、前記タイムスライスは実質的に最下位ビットウェイトを有するデータに対するディスプレイ時間により決定されるアーチファクト低減方法。20

## 【0051】

(5). 第1項記載の方法であって、前記ＳＬＭディスプレイデータの1つは2つのカラーに対するものであり前記ＳＬＭデータの1つは第3のカラーに対するものであるアーチファクト低減方法。

## 【0052】

(6). 第1項記載の方法であって、前記各ＳＬＭディスプレイデータが異なるカラーに対するものであるアーチファクト低減方法。30

## 【0053】

(7). 第1項記載の方法であって、前記ＳＬＭはデジタルマイクロミラーデバイスであるアーチファクト低減方法。

## 【0054】

(8). 第1項記載の方法であって、前記対応するローは前記ＳＬＭの水平ローに沿っておりリセットグループは前記水平ローを含むアーチファクト低減方法。

## 【0055】

(9). 第1項記載の方法であって、前記対応するローは前記ＳＬＭの対角ローに沿っており前記リセットグループは前記対角ローを含むアーチファクト低減方法。

## 【0056】

(10). メモリ多重化空間光変調器(ＳＬＭ)を有し、カラーフォイールを介し、異なるカラーを表すピクセルデータに基づいた像を逐次ディスプレイする、イメージディスプレイシステムにおけるアーチファクト低減方法であって、該方法は、各リセットグループが前記ＳＬＭのいくつかのローからなるようにリセットグループへ前記ＳＬＭのローを割り当てるステップと、前記ピクセルデータの、あるビットウェイトを有するデータを第1のリセットグループへロードするステップと、前記第1のリセットグループへロードされた前記データをディスプレイするステップと、前記リセットグループ間で交互に各リセットグループおよび第1のカラーの前記ピクセルデータの各ビットウェイトについて前記ローディングステップおよび前記ディスプレイステップを繰り返すステップと、前記リセットグループが前記ＳＬＭのさまざまなローを含むように第2のカラーの前記ピクセルデータを表す。40

タについて前記割り当て、ローディング、およびディスプレイステップを繰り返すステップとからなるアーチファクト低減方法。

【0057】

(11). 第10項記載の方法であって、前記繰り返しステップは前記ビットウェイトがさまざまなりセットグループに対してさまざまな順序でロードされるように実施されるアーチファクト低減方法。

【0058】

(12). 第10項記載の方法であって、前記ローディングステップおよび前記ディスプレイステップはフレーム期間の2つの連続するタイムスライス内で実施され、前記タイムスライスは実質的に最下位ビットウェイトを有するデータに対するディスプレイ時間により決定されるアーチファクト低減方法。 10

【0059】

(13). 第10項記載の方法であって、前記リセットグループは前記SLMの対角口一を含むアーチファクト低減方法。

【0060】

(14). 第10項記載の方法であって、前記リセットグループは前記SLMの水平口一を含むアーチファクト低減方法。

【0061】

(15). 第10項記載の方法であって、前記SLMはデジタルマイクロミラーデバイスであるアーチファクト低減方法。 20

【0062】

(16). SLMに基づいたディスプレイシステム10, 20内のアーチファクト低減方法であって、その像はパルス幅変調された強度レベルに対してビットウェイトによりディスプレイされるデータに基づいている。この方法はさまざまなカラーの像を同時にディスプレイするマルチSLMシステム20や各フレーム期間中にさまざまなカラーの像を逐次発生するシングルSLMシステム10に使用することができる。マルチSLMシステム20に対しては、本方法はメモリ多重化された、さまざまな時間にロードされディスプレイされる“リセットグループ”を有するSLM14に使用される。SLMの対応するローはさまざまなりセットグループと連関付けられている。 30

【図面の簡単な説明】

【図1】1個のSLMおよびカラーフォイールを使用してカラー像を与えるSLMベースディスプレイシステムのブロック図。

【図2】多数のSLMを使用してカラー像を与えるSLMに基づくディスプレイシステムのブロック図。

【図3】水平メモリ多重化SLMを有する、図2のシステム内のアーチファクトを低減する方法を示す図。

【図4】対角にメモリ多重化されるSLMに対する方法を示す図。

【符号の説明】

10, 20 SLMに基づくカラーディスプレイシステム

11 信号インターフェイス

40

12 処理システム

13 フレームメモリ

14, 14R, 14-B, 14-G デジタルミラーデバイス

15 光源

16a, 16b レンズ

17 カラーフォイール

18 投影レンズ

19 画面

26a, 26b 集光レンズ

27 カラーフィルタ

50

【 図 1 】

【 図 2 】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ピシャル マーカンディ

アメリカ合衆国テキサス州ダラス, ロアリング ドライブ 5630, アパートメント ナンバー

157

(72)発明者 ロバート ジェイ. ゴウブ

アメリカ合衆国カリフォルニア州ロス ガトス, アダムズ ロード 25734

審査官 河原 正

(56)参考文献 国際公開第92/009172 (WO, A1)

欧州特許出願公開第00610665 (EP, A1)

(58)調査した分野(Int.Cl., DB名)

G02B 26/08

G09G 3/34

H04N 9/30