(12) 发明专利

(10) 授权公告号 CN 109478710 B

(45) 授权公告日 2021.07.13

(21) 申请号 201680061528.7

(72) 发明人 本杰明·史塔生·库克

(22) 申请日 2016.12.29

斯瓦米纳坦·桑卡兰

(65) 同一申请的已公布的文献号

(74) 专利代理机构 北京律盟知识产权代理有限

申请公布号 CN 109478710 A

责任公司 11287

(43) 申请公布日 2019.03.15

代理人 林斯凯

(30) 优先权数据

(51) Int.CI.

14/982,932 2015.12.29 US

H01Q 1/22 (2006.01)

(85) PCT国际申请进入国家阶段日

H01Q 13/20 (2006.01)

2018.04.20

(56) 对比文件

US 6061026 A, 2000.05.09

(86) PCT国际申请的申请数据

EP 1063723 A1, 2000.12.27

PCT/US2016/069137 2016.12.29

CN 104201162 A, 2014.12.10

(87) PCT国际申请的公布数据

CN 1682161 A, 2005.10.12

W02017/117362 EN 2017.07.06

CN 103247581 A, 2013.08.14

(73) 专利权人 德州仪器公司

审查员 韩雪莲

地址 美国德克萨斯州

权利要求书3页 说明书8页 附图14页

(54) 发明名称

用于背侧集成电路高频信号辐射、接收的方法和设备以及互连件

(57) 摘要

在设备(700)的所描述实例中，半导体衬底(710)具有前侧表面及与所述前侧表面相对的背侧表面。金属导体(714)形成于所述前侧表面上方。至少一个空腔开口蚀刻于所述背侧表面中。辐射或耦合结构(716)形成于所述金属导体(714)的一部分中且配置成通过所述背侧表面中的所述空腔开口辐射信号。

## 1. 一种半导体设备,其包括:

半导体衬底,其具有前侧表面及与所述前侧表面相对的背侧表面,所述前侧表面包含第一层级中的电路;

金属导体堆叠,其形成于上覆所述第一层级的第二层级中,其中所述第二层级包含所述第二层级的多个子层级;

至少一个空腔开口,其蚀刻于所述背侧表面中且延伸到所述半导体衬底中,其中至少所述第二层级上覆所述空腔开口;结构,其形成于所述金属导体堆叠的一部分中以通过所述背侧表面中的所述空腔开口辐射信号,其中所述结构形成于上覆所述第一层级的所述第二层级的所述子层级的至少一者中;以及

反射表面,其上覆并邻近所述第二层级、并与所述结构间隔所述第二层级的所述子层级中的至少一者、并经配置以朝向所述背侧表面中的所述空腔开口反射经辐射信号。

2. 根据权利要求1所述的半导体设备,其中所述反射表面为电反射器。

3. 根据权利要求2所述的半导体设备,其中所述反射表面经配置以180度相移反射所述经辐射信号。

4. 根据权利要求2所述的半导体设备,其中所述反射表面与所述结构间隔一距离,所述距离是所述经辐射信号的波长的分数,介于所述波长的1/100与1/2之间。

5. 根据权利要求1所述的半导体设备,其中所述反射表面为磁性反射器。

6. 根据权利要求5所述的半导体设备,其中所述反射表面经配置以0度相移反射所述经辐射信号。

7. 根据权利要求1所述的半导体设备,其中所述经辐射信号具有在0.1THz与30THz之间的频率。

8. 根据权利要求1所述的半导体设备,其中所述空腔开口具有倾斜侧壁。

9. 根据权利要求1所述的半导体设备,其中所述空腔开口形成用于所述经辐射信号的波导。

10. 根据权利要求1所述的半导体设备,其中所述空腔开口具有竖直侧壁。

11. 根据权利要求1所述的半导体设备,其中所述空腔开口具有导电材料涂层。

12. 根据权利要求1所述的半导体设备,其中所述结构形成天线。

13. 根据权利要求1所述的半导体设备,其中所述结构为辐射结构。

14. 根据权利要求1所述的半导体设备,其中所述结构为耦合结构。

15. 根据权利要求1所述的半导体设备,其中所述空腔开口具有阶梯形侧壁。

16. 根据权利要求1所述的半导体设备,其中至少所述第一层级和所述第二层级上覆所述空腔开口。

17. 根据权利要求11所述的半导体设备,其中所述导电材料涂层不延伸到超出所述空腔开口的所述背侧表面上。

18. 一种用于形成半导体设备的方法,其包括:

在第一层级中形成金属导体堆叠,所述第一层级上覆半导体衬底的前侧表面,其中所述第一层级包含所述第一层级的多个子层级,且其中所述前侧表面包含上覆所述第一层级的第二层级中的电路;

在半导体衬底的背侧表面上形成背侧空腔开口并延伸到所述半导体衬底中,其中至少

所述第一层级上覆所述空腔开口,且其中所述半导体衬底的所述背侧表面与所述半导体衬底的所述前侧表面相对;

在所述金属导体堆叠的一部分中形成结构以通过所述背侧空腔开口辐射信号,其中所述结构形成于上覆所述第二层级的所述第一层级的所述子层级的至少一者中;以及

形成反射表面,所述反射表面上覆并邻近所述第一层级、并与所述结构间隔所述第一层级的所述子层级中的至少一者、并经配置以朝向所述背侧表面中的所述空腔开口反射经辐射信号。

19. 根据权利要求18所述的用于形成半导体设备的方法,其中形成所述背侧空腔开口进一步包括:

研磨所述半导体衬底的所述背侧表面以将所述半导体衬底薄化到预定厚度。

20. 根据权利要求18所述的用于形成半导体设备的方法,其中形成所述背侧空腔开口进一步包括执行湿式蚀刻以形成具有倾斜侧壁的开口。

21. 根据权利要求18所述的用于形成半导体设备的方法,其中形成所述背侧空腔开口进一步包括执行蚀刻,所述蚀刻是选自主要由KOH湿式蚀刻、TMAH蚀刻及深度反应性离子蚀刻组成的群中的一者。

22. 根据权利要求18所述的用于形成半导体设备的方法,其中所述结构为辐射结构。

23. 根据权利要求18所述的用于形成半导体设备的方法,其中所述结构为耦合结构。

24. 根据权利要求18所述的用于形成半导体设备的方法,其中所述反射表面为电反射器。

25. 根据权利要求24所述的用于形成半导体设备的方法,其中所述反射表面经配置以180度相移反射所述经辐射信号。

26. 根据权利要求24所述的用于形成半导体设备的方法,其中所述反射表面与所述结构间隔一距离,所述距离是所述经辐射信号的波长的分数,介于所述波长的1/100与1/2之间。

27. 根据权利要求18所述的用于形成半导体设备的方法,其中所述反射表面为磁性反射器。

28. 根据权利要求27所述的用于形成半导体设备的方法,其中所述反射表面经配置以0度相移反射所述经辐射信号。

29. 根据权利要求18所述的用于形成半导体设备的方法,其中所述经辐射信号具有在0.1THz与30THz之间的频率。

30. 根据权利要求18所述的用于形成半导体设备的方法,其中所述背侧空腔开口具有倾斜侧壁。

31. 根据权利要求18所述的用于形成半导体设备的方法,其中所述背侧空腔开口形成用于所述经辐射信号的波导。

32. 根据权利要求18所述的用于形成半导体设备的方法,其中所述背侧空腔开口具有竖直侧壁。

33. 根据权利要求18所述的用于形成半导体设备的方法,其中所述背侧空腔开口具有阶梯形侧壁。

34. 根据权利要求18所述的用于形成半导体设备的方法,其中所述背侧空腔开口具有

导电材料涂层。

35. 根据权利要求34所述的用于形成半导体设备的方法,其中所述导电材料涂层不延伸到超出所述背侧空腔开口的所述背侧表面上。

36. 根据权利要求18所述的用于形成半导体设备的方法,其中所述结构形成天线。

37. 根据权利要求18所述的用于形成半导体设备的方法,其中至少所述第一层级和所述第二层级上覆所述背侧空腔开口。

38. 一种半导体系统,其包括:

第一集成电路,其包含:用于辐射THz频率信号的第一天线,所述第一天线形成于上覆第一半导体衬底的前侧表面的第一层级中的第一金属导体堆叠中,其中所述第一层级包含所述第一层级的多个子层级,且其中所述第一天线形成于所述第一层级的所述子层级中的至少一者中;第一开口,其形成于所述第一半导体衬底的背侧中并在对应于所述第一天线的位置处延伸到所述第一半导体衬底中,其中所述第一层级上覆所述第一开口;以及第一反射表面,其上覆并邻近所述第一层级、并与所述第一天线间隔所述第一层级的所述子层级中的至少一者、并经配置以朝向所述第一半导体衬底的所述背侧中的所述第一开口反射经辐射THz频率信号;及

第二集成电路,其包含:用于接收所述THz频率信号的第二天线,所述第二天线形成于上覆第二半导体衬底的前侧表面的第二层级中的第二金属导体堆叠中,其中所述第二层级包含所述第二层级的多个子层级,且其中所述第二天线形成于所述第二层级的所述子层级中的至少一者中;及第二开口,其形成于所述第二半导体衬底的背侧中且在对应于所述第二天线的位置处延伸到所述第二半导体衬底中,其中所述第二层级上覆所述第二开口;

所述第一开口和所述第二开口面向彼此并彼此对准,以便于将所述THz频率信号从所述第一集成电路发射到所述第二集成电路。

## 用于背侧集成电路高频信号辐射、接收的方法和设备以及互连件

### 技术领域

[0001] 本发明大体上涉及集成电路和集成波结构,且更确切地说,涉及构建用于在半导体装置中高频辐射和接收的背侧波结构。

### 背景技术

[0002] 如本文中所使用,术语“兆赫兹”涵盖具有对应于大致0.1THz到大致30.0THz的频率范围的大致3000μm到10μm的波长的电磁发射。

[0003] 由于三个关键问题,将来自集成电路的毫米波信号、次THZ信号和THz信号耦合到天线或互连件在常规解决方案中可能有问题。

[0004] 第一个问题涉及在后端材料中由于金属中的趋肤深度和氧化物及氮化物中的介电损耗而出现的损耗。为实现高增益天线,或为形成高频芯片间互连件,在后端加工中相对于波长需要大型结构,这大大地增加了导体和介电损耗。

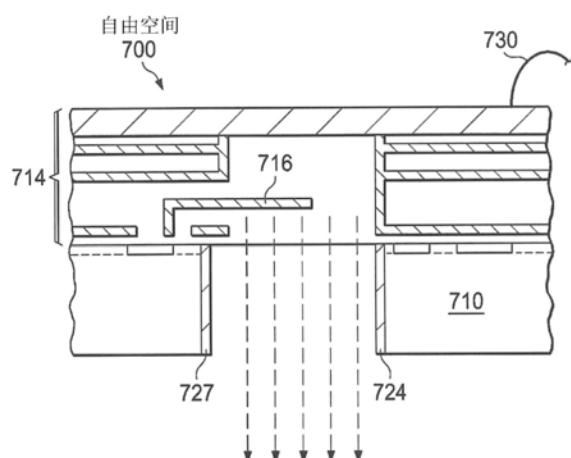

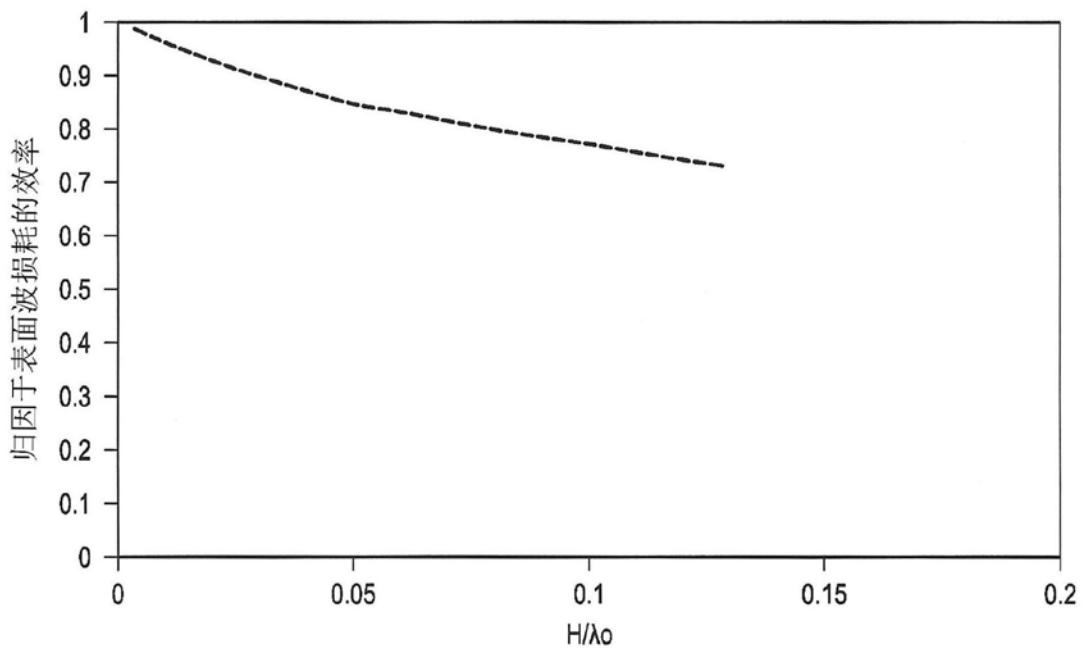

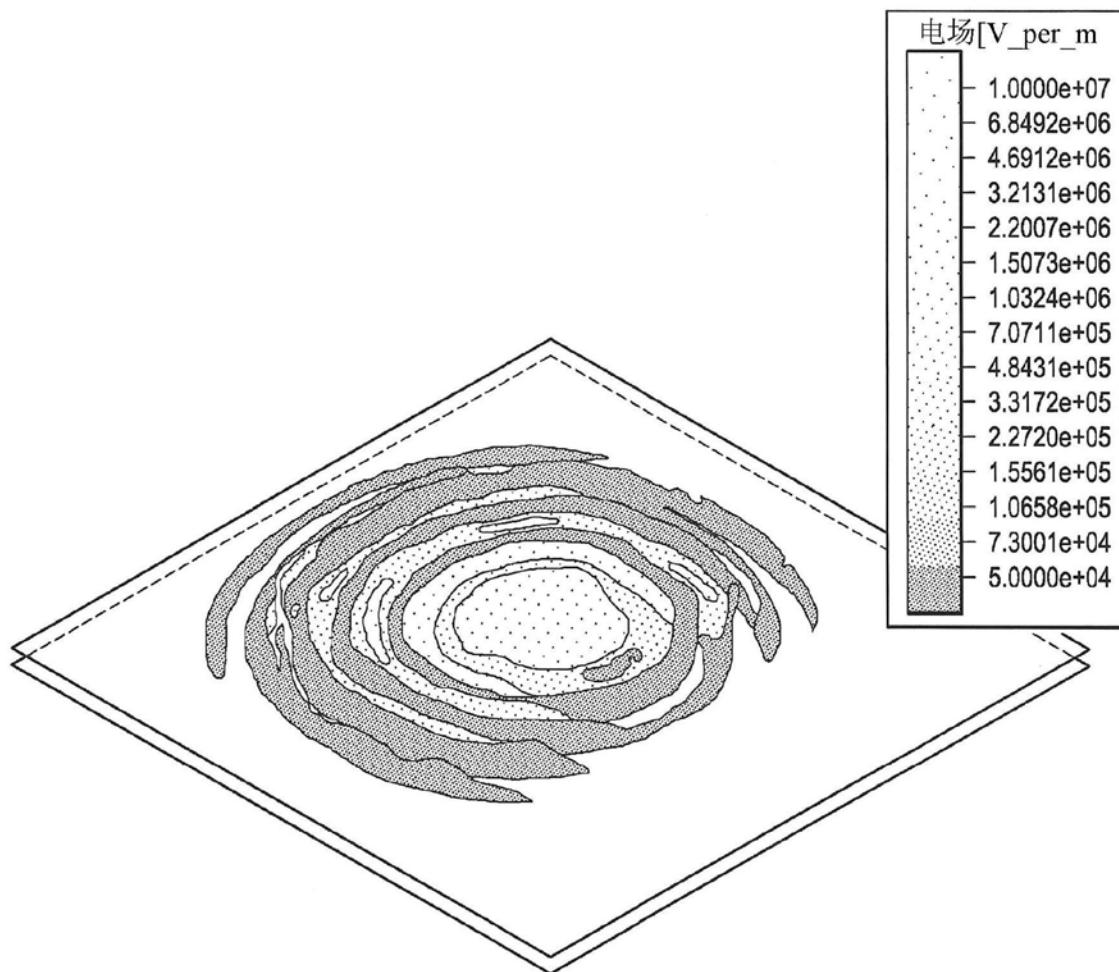

[0005] 第二个问题涉及表面波,其是在金属界面上的介电质相对于信号波长较大时所出现的传播模式。表面波引起天线及互连件中的信号损耗(效率损耗)。图1A及1B展示效率的曲线(展示于图1A的竖直轴上),其中H为金属M1的顶部上方的介电质的厚度,且比率H/λ\_o展示于水平轴上。典型后端介电质为6微米厚,其在1THz频率下为0.02(H/λ\_o),如图1A中所示,由于贴片天线(类似于后端中的发射线)中的表面波,这导致10%电力损耗。图1B说明实例结构中的表面波效应,其展示能量作为波沿着介电层的表面转移且因此不会有效地远离所述结构发射。

[0006] 第三个问题涉及通常用于常规半导体装置的顶层级金属结构和介电材料。在用于辐射器或耦合结构时,这些材料对于THz频率信号的有效辐射和接收来说损耗过大。

[0007] 在一个解决专利第US 8,450,687号(“所述’687专利”)中的至少一些问题的常规方法中,天线直接集成在集成电路(IC)上。在’687专利中,天线形成在IC上,意图在IC的电路侧或顶侧(有时被称作“前”侧)上辐射能量。’687专利中所描述的天线结构是以相比先前方法降低生产成本的方式形成,是因为天线构造可以并入到IC构建过程中,由此与先前方法中一样节省额外微机械加工成本。’687专利的方法的另一特征在于所使用的天线相比常规平面型集成天线改进了辐射效率。然而,额外问题仍然存在。

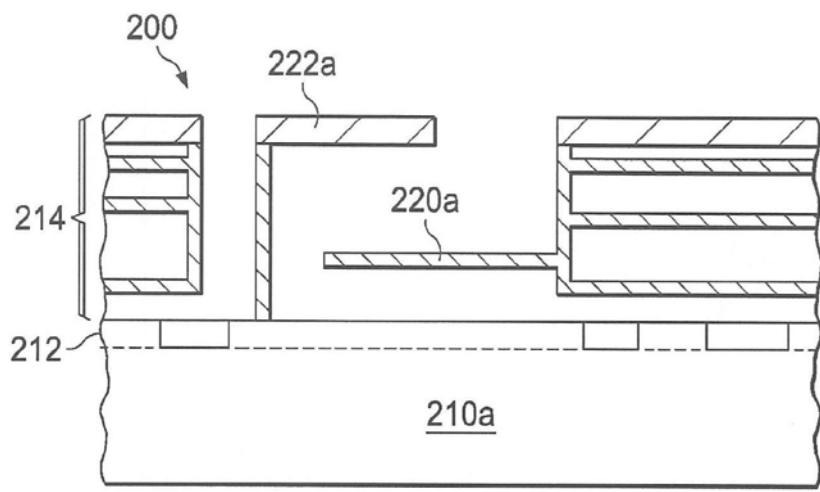

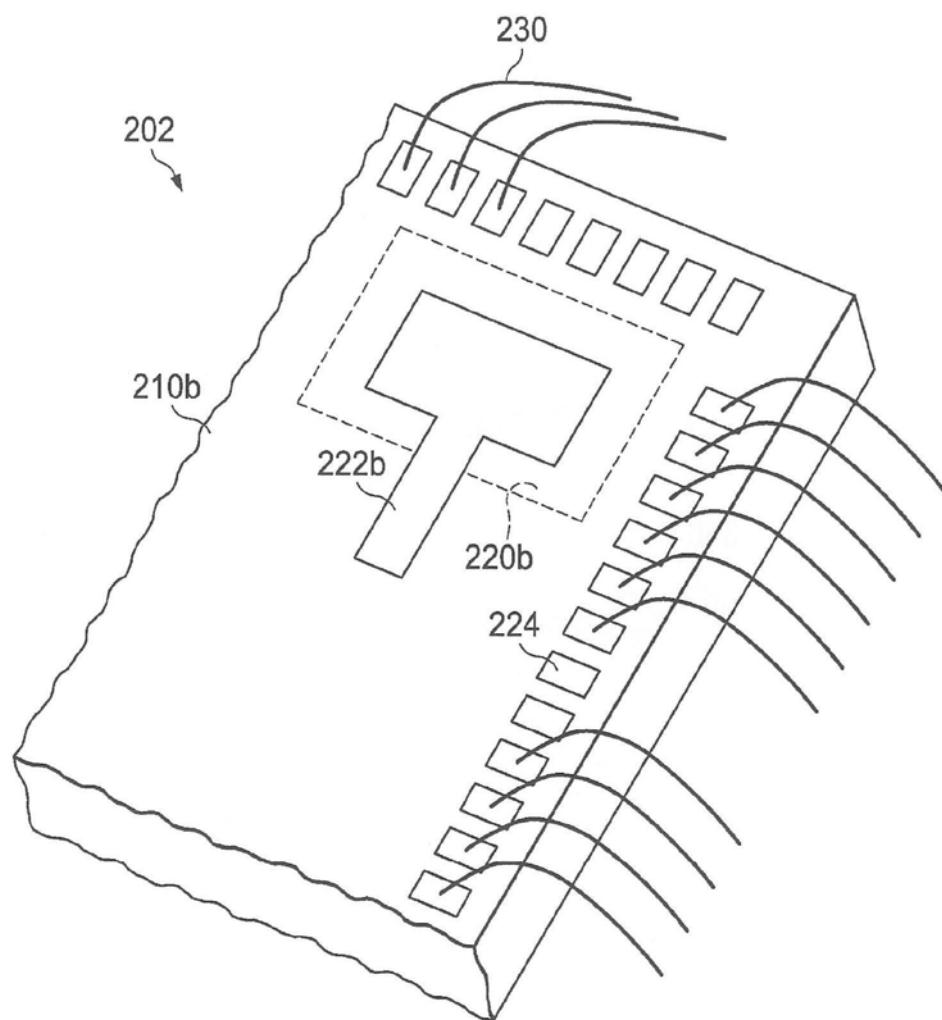

[0008] 图2A及2B说明在IC制造系统内构建的常规顶侧天线。在图2A中,横截面视图200展示半导体衬底210a、形成有源区212的掺杂表面区域以及金属导体堆叠214。在金属导体堆叠中,形成接地平面220a及天线222a,其中天线222a在金属导体堆叠214的最高部分处。金属导体堆叠214可由多层级金属结构形成,其中导体形成在由介电层分离的层级处,例如,在集成电路制造中形成在半导体衬底的表面上方。在图2B中,再次说明此结构的顶视图202,其展示半导体衬底210b、接地平面220b以及天线结构222b。并且,展示多个焊垫224和焊线230以帮助说明这种天线结构形成于半导体衬底(例如硅、锗化硅、砷化镓或其它半导体晶片)的顶侧或电路侧上。在天线222a形成于半导体衬底的顶侧上的情况下,能量朝上远

离晶片或衬底210b的顶侧辐射。

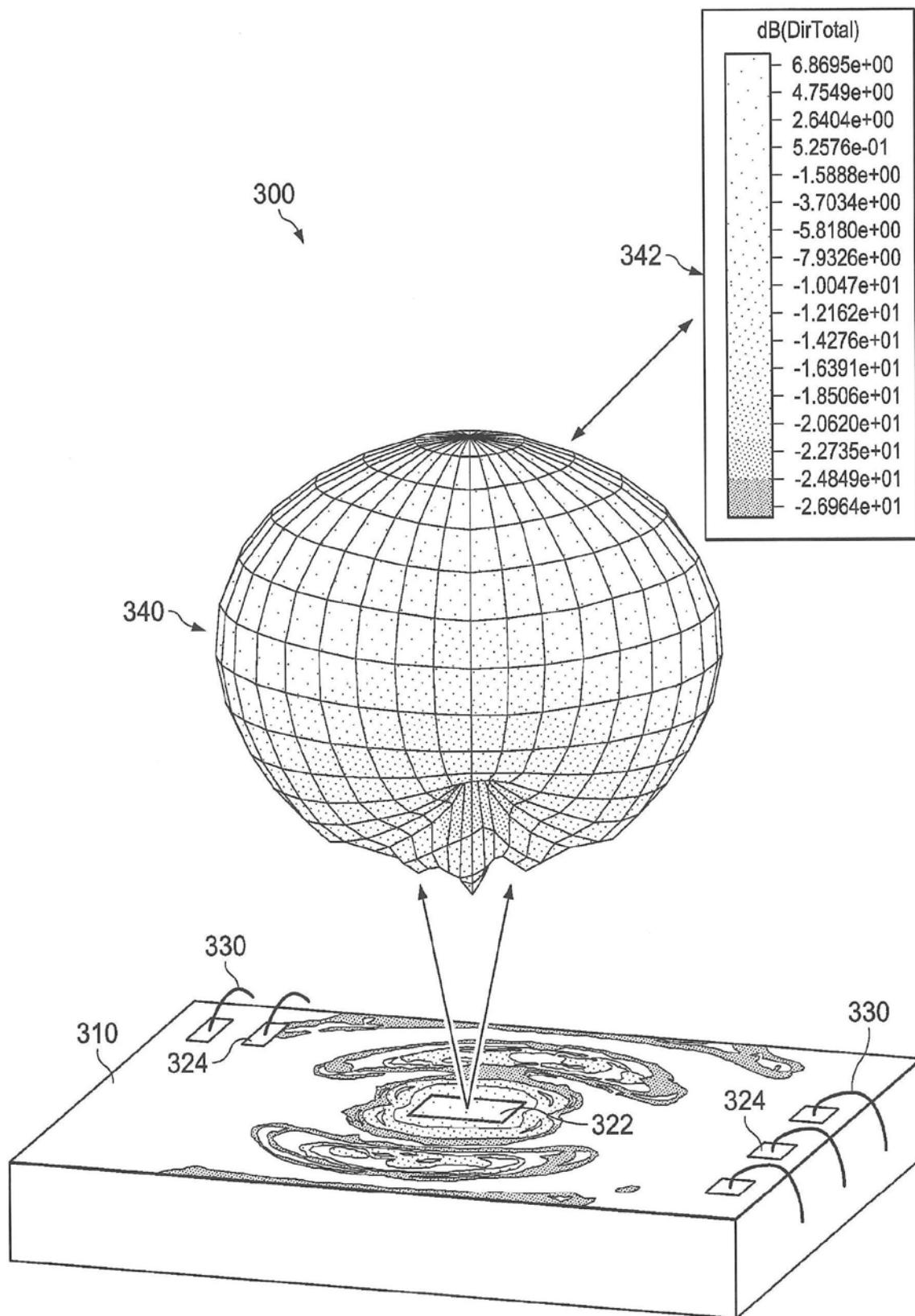

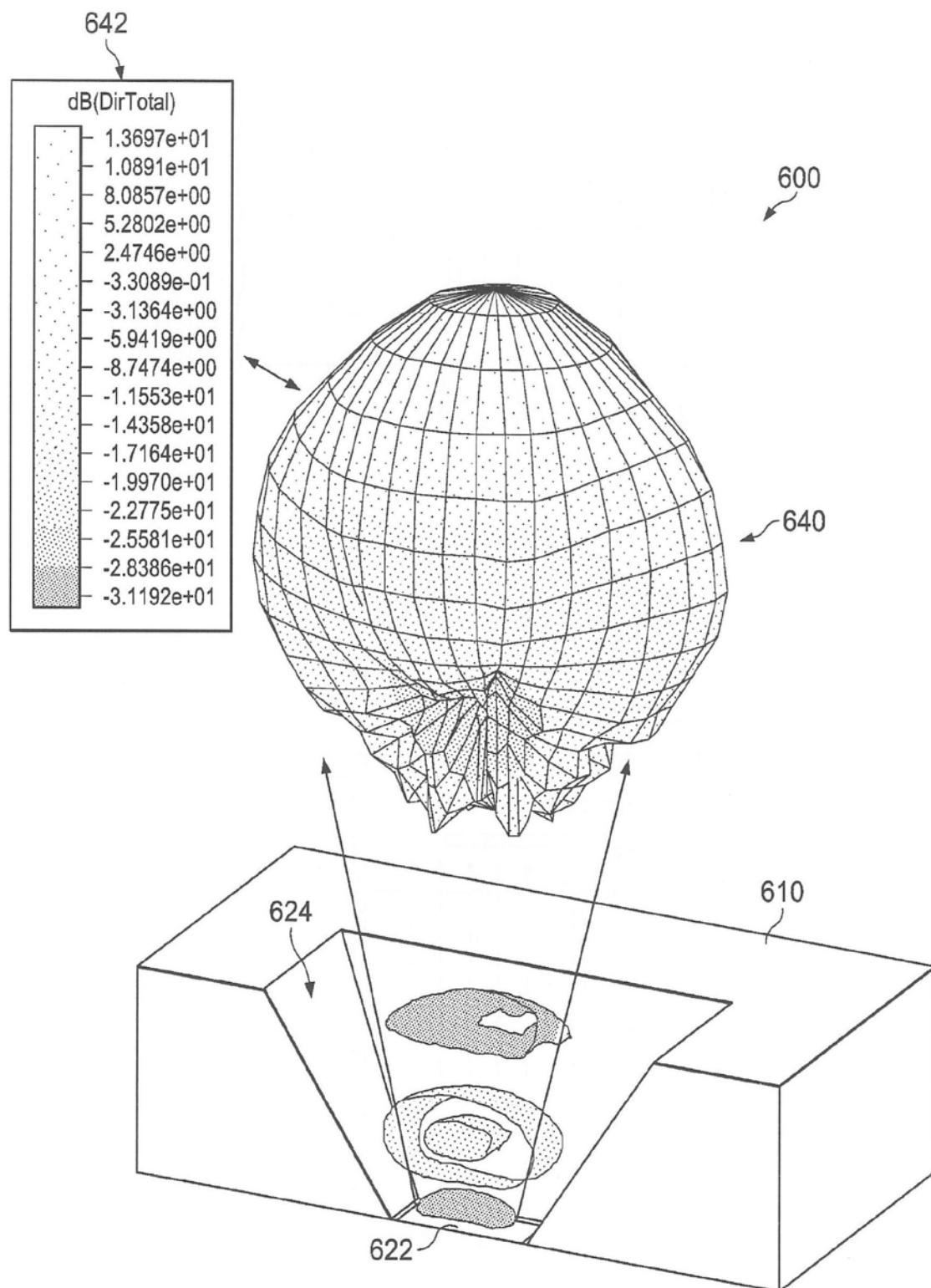

[0009] 图3展示处于操作中的辐射信号的常规顶侧天线300(例如,如图2A及2B中所展示)和相对应的气球图340。图3展示包含晶片或半导体衬底310、顶侧天线322、焊垫324和焊线330的布置300。气球图340表示由操作中的顶侧天线322所辐射的模拟能量。在此布置300中,在模拟中发现峰值增益为大致7dB,如图3的图标尺342及气球图340所指示。

[0010] 因此,需要继续改进方法和耦合器或天线,所述方法与商用半导体工艺兼容且所述耦合器或天线可在THz及次THz频率下有效发射及接收信号。期望较高增益天线能够更有效地将经辐射能量耦合到其它THz组件。

## 发明内容

[0011] 在设备的所描述实例中,半导体衬底具有前侧表面及与所述前侧表面相对的背侧表面。金属导体形成于所述前侧表面上方。至少一个空腔开口蚀刻于所述背侧表面中。辐射或耦合结构形成于所述金属导体的一部分中并配置成通过所述背侧表面中的所述空腔开口辐射信号。

## 附图说明

[0012] 图1A和1B说明信号效率,其展示出具有表面波效应的常规结构中的损耗。

[0013] 图2A及2B说明与IC集成的常规顶侧天线。

[0014] 图3展示常规顶侧天线和说明从所述天线辐射的信号强度的气球图。

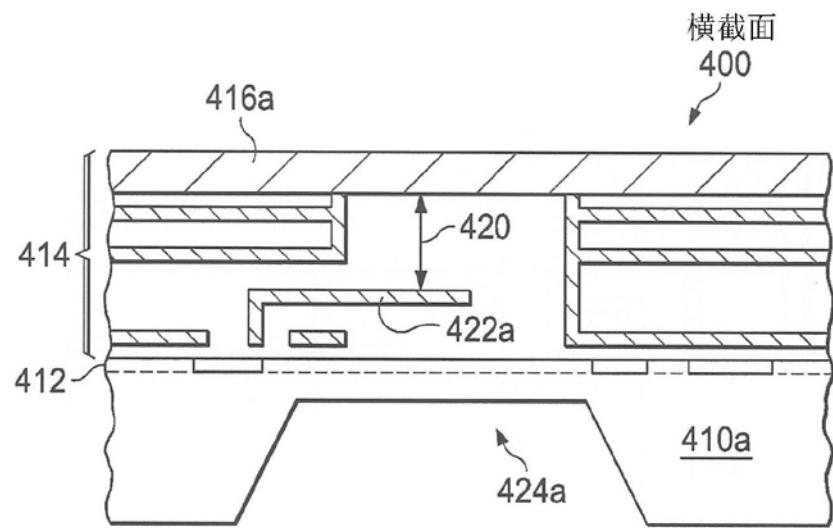

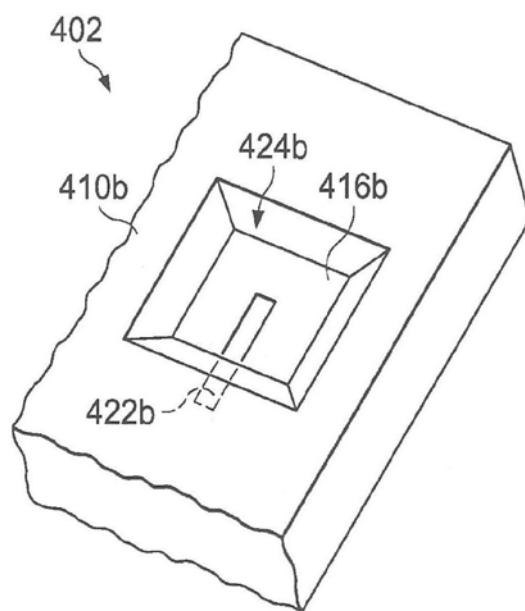

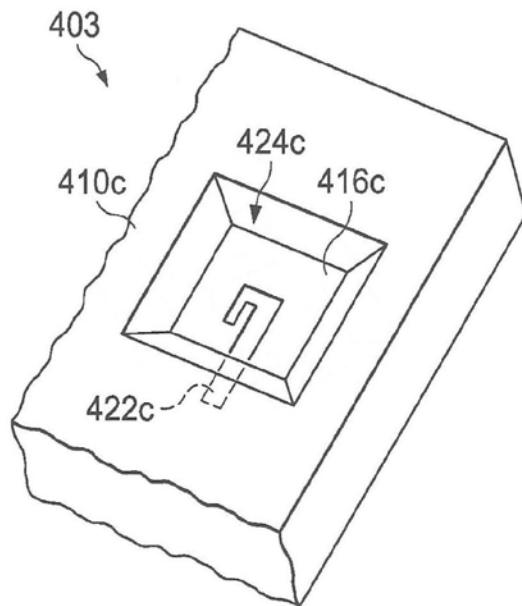

[0015] 图4A、4B及4C说明在CMOS工艺内利用形成于半导体衬底的背侧中的空腔构建的天线布置。

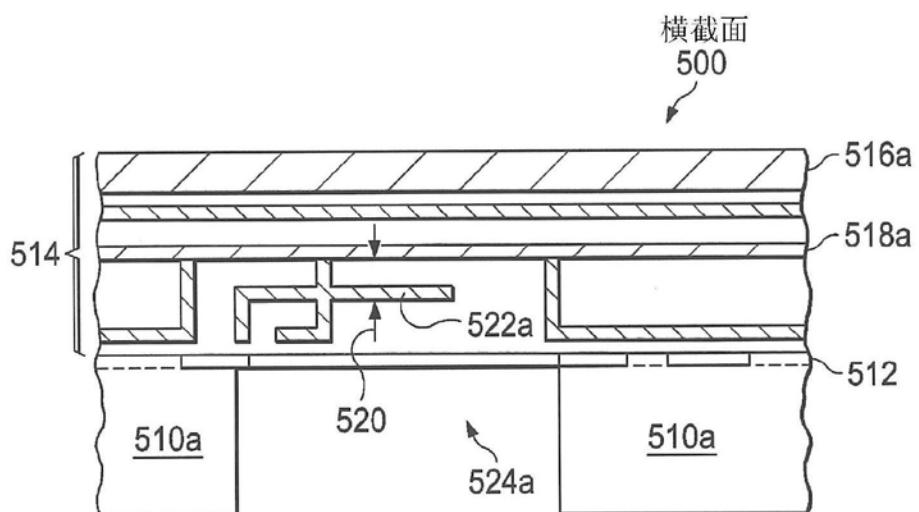

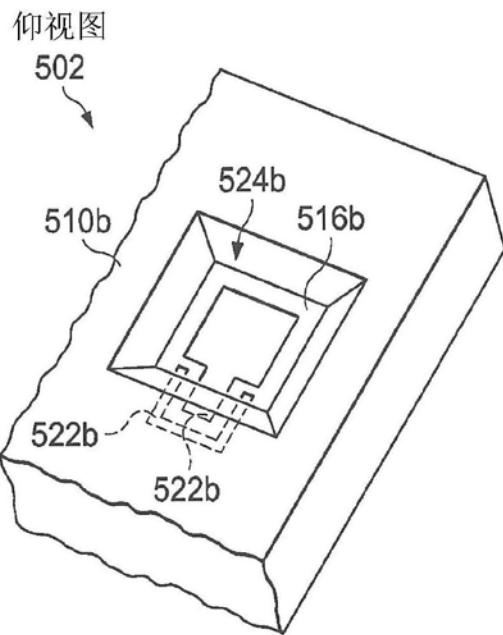

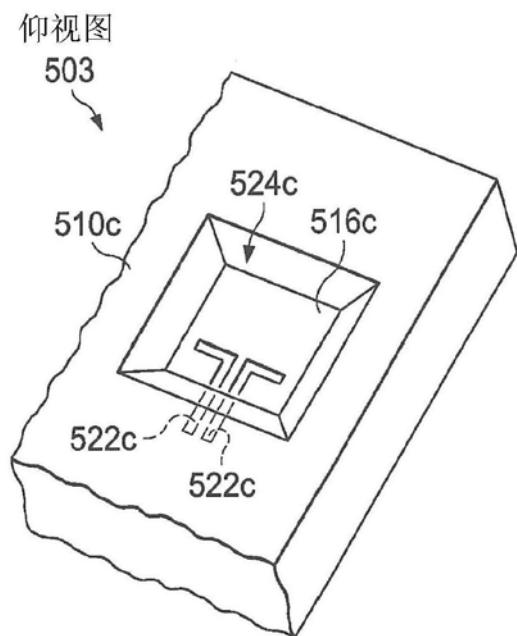

[0016] 图5A、5B及5C说明利用形成于半导体衬底的背侧中的波导构建的另一天线布置。

[0017] 图6展示指示由系统中的背侧天线所辐射的能量的气球图。

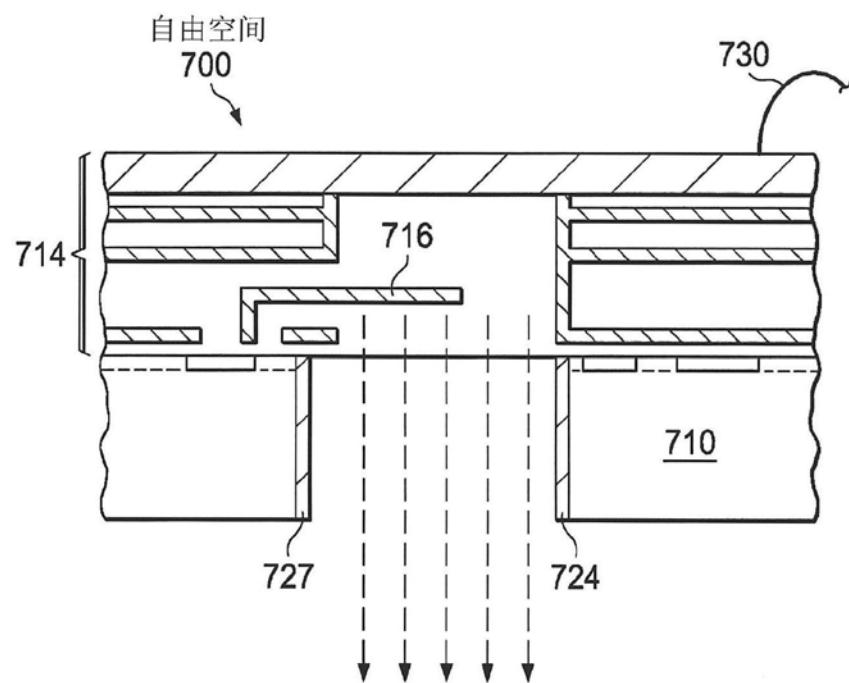

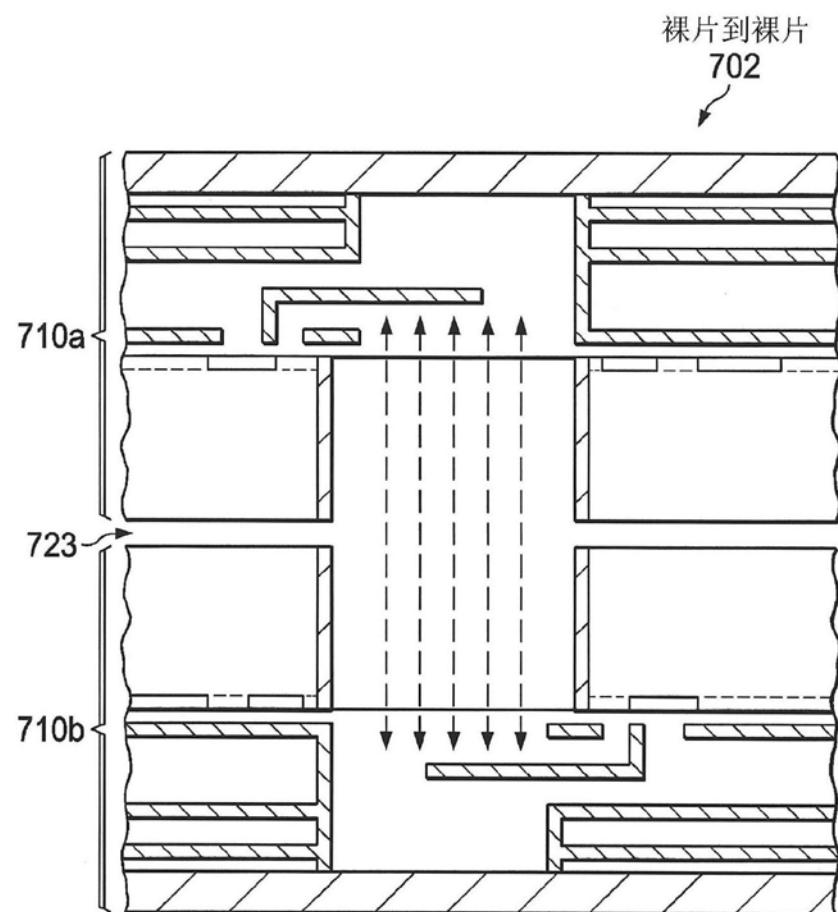

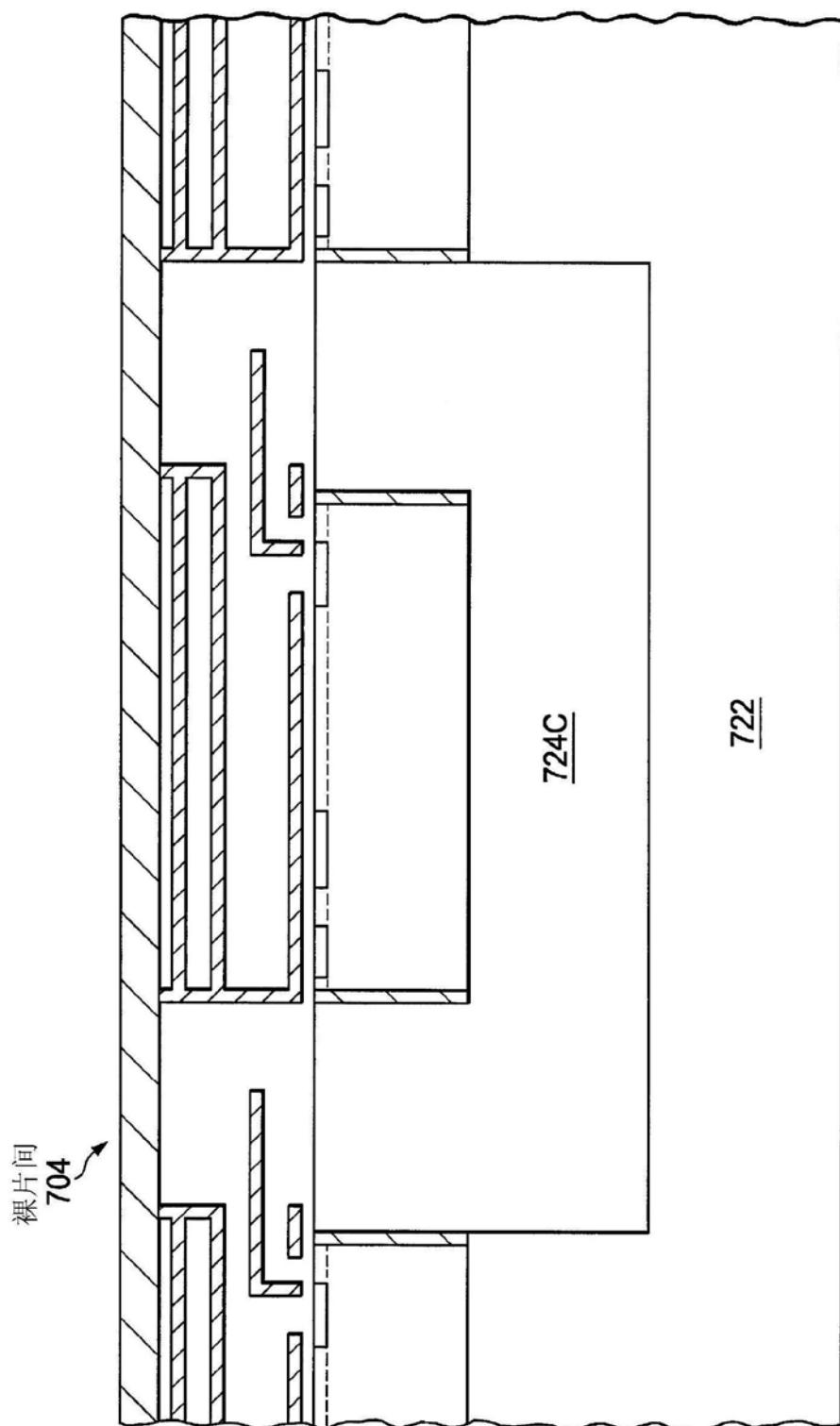

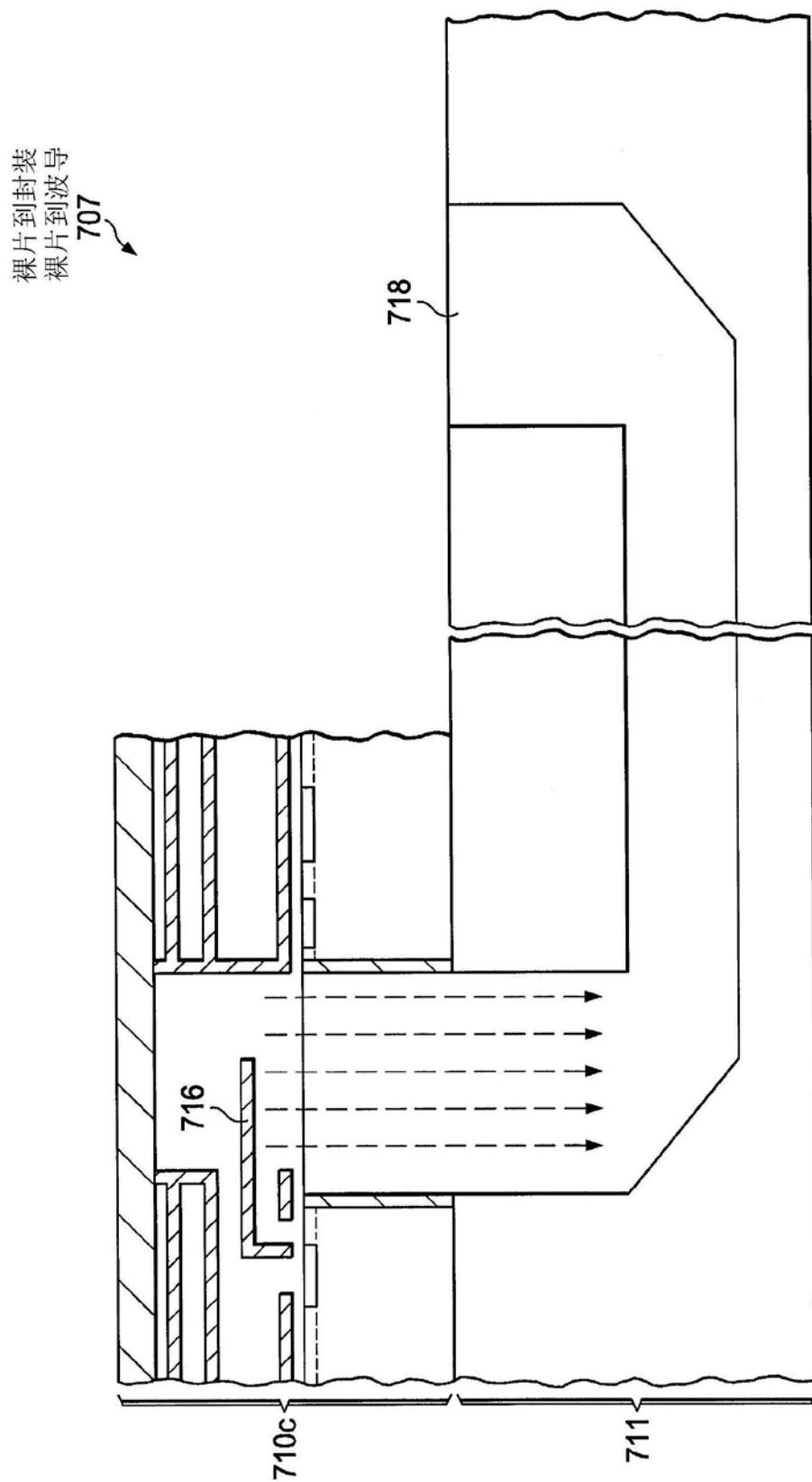

[0018] 图7A、7B、7C及7D展示形成于半导体衬底的背侧中的天线及波导的不同视图来说明几种实例布置。

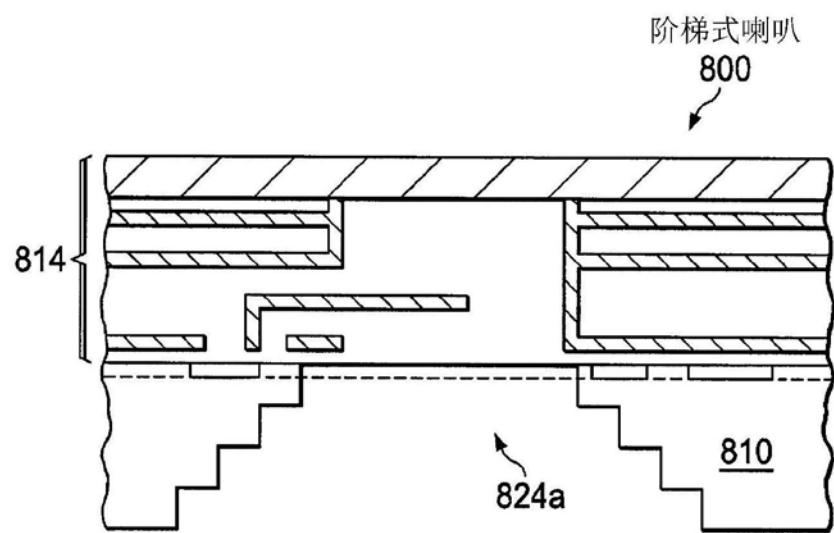

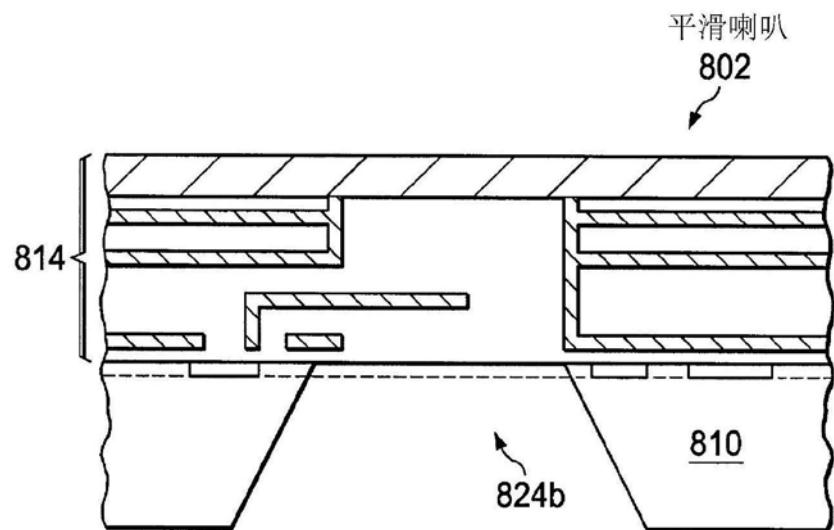

[0019] 图8A、8B及8C展示形成于半导体衬底的背侧上的天线及空腔的额外布置的横截面视图。

## 具体实施方式

[0020] 除非另有指示,否则不同图中的对应标号和符号通常是指对应部分。所述图式未必按比例绘制。

[0021] 实例实施例详述有效辐射及检测来自集成电路、晶片或半导体衬底上所制造的辐射器或耦合结构的THz频率辐射能量的能力。

[0022] 在此描述中,术语“耦合”包含“直接连接”和利用介入元件进行的连接。可在描述为“经耦合”的任何元件之间使用额外元件和各种连接。

[0023] 在所描述实例中,通过用形成在IC的背侧上的空腔来构建天线部分,集成天线将提供从半导体衬底或晶片的背侧引导的次THz及THz辐射以供接收或发射。

[0024] 在衬底的背侧内构建天线使得辐射结构均一平行地定向到接地平面,在辐射器与强化经辐射信号的接地平面反射器之间有精确间距,从而改进增益。并且,实例实施例提供

用于高频信号的天线及耦合结构,其是机械稳固的并与现有半导体制造工艺兼容。

[0025] 此外,实例实施例包含在晶片或衬底内的博导,其使得THz能量能够有效耦合到其它IC、封装、重布层、波导或同一IC上的其它点。

[0026] 至少一个实例实施例包含倒转天线结构以从半导体衬底或晶片的背侧中辐射能量的结构。在各种布置中,使用不同蚀刻技术及工艺以在晶片或半导体衬底的背侧中形成各种空腔或波导,并以不同模式布置在天线或耦合结构下方或接近所述天线或耦合结构。实例实施例相比常规方法改进了经辐射能量的增益特征。并且,实例实施例实现在常规方法不可用于制造次THz及THz天线的额外耦合结构和发射方法。实例实施例提供用于将THz信号从非辐射波导结构中的一点导引到另一点的耦合结构。因为天线或耦合结构形成于晶片的背侧上,所以避免了由常规顶侧天线引发的损耗。如下文中所描述,实例实施例实现另外的优点。空腔可经布置作为波导或天线喇叭。通过控制天线或耦合结构与电或磁性反射器之间的间距和通过改变空腔的形状(包含通过半导体衬底材料的可控蚀刻及通过薄化或控制半导体衬底或晶片的厚度),可以实现重布层或THz波束成形技术。实例实施例提供用于次THz及THz频率信号的高效辐射器及检测器,其无法使用常规方法实现。可以针对先前不可用的高频下的裸片上、裸片到裸片或裸片到封装连接来现使用耦合结构及空腔或波导的THz信令。

[0027] 图4A到4C说明在半导体工艺内利用形成于晶片衬底的背侧中的空腔开口或波导构建的THz天线的实例布置。图4A说明利用常规CMOS加工制造的具有空腔开口或波导424a的晶片410a的横截面400。在衬底410a的表面处的区域412可含有有源或无源电路组件。在使用标准MOS半导体工艺形成的实例布置中,CMOS组件(例如,由MOS晶体管形成的有源电路,且在一些布置中,无源电路,如电容器及电阻器)可形成于有源区412中。举例来说,离子植入、掺杂及扩散工艺可用于形成由沟道间隔的源极区和漏极区,以在区域412中形成有源MOS装置。形成于半导体衬底410a的表面上的金属导体系统414含有至少一个天线结构422a和与天线分隔一定距离420的相对应的反射层416a。金属导体系统的其它部分可用于耦合形成于晶片中或晶片上的组件,如晶体管和电容器。金属导体系统414可由多层级导体形成,所述多层级导体由介电层(例如,氧化硅、氮化硅、氮氧化硅及含碳介电质)电隔离。举例来说,放大器电路可形成于有源区412中并可耦合到天线结构422a,且接收器电路还可形成于有源区412中并耦合到天线422a以用于接收经辐射信号。

[0028] 天线422a的各种物理实施方案是可能的,其中信号通过晶片背侧上的空腔开口或波导424a辐射。图4B及4C中说明两个此类实例。在图4B中,仰视图402展示使用图4A的金属堆叠的电场辐射器。在此实例布置中,已在对应于天线422b的位置处将波导或空腔开口424b蚀刻到晶片衬底410b的背侧中。在一些额外替代布置中,开口424b可以全部延伸穿过半导体衬底,从而使天线暴露于开口,在其它额外布置中,可保持半导体衬底410a或410b的一部分。在图4B中,416b说明形成于天线422b上方(在此仰视图中展示为在天线下方)的金属结构的金属部分,其在此实例布置中充当反射器以将来自天线422b的经辐射能量引导到背侧开口之外。通过使形成于金属416a中的反射器与天线422a间隔开,可形成相长干涉布置。通过所辐射信号的波长 $\lambda$ 来确定间距420。在一个布置中,反射器416b为电反射器,如接地平面,且其将以单位增益和180度相移反射经辐射电磁信号。通过使天线422a以对应于 $\lambda/4$ 的距离420间隔,在天线与反射器416a之间会出现90度相移。接着,以额外180度相移反射

信号,且所述信号经历另外90度相移,在反射器416a/416b与天线422a/422b之间行进。在此布置中,天线处的总相移为360度,以使得经反射信号相长干涉天线416a/416b处的经辐射信号,由此实现增益。可针对所辐射信号的波长(频率的倒数)来调整距离420以获得相长干涉/增益。获得THz频率信号的增益因此容易使用实例实施例实现。此有利结果与常规方法成强烈对比,其中对于所关注的次Thz及Thz频率来说,获得增益是困难或不切实际的,以使得所辐射信号展现出损耗而非增益。在贴片天线布置的情况下,辐射器可如 $\lambda/100$ 一样接近接地平面以仍高效辐射。耦合结构还可如 $\lambda/100$ 一样接近接地平面并执行高效发射,所述耦合结构并非是辐射器或天线,但相反是使用背侧空腔结构发射信号的导体。

[0029] 图4C中说明另一实例实施例。在图4C中,展示磁场耦合天线422c的仰视图403,其中空腔开口或波导424c蚀刻于晶片衬底410c中。经蚀刻开口可延伸穿过衬底以暴露天线422c。然而,在替代布置中,半导体衬底410c的一部分可保持处于较小厚度。说明在天线422c下方的信号反射器416c且其将与天线间隔开,如由如同图4A中的横截面视图400中的距离420所指示。

[0030] 当使用磁性反射层代替电反射器时,出现不同相移。全磁反射器具有为单位增益的反射且具有零度相移。在图4C的实例中,在使用磁性反射器时,因为所反射的电磁能将相长干涉从天线422c辐射的能量,所以间距420可十分近,且因此可以使用所述布置再次实现增益。此方法也适用于图4A及4B的布置以获得增益。

[0031] 可使用人工磁性反射器通过将金属图案图案化到天线上方以形成磁性反射器来实施磁性反射器416c。举例来说,天线或耦合结构422c可在半导体工艺中实施于第一层级金属层中,以使得其接近半导体衬底的表面,且图4B中的电反射器416b(或图4C的磁性反射器416c)可实施于金属结构的上部层级中。例如,如果需要人工磁性反射器,那么各种图案可用于形成反射平面。

[0032] 在常规半导体工艺中,图4A到4C中的金属结构414可形成于半导体工艺的“后段工程”或“BEOL”阶段中。金属结构414中的导体可例如使用单镶嵌或双镶嵌工艺由铜及铜合金形成。举例来说,当在“前段”工艺中使用植入、扩散及退火工艺形成有源区412中的掺杂区之后,越来越多地使用此类工艺来形成金属导体。并且,背侧加工变得更加盛行,以便形成硅穿孔(TSV)的深开口。在实例实施例中,也在BEOL工艺中(或在替代方法中,可在其后)执行经形成为从背侧延伸到半导体衬底中的空腔开口或波导开口。湿式蚀刻(例如KOH、TMAH、HF)及用于半导体材料移除的其它化学湿式蚀刻可用于形成具有倾斜侧的空腔开口,以在所述布置中的不同布置中形成天线喇叭结构。在至少一个实例中,对于硅衬底,KOH化学方法可在具有约57度到水平的角度的开口中形成倾斜侧壁。在另一实例布置中,TMAH湿式蚀刻可用于形成具有约61度的角度的空腔开口。

[0033] 如下文进一步描述,可使用深度反应性离子刻蚀(DRIE)工艺形成具有竖直侧壁的波导或空腔开口。可使用模拟来确定具有用于在特定频率下经辐射能量的高效发射的天线或波导的喇叭形状。可使用波束成形技术来增加天线的效率和输出。并且,模拟可指示高效用于在所选频率下接收经辐射信号的形状(接收与发射为互逆的,辐射及接收图案始终相同)。作为另一替代,可以通过以越来越小的图案重复DRIE或湿式蚀刻工艺来形成阶梯形开口。

[0034] 另外的替代形状可通过使用不同晶片厚度来实现。从晶片背侧机械薄化或“背磨”

可用于薄化晶片以进一步塑形空腔,从而最佳化在所选频率下的电磁能的辐射和检测。背磨可用于移除半导体材料的可控厚度以薄化晶片。移除方法的额外实例包含使用化学机械抛光(CMP)工艺或CMP与机械背磨的组合。

[0035] 在实例布置中,半导体衬底可为如半导体加工中常用的晶片或其一部分。在一个布置实例中,半导体衬底可为硅。在更多替代布置中,半导体衬底可具有其它有用材料,如砷化镓、锗化硅、氮化镓、磷化铟、砷化铟或用于半导体加工或以半导体加工知名的其它“III-V”材料。

[0036] 图5A、5B及5C说明替代布置的三个不同视图,所述替代布置包含在半导体工艺中构建在半导体衬底内的THz天线以及形成于晶片衬底的背侧中的波导。在图5A中,所说明的横截面视图500展示具有波导524a的半导体衬底510a。半导体衬底的表面或晶片中的区域512含有用于集成电路的电路组件。衬底表面上所制造的金属系统514含有天线结构522a和与天线522a分隔一距离520的接地平面518a。在此布置中,距离520具有 $\lambda/10$ 到 $\lambda/8$ 的范围。通过针对所关注的特定频率选择经标记为520的距离,可避免相消干涉,且在一些布置中,可使用相长干涉以将增益增添到从天线522a辐射的信号,其为优于常规方法的优点。可使用频率(如THz及次THz频率)的实例实施例实现增益,在所述实例实施例中,不存在使用常规方法获得增益的切实可行的方式。

[0037] 各种天线结构及各种耦合结构是可能的,其中信号通过背侧开口或波导辐射或通过背侧开口或波导检测。图5B及5C中说明两个额外实例。在图5B中,在一个实例布置中,仰视图502展示通过蚀刻于晶片衬底510b中的背侧波导524b查看的THz天线522b。接地平面516b经展示为在天线后方,且相隔如图5A的横截面500中所指示的距离520。天线522b还可经布置用于其它频率,例如用于毫米波或次THz频率。天线522b还可经布置为检测或接收信号。

[0038] 另一实例实施例展示于图5C的仰视图503中,其中THz天线522c经展示为穿过蚀刻于半导体衬底的背侧上的波导开口524c进入衬底510c或完全穿过衬底510c。在图5C中的天线后面,展示出接地平面516c,且相隔如图5A的横截面500中所指示的距离520。

[0039] 图6展示指示由系统600中的背侧天线622所辐射的能量的气球图640。背侧天线622经展示为经由使用常规工艺蚀刻于衬底610中的背侧开口或波导624辐射能量。气球图640表示由背侧天线经由波导辐射的经模拟能量。在此布置中,峰值增益经模拟为大致14dB,如由图标尺642所指示。在出人意料的结果中,使用实例实施例获得的信号强度可基本上高于使用常规解决方案获得的信号强度。举例来说,如图3中所展示,常规解决方案仅提供约7dB的信号强度。相应地,实例实施例适合于实现约为所关注频率的常规解决方案的性能两倍的性能。

[0040] 各种布置包含可形成于半导体衬底的背侧或晶片上的不同空腔开口或波导形状。波导将使用与用于天线的半导体晶片兼容的半导体加工技术形成。对于极高纵横比蚀刻,可使用DRIE(直接反应性离子蚀刻)工艺。DRIE蚀刻可用作单一蚀刻以形成柱型波导或在多个步骤中随着递增面积形成喇叭型开口或波导。在需要倾斜波导的工艺中,空腔或湿式蚀刻为用于所述形状的常见技术。图7A到7D及8A到8C中展示波导形状及相关联蚀刻的几个实例。

[0041] 图7A到7D展示利用DRIE蚀刻形成的开口或波导或其使用的几个实例的横截面视

图。图7A的集成电路横截面700的一部分含有在具有焊线730的金属结构714内的天线结构716，所述焊线730从金属结构714的顶部突出。竖直空腔或波导724可使用DRIE蚀刻(直接反应性离子蚀刻)工艺蚀刻于晶片衬底710的背侧中。在一些实例布置中，可通过使用兼容的金属化工艺用如图7A中所示的导电层727镀敷来进一步增强空腔。在替代布置中，可省略导电层727。形成于衬底的背侧上的竖直波导724相较常规前侧解决方案产生经改进的定向性和增益。此布置实现信号的自由空间辐射、裸片到裸片信号耦合、裸片间信号耦合、裸片到封装及裸片到波导信号耦合。举例来说，重布层可使用用于Thz信令的这些结构形成。

[0042] 在图7B中，衬底722的横截面704表示裸片间通信波导724c且可在使用兼容的加工蚀刻后或通过嵌入于第二衬底的一部分或其它重布层(RDL)722中的波导形成。如横截面704中所展示，RDL 722可用于将信号从集成电路或晶片的一部分路由到另一部分，从而允许通过波导724c的Thz信号通信而不需要介入元件，例如光学耦合器。

[0043] 在图7C中，展示当前应用的另一方面。在此布置中，使用具有背侧辐射的天线使一对裸片720a、710b彼此电隔离，但仍允许其间的Thz通信。横截面702的两个裸片之间的空间723可构造为隔离气隙。在另一实例布置中，间隙723可填充有绝缘材料以严密地控制天线间距，同时提供裸片对之间的电隔离。以此方式，耦合到不同电位或接地电压的裸片可通信而不连接到共同电位。

[0044] 在图7D中，以横截面706展示另一布置。在此布置中，封装衬底711含有嵌入式波导718，其将来自具有天线或耦合结构716的裸片710c的信号引导到衬底711中的波导718中。衬底波导的另一端处未说明，天线或其它裸片耦合结构可接收信号。因为实例实施例实现Thz频率信令，所以可易于将数据或通信信号从集成电路直接发射到波导而不需要光耦合器或其它介入装置。

[0045] 在替代布置中，波导可为介电波导；也就是说，波导718可填充有介电材料以用于限制或引导Thz频率信号。举例来说，在替代布置中，波导可包含低损耗介电质，如PTFE、PE、PP、石英及陶瓷。

[0046] 图8A到8C展示在衬底或晶片的背侧上的额外波导形成的额外替代布置的横截面视图。在图8A中，可包含有源装置的半导体衬底810的一部分展示于横截面800中，其中金属堆叠814在所述衬底上方。阶梯式波导喇叭824a经展示为使用多次DRIE蚀刻而蚀刻于半导体衬底810的背侧中。举例来说，第一DRIE蚀刻可在衬底的背侧的表面处提供浅开口。接着可执行较窄的第二DRIE蚀刻以在第一开口的边界内形成更深的阶梯式孔。DRIE蚀刻可继续以形成阶梯式结构824a。

[0047] 图8B以横截面802说明替代性布置。在另一方面中，可使用湿式蚀刻方法将光滑喇叭波导824b蚀刻于衬底810中，如图8B中所展示。光滑波导或空腔824b可用于执行裸片到裸片、裸片到RDL、裸片到衬底及裸片到波导耦合，并且还用于自由空间辐射，类似于图7A到7D的各种耦合方法。

[0048] 图8C说明另一实例布置的横截面804。在图8C的横截面804中，具有衬底810a及810b和金属结构814a及814b的一对集成电路裸片经布置用于经由来自其光滑波导喇叭824b的辐射的裸片到裸片耦合。在图8C中，两个裸片之间的电隔离可以通过保留填充空气的裸片823之间的空间来实现。在另一个替代方法中，裸片之间的电隔离可以通过在空间823中的裸片之间插入绝缘材料来实现。

[0049] 在实例布置中,设备包含具有包含电路的前侧表面的半导体衬底和与所述前侧表面相对的背侧表面。金属导体形成于所述前侧表面上方。至少一个空腔开口蚀刻于所述背侧表面中。辐射器(如辐射或耦合结构)形成于金属导体的一部分中且配置成通过所述背侧表面中的空腔开口辐射信号。

[0050] 在另一实例布置中,辐射器形成于上覆半导体衬底的表面的金属导体的层级中。在另外的布置中,所述设备进一步包含反射表面,其与辐射器相间隔并上覆辐射器,且配置成朝向背侧表面中的开口反射信号。在另一布置中,反射表面为电反射器。在又另一布置中,在所述设备中,反射表面以180度相移反射经辐射信号。

[0051] 在更多替代布置中,反射表面与辐射器间隔一距离,所述距离是经辐射信号的波长的分数,介于所述波长的1/10与1/2之间。在又另一布置中,反射表面为磁性反射器。在另一替代布置中,反射表面以0度相移反射经辐射信号。

[0052] 在又另一布置中,经辐射信号的频率在0.1THz与30THz之间。在另外的布置中,经辐射信号的频率为至少约0.1THz。在又另一替代布置中,空腔开口具有倾斜侧壁。在又另一替代布置中,半导体衬底进一步包括有源装置。在又另外的替代布置中,半导体衬底进一步包括金属氧化物半导体晶体管。在另一替代布置中,空腔开口形成用于经辐射信号的波导。在更多替代布置中,空腔开口具有竖直侧壁。在又另一替代布置中,空腔开口涂布有导电材料。在另外的布置中,辐射器形成天线。在又额外布置中,天线进一步配置成接收经辐射信号。在又另一布置中,半导体衬底为硅衬底。

[0053] 在另一布置中,方法包含在半导体衬底的背侧表面上形成背侧空腔开口,所述背侧表面接近形成于上覆所述半导体衬底的前侧表面的金属导体中的辐射器;及从辐射器及通过背侧空腔开口辐射具有0.1THz与约30THz之间的频率范围的信号。在另一布置中,形成背侧空腔开口进一步包含背磨所述半导体衬底以将所述半导体衬底薄化到预定厚度。在又另一布置中,所述方法包含形成背侧空腔开口,其进一步包含执行湿式蚀刻以形成具有倾斜侧壁的开口。

[0054] 在又另一替代布置中,形成背侧空腔开口进一步包括执行KOH湿式蚀刻。在又另一替代布置中,形成背侧空腔开口进一步包含执行TMAH湿式蚀刻。在另一替代布置中,形成背侧空腔进一步包含执行湿式蚀刻以形成具有倾斜侧壁的开口。

[0055] 在又另一替代布置中,形成背侧空腔开口进一步包含执行深度反应性离子蚀刻。在另一替代例中,背侧空腔开口具有竖直侧壁。

[0056] 在另一布置中,系统包含第一集成电路,其具有:用于辐射THz频率信号的天线,所述天线形成于上覆第一半导体衬底的表面的金属结构中,及第一开口,所述第一开口形成于所述第一半导体衬底的背侧中并在对应于所述天线的位置处延伸到所述半导体衬底中;及第二集成电路,其具有:用于接收THz频率信号的天线,所述天线形成于上覆第二半导体衬底的表面的金属结构中,及第二开口,所述第二开口形成于所述第二半导体衬底的背侧中;所述第一开口和所述第二开口面向彼此并彼此对准,以便于将所述THz信号从所述第一集成电路发射到所述第二集成电路。

[0057] 另一布置提供第一集成电路与第二集成电路之间的空间。在又另一布置中,电隔离材料安置于第一集成电路与第二集成电路之间。在又另一布置中,第一开口及第二开口进一步包括波导。在另一布置中,第一开口及第二开口进一步包括具有倾斜侧壁的开口。在

又另一布置中,第一开口及第二开口进一步包括具有竖直侧壁的开口。

[0058] 步骤的次序或步骤的数目有可能有各种修改,以形成实例实施例的额外布置。

[0059] 在所描述的实施例中可能有修改,且在权利要求书的范围内,其它实施例是可能的。

图1A

图1B

图2A (现有技术)

图2B(现有技术)

图3(现有技术)

图4A

图4B

图4C

图5A

图5B

图5C

图7A

图7C

图7B

图7D

图8A

图8B

图8C