(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7584516号

(P7584516)

(45)発行日 令和6年11月15日(2024.11.15)

(24)登録日 令和6年11月7日(2024.11.7)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3266(2016.01) | F I | G 0 9 G | 3/3266       |

| G 0 9 G | 3/3233(2016.01) |     | G 0 9 G | 3/3233       |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/20 6 2 2 E |

| G 0 9 F | 9/30 (2006.01)  |     | G 0 9 G | 3/20 6 2 2 M |

| H 1 0 K | 59/10 (2023.01) |     | G 0 9 G | 3/20 6 2 2 K |

請求項の数 17 (全32頁) 最終頁に続く

|             |                             |

|-------------|-----------------------------|

| (21)出願番号    | 特願2022-528658(P2022-528658) |

| (86)(22)出願日 | 令和2年4月28日(2020.4.28)        |

| (65)公表番号    | 特表2023-531843(P2023-531843) |

|             | A)                          |

| (43)公表日     | 令和5年7月26日(2023.7.26)        |

| (86)国際出願番号  | PCT/CN2020/087637           |

| (87)国際公開番号  | WO2021/217468               |

| (87)国際公開日   | 令和3年11月4日(2021.11.4)        |

| 審査請求日       | 令和5年4月21日(2023.4.21)        |

|          |                                                                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 510280589<br>京東方科技集團股 ふん 有限公司<br>B O E T E C H N O L O G Y G R O U P C O . , L T D .<br>中華人民共和国 1 0 0 0 1 5 北京市朝陽<br>區酒仙橋路 10 號<br>N o . 1 0 J i u x i a n q i a o R<br>d . , C h a o y a n g D i s t r i<br>c t , B e i j i n g 1 0 0 0 1 5 ,<br>C H I N A |

| (73)特許権者 | 511121702<br>成都京東方光電科技有限公司<br>C H E N G D U B O E O P T O E L E<br>C T R O N I C S T E C H N O L O G Y<br>C O . , L T D .                                                                                                                                   |

最終頁に続く

(54)【発明の名称】 ディスプレイパネル、駆動方法およびディスプレイデバイス

## (57)【特許請求の範囲】

## 【請求項 1】

ディスプレイパネルであって、

前記ディスプレイパネルは、表示領域および非表示領域を含むベース基板を備え、

前記表示領域は、

複数の行および複数の列に沿ってマトリックスモードで配置される複数のサブピクセルと、

サブピクセルの1つの行が、少なくとも1つの駆動線に対応して電気的に接続されている、複数の駆動線と、

前記サブピクセルの1つの列がデータラインの少なくとも1つに対応して電気的に接続されている複数のデータラインと

を含み、

前記非表示領域は、ゲート駆動回路を含み、

前記ゲート駆動回路は、複数のクロック信号線および前記クロック信号線の延長方向に順次配列された複数のシフトレジスタユニットを含み、前記複数のクロック信号線が複数のクロック信号線グループに分割され、

前記複数のシフトレジスタユニットは、複数のレジスタユニットグループに分割され、ここで、同じ前記レジスタユニットグループ内のすべての前記シフトレジスタユニットがカスケード接続され、前記クロック信号線の延長方向に隣接する2つのシフトレジスタユニットが異なるレジスタユニットグループに配置され、また、異なる前記レジスタユニット

トグループは、異なる前記クロック信号線グループに対応し、

各前記シフトレジスタユニットは、入力トランジスタおよび出力トランジスタを含み、前記入力トランジスタのゲートは、対応する前記クロック信号線グループ内の1つのクロック信号線に電気的に接続され、前記入力トランジスタの第1の極は、入力信号端に電気的に接続され、前記入力トランジスタの第2の極は、前記出力トランジスタのゲートに電気的に接続され、前記出力トランジスタの第2の極は、対応して、少なくとも1つの駆動線に電気的に接続されており、

前記ディスプレイパネルは、半導体層と、ゲート絶縁層と、第1の導電層と、第1の絶縁層と、第2の導電層とをさらに含み、

前記半導体層は、前記ベース基板上に配置され、かつ、前記半導体層は、前記入力トランジスタの活性層および前記出力トランジスタの活性層を含み、前記活性層は、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域との間のチャネル領域とを含み、

前記ゲート絶縁層は、前記半導体層の前記ベース基板とは反対側に面する側に配置され、前記第1の導電層は、前記ゲート絶縁層の前記ベース基板とは反対側に面する側に配置され、かつ、前記第1の導電層は、前記複数の駆動線と、複数の第1の接続線と、複数の第2の接続線と、前記入力トランジスタのゲートと、前記出力トランジスタのゲートとを含み、1つの前記シフトレジスタユニットは、少なくとも1つの前記第1の接続線および少なくとも1つの前記第2の接続線に対応し、

前記第1の絶縁層は、前記第1の導電層の前記ベース基板とは反対側に面する側に配置され、

前記第2の導電層は、前記第1の絶縁層の前記ベース基板とは反対側に面する側に配置され、かつ、前記第2の導電層は、前記複数のクロック信号線と、複数の第1の転送部とを含み、ここで、1つの前記第1の転送部は、1つの前記出力トランジスタの活性層のソース領域に電気的に接続され、前記第2の導電層は、第1の電力線をさらに含み、

1つの前記シフトレジスタユニットおよび前記シフトレジスタユニットに対応する前記クロック信号線グループの場合、前記第1の接続線の一方の端は、前記シフトレジスタユニットの入力トランジスタのゲートに直接電気的に接続され、前記第1の接続線のもう一方の端は、第1のビアホールを介して前記クロック信号線グループ内の1つのクロック信号線に電気的に接続され、前記第2の接続線の一方の端は、第2のビアホールを介して前記第1の転送部に電気的に接続され、

前記第1のビアホール、前記第2のビアホールは、間隔を置いて形成されることを特徴とするディスプレイパネル。

### 【請求項2】

前記第2の接続線のもう一方の端は第3のビアホールを介して前記クロック信号線グループ内の別のクロック信号線、または第1の電力線に電気的に接続され、

前記第1のビアホール、前記第2のビアホールおよび前記第3のビアホールは、前記第1の絶縁層を貫通し、間隔を置いて形成されることを特徴とする請求項1に記載のディスプレイパネル。

### 【請求項3】

前記複数のクロック信号線は2つのクロック信号線グループに分割され、前記2つのクロック信号線グループは、第1のクロック信号線グループおよび第2のクロック信号線グループを含み、前記第1のクロック信号線グループは、第1のクロック信号線および第2のクロック信号線を含み、前記第2のクロック信号線グループは、第3のクロック信号線および第4のクロック信号線を含み、

前記複数のシフトレジスタユニットは、2つのレジスタユニットグループに分割され、前記2つのレジスタユニットグループは、第1のレジスタユニットグループおよび第2のレジスタユニットグループを含み、前記第1のレジスタユニットグループは、前記クロック信号線の延長方向に順次配列された奇数番目のシフトレジスタユニットを含み、第2のレジスタユニットグループは、前記クロック信号線の延長方向に順次配列された偶数番目

10

20

30

40

50

のシフトレジスタユニットを含み、

前記第1のレジスタユニットグループのカスケード接続された複数のシフトレジスタユニットの場合、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して前記第1のクロック信号線に電気的に接続され、前記奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して前記第2のクロック信号線に電気的に接続されるか、または第1の電力線に電気的に接続され、および、偶数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して前記第2のクロック信号線に電気的に接続され、前記偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して前記第1のクロック信号線に電気的に接続されるか、または第1の電力線に電気的に接続され、

前記第2のレジスタユニットグループのカスケード接続された複数のシフトレジスタユニットの場合、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して前記第3のクロック信号線に電気的に接続され、前記奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して前記第4のクロック信号線に電気的に接続されるか、または第1の電力線に電気的に接続され、および、前記偶数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して前記第4のクロック信号線に電気的に接続され、前記偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して前記第3のクロック信号線に電気的に接続されるか、または第1の電力線に電気的に接続されることを特徴とする請求項2に記載のディスプレイパネル。

#### 【請求項4】

各前記シフトレジスタユニットは、電圧安定化トランジスタをさらに含み、前記入力トランジスタの第2の極は、前記電圧安定化トランジスタの第1の極に電気的に接続され、前記電圧安定化トランジスタの第2の極は、前記出力トランジスタのゲートに電気的に接続され、

前記第2の導電層は、第1の電力線をさらに含み、各前記電圧安定化トランジスタのゲートは、第4のビアホールを介して前記第1の電力線に電気的に接続され、前記第4のビアホールは、前記第1の絶縁層を貫通することを特徴とする請求項3に記載のディスプレイパネル。

#### 【請求項5】

同じ前記ゲート駆動回路において、前記ベース基板上の前記入力トランジスタの正投影は、前記第1の前記ベース基板上の電力線の正投影と前記ベース基板上の前記複数のクロック信号線の正投影との間にあり、

前記ベース基板上の前記電圧安定化トランジスタの正投影は、前記ベース基板上の前記複数のクロック信号線の正投影とは反対側に面する、前記第1の前記ベース基板上の電力線の正投影の片側にあり、

前記ベース基板上の前記出力トランジスタの正投影は、前記第1の前記ベース基板上の電力線の正投影とは反対側に面する、前記ベース基板上の前記電圧安定化トランジスタの正投影の片側にあることを特徴とする請求項4に記載のディスプレイパネル。

#### 【請求項6】

前記シフトレジスタユニットは、第1の制御トランジスタと、第2の制御トランジスタとをさらに含み、

前記半導体層は、前記第1の制御トランジスタの活性層および前記第2の制御トランジスタの活性層をさらに含み、

前記第1の導電層は、前記第1の制御トランジスタのゲートおよび前記第2の制御トランジスタのゲートをさらに含み、

前記第2の導電層は、第2の電力線と、複数の第2の転送部と、複数の第3の転送部とをさらに含み、ここで、1つの前記第2の転送部は、1つの前記第1の制御トランジスタに対応し、1つの前記第3の転送部は、1つの前記第2の制御トランジスタに対応し、

10

20

30

40

50

また、前記ディスプレイパネルは、第4の導電層と、第3の絶縁層とを含み、前記第4の導電層は、前記第1の絶縁層と前記第2の導電層との間にあり、かつ、前記第4の導電層は複数の第1の導電部を含み、1つの前記第1の導電部は、1つの前記第2の制御トランジスタに対応し、

前記第3の絶縁層は、前記第4の導電層と前記第2の導電層との間にあり、

前記第1の制御トランジスタのゲートは、対応する第1の接続線に直接電気的に接続され、前記第1の制御トランジスタの活性層のソース領域は、第5のビアホールを介して前記第1の電力線に電気的に接続され、前記第1の制御トランジスタの活性層のドレイン領域は、対応する前記第2の転送部を介して前記第2の制御トランジスタのゲートに電気的に接続され、前記第5のビアホールは、前記第1の絶縁層および前記第3の絶縁層を貫通し、

前記第2の制御トランジスタの活性層のソース領域は、第6のビアホールを介して対応する前記第3の転送部の一方の端に電気的に接続され、前記第3の転送部のもう一方の端は、第7のビアホールを介して対応する前記第1の導電部の一方の端に電気的に接続され、前記第1の導電部のもう一方の端は、第8のビアホールを介して前記第2の電力線に電気的に接続され、前記第2の制御トランジスタの活性層のドレイン領域は、前記出力トランジスタの活性層のドレイン領域と共有され、前記第6のビアホールは、前記第1の絶縁層および前記第3の絶縁層を貫通し、前記第7のビアホールおよび前記第8のビアホールは、前記第3の絶縁層を貫通することを特徴とする請求項3から請求項5のいずれか一項に記載のディスプレイパネル。

#### 【請求項7】

前記ベース基板上の前記第2の電力線の正投影は、前記ベース基板上の前記複数のクロック信号線の正投影と前記ベース基板上の前記ゲート駆動回路の正投影との間にあり、

前記シフトレジスタユニットにおいて、前記ベース基板上の前記第1の制御トランジスタの正投影は、前記ベース基板上の前記入力トランジスタの正投影と前記第1の前記ベース基板上の電力線の正投影との間にあり、

前記シフトレジスタユニットにおいて、前記ベース基板上の前記第2の制御トランジスタの正投影は、前記第1の前記ベース基板上の電力線の正投影とは反対側に面する、前記ベース基板上の前記入力トランジスタの正投影の片側にあることを特徴とする請求項6に記載のディスプレイパネル。

#### 【請求項8】

前記シフトレジスタユニットにおいて、前記出力トランジスタの活性層および前記第2の制御トランジスタの活性層は、統合された構造で配置されることを特徴とする請求項7に記載のディスプレイパネル。

#### 【請求項9】

前記シフトレジスタユニットは、第1のコンデンサおよび第2のコンデンサをさらに含み、前記第1のコンデンサの第1の極は、前記第2の電力線に電気的に接続され、前記第1のコンデンサの第2の極は、前記第2の制御トランジスタのゲートに電気的に接続され、前記第2のコンデンサの第1の極は、前記出力トランジスタの第2の極に電気的に接続され、前記第2のコンデンサの第2の極は、前記出力トランジスタのゲートに電気的に接続され、

前記第4の導電層は、複数の第2の導電部をさらに含み、ここで、1つの前記第2の導電部は、1つの前記出力トランジスタに対応し、

前記ベース基板上の前記第1の導電部の正投影および前記ベース基板上の前記第2の制御トランジスタのゲートの正投影は、重複領域を有し、かつ、前記第1の導電部は、前記第1のコンデンサの第1の極として機能し、前記第2の制御トランジスタのゲートは、前記第1のコンデンサの第2の極として機能し、

前記ベース基板上の前記第2の導電部の正投影および前記ベース基板上の対応する前記出力トランジスタのゲートの正投影は、重複領域を有し、かつ、前記第2の導電部は、前記第2のコンデンサの第1の極として機能し、前記出力トランジスタのゲートは、前記第

10

20

30

40

50

2のコンデンサの第2の極として機能することを特徴とする請求項6から請求項8のいずれか一項に記載のディスプレイパネル。

【請求項10】

前記ベース基板上の前記第2の制御トランジスタのゲートの正投影は、前記ベース基板上の前記第1の導電部の正投影を覆うことを特徴とする請求項9に記載のディスプレイパネル。

【請求項11】

前記ベース基板上の前記第2の制御トランジスタのゲートの正投影および前記ベース基板上の前記第1の導電部の正投影それぞれは、前記第1の前記ベース基板上の電力線の正投影と重複領域を有することを特徴とする請求項10に記載のディスプレイパネル。

10

【請求項12】

前記ベース基板上の前記第8のビアホールの正投影は、前記第1の電力線と前記第2の前記ベース基板上の電力線の正投影との間にあり、前記ベース基板上の前記第7のビアホールの正投影は、前記第1の前記ベース基板上の電力線の正投影と前記ベース基板上の前記第2の制御トランジスタの活性層の正投影との間にあることを特徴とする請求項6から請求項11のいずれか一項に記載のディスプレイパネル。

【請求項13】

前記ディスプレイパネルは、第2の絶縁層と、第3の導電層とをさらに備え、前記第2の絶縁層は、前記第2の導電層の前記ベース基板とは反対側に面する側にあり、前記第3の導電層は、前記第2の絶縁層の前記ベース基板とは反対側に面する側にあり、かつ、前記第2の導電層は、少なくとも1つの補助線を含み、

20

1つの前記補助線および1つの前記クロック信号線は、少なくとも1つの第9のビアホールを介して電気的に接続され、かつ、前記第9のビアホールは、前記第2の絶縁層を貫通することを特徴とする請求項2から請求項12のいずれか一項に記載のディスプレイパネル。

【請求項14】

前記ベース基板上の前記クロック信号線の正投影は、前記ベース基板上の電気的に接続された補助線の正投影を覆うことを特徴とする請求項13に記載のディスプレイパネル。

【請求項15】

請求項1から請求項14のいずれか一項に記載のディスプレイパネルを含む、ディスプレイデバイス。

30

【請求項16】

ディスプレイパネルの駆動方法であって、1フレームのスキャン時間において、すべての前記シフトレジスタユニットを制御して、すべての前記駆動線を行ごとに順次スキャンするように制御するステップを備え、前記クロック信号線の延長方向に順次配列された奇数番目のシフトレジスタユニットおよび偶数番目のシフトレジスタユニットは、異なるクロック信号線グループの制御下で独立して駆動されることを特徴とする請求項1から請求項14のいずれか一項に記載のディスプレイパネルの駆動方法。

40

【請求項17】

異なるクロック信号線グループの複数のクロック信号線に印加される信号の、アクティペレルを維持するための時間は、お互いに重複しないことを特徴とする請求項16に記載のディスプレイパネルの駆動方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ディスプレイの技術分野に関し、特にディスプレイパネル、駆動方法、およびディスプレイデバイスに関する。

【背景技術】

【0002】

50

ディスプレイ技術の急速な発展に伴い、ディスプレイデバイスは、高度な統合および低コストの開発傾向を示している。アレイ上のゲートドライバー (Gate Driver on Array, GOA、アレイ基板行ドライブ) テクノロジーは、ディスプレイパネルのベース基板上に薄膜トランジスタ (Thin Film Transistor, TFT) ゲート駆動回路を統合して、ディスプレイパネルのスキャンドライブを形成し、それによってゲート集積回路 (IC, Integrated Circuit) のボンディング (Bonding) とファンアウト (Fan-out) 領域の配線スペースを節約し、製品コストを削減する。

【発明の概要】

【0003】

10

本発明の実施形態によって提供されるディスプレイパネルは、表示領域および非表示領域を含むベース基板を備え、前記表示領域は、複数の行および複数の列に沿ってマトリックスモードで配置される複数のサブピクセルと、

サブピクセルの1つの行が、少なくとも1つの駆動線に対応して電気的に接続されている、複数の駆動線と、

前記サブピクセルの1つの列がデータラインの少なくとも1つに対応して電気的に接続されている複数のデータラインとを含み、

前記非表示領域は、

複数のクロック信号線と、前記クロック信号線の延長方向に順次配列された複数のシフトレジスタユニットとを備えるゲート駆動回路を含み、前記複数のクロック信号線が複数のクロック信号線グループに分割され、

前記複数のシフトレジスタユニットは、複数のレジスタユニットグループに分割され、ここで、同じ前記レジスタユニットグループ中のすべての前記シフトレジスタユニットがカスケード接続され、前記クロック信号線の延長方向に隣接する2つのシフトレジスタユニットが異なるレジスタユニットグループに配置され、また、異なる記レジスタユニットグループは、異なる記クロック信号線グループに対応し、

各前記シフトレジスタユニットは、入力トランジスタおよび出力トランジスタを含み、前記入力トランジスタのゲートは、対応する前記クロック信号線グループ内の1つのクロック信号線に電気的に接続され、前記入力トランジスタの第1の極は、入力信号端に電気的に接続され、前記入力トランジスタの第2の極は、前記出力トランジスタのゲートに電気的に接続され、前記出力トランジスタの第2の極は、対応して、少なくとも1つの駆動線に電気的に接続されている。

【0004】

任意選択で、本発明の実施形態において、前記ディスプレイパネルは、半導体層と、ゲート絶縁層と、第1の導電層と、第1の絶縁層と、第2の導電層とをさらに備え、

前記半導体層は、前記ベース基板上に配置され、かつ、前記半導体層は、前記入力トランジスタの活性層および前記出力トランジスタの活性層を含み、前記活性層は、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域との間のチャネル領域とを含み、

前記ゲート絶縁層は、前記半導体層の前記ベース基板とは反対側に面する側に配置され、前記第1の導電層は、前記ゲート絶縁層の前記ベース基板とは反対側に面する側に配置され、かつ、前記第1の導電層は、前記複数の駆動線と、複数の第1の接続線と、複数の第2の接続線と、前記入力トランジスタのゲートと、前記出力トランジスタのゲートとを含み、1つの前記シフトレジスタユニットは、少なくとも1つの前記第1の接続線および少なくとも1つの前記第2の接続線に対応し、

前記第1の絶縁層は、前記第1の導電層の前記ベース基板とは反対側に面する側に配置され、

前記第2の導電層は、前記第1の絶縁層の前記ベース基板とは反対側に面する側に配置

20

30

40

50

され、かつ、前記第2の導電層は、前記複数のデータラインと、前記複数のクロック信号線と、複数の第1の転送部とを含み、ここで、1つの前記第1の転送部は、1つの前記出力トランジスタの活性層のソース領域に電気的に接続され、前記第2の導電層は、第1の電力線をさらに含み、

1つの前記シフトレジスタユニットおよび前記シフトレジスタユニットに対応する前記クロック信号線グループの場合、前記第1の接続線の一方の端は、前記シフトレジスタユニットの入力トランジスタのゲートに直接電気的に接続され、前記第1の接続線のもう一方の端は、第1のビアホールを介して前記クロック信号線グループ内の1つのクロック信号線に電気的に接続され、前記第2の接続線の一方の端は、第2のビアホールを介して前記第1の転送部に電気的に接続され、前記第2の接続線のもう一方の端は第3のビアホールを介して前記クロック信号線グループ内の別のクロック信号線、または第1の電力線に電気的に接続され、

前記第1のビアホール、前記第2のビアホールおよび前記第3のビアホールは、前記第1の絶縁層を貫通し、間隔を置いて形成される。

#### 【0005】

任意選択で、本発明の実施形態において、前記複数のクロック信号線は2つのクロック信号線グループに分割され、前記2つのクロック信号線グループは、第1のクロック信号線グループおよび第2のクロック信号線グループを含み、前記第1のクロック信号線グループは、第1のクロック信号線および第2のクロック信号線を含み、前記第2のクロック信号線グループは、第3のクロック信号線および第4のクロック信号線を含み、

前記複数のシフトレジスタユニットは、2つのレジスタユニットグループに分割され、前記2つのレジスタユニットグループは、第1のレジスタユニットグループおよび第2のレジスタユニットグループを含み、前記第1のレジスタユニットグループは、前記クロック信号線の延長方向に順次配列された奇数番目のシフトレジスタユニットを含み、第2のレジスタユニットグループは、前記クロック信号線の延長方向に順次配列された偶数番目のシフトレジスタユニットを含み、

前記第1の個レジスタユニットグループのカスケード接続された複数のシフトレジスタユニットの場合、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して前記第1のクロック信号線に電気的に接続され、前記奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して前記第2のクロック信号線に電気的に接続されるか、または第1の電力線に電気的に接続され、および、偶数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して前記第2のクロック信号線に電気的に接続され、前記偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して前記第1のクロック信号線に電気的に接続されるか、または第1の電力線に電気的に接続され、

前記第2のレジスタユニットグループのカスケード接続された複数のシフトレジスタユニットの場合、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して前記第3のクロック信号線に電気的に接続され、前記奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して前記第4のクロック信号線に電気的に接続されるか、または第1の電力線に電気的に接続され、および、前記偶数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して前記第4のクロック信号線に電気的に接続され、前記偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して前記第3のクロック信号線に電気的に接続されるか、または第1の電力線に電気的に接続される。

#### 【0006】

任意選択で、本発明の実施形態において、各前記シフトレジスタユニットは、電圧安定化トランジスタをさらに含み、前記入力トランジスタの第2の極は、前記電圧安定化トランジスタの第1の極に電気的に接続され、前記電圧安定化トランジスタの第2の極は、前

10

20

30

40

50

記出力トランジスタのゲートに電気的に接続され、

前記第2の導電層は、第1の電力線をさらに含み、各前記電圧安定化トランジスタのゲートは、第4のビアホールを介して前記第1の電力線に電気的に接続され、前記第4のビアホールは、前記第1の絶縁層を貫通する。

【0007】

任意選択で、本発明の実施形態において、同じ前記ゲート駆動回路において、前記ベース基板上の前記入力トランジスタの正投影は、前記第1の前記ベース基板上の電力線の正投影と前記ベース基板上の前記複数のクロック信号線の正投影との間にあり、

前記ベース基板上の前記電圧安定化トランジスタの正投影は、前記ベース基板上の前記複数のクロック信号線の正投影とは反対側に面する、前記第1の前記ベース基板上の電力線の正投影の片側にあり、

前記ベース基板上の前記出力トランジスタの正投影は、前記第1の前記ベース基板上の電力線の正投影とは反対側に面する、前記ベース基板上の前記電圧安定化トランジスタの正投影の片側にある。

【0008】

任意選択で、本発明の実施形態において、前記シフトレジスタユニットは、第1の制御トランジスタおよび第2の制御トランジスタをさらに含み、

前記半導体層は、前記第1の制御トランジスタの活性層および前記第2の制御トランジスタの活性層をさらに含み、

前記第1の導電層は、前記第1の制御トランジスタのゲートおよび前記第2の制御トランジスタのゲートをさらに含み、

前記第2の導電層は、第2の電力線と、複数の第2の転送部と、複数の第3の転送部とをさらに含み、ここで、1つの前記第2の転送部は、1つの前記第1の制御トランジスタに対応し、1つの前記第3の転送部は、1つの前記第2の制御トランジスタに対応し、

また、前記ディスプレイパネルは、第4の導電層と、第3の絶縁層とをさらに含み、

前記第4の導電層は、前記第1の絶縁層と前記第2の導電層との間にあり、かつ、前記第4の導電層は複数の第1の導電部を含み、ここで、1つの前記第1の導電部は、1つの前記第2の制御トランジスタに対応し、

前記第3の絶縁層は、前記第4の導電層と前記第2の導電層との間にあり、

前記第1の制御トランジスタのゲートは、対応する第1の接続線に直接電気的に接続され、前記第1の制御トランジスタの活性層のソース領域は、第5のビアホールを介して前記第1の電力線に電気的に接続され、前記第1の制御トランジスタの活性層のドレイン領域は、対応する前記第2の転送部を介して前記第2の制御トランジスタのゲートに電気的に接続され、前記第5のビアホールは、前記第1の絶縁層および前記第3の絶縁層を貫通し、

前記第2の制御トランジスタの活性層のソース領域は、第6のビアホールを介して対応する前記第3の転送部の一方の端に電気的に接続され、前記第3の転送部のもう一方の端は、第7のビアホールを介して対応する前記第1の導電部の一方の端に電気的に接続され、前記第1の導電部のもう一方の端は、第8のビアホールを介して前記第2の電力線に電気的に接続され、前記第2の制御トランジスタの活性層のドレイン領域は、前記出力トランジスタの活性層のドレイン領域と共有され、前記第6のビアホールは、前記第1の絶縁層および前記第3の絶縁層を貫通し、前記第7のビアホールおよび前記第8のビアホールは、前記第3の絶縁層を貫通する。

【0009】

任意選択で、本発明の実施形態において、前記ベース基板上の前記第2の電力線の正投影は、前記ベース基板上の前記複数のクロック信号線の正投影と前記ベース基板上の前記ゲート駆動回路の正投影との間にあり、

前記シフトレジスタユニットにおいて、前記ベース基板上の前記第1の制御トランジスタの正投影は、前記ベース基板上の前記入力トランジスタの正投影と前記第1の前記ベース基板上の電力線の正投影との間にあり、

10

20

30

40

50

前記シフトレジスタユニットにおいて、前記ベース基板上の前記第2の制御トランジスタの正投影は、前記第1の前記ベース基板上の電力線の正投影とは反対側に面する、前記ベース基板上の前記入力トランジスタの正投影の片側にある。

【0010】

任意選択で、本発明の実施形態において、前記シフトレジスタユニットにおいて、前記出力トランジスタの活性層および前記第2の制御トランジスタの活性層は、統合された構造で配置される。

【0011】

任意選択で、本発明の実施形態において、前記シフトレジスタユニットは、第1のコンデンサおよび第2のコンデンサをさらに含み、前記第1のコンデンサの第1の極は、前記第2の電力線に電気的に接続され、前記第1のコンデンサの第2の極は、前記第2の制御トランジスタのゲートに電気的に接続され、前記第2のコンデンサの第1の極は、前記出力トランジスタの第2の極に電気的に接続され、前記第2のコンデンサの第2の極は、前記出力トランジスタのゲートに電気的に接続され、

10

前記第4の導電層は、複数の第2の導電部をさらに含み、ここで、1つの前記第2の導電部は、1つの前記出力トランジスタに対応し、

前記ベース基板上の前記第1の導電部の正投影および前記ベース基板上の前記第2の制御トランジスタのゲートの正投影は、重複領域を有し、かつ、前記第1の導電部は、前記第1のコンデンサの第1の極として機能し、前記第2の制御トランジスタのゲートは、前記第1のコンデンサの第2の極として機能し、

20

前記ベース基板上の前記第2の導電部の正投影および前記ベース基板上の対応する前記出力トランジスタのゲートの正投影は、重複領域を有し、かつ、前記第2の導電部は、前記第2のコンデンサの第1の極として機能し、前記出力トランジスタのゲートは、前記第2のコンデンサの第2の極として機能する。

【0012】

任意選択で、本発明の実施形態において、前記ベース基板上の前記第2の制御トランジスタのゲートの正投影は、前記ベース基板上の前記第1の導電部の正投影を覆う。

【0013】

任意選択で、本発明の実施形態において、前記ベース基板上の前記第2の制御トランジスタのゲートの正投影および前記ベース基板上の前記第1の導電部の正投影それぞれは、前記第1の前記ベース基板上の電力線の正投影と重複領域を有する。

30

【0014】

任意選択で、本発明の実施形態において、前記ベース基板上の前記第8のビアホールの正投影は、前記第1の電力線と前記第2の前記ベース基板上の電力線の正投影との間にあり、前記ベース基板上の前記第7のビアホールの正投影は、前記第1の前記ベース基板上の電力線の正投影と前記ベース基板上の前記第2の制御トランジスタの活性層の正投影との間にある。

【0015】

任意選択で、本発明の実施形態において、前記ディスプレイパネルは、第2の絶縁層と、第3の導電層とを含み、

40

前記第2の絶縁層は、前記第2の導電層の前記ベース基板とは反対側に面する側にあり、前記第3の導電層は、前記第2の絶縁層の前記ベース基板とは反対側に面する側にあり、かつ、前記第2の導電層は、少なくとも1つの補助線を含み、

1つの前記補助線および1つの前記クロック信号線は、少なくとも1つの第9のビアホールを介して電気的に接続され、かつ、前記第9のビアホールは、前記第2の絶縁層を貫通する。

【0016】

任意選択で、本発明の実施形態において、前記ベース基板上の前記クロック信号線の正投影は、前記ベース基板上の電気的に接続された補助線の正投影を覆う。

【0017】

50

本発明の実施形態上記のディスプレイパネルを含むディスプレイデバイスをさらに提供する。

【0018】

本発明の実施形態によって提供される上記ディスプレイパネルの駆動方法は、1フレームのスキャン時間において、すべての前記シフトレジスタユニットを制御して、すべての前記駆動線を行ごとに順次スキャンするように制御するステップを備え、前記クロック信号線の延長方向に順次配列された奇数番目のシフトレジスタユニットおよび偶数番目のシフトレジスタユニットは、異なるクロック信号線グループの制御下で独立して駆動される。

【0019】

本発明の実施形態によって提供される上記ディスプレイパネルの駆動方法は、異なるクロック信号線グループの複数のクロック信号線に印加される信号の、アクティブレベルを維持するための時間は、お互いに重複しない。

【図面の簡単な説明】

【0020】

【図1】本発明の実施形態によって提供されるいくつかのディスプレイパネルの概略構造図である。

【図2】本発明の実施形態によって提供されるいくつかのサブピクセルにおけるピクセル駆動回路の概略構造図である。

【図3】本発明の実施形態によって提供されるいくつかのピクセル駆動回路の信号シーケンス図である。

【図4a】本発明の実施形態によって提供されるいくつかのシフトレジスタユニットの概略構造図である。

【図4b】本発明の実施形態によって提供されるいくつかのシフトレジスタユニットの信号シーケンス図である。

【図4c】本発明の実施形態によって提供されるいくつかのゲート駆動回路の出力信号シーケンス図である。

【図5a】本発明の実施形態によって提供されるいくつかの他のシフトレジスタユニットの概略構造図である。

【図5b】本発明の実施形態によって提供されるいくつかの他のシフトレジスタユニットの信号シーケンス図である。

【図6】本発明の実施形態によって提供されるいくつかのゲート駆動回路のレイアウト構造の概略図である。

【図7a】本発明の実施形態によって提供されるいくつかの半導体層のレイアウト構造の概略図である。

【図7b】本発明の実施形態によって提供されるいくつかのゲート導電層のレイアウト構造の概略図である。

【図7c】本発明の実施形態によって提供されるいくつかの第4の導電層のレイアウト構造の概略図である。

【図7d】本発明の実施形態によって提供されるいくつかの第2の導電層のレイアウト構造の概略図である。

【図8a】図6に示すレイアウト構造の概略図において、AA'方向に沿った断面構造の概略図である。

【図8b】図6に示すレイアウトの概略図において、BB'方向に沿った断面構造の概略図である。

【図9】本発明の実施形態によって提供される他のいくつかのゲート駆動回路のレイアウト構造の概略図である。

【図10】本発明の実施形態によって提供されるいくつかの第3の導電層のレイアウト構造の概略図である。

【図11】図9に示すレイアウト構造の概略図において、AA'方向に沿った断面構造の概

10

20

30

40

50

略図である。

【図12】本発明の実施形態によって提供される他のいくつかのシフトレジスタユニットの信号シーケンス図である。

【発明を実施するための形態】

【0021】

本発明に係る実施例の目的、技術案及びメリットをより明確にするため、以下、本発明に係る実施例の図面を参考しながら、本発明に係る実施例の技術案を明確かつ完全に説明する。説明した実施例は本発明の一部の実施例にすぎず、全部の実施例ではないのが明らかである。本発明の実施例に基づき、当業者は、創造性作業を行わない限りに得られた他の実施例は、全部本発明の保護範囲に属する。

10

【0022】

別段の定義がない限り、本発明で使用される技術的または科学的用語は、本発明が属する当業者によって理解される通常の意味を有するものとする。本発明で使用される「第1」、「第2」などの用語は、順序、量、または重要性を示すものではなく、異なる構成要素を区別するためにのみ使用される。「含む」または「包括」などの用語は、単語の前にある要素またはアイテムが、他の要素またはアイテムを除外することなく、単語の後にリストされた要素またはアイテムおよびその同等物をカバーすることを意味する。「接続」または「結合」などの用語は、物理的または機械的接続に限定されず、直接または間接を問わず、電気的接続を含み得る。

【0023】

図面中のすべてのグラフのサイズおよび形状は、真の縮尺を反映しておらず、本発明の内容を説明することのみを意図していることに留意されたい。同じまたは類似の参照番号は、同じまたは類似の要素、または最初から最後まで同じまたは類似の機能を持つ要素を表す。

20

【0024】

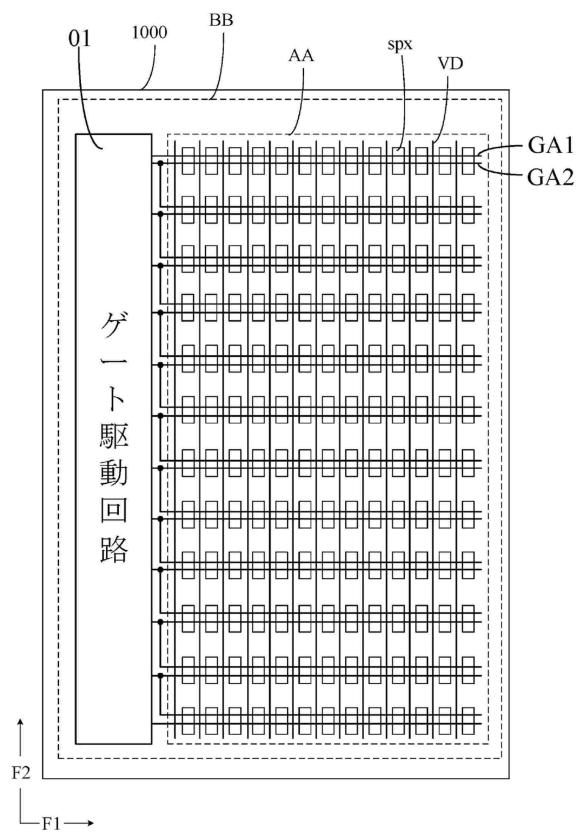

図1に示されるように、本発明の実施形態によって提供されるディスプレイパネルは、ベース基板1000を含み得る。ここで、ベース基板1000は、表示領域AAおよび非表示領域BBを含み得る。非表示領域BBは、表示領域を取り囲むことができる。表示領域AAは、複数のピクセルユニットPXを含み得、ピクセルユニットPXは、複数のサブピクセルSPXを含み得る。複数のサブピクセルSPXは、複数の行および複数の列に沿ってマトリックスモードで配置される。

30

【0025】

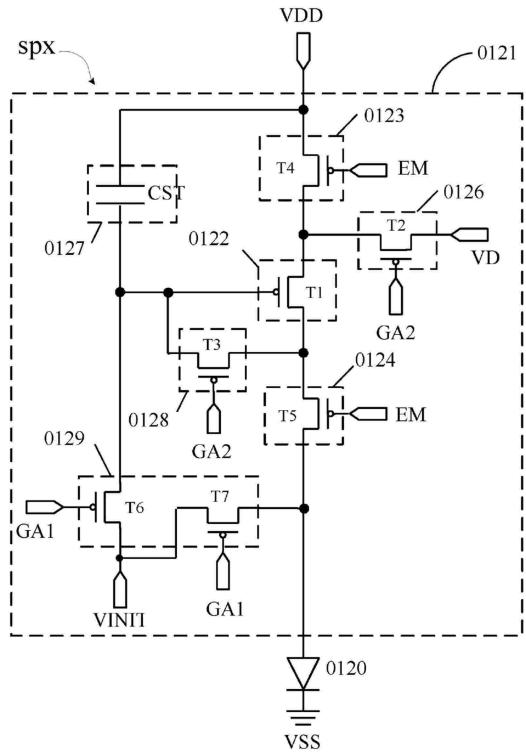

例示的に、図1および図2に示されるように、複数のサブピクセルSPXのうちの少なくとも1つのサブピクセルSPXには、ピクセル駆動回路0121および発光デバイス0120が含まれ得る。ここで、ピクセル駆動回路0121には、トランジスタおよびコンデンサが含まれ、トランジスタとコンデンサとの相互作用により電気信号が生成され、生成された電気信号は、発光デバイス0120の第1の電極に入力される。さらに、発光デバイス0120の第2の電極に対応する電圧を印加して、駆動発光デバイス0120を駆動して発光させることができるようとする。

【0026】

図2を参照して示すように、ピクセル駆動回路0121は、駆動制御回路0122、第1の発光制御回路0123、第2の発光制御回路0124、データ書き込み回路0126、記憶回路0127、閾値補償回路0128およびリセット回路0129を含む。

40

【0027】

駆動制御回路0122は、制御端、第1の極および第2の極を含み得る。駆動制御回路0122は、発光デバイス0120を駆動して発光させるための駆動電流を発光デバイス0120に提供するように構成される。例えば、第1の発光制御回路0123は、駆動制御回路0122の第1の極および第1の電圧端VDDに接続されている。第1の発光制御回路0123は、駆動制御回路0122と第1の電圧端VDDとの間の接続導通または切断を実現するように構成される。

50

## 【0028】

第2の発光制御回路0124は、駆動制御回路0122の第2の極および発光デバイス0120の第1の電極に電気的に接続されている。第2の発光制御回路0124は、駆動制御回路0122と発光装置0120との間の接続導通または切断を実現するように構成される。

## 【0029】

データ書き込み回路0126は、駆動制御回路0122の第1の極に電気的に接続されている。第2の発光制御回路0124は、スキャンラインGA2の信号の制御下でデータラインVDの信号を記憶回路0127に書き込むように構成される。

## 【0030】

記憶回路0127は、駆動制御回路0122の制御端および第1の電圧端VDDに電気的に接続されている。記憶回路0127は、データ信号を記憶するように構成される。

## 【0031】

閾値補償回路0128は、駆動制御回路0122の制御端および第2の極に電気的に接続されている。閾値補償回路0128は、駆動制御回路0122に対して閾値補償を実行するように構成される。

## 【0032】

リセット回路0129は、駆動制御回路0122の制御端および発光デバイス0120の第1の電極に電気的に接続されている。リセット回路0129は、スキャンラインGA1の信号の制御下で駆動制御回路0122の制御端および発光デバイス0120の第1の電極をリセットする。

## 【0033】

ここで、発光デバイス0120は、OLEDおよびQLEDのうちの少なくとも1つなどのエレクトロルミネセンスダイオードとして配置され得る。ここで、発光デバイス0120は、積層された第1の電極、発光機能層および第2の電極であり得る。例示的に、第1の電極はアノードであり得、第2の電極はカソードであり得る。発光機能層は、発光層を含み得る。さらに、発光機能層は、正孔注入層、正孔輸送層、発光層、電子輸送層、および電子注入層などの膜層をさらに含み得る。もちろん、実際のアプリケーションでは、発光デバイス0120は、ここで限定されない実際のアプリケーション環境の要件に従つて設計および決定され得る。

## 【0034】

例示的に、図2に示されるように、駆動制御回路0122は、駆動トランジスタT1を含み、駆動制御回路0122の制御端は、駆動トランジスタT1のゲートを含み、駆動制御回路0122の第1の極は、駆動トランジスタT1の第1の極を含み、駆動制御回路0122の第2の極は、駆動トランジスタT1の第2の極を含む。

## 【0035】

例示的に、図2に示されるように、データ書き込み回路0126は、データ書き込みトランジスタT2を含む。記憶回路0127は、記憶コンデンサCSTを含む。閾値補償回路0128は、閾値補償トランジスタT3を含む。第1の発光制御回路0123は、第1の発光制御トランジスタT4を含む。第2の発光制御回路0124は、第2の発光制御トランジスタT5を含む。リセット回路0129は、第1のリセットトランジスタT6および第2のリセットトランジスタT7を含む。

## 【0036】

具体的に、データ書き込みトランジスタT2の第1の極は、駆動トランジスタT1の第1の極に電気的に接続され、データ信号の受信のため、データ書き込みトランジスタT2の第2の極は、データラインVDに電気的に接続され、スキャン信号の受信のため、データ書き込みトランジスタT2のゲートは、第2のスキャンラインGA2に電気的に接続されるように構成される。

## 【0037】

記憶コンデンサCSTの第1の極は、第1の電力端VDDに電気的に接続され、記憶コ

10

20

30

40

50

ンデンサ C S T の第 2 の極は、駆動トランジスタ T 1 のゲートに電気的に接続される

閾値補償トランジスタ T 3 の第 1 の極は、駆動トランジスタ T 1 の第 2 の極に電気的に接続され、閾値補償トランジスタ T 3 の第 2 の極は、駆動トランジスタ T 1 のゲートに電気的に接続され、信号受信のため、閾値補償トランジスタ T 3 のゲートは、第 2 のスキャンライン G A 2 に電気的に接続されるように構成される。

【 0 0 3 8 】

第 1 のリセットトランジスタ T 6 の第 1 の極は、リセット信号を受信するためにリセット信号線 V I N I T に電気的に接続されるように構成され、第 1 のリセットトランジスタ T 6 の第 2 の極は、駆動トランジスタ T 1 のゲートに電気的に接続され、第 1 のリセットトランジスタ T 6 のゲートは、信号を受信するために第 1 のスキャンライン G A 1 に電気的に接続されるように構成される。

10

【 0 0 3 9 】

第 2 のリセットトランジスタ T 7 の第 1 の極は、リセット信号を受信するためにリセット信号線 V I N I T に電気的に接続されるように構成される。第 2 のリセットトランジスタ T 7 の第 2 の極は、発光デバイス 0 1 2 0 の第 1 の電極に電気的に接続され、第 2 のリセットトランジスタ T 7 のゲートは、信号を受信するために第 1 のスキャンライン G A 1 に電気的に接続されるように構成される。

【 0 0 4 0 】

第 1 の発光制御トランジスタ T 4 の第 1 の極は、第 1 の電力端 V D D に電気的に接続され、第 1 の発光制御トランジスタ T 4 の第 2 の極は、駆動トランジスタ T 1 の第 1 の極に電気的に接続され、第 1 の発光制御トランジスタ T 4 のゲートは、発光制御回路信号を受信するために発光制御ライン E M に電気的に接続されるように構成される。

20

【 0 0 4 1 】

第 2 の発光制御トランジスタ T 5 の第 1 の極は、駆動トランジスタ T 1 の第 2 の極に電気的に接続され、第 2 の発光制御トランジスタ T 5 の第 2 の極は、発光デバイス 0 1 2 0 の第 1 の電極に電気的に接続され、第 2 の発光制御トランジスタ T 5 のゲートは、発光制御回路信号を受信するために発光制御ライン E M に電気的に接続されるように構成される。

【 0 0 4 2 】

発光デバイス 0 1 2 0 の第 2 の電極は、第 2 の電力端 V S S に電気的に接続されるここで、上記トランジスタの第 1 の極および第 2 の極は、実際の用途に応じてソース電極またはドレイン電極として決定することができ、これらはここで限定されない。

30

【 0 0 4 3 】

例示的に、第 1 の電力端 V D E D および第 2 の電力端 V S S の一方は高電圧端であり、他方は低電圧端である。例えば、図 2 に示される実施形態では、第 1 の電力端 V D D は、一定の第 1 の電圧を出力するための電圧源であり、第 1 の電圧は正の電圧である。そして、第 2 の電力端 V S S は、一定の第 2 の電圧を出力するための電圧源であり得る、第 2 の電圧は負の電圧である。たとえば、いくつかの例では、第 2 の電力端の V S S は接地され得る。

【 0 0 4 4 】

図 2 に示すピクセル駆動回路に対応する信号シーケンス図を図 3 に示す。1 フレームの表示時間において、ピクセル駆動回路の動作過程は、T 1 0 ステージ、T 2 0 ステージおよび T 3 0 ステージの 3 ステージである。ここで、g a 1 は、第 1 のスキャンライン G A 1 で送信される信号を表し、g a 2 は、第 2 のスキャンライン G A 2 で送信される信号を表し、e m は、発光制御ライン E M で送信される信号を表す。

40

【 0 0 4 5 】

T 1 0 ステージにおいて、信号 g a 1 は、第 1 のリセットトランジスタ T 6 および第 2 のリセットトランジスタ T 7 の導通を制御する。導通された第 1 のリセットトランジスタ T 6 は、リセット信号線 V I N I T で送信された信号を駆動トランジスタ T 1 のゲートに提供して、駆動トランジスタ T 1 のゲートをリセットし、リセット信号線 V I N I T で送信された信号を駆動トランジスタ T 1 のゲートに提供して、導通された第 2 のリセットト

50

ランジスタT7は、リセット信号線VINIT送信された信号を発光デバイス0120の第1の電極に提供して、発光デバイス0120の第1の電極をリセットする。また、T10ステージにおいて、信号g a 2は、データ書き込みトランジスタT2と閾値補償トランジスタT3の両方が遮断されるように制御する。信号e mは、第1の発光制御トランジスタT4と第2の発光制御トランジスタT5の両方が遮断されるように制御する。

【0046】

T20ステージでは、信号g a 2は、データ書き込みトランジスタT2と閾値補償トランジスタT3の導通を制御し、データラインVDで送信されたデータ信号が駆動トランジスタT1のゲートを充電できるようにする。したがって、駆動トランジスタT1のゲートの電圧は、Vdata+|Vth|になる。ここで、Vthは、駆動トランジスタT1の閾値電圧を表し、Vdataは、データ信号の電圧を表す。また、この段階では、信号g a 1は、第1のリセットトランジスタT6と第2のリセットトランジスタT7の両方が遮断されるように制御する。信号e mは、第1の発光制御トランジスタT4と第2の発光制御トランジスタT5の両方が遮断されるように制御する。

10

【0047】

T30ステージでは、信号e mは、第1の発光制御トランジスタT4と第2の発光制御トランジスタT5の導通を制御する。導通された第1の発光制御トランジスタT4は、第1の電力端VDDの電圧Vddを駆動トランジスタT1の第1の極に提供し、その結果、駆動トランジスタT1の第1の極の電圧はVdd。である。駆動トランジスタT1は、ゲート電圧Vdata+|Vth|および第1の極の電圧Vddに従って駆動電流を生成する。当該駆動電流は、導通された第2の発光制御トランジスタT5を介して発光デバイス0120に供給され、駆動発光デバイス0120を駆動して発光させる。また、この段階では、信号g a 1は、第1のリセットトランジスタT6と第2のリセットトランジスタT7の両方が遮断されるように制御する。信号g a 2は、データ書き込みトランジスタT2と閾値補償トランジスタT3の両方が遮断されるように制御する。

20

【0048】

本発明の実施形態において、サブピクセルにおけるピクセル駆動回路は、本発明の実施形態に限定されない、図2に示される構造に加えて、他の数のトランジスタを含む構造であり得ることに留意されたい。

30

【0049】

特定の実施中、本発明の実施形態において、図1に示されるように、表示領域は、複数の駆動線および複数のデータラインを含み得、ここで、サブピクセルの1つの行は、対応して、少なくとも1つの前記駆動線に電気的に接続される。サブピクセルの1つの列は、対応して、少なくとも1つのデータラインに電気的に接続される。例示的に、駆動線は、複数のスキャンラインおよび複数の発光制御ラインのうちの少なくとも1つを含む。ここで、サブピクセルの1つの行は、対応して、少なくとも1つのスキャンラインおよび少なくとも1つの発光制御ラインに電気的に接続される。例示的に、ピクセル駆動回路が図2に示される構造に設定される場合、サブピクセルの1つの列が、対応して、1つのデータラインに電気的に接続され、または、サブピクセルの1つの列の異なる行に位置する少サブピクセルそれぞれは、対応して、2つのデータラインに電気的に接続される。サブピクセルの1つの行は、1つの発光制御ラインに対応する。複数のスキャンラインは、複数の第1のスキャンラインおよび複数の第2のスキャンラインを含み得、サブピクセルの1つの行は、対応して2つのスキャンラインに電気的に接続される。すなわち、サブピクセルの1つの行は、対応して1つの第1のスキャンラインおよび1つの第2のスキャンラインに電気的に接続される。また、隣接する2つの行ごとに、第1の行に対応して電気的に接続された第2のスキャンラインと、第2の行に対応して電気的に接続された第1のスキャンラインは同じ信号を送信するように電気的に接続される。

40

【0050】

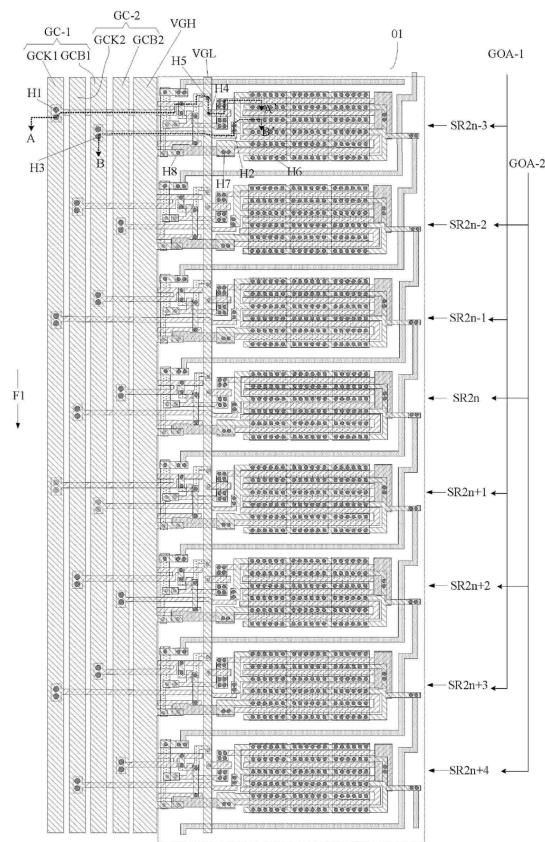

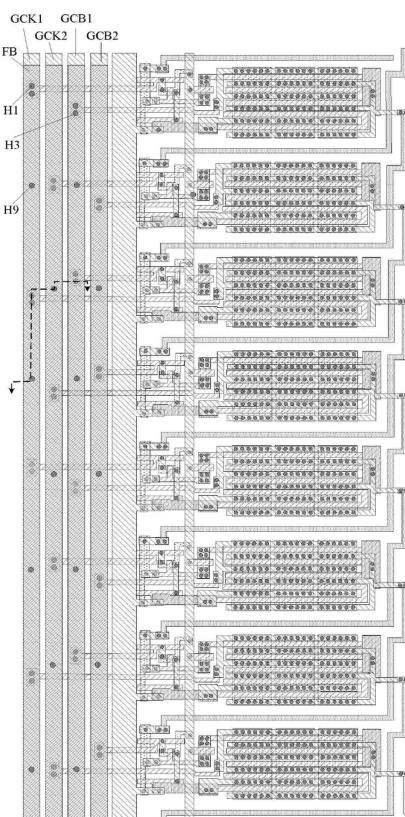

図1および図6に示されるように、本発明の実施形態では、特定の実施中に、第1のスキャンラインおよび第2のスキャンラインが信号を送信するようにするために、非表示領

50

域 B B は、ゲート駆動回路 0 1 および複数のクロック信号線が含まれる。ここで、クロック信号線の延長方向は、スキャンラインの延長方向とは異なり、例えば、クロック信号線の延長方向とスキャンラインの延長方向交とが交差している。当該複数のクロック信号線は、スキャンラインとは反対側に面するゲート駆動回路 0 1 に、間隔を置いて配置されている。例示的に、ゲート駆動回路 0 1 は、クロック信号線の延長方向 F 1 に順次配置される複数のシフトレジスタユニット：S R 2 n - 3、S R 2 n - 2、S R 2 n - 1、S R 2 n、S R 2 n + 1、S R 2 n + 2、S R 2 n + 3、S R 2 n + 4 (n は 0 より大きい整数である) を含み得る。例示的に、1 つのシフトレジスタユニットの出力信号端 O P 駆動線は、少なくとも 1 つの駆動線に対応して電気的に接続され得る。例示的に、シフトレジスタユニットの出力信号端 O P はまた、少なくとも 1 つのスキャンラインに対応して電気的に接続され得る。また、シフトレジスタユニットの出力信号端 O P は、少なくとも 1 つの発光制御ラインに対応して電気的に接続され得る。

#### 【 0 0 5 1 】

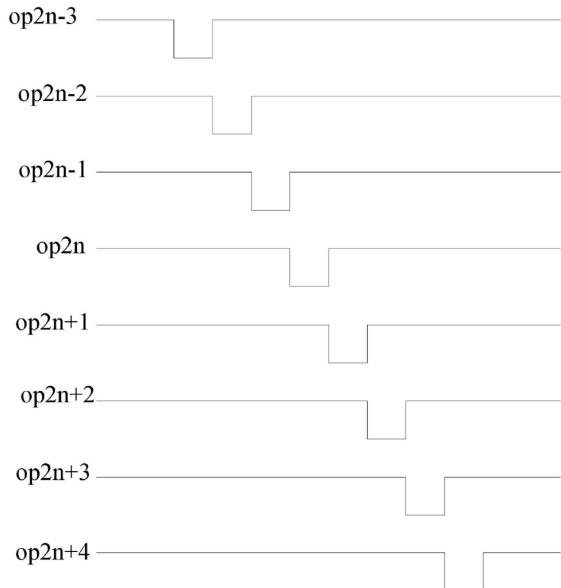

また、クロック信号線の延長方向 F 1 に順次配置される複数のシフトレジスタユニット S R 2 n - 3、S R 2 n - 2、S R 2 n - 1、S R 2 n、S R 2 n + 1、S R 2 n + 2、S R 2 n + 3、S R 2 n + 4 の出力信号端 O P は、図 4 C に示すような信号を出力することができる。ここで、o p 2 n - 3 は、シフトレジスタユニット S R 2 n - 3 の出力信号端 O P によって出力される信号であり、o p 2 n - 2 は、シフトレジスタユニット S R 2 n - 2 の出力信号端 O P によって出力される信号であり、o p 2 n - 1 は、シフトレジスタユニット S R 2 n - 1 の出力信号端 O P によって出力される信号であり、o p 2 n は、シフトレジスタユニット S R 2 n の出力信号端 O P によって出力される信号であり、o p 2 n + 1 は、シフトレジスタユニット S R 2 n + 1 の出力信号端 O P によって出力される信号であり、o p 2 n + 2 は、シフトレジスタユニット S R 2 n + 2 の出力信号端 O P によって出力される信号であり、o p 2 n + 3 は、シフトレジスタユニット S R 2 n + 3 の出力信号端 O P によって出力される信号であり、o p 2 n + 4 は、シフトレジスタユニット S R 2 n + 4 の出力信号端 O P によって出力される信号である。

#### 【 0 0 5 2 】

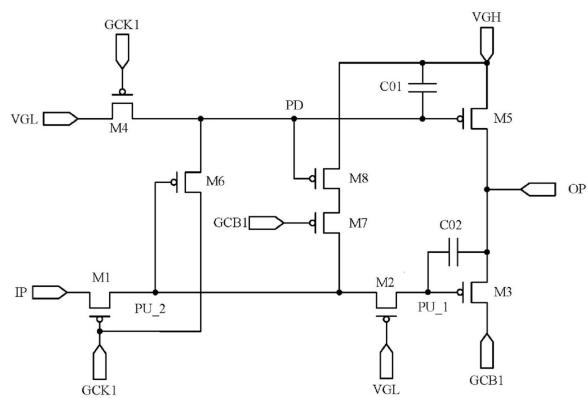

特定の実施中、本発明の実施形態において、図 4 a に示されるように、シフトレジスタユニットは、複数のトランジスタを含むことができる。複数のトランジスタは、入力トランジスタ M 1、電圧安定化トランジスタ M 2、出力トランジスタ M 3、第 1 の制御トランジスタ M 4、第 2 の制御トランジスタ M 5、第 6 のトランジスタ M 6、第 7 のトランジスタ M 7、第 8 のトランジスタ M 8、第 1 のコンデンサ C 0 1 および第 2 のコンデンサ C 0 2 を含むことができる。ここで、入力トランジスタ M 1 のゲートは、第 1 のクロック信号端 C K に電気的に接続され、入力トランジスタ M 1 の第 1 の極は、入力信号端 I P に電気的に接続され、入力トランジスタ M 1 の第 2 の極は、電圧安定化トランジスタ M 2 の第 1 の極に電気的に接続され、電圧安定化トランジスタ M 2 のゲートは、第 1 の電力線 V G L に電気的に接続され、電圧安定化トランジスタ M 2 の第 2 の極は、出力トランジスタ M 3 のゲートに電気的に接続され、出力トランジスタ M 3 の第 1 の極は、第 2 のクロック信号端 C B に電気的に接続され、出力トランジスタ M 3 の第 2 の極は、出力信号端 O P に電気的に接続され、すなわち、出力トランジスタの第 2 の極は、少なくとも 1 つのスキャンラインに対応して電気的に接続される。

#### 【 0 0 5 3 】

第 1 の制御トランジスタ M 4 のゲートは、入力トランジスタ M 1 のゲートに電気的に接続され、第 1 の制御トランジスタ M 4 の第 1 の極は、第 1 の電力線 V G L に電気的に接続され、第 1 の制御トランジスタ M 4 の第 2 の極は、第 2 の制御トランジスタ M 5 のゲートに電気的に接続される第 2 の制御トランジスタ M 5 の第 1 の極は、第 2 の電力線 V G H に電気的に接続され、第 2 の制御トランジスタ M 5 の第 2 の極は、出力トランジスタの第 2 の極に電気的に接続される。

#### 【 0 0 5 4 】

第 6 のトランジスタ M 6 のゲートは、入力トランジスタ M 1 の第 2 の極に電気的に接続

10

20

30

40

50

され、第6のトランジスタM6の第1の極は、第1のクロック信号端CKに電気的に接続され、第6のトランジスタM6の第2の極は、第1の制御トランジスタM4の第2の極に電気的に接続される。

【0055】

第7のトランジスタM7のゲートは、第2のクロック信号端CBに電気的に接続され、第7のトランジスタM7の第1の極は、入力トランジスタM1のゲートに電気的に接続され、第7のトランジスタM7の第2の極は、第8のトランジスタM8の第1の極に電気的に接続される。

【0056】

第8のトランジスタM8のゲートは、第1の制御トランジスタM4の第2の極に電気的に接続され、第8のトランジスタM8の第2の極は、第2の電力線VGHに電気的に接続される。

10

【0057】

第1のコンデンサC01の第1の極は、第2の電力線VGHに電気的に接続され、第1のコンデンサC01の第2の極は、第2の制御トランジスタM5のゲートに電気的に接続され、第2のコンデンサC02の第1の極は、出力トランジスタの第2の極に電気的に接続され、第2のコンデンサC01の第2の極は、出力トランジスタM3のゲートに電気的に接続される。

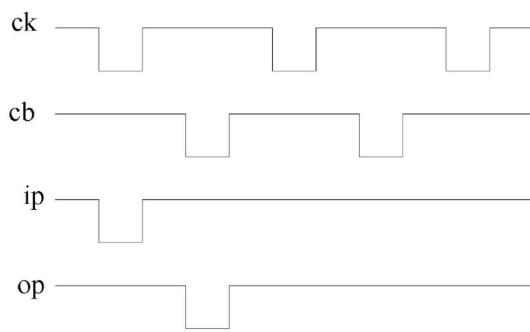

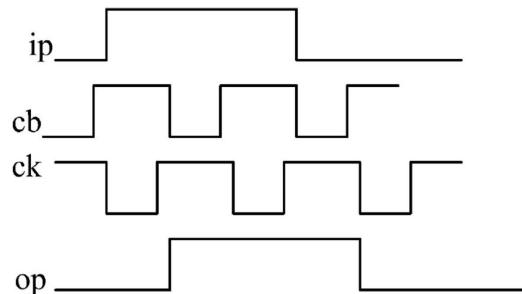

【0058】

図4aに示されるシフトレジスタ対応する信号シーケンス図が図4bに示される。ここで、ckは入力トランジスタM1のゲートによって入力されたクロック信号を表し、cbは出力トランジスタM3の第1の極によって入力されたクロック信号を表し、ipは、入力信号端IPの信号を表し、opは、出力信号端OPの信号を表す。クロック信号ck、cb、入力信号端IPの信号ip各トランジスタと第1のコンデンサC01および第2のコンデンサC02の協調により、出力トランジスタM3は信号opを出力することができる。図4aに示されるシフトレジスタに対応する信号シーケンス図は、図4bに示される信号シーケンス図に加えて、実際のニーズに応じて、他の形態の信号シーケンス図であり得、本発明の実施形態に限定されないことに留意されたい。

20

【0059】

例示的に、本発明の実施形態において、上記ゲート駆動回路01内の各シフトレジスタユニットの特定の構造は、機能および構造において本発明の図4aに示されるシフトレジスタユニットと同じであり得る。このようにして、ゲート駆動回路01は、第1のスキャンラインGA1および第2のスキャンラインGA2に信号を入力することができ、その結果、第1のリセットトランジスタT6、第2のリセットトランジスタT7、データ書き込みトランジスタT2および閾値補償トランジスタT3を制御することができる。

30

【0060】

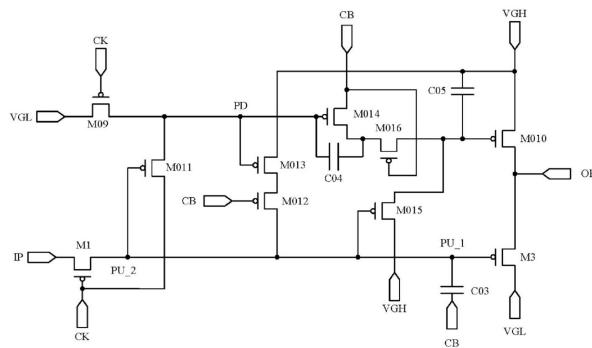

特定の実施中、本発明の実施形態において、図5aに示されるように、シフトレジスタユニットは、複数のトランジスタを含む。複数のトランジスタは、入力トランジスタM1、出力トランジスタM3、第9のトランジスタM09、第10のトランジスタM010、第11のトランジスタM011、第12のトランジスタM012、第13のトランジスタM013、第14のトランジスタM014、第15のトランジスタM015、第16のトランジスタM016、第3のコンデンサC03、第4のコンデンサC04および第5のコンデンサC05を含む。

40

【0061】

ここで、入力トランジスタM1のゲートは、第1のクロック信号端CKに電気的に接続され、入力トランジスタM1の第1の極は、入力信号端IPに電気的に接続され、入力トランジスタM1の第2の極は、出力トランジスタM3のゲートに電気的に接続され、出力トランジスタM3の第1の極は、第1の電力線VGLに電気的に接続され、出力トランジスタM3の第2の極は、出力信号端OPに電気的に接続され、すなわち、出力トランジスタの第2の極は、少なくとも1つの発光制御ラインに対応的に電気的に接続される。

50

## 【0062】

第9のトランジスタM09のゲートは、入力トランジスタM1のゲートに電気的に接続され、第9のトランジスタM09の第1の極は、第1の電力線VGLに電気的に接続され、第9のトランジスタM09の第2の極は、第14のトランジスタM014のゲートに電気的に接続される。

## 【0063】

第14のトランジスタM014の第1の極は、第2のクロック信号端CBに電気的に接続され、第14のトランジスタM014の第2の極は、第16のトランジスタM016の第1の極に電気的に接続される。

## 【0064】

第16のトランジスタM016の第2の極は、第10のトランジスタM010のゲートに電気的に接続され、第16のトランジスタM016のゲートは、第2のクロック信号端CBに電気的に接続される。

10

## 【0065】

第10のトランジスタM010の第1の極は、第2の電力線VGHに電気的に接続され、第10のトランジスタM010の第2の極は、出力トランジスタM3の第2の極に電気的に接続される。

## 【0066】

第11のトランジスタM011のゲートは、入力トランジスタM1の第2の極に電気的に接続され、第11のトランジスタM011の第1の極は、第1のクロック信号端CKに電気的に接続され、第11のトランジスタM011の第2の極は、第9のトランジスタM09の第2の極に電気的に接続される。

20

## 【0067】

第12のトランジスタM012のゲートは、第2のクロック信号端CBに電気的に接続され、第12のトランジスタM012の第1の極は、入力トランジスタM1のゲートに電気的に接続され、第12のトランジスタM012の第2の極は、第13のトランジスタM013の第1の極に電気的に接続される。

## 【0068】

第13のトランジスタM013のゲートは、第9のトランジスタM09の第2の極に電気的に接続され、第13のトランジスタM013の第2の極は、第2の電力線VGHに電気的に接続される。

30

## 【0069】

第5のコンデンサC05の第1の極は、第2の電力線VGHに電気的に接続され、第5のコンデンサC05の第2の極は、第10のトランジスタM010のゲートに電気的に接続され、第3のコンデンサC03の第1の極は、第2のクロック信号端CBに電気的に接続され、第3のコンデンサC03の第2の極は、出力トランジスタM3のゲートに電気的に接続される第4のコンデンサC04の第1の極は、第14のトランジスタM014のゲートに電気的に接続され、第4のコンデンサC04の第2の極は、第14のトランジスタM014の第2の極に電気的に接続される。

## 【0070】

図5aに示されるシフトレジスタに対応する信号シーケンスが図5bに示される。ここで、ckは入力トランジスタM1のゲートによって入力されたクロック信号を表し、cbは、第12のトランジスタM012のゲートによって入力されたクロック信号を表し、ipは、入力信号端IPの信号を表し、opは、出力信号端OPの信号を表す。クロック信号ck、cb、入力信号端IPの信号ip、各トランジスタと第1のコンデンサC01および第2のコンデンサC02の協調により、出力トランジスタM3は信号opを出力することができる。5bに示されるシフトレジスタ対応する信号シーケンス図は、5bに示される信号シーケンス図に加えて、実際のニーズに応じて、他の形態の信号シーケンス図であり得、本発明の実施形態に限定されないことに留意されたい。

40

## 【0071】

50

例示的に、本発明の実施形態において、上記ゲート駆動回路 0 1 内の各シフトレジスタユニットの特定の構造は、機能および構造において、本発明の図 5 a に示されるシフトレジスタユニットと同じであり得る。このようにして、ゲート駆動回路 0 1 は、第 1 の発光制御トランジスタ T 4 および第 2 の発光制御トランジスタ T 5 の導通および切断を制御するために、発光制御ラインに信号を入力することができる。

【 0 0 7 2 】

もちろん、実際の用途では、シフトレジスタユニットは、本発明の実施形態に限定されない、図 4 a および図 5 a に示される構造に加えて、他の数のトランジスタを含む構造であり得る。以下の説明では、図 4 a に示すシフトレジスタユニットの構造を例として取り上げる。

10

【 0 0 7 3 】

各シフトレジスタユニットに対応するクロック信号を入力するために、ゲート駆動回路 0 1 の各シフトレジスタユニットに対応するクロック信号を入力するために、通常、2つのクロック信号線のみが使用され、これにより、クロック信号線の負荷が比較的高くなる。特に大型のディスプレイパネルでは、シフトレジスタユニットの数が増えており、クロック信号線の負荷がさらに大きくなり、シフトレジスタユニットが出力する信号の不安定さが増加する。それによってディスプレイパネルの表示効果に影響を与える。したがって、本発明の実施形態は、いくつかのディスプレイパネルを提供する。特に大型ディスプレイパネルでは、各クロック信号線に電気的に接続されるシフトレジスタユニットの数を減らすことができるため、クロック信号線の負荷が軽減され、シフトレジスタユニットによって出力される信号の安定性が向上し、ディスプレイパネルの表示効果を向上する。

20

【 0 0 7 4 】

特定の実施中、本発明の実施形態では、図 6 に示されるように、複数のシフトレジスタユニットは、複数のレジスタユニットグループ G O A - m ( 1 ≤ m ≤ M, m および M は整数である ) に分割され得る。M はレジスタユニットグループの総数である。図 6 では、例として M = 2 を使用する。同じレジスタユニットグループ G O A - m 内のすべてのシフトレジスタユニットはカスケード接続され、クロック信号線の延長方向に隣接する 2 つのシフトレジスタユニットが異なるレジスタユニットグループに配置される。例えば、各レジスタユニットグループ G O A - m 内の 2 つの隣接するシフトレジスタユニットごとに電気的に接続されているスキャンラインの間に、少なくとも 1 つの残りのスキャンラインが配置されている。つまり、異なるレジスタユニットグループ内のシフトレジスタユニットが交互に配置される。

30

【 0 0 7 5 】

また、特定の実施中、本発明の実施形態において、図 6 に示されるように、複数のクロック信号線は、複数のクロック信号線グループ G C - m に分割され、異なるレジスタユニットグループは、異なるクロック信号線グループに対応する。つまり、1 つのレジスタユニットグループ G O A - m は、1 つのクロック信号線グループ G C - m に対応して電気的に接続される。例示的に、入力トランジスタ M 1 のゲートは、対応するクロック信号線グループ内の 1 つのクロック信号線に電気的に接続され、入力トランジスタ M 1 の第 1 の極は、入力信号端 I P に電気的に接続され、入力トランジスタ M 1 の第 2 の極は、電圧安定化トランジスタ M 2 の第 1 の極に電気的に接続され、電圧安定化トランジスタ M 2 の第 2 の極は、出力トランジスタ M 3 のゲートに電気的に接続され、出力トランジスタ M 3 の第 1 の極は、対応するクロック信号線グループ内の別のクロック信号線に電気的に接続され、出力トランジスタ M 3 の第 2 の極は、少なくとも 1 つのスキャンラインに対応的に電気的に接続される。

40

【 0 0 7 6 】

本発明の実施形態、シフトレジスタユニットをグループ化し、1 つのレジスタユニットグループを 1 つのクロック信号線グループに対応させることにより、対応するクロック信号が、クロック信号線グループを介して対応するレジスタユニットグループにロードされる。このようにして、1 つのクロック信号線に電気的に接続されるシフトレジスタユニッ

50

トの数を減らすことができ、それにより、クロック信号線の負荷を減らし、シフトレジスタユニットによって出力される信号の安定性を改善し、ディスプレイパネルの表示効果を改善する。

【0077】

特定の実施中、シフトレジスタユニットの構造が図4aに示される場合、1つのシフトレジスタユニットが2つのクロック信号線に電気的に接続され得る。本発明の実施形態では、図6に示すように、ゲート駆動回路01内の複数のシフトレジスタユニットを2つのレジスタユニットグループに分割することができる。複数のクロック信号線は、2つのクロック信号線グループに分けられる。もちろん、ゲート駆動回路01内の複数のシフトレジスタユニットは、3、4、5、6以上のレジスタユニットグループに分割されてもよく、または、複数のクロック信号線は、3、4、5、6以上のクロック信号線グループに分割されてもよい。

10

【0078】

例示的に、M=2の場合、図6に示すように、上記2つのレジスタユニットグループは、第1のレジスタユニットグループG0A-1および第2のレジスタユニットグループG0A-2を含み得る。上記2つのクロック信号線グループは、第1のクロック信号線群Gc-1と第2のクロック信号線群Gc-2を含む。ここで、第1のレジスタユニットグループG0A-1は、第1のクロック信号線グループGc-1に電気的に接続され、第2のレジスタユニットグループG0A-2は、第2のクロック信号線グループGc-2に電気的に接続される。

20

【0079】

例示的に、M=2の場合、図6に示すように、第1のレジスタユニットグループG0A-1は、クロック信号線の延長方向F1に順次配置される奇数番目のシフトレジスタユニットを含み得る。第1のクロック信号線グループGc-1は、第1のクロック信号線GCK1および第2のクロック信号線GCB1を含み得る。第1のレジスタユニットグループG0A-1のシフトレジスタユニットはカスケード接続される。例えば、第1のレジスタユニットグループG0A-1では、第1レベルのシフトレジスタユニットの入力信号端は、第1のフレームにおいてトリガ信号端に電気的に接続され、シフトレジスタユニットの隣接する2つのレベルごとに、前のレベルのシフトレジスタユニットの出力信号端は、次のレベルのシフトレジスタユニットの入力信号端に電気的に接続される。例えば、第1のレジスタユニットグループG0A-1は、シフトレジスタユニットSR2n-3、SR2n-1、SR2n+1、SR2n+3などを含み得る。ここで、シフトレジスタユニットSR2n-3の出力信号端は、シフトレジスタユニットSR2n-1の入力信号端に電気的に接続され、シフトレジスタユニットSR2n-1の出力信号端は、シフトレジスタユニットSR2n+1の入力信号端に電気的に接続され、シフトレジスタユニットSR2n+1の出力信号端は、シフトレジスタユニットSR2n+3の入力信号端に電気的に接続される。

30

【0080】

また、第1のレジスタユニットグループG0A-1にカスケード接続された複数のシフトレジスタユニットについて、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートおよび偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極はすべて、第1のクロック信号線GCK1に電気的に接続される。および、奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極と偶数レベルのシフトレジスタユニットの入力トランジスタのゲートはすべて、第2のクロック信号線GCB1に電気的に接続される。または、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して第1のクロック信号線に電気的に接続され、奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して第1の電力線に電気的に接続される。および、偶数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して第2のクロック信号線に電気的に接続され、偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極は

40

50

、対応する第2の接続線を介して第1の電力線に電気的に接続される。

【0081】

例示的に、 $M = 2$ の場合、図6に示すように、第2のレジスタユニットグループG O A - 2は、クロック信号線の延長方向に順次配置された偶数番目のシフトレジスタユニットを含み得る。第2のクロック信号線グループG C - 2は、第3のクロック信号線G C K 2および第4のクロック信号線G C B 2を含み得る。第2のレジスタユニットグループG O A - 2のシフトレジスタユニットはカスケード接続される。例えば、第2のレジスタユニットグループG O A - 2において、第1レベルのシフトレジスタユニットの入力信号端は、第2のフレームにおいてトリガ信号端に電気的に接続され、シフトレジスタユニットの隣接する2つのレベルごとに、前のレベルのシフトレジスタユニットの出力信号端は、次のレベルのシフトレジスタユニットの入力信号端に電気的に接続される。例えば、第2のレジスタユニットグループG O A - 2は、シフトレジスタユニットS R 2 n - 2、S R 2 n、S R 2 n + 2、S R 2 n + 4などを含み得る。ここで、シフトレジスタユニットS R 2 n - 2の出力信号端は、シフトレジスタユニットS R 2 nの入力信号端に電気的に接続され、シフトレジスタユニットS R 2 nの出力信号端は、シフトレジスタユニットS R 2 n + 2の入力信号端に電気的に接続され、シフトレジスタユニットS R 2 n + 2の出力信号端は、シフトレジスタユニットS R 2 n + 4の入力信号端に電気的に接続される。

10

【0082】

また、第2のレジスタユニットグループG O A - 2にカスケード接続された複数のシフトレジスタユニットについて、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートおよび偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極はすべて、第3のクロック信号線G C K 2に電気的に接続される。および、奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極と偶数レベルのシフトレジスタユニットの入力トランジスタのゲートはすべて、第4のクロック信号線G C B 2に電気的に接続される。または、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して第3のクロック信号線に電気的に接続され、奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して第1の電力線に電気的に接続され、および、偶数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線を介して第4のクロック信号線に電気的に接続され、偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線を介して第1の電力線に電気的に接続される。

20

【0083】

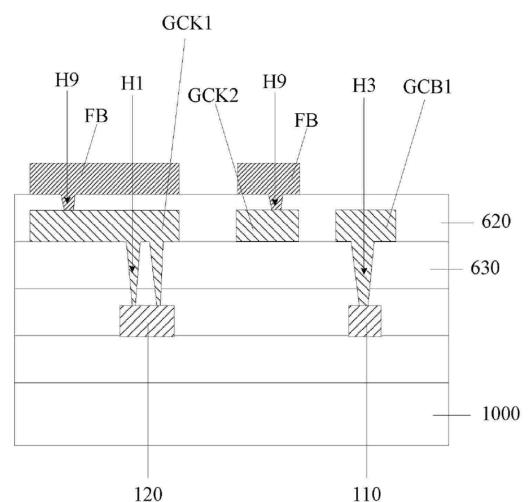

図6は、本発明いくつかの実施形態によって提供されるゲート駆動回路01のレイアウト(Layout)構造の概略図である。図7a - 図7dは、本発明いくつかの実施形態によって提供されるゲート駆動回路01のすべての層の概略図である。図8aは、図6に示すゲート駆動回路01のレイアウト構造の概略図の方向A A'に沿った断面構造の概略図である。図8bは、方向に沿った断面構造の概略図である。ここで、示す例は、第1のレジスタユニットグループG O A - 1に含まれるシフトレジスタユニットS R 2 n - 3、S R 2 n - 1、S R 2 n + 1、S R 2 n + 3、第2のレジスタユニットグループG O A - 2に含まれるシフトレジスタユニットS R 2 n - 2、S R 2 n、S R 2 n + 2、S R 2 n + 4を例として挙げた。

30

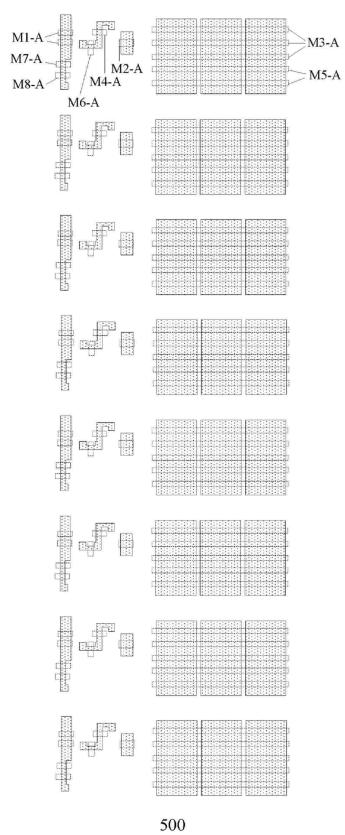

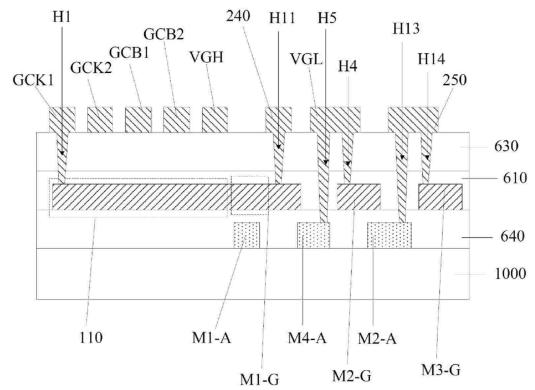

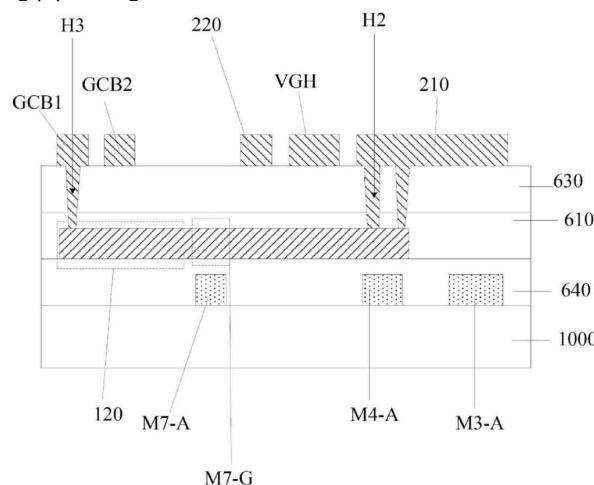

【0084】

例示的に、図6、図7a、図8aおよび図8bに示されるように、ゲート駆動回路01の半導体層500が示されている。半導体層500は、半導体材料をパターン化することによって形成することができる。半導体層500を使用して、上記の複数のトランジスタの活性層を製造し、例えば、入力トランジスタから第8のトランジスタM1 ~ M8への活性層を製造する。ここで、各活性層は、ソース領域、ドレイン領域およびソース領域とドレイン領域との間に位置するチャネル領域を含む。例えば、入力トランジスタM1のチャネル領域M1 - A、電圧安定化トランジスタM2のチャネル領域M2 - A、出力トランジスタM3のチャネル領域M3 - A、第1の制御トランジスタM4のチャネル領域M4 - A

40

50

、第2の制御トランジスタM5のチャネル領域M5-A、第6のトランジスタM6のチャネル領域M6-A、第7のトランジスタM7のチャネル領域M7-A、第8のトランジスタM8のチャネル領域M8-A。図7aの長方形の破線のボックスは、上記のトランジスタのチャネル領域を示している。

【0085】

いくつかの実施形態では、図6および図7aに示されるように、同じシフトレジスタユニットにおいて、出力トランジスタの活性層および第2の制御トランジスタの活性層は、統合された構造で配置され得る。

【0086】

さらに、半導体層500は、上記ピクセル駆動回路上の駆動トランジスタT1、データ書き込みトランジスタT2、閾値補償トランジスタT3、第1の発光制御トランジスタT4、第2の発光制御トランジスタT5、第1のリセットトランジスタT6および第2のリセットトランジスタT7の活性層を製造するためにさらに使用されることに留意されたい。

10

【0087】

さらに、例示的に、半導体層500は、アモルファスシリコン、ポリシリコン、酸化物半導体材料などを採用することによって製造することができる。上記のソース領域およびドレイン領域は、n型不純物またはp型不純物をドープすることによって形成された導電性領域であり得ることに留意されたい。

【0088】

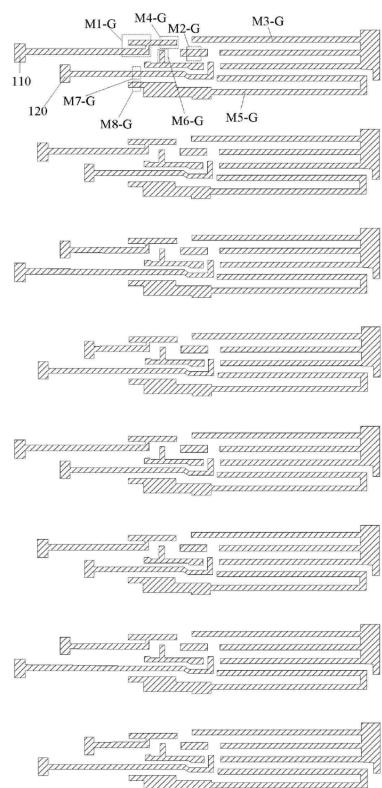

例示的に、図8aおよび図8bに示されるように、ゲート絶縁層640は、上記の半導体層500を保護するために、上記の半導体層500上に形成される。図6、図7b、図8aおよび図8bには、上記ゲート駆動回路01の第1の導電層100が示されている。第1の導電層100は、半導体層500から絶縁されるように、ベース基板1000とは反対側に面するゲート絶縁層640の片側に配置される。第1の導電層100は、複数のスキャンライン、上記複数のトランジスタのゲート、複数の第1の接続線110および複数の第2の接続線120を含む。例えば、入力トランジスタM1のゲートM1-G、電圧安定化トランジスタM2のゲートM2-G、出力トランジスタM3のゲートM3-G、第1の制御トランジスタM4のゲートM4-G、第2の制御トランジスタM5のゲートM5-G、第6のトランジスタM6のゲートM6-G、第7のトランジスタM7のゲートM7-G、第8のトランジスタM8のゲートM8-Gを含む。また、第1の導電層100は、さらに、ピクセル駆動回路内の駆動トランジスタT1、データ書き込みトランジスタT2、閾値補償トランジスタT3、第1の発光制御トランジスタT4、第2の発光制御トランジスタT5、第1のリセットトランジスタT6および第2のリセットトランジスタT7のゲートを含む。第1の導電層100は、さらに発光制御ラインEMなどをさらに含むことができる。ベース基板1000上の第1の導電層100の正投影とベース基板1000上の半導体層500内のチャネル領域の正投影の重複部分は、上記トランジスタのゲートとして設定されていることに留意されたい。

20

30

【0089】

いくつかの実施形態では、1つのシフトレジスタユニットは、少なくとも1つの第1の接続線110および少なくとも1つの第2の接続線120に対応する。1つのシフトレジスタユニットおよびシフトレジスタユニットに対応するクロック信号線グループについて、第1の接続線110の一方の端は、シフトレジスタユニットの入力トランジスタのゲートに直接電気的に接続され、第1の接続線110のもう一方の端は、第1のビアホールH1を介してクロック信号線グループ内の1つのクロック信号線に電気的に接続される。第2の接続線の一方の端は、第2のビアホールを介して第1の転送部に電気的に接続され、第2の接続線のもう一方の端は、第3のビアホールを介してクロック信号線グループ内の別のクロック信号線、または第1の電力線に電気的に接続される。例えば、第1のレジスタユニットグループG0A-1では、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線110を介して第1のクロック信号線GCK1に電気的に接続され、偶数レベルのシフトレジスタユニットの入力トランジスタのゲート

40

50

は、対応する第1の接続線110を介して第2のクロック信号線GCB1に電気的に接続される。および、第2のレジスタユニットグループGOA-2では、奇数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線110を介して第3のクロック信号線GCK2に電気的に接続され、偶数レベルのシフトレジスタユニットの入力トランジスタのゲートは、対応する第1の接続線110を介して第4のクロック信号線GCB2に電気的に接続される。

【0090】

また、1つのシフトレジスタユニットについて、当該シフトレジスタユニットの第1の制御トランジスタのゲートは、対応する第1の接続線110に直接電気的に接続され、その結果、第1の制御トランジスタのゲートおよび入力トランジスタのゲートは、一体構造として配置することができる。

10

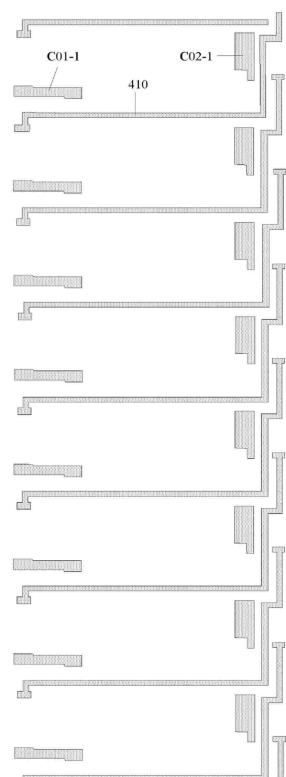

【0091】

例示的に、図8aおよび図8bに示されるように、第1の絶縁層610は、上記の第1の導電層100を保護するために、上記の第1の導電層100上に形成される。図6、図7c図、8aおよび図8bには、前記ゲート駆動回路01の第4の導電層400が示されている。第4の導電層400は、ベース基板1000とは反対側に面する第1の絶縁層610の片側に配置される。第4の導電層400は、複数の第1の導電部C01-1、複数の第2の導電部C02-1、複数の第3の導電部410を含み得る。ここで、1つの第1の導電性部分C01-1および1つの第2の導電性部分C02-1は、1つのシフトレジスタに配置されている。すなわち、1つの第1の導電性部分C01-1は、1つの第2の制御トランジスタM5に対応し、1つの第2の導電性部分C02-1は、1つの出力トランジスタM3に対応する。

20

【0092】

例示的に、ベース基板上の第1の導電部C01-1の正投影およびベース基板上の第2の制御トランジスタM5のゲートM5-Gの正投影は、重複領域を有し、それにより、第1のコンデンサC01が形成される。ここで、第1の導電部C01-1は、第1のコンデンサC01の第1の極C01-1として機能し、第2の制御トランジスタM5のゲートM5-Gは、第1のコンデンサC01の第2の極として機能する。

30

【0093】

いくつかの実施形態では、ベース基板上の第2の導電部C02-1の正投影とベース基板上の出力トランジスタM3のゲートM3-Gの正投影とは、重なり合う領域を有し、それにより、第2のコンデンサC02が形成される。ここで、第2の導電部C02-1は、第2のコンデンサC02の第1の極として機能する。出力トランジスタM3のゲートM3-Gは、第2のコンデンサC02の第2の極として機能する。

40

【0094】

いくつかの実施形態では、カスケードの2つのシフトレジスタユニットは、1つの第3の導電部410を介して電気的に接続され得る。例えば、カスケードの2つのシフトレジスタユニットでは、前のレベルのシフトレジスタユニットの出力トランジスタの第1の極は、第3の導電部410を介して次のレベルのシフトレジスタユニットの入力トランジスタの第1の極に電気的に接続される。

40

【0095】

いくつかの実施形態では、ベース基板上の第2の制御トランジスタのゲートの正投影は、ベース基板上の第1の導電性部分の正投影を覆うように作られ得る。

【0096】

第4の導電層400は、上記のピクセル駆動回路内の記憶コンデンサCSTの第1の極およびリセット信号線をさらに含み得ることに留意されたい。

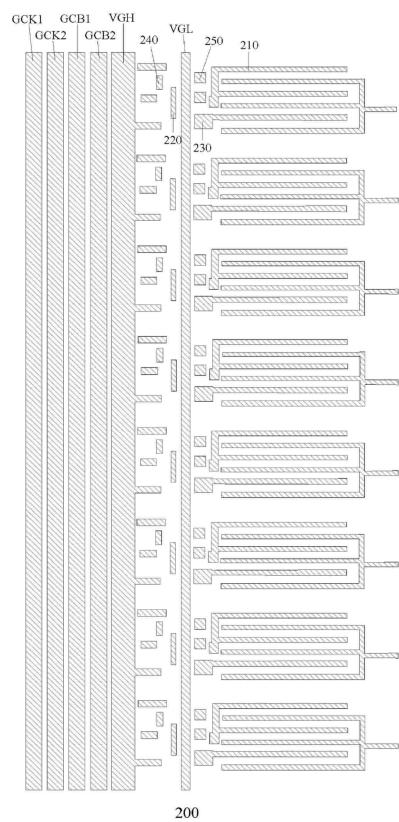

【0097】

例示的に、図8aおよび図8bに示されるように、第3の絶縁層630は、上記の第4の導電層400を保護するために、上記の第4の導電層400上に形成される。図6、図7d、図8aおよび図8bには、当該ゲート駆動回路01の第2の導電層200が示され

50

、第2の導電層200は、ベース基板1000とは反対側に面する第3の絶縁層630の片側に配置される。第2の導電層200は、複数のデータラインVD、第1の電力線VG<sub>L</sub>、第2の電力線VG<sub>H</sub>、複数のクロック信号線（例えば、第1のクロック信号線GCK<sub>1</sub>、第2のクロック信号線GCK<sub>2</sub>、第3のクロック信号線GCK<sub>3</sub>、第4のクロック信号線GCK<sub>4</sub>）、複数の第1の転送部210、複数の第2の転送部220、複数の第3の転送部230、複数の第4の転送部240および複数の第5の転送部250を含み得る。ここで、1つのシフトレジスタには、1つの第1の転送部210、1つの第2の転送部220、1つの第3の転送部230、1つの第4の転送部240、1つの第5の転送部250が配置されている。

#### 【0098】

10

いくつかの実施形態では、図6および図8bに示されるように、1つの第1の転送部210は、1つの出力トランジスタに対応して配置され、1つの第1の転送部210は、第10のビアホールを介して1つの出力トランジスタの活性層のソース領域に電気的に接続される。また、第2の接続線120の一方の端は、第2のビアホールH2を介して第1の転送部210に電気的に接続され、第2の接続線120のもう一方の端は、第3のビアホールH3を介してクロック信号線に電気的に接続される。

#### 【0099】

20

いくつかの実施形態では、図6に示されるように、1つの第2の転送部220は、1つの第1の制御トランジスタに対応して配置され、第1の制御トランジスタの活性層のドレイン領域は、対応する第2の転送部220を介して第2の制御トランジスタのゲートに電気的に接続される。

#### 【0100】

いくつかの実施形態では、図6および図8aに示されるように、1つの第3の転送部230は、1つの第2の制御トランジスタに対応する。第2の制御トランジスタの活性層のソース領域は、第6のビアホールH6を介して対応する第3の転送部230の一方の端に電気的に接続され、第3の転送部230のもう一方の端は、第7のビアホールH7を介して対応する第1の導電部の一方の端に電気的に接続され、第1の導電部のもう一方の端は、第8のビアホールH8を介して第2の電力線に電気的に接続され、第2の制御トランジスタの活性層のドレイン領域は、出力トランジスタの活性層のドレイン領域と共有される。

#### 【0101】

30

いくつかの実施形態では、図6および図8aに示されるように、1つの第4の転送部240は、1つの第6のトランジスタM6に対応する。第4の転送部240の一方の端は、第11のビアホールH11を介して入力トランジスタM1のゲートM1-Gに電気的に接続され、第4の転送部240のもう一方の端は、第12のビアホールを介して第6のトランジスタM6の活性層のソース領域に電気的に接続される。

#### 【0102】

いくつかの実施形態では、図6および図8aに示されるように、1つの第5の転送部250は、1つの電圧安定化トランジスタM2に対応する。第5の転送部250の一方の端は、第13のビアホールH13を介して電圧安定化トランジスタM2の活性層のドレイン領域に電気的に接続され、第5の転送部250のもう一方の端は、第14のビアホールH14を介して出力トランジスタM3のゲートに電気的に接続される。

40

#### 【0103】

他のトランジスタ間の電気的接続関係は、他の転送部を使用することによって達成できることに留意されたい。ここでは繰り返されない。

#### 【0104】

いくつかの実施形態では、図6に示されるように、第1のレジスタユニットグループG<sub>0A-1</sub>では、奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極（例えば、出力トランジスタの活性層のソース領域）は、対応する第2の接続線120を介して第2のクロック信号線GCB1に電気的に接続され、偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極（例えば、出力トランジスタの活性層のソース領域）

50

は、対応する第2の接続線120を介して第1のクロック信号線GCK1に電気的に接続される。および、第2のレジスタユニットグループGOA-2では、奇数レベルのシフトレジスタユニットの出力トランジスタの第1の極（例えば、出力トランジスタの活性層のソース領域）は、対応する第2の接続線120を介して第4のクロック信号線GCB2に電気的に接続され、偶数レベルのシフトレジスタユニットの出力トランジスタの第1の極は、対応する第2の接続線120を介して第3のクロック信号線GCK2に電気的に接続される。

#### 【0105】

いくつかの実施形態では、図6、図8aおよび図8bに示されるように、各電圧安定化トランジスタのゲートは、第4のピアホールH4を介して第1の電力線に電気的に接続され、電圧安定化トランジスタのゲートに対応の電圧信号を入力する。

10

#### 【0106】

いくつかの実施形態では、図6、図8aおよび図8bに示されるように、同じゲート駆動回路01では、ベース基板上の入力トランジスタの正投影は、ベース基板上の第1の電力線の正投影とベース基板上の複数のクロック信号線の正投影との間に配置される。ベース基板上の電圧安定化トランジスタの正投影は、ベース基板上の複数のクロック信号線の正投影とは反対側を面する、ベース基板上の第1の電力線の正投影の片側に配置されている。ベース基板上の出力トランジスタの正投影は、ベース基板上の第1の電力線の正投影とは反対側を面する、ベース基板上の電圧安定化トランジスタの正投影の片側に配置されている。

20

#### 【0107】

いくつかの実施形態では、図6、図8aおよび図8bに示されるように、第1の制御トランジスタの活性層のソース領域は、第5のピアホールH5を介して第1の電力線に電気的に接続され、その結果、対応する電圧信号が、第1の制御トランジスタの活性層のソース領域に入力され得る。

#### 【0108】

いくつかの実施形態では、図6に示されるように、ベース基板上の第2の電力線の正投影は、ベース基板上の複数のクロック信号線の正投影とベース基板上のゲート駆動回路01の正投影との間に配置される。また、シフトレジスタユニットでは、ベース基板上の第1の制御トランジスタの正投影は、ベース基板上の入力トランジスタの正投影とベース基板上の第1の電力線の正投影との間に配置される。および、シフトレジスタユニットでは、ベース基板上の第2の制御トランジスタの正投影は、ベース基板上の第1の電力線の正投影とは反対側を面する、ベース基板上の入力トランジスタの正投影の片側に配置されている。

30

#### 【0109】

いくつかの実施形態では、図6に示されるように、ベース基板上の第2の制御トランジスタのゲートの正投影およびベース基板上の第1の導電部の正投影は、それぞれ、ベース基板上の第1の電力線の正投影と重複領域を有する。

#### 【0110】

いくつかの実施形態では、図6に示されるように、ベース基板上の第8のピアホールH8の正投影は、第1の電力線とベース基板上の第2の電力線の正投影との間に配置される。ベース基板上の第7のピアホールH7の正投影は、ベース基板上の第1の電力線の正投影とベース基板上の第2の制御トランジスタの活性層の正投影との間に配置される。

40

#### 【0111】

図8aおよび図8bに示すように、ゲート絶縁層640は、半導体層500と第1の導電層100との間に配置され、第1の絶縁層610は、第1の導電層100と第4の導電層400との間に配置される。第3の絶縁層630は、第4の導電層400と第2の導電層200との間に配置され、第2の絶縁層620は、第2の導電層200と第3の導電層300との間に配置される。上記各ピアホールは、間隔を置いて形成される。また、第1のピアホールH1、第2のピアホールH2、第3のピアホールH3、第4のピアホールH

50

4、第11のピアホールH11、第14のピアホールH14は、第1の絶縁層と第3の絶縁層を貫通している。第5のピアホールH5、第6のピアホールH6、第12のピアホール、および第13のピアホールH13は、第1の絶縁層、第3の絶縁層、およびゲート絶縁層を貫通する。第7のピアホールH7および第8のピアホールH8は、第3の絶縁層を貫通する。

#### 【0112】

図9に示されるように、本発明の実施形態によって提供されるいくつかの他のディスプレイパネルの概略構造図は、上記の実施形態の実施のために修正される。本実施形態と上記実施形態との相違点のみを以下に説明し、ここでは類似点を繰り返さない。

#### 【0113】

例示的に、図9から図11に示されるように、第2の絶縁層620は、上記の第2の導電層200を保護するために、上記の第4の導電層200上に形成される。図9から図11に示されるように、当該ゲート駆動回路01の第3の導電層300が示され、第3の導電層300は、ベース基板1000とは反対側に面する第2の絶縁層620の片側に配置される。また、第3の導電層300は、少なくとも1つの補助線を含む。ここで、1つの補助線と1つのクロック信号線は、少なくとも1つの第9のピアホールH9に電気的に接続され、第9のピアホールH9は、第2の絶縁層620を貫通する。

#### 【0114】

いくつかの実施形態では、図9に示されるように、ベース基板上のクロック信号線の正投影は、ベース基板上の電気的に接続された補助線の正投影覆う。さらに、ベース基板上のクロック信号線の正投影は、ベース基板上の電気的に接続された補助線の正投影と重複するようにすることができる。このようにして、補助線の占有面積を減らすことができ、その結果、非表示領域BBの占有面積を減らすことができる。

#### 【0115】

いくつかの実施形態では、図9に示されるように、第2の導電層は、複数の補助線を含む。1つの補助線は、複数の第9のピアホールH9を介して1つのクロック信号線に電気的に接続される。このようにして、各クロック信号線の抵抗を低減することができる。

#### 【0116】

いくつかの実施形態では、図9に示されるように、2つの隣接するクロック信号線ごとの第9のピアホールH9は、ずらして配置され得る。このようにして、均一性を改善するために、第9のピアホールH9を分散して配置することができる。

#### 【0117】

いくつかの実施形態では、図9に示されるように、ベース基板上の第9のピアホールH9の正投影は、ベース基板上の第1のピアホールH1および第3のピアホールH3の正投影と重複しない。電気接続の精度を向上させることができる。

#### 【0118】

同じ発明の思想に基づいて、本発明の実施形態は、以下を含むディスプレイパネルの駆動方法をさらに提供する。

#### 【0119】

1フレームのスキャン時間において、すべての駆動ラインを行ごとにスキャンするように順次動作するように各シフトレジスタユニットを制御し、ここで、クロック信号線の延長方向に順次配置された奇数番目のシフトレジスタユニットおよび偶数番目のシフトレジスタユニットは、異なるクロック信号線グループの制御下で独立して駆動される。

#### 【0120】

例示的に、図4c、図6および図12に示されるように、1フレームのスキャン時間において、奇数番目のシフトレジスタユニット（すなわち、第1のレジスタユニットグループG0A-1）は、電気的に接続されたスキャンラインに信号を入力するために、第1のクロック信号線GCK1と第2のクロック信号線GCB1によって入力されたクロック信号の制御下で動作する。また、偶数番目のシフトレジスタユニット（すなわち、第2のレジスタユニットグループG0A-2）は、電気的に接続されたスキャンラインに信号を入

10

20

30

40

50

力するために、第3のクロック信号線GCK2と第4のクロック信号線GCB2によって入力されたクロック信号の制御下で動作する。したがって、すべてのスキャンラインが行ごとにスキャンを実行できる。

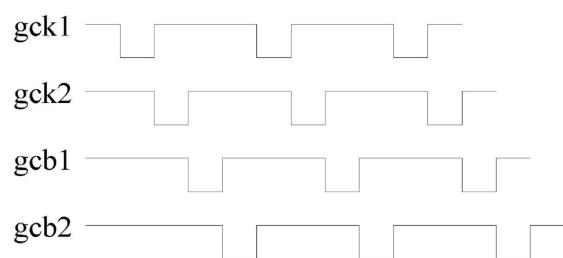

【0121】

図12は、第1のクロック信号線GCK1によって送信される信号gkk1、第2のクロック信号線GCB1によって送信される信号gcb1、第3のクロック信号線GCK2によって送信される信号gkk2、および第4のクロック信号線GCB2を示す。

【0122】

本発明の実施形態は、ディスプレイパネルの駆動方法を提供する。異なるクロック信号線グループの複数のクロック信号線に印加される信号の、アクティブルーベルを維持するための時間は、お互いに重複しない。例えば、図12に示すように、クロック信号線に印加される信号アクティブルーベルは低レベルであり、すべてのクロック信号線に印加される信号の低レベルは重複しない。

10

【0123】

同じ発明の思想に基づいて、本発明の実施形態は、本発明の実施形態によって提供される上記のディスプレイパネルを含む、ディスプレイデバイスをさらに提供する。当該ディスプレイデバイスの実施は、上記のディスプレイパネルの実施形態を参照することができ、繰り返しは省略される。

【0124】

特定の実施中、本発明の実施形態では、ディスプレイデバイスは、携帯電話、タブレットコンピュータ、テレビ、ディスプレイ、ノートブックコンピュータ、デジタルフォトフレーム、およびナビゲーターなどの、ディスプレイ機能を備えた任意の製品またはコンポーネントであり得る。当業者は、当該ディスプレイデバイスが他の必須の構成部品を有するべきであり、これはここでは繰り返されず、本発明の限定と見なされるべきではないことを理解されるべきである。

20

【0125】

本発明の好ましい実施形態が説明されてきたが、当業者は、基本的な創造的概念を知った後、これらの実施形態に追加の修正および変形を加えることができる。したがって、添付の特許請求の範囲は、本発明の範囲内にある好ましい実施形態およびすべての修正および変形を含むものとして説明されることを意図している。

30

【0126】

明らかに、当技術分野の当業者は、本発明の実施形態の精神および範囲から逸脱することなく、本発明の実施形態に対して様々な修正および変形を行うことができる。このように、本発明の実施形態のこれらの修正および変形は、本発明およびそれらの同等の技術の特許請求の範囲内にある場合、本発明はまた、これらの修正および変形を含むことを意図する。

40

50

【図面】

【図 1】

【図 2】

10

20

30

40

【図 3】

【図 4 a】

50

【図 4 b】

【図 4 c】

10

【図 5 a】

【図 5 b】

20

30

40

50

【図6】

【図7 a】

10

20

500

【図7 b】

100

【図7 c】

30

40

400

50

【図 7 d】

【図 8 a】

10

20

【図 8 b】

【図 9】

30

40

50

【図 1 0】

【図 1 1】

10

20

【図 1 2】

30

40

50

## フロントページの続き

## (51)国際特許分類

|         | F I              |         |        |       |

|---------|------------------|---------|--------|-------|

| H 1 0 K | 59/12 (2023.01)  | G 0 9 F | 9/30   | 3 3 8 |

| H 1 0 K | 59/131 (2023.01) | G 0 9 F | 9/30   | 3 6 5 |

| G 1 1 C | 19/28 (2006.01)  | H 1 0 K | 59/10  |       |

|         |                  | H 1 0 K | 59/12  |       |

|         |                  | H 1 0 K | 59/131 |       |

|         |                  | G 1 1 C | 19/28  | 2 3 0 |

中華人民共和国 6 1 1 7 3 1 四川省成都市高新區(西區)合作路 1 1 8 8 號

N o . 1 1 8 8 , H e z u o R d . , ( W e s t Z o n e ) , H i - t e c h D e v e l o p

m e n t Z o n e , C h e n g d u , S i c h u a n , 6 1 1 7 3 1 , P . R . C H I N A

(74)代理人 110001243

弁理士法人谷・阿部特許事務所

(72)発明者 パン ユーチエン

中華人民共和国 1 0 0 1 7 6 ベイジン ビーディーエー ディーゾー ロード ナンバー 9

(72)発明者 シアオ ユンション

中華人民共和国 1 0 0 1 7 6 ベイジン ビーディーエー ディーゾー ロード ナンバー 9

(72)発明者 チン ハイガン

中華人民共和国 1 0 0 1 7 6 ベイジン ビーディーエー ディーゾー ロード ナンバー 9

(72)発明者 ワン ミアオ

中華人民共和国 1 0 0 1 7 6 ベイジン ビーディーエー ディーゾー ロード ナンバー 9

(72)発明者 ジャン ティアオメイ

中華人民共和国 1 0 0 1 7 6 ベイジン ビーディーエー ディーゾー ロード ナンバー 9

(72)発明者 ワン モンチー

中華人民共和国 1 0 0 1 7 6 ベイジン ビーディーエー ディーゾー ロード ナンバー 9

審査官 中村 直行

(56)参考文献 国際公開第2 0 1 1 / 0 0 7 5 9 1 ( W O , A 1 )

特開2 0 1 9 - 1 0 6 5 4 0 ( J P , A )

中国特許出願公開第1 0 5 4 4 8 2 6 1 ( C N , A )

米国特許出願公開第2 0 1 9 / 0 3 0 4 3 7 4 ( U S , A 1 )

(58)調査した分野 (Int.Cl. , D B 名)

G 0 9 G 3 / 0 0 - 5 / 4 2

G 0 9 F 9 / 0 0 - 9 / 4 6

H 0 5 B 4 4 / 0 0

H 0 5 B 4 5 / 6 0

H 0 5 B 3 3 / 0 0 - 3 3 / 2 8

H 1 0 K 5 0 / 0 0 - 9 9 / 0 0

G 1 1 C 1 9 / 2 8