(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5680184号

(P5680184)

(45) 発行日 平成27年3月4日(2015.3.4)

(24) 登録日 平成27年1月16日(2015.1.16)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G06F 12/00 550E

請求項の数 19 (全 11 頁)

(21) 出願番号 特願2013-504943 (P2013-504943)

(86) (22) 出願日 平成23年4月5日 (2011.4.5)

(65) 公表番号 特表2013-524383 (P2013-524383A)

(43) 公表日 平成25年6月17日 (2013.6.17)

(86) 國際出願番号 PCT/US2011/031221

(87) 國際公開番号 WO2011/130059

(87) 國際公開日 平成23年10月20日 (2011.10.20)

審査請求日 平成26年4月7日 (2014.4.7)

(31) 優先権主張番号 12/758,301

(32) 優先日 平成22年4月12日 (2010.4.12)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンノイベイル、ビィ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】データバス反転信号伝達を用いる同時スイッチング出力の低減

## (57) 【特許請求の範囲】

## 【請求項 1】

データを通信するためのデータバスを定義する複数のデータ線と、

複数のデータタイムスロットを用いて前記データバスを介して複数のデータ転送を通信

するように動作する制御器と、を備える装置であって、

前記データタイムスロットの少なくともサブセットに対して前記制御器は関連データタ

イムスロットの間に通信されるビットが反転されている旨を示す関連データバス反転標識

を通信するように動作し、前記データ転送の前記サブセットに対する前記関連データバス

反転標識はデータバス反転ベクトルへとグループ化され、前記制御器は前記データバス反

転ベクトルの反転を示すグローバルデータバス反転標識を通信するように動作する装置。 10

## 【請求項 2】

信号線を更に備え、前記制御器は前記信号線を介して前記グローバルデータバス反転標

識を通信するように動作する請求項 1 の装置。

## 【請求項 3】

前記信号線はデータマスク線を含む請求項 2 の装置。

## 【請求項 4】

前記データバス反転ベクトルは前記複数のデータタイムスロット以外の制御タイムスロ

ットにおいて前記データ線を介して通信され、前記制御器は、書き込み動作の間の前記デ

タ転送に対して前記データマスク線を介してデータマスク情報を通信するとともに、前

記制御タイムスロットの間に前記データマスク線を介して前記グローバルデータバス反転 20

標識を通信するように動作する請求項 3 の装置。

**【請求項 5】**

前記データバス反転ベクトルは前記複数のデータタイムスロット以外の制御タイムスロットにおいて前記データ線を介して通信され、前記制御器は、前記制御タイムスロットの間に前記データ線を介して前記グローバルデータバス反転標識を通信するように動作する請求項 3 の装置。

**【請求項 6】**

前記データバス反転ベクトルは前記複数のデータタイムスロット以外の制御タイムスロットにおいて前記データ線を介して通信される請求項 1 の装置。

**【請求項 7】**

前記グローバルデータバス反転標識は前記制御タイムスロットの間に前記データ線を介して通信される請求項 6 の装置。

**【請求項 8】**

前記データ線は第 1 のグループ及び第 2 のグループへとグループ化され、前記データバス反転ベクトルは前記第 1 のグループに関連付けられる第 1 の部分及び前記第 2 のグループに関連付けられる第 2 の部分を有し、前記第 1 の部分は前記データタイムスロットの第 1 のサブセットをカバーし、前記第 2 の部分は前記データタイムスロットの第 2 のサブセットをカバーし、前記第 1 のサブセットに含まれないデータタイムスロットは前記第 2 のサブセットに含まれないデータタイムスロットと重複しない請求項 7 の装置。

**【請求項 9】**

前記第 1 のグループは第 1 のメモリに関連付けられ、前記第 2 のグループは第 2 のメモリに関連付けられる請求項 8 の装置。

**【請求項 10】**

前記制御器はメモリ制御器である請求項 1 の装置。

**【請求項 11】**

前記制御器はメモリデバイスに組み込まれている請求項 1 の装置。

**【請求項 12】**

プロセッサとメモリとを更に備え、

前記複数のデータ線は前記プロセッサを前記メモリに接続する請求項 1 の装置。

**【請求項 13】**

前記データバスはアドレスバスを含む請求項 1 の装置。

**【請求項 14】**

複数のデータタイムスロットを用いデータバスを定義する複数のデータ線を介して複数のデータ転送を通信することと、

前記データタイムスロットの少なくともサブセットに対するデータバス反転標識であつて関連データタイムスロットの間に通信されるビットが反転されている旨を示すデータバス反転標識を通信することと、

データバス反転ベクトルの反転を示すグローバルデータバス反転標識を通信することと、を備え、

前記データ転送の前記サブセットに対する前記データバス反転標識は前記データバス反転ベクトルへとグループ化される方法。

**【請求項 15】**

前記グローバルデータバス反転標識を通信することは前記データ線の少なくとも 1 つを用いて前記グローバルデータバス反転標識を通信することを備える請求項 14 の方法。

**【請求項 16】**

前記データバス反転ベクトルは前記データタイムスロットの総数未満をカバーし、前記グローバルデータバス反転標識は少なくとも 1 つの制御タイムスロットの間に前記データバス反転ベクトルと共に通信される請求項 15 の方法。

**【請求項 17】**

前記グローバルデータバス反転標識を通信することは前記データ線以外の前記データバ

10

20

30

40

50

スに関連する信号線を用いて前記グローバルデータバス反転標識を通信することを備える請求項14の方法。

【請求項18】

前記信号線はデータマスク線を含む請求項17の方法。

【請求項19】

前記データバスはアドレスバスを含む請求項14の方法。

【発明の詳細な説明】

【技術分野】

【0001】

開示される主題は、概してコンピューティングシステムに関し、より特定的にはデータバス反転信号伝達(data bus inversion signaling)を用いて同時スイッチング出力(simultaneous switching outputs)を低減するための方法及び装置に関する。 10

【背景技術】

【0002】

コンピューティングシステムにおいては、プロセッサ又は他のコンピューティングデバイスによってその動作の間に使用される大量のデータを記憶するために、ダイナミックメモリデバイスが用いられる。データはコンピューティングデバイスとメモリデバイスの間でメモリバスを介して転送される。このような電子システムにおいては、通常、電気的な「1」を駆動するのと、電気的な「0」を駆動するのとで、異なる電力要求が存在する。例えばある種のダブルデータレート(DDR)同期ダイナミックランダムアクセスメモリ(SDRAM)においては、「1」を駆動するよりも「0」を駆動する方が大きな電力を消費する。 20

【0003】

データバス反転(DBI)は、交互信号伝達状態(alternate signaled states)の両者間で消費電力が非対称なシステムに対してデータバスを選択的に反転することによってDC電力消費を低減することを目的としたI/O信号伝達技術である。データを通信するデバイス(即ち書き込み動作のためのプロセッサ又は読み出し動作のためのメモリデバイス)は、1つのビット転送時間の間にバス上で駆動される「0」の数をカウントし、半分を超えてバスが電気的に「0」であれば、バス状態は反転される。バス反転が生じたことを示すために、DBI標識ビットが切り換えられる。当該ビット転送時間における「0」及び「1」の数がバス幅の半分以下である場合には、反転は生じない。受信デバイスがデータを処理する場合、DBI標識ビットは、データを再び反転して元のデータパターンを再構成するためのトリガーとして用いられる。このようにして、1つのビット転送時間内に送信される「1」の平均数が増大させられ、それによりDC電力が低減される。バス反転はアドレス線の場合にも用いられ得る。従って、ここで用いられる「データバス反転」の用語は、DQバス又はアドレスバス等の任意の種類のバス反転に一般的に適用される。 30

【発明の概要】

【発明が解決しようとする課題】

【0004】

DBIはまた、2つの連続するビット時間転送において「1」へ変化する出力の数から「0」へ変化する出力の数を差し引いた値の絶対値として定義される同時スイッチング出力(SSO)を低減する特性を有する。「0」を传送するよりも「1」を传送する方が低電力であるシステムにおいては、传送されたDBIビットは、非反転に対して「1」で定義され、反転に対して「0」で定義される。全てのビット転送時間が反転を必要とする場合(例えば「0」のストリームの場合であり、この場合「1」へと反転されることになる)であって且つDBIベクトルが最後のデータ転送時間の後に传送される場合、システムは、最後のデータ転送が全て「1」であり且つDBIビット転送が全て「0」である最悪の状況のSSO遷移に直面する。従って、DBIは、新たなSSO問題を導入し得るし、また全体的なSSO利益を損ねる可能性がある。 40

【0005】

50

この文書のこの欄は、以下に説明され且つ／又は特許請求に係る開示される主題の種々の態様に関連し得る技術の種々の態様を紹介することを意図されている。この欄は、開示される主題の種々の態様のより良い理解を容易にするための背景的情情報を提供する。このことを考慮してこの文書のこの欄における記述が読まれるべきであること及び従来技術としての了解ではないことが理解されるべきである。開示される主題は、上述の1つ以上の問題の影響を克服し又は少なくとも低減することに向けられている。

**【課題を解決するための手段】**

**【0006】**

開示される主題の幾つかの態様の基本的な理解を提供するために、開示される主題の簡略化された概要を以下に提示する。この概要是開示される主題の包括的な概説である。開示される主題の鍵となる若しくは臨界的な要素を特定すること又は開示される主題の範囲を表すことは意図されていない。その唯一の目的は、後で議論される更に詳細な説明への序として、幾つかの概念を単純化された形態で提示することである。10

**【0007】**

開示される主題の1つの態様は、データを通信するためのデータバスを定義する複数のデータ線を含む装置において見られる。制御器は、複数のデータタイムスロットを用いてデータバスを介して複数のデータ転送を通信するように動作し、データタイムスロットの少なくともサブセットに対して、制御器は、関連データタイムスロットの間に通信されるビットが反転されている旨を示す関連データバス反転標識を通信するように動作し、データ転送のサブセットに対するデータバス反転標識は、データバス反転ベクトルへとグループ化され、制御器は、データバス反転ベクトルの反転を示すグローバルデータバス反転標識を通信するように動作する。20

**【0008】**

開示される主題の別の態様は、複数のデータタイムスロットを用いデータバスを定義する複数のデータ線を介して複数のデータ転送を通信することと、データタイムスロットの少なくともサブセットに対するデータバス反転標識であって関連データタイムスロットの間に通信されるビットが反転されている旨を示すデータバス反転標識を通信することと、データバス反転ベクトルの反転を示すグローバルデータバス反転標識を通信することと、を含む方法において見られ、データ転送のサブセットに対するデータバス反転標識は、データバス反転ベクトルへとグループ化される。30

**【図面の簡単な説明】**

**【0009】**

開示される主題は添付の図面を参照して以下に説明され、図面において同様の参照番号は同様の要素を表す。

**【0010】**

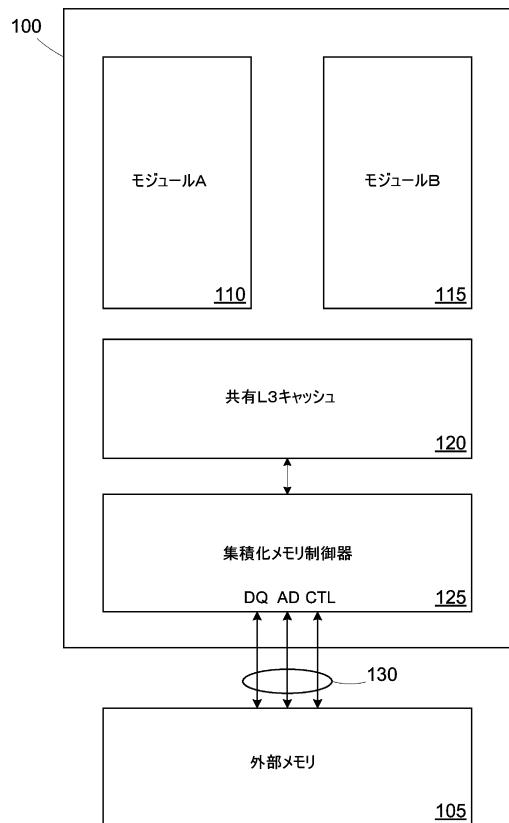

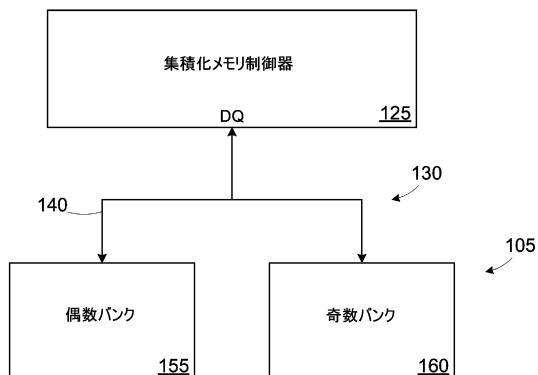

【図1】図1は外部メモリとインターフェースするマイクロプロセッサの単純化されたブロックレベル図である。

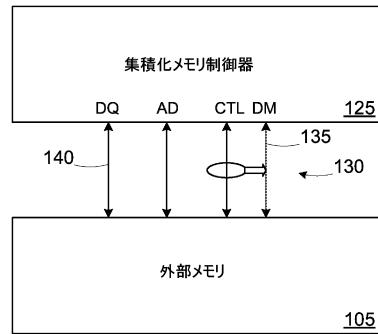

【図2】図2は図1のシステムにおけるメモリ制御器とメモリの間でのインターフェースを示す単純化されたブロック図である。

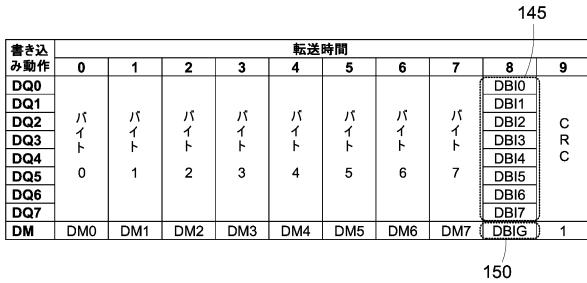

【図3】図3はサイドバンドD B I信号伝達技術を用いるデータ転送を示す図（その1）である。40

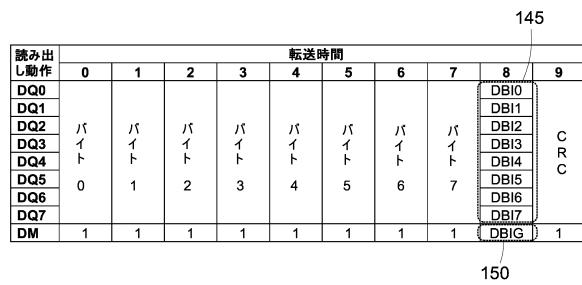

【図4】図4はサイドバンドD B I信号伝達技術を用いるデータ転送を示す図（その2）である。

【図5】図5はサイドバンドD B I信号伝達技術を用いるデータ転送を示す図（その3）である。

【図6】図6は図1のシステムにおけるメモリ制御器とメモリの間でのインターフェースの代替的な実施形態を示す単純化されたブロック図である。

【図7】図7はグローバルD B I信号伝達技術を用いるデータ転送を示す図である。

**【0011】**

開示される主題は種々の修正及び代替的な形態を許容する一方で、その特定の実施形態50

が図面において例として示されており、またここに詳細に説明される。しかし、具体的な実施形態のここでの説明は、開示される主題を開示される特定の形態に限定することを意図されておらず、むしろそれとは逆に、添付の特許請求の範囲によって画定される開示される主題の精神及び範囲内にある全ての修正、均等なもの及び代替案を網羅することが意図されている。

#### 【発明を実施するための形態】

##### 【0012】

開示される主題の1つ以上の具体的な実施形態が以下に説明される。開示される主題は、ここに含まれる実施形態及び図示に限定されるものではなく、むしろ特許請求の範囲内にある実施形態の一部や異なる実施形態の要素の組み合わせを含む実施形態の修正された形態を含むことが具体的に意図されている。任意のそのような実際の実装の開発においては、任意のエンジニアリング又は設計プロジェクトにおいて見られるように、システム関連及びビジネス関連の制約の遵守等の実装毎に変わり得る設計者の具体的な目標を達成するために、種々の実装固有の決定がなされる必要があることが理解されるべきである。また、そのような開発努力は得てして複雑で且つ時間を費やすものであるが、この開示の利益を享受する当業者にとっては設計、製造及び製品化のルーチン的な業務であろうことが理解されるべきである。明示的に「臨界的」又は「本質的」であるものとして示されている場合を除き、本出願のいずれの内容も、開示される主題に対して臨界的又は本質的であると考えられることはない。

##### 【0013】

次に添付の図面を参照して、開示される主題を説明する。説明のみを目的とし且つ開示される主題を当業者にとって周知である詳細で不明瞭にすることのないように、種々の構造、システム及びデバイスが図面に模式的に示されている。にもかかわらず、添付の図面は、開示される主題の例証的な例を記載し且つ説明するために含まれている。ここで用いられる語句は、関連分野を含めた当業者によるそれらの語句の理解と一致する意味を有するもとのして理解され且つ解釈されるべきである。ある用語又は句の特別の定義、即ち当業者によって理解される通常の且つ慣例的な意味とは異なる定義は、ここでのその用語又は句の一貫した使用によって暗示されることが意図されるわけではない。ある用語又は句が特別な意味、即ち当業者によって理解される以外の意味を有することが意図される限りにおいて、そのような特別な定義は、その用語又は句に対するその特別な定義を直接的且つ明白に提供する定義的な方法において明細書内に明示的に記載されることになる。

##### 【0014】

次に、種々の図面を通して同様の参照番号が類似の要素に対応する図面を参照すると、特に図1を参照すると、外部メモリ105に結合されるマイクロプロセッサ100との関連において、開示される主題が説明されることになる。当業者であれば、これらの要素及び他の要素からコンピュータシステムが構成され得ることを認識するはずである。しかし、本発明を不明瞭にすることを避けるために、本発明の理解に有用である要素のみが含まれている。

##### 【0015】

1つの実施形態においては、マイクロプロセッサ100は、一対の実質的に類似のモジュール、即ちモジュールA110及びモジュールB115を採用している。モジュール110, 115は同様の処理能力を含む。モジュール110, 115は、ソフトウェアの制御の下での処理を行い、従ってメモリ、例えば外部メモリ105並びに/又は共有L3キャッシュ120及び/若しくは内部キャッシュ(図示せず)等のキャッシュ、にアクセスする。メモリバス130を介してモジュール110, 115を外部メモリ105とインターフェースするために、集積化メモリ制御器125が設けられている。当業者であれば、モジュール110, 115の各々が他の有用なタスクを行うための追加的な回路を含み得ることを理解するはずである。

##### 【0016】

概してメモリバス130は、データ線(DQ)、アドレス線(AD)並びにチップ選択

10

20

30

40

50

(C S)、書き込みイネーブル (W E)、バンク選択 (B S)、列アクセストロープ (C A S)、行アクセストロープ (R A S)、データマスク (D M) 及びクロック (C L K) 等の制御線 (C T L) を含む。例示される実施形態においては、外部メモリ 105 はダブルデータレート (D D R) メモリであり、この場合データはクロック信号の立ち上がりエッジ及び立下りエッジの両方において転送され得る。

#### 【0017】

集積化メモリ制御器 125 及び外部メモリ 105 はデータバス反転 (D B I) スキームを用いて通信し、ここではデバイスの電力消費を低減するために及び同時スイッチング出力 (S S O) の数を制限することにより雑音を低減するために、D Q 線及び / 又はアドレス線上で駆動されるビットが反転され得る。例示のみを目的として以下の例は D Q 線の反転に関連しているが、この概念はアドレスバス等の任意のバスに適用可能である。概してデータ転送は n 個のタイムスロットを占有し、またデータバス反転は n ビットの D B I ベクトルによって制御され、この場合、ベクトルにおける各ビットは、当該タイムスロットにおいて関連ビットが既に反転されているかどうかを示す。D B I ベクトルそれ自身が既に反転されているかどうかを示すために、従来の D B I ベクトルに加えてグローバル D B I (D B I G) ビットが用いられる。グローバル D B I 制御を設けることで制御の程度が高まり、電力節約及び / 又は雑音特性が D B I ベクトルによって低下する事がない。10

#### 【0018】

幾つかの実施形態においては、グローバル D B I ビットはデータタイムスロットの範囲内で通信されてよいが、他の実施形態においては、グローバル D B I ビットはサイドバンド信号を用いて（即ちデータ転送のビットの外側で）通信されてよい。20

#### 【0019】

図 2 ~ 5 を参照すると、サイドバンド信号を用いてグローバル D B I 制御ビットを通信するための第 1 のトポロジーが示されている。図 2 の実施形態においては、外部メモリ 105 は 8 ビットデータバスを有しており且つデータ転送は 8 つのデータタイムスロット、1 つの D B I 制御タイムスロット及び 1 つのサイクル冗長性チェック (cyclic redundancy check) (C R C) タイムスロットを用いて実装されることが仮定されている。また、ビット値の「1」は外部メモリ 105 に対する低電力状態であることが仮定されている。従来的には、D Q 線 140 上のデータがいつ有効になるのかを示すために、データマスク (D M) 線 155 が書き込み動作の間に用いられる。あるデータスロットに対して D M ビットが有効化されると、当該データは無視される。D M 線 135 は読み出し動作の間には典型的には用いられない。本実施形態に従うと、書き込み動作に対しては図 3 に示されるように、また読み出し動作に対しては図 4 又は 5 に示されるように、D B I 信号伝達情報を通信するために D M 線 135 が双方向で用いられる。30

#### 【0020】

図 3 の書き込み動作に示されるように、データタイムスロット 0 ~ 7 は従来どおりに実装され、ここで D M ビットは書き込まれつつあるバイトを選択的にマスクするために用いられる。タイムスロット 8 の間、D Q 線 140 上で D B I ベクトル 145 が通信され、先行するデータスロットにおけるバイトが既に反転されていたかどうかを示す。グローバル D B I (D B I G) ビット 150 は D M 線 135 を用いて通信される。従って、D B I G ビット 150 が有効化されていると、外部メモリ 105 には D B I ベクトル 145 それ自身が既に反転されている旨の信号伝達がなされる。D B I G ビット 150 の有効化に応答して、外部メモリ 105 内の制御器は、D B I ベクトル 145 を反転させて、次いで反転された値を用いてデータタイムスロット内のバイトを処理する。40

#### 【0021】

図 4 の読み出し動作に示されるように、データ転送スロット 0 ~ 7 は従来どおりに実装され、また D M ビットは用いられない（即ち低電力状態の「1」で保持される）。タイムスロット 8 の間、D Q 線 140 上で D B I ベクトル 145 が通信され、先行するデータタイムスロットにおけるバイトが既に反転されているかどうかを示す。グローバル D B I (D B I G) ビット 150 は、D B I タイムスロット 8 の間、D M 線 135 を用いて通信さ50

れる。従って、D B I G ピット 150 が有効化されていると、メモリ制御器 125 には D B I ベクトル 145 それ自身が既に反転されている旨の信号伝達がなされる。D B I G ピット 150 の有効化に応答して、メモリ制御器 125 は、D B I ベクトル 145 を反転させて、次いで反転された値を用いてデータタイムスロット内のバイトを処理する。

#### 【0022】

図 5 は読み出し動作の代替的な実施形態を示しており、ここではデータタイムスロット 0 ~ 7 は従来どおりに実装されるが、D B I ベクトル 145 を通信するために D M 線 135 が用いられる。C R C データはデータスロット 8 において送られ、また D B I G ピット 150 は D M 線 135 を用いて通信される。

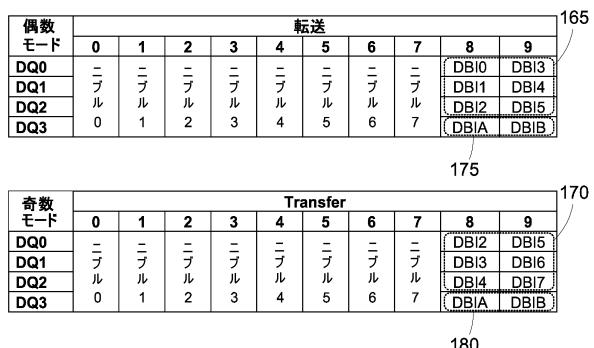

#### 【0023】

次に図 6 及び 7 を参照すると、グローバル D B I 情報を通信するためにサイドバンド信号が利用可能ではない別の実施形態が示されている。図 6 に示されるように、外部メモリ 105 は、8 ビット配置にグループ化される 2 つの 4 ビット D D R メモリ 155, 160 のバンクを含んでいてよい。モードレジスタの使用を通じて、メモリ 155 は偶数バンクとして指定され、またメモリ 160 は奇数バンクとして指定される。偶数バンク 155 の D Q 線 140 及び奇数バンク 160 の D Q 線は、バンクによって交互配置される。この交互配置パターンは、追加的なバンクに対して繰り返す。4 ビット実装においては、データマスク線は典型的にはメモリ 155, 160 にとって利用可能ではないので、グローバル D B I 信号を送るためのサイドバンドピンは無い。図 7 に示されるように、グローバル D B I の使用を可能にするために、D B I が実装されるデータスロットの数が減少させられ、そしてグローバル D B I ピット 150 は、減少させられた D B I ベクトル 165, 170 と共に D Q 線 140 を介して各メモリ 155, 160 へ送られる。

#### 【0024】

データスロット 0 ~ 7 において通信されるニブル（それぞれの 4 ビット）(nibbles) は従来どおりである。しかし、8 つのデータタイムスロットに対応する 8 ビットを有する D B I ベクトルを提供するのではなく、各 D B I ベクトル 165, 170 は 6 つのタイムスロットのみをカバーする。図示される実施形態においては、偶数モードメモリ 155 のための D B I ベクトル 165 はデータスロット 0 ~ 5 に対する D B I を実装し、また奇数モードメモリはデータスロット 2 ~ 7 に対する D B I を実装する。偶数モードメモリ 155 に対するタイムスロット 6 及び 7 におけるニブル並びに奇数モードメモリ 160 に対するタイムスロット 0 及び 1 におけるニブルは反転されない。D B I ベクトル 165, 170 は制御タイムスロット 8 及び 9 を介して通信される。D B I ベクトル 165, 170 のタイムスロット 8 部分が既に反転されているかどうかを示す D B I A ピット及び D B I ベクトル 165, 170 のタイムスロット 9 部分が既に反転されているかどうかを示す D B I B ピットを伴い、グローバル D B I ベクトル 175, 180 もまた制御タイムスロット 8 及び 9 において送られる。

#### 【0025】

この手法を用いることで、ビット転送スロット 7 及び 8 の間とスロット 8 及び 9 の間で 8 ビットを介した最大で 8 つの S S O が回避され得る。しかし、一対のうちの一方のニブルだけが D B I によってカバーされる 4 つのスロットがあるので、D C 電力節約の低減は僅かである。一対における両バンク 155, 160 を介しての S S O 低減は、各バンク個別の S S O 特性よりも良好である。単一のバンクに対する S S O 特性は最悪の場合に 4 であろう一方で、2 つの隣接したバンクを介しては S S O は最大で 6 に制限される。

#### 【0026】

ここに説明される D B I 信号伝達技術は、最小の S S O を伴う D B I を可能にする。グローバル D B I ピット 150 を搬送するサイドバンド信号を有する × 8 / × 16 デバイスに対して、S S O は 4 未満である。サイドバンド信号を伴わない × 4 デバイスに対して、S S O は 8 ビットを介して最大で 6 である。電力消費を低減することにより、冷却要求が低減されると共にバッテリ寿命が延びる可能性がある。S S O を低減することにより雑音特性が改善され、それによりメモリバスが動作する最大周波数が増大する可能性が生じ得

10

20

30

40

50

る。

**【 0 0 2 7 】**

開示される主題は、ここで教示の利益を享受する当業者には明らかな、異なるが均等な方法において修正されてよく且つ実施されてよく、従って上に開示される特定の実施形態は例示のみを目的としている。また、ここに示される構成又は設計の詳細に対しては、特許請求の範囲に記述される以外は、限定は意図されていない。従って、上に開示される特定の実施形態は変更又は修正されてよく、また全てのそのような変形は開示される主題の範囲及び精神内にあるとみなされることは明らかである。よって、ここに求められる保護は特許請求の範囲に記述されている。

**【 0 0 2 8 】**

本主題の1つの実施形態に従う装置は、データを通信するためのデータバスを定義する複数のデータ線を含む。制御器は、複数のデータタイムスロットを用いてデータバスを介して複数のデータ転送を通信するように動作し、データタイムスロットの少なくともサブセットに対して、制御器は、関連データタイムスロットの間に通信されるビットが反転されている旨を示す関連データバス反転標識を通信するように動作し、データ転送のサブセットに対するデータバス反転標識は、データバス反転ベクトルへとグループ化され、制御器は、データバス反転ベクトルの反転を示すグローバルデータバス反転標識を通信するように動作する。

**【 0 0 2 9 】**

装置は信号線を更に含んでいてよく、また制御器は信号線を介してグローバルデータバス反転標識を通信するように動作してよい。

**【 0 0 3 0 】**

信号線はデータマスク線であってよい。

**【 0 0 3 1 】**

データバス反転ベクトルは、複数のデータタイムスロット以外の制御タイムスロットにおいてデータ線を介して通信されてよく、また制御器は、書き込み動作の間のデータ転送に対してデータマスク線を介してデータマスク情報を通信すると共に制御タイムスロットの間にデータマスク線を介してグローバルデータバス反転標識を通信するように動作してよい。

**【 0 0 3 2 】**

制御器は、制御タイムスロットの間にデータマスク線を介してグローバルデータバス反転標識を通信するように動作してよい。

**【 0 0 3 3 】**

データバス反転ベクトルは、複数のデータタイムスロット以外の制御タイムスロットにおいてデータ線を介して通信されてよく、また制御器は、制御タイムスロットの間にデータマスク線を介してグローバルデータバス反転標識を通信するように動作してよい。

**【 0 0 3 4 】**

データバス反転ベクトルは、複数のデータタイムスロット以外の制御タイムスロットにおいてデータ線を介して通信されてよい。

**【 0 0 3 5 】**

グローバルデータバス反転標識は、制御タイムスロットの間にデータ線を介して通信されてよい。

**【 0 0 3 6 】**

データ線は、第1のグループ及び第2のグループへとグループ化されてよい。データバス反転ベクトルは、第1のグループに関連付けられる第1の部分及び第2のグループに関連付けられる第2の部分を有していてよい。第1の部分はデータタイムスロットの第1のサブセットをカバーし、第2の部分はタイムスロットの第2のサブセットをカバーし、そして第1のサブセットに含まれないデータタイムスロットは、第2のサブセットに含まれないデータタイムスロットと重複しない。

**【 0 0 3 7 】**

10

20

30

40

50

第 1 のグループは第 1 のメモリに関連付けられてよく、また第 2 のグループは第 2 のメモリに関連付けられてよい。制御器はメモリ制御器であってよい。制御器はメモリデバイスへと集積化されてよい。

【 0 0 3 8 】

装置はプロセッサ及びメモリを含んでいてよい。複数のデータ線はプロセッサをメモリに接続してよい。

【 0 0 3 9 】

データバスはアドレスバスであってよい。

【 0 0 4 0 】

本主題の別の実施形態に従う方法は、複数のデータタイムスロットを用いデータバスを定義する複数のデータ線を介して複数のデータ転送を通信することと、データタイムスロットの少なくともサブセットに対するデータバス反転標識であって関連データタイムスロットの間に通信されるビットが反転されている旨を示すデータバス反転標識を通信することと、データバス反転ベクトルの反転を示すグローバルデータバス反転標識を通信することと、を含んでいてよく、データ転送のサブセットに対するデータバス反転標識は、データバス反転ベクトルへとグループ化される。10

【 0 0 4 1 】

グローバルデータバス反転標識を通信することは、データ線の少なくとも 1 つを用いてグローバルデータバス反転標識を通信することを含んでいてよい。

【 0 0 4 2 】

データバス反転ベクトルはデータタイムスロットの総数未満をカバーしてよく、またグローバルデータバス反転標識は少なくとも 1 つの制御タイムスロットの間にデータバス反転ベクトルと共に通信されてよい。20

【 0 0 4 3 】

グローバルデータバス反転標識を通信することは、データ線以外のデータバスに関連する信号線を用いてグローバルデータバス反転標識を通信することを含んでいてよい。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 グレン エイ. デアース

アメリカ合衆国、01450 マサチューセッツ州、グロットン、スクアナコック ドライブ 2

0

(72)発明者 シュウェトル エイ. パテル

アメリカ合衆国、95135 カリフォルニア州、サンノゼ、ジャスミン サークル 3677

審査官 松永 稔

(56)参考文献 特開2004-310700(JP,A)

特開2011-187153(JP,A)

米国特許出願公開第2010/0057971(US,A1)

米国特許出願公開第2009/0182918(US,A1)

米国特許出願公開第2005/0132112(US,A1)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00 - G06F 12/06

G06F 13/16

G06F 13/42

G06F 3/00

G11C 11/409 - G11C 11/4096