(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7504625号**

**(P7504625)**

(45)発行日 令和6年6月24日(2024.6.24)

(24)登録日 令和6年6月14日(2024.6.14)

(51)国際特許分類

F I

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 4 N | 25/78 (2023.01)  | H 0 4 N | 25/78  |

| H 0 4 N | 25/585 (2023.01) | H 0 4 N | 25/585 |

| H 0 4 N | 25/771 (2023.01) | H 0 4 N | 25/771 |

| H 0 4 N | 25/76 (2023.01)  | H 0 4 N | 25/76  |

請求項の数 39 (全36頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2020-33819(P2020-33819)   |

| (22)出願日  | 令和2年2月28日(2020.2.28)        |

| (65)公開番号 | 特開2021-136667(P2021-136667) |

| A)       |                             |

| (43)公開日  | 令和3年9月13日(2021.9.13)        |

| 審査請求日    | 令和5年2月20日(2023.2.20)        |

|          |                                            |

|----------|--------------------------------------------|

| (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74)代理人  | 100126240<br>弁理士 阿部 琢磨                     |

| (74)代理人  | 100223941<br>弁理士 高橋 佳子                     |

| (74)代理人  | 100159695<br>弁理士 中辻 七郎                     |

| (74)代理人  | 100172476<br>弁理士 富田 一史                     |

| (74)代理人  | 100126974<br>弁理士 大朋 靖尚                     |

| (72)発明者  | 中村 恒一<br>東京都大田区下丸子3丁目30番2号                 |

最終頁に続く

(54)【発明の名称】 光電変換装置

**(57)【特許請求の範囲】****【請求項1】**

第一の光電変換部、第二の光電変換部、フローティングディフュージョン部、並びに前記第一の光電変換部及び第二の光電変換部以外の場所で信号電荷を蓄積する容量素子を有する画素と、

前記第一の光電変換部で生じた信号電荷に基づく信号及び前記第二の光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、

電荷蓄積期間中、前記第一の光電変換部に蓄積される第一の信号電荷に基づく第一の信号と、

前記電荷蓄積期間中、前記第二の光電変換部に蓄積される第二の信号電荷に基づく第二の信号と、

前記第二の光電変換部で生じ、前記電荷蓄積期間中は前記容量素子に蓄積される第三の信号電荷に基づく第三の信号と、を読み出し、

前記第一の信号または前記第二の信号に対して行われるアナログデジタル変換の変換期間の長さと、前記第三の信号に対して行われるアナログデジタル変換の変換期間の長さと、が異なることを特徴とする光電変換装置。

**【請求項2】**

第一の光電変換部、第二の光電変換部、フローティングディフュージョン部、並びに前記第一の光電変換部及び第二の光電変換部以外の場所で信号電荷を蓄積する容量素子を有

する画素と、

前記第一の光電変換部で生じた信号電荷に基づく信号及び前記第二の光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、

電荷蓄積期間中、前記第一の光電変換部に蓄積される第一の信号電荷に基づく第一の信号と、

前記電荷蓄積期間中、前記第二の光電変換部に蓄積される第二の信号電荷に基づく第二の信号と、

前記第二の光電変換部で生じ、前記電荷蓄積期間中は前記容量素子に蓄積される第三の信号電荷に基づく第三の信号と、を読み出し、

前記第一の信号または前記第二の信号に対して行われるアナログデジタル変換の分解能と、前記第三の信号に対して行われるアナログデジタル変換の分解能と、が異なることを特徴とする光電変換装置。

#### 【請求項 3】

マイクロレンズを有し、前記画素において前記第一の光電変換部と前記第二の光電変換部とは同一のマイクロレンズの下に配置されることを特徴とする請求項 1 又は請求項 2 のいずれか一項に記載の光電変換装置。

#### 【請求項 4】

前記画素は、前記信号を出力する出力部を備え、前記容量素子はトランジスタによって前記出力部の入力ノードと電気的に接続されることを特徴とする請求項 1 乃至請求項 3 のいずれか一項に記載の光電変換装置。

10

#### 【請求項 5】

前記第一の信号及び前記第二の信号は、それぞれ、前記出力部の前記入力ノードが前記容量素子と接続されていない状態で出力され、

前記第三の信号電荷は、前記出力部の入力ノードと前記容量素子とが接続された状態で出力されることを特徴とする請求項 4 に記載の光電変換装置。

#### 【請求項 6】

前記第一の光電変換部の感度が、前記第二の光電変換部の感度と異なることを特徴とする、請求項 1 乃至請求項 5 のいずれか一項に記載の光電変換装置。

#### 【請求項 7】

前記第一の光電変換部の受光面の面積は、前記第二の光電変換部の受光面の面積と異なることを特徴とする請求項 1 乃至請求項 6 のいずれか一項に記載の光電変換装置。

30

#### 【請求項 8】

前記第一の光電変換部上に存在する第一のフィルターと、前記第二の光電変換部上に存在する第二のフィルターとを備え、

前記第一のフィルターの光透過率は、前記第二のフィルターの光透過率と異なることを特徴とする請求項 1 乃至請求項 7 のいずれか一項に記載の光電変換装置。

#### 【請求項 9】

前記第一の光電変換部の感度は前記第二の光電変換部の感度よりも高いことを特徴とする請求項 1 乃至請求項 8 のいずれか一項に記載の光電変換装置。

#### 【請求項 10】

前記第一の光電変換部の受光面の面積は、前記第二の光電変換部の受光面の面積よりも大きいことを特徴とする請求項 1 乃至請求項 9 のいずれか一項に記載の光電変換装置。

#### 【請求項 11】

前記第一の信号に対して行われる第一のアナログデジタル変換の変換期間が、前記第二の信号に対して行われる第二のアナログデジタル変換の変換期間よりも長いことを特徴とする、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

#### 【請求項 12】

前記第一の信号に対して行われる第一のアナログデジタル変換の変換期間が、前記第二の信号に対して行われる第二のアナログデジタル変換の変換期間よりも短いことを特徴と

40

50

する、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

【請求項 13】

前記第一の信号に対して行われる第一のアナログデジタル変換の変換期間が、前記第三の信号に対して行われる第三のアナログデジタル変換の変換期間よりも長いことを特徴とする、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

【請求項 14】

前記第一の信号に対して行われる第一のアナログデジタル変換の変換期間が、前記第三の信号に対して行われる第三のアナログデジタル変換の変換期間よりも短いことを特徴とする、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

【請求項 15】

前記第二の信号に対して行われる第二のアナログデジタル変換の変換期間が、前記第三の信号に対して行われる第三のアナログデジタル変換の変換期間よりも長いことを特徴とする、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

【請求項 16】

前記第二の信号に対して行われる第二のアナログデジタル変換の変換期間が、前記第三の信号に対して行われる第三のアナログデジタル変換の変換期間よりも短いことを特徴とする、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

【請求項 17】

前記第一の信号をデジタルデータに変換する第一の分解能と、前記第二の信号をデジタルデータに変換する第二の分解能とが異なることを特徴とする、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

【請求項 18】

前記第一の信号をデジタルデータに変換する第一の分解能と、前記第三の信号をデジタルデータに変換する第三の分解能とが異なることを特徴とする、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

【請求項 19】

前記第二の信号をデジタルデータに変換する第二の分解能と、前記第三の信号をデジタルデータに変換する第三の分解能とが異なることを特徴とする、請求項 6 乃至請求項 10 のいずれか一項に記載の光電変換装置。

【請求項 20】

前記アナログデジタル変換部は、参照信号を出力する参照信号源と、前記信号と前記参照信号とを比較する比較器とを備え、

前記参照信号の掃引を開始してから前記信号と前記参照信号との大小関係が反転するまでの時間に応じたデジタルデータを取得することを特徴とする請求項 1 乃至請求項 19 のいずれか一項に記載の光電変換装置。

【請求項 21】

前記参照信号の振幅の一端から他端まで掃引するのに要する時間が、アナログデジタル変換の変換期間の長さであることを特徴とする請求項 20 記載の光電変換装置。

【請求項 22】

前記アナログデジタル変換部はカウンタを有し、

前記カウンタがカウントを開始してから終了するまでに要する時間が、アナログデジタル変換の変換期間の長さであることを特徴とする請求項 20 記載の光電変換装置。

【請求項 23】

アナログデジタル変換における逐次比較の回数が異なることで、アナログデジタル変換の変換期間の長さが異なることを特徴とする請求項 1 乃至請求項 19 のいずれか一項に記載の光電変換装置。

【請求項 24】

前記アナログデジタル変換部は、参照信号を出力する参照信号源と、前記信号と前記参照信号とを比較する比較器とを備え、

前記第一のアナログデジタル変換に用いられる参照信号に対してオフセットを付与した

10

20

30

40

50

信号を、前記第二のアナログデジタル変換に用いられる参照信号とすることを特徴とする請求項 1 1 記載の光電変換装置。

**【請求項 2 5】**

前記第一の信号、前記第二の信号、及び、前記第三の信号を増幅する増幅回路を備える光電変換装置であって、

前記第一の信号、前記第二の信号、及び、前記第三の信号のうち、少なくとも二つの信号に対して互いに異なる増幅ゲインを適用することを特徴とする請求項 1 乃至請求項 2 4 のいずれか一項に記載の光電変換装置。

**【請求項 2 6】**

光電変換部と、フローティングディフュージョン部と、容量素子と、前記光電変換部で生じた信号電荷を受ける入力ノードを有し、前記信号電荷に基づく信号を出力する出力部とを有する画素と、

前記信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、

前記容量素子は、トランジスタを介して前記入力ノードと電気的に接続されることにより前記入力ノードの容量の一部を構成し、

前記容量素子と前記入力ノードとが電気的に接続されている場合に前記出力部から出力される第一の信号と、前記容量素子と前記入力ノードとが電気的に接続されていない場合に前記出力部から出力される第二の信号と、に対して行われるアナログデジタル変換の変換期間の長さが互いに異なることを特徴とする光電変換装置。

**【請求項 2 7】**

光電変換部と、フローティングディフュージョン部と、容量素子と、前記光電変換部で生じた信号電荷を受ける入力ノードを有し、前記信号電荷に基づく信号を出力する出力部とを有する画素と、

前記信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、

前記容量素子は、トランジスタを介して前記入力ノードと電気的に接続されることにより前記入力ノードの容量の一部を構成し、

前記容量素子と前記入力ノードとが電気的に接続されている場合に前記出力部から出力される第一の信号と、前記容量素子と前記入力ノードとが電気的に接続されていない場合に前記出力部から出力される第二の信号と、に対して行われるアナログデジタル変換の分解能が互いに異なることを特徴とする光電変換装置。

**【請求項 2 8】**

前記画素はセレクトスイッチを含み、前記セレクトスイッチがオン状態の期間において、前記容量素子と前記入力ノードとが電気的に接続されている場合と、前記容量素子と前記入力ノードとが電気的に接続されていない場合と、が切り替わることを特徴とする請求項 2 6 又は請求項 2 7 のいずれか一項に記載の光電変換装置。

**【請求項 2 9】**

複数の前記画素は複数行に配され、前記複数行のうちの 1 行の読み出し期間において、前記容量素子と前記入力ノードとが電気的に接続されている場合と、前記容量素子と前記入力ノードとが電気的に接続されていない場合と、が切り替わることを特徴とする請求項 2 6 乃至請求項 2 8 のいずれか一項に記載の光電変換装置。

**【請求項 3 0】**

光電変換部と、フローティングディフュージョン部とを有する画素と、前記光電変換部で生じた信号電荷を前記光電変換部以外の場所で蓄積する容量素子と、前記光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、

電荷蓄積期間中、前記光電変換部に蓄積される第一の信号電荷に基づく第一の信号と、前記電荷蓄積期間中は前記容量素子に蓄積される第二の信号電荷に基づく第二の信号と、を読み出し、

10

20

30

40

50

前記第一の信号、前記第二の信号に対して行われるアナログデジタル変換の変換期間の長さが互いに異なることを特徴とする光電変換装置。

**【請求項 3 1】**

光電変換部と、フローティングディフュージョン部とを有する画素と、前記光電変換部で生じた信号電荷を前記光電変換部以外の場所で蓄積する容量素子と、前記光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、

電荷蓄積期間中、前記光電変換部に蓄積される第一の信号電荷に基づく第一の信号と、前記電荷蓄積期間中は前記容量素子に蓄積される第二の信号電荷に基づく第二の信号と、を読み出し、

前記第一の信号、前記第二の信号に対して行われるアナログデジタル変換の分解能が互いに異なることを特徴とする光電変換装置。

**【請求項 3 2】**

前記画素を複数備えることを特徴とする請求項 1 乃至 2 8 のいずれか一項に記載の光電変換装置。

**【請求項 3 3】**

前記光電変換装置は複数の半導体基板を積層して構成されることを特徴とする請求項 1 乃至 請求項 3 2 のいずれか一項に記載の光電変換装置。

**【請求項 3 4】**

前記第一の信号と減算処理を行うための第一のリセット信号、前記第二の信号と減算処理を行うための第二のリセット信号、及び、前記第三の信号と減算処理を行うための第三のリセット信号を出力することを特徴とする請求項 1 乃至 請求項 2 5 のいずれか一項に記載の光電変換装置。

**【請求項 3 5】**

前記第一の信号、前記第二の信号、及び、前記第三の信号と、前記第一のリセット信号、前記第二のリセット信号、及び、前記第三のリセット信号とが、前記第二のリセット信号、前記第二の信号、前記第三の信号、前記第三のリセット信号、前記第一のリセット信号、前記第一の信号、の順に読み出されることを特徴とした請求項 3 4 記載の光電変換装置。

**【請求項 3 6】**

請求項 1 乃至 2 5 のいずれか一項に記載の光電変換装置と、

前記光電変換装置から出力された信号に対して処理を行う処理装置と、

を有することを特徴とする撮像システム。

**【請求項 3 7】**

前記処理装置は、前記第一の信号に基づいて生成された第一のデジタル信号、前記第二の信号に基づいて生成された第二のデジタル信号、前記第三の信号に基づいて生成された第三のデジタル信号からいずれか 1 つのデジタル信号を選択して画像を形成することを特徴とする請求項 3 6 記載の撮像システム。

**【請求項 3 8】**

移動体であって、

請求項 1 乃至 2 5 のいずれか一項に記載の光電変換装置と、

前記光電変換装置から出力された信号に対して処理を行う処理装置と、

前記処理の結果に基づいて前記移動体を制御する制御手段と、を有することを特徴とする移動体。

**【請求項 3 9】**

前記処理装置は、前記第一の信号に基づいて生成された第一のデジタル信号、前記第二の信号に基づいて生成された第二のデジタル信号、前記第三の信号に基づいて生成された第三のデジタル信号からいずれか 1 つのデジタル信号を選択して画像を形成することを特徴とする請求項 3 8 記載の移動体。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、光電変換装置に関する。

**【背景技術】****【0002】**

近年、ダイナミックレンジの広い光電変換装置が求められている。ダイナミックレンジを拡大する手段として、非特許文献1には、画素内に受光面積の大きいフォトダイオードと、受光面積の小さいフォトダイオードと、オーバーフロー用の容量を配置した画素を備えた撮像装置が開示されている。非特許文献1に記載の撮像装置は、3つの信号を読み出すことで、ダイナミックレンジの拡大を実現している。まず、受光面積の大きいフォトダイオードで光電変換された電荷を、フローティングディフェュージョン（以降、FDとよぶ）容量で電圧変換した信号と、受光面積の小さいフォトダイオードで光電変換された電荷をFD容量で電圧変換した信号と、が読み出される。撮像装置は、さらに、受光面積の小さいフォトダイオードで光電変換され、オーバーフローした電荷をFD容量とオーバーフロー用容量の合成容量で電圧変換した信号を読み出す。10

**【先行技術文献】****【非特許文献】****【0003】**

【文献】Manuel Innocent, et al. "Pixel with nested photo diodes and 120 dB single exposure dynamic range" IISW Dig. Tech. Papers, pp. 13, June 2019.20

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

非特許文献1に記載の撮像装置では、受光面積の大きいフォトダイオードの信号と、受光面積の小さいフォトダイオードの信号と、オーバーフロー用の容量に蓄積された信号のそれぞれを順次読み出している。非特許文献1には、3つの信号に対してアナログデジタル変換（以降AD変換）を行うことについて開示はなく、また、どのようにAD変換を行うかについて開示も示唆もない。30

**【0005】**

これらの信号は扱う信号範囲と扱う輝度範囲が異なる。各信号の信号値の取りうる範囲は、撮像装置の回路構成あるいは素子構成に応じて決まり、典型的には共通である。しかし、この信号値の取りうる範囲のうちどの部分が実際に画像データに用いられるかは、各信号が扱う輝度範囲の設定に応じて変わる。例えば3つの信号の1つについては、取りうる信号値の範囲のうち一部だけが画像データに用いられることがある。そのため、これらの3つの信号に対して同一のAD変換を行うと、信号によっては冗長な動作が存在する可能性がある。冗長な動作を省略したり、あるいは、別の動作に置換したりすることで、例えばAD変換期間の短縮やAD変換の分解能の最適化など、AD変換性能を向上させる余地がある。40

**【0006】**

本発明は上記課題を鑑みてなされたものであり、AD変換性能を向上させることを目的とする。

**【課題を解決するための手段】****【0007】**

本発明の一つの側面は、光電変換装置であって、第一の光電変換部、第二の光電変換部、フローティングディフェュージョン部、並びに前記第一の光電変換部及び第二の光電変換部以外の場所で信号電荷を蓄積する容量素子を有する画素と、前記第一の光電変換部で生じた信号電荷に基づく信号及び前記第二の光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって50

、電荷蓄積期間中、前記第一の光電変換部に蓄積される第一の信号電荷に基づく第一の信号と、前記電荷蓄積期間中、前記第二の光電変換部に蓄積される第二の信号電荷に基づく第二の信号と、前記第二の光電変換部で生じ、前記電荷蓄積期間中は前記容量素子に蓄積される第三の信号電荷に基づく第三の信号と、を読み出し、前記第一の信号または前記第二の信号に対して行われるアナログデジタル変換の変換期間の長さと、前記第三の信号に対して行われるアナログデジタル変換の変換期間の長さと、が異なる。

#### 【 0 0 0 8 】

本発明の別の側面に係る実施例の光電変換装置は、第一の光電変換部、第二の光電変換部、フローティングディフュージョン部、並びに前記第一の光電変換部及び第二の光電変換部以外の場所で信号電荷を蓄積する容量素子を有する画素と、前記第一の光電変換部で生じた信号電荷に基づく信号及び前記第二の光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、電荷蓄積期間中、前記第一の光電変換部に蓄積される第一の信号電荷に基づく第一の信号と、前記電荷蓄積期間中、前記第二の光電変換部に蓄積される第二の信号電荷に基づく第二の信号と、前記第二の光電変換部で生じ、前記電荷蓄積期間中は前記容量素子に蓄積される第三の信号電荷に基づく第三の信号と、を読み出し、前記第一の信号または前記第二の信号に対して行われるアナログデジタル変換の分解能と、前記第三の信号に対して行われるアナログデジタル変換の分解能と、が異なる。

#### 【 0 0 0 9 】

本発明の別の側面に係る実施例の光電変換装置は、光電変換部と、フローティングディフュージョン部と、容量素子と、前記光電変換部で生じた信号電荷を受ける入力ノードを有し、前記信号電荷に基づく信号を出力する出力部とを有する画素と、前記信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、前記容量素子は、トランジスタを介して前記入力ノードと電気的に接続されることにより前記入力ノードの容量の一部を構成し、前記容量素子と前記入力ノードとが電気的に接続されている場合に前記出力部から出力される第一の信号と、前記容量素子と前記入力ノードとが電気的に接続されていない場合に前記出力部から出力される第二の信号と、に対して行われるアナログデジタル変換の変換期間の長さが互いに異なる。

#### 【 0 0 1 0 】

本発明の別の側面に係る実施例の光電変換装置は、光電変換部と、フローティングディフュージョン部と、容量素子と、前記光電変換部で生じた信号電荷を受ける入力ノードを有し、前記信号電荷に基づく信号を出力する出力部を有する画素と、前記信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、前記容量素子は、トランジスタを介して前記入力ノードと電気的に接続されることにより前記入力ノードの容量の一部を構成し、前記容量素子と前記入力ノードとが電気的に接続されている場合に前記出力部から出力される第一の信号と、前記容量素子と前記入力ノードとが電気的に接続されていない場合に前記出力部から出力される第二の信号と、に対して行われるアナログデジタル変換の分解能が互いに異なる。

#### 【 0 0 1 1 】

本発明の別の側面に係る実施例の光電変換装置は、光電変換部と、フローティングディフュージョン部とを有する画素と、前記光電変換部で生じた信号電荷を前記光電変換部以外の場所で蓄積する容量素子と、前記光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、電荷蓄積期間中、前記光電変換部に蓄積される第一の信号電荷に基づく第一の信号と、前記電荷蓄積期間中は前記容量素子に蓄積される第二の信号電荷に基づく第二の信号と、を読み出し、前記第一の信号、前記第二の信号に対して行われるアナログデジタル変換の変換期間の長さが互いに異なる。

#### 【 0 0 1 2 】

本発明の別の側面に係る実施例の光電変換装置は、光電変換部と、フローティングディフュージョン部とを有する画素と、前記光電変換部で生じた信号電荷を前記光電変換部以

10

20

30

40

50

外の場所で蓄積する容量素子と、前記光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、電荷蓄積期間中、前記光電変換部に蓄積される第一の信号電荷に基づく第一の信号と、前記電荷蓄積期間中は前記容量素子に蓄積される第二の信号電荷に基づく第二の信号と、を読み出し、前記第一の信号、前記第二の信号に対して行われるアナログデジタル変換の分解能が互いに異なる。

#### 【0013】

本発明の別の側面に係る実施例の光電変換装置は、光電変換部を有する画素と、前記光電変換部で生じた信号電荷に基づく信号をアナログデジタル変換するためのアナログデジタル変換部と、を含む光電変換装置であって、前記アナログデジタル変換部は、アナログデジタル変換のための参照信号と前記信号とを比較する比較器とを備え、前記参照信号の取りうる第一の電位範囲が、前記参照信号と比較される前記信号が取りうる第二の電位範囲よりも狭い。

10

#### 【発明の効果】

#### 【0014】

本発明によれば、A/D変換性能を向上させることができる。

#### 【図面の簡単な説明】

#### 【0015】

【図1】実施例にかかる光電変換装置の概略図である。

【図2】実施例にかかる光電変換装置の画素回路の構成例である。

20

【図3】実施例にかかる光電変換装置の平面構造を模式的に示す図面である。

【図4】実施例にかかる光電変換装置の画素回路の動作を説明するタイミングチャートである。

【図5】実施例にかかる光電変換装置のA/D変換の方式を説明する図面である。

【図6】実施例にかかる光電変換装置のランプ源の(a)構成例、(b)動作を説明するタイミングチャートである。

【図7】実施例にかかる光電変換装置における各信号の輝度と信号振幅の関係を説明する図面である。

【図8】実施例にかかる光電変換装置における各信号の輝度とデジタルデータの関係を説明する図面である。

30

【図9】実施例にかかる光電変換装置における各信号の輝度と信号振幅の関係を説明する図面である。

【図10】実施例にかかる光電変換装置のA/D変換部の動作を説明するタイミングチャートである。

【図11】実施例にかかる光電変換装置における各信号の輝度と信号振幅の関係を説明する図面である。

【図12】実施例にかかる光電変換装置のA/D変換部の動作を説明するタイミングチャートである。

【図13】実施例にかかる光電変換装置における各信号の輝度と信号振幅の関係を説明する図面である。

【図14】実施例にかかる光電変換装置のA/D変換部の動作を説明するタイミングチャートである。

40

【図15】実施例にかかる光電変換装置における各信号の輝度と信号振幅の関係を説明する図面である。

【図16】実施例にかかる光電変換装置のA/D変換部の動作を説明するタイミングチャートである。

【図17】実施例にかかる光電変換装置のA/D変換部の動作を説明するタイミングチャートである。

【図18】実施例にかかる光電変換装置の概略図である。

【図19】実施例にかかる光電変換装置のA/D変換部の動作を説明するタイミングチャートである。

50

トである。

【図20】実施例にかかる光電変換装置のA D変換部の動作を説明するタイミングチャートである。

【図21】積層構成の光電変換装置の概略図である。

【図22】撮像システムの実施例のブロック図である。

【図23】移動体の実施例のブロック図である。

【発明を実施するための形態】

【0016】

(実施例1)

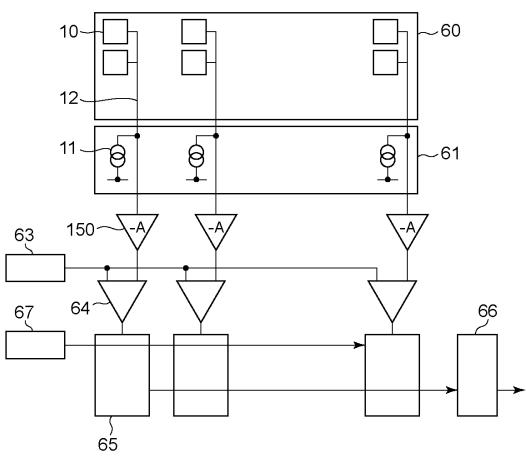

本実施例を実施するための形態の一例について図面を用いて説明する。図1は本実施例にかかる光電変換装置の構成を示す概略図である。本実施例の光電変換装置は、撮像装置、測距センサ、赤外線センサ、放射線センサ、その他の光検知センサに適用される。

【0017】

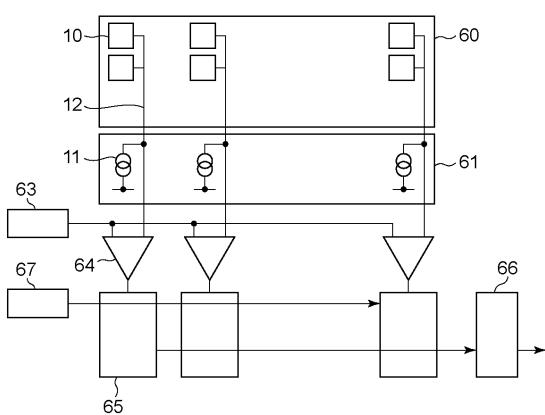

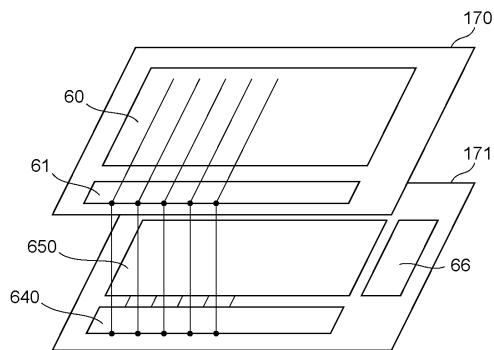

図1の光電変換装置は、マトリクス上に配置された画素回路10からなる画素部60、電流源11からなる電流源群61、列ごとの比較回路64、ランプ源63、列ごとの列メモリ65、カウンタ回路66、演算処理部67を含む。

【0018】

画素回路10は、入射光を信号に変換し、入射光に基づく信号を出力する。電流源11は後述のソースフォロワトランジスタに電流を供給し、当該ソースフォロワトランジスタとともにソースフォロワ回路を構成する。ソースフォロワ回路を出力部として、画素回路10から読み出された信号は垂直出力線12に出力される。

【0019】

比較回路64、ランプ源63、および、カウンタ回路66が、画素回路10から出力された信号に対してアナログデジタル変換(以降A D変換)を行うアナログデジタル変換部の一例である。比較回路64の2つの入力には、垂直出力線12とランプ源63の出力とがそれぞれ接続される。ランプ源63は、ランプ信号などのA D変換に用いられる参照信号を出力する参照信号源の一例である。比較回路64は垂直出力線12の電位とランプ源63の出力電位とを比較する比較器であり、電位の大小関係が反転すると、比較回路64の出力には列メモリ65が接続される。列メモリ65はさらにカウンタ回路67の出力が入力され、列メモリ65では比較回路64の出力電位が反転したときにカウンタ回路67が出力するカウント値をデジタルデータとして記憶する。A D変換が行われた後に列メモリ65に記憶されるデジタルデータは、画素回路10から出力された信号から変換されたデジタルデータである。

【0020】

列メモリ65に記憶されたデジタルデータを演算処理部67に転送し、演算処理部67で前述のC D S処理やオフセット補正の演算処理が施され、光電変換装置の外部に演算処理が施されたデータを出力する。

【0021】

なお、図1では光電変換装置の外部にデータを出力するためのトランスミッタやその他の回路は省略している。

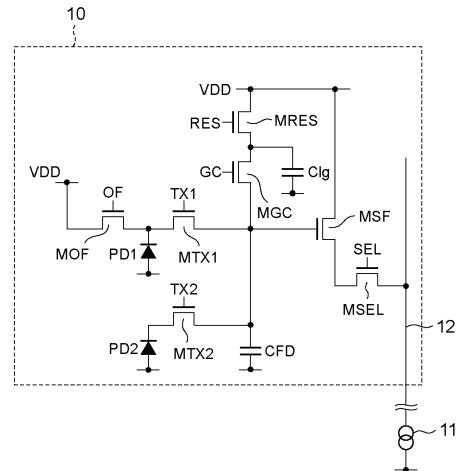

【0022】

図2は本実施例にかかる画素回路10の等価回路を示している。図2に示した画素回路10について説明する。画素回路10は第1のフォトダイオードP D 1と第2のフォトダイオードP D 2とを有する。さらに転送スイッチM T X 1およびM T X 2と、オーバーフロー用スイッチM O FとF D容量C F D、ゲインコントロールスイッチM G C、容量素子C l g、リセットスイッチM R E S、ソースフォロワトランジスタM S F、セレクトスイッチM S E Lで構成される。

【0023】

各素子の機能と接続について説明する。第1のフォトダイオードP D 1および第2のフ

10

20

30

40

50

オトダイオード P D 2 は、それぞれ、光電変換部の一例である。第 1 のフォトダイオード P D 1 と第 2 のフォトダイオード P D 2 にそれぞれ光が入射すると光電変換により電荷が発生する。第 1 のフォトダイオード P D 1 と第 2 のフォトダイオード P D 2 とのそれぞれは、発生した電荷を信号電荷として蓄積する。

#### 【 0 0 2 4 】

転送スイッチ M T X 1 のソースと第 1 のフォトダイオード P D 1 のカソードが電気的に接合され、転送スイッチ M T X 1 のドレインとソースフォロワトランジスタ M S F の入力ノード（ゲート）が電気的に接合される。転送スイッチ M T X 2 のソースと第 2 のフォトダイオード P D 2 のカソードが電気的に接合され、ソースフォロワトランジスタ M S F の入力ノードが電気的に接合されている。

10

#### 【 0 0 2 5 】

転送スイッチ M T X 1 と M T X 2 のゲートにはそれぞれ制御信号 T X 1 、 T X 2 が入力される。各制御信号が H i g h レベルのとき、ソースフォロワトランジスタ M S F の入力ノードに各フォトダイオードから信号電荷が転送される。

#### 【 0 0 2 6 】

オーバーフロー用スイッチ M O F のドレインは電源 V D D に接続される。オーバーフロー用スイッチ M O F のソースは第 1 のフォトダイオード P D 1 のカソードに接続される。オーバーフロー用スイッチ M O F のゲートには制御信号 O F が入力される。オーバーフロー用スイッチ M O F ではゲート電位に応じたポテンシャルバリアが形成される。制御信号 O F が H i g h レベルのとき、電源 V D D に第 1 のフォトダイオード P D 1 から信号電荷が転送される。制御信号 O F が中間電位 L M 1 ( L o w < L M 1 < H i g h ) のとき、電源 V D D と第 1 のフォトダイオード P D 1 の間のポテンシャルバリアが他の領域のバリアより低いレベルになることによって、電源 V D D に余剰な電荷を排出することができる。

20

#### 【 0 0 2 7 】

転送スイッチ M T X 1 と M T X 2 のドレイン、ゲインコントロールスイッチ M G C のソース、および、ソースフォロワトランジスタ M S F のゲートは、互いに接続され、1つのノードを構成している。この1つのノードを、フローティングディフュージョン（以降 F D ）ノードまたは F D 部と呼ぶことがある。図 2 において、 F D 部の持つ容量が、 F D 容量 C F D として表されている。 F D 容量 C F D は、 F D 部を構成する配線の寄生容量成分や F D 部に接続されたトランジスタのゲートの寄生容量成分を含みうる。また、 F D 容量 C F D は、 F D 部を構成する半導体領域の P N 接合容量成分、および、 F D 部に接続されたトランジスタのソースまたはドレインの P N 接合容量成分を含みうる。これらの容量成分に加えて、 F D 容量 C F D は、 P I P 容量、 M I M 容量、 M O S 容量などの容量素子によって構成されてもよい。これらの容量素子が配される場合には、当該容量素子の一端が、転送スイッチ M T X 1 、 M T X 2 のドレイン、ゲインコントロールスイッチ M G C のソース、および、ソースフォロワトランジスタ M S F のゲートに接続される。

30

#### 【 0 0 2 8 】

ゲインコントロールスイッチ M G C のドレインは容量素子 C 1 g の一方の端子とリセットスイッチ M R E S のソースに接続される。ゲインコントロールスイッチ M G C のゲートには制御信号 G C が入力される。容量素子 C 1 g に電荷が蓄積された状態で制御信号 G C を L o w レベルにし、ゲインコントロールスイッチ M G C をオフにすることで、容量素子 C 1 g は容量 C F D から分離される。また、制御信号 G C が H i g h レベル / L o w レベルに切り替わり、ゲインコントロールスイッチ M G C のオン / オフが切り替わることで、容量素子 C 1 g を F D 容量の一部として扱うか否かを切り替えられ、電荷電圧変換のゲインを異ならせることができる。さらに、制御信号 G C が中間電位 L M 1 ( L o w < L M 1 < H i g h ) のとき、容量素子 C 1 g と第 2 のフォトダイオード P D 2 の間のポテンシャルバリアが他の領域のバリアより低いレベルになることで、容量素子 C 1 g に余剰な電荷を排出することができる。

40

#### 【 0 0 2 9 】

リセットスイッチ M R E S のドレインおよびソースフォロワトランジスタ M S F のドレ

50

インには電源 V D D が接続される。リセットスイッチ M R E S のゲートには制御信号 R E S が入力される。制御信号 R E S が H i g h レベルのとき、リセットスイッチ M R E S がオンする。リセットスイッチ M R E S がオンすることで、第 1 のフォトダイオード P D 1 、第 2 のフォトダイオード P D 2 、 F D 部、および、容量素子 C 1 g の一部または全部をリセットすることができる。

#### 【 0 0 3 0 】

ソースフォロワトランジスタ M S F のソースはセレクトスイッチ M S E L を介して垂直出力線 1 2 に接続される。セレクトスイッチ M S E L のゲートには制御信号 S E L が入力される。制御信号 S E L が H i g h レベルのとき、セレクトスイッチ M S E L が O N になり、ソースフォロワトランジスタ M S F と電流源 1 1 でソースフォロワ回路が形成される。

10

#### 【 0 0 3 1 】

第 1 のフォトダイオード P D 1 のアノード、および、第 2 のフォトダイオード P D 2 のアノードは、それぞれ接地電位に接続される。また容量 C F D および C 1 g のもう一方の端子はそれぞれ接地電位に接続されるものとして記載している。

#### 【 0 0 3 2 】

第 2 のフォトダイオード P D 2 は、信号電荷である電子にとってポテンシャルが低い領域を含み、当該領域の周囲には信号電荷に対するポテンシャルバリアが形成される。すなわち、第 2 のフォトダイオード P D 2 のカソードには、局的に電位が高い領域が存在する。そのため、発生した信号電荷は第 2 のフォトダイオード P D 2 のカソードに蓄積される。信号電荷である電子が蓄積されることに伴い、第 2 のフォトダイオード P D 2 のカソード電位が下がる。その結果、第 2 のフォトダイオード P D 2 の周囲に形成されるポテンシャルバリアの高さは低くなる。

20

#### 【 0 0 3 3 】

光電変換により発生した電荷のうち、フォトダイオードに蓄積可能な量を超えて過剰な電荷が発生する場合がある。第 2 のフォトダイオード P D 2 に大量の光が入射し過剰な電荷が発生したときには、ポテンシャルバリアの最も低いところから過剰な電荷が外にあふれ出す。

#### 【 0 0 3 4 】

第 2 のフォトダイオード P D 2 と F D 部の間には転送スイッチ M T X 2 が存在し、 F D 部と容量素子 C 1 g との間にはゲインコントロールスイッチ M G C が存在する。転送スイッチ M T X 2 のゲート電位 T X 2 によって、転送スイッチ M T X 2 のゲートの直下の領域、すなわち、転送スイッチ M T X 2 のチャネル領域のポテンシャルバリアの高さを制御することができる。また、同様に、ゲインコントロールスイッチ M G C のゲート電位 G C によって、ゲインコントロールスイッチ M G C のゲートの直下の領域、すなわち、ゲインコントロールスイッチ M G C のチャネル領域のポテンシャルバリアの高さを制御することができる。

30

#### 【 0 0 3 5 】

フォトダイオード P D 2 と F D 部の間のポテンシャルバリアがフォトダイオード周辺を囲むポテンシャルバリアの中で最も低くなるように転送スイッチ M T X 2 の制御信号 T X 2 が制御される。このとき、第 2 のフォトダイオード P D 2 で発生した過剰な電荷は転送スイッチ M T X 2 を介して排出される。ゲインコントロールスイッチ M G C がオフであれば、排出された過剰な電荷は F D 部に保持される。ゲインコントロールスイッチ M G C に入力される制御信号 G C によって、ゲインコントロールスイッチ M G C のオン、オフが制御される。ゲインコントロールスイッチ M G C がオンであれば、排出された余剰な電荷は F D 部及び容量素子 C 1 g に保持される。

40

#### 【 0 0 3 6 】

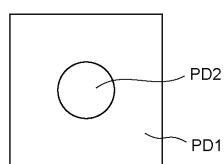

図 3 を用いて、図 2 に示した画素回路 1 0 における第 1 および第 2 のフォトダイオード P D 1 、 P D 2 の配置の一例を説明する。図 3 は本実施例の光電変換装置の平面構造を模式的に示している。具体的に、図 3 は、光電変換装置の受光面における第 1 および第 2 のフォトダイオード P D 1 、 P D 2 の配置が示されている。

50

## 【0037】

本実施例では第2のフォトダイオードPD2の受光面が画素の中央で円形に配置され、第1のフォトダイオードPD1の受光面が第2のフォトダイオードPD2の受光面を囲んだ領域に配置されている。図3に示した通り、第1のフォトダイオードPD1の方が、第2のフォトダイオードPD2よりも受光面積が大きい。そのため、受光面全体に一様な強さの光が入射した場合、つまり、単位面積当たりで等量の入射光が照射された場合、第1のフォトダイオードPD1で生じる電荷の量の方が、第2のフォトダイオードPD2で生じる電荷の量より多い。即ち第1のフォトダイオードPD1は、第2のフォトダイオードPD2と比較して光に対する感度が高い。

## 【0038】

第1および第2のフォトダイオードの形状及び配置は図3に示す例に限られない。例えば、第2のフォトダイオードPD2が矩形その他の形状であってもよい。また、一方のフォトダイオード(第1のフォトダイオードPD1)によって他方のフォトダイオード(第2のフォトダイオードPD2)が囲われていなくてもよい。

## 【0039】

また、本実施例では、第1のフォトダイオードPD1の受光面の面積と、第2のフォトダイオードPD2の受光面の面積とが異なっているが、両者は等しくてもよい。この場合、第1のフォトダイオードPD1の感度が、第2のフォトダイオードPD2の感度と等しい。2つのフォトダイオードの感度が異なることで、ダイナミックレンジ拡大の効果を得られる。しかし、2つのフォトダイオードの感度が異なることによるダイナミックレンジの拡大の効果は、本実施例において必ずしも得られなくてよい。なお、2つのフォトダイオード(PD1、PD2)の感度を異ならせるための構成は変更可能である。例えば、第1のフォトダイオードPD1及び第2のフォトダイオードPD2の上に、互いに光透過率の異なるフィルターを配置してもよい。あるいは、各フォトダイオードの受光面の面積を、遮光膜の開口の面積によって設定してもよい。

## 【0040】

なお、光電変換部上に入射光を受光部に導くためのマイクロレンズが設けられる場合、1つのマイクロレンズがフォトダイオードPD1、PD2の双方を覆うように配される。したがって、1つのマイクロレンズを受光面に射影した際に、当該マイクロレンズの射影がフォトダイオードPD1、PD2のそれぞれの受光面と少なくとも部分的に重なる。

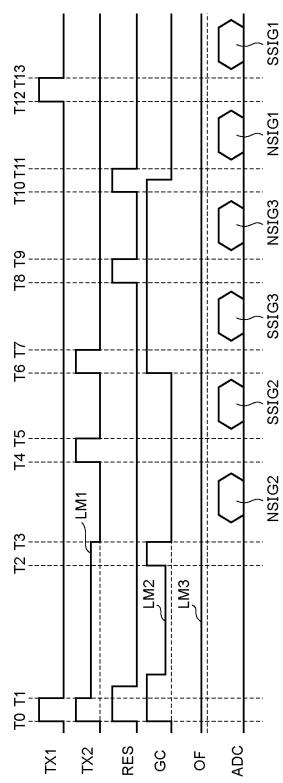

## 【0041】

図4は本実施例の動作を説明するタイミングチャートである。図4を用いて、図2に示した画素回路の動作について説明する。図4は、制御信号TX1、制御信号TX2、制御信号RES、制御信号GC、制御信号OFを示している。また、図4のADCは、画素回路から読み出される信号に対してAD変換が行われる期間を模式的に示している。

## 【0042】

本説明では時刻T2以降を画素回路から信号を読み出す読み出し期間とする。図4中で図示していないが、読み出し行に該当する行では、読み出し期間では制御信号SELはHIGHになりセレクトスイッチMSELはオンになっている。

## 【0043】

また、1行の読み出し操作の間に画素回路からは信号SSIG1、SSIG2、SSIG3、リセット信号NSIG1、NSIG2、NSIG3の6つの信号が読み出される。上述の6の信号は、それぞれ図4中のADCに対応する符号で示す期間にAD変換される。

## 【0044】

信号SSIG1は、第1のフォトダイオードPD1に蓄積された電荷Q1に基づく信号である。信号SSIG2は、第2のフォトダイオードPD2に蓄積された電荷Q2に基づく信号である。信号SSIG3は、第2のフォトダイオードPD2に蓄積された電荷Q2と蓄積期間中に第2のフォトダイオードPD2からあふれ出た電荷(QCFDとQC1g)に基づく信号である。リセット信号NSIG1、NSIG2、NSIG3は、それぞれ、信号SSIG1、SSIG2、SSIG3に対応するリセット状態でのノイズレベル

10

20

30

40

50

(N1、N2、N3)を表す信号である。

#### 【0045】

図4に示す例では、リセット信号NSIG2、信号SSIG2、信号SSIG3、リセット信号NSIG3、リセット信号NSIG1、信号SSIG1の順で読み出している。この順にすることで、低輝度側の信号SSIG1、SSIG2に対して相関二重サンプリング(CDS:Correlated Double Sampling)を行うことができるため、ノイズを低減できる。しかし、本実施例はこのような信号読み出しの順序に限定されない。

#### 【0046】

図4において、制御信号TX2、GC、OFを中間電位LM1、LM2、LM3(Low < LM < High)とすることがある。制御信号TX2、GC、OFが中間電位にある理由は、大量の光が入射した場合にフォトダイオードPD1、PD2で発生する過剰な電荷を制御するためである。このような制御によって、一部の電荷があふれて周辺画素や素子に影響を及ぼすことを低減するあるいは防ぐことができる。

10

#### 【0047】

フォトダイオードPD1とPD2に光が入射すると、入射する光量に応じてそれぞれのカソード電位が小さくなる。第1のフォトダイオードPD1の場合、カソード電位に対するオーバーフロースイッチM0Fのゲート電位LM3の電位差(Vgs)がオーバーフロースイッチM0Fの閾値を超えると、オーバーフロースイッチM0Fがオンする。オーバーフロースイッチM0Fがオンした以降は、第1のフォトダイオードPD1で生じた電荷が電源VDDに流れる。そのため、第1のフォトダイオードPD1のカソード電位はそれ以上小さくならない。換言すると、第1のフォトダイオードPD1に蓄積される電荷の量がオーバーフロースイッチM0Fのゲート電位LM3によって制限される。

20

#### 【0048】

第1のフォトダイオードPD1で生じた電荷がオーバーフロースイッチM0Fを介して電源VDDに流れるようにするためのポテンシャルの状態について説明する。まず、リセットされた状態の第1のフォトダイオードPD1は、信号電荷である電子にとってポテンシャルが低い領域を含み、当該領域の周囲には信号電荷に対するポテンシャルバリアが形成される。すなわち、第1のフォトダイオードPD1のカソードには、局所的に電位が高い領域が存在する。そのため、発生した信号電荷は第1のフォトダイオードPD1のカソードに蓄積される。信号電荷である電子が蓄積されることに伴い、第1のフォトダイオードPD1のカソード電位が下がる。その結果、第1のフォトダイオードPD1の周囲に形成されるポテンシャルバリアの高さは低くなる。そして、第1のフォトダイオードPD1に大量の光が入射し過剰な電荷が発生したときには、ポテンシャルバリアの最も低いところから過剰な電荷が外にあふれ出す。

30

#### 【0049】

オーバーフロースイッチM0Fのゲート電位LM3によって、オーバーフロースイッチM0Fのゲートの直下の領域、すなわち、オーバーフロースイッチM0Fのチャネル領域のポテンシャルバリアの高さを制御することができる。また、同様に、第1の転送スイッチMTX1のゲート電位TX1によって、第1の転送スイッチMTX1のゲートの直下の領域、すなわち、第1の転送スイッチMTX1のチャネル領域のポテンシャルバリアの高さを制御することができる。そこで、本実施例では、電荷蓄積期間において、オーバーフロースイッチM0Fのゲート電位LM3を、制御信号TX1の電位よりも高くしている。これにより、第1のフォトダイオードPD1と電源VDDの間の領域(オーバーフロースイッチM0Fのチャネル領域)のポテンシャルバリアは、第1のフォトダイオードPD1とほかの領域とを隔てるポテンシャルバリアよりも低くなる。そのため、第1のフォトダイオードPD1に大量の光が入射し、過剰な電荷が発生したとき、第1のフォトダイオードPD1からオーバーフロースイッチM0Fを介して電源VDDに電荷を転送可能である。これにより大量の光が入射し第1のフォトダイオードPD1で過剰な電荷が発生しても、電源VDDに余剰な電荷を排出することができる。

40

50

### 【 0 0 5 0 】

第2のフォトダイオード P D 2 の場合、制御信号 T X 2 と制御信号 G C が中間電位にあり、第2のフォトダイオード P D 2 に蓄積しきれない電荷が発生した場合は容量 C F D および容量素子 C 1 g に電荷を保持することができる。第2のフォトダイオード P D 2 には第2の転送スイッチ M T X 2 のみが接続されているため、第2のフォトダイオード P D 2 に蓄積される電荷の量は第2の転送スイッチ M T X 2 のゲート電位 L M 1 によって制限される。

### 【 0 0 5 1 】

なお、ゲインコントロールスイッチ M G C は容量 C F D と容量素子 C 1 gとの間にポテンシャルバリアを形成するために設けられている。容量 C F D と容量素子 C 1 g の間にポテンシャルバリアが形成されているとき、第2のフォトダイオード P D 2 から溢れた余剰な電荷はまず容量 C F D に保持される。その後、ポテンシャルバリアを超えて余剰な電荷が生じると、容量素子 C 1 g に保持される。そのため制御電圧 G C を中間電位としたまま信号の読み出しを行うと容量 C F D に保持されている電荷量によっては後述する信号 N S I G 2 と信号 S S I G 2 に差がつかない。つまり第2のフォトダイオード P D 2 に保持される電荷に基づく信号を正確に読み出すことができなくなってしまう。そのため容量 C F D に保持された電荷を容量素子 C 1 g に分配するために一度ゲインコントロールスイッチ M G C をオンにして容量 C F D に保持される電荷を低減する必要がある。はじめから容量 C F D と容量素子 C 1 g の両方に電荷を蓄積する場合にはポテンシャルバリアは不要である。つまり第2のフォトダイオード P D 2 で発生した過剰電荷を容量 C F D および容量素子 C 1 g に保持する際は、制御信号 T X 2 が中間電位であれば制御信号 G C は H i g h でもよい。

10

### 【 0 0 5 2 】

以上のように制御信号 O F 、 T X 2 、 G C を中間電位に設定することで、フォトダイオード P D 1 および P D 2 で発生した過剰な電荷を電源 V D D や容量 C F D と C 1 g に排出したり保持したりすることができ、周辺画素や素子への電荷の漏れ出しを低減している。

20

### 【 0 0 5 3 】

図4のタイミングチャートと画素回路の動作の対応を説明する。まず時刻 T 0 ~ 時刻 T 1 の期間は、フォトダイオード P D 1 、 P D 2 をリセットする期間である。時刻 T 0 で制御信号 T X 1 、 T X 2 、 R E S 、 G C が L o w から H i g h に遷移し、各スイッチ M T X 1 、 M T X 2 、 M R E S 、 M G C が O N になる。この時、電源 V D D から第1のフォトダイオード P D 1 のカソードまでと第2のフォトダイオード P D 2 のカソードまでの電気的な経路が形成され、フォトダイオード P D 1 および P D 2 がリセットされる。また、このとき、 F D 部の電位も電源 V D D の電位にリセットされる。

30

### 【 0 0 5 4 】

時刻 T 1 以降は、電荷蓄積期間である。時刻 T 1 になると制御信号 T X 1 が L o w に遷移し、制御信号 T X 2 は中間電位 L M 1 ( L o w < L M 1 < H i g h ) に遷移する。時刻 T 1 で転送スイッチ M T X 1 および M T X 2 がオフになり、フォトダイオード P D 1 および P D 2 で光電変換による電荷蓄積が開始され、電荷蓄積期間がスタートする。

### 【 0 0 5 5 】

時刻 T 1 以後に制御信号 R E S が L o w になりリセットスイッチ M R E S がオフする。リセットスイッチ M R E S がオフすると、容量 C F D および容量素子 C 1 g を含むノードが電気的にフローティングになる。この時の容量 C F D および容量素子 C 1 g の電圧がノイズ信号 N 1 に相当する。リセットスイッチ M R E S がオフする時の電源電圧 V D D の変動やリセットスイッチ M R E S がオフする直前にリセットスイッチ M R E S のチャネルに残留していた電荷の影響により、ノイズ信号 N 1 はランダムなノイズ成分を含みうる。その後制御信号 G C が中間電位 L M 2 ( L o w < L M 2 < H i g h ) に遷移する。この時ゲインコントロールスイッチ M G C はオフである。すなわち、リセット状態の容量 C F D と容量素子 C 1 g との間に、ポテンシャルバリアが生じるような電位に、中間電位 L M 2 は設定されている。なお制御信号 O F は常に中間電位 L M 3 ( L o w < L M 3 < H i g h )

40

50

である。

#### 【 0 0 5 6 】

時刻 T 2 になると制御信号 G C が H i g h に遷移し、ゲインコントロールスイッチ M G C がオンし、そして、容量 C F D と C l g の電位は等しくなる。このとき、第 2 のフォトダイオード P D 2 で発生した過剰な電荷は、容量 C F D と容量素子 C l g とによって保持されている。その後、時刻 T 3 に制御信号 G C が L o w に遷移し、ゲインコントロールスイッチ M G C がオフする。このとき容量 C F D に保持される第 2 のフォトダイオード P D 2 で発生した過剰な電荷を Q C F D とする。また、容量素子 C l g に保持される過剰な電荷を Q C l g とする。

#### 【 0 0 5 7 】

時刻 T 3 ~ T 4 の間にリセット信号 N S I G 2 の読み出しと、リセット信号 N S I G 2 に対する A D 変換が行われる。時刻 T 3 になると制御信号 T X 2 が中間電位 L M 2 から L o w に遷移する。後述の時刻 T 4 での電位の遷移量と T 5 での電位の遷移量を揃え、時刻 T 3 ~ T 4 の N S I G 2 の読み出し及び時刻 T 4 ~ T 5 の S S I G 2 の読み出しの際容量 C F D の電位を同一に保つためである。

#### 【 0 0 5 8 】

ソースフォロワトランジスタ M S F と電流源 1 1 で構成されるソースフォロワ回路が、リセット信号 N S I G 2 を垂直出力線 1 2 に出力する。この時の F D 部の電位は、電源 V D D の電位に時刻 T 1 の後にリセットスイッチがオフした時に生じるノイズが重畠された電位（ノイズ信号 N 1 ）に、さらに、電荷 Q C F D による電位変動分が重畠された電位になっている。したがって、リセット信号 N S I G 2 は、ノイズ信号 N 1 と電荷 Q C F D とに基づく信号である。また、この期間に、垂直出力線 1 2 から出力されたリセット信号 N S I G 2 の A D 変換が行われる。

#### 【 0 0 5 9 】

時刻 T 4 になると制御信号 T X 2 が H i g h に遷移、転送スイッチ M T X 2 がオンになり、第 2 のフォトダイオード P D 2 で光電変換された電荷 Q 2 が容量 C F D に転送される。

#### 【 0 0 6 0 】

時刻 T 5 ~ T 6 の間に S S I G 2 の読み出しと A D 変換が行われる。時刻 T 5 で制御信号 T X 2 が L o w に遷移、転送スイッチ M T X 2 がオフとなる。この時容量 C F D に保持されているのは、時刻 T 3 以後 C F D に蓄積されていた電荷 Q C F D と時刻 T 4 ~ T 5 間に転送された電荷 Q 2 である。電荷 Q C F D と電荷 Q 2 は容量 C F D で電圧信号に変換される。したがって、この時の F D 部の電位は、ノイズ信号 N 1 に電荷 Q C F D 及び電荷 Q 2 による電位変動分が重畠された電位である。ソースフォロワ回路が信号 S S I G 2 を垂直出力線に出力する。すなわち、信号 S S I G 2 は、ノイズ信号 N 1 と電荷 Q C F D と電荷 Q 2 とに基づく信号である。また、この期間に、垂直出力線 1 2 から出力された信号 S S I G 2 の A D 変換が行われる。

#### 【 0 0 6 1 】

時刻 T 6 ~ T 8 の間に S S I G 3 の読み出しと A D 変換が行われる。時刻 T 6 になると制御信号 T X 2 と G C が H i g h に遷移し、転送スイッチ M T X 2 とゲインコントロールスイッチ M G C がオンになる。この時第 2 のフォトダイオード P D 2 に蓄積されている、時刻 T 4 ~ T 5 間の容量 C F D への転送動作の際は容量が不足し転送しきれなかった電荷が、容量 C F D のみを転送先とした場合と比べ拡大された容量である容量 C F D と容量素子 C l g に転送される。

#### 【 0 0 6 2 】

時刻 T 7 で制御信号 T X 2 が L o w になり、転送スイッチ M T X 2 がオフになる。この時、容量 C F D に保持された電荷 Q C F D と、電荷 Q 2 と、容量素子 C l g に保持された電荷 Q C l g とは、容量 C F D と容量素子 C l g の合成容量で電圧変換される。したがって、この時の F D 部の電位は、ノイズ信号 N 1 に、電荷 Q C F D 、電荷 Q C l g 及び電荷 Q 2 による電位変動分が重畠された電位である。この期間にソースフォロワ回路が出力する信号 S S I G 3 は、ノイズ信号 N 1 と電荷 Q C F D と電荷 Q C l g と電荷 Q 2 とに基づ

10

20

30

40

50

く信号である。として垂直出力線に出力される。その後信号 S S I G 3 の A D 変換がなされる。

#### 【 0 0 6 3 】

なお、信号電荷を電圧信号に変換する変換ゲインは変換容量の逆数に比例することから、等量の電荷であれば容量 C F D と C 1 g で変換した電圧のほうが容量 C F D で変換した電圧よりも小さい。

#### 【 0 0 6 4 】

時刻 T 8 ~ T 10 の間に N S I G 3 の読み出しと A D 変換が行われる。時刻 T 8 で、制御信号 R E S が H i g h になり、リセットスイッチ M R E S がオンする。すでにゲインコントロールスイッチ M G C もオンなので、容量 C F D および容量素子 C 1 g の電位が電源 V D D の電位にリセットされる。

10

#### 【 0 0 6 5 】

時刻 T 9 で制御 R E S が L o w になり、リセットスイッチ M R E S がオフになる。この時の容量 C F D 及び容量素子 C 1 g の電位は、電源 V D D の電位に時刻 T 9 にリセットスイッチがオフした時に生じるノイズが重畠された電位（ノイズ信号 N 2 ）である。したがって、ノイズ信号 N 2 に基づくりセット信号 N S I G 3 が垂直出力線に出力され、その後、リセット信号 N S I G 3 の A D 変換がなされる。

#### 【 0 0 6 6 】

時刻 T 10 ~ T 11 の期間に、F D 部を再びリセットする。時刻 T 10 で制御信号 R E S が H i g h になり、リセットスイッチ M R E S がオンし、容量 C F D および C 1 g がリセットされる。その後制御信号 G C が L o w になり、時刻 T 11 で制御信号 R E S が L o w になる。これにより、リセットスイッチ M R E S 及びゲインコントロールスイッチ M G C がオフになる。この時の F D 部の電位は、電源 V D D の電位に時刻 T 10 以降にリセットスイッチ及びゲインコントロールスイッチ M G C がオフした時に生じるノイズが重畠された電位（ノイズ信号 N 3 ）である。

20

#### 【 0 0 6 7 】

容量 C F D のノイズ信号 N 3 はリセット信号 N S I G 1 として垂直出力線から出力され、時刻 T 11 ~ T 12 の間にリセット信号 N S I G 1 の A D 変換がなされる。

#### 【 0 0 6 8 】

リセット信号 N S I G 1 の A D 変換が終了した後、時刻 T 12 で制御信号 T X 1 が H i g h に遷移、転送スイッチ M T X 1 がオンになり、時刻 T 13 までの間に第 1 のフォトダイオード P D 1 に蓄積されている電荷 Q 1 が容量 C F D に転送される。

30

#### 【 0 0 6 9 】

時刻 T 13 になると制御信号 T X 1 が L o w になり、転送スイッチ M T X 1 がオフになって、電荷蓄積期間は終了する。この時、容量 C F D に保持された電荷 Q 1 は信号 N 3 に則る信号 S S I G 1 として垂直出力線から出力され、その後信号 S S I G 1 の A D 変換がなされる。信号 S S I G 1 の A D 変換が終了すると制御信号 S E L が L o w になり、1 行の読み出しが終了する。

#### 【 0 0 7 0 】

以上 1 行の読み出し操作の間に画素回路から読み出された信号 S S I G 1 、 S S I G 2 、 S S I G 3 、リセット信号 N S I G 1 、 N S I G 2 、 N S I G 3 は、前述の通りそれぞれ下記の情報を有する。

40

#### 【 0 0 7 1 】

S S I G 1 : ノイズ信号 N 3 + 電荷 Q 1

N S I G 1 : ノイズ信号 N 3

S S I G 2 : ノイズ信号 N 1 + 電荷 Q C F D + 電荷 Q 2

N S I G 2 : ノイズ信号 N 1 + 電荷 Q C F D

S S I G 3 : ノイズ信号 N 1 + 電荷 Q C F D + 電荷 Q C 1 g + 電荷 Q 2

N S I G 3 : ノイズ信号 N 2

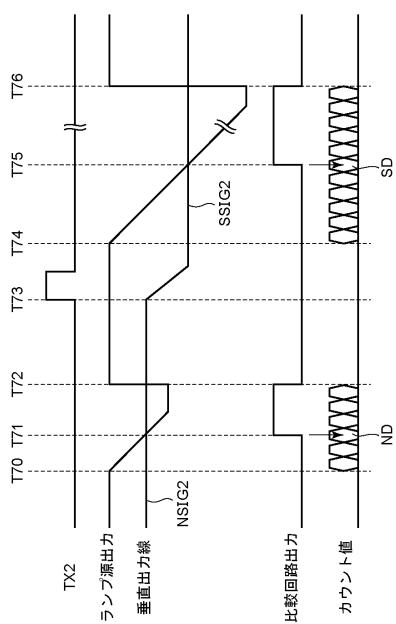

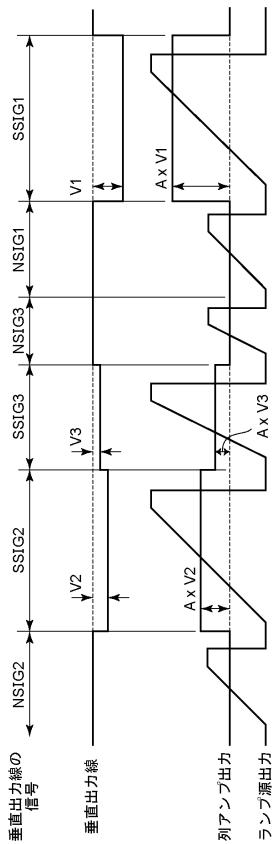

図 5 のタイミングチャートを用いて、本実施例の光電変換装置の A D 変換の動作を詳細

に説明する。図5は、制御信号TX2、ランプ源63の出力する参照信号の電位（ランプ源出力）、垂直出力線12の電位（リセット信号NSIG2および信号SSIG2の信号値）、比較回路64の出力、および、カウンタ回路66の出力するカウンタ値を示している。

#### 【0072】

ここでは説明の簡略化のために、前述の信号SSIG2とリセット信号NSIG2のAD変換を用いて説明する。まず垂直出力線にはリセット信号NSIG2が出力されている。また、ランプ源出力は初期値に設定されている。

#### 【0073】

時刻T70になると、リセット信号NSIG2のAD変換が開始される。カウンタ回路67がカウント動作を開始する。また、ランプ源63は、時間の経過とともに電位が下降するランプ信号を出力する。つまり、ランプ源出力の電位が初期値から変化し始める。

#### 【0074】

時刻T71になるとランプ源63出力と垂直出力線12の両電位の大小関係が反転し、比較回路64の出力はLowからHighに遷移する。その時のカウント値をNDとする。列メモリ65はカウント値NDを記憶する。

#### 【0075】

時刻T72で、ランプ信号は設定された電位振幅の下限まで掃引し終え、リセット信号NSIG2のAD変換は終了する。ランプ源出力はランプ信号を出力する前の電位に戻る。この時ランプ源63出力の電位が垂直出力線12の電位よりも大きくなり、比較回路63出力はHighからLowに遷移する。またカウンタ回路67もカウント動作を終了する。

#### 【0076】

時刻T73になると制御信号TX2がHighになり、第2のフォトダイオードPD2で光電変換された電荷がCFDに転送され、それに対応した信号SSIG2が垂直出力線に出力される。後に制御信号TX2はLowになる。

#### 【0077】

時刻T74になると、信号SSIG2のAD変換が開始される。カウンタ回路67がカウント動作を開始する。また、ランプ源63出力はランプ信号を出力する。つまり、ランプ源出力の電位が初期値から変化し始める。

#### 【0078】

時刻T75でランプ源63出力の電位が垂直出力線12の電位よりも小さくなり、比較回路出力がLowからHighに遷移する。その時のカウント値をSDとすると、列メモリ65はカウント値SDを記憶する。

#### 【0079】

時刻T76で、ランプ信号は設定された電位振幅の下限まで掃引し終え、信号SSIG2のAD変換は終了する。ランプ源63出力はランプ信号を出力する前の電位に戻る。この時ランプ源63出力の電位が垂直出力12線の電位よりも大きくなり、比較回路63出力はHighからLowに遷移する。またカウンタ回路67もカウント動作を終了する。

#### 【0080】

以上のAD変換で得られたカウント値SDとカウント値NDはそれぞれ演算処理部66に転送される。

#### 【0081】

信号SSIG1、SSIG3、および、リセット信号NSIG1、3に対しても、同様に、ランプ信号を比較回路64に入力しつつ、カウンタ回路67のカウント動作を行うことで、AD変換を行うことができる。

#### 【0082】

図5では、例えば信号SSIG2に対するAD変換において、ランプ信号の振幅の初期値から最大値まで掃引している。そのため、ランプ源出力をランプ信号の振幅の一端から他端まで掃引する期間が長いので、同様のランプ信号を3つ信号SSIG1、SSIG2

10

20

30

40

50

、 S S I G 3 に適用すると、必要以上に A D 変換期間を延ばしてしまう可能性がある。光電変換装置の読み出し時間が長くなり、結果として光電変換装置の A D 変換の性能を低下させる要因となってしまう。

#### 【 0 0 8 3 】

本実施例では、3種類のリセットレベル信号 N S I G 1 ~ 3 と、画素信号 S S I G 1 ~ 3 の A D 変換期間をそれぞれ適切に設定することで、光電変換装置の A D 変換の高性能化を実現する。

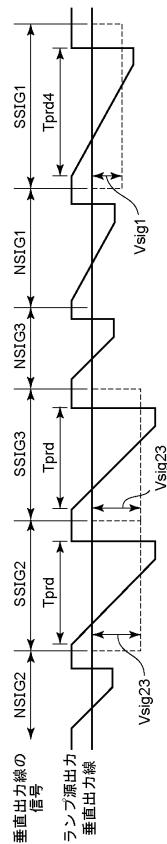

#### 【 0 0 8 4 】

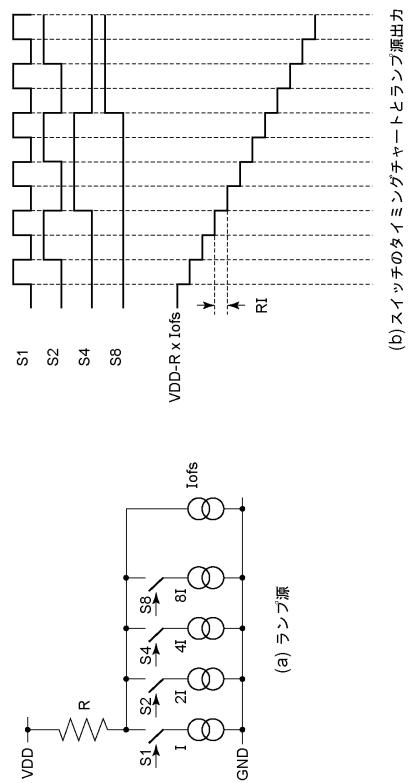

図 6 にランプ源の一例を示す。図 6 ( a ) は、ランプ源 6 3 の等価回路を示す図である。ランプ源 6 3 は、抵抗 R および、それぞれが抵抗 R に直列に接続された電流源 I 、 2 I 、 4 I 、 8 I を含む。電流源 I 、 2 I 、 4 I 、 8 I は、互いに並列の経路を形成している。抵抗 R と各電流源との間には、各電流源に対応するスイッチとして S 1 、 S 2 、 S 4 、 S 8 が接続される。図 6 ( b ) は S 1 ~ 8 のスイッチの動作のタイミングチャートとランプ源 6 3 の出力する参照信号の電位 ( ランプ源出力 ) を示している。

10

#### 【 0 0 8 5 】

図 6 ( a ) 記載の回路において、スイッチ S のいずれかがオンになると、抵抗 R にオンになったスイッチに対応する電流源からの電流が流れる。ランプ源出力は  $V_{DD} - R \times (I_{off} + nI)$  で表され、流れる電流に応じてランプ源の電位が低下する。各電流源の出力は I に対し 2 の累乗倍で表される値を取るので、図 6 ( b ) のタイミングチャートに示すようにスイッチのオンオフを切り替えれば抵抗 R に流れる電流は I ずつ段階的に増加し、ランプ源の電位もまた I R ずつ段階的に減少していく。

20

#### 【 0 0 8 6 】

なお、電流源 I off はオフセット電流を流す電流源である。オフセット電流によりランプ信号の掃引開始時の電位は  $V_{DD} - R \times I_{off}$  になる。電流源 I off はランプ源の構成として必須なものではなく、電位 V DD をランプ信号の開始時の電位としてもよい。電流源 I ~ 8 I のいずれかを I off として使用することも可能である。

#### 【 0 0 8 7 】

本実施例においてランプ源が出力するランプ信号は時間の経過とともに電位が下降するランプ信号であるが、時間の経過とともに電位が上昇するランプ信号でもよい。この場合、抵抗 R に流れる電流を I ずつ段階的に減らしていく。

30

#### 【 0 0 8 8 】

A D 変換で得られたデジタルデータの演算処理について説明する。例えば、第 1 のフォトダイオード P D 1 で光電変換され読み出された信号 S S I G 1 の A D 変換されたデジタルデータから、そのリセットレベルであるリセット信号 N S I G 1 の A D 変換されたデジタルデータを減算する。これによって電荷 Q 1 のみに対応するデータを得られる。本実施例ではノイズ信号 N 3 と電荷 Q 1 の情報を有する信号 S S I G 1 からノイズ信号 N 3 の情報を有するリセット信号 N S I G 1 を減算することで電荷 Q 1 の情報を得ることができる。

#### 【 0 0 8 9 】

同様に信号 S S I G 2 に対応するデジタルデータから、リセット信号 N S I G 2 に対応するデジタルデータを減算することで電荷 Q 2 のみに対応するデータを得られる。本実施例ではノイズ信号 N 1 、電荷 Q C F D 、電荷 Q 2 の情報を有する信号 S S I G 2 からノイズ信号 N 1 と電荷 Q C F D の情報を有するリセット信号 N S I G 2 を減算することで電荷 Q 2 の情報を得ることができる。

40

#### 【 0 0 9 0 】

このようにそれぞれの信号からリセット信号を減算処理することによって、各信号の C D S が実現できる。上述の読み出し順序であれば、F D 部がフローティングである状態を維持したまま、リセット信号 N S I G 1 / 2 を読み出し、続けて信号 S S I G 1 / 2 を読み出すことができるためである。

#### 【 0 0 9 1 】

本実施例において、信号 S S I G 3 も同様に対応するデジタルデータからリセット信号

50

N S I G 3 に対応するデジタルデータを減算する場合について説明する。信号 S S I G 3 はノイズ信号 N 1、電荷 Q C F D、電荷 Q C 1 g、電荷 Q 2 の情報を有するのに対しリセット信号 N S I G 3 はノイズ信号 N 2 の情報を有する。つまりリセット信号 N S I G 3 に含まれるノイズ信号 N 2 は、信号 S S I G 3 のリセットレベル（ノイズ信号 N 1）と同一ではなく、S S I G 3 については C D S が成り立たない。しかしノイズ信号 N 1 と N 2 の違いはわずかであると考えられることから、S S I G 3 から N S I G 3 を減算したデータを電荷 Q C F D、電荷 Q C 1 g、電荷 Q 2 の和に対応するデータとして扱うことができる。また、画素ごとの固定パターンノイズは除去することができる。

#### 【 0 0 9 2 】

なお、以降の説明では信号 S S I G 1、S S I G 2、S S I G 3 を総称して S 信号とも呼び、リセット信号 N S I G 1、N S I G 2、N S I G 3 を総称して N 信号とも呼ぶ。

10

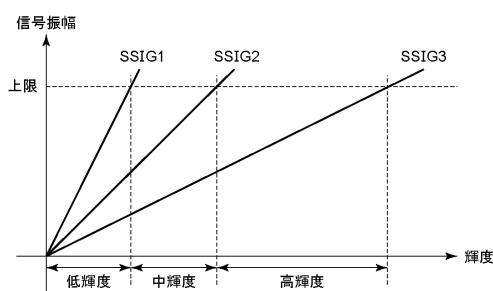

#### 【 0 0 9 3 】

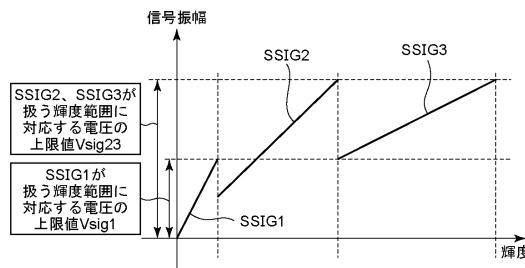

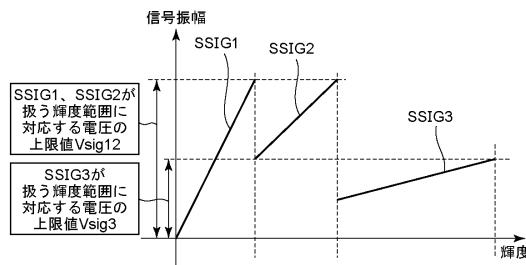

図 7 は、輝度に対する信号 S S I G 1、S S I G 2、S S I G 3 の信号値を示した図面である。本実施例では、信号 S S I G 1、S S I G 2、S S I G 3 の信号値は電圧の大きさによって表現される。輝度は、単位面積当たりの入射光量を表している。簡単のため、受光面の全体において均一な量の光が入射することとする。

20

#### 【 0 0 9 4 】

単位面積当たりの入射光量が均一であれば、受光面積の大きい第 1 のフォトダイオード P D 1 では、受光面積の小さい第 2 のフォトダイオード P D 2 よりも多くの電荷が光電変換される。第 1 のフォトダイオード P D 1 に保持される電荷 Q 1 及び第 2 のフォトダイオード P D 2 に保持される電荷 Q 2 は共に容量 C F D で電荷電圧変換され、信号 S S I G 1 及び信号 S S I G 2 として出力される。そのため、同一の輝度の光に対する信号値は信号 S S I G 1 のほうが大きい。受光面積の大きい第 1 のフォトダイオード P D 1 では微弱な光でも多くの電荷を発生させることができるために、低輝度の光については S / N の良好な信号を得ることができるが、比較的低輝度の光で回路が取りうる電圧範囲の上限を迎える。一方で、受光面積の小さい第 2 のフォトダイオード P D 2 で発生する電荷に対応する信号 S S I G 2 は、信号 S S I G 1 よりも高い輝度の光に対して線形性の維持された信号値を持つことができる。

20

#### 【 0 0 9 5 】

次に、信号 S S I G 3 が、信号 S S I G 2 よりも高い輝度の光を光電変換することができるることを説明する。高輝度への対応は、まず信号 S S I G 3 が信号 S S I G 2 よりも多くの電荷に基づく信号であることに起因する。加えて、より多くの電荷が生じる状況でも線形性を維持するため、信号 S S I G 3 を読み出す際の電荷から電圧への変換ゲインが信号 S S I G 2 の場合のそれよりも低いことに起因する。

30

#### 【 0 0 9 6 】

前述の通り信号 S S I G 2 は第 2 のフォトダイオード P D 2 に保持される電荷 Q 2 を容量 C F D で電荷電圧変換することによって得られる。一方、信号 S S I G 3 は第 2 のフォトダイオード P D 2 に保持される電荷 Q 2 と第 2 のフォトダイオード P D 2 から溢れた余剰な電荷 Q C F D 及び Q C 1 g を容量 C F D と容量素子 C 1 g の合成容量で電荷電圧変換することによって得られる。したがって、第 2 のフォトダイオード P D 2 から溢れた電荷も電荷電圧変換する信号 S S I G 3 は、信号 S S I G 2 よりも高い輝度の光に対応した信号値を持つことができる。

40

#### 【 0 0 9 7 】

また、電荷信号から電圧信号への変換ゲインは変換容量の逆数として定まることから、容量 C F D と容量 C 1 g の合成容量で変換した電圧は、容量 C F D のみで変換した電圧よりも小さくなる。信号 S S I G 3 を読み出すときは、F D 部に容量素子 C 1 g が接続されている。すなわち、F D 部の変換容量は相対的に大きい。一方、信号 S S I G 3 を読み出すときは、F D 部に容量素子 C 1 g が接続されていない。すなわち、F D 部の変換容量は相対的に小さい。ここで、第 2 のフォトダイオード P D 2 から溢れない程度の量の電荷を電荷電圧変換する場合を例に説明する。第 2 のフォトダイオード P D 2 から電荷が溢れな

50

いため、電荷 Q C F D 及び電荷 Q C 1 g はゼロであるとして、以降の説明では表記を割愛する。信号 S S I G 3 の読み出しでは、電荷 Q 2 を容量 C F D と容量 C 1 g の合成容量で電荷電圧変換する。一方、信号 S S I G 2 の読み出しでは、電荷 Q 2 を容量 C F D で電荷電圧変換する。したがって、信号 S S I G 3 の電荷量あたりの電圧の変化は、信号 S S I G 2 の電荷量あたりの電圧の変化より小さい。すなわち信号 S S I G 3 は輝度の変化に対する電圧の変化が小さくなり、信号 S S I G 2 と比べ高輝度の光まで光電変換可能である。

#### 【 0 0 9 8 】

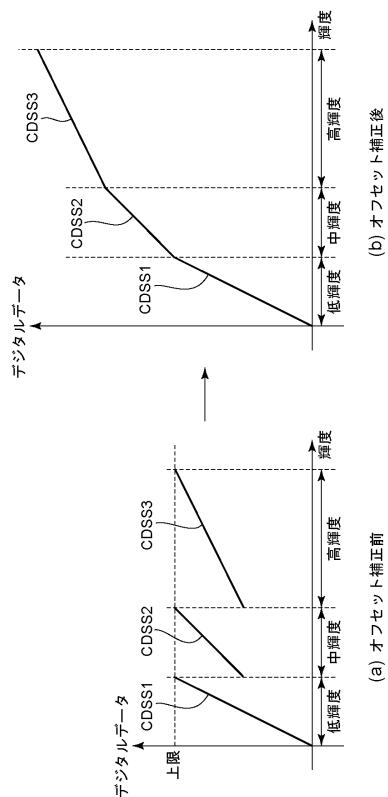

図 8 に各信号のデジタルデータを選択的に使用することでダイナミックレンジが拡大されるイメージを示す。横軸を入射する光の輝度とし、縦軸は各デジタルデータの信号値である。

10

#### 【 0 0 9 9 】

信号 S S I G 1 の減算処理後のデジタルデータを C D S S 1 、信号 S S I G 2 の減算処理後のデジタルデータを C D S S 2 、信号 S S I G 3 の減算処理後のデジタルデータを C D S S 3 とする。本実施例では、いずれの輝度範囲の光が入射したときでも、各画素回路 10 からは C D S S 1 、 C D S S 2 , C D S S 3 の 3 種類の信号が得られる。画像を形成するときは、図 8 に示すように輝度ごとに読み出された信号から使う信号 1 つを選択する処理を行う。

#### 【 0 1 0 0 】

よって例えば、入射光に対して低輝度側を信号 S S I G 1 に対応する前述の減算処理後のデジタルデータを用い、中輝度を信号 S S I G 2 に対応する減算処理後のデジタルデータを用い、高輝度側を信号 S S I G 3 に対応する減算処理後のデジタルデータを用いる。さらに各々のデジタルデータに対してオフセット補正の演算処理を行うことで、ダイナミックレンジの拡大が実現できる。

20

#### 【 0 1 0 1 】

図 8 ( a ) ではオフセット補正処理前の各輝度に対するデジタルデータの信号値を示し、図 8 ( b ) では、データ C D S S 2 および C D S S 3 のオフセット補正処理後のデジタルデータの値を示している。

#### 【 0 1 0 2 】

なお、一般的に低輝度側の方が高輝度側よりも輝度の変化に対する視認性が高いため、低輝度側は輝度に対する感度が高く S / N 比の低い信号 S S I G 1 で扱うことが望ましい。

30

#### 【 0 1 0 3 】

前述の通り、 3 つの信号は共通の回路を介して読み出されるため、 3 つの信号の上限値は一意に定まる。一方、 3 つの信号は輝度の変化に対する信号値の変化の割合が互いに異なるので、各信号がその電圧の上限値に到達するまでに扱いうる輝度の範囲は互いに異なる（図 7 ）。これらの各信号が扱いうる輝度の範囲から、画像形成において各信号が扱う輝度範囲を選択することができる。図 8 ( a ) に示すデジタルデータと輝度範囲の選択の例を説明する。図 8 ( a ) では、データ C D S S 2 がその上限値に到達するまでに扱いうる輝度の範囲のうち、データ C D S S 1 が上限値に達する輝度からデータ C D S S 2 が上限値に達する輝度までをデータ C D S S 2 が扱う輝度範囲としている。また、データ C D S S 3 がその上限値に到達するまでに扱いうる輝度の範囲のうち、データ C D S S 2 が上限値に達する輝度からデータ C D S S 3 が上限値に達する輝度までをデータ C D S S 3 が扱う輝度範囲としている。この場合、最も感度の高い信号 S S I G 1 の扱う輝度の範囲を広くとることができるので、 S / N 比の良好な信号を優先的に使用することができる。図 8 ( a ) の例に限らず、各信号が扱う輝度の範囲は、求められる画質や、他の信号と重複することにより画像の形成には使用しないにも関わらず A D 変換が行われる期間の長さなどを考慮して定めることができる。

40

#### 【 0 1 0 4 】

このように本実施例では第 1 のフォトダイオード P D 1 、第二のフォトダイオード P D 2 、蓄積部からなる構成を取る。この場合例えば第 1 のフォトダイオード P D 1 のみを使用した場合に得られるデータ C D S S 1 で扱える輝度範囲よりも高い輝度を扱えるデータ

50

C D S S 2 および C D S S 3 を取得することもできる。つまりデジタルデータとして扱える輝度範囲が拡大され、光電変換装置のダイナミックレンジが拡大されているといえる。

#### 【 0 1 0 5 】

図 9 は、S 信号が扱う輝度範囲と信号電圧範囲の関係について、図 8 ( a ) の例とは別の例を示している。この例では信号 S S I G 1 の扱う輝度範囲に対応する電圧の取りうる範囲の上限 V s i g 1 が、信号 S S I G 2 および S S I G 3 の扱う輝度範囲に対応する電圧の取りうる範囲の上限 V s i g 2 3 よりも小さい。前述の通り輝度の変化に対する視認性を考慮すれば低輝度側はなるべく高い輝度まで信号 S S I G 1 で扱うことが望ましい。しかし信号 S S I G 1 が V s i g 2 3 と同じ電圧までの範囲を扱う場合、信号 S S I G 2 が扱いうる輝度範囲のうち信号 S S I G 1 が扱う輝度範囲と重複する輝度範囲については信号 S S I G 1 で扱われるため、信号 S S I G 2 の情報は使用されない。つまり信号 S S I G 2 と信号 S S I G 1 が扱いうる輝度範囲のうち重複する輝度範囲についての信号 S S I G 2 の A D 変換は冗長になってしまう。信号 S S I G 1 の信号値が大きくなるような輝度領域では、信号 S S I G 2 の信号値も十分に高い S N 比を得られる程度に大きくなる。そこで、信号 S S I G 1 の扱う輝度範囲に対応する電圧の取りうる範囲の上限 V s i g 1 を、信号 S S I G 1 の信号値がとりうる電圧範囲の上限値よりも小さい電圧の範囲、具体的には、低輝度側の範囲のみに設定する。信号 S S I G 1 の扱う輝度範囲に対応する電圧の取りうる範囲の上限 V s i g 1 が小さければ信号 S S I G 1 の扱う電圧範囲に対応する輝度範囲及び信号 S S I G 2 と重複する輝度範囲も小さくなり、S S I G 2 の A D 変換が最適化される。

10

#### 【 0 1 0 6 】

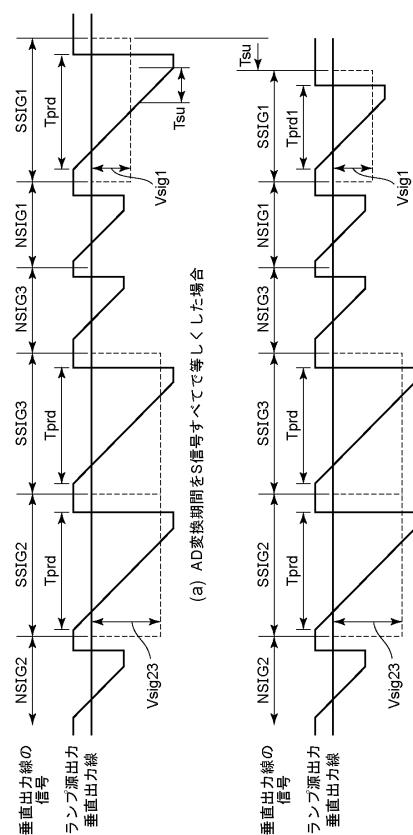

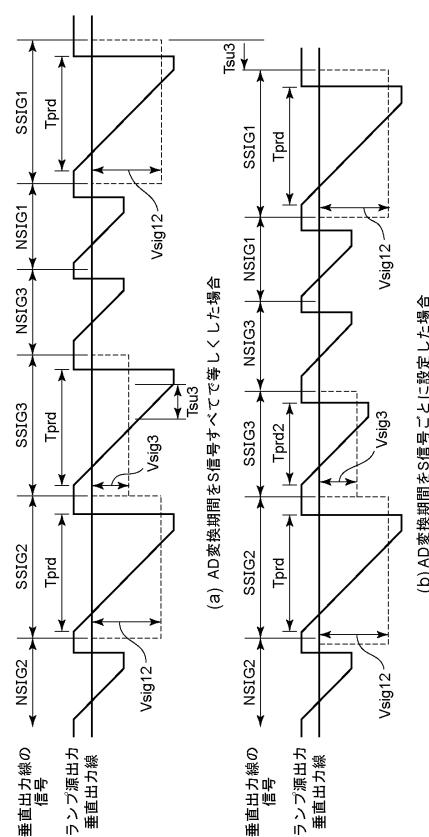

図 1 0 は図 9 に示した S 信号の電圧範囲において A D 変換を実施した場合のタイミングチャートの一例である。なお、図 1 0 のタイミングチャートに示した A D 変換の実施順番は図 4 のタイミングチャートに基づいている。

20

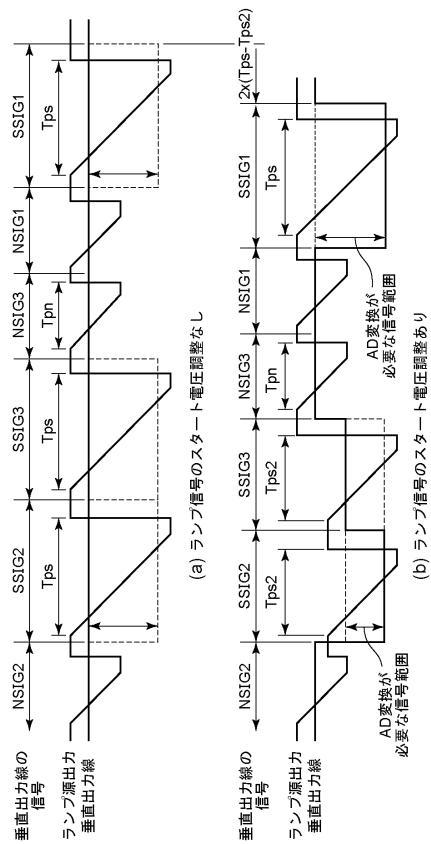

#### 【 0 1 0 7 】

図 1 0 ( a ) は S 信号すべての A D 変換期間が同じ場合を示したタイミングチャートである。この時の S 信号の A D 変換期間を T p r d とする。前述の通り、信号 S S I G 1 の扱う輝度範囲に対応する電圧の取りうる範囲の上限は V s i g 1 であり、信号 S S I G 2 と S S I G 3 の扱う輝度範囲に対応する電圧の取りうる範囲の上限の V s i g 2 3 より小さい。しかし、図 1 0 ( a ) の例では、各 S 信号の A D 変換において、ランプ源出力が同じ電圧振幅で掃引している。したがって、各 S 信号の A D 変換期間は全て T p r d である。図 9 に示す通り、信号 S S I G 1 の場合、扱う輝度範囲に対応する電圧の振幅が他の信号に比べて小さい。そのため、他の信号の場合と同じ振幅で掃引されるランプ源出力によつて A D 変換をすることは冗長である。換言すると、信号 S S I G 1 の場合、ランプ源出力が冗長な範囲を掃引するのに要する時間の分だけ、扱う電圧振幅に対して、A D 変換期間が長い。図示した通り期間 T s u に行われる動作は冗長であり、削減可能である。期間 T s u を削減した場合のタイミングチャートを図 1 0 ( b ) に示す。S S I G 1 の A D 変換期間を T s u 削減することで、1 行あたりの読み出し期間を T s u だけ短くすることができる。

30

#### 【 0 1 0 8 】

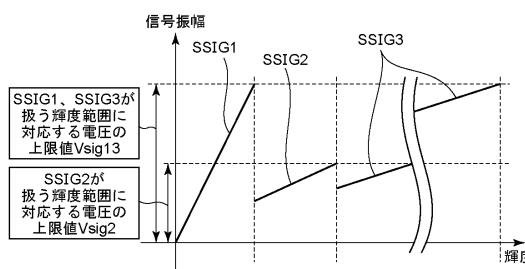

図 1 1 は、S 信号が扱う輝度範囲と信号電圧範囲を示した別の例である。

40

#### 【 0 1 0 9 】

この例では信号 S S I G 2 の扱う輝度範囲に対応する電圧の取りうる範囲の上限 V s i g 2 が、信号 S S I G 1 および S S I G 3 の扱う輝度範囲に対応する電圧の取りうる範囲の上限 V s i g 1 3 よりも小さい。

#### 【 0 1 1 0 】

図 1 2 ( a ) は、図 1 1 で示した電圧範囲を持つ各 S 信号について同一の A D 変換期間で A D 変換を行った場合を示したタイミングチャートである。信号 S S I G 2 の A D 変換において、扱う信号範囲 V s i g 2 に対して、A D 変換期間 T s u 2 に行われる動作は冗長であり、削減可能である。T s u 2 を削減した場合のタイミングチャートを図 1 2 ( b )

50

)に示す。

#### 【0111】

S S I G 2 の A D 変換期間を T s u 2 削減することで、1行の読み出し期間を T s u 2 だけ短くすることができる。

#### 【0112】

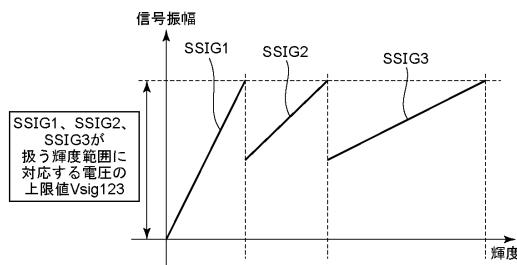

また、図 13 のように信号 S S I G 3 の扱う輝度範囲に対応する電圧の取りうる範囲の上限 V s i g 3 が、信号 S S I G 1、S S I G 2 が扱う輝度範囲に対応する電圧の取りうる範囲の上限 V s i g 1 2 よりも小さい場合も考えられる。

#### 【0113】

この場合でもこれまでと同様に信号 S S I G 3 の A D 変換期間を信号 S S I G 1、S S I G 2 の A D 変換期間よりも短縮することが可能である。図 13 に示した電圧範囲の S 信号について同一の A D 変換期間で A D 変換を実施した場合のタイミングチャートの一例を図 14 ( a )、冗長期間 T s u 3 を削減した場合のタイミングチャートを図 14 ( b )に示す。よって図 13 のような場合でも1行の読み出し期間の短縮が可能である。

10

#### 【0114】

これまでの説明では、1行当たりの読み出し時間を短縮することに着目してきた。前述の通り、各信号が取りうる電圧の上限値は等しい。一方、各信号が扱う電圧の下限から上限までの範囲は信号によって異なる。各信号の A D 変換に際して、ランプ信号は少なくとも各信号が扱う電圧の下限から上限までの範囲を掃引すればよい。上述の通り、少なくとも1つの信号については、当該1つの信号が扱う電圧の下限から上限までの範囲は、当該1つの信号が取りうる電圧の下限値から上限値までの電圧範囲よりも狭い。したがって、本実施例によって得られる効果の1つの側面は、ランプ信号の掃引する範囲を信号の取りうる電圧の範囲よりも狭くすることによっても実現できるといえる。この場合、複数の信号に対して行われる A D 変換の変換期間がすべて等しくてもよい。例えば、他の A D 変換の場合に比べて傾きの緩やかなランプ信号を用いて、ランプ信号の掃引する範囲を狭くする。これにより、読み出し時間の短縮の効果は必ずしも得られるわけではないが、より高い精度での変換が実現され、ひいては A D 変換の高性能化が可能である。

20

#### 【0115】

これまでの説明では、S 信号 3 種類のうち、1種類のみで A D 変換期間を短縮したが、例えば2種類で A D 変換期間を短縮してもよいし、各 S 信号で各々異なる A D 変換期間を設定してもよい。また、S 信号の短縮についてこれまで説明してきたが、N 信号も可能ならば、各々で異なる A D 変換期間を設定してもよい。

30

#### 【0116】

以上のように、本実施例は信号毎に振幅に応じた A D 変換期間を設定する。これにより受光面積の異なる複数のフォトダイオードと、容量を有する画素が配置された光電変換装置において、S 信号をすべて同一の A D 変換期間にした場合と比較して、1行の読み出し期間を短縮することができる。結果として、光電変換装置のアナログデジタル変換の高性能化が実現できる。

#### 【0117】

複数のフォトダイオードの配置例として図 3 を用いて説明したが、本実施例はそれに限定されない。光に対する感度が異なる複数の光電変換部であれば本実施例は適用可能であり、感度を異ならせる方法は遮光膜の開口面積を異ならせる、光吸収率の異なるフィルターを設置する、など、光電変換部の面積を異ならせることに限られない。

40

#### 【0118】

図 4 のタイミングチャートを用いて、画素回路の動作を説明したが、本実施例はそれに限定されるものではない。図 4 とは異なるタイミングでも、本実施例は適用可能である。

#### 【0119】

(実施例 2 )

本実施例について図面を用いて説明する。

本実施例においては各信号の A D 変換の分解能を異ならせることによって1行当たりの読

50

み出し時間を短縮する。第2の実施例の光電変換装置、画素回路構成とその動作は第1の実施例と同じであるため、重複する説明を省略し、主として実施例1と異なる部分を説明する。

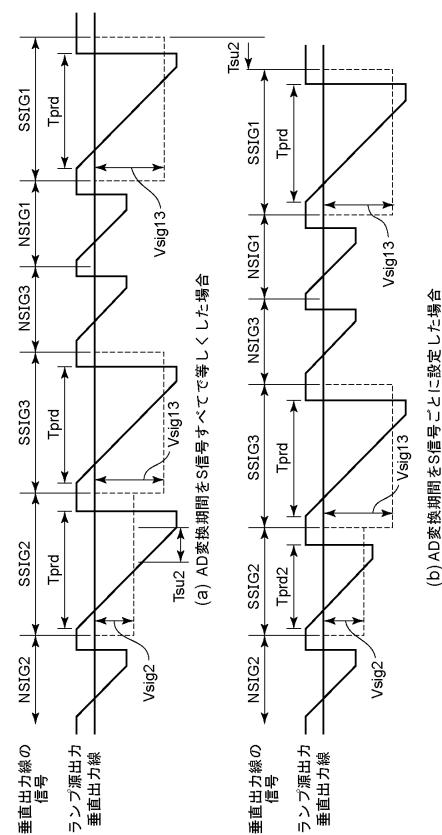

#### 【0120】

図15のようにS信号すべてで扱う輝度範囲に対応する電圧が取りうる範囲の上限が同じ場合について考える。図16(a)は図15に示した電圧範囲で、ランプ信号の傾きがすべて等しい、すなわち1 LSBあたりの電圧が等しくAD変換の分解能が等しい場合の、各信号のAD変換期間および順番を示したタイミングチャート例である。なお、信号のAD変換を実施する順番は図4に示したタイミングチャートに基づいている。

#### 【0121】

図16(a)に示したタイミングチャートでは、S信号すべてで等しい電圧振幅を扱い、ランプ信号の傾きも等しいため、S信号すべてについてのAD変換期間が等しくなっている。

#### 【0122】

前述の通り、高輝度側よりも低輝度側の方が、輝度の変化が視認されやすいことが知られている。よって、本実施例では、視認性の高い低輝度側のAD変換の分解能を高く、視認性の低い高輝度側ではAD変換の分解能を低くし、分解能に合わせてAD変換期間を設定することで、アナログデジタル変換の高性能化を実現する。

#### 【0123】

図16(b)は高輝度側の信号SSIG3とリセット信号NSIG3のAD変換の分解能を、他の信号よりも低くした場合のタイミングチャートである。分解能を低くする場合は、ランプ信号の傾きを急峻にして1 LSBあたりの電圧を大きくする。図16(b)では信号SSIG3とリセット信号NSIG3の分解能を低くしているため、図示した通り、ランプの傾きが急峻である。よってランプ源63出力が掃引を始めてから最大振幅の電位に到達するまでの期間が、分解能が高いときと比較して短くなるため、すべてのS信号を同一の分解能でAD変換していたときと比べAD変換期間を短縮可能である。

#### 【0124】

AD変換の分解能が高いときの信号SSIG3のAD変換期間をTpS、リセット信号NSIG3のAD変換期間をTpN、分解能が低いときの信号SSIG3のAD変換期間をTpS2、リセット信号NSIG3のAD変換期間をTpN2とする。このとき、信号SSIG3、NSIG3の分解能を低くすることで(TpS - TpS2 + TpN - TpN2)の期間を短縮でき、一行あたりの読み出し時間が短縮される。

#### 【0125】

なお、このとき視認性の高い低輝度側でAD変換の分解能を高く、視認性の低い高輝度側で分解能を低くしているので、画質への影響は小さい。また、画質を考慮しつつ、各信号のAD変換の分解能を設定してもよい。

#### 【0126】

これまでの説明では、S信号1種類とそのリセットレベルとなるN信号1種類でAD変換の分解能を低くする例で説明したが、例えば、S信号2種類とそれらのリセットレベルとなるN信号2種類でAD変換分解能を異ならせててもよい。また、中間輝度を扱う信号SSIG2とリセット信号NSIG2のAD変換分解能を、低輝度側の信号SSIG1およびNSIG1のAD変換分解能より低く、かつ高輝度側の信号SSIG3およびNSIG3のAD変換分解能より高くすることも可能である。このように2つ以上のS信号およびN信号でAD変換分解能を低くしたり、信号ごとにAD変換分解能を設定したりすることで、さらに1行の読み出し期間の短縮が可能であり、高フレームレート化が期待できる。

#### 【0127】

本実施例では、AD変換の分解能を信号ごとで設定することで、AD変換期間の短縮を実現するが、実施例1で説明した、AD変換期間を信号振幅によって設定する技術を併用してもよい。例えば信号SSIG1とSSIG2はAD変換の分解能は等しいが、AD変換期間が異なり、信号SSIG3のAD変換の分解能をSSIG1やSSIG2よりも低

10

20

30

40

50

くすることなどが考えられる。

#### 【0128】

A D変換の分解能が信号ごとに異なる場合は、各信号のA D変換の諧調を、例えば低輝度側の諧調を12ビット、高輝度側を10ビット、その間の中間輝度を11ビットとするなど、それぞれで設定してもよい。

#### 【0129】

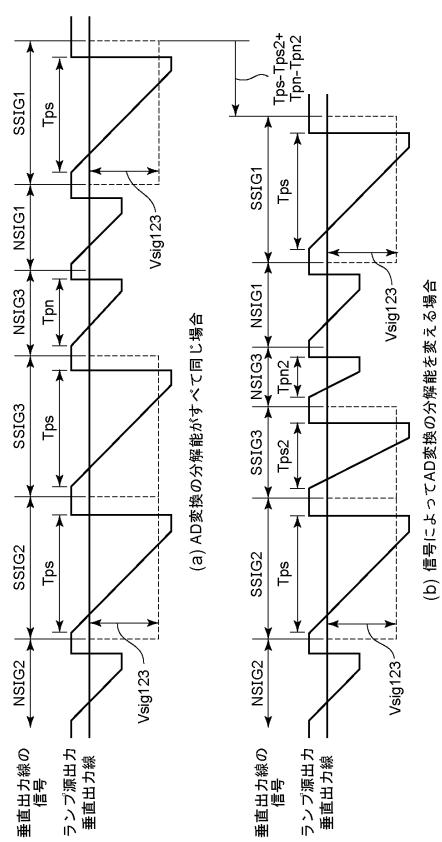

##### (実施例3)

本実施例について図面を用いて説明する。本実施例においてはランプ信号の掃引開始時の電位にオフセットを付与することによって1行当たりの読み出し時間を短縮する。第3の実施例の光電変換装置、画素回路構成とその動作は第1の実施例と同じであるため、重複する説明を省略し、主として実施例1と異なる部分を説明する。

10

#### 【0130】

図15のようにS信号すべてが取りうる電圧の上限が同じ場合について考える。図17(a)は図15に示した電圧範囲で、ランプ信号の傾きとランプ信号の掃引開始時の電位がすべて等しい場合の、各信号のA D変換期間および順番を示したタイミングチャート例である。なお、信号のA D変換を実施する順番は図4に示したタイミングチャートに基づいている。

#### 【0131】

図17(a)に示したタイミングチャートでは、S信号すべてで等しい電圧振幅を扱い、ランプ信号の傾きと掃引開始時の電位も等しいため、S信号すべてのA D変換期間が等しくなっている。

20

#### 【0132】

図15において、信号SSIG1, SSIG2, SSIG3がいずれも電圧範囲Vsig123を扱う場合を説明する。前述の通り信号SSIG2の扱いうる輝度範囲のうち信号SSIG1と重複する輝度範囲については信号SSIG1で扱われ、信号SSIG2の情報は使用されない。同様に信号SSIG3の扱いうる輝度範囲のうち信号SSIG2と重複する輝度範囲については信号SSIG2で扱われ、信号SSIG3の情報は使用されない。つまり信号SSIG2の扱いうる輝度範囲のうち信号SSIG1と輝度範囲が重複する範囲及び信号SSIG3の扱いうる輝度範囲のうち信号SSIG2と輝度範囲が重複する範囲に関してのA D変換は冗長である。よって、本実施例では、ランプ信号の掃引開始時の電位にオフセットを設定し、各信号の情報が使用される輝度についてのみA D変換を行うこととする。例えば、信号SSIG2をA D変換するために用いるランプ信号を、信号SSIG1をA D変換するために用いるランプ信号にオフセットを付与した信号とし、信号SSIG1と重複する輝度範囲の信号についてA D変換を行わない。これによって、重複する輝度範囲についてのA D変換に要する期間の分、1行当たりのA D変換に要する期間を短縮でき、アナログデジタル変換の高性能化を実現できる。

30

#### 【0133】

図17(b)は信号SSIG2及び信号SSIG3のA D変換にあたりランプ信号の開始時点の電位を調整した場合のタイミングチャートである。図17(b)に図示した通り、輝度範囲が重複しA D変換結果を使用しない範囲に関してはA D変換を行わないため、すべてのS信号を同一の電位から掃引を始めるランプ信号でA D変換していたときと比べ、A D変換期間を短縮可能である。

40

#### 【0134】

また、本実施例はランプ信号が掃引を始めるときの電位が信号毎に異なると説明することもできる。図15の3つのS信号はすべて取りうる電圧の上限が同じであるが、各信号が扱う輝度範囲に対応する電圧の下限はそれぞれ異なる。各信号をA D変換するにあたり、ランプ信号は少なくとも各信号の電圧範囲の下限から上限までを掃引すればよい。したがって、ランプ信号が掃引を始めるときの電位を、対応する信号の扱う輝度範囲に対応する電圧の下限に対応させることで信号毎に異ならせてよい。

#### 【0135】

50

A D変換のランプ信号の開始時の電位がすべて等しいときの信号SSIG1～3のA D変換期間をTp s、ランプ信号の開始時の電位を調整したときの信号SSIG2、SSIG3のA D変換期間をTp s2とする。このとき信号SSIG3、NSIG3の分解能を低くすることで(Tp s - Tp s2 + Tpn - Tpn2)の期間を短縮でき、一行あたりの読み出し時間が短縮される。

#### 【0136】

また、ここまで図17(b)に基づいて動作を説明してきたが、本発明はそれに限定されない。例えば、他の信号のA D変換結果を使用する範囲に関してはランプ信号の単位時間当たりの変化率を相対的に大きくし、A D変換した結果を使用する範囲についてA D変換を行う際はランプ信号の時間当たりの変化率を相対的に小さく変化させてもよい。

10

#### 【0137】

##### (実施例4)

本実施例について図面を用いて説明する。本実施例においては各信号を増幅し、信号毎にA D変換に要する期間を異らせることによって1行当たりの読み出し時間を短縮する。第4の実施例の画素回路構成とその動作は第1の実施例と同じであるため、重複する説明を省略し、主として実施例1と異なる部分を説明する。

#### 【0138】

図18は本発明にかかる光電変換装置の一例を示す概略図である。図18の光電変換装置と、図1の光電変換装置で異なる点は、比較回路64と垂直出力線12の間に列アンプ150を配置している点である。列アンプ150は垂直出力線12の信号を増幅して比較回路64に入力する増幅回路の一例である。なお、列アンプ150は反転アンプで、そのゲインは可変であるものとする。また、図4と重複する回路においては前述のため説明を省略する。

20

#### 【0139】

図19は図18に示した光電変換装置において、ある光量の光がフォトダイオードPD1およびPD2に入射されたときのA D変換の動作を説明するタイミングチャートである。図19に示したタイミングチャートでは列アンプが反転アンプなので、垂直出力線の電位が反転して出力される。よって図示したように、ランプ源63出力も同様に、これまでに説明してきた列アンプ150がない場合のランプ源63出力を反転した信号となる。つまり、A D変換中のランプ源63出力は時間の経過とともに電位が上昇するランプ信号となる。

30

#### 【0140】

この例では、信号SSIG3およびリセット信号NSIG3のA D変換において、実施例2で説明したA D変換の分解能を他の信号よりも低くする技術を用いて、1行の読み出し期間を短縮している。列アンプの増幅ゲインをAとし、垂直出力線12の信号を増幅させる。信号SSIG2の振幅をV2とすると、列アンプ出力の信号振幅はA×V2となり、信号SSIG3の振幅をV3とすると、アンプ出力の信号振幅はA×V3、信号SSIG1の振幅をV1とすると、列アンプ出力の信号振幅はA×V1となる。N信号についても対応するS信号と同じゲインで列アンプ出力の信号振幅を増幅される。

30

#### 【0141】

本実施例のように列アンプがある場合でも、各信号の扱う信号振幅によっては、A D変換の分解能は変更せずに、A D変換期間のみを信号によって異らせることも可能である。また、A D変換の分解能を変更せずにA D変換期間を短縮する信号と、A D変換の分解能を変更してA D変換期間を短縮する信号があつてもよい。例えば信号SSIG1とSSIG2はA D変換の分解能は等しいが、A D変換期間が異なり、信号SSIG3のA D変換の分解能を信号SSIG1やSSIG2よりも低くすることなどが考えられる。

40

#### 【0142】

また、列アンプ150のゲインは各信号で異なっていてもよい。例えば、ノイズが視認されやすい低輝度側の信号である信号SSIG1およびリセット信号NSIG1のゲインを、他の信号のゲインよりも大きくすることも可能である。ゲインを大きくし、画素信号

50

を大きくすることで、列アンプ 150 や比較回路 64 のノイズが画素信号及び画素ノイズと比較して相対的に小さくなるので、S/N 比の向上が見込める。

#### 【0143】

また、図 7 にも示したように各 S 信号の輝度と信号振幅の関係から、列アンプで増幅された各信号の振幅が同等になるように設定してもよい。例えば、輝度に対する信号振幅が最も大きい信号 SSIG1 と対応するリセット信号 NSIG1 のゲインを最も小さく、輝度に対する信号振幅が最も小さい信号 SSIG3 と対応するリセット信号 NSIG3 のゲインを最も大きくする。また、信号 SSIG2 とリセット信号 NSIG2 のゲインをその中間にする。このように、列アンプのゲインを信号ごとに設定することによって、列アンプ出力の振幅を信号によらずおおよそ等しくすることができる。これにより、特定の信号で振幅が著しく小さくなり、アナログデジタル変換において冗長な動作が発生することを防ぐことができる。換言すればアナログデジタル変換の高性能化が実現できる。

#### 【0144】

##### (実施例 5)

本実施例について図面を用いて説明する。本実施例においては 1 行当たりの読み出し期間を保ったまま A/D 変換の分解能を設定することによって A/D 変換期間を最適化する。第 5 の実施例の光電変換装置、画素回路構成とその動作は第 1 の実施例と同じであるため、重複する説明を省略し、主として実施例 1 と異なる部分を説明する。

#### 【0145】

前述の通り、図 10 (a) のタイミングチャートでは S 信号すべての A/D 変換期間が同じであり、信号 SSIG1 の場合、期間 Tsu における動作が冗長である。本実施例では、期間 Tsu に合わせて信号 SSIG1 の分解能を設定することで A/D 変換期間の最適化を実現する。冗長期間 Tsu に合わせて信号 SSIG1 の分解能を他の信号よりも高く設定した場合のタイミングチャートを図 20 に示す。分解能を高くする場合は、ランプ信号の傾きを緩やかにして LSBあたりの電圧を小さくする。図 20 では信号 SSIG1 とリセット信号 NSIG1 の分解能を高くしているため、図示した通り、ランプの傾きが緩やかである。よってランプ源 63 出力が掃引を始めてから最大振幅の電位に到達するまでの期間は分解能が低いときと比較して長くなるため、期間 Tsu を活用することができ、1 行の読み出し期間は変わらないままで低輝度側の画質を高めることができる。

#### 【0146】

また、本実施例において信号 SSIG1 の A/D 変換のためにランプ信号を掃引した範囲 Vsig1 は少なくとも Vsig2 3 よりも狭く、各信号が取りうる電圧の範囲よりも狭い。したがって実施例 5 は、ランプ信号の掃引する振幅範囲を信号の取りうる電圧の範囲よりも狭くすることによっても実現できるといえる。

#### 【0147】

実施例 1 から 5 まで図 1 や図 18 の光電変換装置の概略図を用いて説明したが、本発明は 1 枚の半導体基板上に図 1 や図 18 に記載された回路をすべて配置してもよい。また、図 21 に示したように回路を 2 つ以上の基板に配置して、それらの基板を貼り合わせた積層構造にしてもよい。図 21 に示した積層構造の光電変換装置は第 1 基板 170 と第 2 基板 171 からなる。

#### 【0148】

なお、図 21 に示した積層構造の光電変換装置は、図 1 に示した概略図を 2 枚の基板に分けた場合の一例である。この例では第 1 基板 170 は画素部 60 と電流源群 61 が配置される。第 2 基板 171 には全列分の比較回路 64 からなる比較回路群 640 と、全列分の列メモリ 65 からなるメモリ群、演算処理部 66 が配置されている。なお、図面で省略しているが、第 2 基板 171 にはランプ源 63 やカウンタ回路 67 も配置される。また図 18 で示した光電変換装置のように、全列分の列アンプ 150 を第 1 基板 170 か第 2 基板 171 のどちらかに配置してもよい。図 21 の積層構造の光電変換装置は一例であって、本発明を限定するものではない。例えば、比較回路群 640 を第 1 基板に配置してもよい。また、図 21 の例では第 1 基板と第 2 基板が列ごとで電気的に接続されるが、例えば

画素ごとに接続されてもよい。図21では2枚の積層構造で説明したが、例えばさらに回路を分類するか、回路や機能を追加するなどして3枚の積層構造にしてもよい。

#### 【0149】

図1や図18ではランプ源63出力を比較回路64の入力に接続しているが、ランプ源63出力と比較回路64の間に列ごと、または複数列に共有のバッファ回路を配置し、ランプ源63出力の信号をバッファして比較回路64に入力してもよい。

#### 【0150】

実施例1から実施例5まで、A/D変換の方式をロープ型A/Dとして説明してきたが、本発明はそれに限定されない。例えば、A/D変換の方式を逐次比較方式として逐次比較の回数をカウントしてもよいし、使用できるならば他のA/D変換方式でもよい。

10

#### 【0151】

実施例1から実施例5まで、図4のタイミングチャートに基づいて動作を説明してきたが、本発明はそれに限定されない。例えば、各信号をサンプルホールドする機構を設けて、サンプルホールドされた信号をA/D変換している間に、垂直出力線12にはそれとは異なる信号を出力していくてもよい。

#### 【0152】

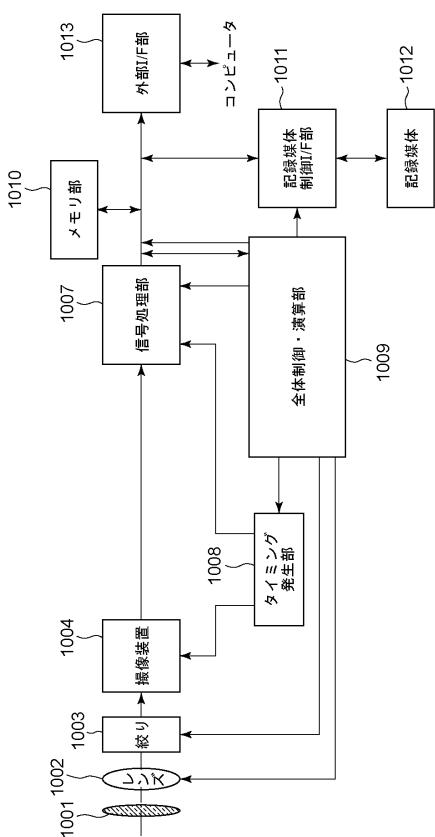

##### (実施例6)

撮像システムの実施例について説明する。撮像システムとして、デジタルスチルカメラ、デジタルカムコーダ、カメラヘッド、複写機、ファックス、携帯電話、車載カメラ、観測衛星などがあげられる。図26に、撮像システムの例としてデジタルスチルカメラのブロック図を示す。

20

#### 【0153】

図26において、1001はレンズの保護のためのバリアである。1002は被写体の光学像を撮像装置1004に結像させるレンズである。1003はレンズ1002を通った光量を可変するための絞りである。撮像装置1004には、上述の各実施例で説明した撮像装置が用いられる。

#### 【0154】

1007は撮像装置1004より出力された画素信号に対して、補正やデータ圧縮などの処理を行い、画像信号を取得する信号処理部である。そして、図26において、1008は撮像装置1004および信号処理部1007に、各種タイミング信号を出力するタイミング発生部、1009はデジタルスチルカメラ全体を制御する全体制御部である。1010は画像データを一時的に記憶する為のフレームメモリ部である。1011は記録媒体に記録または読み出しを行うためのインターフェース部である。1012は撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体である。1013は外部コンピュータ等と通信する為のインターフェース部である。

30

#### 【0155】

なお、撮像システムは少なくとも撮像装置1004と、撮像装置1004から出力された画素信号を処理する信号処理部1007とを有すればよい。その場合、他の構成は撮像システムの外部に配される。

#### 【0156】

40

以上に説明した通り、撮像システムの実施例において、撮像装置1004には、第1の実施例、乃至、第5の実施例のいずれかの撮像装置が用いられる。このような構成によれば、撮像装置から得られる画像のダイナミックレンジを拡大させることができる。

#### 【0157】

##### (実施例7)

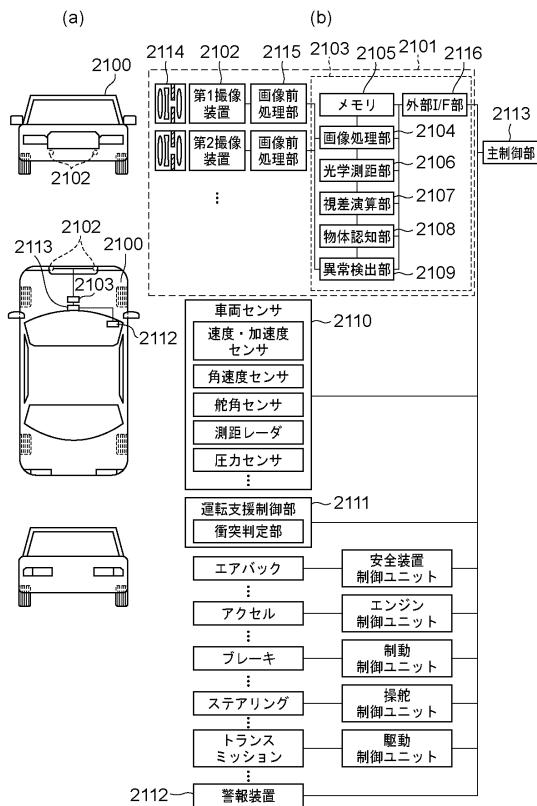

移動体の実施例について説明する。本実施例の移動体は、車載カメラを備えた自動車である。図27(a)は、自動車2100の外観と主な内部構造を模式的に示している。自動車2100は、撮像装置2102、撮像システム用集積回路(ASIC: Application Specific Integrated Circuit)2103、警報装置2112、主制御部2113を備える。

50

**【 0 1 5 8 】**

撮像装置 2102 には、上述の各実施例で説明した撮像装置が用いられる。警報装置 2112 は、撮像システム、車両センサ、制御ユニットなどから異常を示す信号を受けたときに、運転手へ向けて警告を行う。主制御部 2113 は、撮像システム、車両センサ、制御ユニットなどの動作を統括的に制御する。なお、自動車 2100 が主制御部 2113 を備えていなくてもよい。この場合、撮像システム、車両センサ、制御ユニットが個別に通信インターフェースを有して、それぞれが通信ネットワークを介して制御信号の送受を行う（例えば CAN 規格）。

**【 0 1 5 9 】**

図 27 (b) は、自動車 2100 のシステム構成を示すブロック図である。自動車 2100 は、第 1 の撮像装置 2102 と第 2 の撮像装置 2102 を含む。つまり、本実施例の車載カメラはステレオカメラである。撮像装置 2102 には、光学部 2114 により被写体像が結像される。撮像装置 2102 から出力された画素信号は、画像前処理部 2115 によって処理され、そして、撮像システム用集積回路 2103 に伝達される。画像前処理部 2115 は、S-N 演算や、同期信号付加などの処理を行う。

10

**【 0 1 6 0 】**

撮像システム用集積回路 2103 は、画像処理部 2104、メモリ 2105、光学測距部 2106、視差演算部 2107、物体認知部 2108、異常検出部 2109、および、外部インターフェース (I/F) 部 2116 を備える。画像処理部 2104 は、画素信号を処理して画像信号を生成する。また、画像処理部 2104 は、画像信号の補正や異常画素の補完を行う。メモリ 2105 は、画像信号を一時的に保持する。また、メモリ 2105 は、既知の撮像装置 2102 の異常画素の位置を記憶していくてもよい。光学測距部 2106 は、画像信号を用いて被写体の合焦または測距を行う。視差演算部 2107 は、視差画像の被写体照合（ステレオマッチング）を行う。物体認知部 2108 は、画像信号を解析して、自動車、人物、標識、道路などの被写体の認知を行う。異常検出部 2109 は、撮像装置 2102 の故障、あるいは、誤動作を検知する。異常検出部 2109 は、故障や誤動作を検知した場合には、主制御部 2113 へ異常を検知したことを示す信号を送る。外部 I/F 部 2116 は、撮像システム用集積回路 2103 の各部と、主制御部 2113 あるいは種々の制御ユニット等との間での情報の授受を仲介する。

20

**【 0 1 6 1 】**

30

自動車 2100 は、車両情報取得部 2110 および運転支援部 2111 を含む。車両情報取得部 2110 は、速度・加速度センサ、角速度センサ、舵角センサ、測距レーダ、圧力センサなどの車両センサを含む。

**【 0 1 6 2 】**

運転支援部 2111 は、衝突判定部を含む。衝突判定部は、光学測距部 2106、視差演算部 2107、物体認知部 2108 からの情報に基づいて、物体との衝突可能性があるか否かを判定する。光学測距部 2106 や視差演算部 2107 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。

40

**【 0 1 6 3 】**

運転支援部 2111 が他の物体と衝突しないように自動車 2100 を制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。

**【 0 1 6 4 】**

自動車 2100 は、さらに、エアバッグ、アクセル、ブレーキ、ステアリング、トランスマッision 等の走行に用いられる駆動部を具備する。また、自動車 2100 は、それらの制御ユニットを含む。制御ユニットは、主制御部 2113 の制御信号に基づいて、対応

50

する駆動部を制御する。

【0165】

本実施例に用いられた撮像システムは、自動車に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

【0166】

以上に説明した通り、自動車の実施例において、撮像装置2102には、第1の実施例、乃至、第5の実施例のいずれかの撮像装置が用いられる。このような構成によれば、撮像装置から得られる画像のダイナミックレンジを拡大させることができる。

10

【符号の説明】

【0167】

10 画素回路

11 電流源

12 垂直出力線

60 画素部

61 電流源群

63 ランプ源

64 比較回路

65 列メモリ

66 演算処理部

67 カウンタ回路

150 列アンプ

170 第1基板

171 第2基板

P D 1 第1のフォトダイオード

P D 2 第2のフォトダイオード

20

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

20

30

40

50

【図 5】

【図 6】

10

20

30

40

【図 7】

【図 8】

50

【図 9】

【図 10】

10

20

30

40

【図 11】

【図 12】

50

【図 1 3】

【図 1 4】

10

20

30

40

【図 1 5】

【図 1 6】

50

【図 17】

【図 18】

【図 19】

【図 20】

【図 2 1】

【図 2 2】

10

20

30

40

【図 2 3】

50

---

フロントページの続き

キヤノン株式会社内

審査官 三沢 岳志

- (56)参考文献

- 米国特許出願公開第2017/0324917(US, A1)

特開2013-211832(JP, A)

特開2014-075767(JP, A)

特開2019-062398(JP, A)

国際公開第2017/018215(WO, A1)

特開2001-267543(JP, A)

特開2007-329721(JP, A)

国際公開第2017/138370(WO, A1)

Manuel Innocent, et al., "Pixel with nested photo diodes and 120 db single exposure dynamic range", International Image Sensor Workshop, 2019年06月, pp.95-98

- (58)調査した分野 (Int.Cl., DB名)

- H04N 25/78

H04N 25/585

H04N 25/771

H04N 25/76