US008492173B2

## (12) United States Patent Maki et al.

## (10) **Patent No.:**

US 8,492,173 B2

(45) **Date of Patent:**

Jul. 23, 2013

#### (54) MANUFACTURING METHOD FOR SEMICONDUCTOR INTEGRATED DEVICE

(71) Applicant: Renesas Electronics Corporation,

Kawasaki (JP)

(72) Inventors: Hiroshi Maki, Tokyo (JP); Tsuyoshi

Yokomori, Tokyo (JP); Tatsuyuki

Okubo, Tokyo (JP)

(73) Assignee: Renesas Electonics Corporation,

Kawasaki-shi (JP)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 13/742,788

(22) Filed: Jan. 16, 2013

#### (65) **Prior Publication Data**

US 2013/0130408 A1 May 23, 2013

#### Related U.S. Application Data

(62) Division of application No. 13/533,963, filed on Jun. 26, 2012, now Pat. No. 8,372,665, which is a division of application No. 13/208,171, filed on Aug. 11, 2011, now Pat. No. 8,222,050, which is a division of application No. 12/987,779, filed on Jan. 10, 2011, now Pat. No. 8,003,495, which is a division of application No. 12/137,522, filed on Jun. 11, 2008, now Pat. No. 7,888,141.

### (30) Foreign Application Priority Data

| Jun. 19, 2007 | (JP) | 2007-160922 |

|---------------|------|-------------|

| Jun. 22, 2007 | (JP) | 2007-164820 |

| Anr 8 2008    | (IP) | 2008-099965 |

(51) **Int. Cl.**

H01L 21/00

(2006.01)

(52) **U.S. Cl.**

####

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 6,352,073    | В1   | 3/2002  | Kurosawa et al.  |

|--------------|------|---------|------------------|

| 7,115,482    | B2   | 10/2006 | Maki et al.      |

| 7,888,141    | B2   | 2/2011  | Maki et al.      |

| 8,372,665    | B2 * | 2/2013  | Maki et al 438/5 |

| 2002/0026931 | A1   | 3/2002  | Kurosawa et al.  |

| 2002/0129899 | A1   | 9/2002  | Mimata et al.    |

| 2005/0061856 | A1   | 3/2005  | Maki et al.      |

| 2005/0200142 | A1   | 9/2005  | Isetani et al.   |

| 2006/0252233 | A1   | 11/2006 | Honma et al.     |

| 2007/0275544 | A1   | 11/2007 | Maki et al.      |

| 2007/0287262 | A1   | 12/2007 | Maki et al.      |

|              |      |         |                  |

#### FOREIGN PATENT DOCUMENTS

| JP | 2000-208447 | 7/2000 |

|----|-------------|--------|

| JP | 2002-270542 | 9/2002 |

(Continued)

#### OTHER PUBLICATIONS

Office Action dated Dec. 6, 2012 in Japanese Patent Application 2011-245323.

Primary Examiner — Richard Booth (74) Attorney, Agent, or Firm — Miles & Stockbridge P.C.

#### (57) ABSTRACT

In a chip pick-up process after dicing in an assembly process during manufacture of a semiconductor integrated circuit device it is an important subject to diminish a pick-up defect caused by the reduction in thickness of each chip which is proceeding in quick tempo. Particularly, bending of the chip peripheral portion caused by a peeling operation is very likely to induce cracking and chipping of the chip. In the present invention, to solve these problems, in case of peeling a chip from a dicing tape (adhesive tape) or the like while vacuum-chucking the chip by a chucking collet, the flow rate of a vacuum chucking system in the chucking collet is monitored to check a bent state of the chip before complete separation of the first chip from the adhesive tape.

#### 4 Claims, 72 Drawing Sheets

# **US 8,492,173 B2**Page 2

|     | FOREIGN PATENT DOCUMENTS | JP        | 2005-117019 A | 4/2005  |

|-----|--------------------------|-----------|---------------|---------|

| JP  | 2002-299418 10/2002      | JP        | 2005-150311 A | 6/2005  |

| JР  | 2003-133791 A 5/2003     | JР        | 2005-322815 A | 11/2005 |

| JР  | 2004-022995 A 1/2004     | JР        | 2006-165188 A | 6/2006  |

| JР  | 2004-023027 A 1/2004     | JP        | 2007-103777 A | 4/2007  |

| JP  | 2004-186352 A 7/2004     | WO        | 10-004258 A   | 1/1998  |

| JP  | 2004-009166 A 1/2005     |           |               |         |

| JP. | 2005-093838 A 4/2005     | * cited l | ov examiner   |         |

FIG.5

FIG. 6

FIG.9

FIG. 11

FIG.13

FIG. 14

FIG.15

FIG. 16

FIG.17

FIG. 18

FIG.19

FIG.20

FIG.21

**FIG.22**

FIG. 23

FIG.24

FIG.25

**FIG.26**

FIG.30

Vacuum Supply Source 107 Pickup section control system <u>144</u> **Q** 141 Analog Signal Digital Signal 143 Set Value FIG. 31 Lime 105 102 Digital Signal Analog Signal ۍـ Sensor Output Leak (incl. open condition) No leak Approx. "0" Suction (a)

മ 121 **Q** 105 FIG. 32 ⋖ മ (a)

<u>m</u> 121 **Q** 105 FIG.33 ⋖ മ A - 106b

FIG. 34

FIG.35 122 106a 121 105 125 102a 103 110a 110c 110b

121 **a** 105 FIG. 36 (a) 106w 106b /

FIG. 37

106a

122

106b

106c

106c

106k

125

110a

110a

Jul. 23, 2013

**FIG.39**

**FIG.40**

FIG. 45

FIG.46

FIG. 47

FIG. 49

FIG. 50

FIG. 51

**FIG.53**

**FIG.54**

**FIG.55**

FIG.56

FIG. 57

FIG. 58

FIG. 59

FIG. 60

FIG. 61

**FIG. 66**

# MANUFACTURING METHOD FOR SEMICONDUCTOR INTEGRATED DEVICE

#### CLAIM OF PRIORITY

The present application claims priority from Japanese applications JP 2007-160922 filed on Jun. 19, 2007, JP 2007-164820 filed on Jun. 22, 2007 and JP 2008-099965 filed on Apr. 8, 2008, the contents of which are hereby incorporated by reference into this application.

## FIELD OF THE INVENTION

The present invention relates to a technique applicable effectively to the die bonding technique or chip peeling technique (die pickup technique) in a manufacturing method for a semiconductor integrated circuit device (or a semiconductor device).

#### BACKGROUND OF THE INVENTION

In Japanese patent laid-open No. 2005-322815 (Patent Literature 1) there is disclosed a die bonding technique wherein die bonding is performed using a convex collet having elasticity, vacuum suction of the collet is released into atmospheric pressure to remove the chucking force for the chip, and the collet is raised in this state.

In Japanese patent laid-open No. Hei 10 (1998)-004258 (Patent Literature 2) there is disclosed a chip mounting technique wherein a through hole is formed in one side face of a 30 collet for mounting a chip or the like to prevent solder from being sucked up during the mounting work.

In Japanese patent laid-open No. 2006-165188 (Patent Literature 3) there is disclosed a die bonding technique wherein vacuum suction holes are formed in only the peripheral portion of a collet rubber chip (hardness JIS-A60) having elasticity so as not to let voids remain in a thin-film chip and die bonding is preformed in a downwardly convex state of the chip.

In Japanese patent laid-open No. 2004-022995 (Patent Literature 4) or No. 2005-150311 (Patent Literature 5) there is disclosed a convex collet having elasticity.

In Japanese patent laid-open No. 2005-093838 (Patent Literature 6) or US patent laid-open No. 2005-0061856 (Patent Literature 7) there is disclosed a die bonding technique 45 wherein temporary pressure bonding and eternal pressure bonding are carried out in separate stages.

In Japanese patent laid-open No. 2005-9166 (Patent Literature 8) or US patent laid-open No. 2005-0200142 (Patent Literature 9) it is disclosed that, in connection with a chuck-50 ing nozzle such as an electronic part mounter, whether a part has been chucked or not is detected on the basis of a change in flow rate detected by an air flow sensor.

In Japanese patent laid-open No. 2003-133791 (Patent Literature 10), No. 2004-23027 (Patent Literature 11), or No. 55 2007-103777 (Patent Literature 12), it is disclosed that, when chucking and conveying an electronic part by a chucking nozzle such as an electronic part mounter, whether the part is in a properly chucked state or not is detected on the basis of a change in flow rate detected by an air flow sensor.

In Japanese patent laid-open No. 2004-186352 (Patent Literature 13) or US patent laid-open No. 2006-0252233 (Patent Literature 14) it is disclosed that, in connection with picking up a thin-film chip after wafer dicing, when applying ultrasonic oscillation from below a dicing tape and peeling the 65 chip from an adhesive sheet (dicing tape) from above by a chucking collet, a chucking flow rate of the chucking collet is

2

measured to make sure whether the chip was completely separated from the dicing tape and chucked by the chucking collet

In Japanese patent laid-open No. 2005-117019 (Patent Literature 15) or U.S. Pat. No. 7,115,482 (Patent Literature 16) it is disclosed that, in connection with picking up a thin-film chip after wafer dicing, a lower surface of the chip is stuck up from below a dicing tape by a stick-up mechanism and the chip is peeled from an adhesive sheet (dicing tape) from above by a chucking collet.

## PATENT LITERATURES

- 1. Japanese patent laid-open No. 2005-322815

- 5 2. Japanese patent laid-open No. Hei 10 (1998)-004258

- 3. Japanese patent laid-open No. 2006-165188

- 4. Japanese patent laid-open No. 2004-022995

- 5. Japanese patent laid-open No. 2005-150311

- 6. Japanese patent laid-open No. 2005-093838

- 20 7. US patent laid-open No. 2005-0061856

- 8. Japanese patent laid-open No. 2005-9166

- 9. US patent laid-open No. 2005-0200142

- 10. Japanese patent laid-open No. 2003-133791

- 11. Japanese patent laid-open No. 2004-23027

- 12. Japanese patent laid-open No. 2007-103777

- 13. Japanese patent laid-open No. 2004-186352

- 14. US patent laid-open No. 2006-0252233

- 15. Japanese patent laid-open No. 2005-117019

- 16. U.S. Pat. No. 7,115,482

#### SUMMARY OF THE INVENTION

in a chip pick-up process or a die bonding process after dicing in an assembly process during manufacture of a semi-conductor integrated circuit device, it is now an important subject to diminish a pick-up defect or a die bonding defect caused by the reduction in thickness of each chip which is proceeding in quick tempo. Particularly, according to investigations made by the present inventors it has become clear that bending of a chip peripheral portion resulting from a peeling operation is very likely to cause cracking or chipping of the chip and that the formation of voids caused by a vacuum chucking operation of a collet in die bonding is unignorable. The present invention has been accomplished for solving these problems.

It is an object of the present invention to provide a highly reliable manufacturing process for a semiconductor integrated circuit device.

The above and other objects and novel features of the present invention will become apparent from the following description and the accompanying drawings.

The following is an outline of typical inventions as dis-

According to one aspect of the present invention, in case of vacuum-chucking and peeling a chip from a dicing tape (adhesive tape) or the like with use of a chucking collet, the flow rate of a vacuum chucking system in the chucking collet is monitored to monitor the state of bending of the chip before complete separation of the first chip from the adhesive tape.

According to another aspect of the present invention, in case of vacuum-chucking and peeling a chip from a dicing tape (adhesive tape) or the like with use of a chucking collet or in case of vacuum-chucking a chip by a collet and performing die bonding, the vacuum-chucking operation of the chucking collet is stopped in an early stage to avoid the formation of voids which is attributable to the state of bending caused by vacuum chucking of the chip in die bonding.

The following is a brief description of effects obtained by the typical inventions as disclosed herein.

In the one aspect of the present invention, since the state of bending of the chip before complete separation from the adhesive tape can be monitored by monitoring the flow rate of 5 the vacuum chucking system in the chucking collet, it is possible to provide a pick-up process free of cracking or chipping.

In the other aspect of the present invention, in case of vacuum-chucking the chip with a collet and performing die 10 bonding, the vacuum-chucking operation of the chucking collet is stopped in an early stage, allowing the chip to land in the state of atmospheric pressure, thus permitting the provision of a die bonding process with few voids.

## BRIEF DESCRIPTION OF THE DRAWINGS

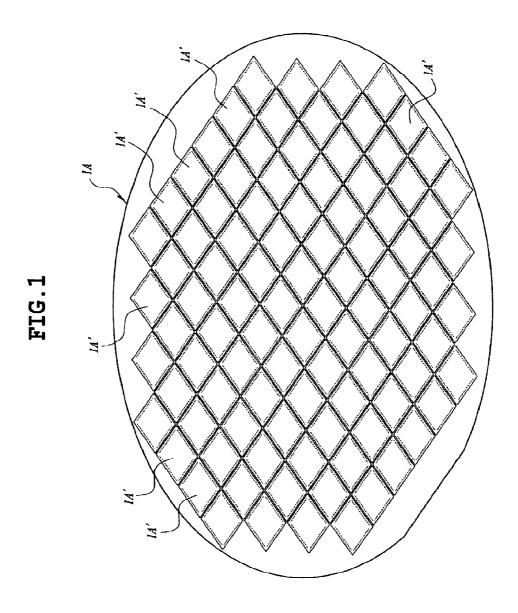

- FIG. 1 is a perspective view of semiconductor chips used in a method for manufacturing a semiconductor integrated circuit device according to an embodiment of the present invention:

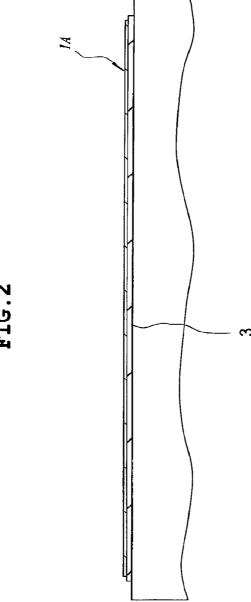

- FIG. 2 is a side view showing a semiconductor wafer grinding process;

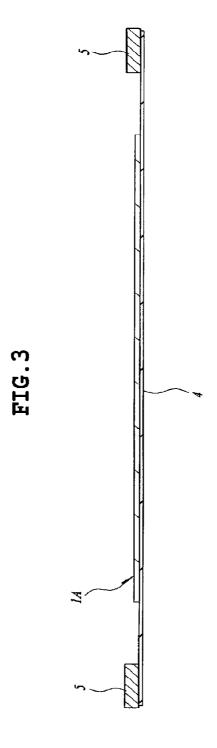

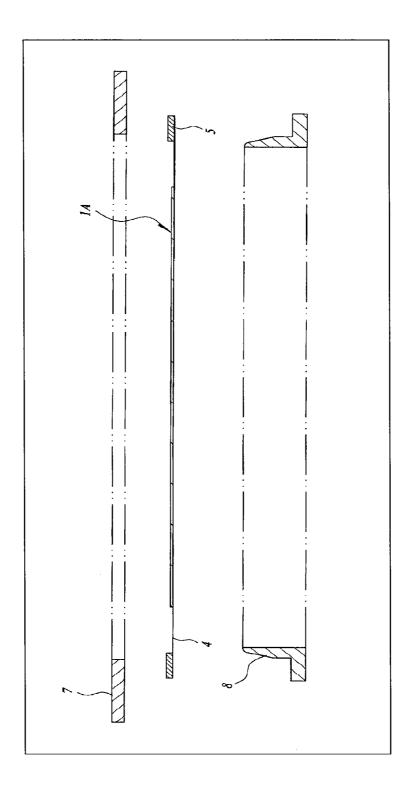

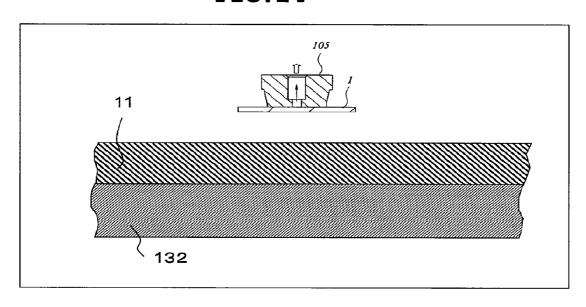

- FIG. 3 is a side view showing a process of affixing a dicing tape to the semiconductor wafer;

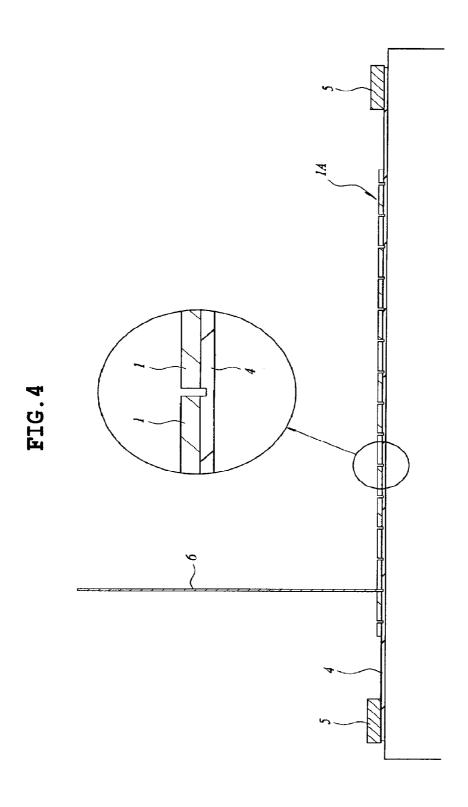

- FIG. 4 is a side view showing a semiconductor wafer dicing process;

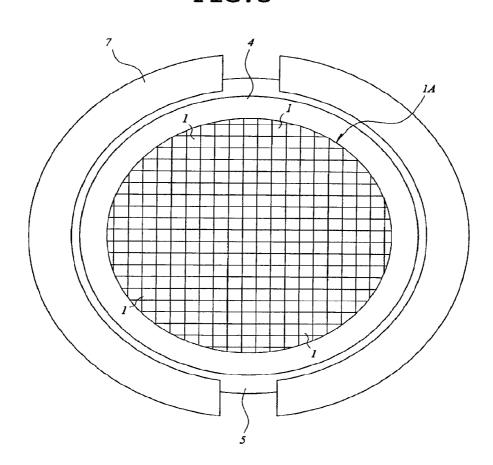

- FIG. **5** is a plan view showing a state in which the semiconductor wafer and the dicing tape are fixed to a wafer ring, presser plates are disposed thereabove, and an expand ring is 30 disposed therebelow;

- FIG. 6 is a sectional view thereof;

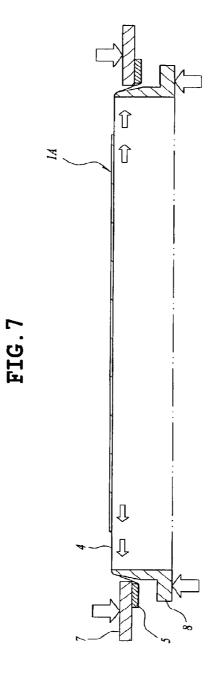

- FIG. 7 is a sectional view showing a state in which tension is applied to the dicing tape by sandwiching the wafer ring in between the presser plates and the expand ring;

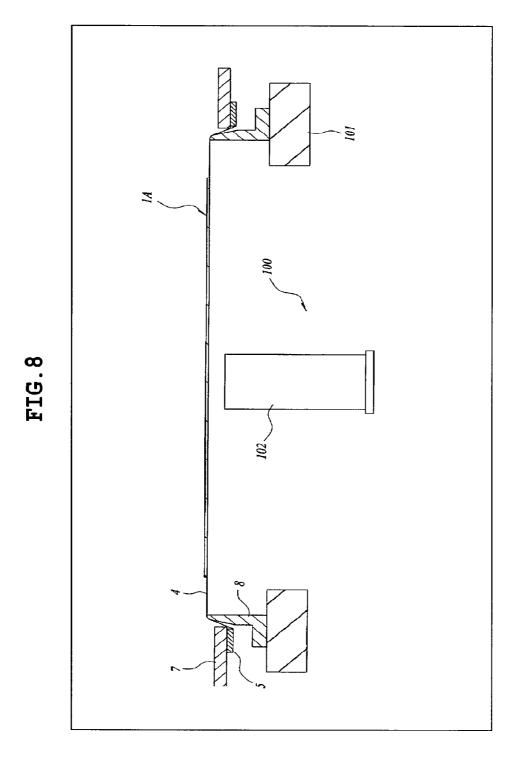

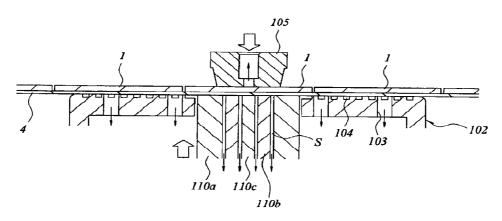

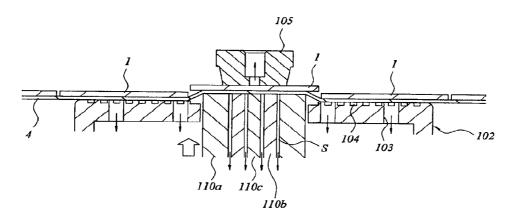

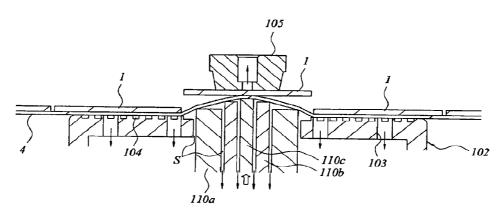

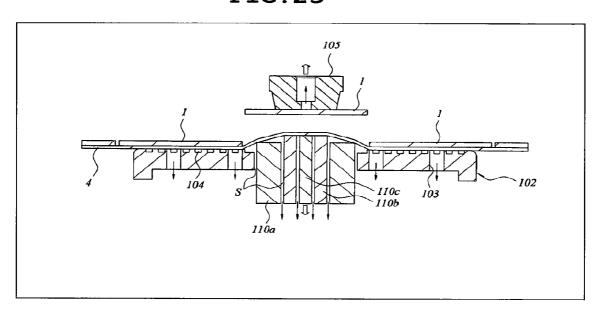

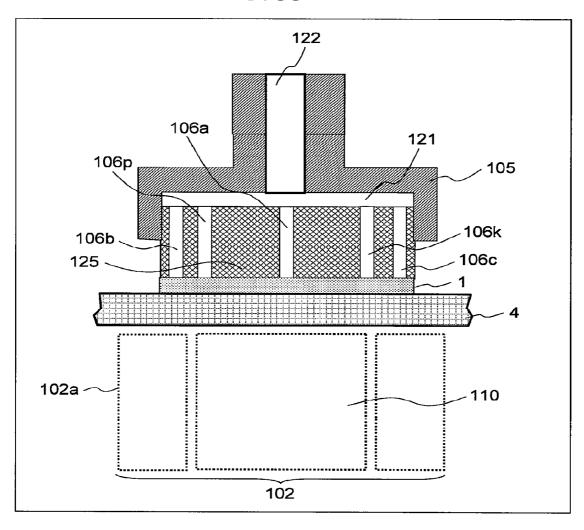

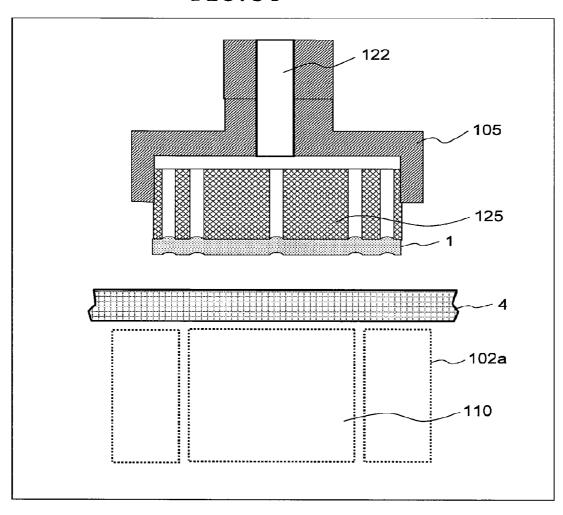

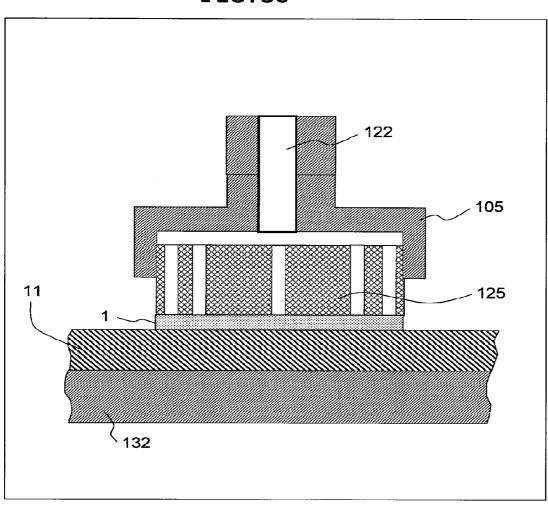

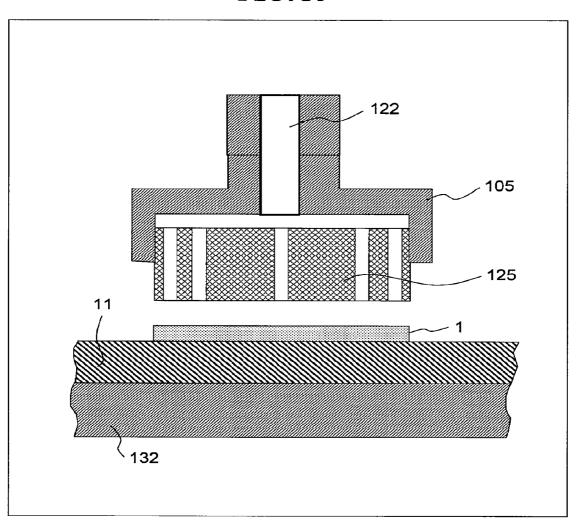

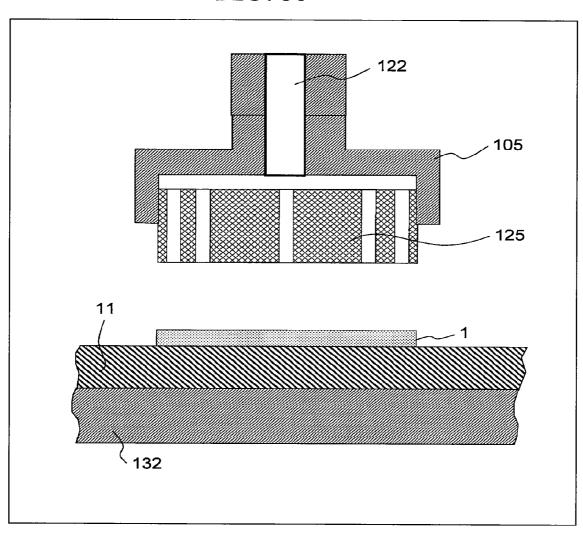

- FIG. 8 is a sectional view of a principal portion of a chip peeling device for explaining a method for peeling a semi-conductor chip with the dicing tape affixed thereto;

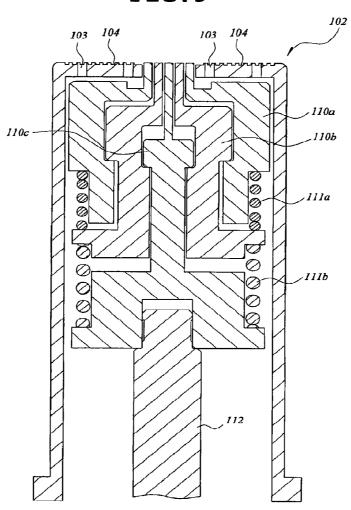

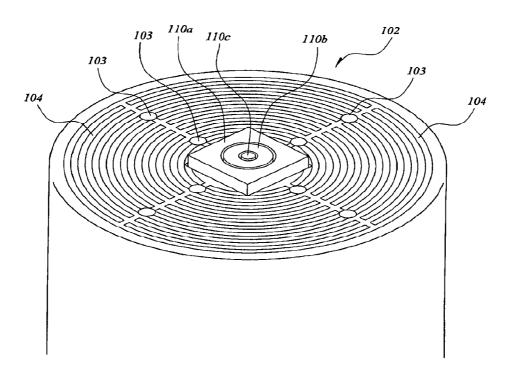

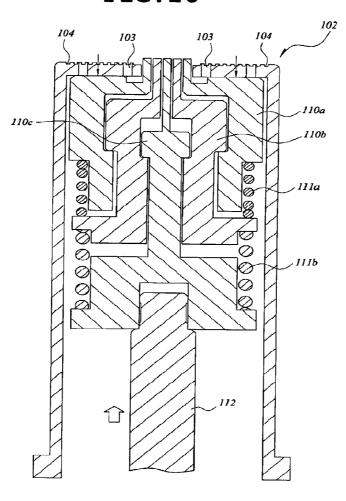

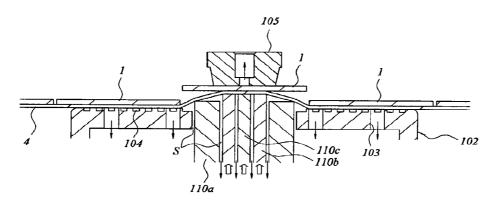

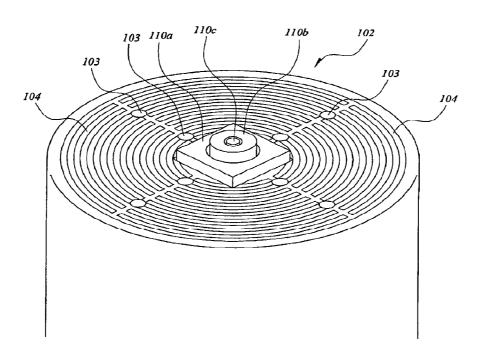

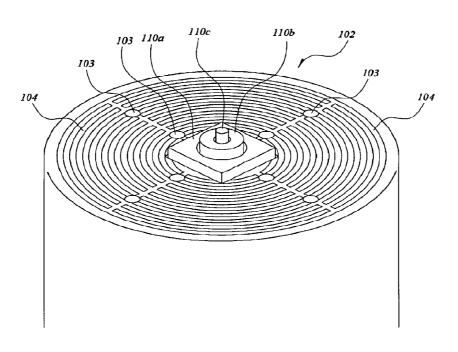

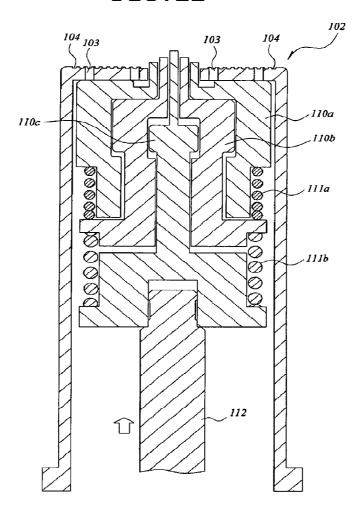

- FIG. 9 is a sectional view showing a chucking piece of the chip peeling device;

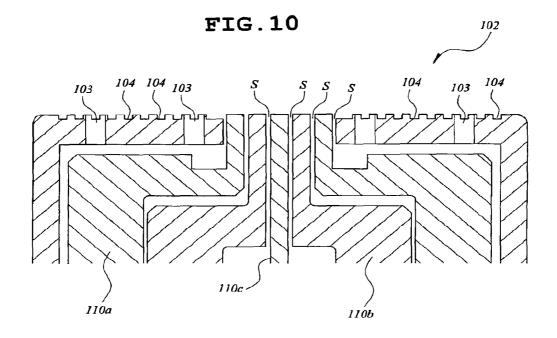

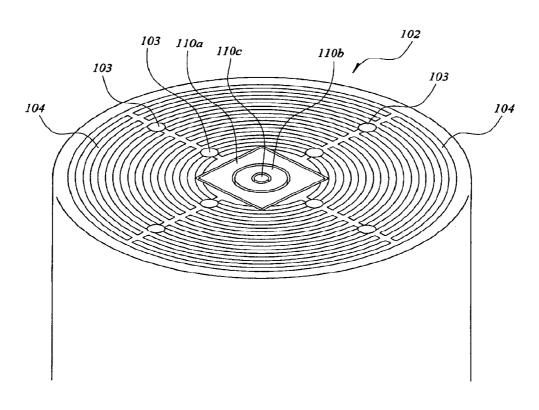

- FIG. 10 is an enlarged sectional view of an upper surface and the vicinity thereof of the chucking piece;

- FIG. 11 is an enlarged perspective view thereof;

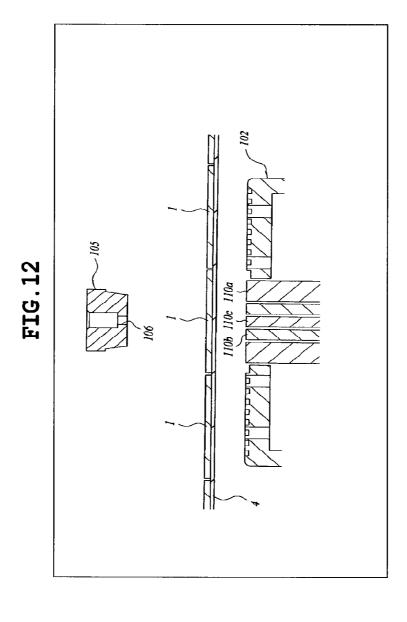

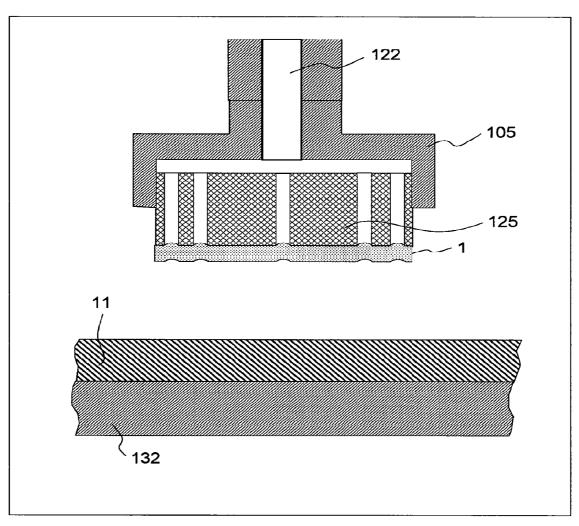

- FIG. 12 is an enlarged sectional view of the upper surface and the vicinity thereof of the chucking piece for explaining 45 a semiconductor chip peeling method;

- FIG. 13 is an enlarged sectional view of the upper surface and the vicinity thereof of the chucking piece for explaining the semiconductor chip peeling method;

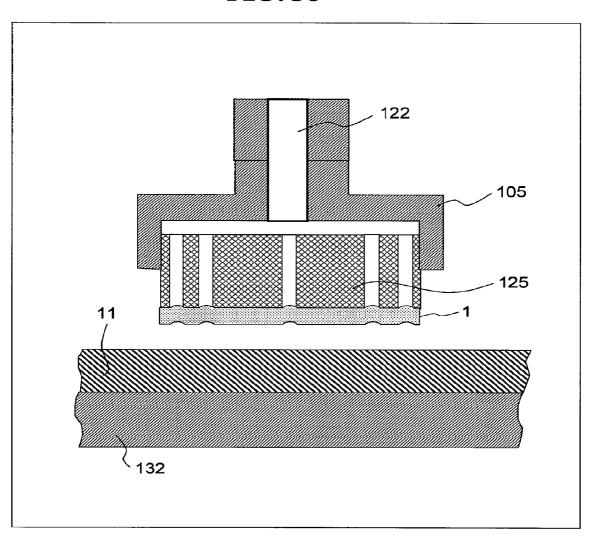

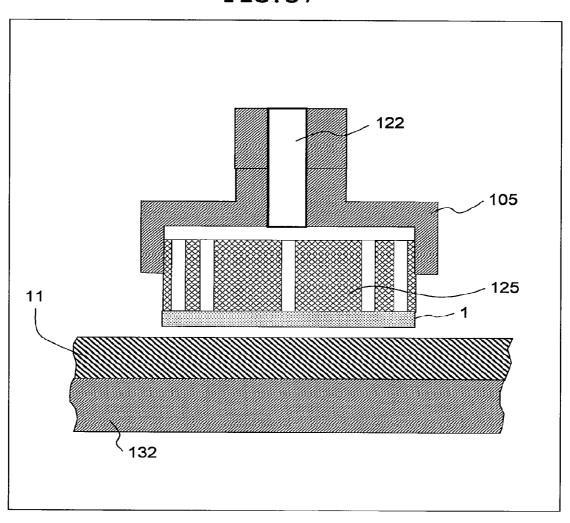

- FIG. 14 is an enlarged sectional view of the upper surface 50 and the vicinity thereof of the chucking piece for explaining the semiconductor chip peeling method:

- FIG. 15 is an enlarged perspective view of the upper surface and the vicinity thereof of the chucking piece for explaining the semiconductor chip peeling method;

- FIG. 16 is a sectional view of the chucking piece for explaining the semiconductor chip peeling method;

- FIG. 17 is an enlarged sectional view of the supper surface and the vicinity thereof of the chucking piece for explaining the semiconductor chip peeling method;

- FIG. **18** is an enlarged perspective view thereof;

- FIG. 19 is a sectional view of the chucking piece for explaining the semiconductor chip peeling method;

- FIG. **20** is an enlarged sectional view of the upper surface and the vicinity thereof of the chucking piece for explaining 65 the semiconductor chip peeling method;

- FIG. 21 is an enlarged perspective view thereof;

4

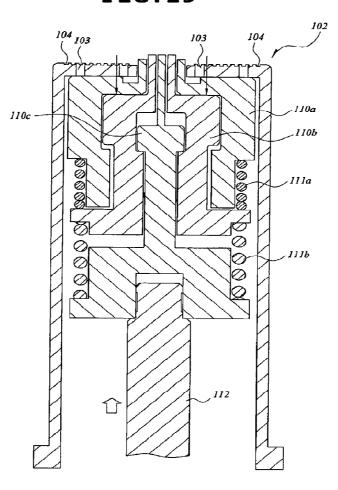

- FIG. 22 is a sectional view of the chucking piece for explaining the semiconductor chip peeling method;

- FIG. 23 is an enlarged sectional view of the upper surface and the vicinity thereof of the chucking piece for explaining the semiconductor chip peeling method;

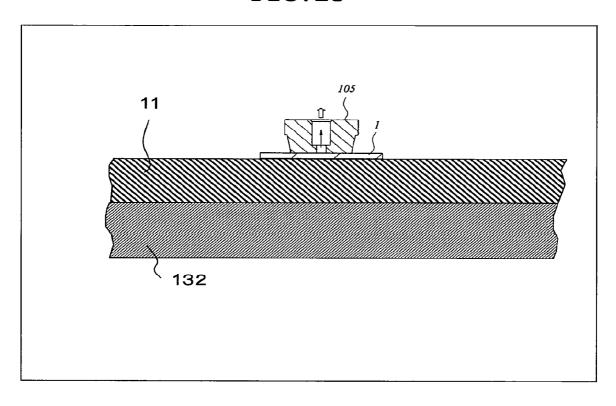

- FIG. 24 is a sectional view showing in what manner the semiconductor chip peeled in FIG. 23 is conveyed to a die bonding section;

- FIG. 25 is a sectional view showing a state in which the semiconductor chip peeled in FIG. 23 has been conveyed to the die bonding section and landed on a wiring substrate;

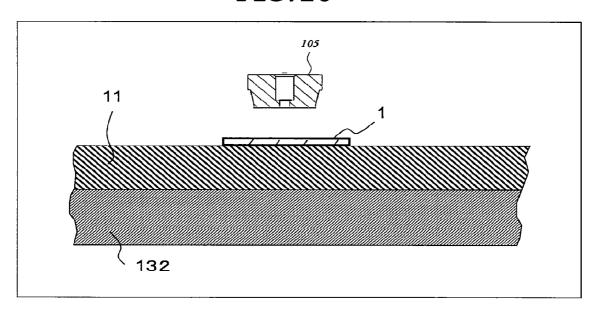

- FIG. 26 is a sectional view showing a state in which the semiconductor chip peeled in FIG. 23 has been bonded onto the wiring substrate in the die bonding section;

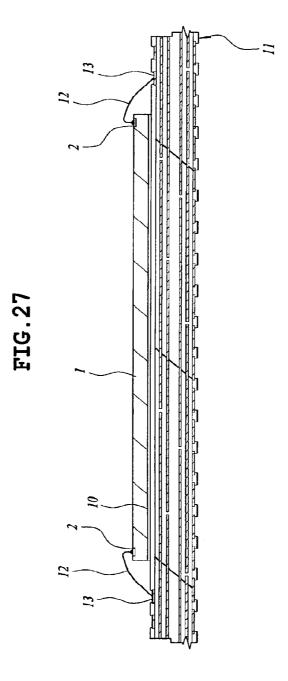

- FIG. 27 is a sectional view of the wiring substrate, showing a pellet mounting step for the semiconductor chip;

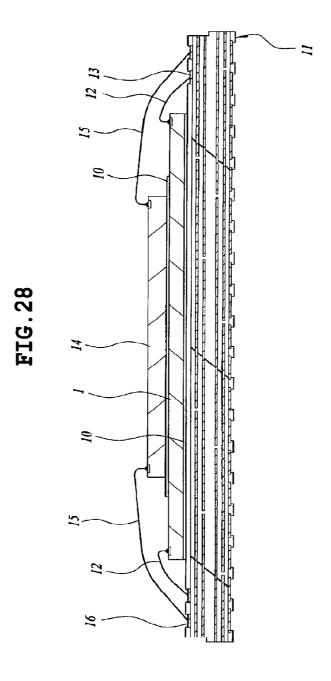

- FIG. 28 is a sectional view of the wiring substrate, showing a semiconductor chip stacking and wire bonding step;

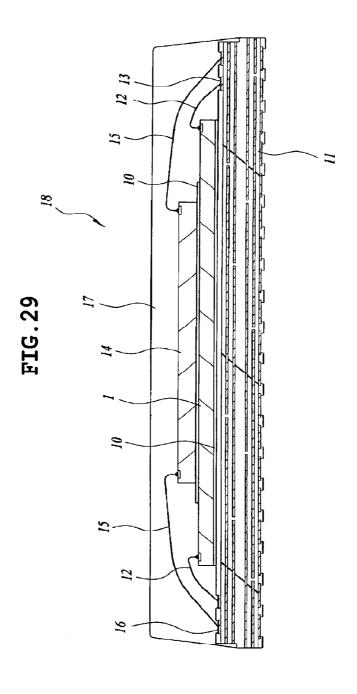

- FIG. 29 is a sectional view of the wiring substrate, showing a resin sealing step for the semiconductor chip;

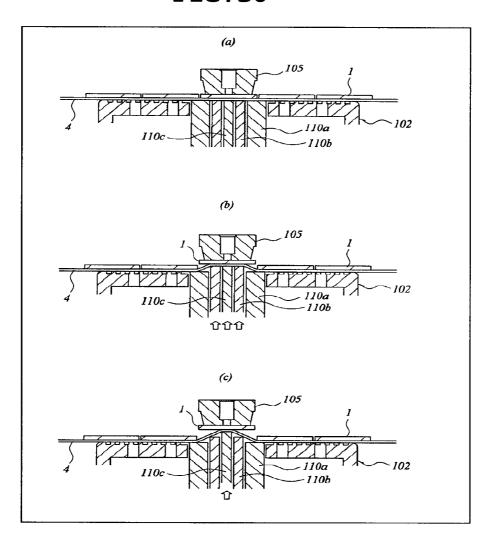

- FIGS. 30(a) to 30(c) are sectional views of the upper surface and the vicinity thereof of the chucking piece for explaining another example of the semiconductor chip peeling method;

- FIGS. 31(a) and 31(b) are explanatory diagrams for explaining the principle of the semiconductor chip peeling method;

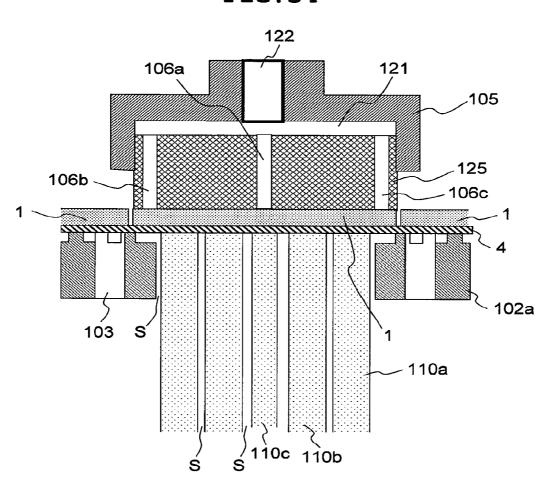

- FIGS. 32(a) and 32(b) are plan views showing an example of a rubber chip, an example of stick-up blocks and the structure of a collet body;

- FIGS. 33(a) and 33(b) are plan views showing another example of a rubber chip, another example of stick-up blocks and the structure of the collet body;

- FIG. 34 is a sectional view explaining the state of the section taken on line A-A in FIG. 34;

- FIG. 35 is a sectional view explaining the state of the section taken on line B-B in FIG. 34;

- FIG. 36(a) and FIG. 36(b) are plan views showing a further example of a rubber chip, a further example of stick-up blocks and the structure of the collet body;

- FIG. 37 is a sectional view explaining the state of the section taken on line A-A in FIG. 36;

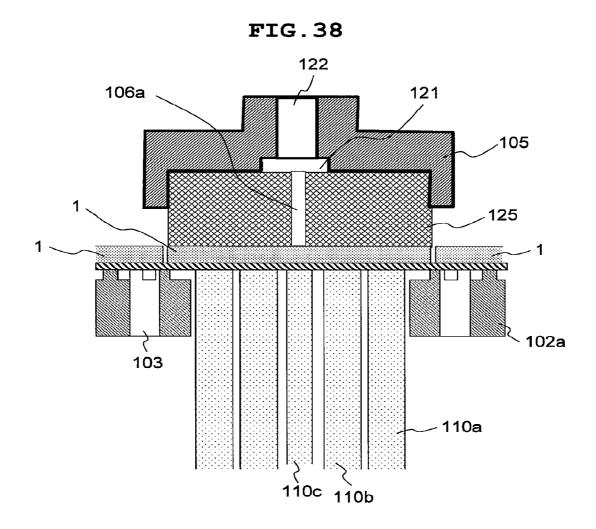

- FIG. 38 is a sectional view explaining the state of the section taken on line B-B in FIG. 36;

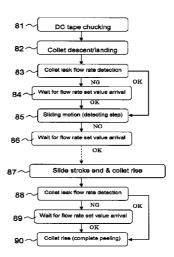

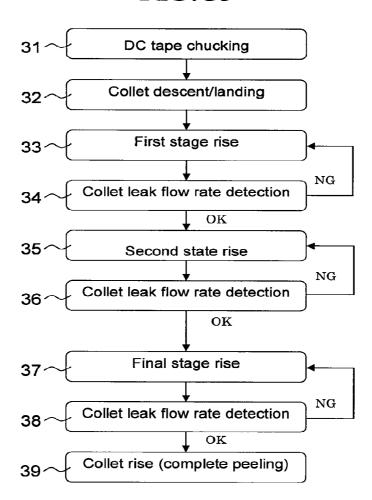

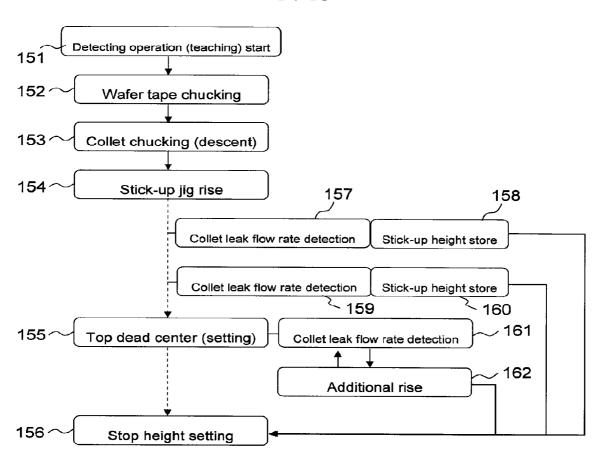

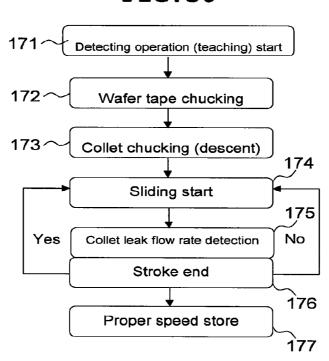

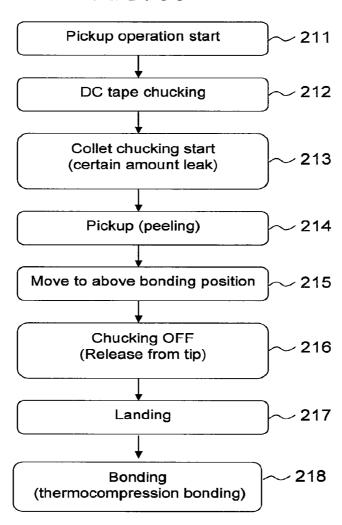

- FIG. 39 is a process flow chart showing a peeling process 1 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

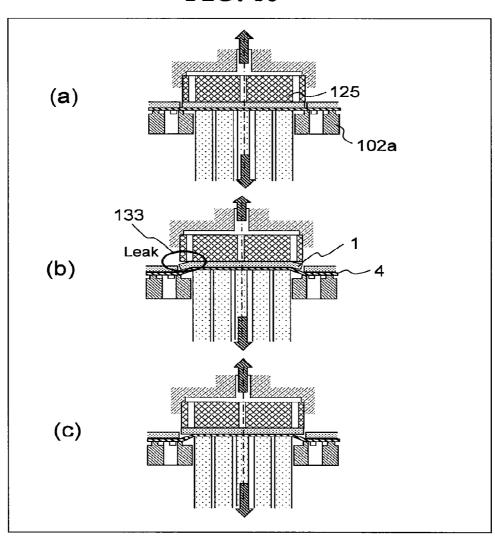

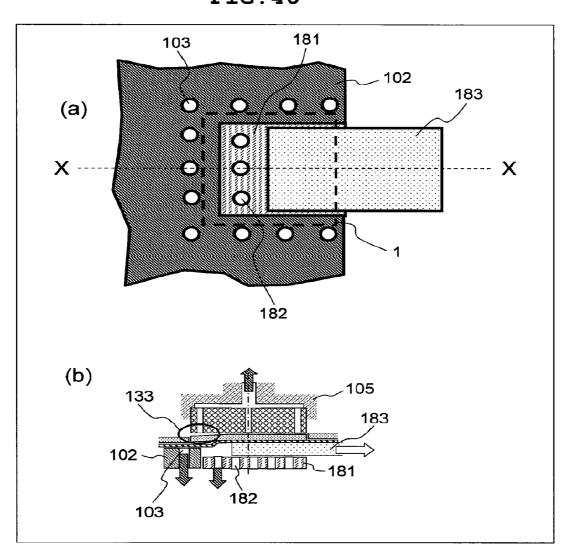

- FIGS. 40(a) to 40(c) are flow diagrams in schematic section showing the peeling process 1 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

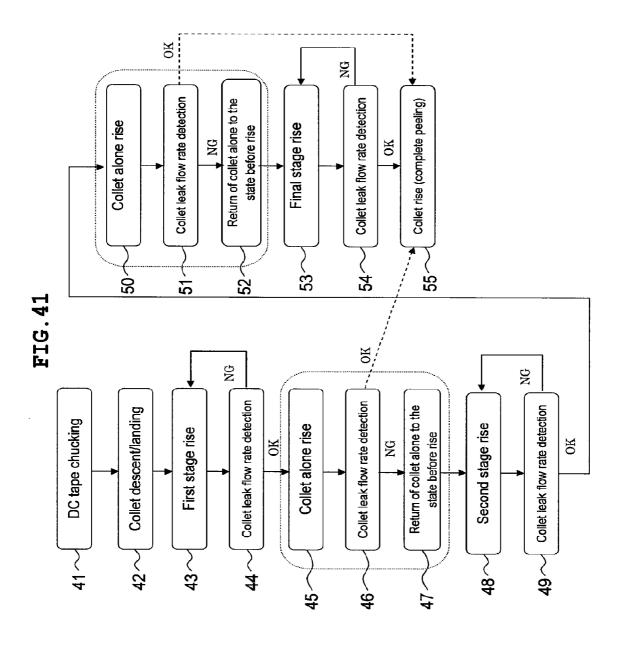

- FIG. 41 is a process flow chart showing a peeling process 2 55 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

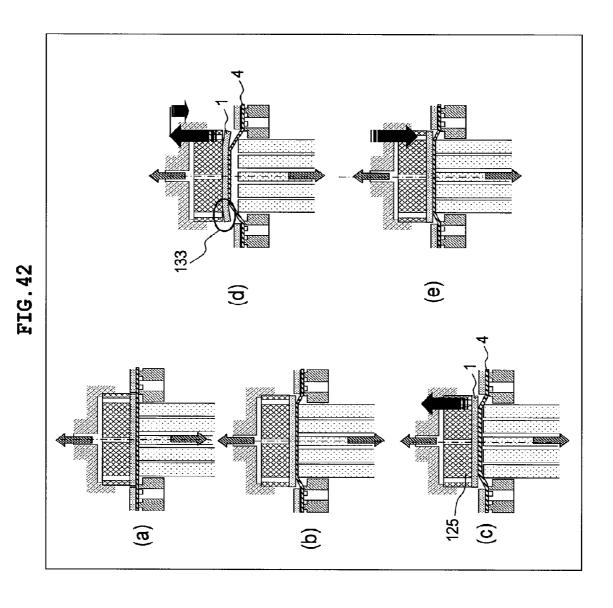

- FIGS. 42(a) to 42(e) are flow diagrams in schematic section showing the peeling process 2 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

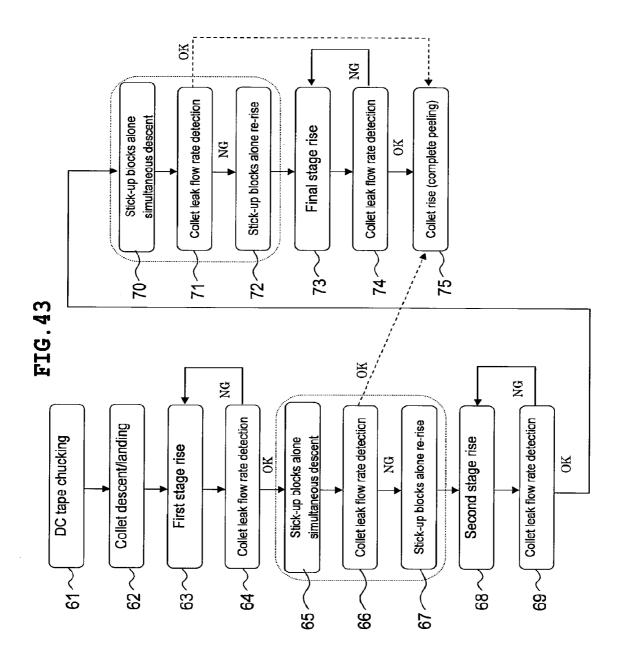

- FIG. 43 is a process flow chart showing a peeling process 3 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

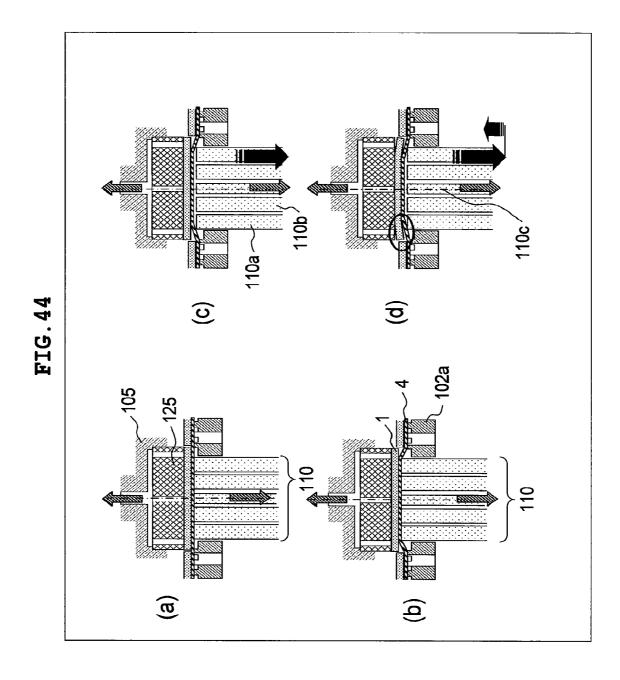

- FIGS. 44(a) to 44(d) are flow diagrams in schematic section showing a peeling process 3 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

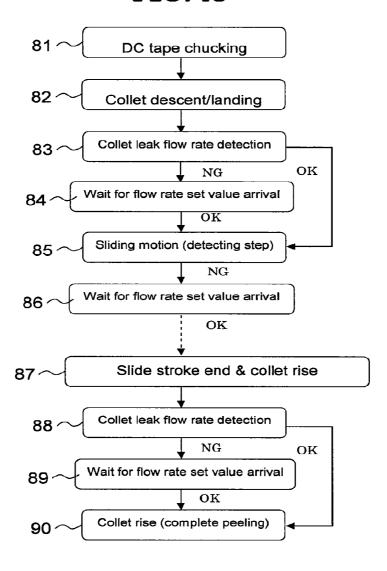

FIG. **45** is a process flow chart showing a peeling process 4 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

FIGS. 46(a) and 46(b) are top views of a principal portion of a peeling device for explaining the structure of the peeling device used in the peeling process 4 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

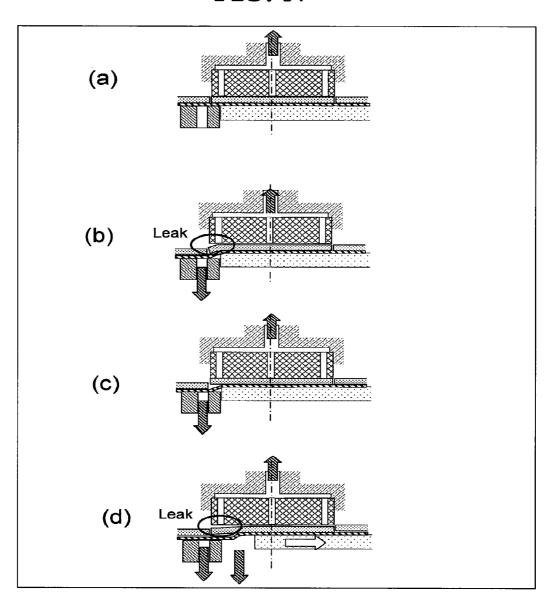

FIGS. 47(a) to 47(d) are flow diagrams in schematic section showing the peeling process 4 in the semiconductor integrated circuit device manufacturing method embodying the present invention;

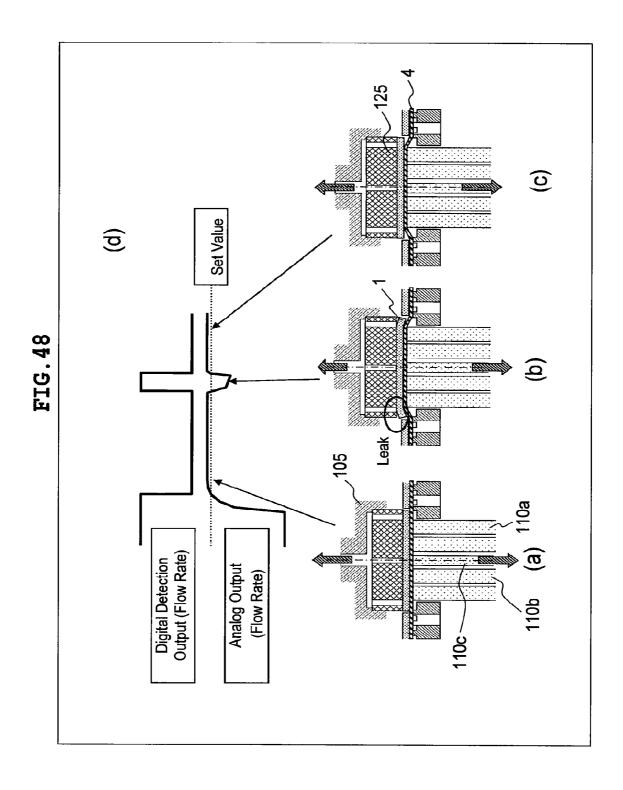

FIGS. **48**(*a*) to **48**(*d*) are flow diagrams in schematic section showing an automatic initial parameter setting method 1 in the semiconductor integrated circuit device manufacturing 15 method embodying the present invention;

FIG. **49** is a process flow chart showing the automatic initial parameter setting method in the semiconductor integrated circuit device manufacturing method embodying the present invention;

FIG. 50 is a process flow chart showing an automatic initial parameter setting method 2 in the semiconductor integrated circuit device manufacturing method embodying the present invention:

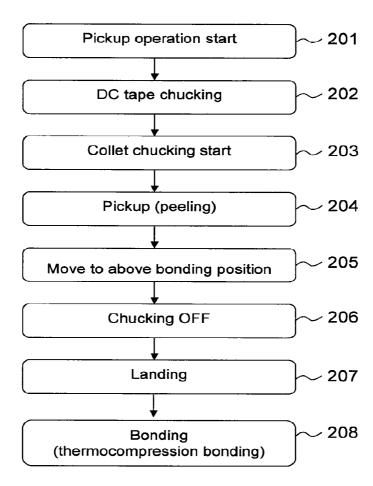

FIG. **51** is a step flow chart explaining a die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present invention;

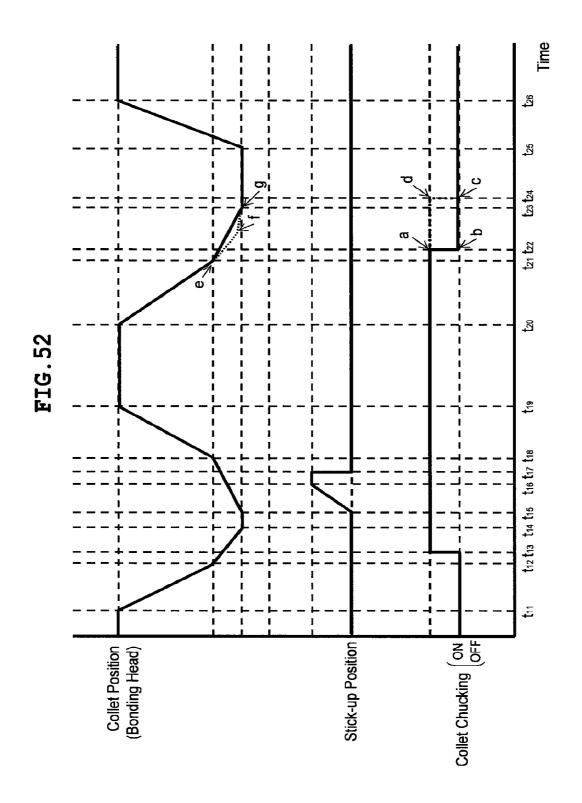

FIG. **52** is a time chart explaining the die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present invention;

FIG. 53 is a flow diagram 1 in schematic section explaining the die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present invention;

FIG. **54** is a flow diagram **2** in schematic section explaining 35 the die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present invention;

FIG. 55 is a flow diagram 3 in schematic section explaining the die bonding procedure in the semiconductor integrated 40 circuit device manufacturing method embodying the present invention;

FIG. **56** is a flow diagram **4** in schematic section explaining the die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present 45 invention;

FIG. 57 is a flow diagram 5 in schematic section explaining the die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present invention;

FIG. **58** is a flow diagram **6** in schematic section explaining the die bonding procedure in the semiconductor integrated circuit device embodying the present invention;

FIG. **59** is a flow diagram **7** in schematic section explaining the die bonding procedure in the semiconductor integrated 55 circuit device manufacturing method embodying the present invention:

FIG. **60** is a flow diagram **8** in schematic section explaining the die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present 60 invention;

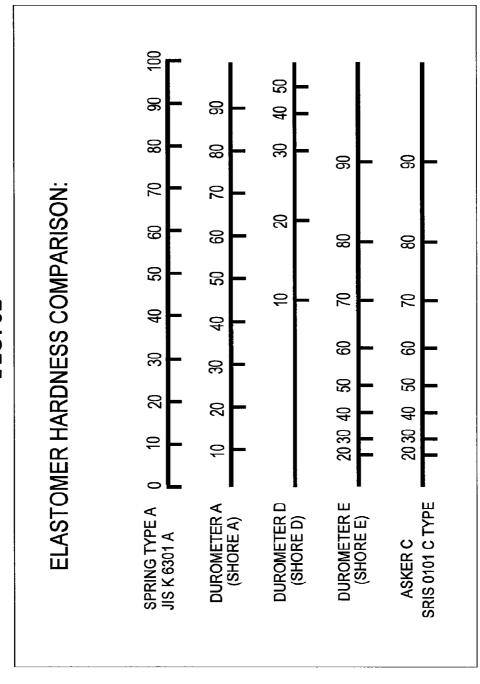

FIG. **61** is a diagram comparing hardness among various standards with respect to the material of a rubber chip used in die bonding in the semiconductor integrated circuit device embodying the present invention;

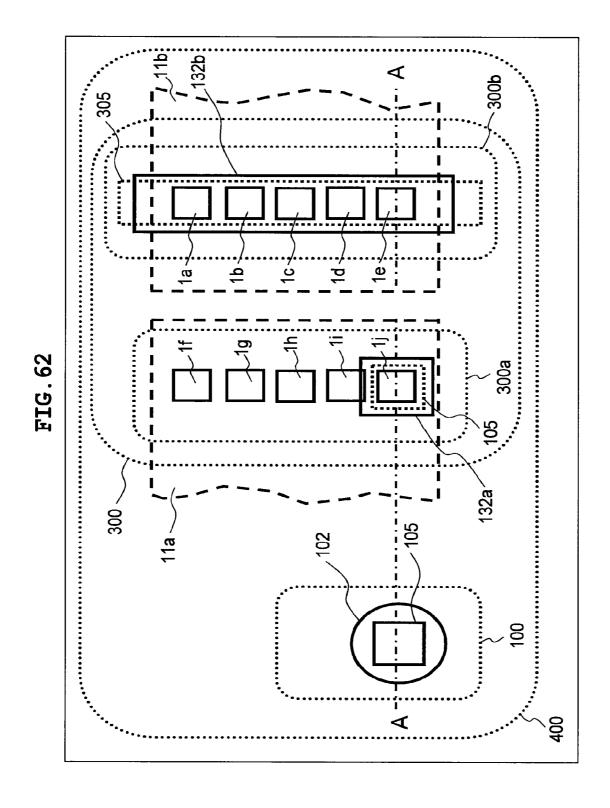

FIG. 62 is a schematic top view showing the construction of a chip peeling/die bonding device used in a step die bond-

6

ing method in the semiconductor integrated circuit device manufacturing method embodying the present invention;

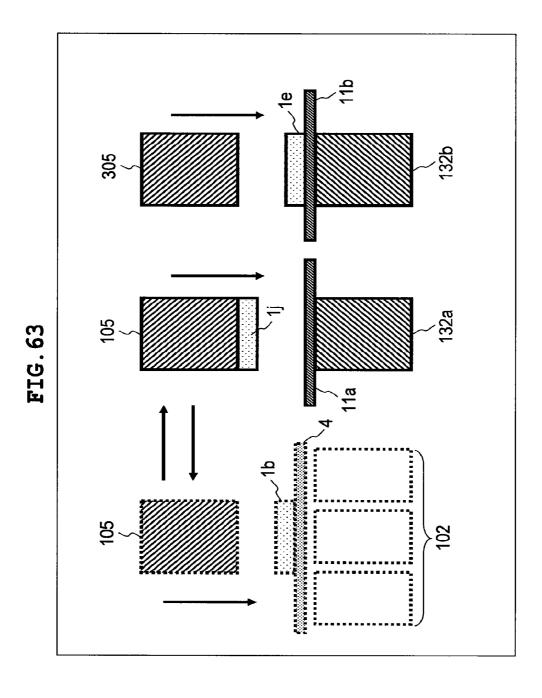

FIG. 63 is a sectional step flow diagram 1 showing a flow of the step die bonding method in the semiconductor integrated circuit device manufacturing method embodying the present invention;

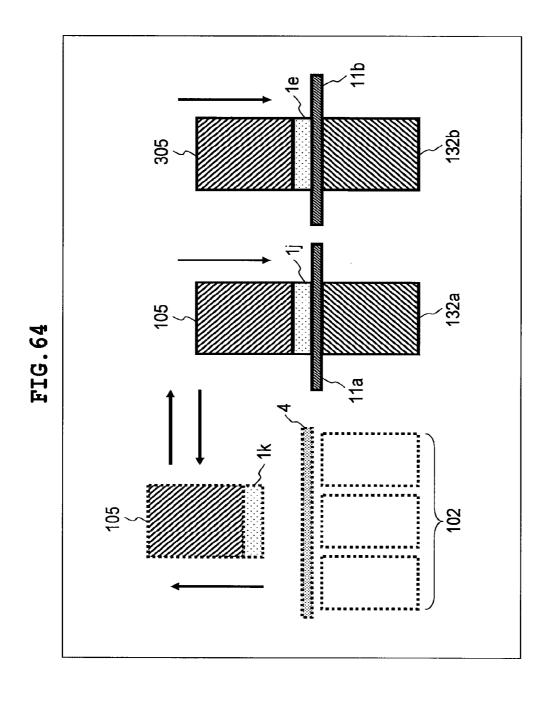

FIG. **64** is a sectional step flow diagram **2** showing the flow of a step die bonding method in the semiconductor integrated circuit device manufacturing method embodying the present invention;

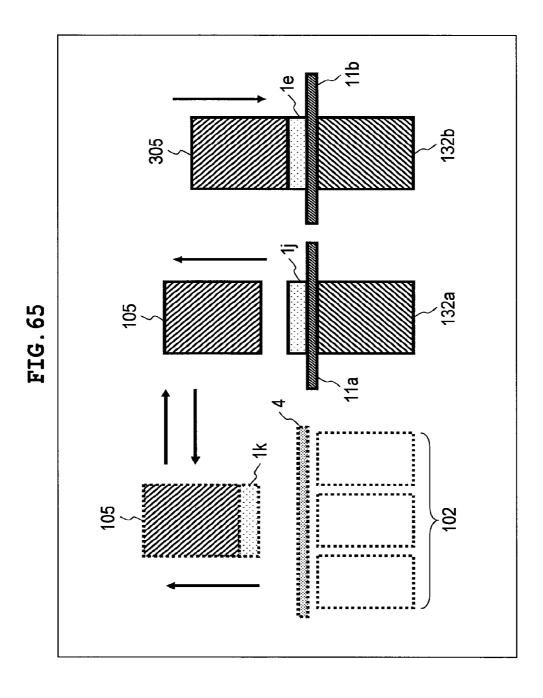

FIG. **65** is a sectional step flow diagram **3** showing a flow of the step die bonding method in the semiconductor integrated circuit device manufacturing method embodying the present invention;

FIG. **66** is a step flow chart explaining a modified example of the die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present invention;

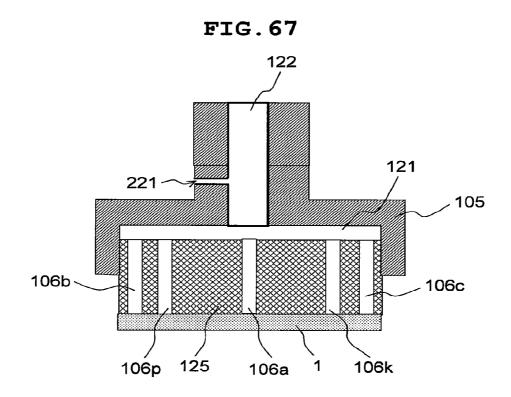

FIG. **67** is a sectional view of a collet used in the modified <sup>20</sup> example of the die bonding procedure in the semiconductor integrated circuit device manufacturing method embodying the present invention;

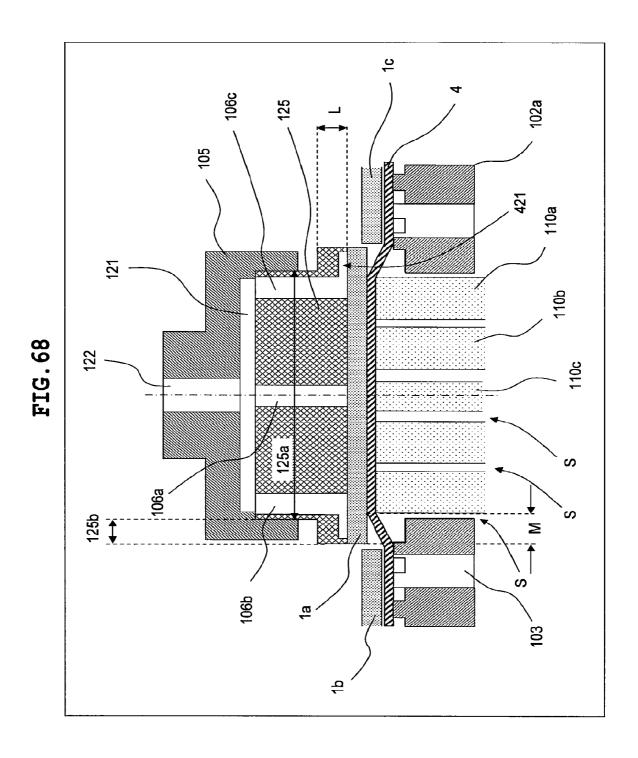

FIG. **68** is a schematic sectional view showing an intermediate state in a die pick-up process (using a rubber chip having a peripheral flange) in the semiconductor integrated circuit device manufacturing method embodying the present invention:

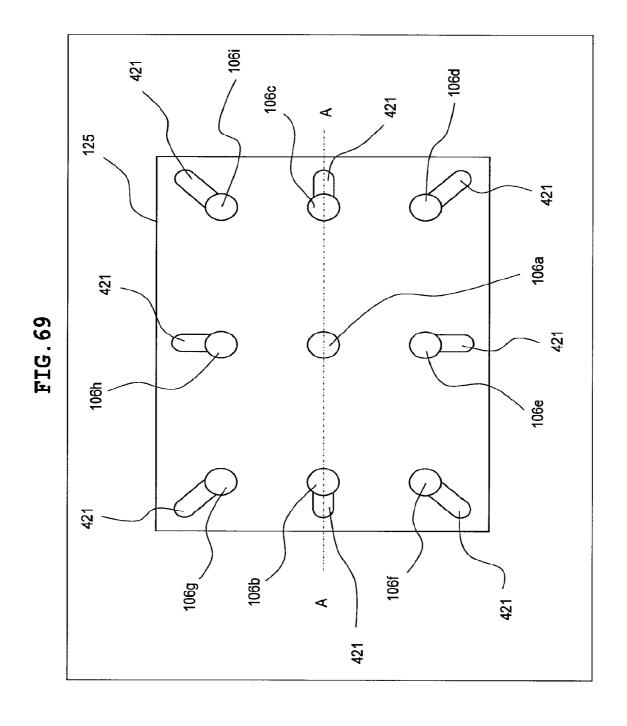

FIG. **69** is a bottom view (concrete example "a") of a rubber chip corresponding to FIG. **68**;

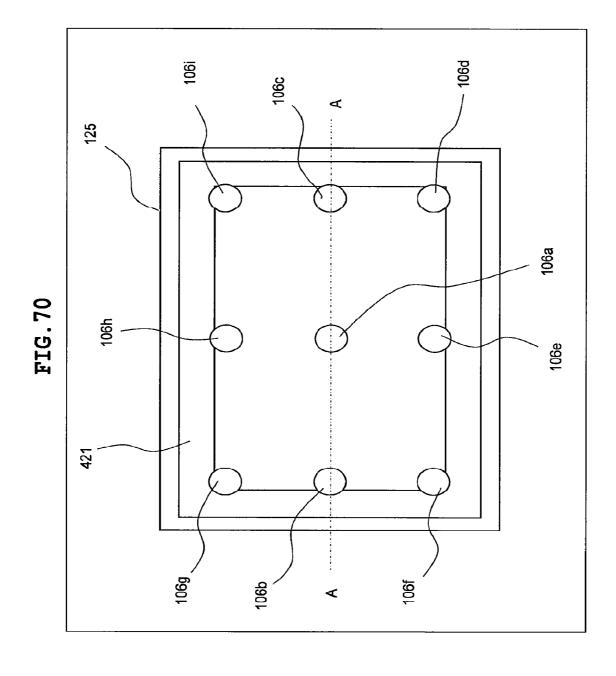

FIG. 70 is a bottom view (concrete example "b") of a rubber chip corresponding to FIG. 68;

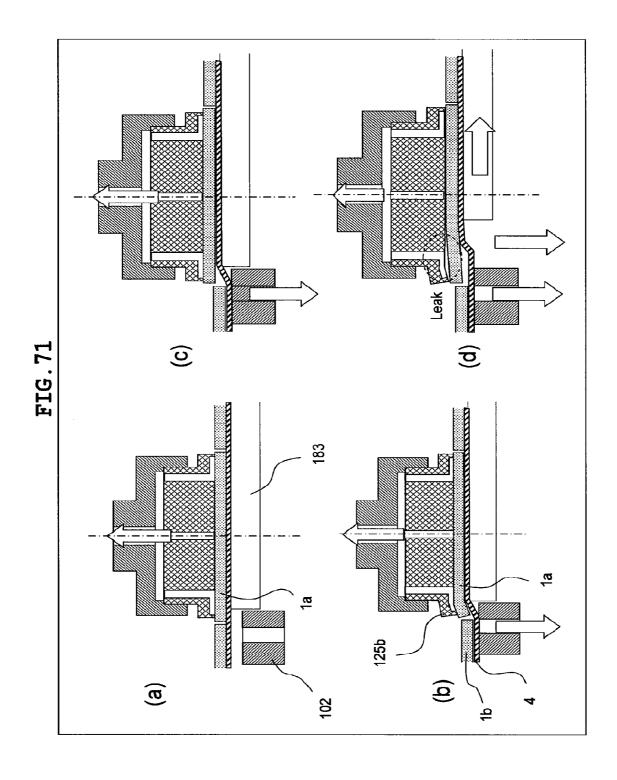

FIGS. 71(a) to 71(d) are sectional flow diagrams in which the rubber chip corresponding to FIG. **68** is applied to the peeling process of section (3-4); and

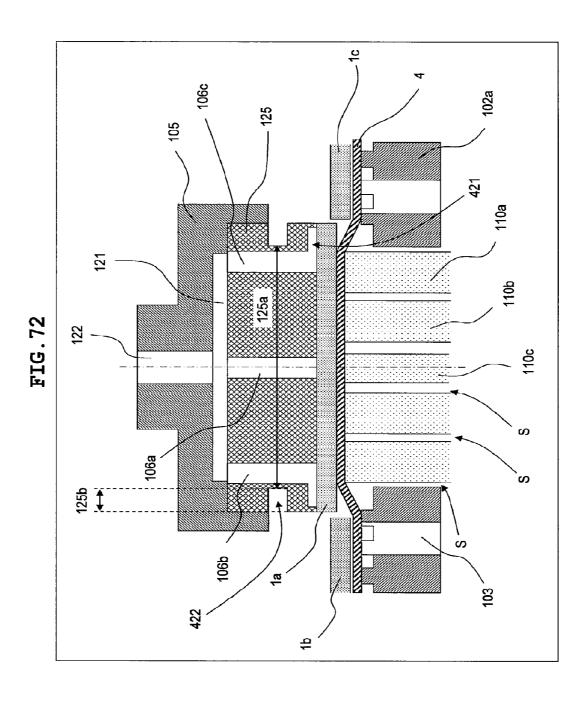

FIG. **72** is a schematic sectional view showing a state halfway in a die pick-up process (using another rubber chip having a peripheral flange) in the semiconductor integrated circuit device manufacturing method.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

# Outline of Embodiments

The following is an outline of typical embodiments of the present invention as disclosed herein.

1. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

(a) supplying a plurality of chips divided in individual chip regions while being arranged substantially in their original two-dimensional layout upon a wafer, to a chip treating apparatus with their back surfaces fixed to an adhesive tape; and (b) vacuum-chucking a surface of a first chip out of the chips with a chucking collet and peeling the adhesive tape from the back surface of the first chip in a state in which the adhesive tape over the back surface of the first chip is vacuum-chucked to an upper surface of a lower base,

the step (b) comprising a following sub-step of:

- (b1) monitoring a bent state of the first chip before complete separation of the first chip from the adhesive tape by measuring the flow rate of a vacuum chucking system in the chucking collet.

- 2. A method according to the above 1, wherein the step (b) further comprises the following sub-steps of:

- (b2) continuing or interrupting the peeling operation on the basis of the monitor information obtained in the sub-step (b1); and

- (b3) in case of interrupting the peeling operation, resuming the peeling operation on the basis of the monitor information obtained in the sub-step (b1).

- 3. A method according to the above 1 or 2, wherein the step (b) further comprises the following sub-steps of:

- (b4) continuing or decelerating the peeling operation on the basis of the monitor information obtained in the sub-step (b1); and

- (b5) in case of decelerating the peeling operation, re-accelerating the peeling operation on the basis of the monitor information obtained in the sub-step (b1).

- 4. A method according to any of the above 1 to 3, wherein the step (b) further comprises a following sub-step of:

- (b6) on the basis of the monitor information obtained in the sub-step (b1), continuing the peeling operation, or retreating the peeling operation until the bent state of the first chip falls under an allowable range.

- 5. A method according to any of the above 1 to 4, wherein the step (b) further comprises a following sub-step of:

- (b7) on the basis of the monitor information obtained in the 20 sub-step (b1), continuing the peeling operation, or decelerating the peeling operation until the bent state of the first chip falls under an allowable range.

- 6. A method according to any of the above 1 to 5, wherein the step (b) further comprises the following sub-steps of:

- (b9) raising the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b9) after the sub-step (b8) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise of the chucking collet, or bringing down the chucking collet 30 until the bent state of the first chip falls under the allowable range.

- 7. A method according to any of the above 1 to 6, wherein the step (b) further comprises the following sub-steps of:

- (b10) raising the chucking collet until the bent state of the first 35 chip exceeds an allowable range; and

- (b11) after the step (b10) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise of the chucking collet, or making the chucking collet stand by until the bent state of the first chip falls under the allowable 40 range.

- 8. A method according to any of the above 1 to 7, wherein the step (b) further comprises the following sub-steps of:

- (b12) raising the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (13) after the sub-step (b12) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise of the chucking collet, or decelerating the chucking collet until the bent state of the first chip falls under the allowable range.

- 9. A method according to any of the above 1 to 8, wherein the step (b) further comprises the following sub-steps of:

- (b14) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

- (b15) after the sub-step (b14), bringing down only the stickup block out of the stick-up block and the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b16) after the sub-step (b15) and on the basis of the monitor information obtained in the sub-step (b1), continuing the 60 descent of the stick-up block, or raising the stick-up block until the bent state of the first chip falls under the allowable range.

- 10. A method according to any of the above 1 to 9, wherein the step (b) further comprises the following sub-steps of:

- (b17) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

8

- (b18) after the sub-step (b17), bringing down only the stick-up block out of the stick-up block and the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b19) after the sub-step (b18) and on the basis of the monitor information obtained in the sub-step (b1), continuing the descent of the stick-up block, or making the stick-up block stand by until the bent state of the first chip falls under the allowable range.

- 11. A method according to any of the above 1 to 10, wherein the step (b) further comprises the following sub-steps of:

- (b20) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

- (b21) after the sub-step (b20), bringing down only the stick-up block out of the stick-up block and the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b22) after the sub-step (b21) and on the basis of the monitor information obtained in the sub-step (b1), continuing the descent of the stick-up block, or decelerating the descent of the stick-up block until the bent state of the first chip falls under the allowable range.

- 12. A method according to any of the above 1 to 11, wherein 25 the step (b) further comprises the following sub-steps of:

- (b23) causing a slide plate serving as a principal portion of the lower base to slide so as to decrease an overlap thereof with the first chip until the bent state of the first chip exceeds an allowable range; and

- (b24) on the basis of the monitor information obtained in the sub-step (b1), making the slide plate stand by until the bent state of the first chip falls under the allowable range.

- 13. A method according to any of the above 1 to 12, wherein the step (b) further comprises the following sub-steps of:

- (b25) continuing or interrupting the peeling operation on the basis of the monitor information obtained in the sub-step (b1); and

- (b26) in case of interrupting the peeling operation, resuming the peeling operation, or retreating the peeling operation until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the substep (b1).

- 14. A method according to any of the above 1 to 13, wherein the step (b) further comprises the following steps of:

- 5 (b27) continuing or decelerating the peeling operation on the basis of the monitor information obtained in the sub-step (b1); and

- (b28) in case of decelerating the peeling operation, re-accelerating the peeling operation, or retreating the peeling operation until the bent state of the first chip falls under an allowable range, on the basis of the monitor information obtained in the sub-step (b1).

- 15. A method according to any of the above 1 to 14, wherein the step (b) further comprises the following sub-steps of:

- (b29) raising the chucking collet until the bent state of the first chip exceeds an allowable range;

- (b30) after the sub-step (b29) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise of the chucking collet, or making the chucking collet stand by until the bent state of the first chip falls under the allowable range; and

- (b31) in case of making the chucking collet standby until the bent state of the first chip falls under the allowable range, resuming the rise of the chucking collet, or bringing down the chucking collet until the bent state of the first chip falls under

the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

16. A method according to any of the above 1 to 15, wherein the step (b) further comprises the following sub-steps of: (b32) raising a stick-up block as a principal portion of the

lower base together with the chucking collet;

(b33) after the sub-step (b32), bringing down only the stickup block out of the stick-up block and the chucking collet until the bent state of the first chip exceeds an allowable range:

(b34) after the sub-step (b33) and on the basis of the monitor information obtained in the sub-step (b1), continuing the 10 descent of the stick-up block, or making the stick-up block standby until the bent state of the first chip falls under the allowable range; and

(b35) in case of making the stick-up block stand by until the bent state of the first block falls under the allowable range, 15 resuming the descent of the stick-up block, or raising the stick-up block until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

17. A method according to any of the above 1 to 16, wherein 20 the step (b) further comprises the following sub-steps of: (b36) raising the chucking collet until the bent state of the first chip exceeds an allowable range;

(b37) after the sub-step (b36) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise 25 of the chucking collet, or decelerating the chucking collet until the bent state of the first chip falls under the allowable range; and

(b38) in case of decelerating the chucking collet until the bent state of the first chip falls under the allowable range, resuming 36 the rise of the chucking collet, or bringing down the chucking collet until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

18. A method according to any of the above 1 to 17, wherein 35 the step (b) further comprises the following sub-steps of: (b39) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

(b40) after the sub-step (b39), bringing down only the stickup block out of the stick-up block and the chucking collet 40 until the bent state of the first chip exceeds an allowable range;

(b41) after the sub-step (b40) and on the basis of the monitor information obtained in the sub-step (b1), continuing the descent of the stick-up block, or decelerating the descent of 45 the stick-up block until the bent state of the first chip falls under the allowable range; and

(b42) in case of making the stick-up block stand by until the bent state of the first chip falls under the allowable range, resuming the descent of the stick-up block, or raising the 50 stick-up block until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

19. A method according to any of the above 1 to 18, wherein an adhesive layer is formed beforehand over the back surface 55 of the first chip.

20. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

(a) supplying a plurality of chips divided in individual chip regions while being arranged substantially in their original 60 two-dimensional layout upon a wafer, to a chip treating apparatus with their back surfaces fixed to an adhesive tape;

(b) vacuum-chucking a surface of a first chip out of the chips with a chucking collet and peeling the adhesive tape from the back surface of the first chip in a state in which the adhesive 65 tape over the back surface of the first chip is vacuum-chucked to an upper surface of a lower base;

10

the step (b) comprising the following sub-steps of:

(b1) monitoring a bent state of the first chip before complete separation of the first chip from the adhesive tape by measuring the flow rate of a vacuum chucking system in the chucking collet, and

(b2) determining an optimum speed (a speed to be applied to a subsequent chip) of the peeling operation on the basis of the monitor information obtained in the sub-step (b1),

the method further comprising a following step of: (c) after the step (b), vacuum-chucking a surface of a second chip out of the plural chips with the chucking collet, and in a state in which the adhesive tape over the back surface of the second chip is vacuum-chucked to the upper surface of the lower base, carrying out the peeling operation at the optimum speed to peel the adhesive tape from the back surface of the second chip.

21. A method according to the above 20, wherein the first chip may be a non-product chip (or may be a product chip).

22. A method according to the above 20, wherein the second chip is a product chip.

23. A method according to any of the above 20 to 22, wherein an adhesive layer for die bonding is formed beforehand over the back surface of the first chip and that of the second chip.

24. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

(a) supplying a plurality of chips divided in individual chip regions while being arranged substantially in their original two-dimensional layout upon a wafer, to a chip treating apparatus with their back surfaces fixed to an adhesive tape;

(b) vacuum-chucking a surface of a first chip out of the chips with a chucking collet and peeling the adhesive tape from the back surface of the first chip in a state in which the adhesive tape over the back surface of the first chip is vacuum-chucked to an upper surface of a lower base,

the step (b) comprising the following sub-steps of:

(b1) monitoring a bent state of the first chip before complete separation of the first chip from the adhesive tape by measuring the flow rate of a vacuum chucking system in the chucking collet;

(b2) raising a stick-up block as a principal portion of the lower base together with the chucking collet; and

(b3) determining an optimum rising height of the stick-up block on the basis of the monitor information obtained in the sub-step (b1),

the method further comprising a following step of:

(c) after the step (b), vacuum-chucking a surface of a second chip out of the chips with a chucking collet and raising the stick-up block by only a distance corresponding to the optimum rising height in a state in which the adhesive tape over the back surface of the second chip is vacuum-chucked to the upper surface of the lower base.

25. A method according to the above 24, wherein the first chip is a non-product chip (or may be a product chip).

26. A method according to the above 24, wherein the second chip is a product chip.

27. A method according to any of the above 24 to 26, wherein an adhesive layer for die bonding is formed beforehand over the back surface of the first chip and that of the second chip. 28. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

(a) supplying a plurality of chips divided in individual chip regions while being arranged substantially in their original two-dimensional layout upon a wafer, to a chip treating apparatus with their back surfaces fixed to an adhesive tape;

(b) vacuum-chucking a surface of a first chip out of the chips with a chucking collet and peeling the adhesive tape from the back surface of the first chip in a state in which the adhesive

tape over the back surface of the first chip is vacuum-chucked to an upper surface of a lower base,

the step (b) comprising the following steps of:

- (b1) monitoring a bent state of the first chip before complete separation of the first chip from the adhesive tape by measuring the flow rate of a vacuum chucking system in the chucking collet:

- (b2) causing a slide plate as a principal portion of the lower base to slide so as to decrease an overlap thereof with the first chip until the bent state of the first chip exceeds an allowable range; and

- (b3) determining an optimum sliding speed of the slide plate on the basis of the monitor information obtained in the substep (b1),

the method further comprising a following step of:

- (c) after the step (b), vacuum-chucking a surface of a second chip out of the chips with a chucking collet and, in a state in which the back surface of the second chip is vacuum-chucked to the upper surface of the lower base, causing the slide plate 20 to slide at the optimum sliding speed so as to decrease an overlap thereof with the second chip, thereby peeling the adhesive tape from the back surface of the second chip.

- 29. A method according to the above 28, wherein the first chip is a non-product chip (or may be a product chip).

- 30. A method according to the above 29, wherein the second chip is a product chip.

- 31. A method according to any of the above 28 to 30, wherein an adhesive layer for die bonding is formed beforehand over the back surface of the first chip and that of the second chip. 30

Next, other typical embodiments of the present invention as disclosed herein will be outlined below.

- 1. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

- (a) supplying a plurality of chips to a chip pick-up section of 35 a chip treating apparatus;

- (b) in a state in which a surface of a first chip out of the chips supplied to the chip pick-up section is vacuum-chucked to a lower surface of a rubber chip of a chucking collet, conveying the first chip toward a die bonding section of the chip treating 40 apparatus;

- (c) after the step (b) in a state in which mainly the surface of the first chip is held by physical chucking (chucking no using a vacuum source, this is true also in the following) between it and the lower surface of the rubber chip, causing a back 45 surface side of the first chip to be landed over an upper surface of a wiring substrate placed in the die bonding section of the chip treating apparatus; and

- (d) after the step (c), pressing the surface of the first chip downward by the lower surface of the rubber chip, thereby 50 fixing the first chip to the upper surface of the wiring substrate through an adhesive layer formed between the back surface of the first chip and the upper surface of the wiring substrate.

- 2. A method according to the above 1, wherein in the steps (c) to (d) the vacuum chucking is OFF (chucking not using 55 vacuum chucking, i.e., chucking not using a vacuum source, this is true also in the following).

- 3. A method according to the above 1 or 2, wherein the rubber chip has a central vacuum suction hole. (It is not always necessary to have such a central vacuum suction hole. 60 Vacuum suction holes may be formed in one row in only the peripheral portion in case of not utilizing leak detection. Even in case of detecting leak, at least plural groups of vacuum suction holes different in the distance from the center will suffice. This is also true in the following.)

- 4. A method according to any of the above 1 to 3, wherein the step (b) comprises the following sub-steps of:

12

- (b1) bringing down the first chip at a first speed toward the upper surface of the wiring substrate; and

- (b2) subsequent to the step (b1), bringing down the first chip toward the upper surface of the wiring substrate at a second speed lower than the first speed,

further, the step (c) comprises a following sub-step of:

- (c1) bringing down the first chip toward the upper surface of the wiring substrate at the second speed until landing.

- 5. A method according to any of the above 1 to 4, wherein the rubber chip contains elastomer as a principal component and has a hardness of 10 or higher and lower than 70.

- 6. A method according to any of the above 1 to 4, wherein the rubber chip contains elastomer as a principal component and has a hardness of 15 or higher and lower than 55.

- 7. A method according to any of the above 1 to 4, wherein the rubber chip contains elastomer as a principal component and has a hardness of 20 or higher and lower than 40.

- 8. A method according to any of the above 1 to 7, wherein the elastomer is a thermosetting elastomer.

- 9. A method according to any of the above 1 to 8, wherein the elastomer is a silicone-based elastomer.

- 10. A method according to any of the above 1 to 9, wherein the adhesive layer is a DAF layer.

- 25 11. A method according to any of the above 1 to 10, further comprising a following step of:

- (e) before the step (b), radiating UV light from an adhesive tape side to the chips whose back surfaces are fixed to the adhesive tape.

- 12. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

- (a) supplying a plurality of chips divided in individual chip regions while being arranged substantially in their original two-dimensional layout upon a wafer, to a chip treating apparatus with their back surfaces fixed to an adhesive tape; and (b) vacuum-chucking a surface of a first chip out of the chips to a lower surface of a rubber chip of a chucking collet and, in a state in which the adhesive tape over the back surface of the first chip is vacuum-chucked to an upper surface of a lower base, peeling the adhesive tape from the back surface of the first chip.

the rubber chip containing elastomer as a principal component and having a hardness of 15 or higher and lower than

- 5 13. A method according to the above 12, wherein the hardness is 20 or higher and lower than 40.

- 14. A method according to the above 12 or 13, wherein the elastomer is a thermosetting elastomer.

- 15. A method according to any of the above 12 to 14, wherein the elastomer is a silicone-based elastomer.

- 16. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

- (a) supplying a plurality of chips to a chip pick-up section of a chip treating apparatus;

- (b) in a state in which a surface of a first chip out of the chips supplied to the chip pick-up section is vacuum-chucked to a lower surface of a rubber chip of a chucking collet, conveying the first chip toward a die bonding section of the chip treating apparatus;

- (c) after the step (b), in a state in which mainly the surface of the first chip is chucked to the lower surface of the rubber chip, causing aback surface side of the first chip to be landed over an upper surface of a wiring substrate placed in the die bonding section of the chip treating apparatus; and

- 5 (d) after the step (c), pressing the surface of the first chip downward by the lower surface of the rubber chip, thereby fixing the first chip to the upper surface of the wiring substrate

through an adhesive layer formed between the back surface of the first chip and the upper surface of the wiring substrate,

the rubber chip containing elastomer as a principal component and having a hardness of 15 or higher and lower than 55.

- 17. A method according to the above 16, wherein the hardness of the elastomer is 20 or higher and lower than 40.

- 18. A method according to the above 16 or 17, wherein the elastomer is a thermosetting elastomer.

- 19. A method according to any of the above 16 to 18, wherein the elastomer is a silicone-based elastomer.

- 20. A method according to any of the above 16 to 19, wherein a leak hole is formed in a vacuum suction system provided within a body of the chucking collet and vacuum chucking is carried out in a leaking state through the leak hole.

- 21. A method according to any of the above 16 to 20, wherein the adhesive layer is a DAF layer.

- 22. A method according to any of the above 16 to 21, further comprising a following step of:

- (e) before the step (b), radiating UV light from the adhesive tape side to the chips whose back surfaces are fixed to the adhesive tape.

- 23. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

- (a) supplying a plurality of chips divided in individual chip regions while being arranged in their original two-dimensional layout upon a wafer, to a chip treating apparatus with their back surfaces fixed to an adhesive tape;

- (b) vacuum-chucking a surface of a first chip out of the chips to a lower surface of a rubber chip of the chucking collet and, in a state in which the adhesive tape over the back surface of the first chip is vacuum-chucked to an upper surface of a lower base, peeling the adhesive tape from the back surface of the first chip;

- (c) after the step (b), conveying the first chip toward a die bonding section of the chip treating apparatus in a state in which the surface of the first chip is chucked to the lower surface of the rubber chip of the chucking collet;

- (d) after the step (c), causing the back surface side of the first chip to be landed over an upper surface of a wiring substrate placed in the die bonding section of the chip treating apparatus in a state in which the surface of the first chip is chucked to the lower surface of the rubber chip; and

- (e) after the step (d), pressing the surface of the first chip by the lower surface of the rubber chip, thereby fixing the first chip to the upper surface of the wiring substrate through an adhesive layer formed between the back surface of the first chip and the upper surface of the wiring substrate,

the rubber chip containing elastomer as a principal component and having a hardness of 15 or higher and lower than 55.

- 24. A method according to the above 23, wherein the hardness is 20 or higher and lower than 40.

- 25. A method according to the above 23 or 24, wherein the elastomer is a thermosetting elastomer.

- 26. A method according to any of the above 23 to 25, wherein the elastomer is a silicone-based elastomer.

- 27. A method according to any of the above 23 to 26, wherein 60 a leak hole is formed in a vacuum suction system provided within a body of the chucking collet and vacuum chucking is performed in a leaking state through the leak hole.

- 28. A method according to any of the above 23 to 27, wherein the adhesive layer is a DAF layer.

- 29. A method according to any of the above 23 to 28, further comprising a following step of:

14

- (e) before the step (b), radiating UV light to the chips from the adhesive tape side of the chips whose back surfaces are fixed to the adhesive tape.

- 30. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

- (a) supplying a plurality of chips to a chip pick-up section of a chip treating apparatus;

- (b) in a state in which a surface of a first chip out of the chips supplied to the chip pick-up section is vacuum-chucked to a lower surface of a rubber chip of a chucking collet, conveying the first chip toward a die bonding section of the chip treating apparatus;

- (c) after the sep (b), in a state in which the surface of the first chip is chucked to the lower surface of the rubber chip, causing a back surface side of the first chip to be landed over an upper surface of a wiring substrate placed in the die bonding section of the chip treating apparatus; and

- (d) after the step (c) pressing the surface of the first chip downward by the lower surface of the rubber chip, thereby

fixing the first chip to the upper surface of the wiring substrate through an adhesive layer formed between the back surface of the first chip and the upper surface of the wiring substrate,

the rubber chip having a central vacuum suction hole, containing elastomer as a principal component and having a hardness of 10 or higher and lower than 70.

- 31. A method according to the above 30, wherein the elastomer is a thermosetting elastomer.

- 32. A method according to the above 30 or 31, wherein the elastomer is a silicone-based elastomer.

- 33. A method according to any of the above 30 to 32, wherein a leak hole is formed in a vacuum suction system provided within a body of the chucking collet and vacuum chucking is performed in a leaking state through the leak hole.

- 34. A method according to any of the above 30 to 33, wherein the adhesive layer is a DAF member layer.

- 35. A method according to any of the above 30 to 34, further comprising a following step of:

- (e) before the step (b), radiating UV light to the chips from the adhesive tape side of the chips whose back surfaces are fixed to the pressure-sensitive adhesive tape.

- 36. A method according to any of the above 30 to 35, wherein the chucking to the lower surface of the rubber chip in the step (c) is done mainly by physical chucking.

- 37. A method according to any of the above 30 to 36, wherein the vacuum chucking is turned OFF in the steps (c) to (d).

- 38. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

- (a) supplying a plurality of chips to a chip pick-up section of a chip treating apparatus;

- (b) in a state in which a surface of a first chip out of the chips supplied to the chip pick-up section is vacuum-chucked to a lower surface of a rubber chip of a chucking collet, conveying the first chip toward a die bonding section of the chip treating apparatus;

- (c) after the step (b), in a state in which mainly the surface of the first chip is chucked to the lower surface of the rubber chip, causing aback surface side of the first chip to be landed over an upper surface of a wiring substrate placed in the die bonding section of the chip treating apparatus; and

- (d) after the step (c), pressing the surface of the first chip downward by the lower surface of the rubber chip, thereby fixing the first chip to the upper surface of the wiring substrate through an adhesive layer formed between the back surface of the first chip and the upper surface of the wiring substrate,

- wherein a leak hole is formed in a vacuum suction system provided within a body of the chucking collet and vacuum chucking is carried out in a leaking state through the leak hole.

- 39. A method according to the above 38, wherein the rubber chip has a central vacuum suction hole and containing elastomer as a principal component, the elastomer having a hardness of 10 or higher and lower than 70.

- 40. A method according to the above 38 or 39, wherein the <sup>5</sup> adhesive layer is a DAF layer.

- 41. A method according to any of the above 38 to 40, further comprising a following step of:

- (e) before the step (b), radiating UV light to the chips from the adhesive tape side of the chips whose back surfaces are fixed to the adhesive tape.

- 42. A method according to any of the above 38 to 41, wherein the chucking to the lower surface of the rubber chip in the step(c) is done mainly by physical chucking.

- 43. A method according to any of the above 38 to 42, wherein the vacuum chucking is turned OFF in the steps (c) to (d).

- 44. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

- (a) supplying a plurality of chips to a chip pick-up section of 20 a chip treating apparatus;

- (b) in a state in which a surface of a first chip out of the chips supplied to the chip pick-up section is vacuum-chucked to a lower surface of a rubber chip of a chucking collet, conveying the first chip toward a die bonding section of the chip treating 25 apparatus;

- (c) after the step (b), in a state in which mainly the surface of the first chip is held by physical chucking between it and the lower surface of the rubber chip, causing a back surface side of the first chip to be landed over an upper surface of a wiring substrate placed in the die bonding section of the chip treating apparatus;

- (d) after the step (c), pressing the surface of the first chip downward by the lower surface of the rubber chip, thereby fixing the first chip to the upper surface of the wiring substrate through an adhesive layer formed between the back surface of the first chip and the upper surface of the wiring substrate;

- (e) in a state in which a surface of a second chip out of the chips supplied to the chip pick-up section is vacuum-chucked 40 to the lower surface of the rubber chip of the chucking collet, conveying the second chip toward the die bonding section of the chip treating apparatus;

- (f) after the step (e), in a state in which mainly the surface of the second chip is held by physical chucking between it and 45 the lower surface of the rubber chip, causing a back surface side of the second chip to be landed over the upper surface of the wiring substrate placed in the die bonding section of the chip treating apparatus;

- (g) after the step (f), pressing the surface of the second chip 50 downward by the lower surface of the rubber chip, thereby fixing the second chip to the upper surface of the wiring substrate through the adhesive layer formed between the back surface of the first chip and the upper surface of the wiring substrate; and

- (h) after the step (g), pressing the surface side of the first chip and that of the second chip together by a member different from the collet to accelerate theremocompression bonding thereof with the upper surface of the wiring substrate.

- 45. A method according to the above 44, wherein the rubber 60 chip has a central vacuum suction hole, contains elastomer as a principal component and has a hardness of 10 or higher and lower than 70.

- 46. A method according to the above 44 or 45, wherein the adhesive layer is a DAF layer.

- 47. A method according to any of the above 44 to 46, further comprising a following step of:

16

- (e) before the step (b), radiating UV light to the chips from the adhesive tape side of the chips whose back surfaces are fixed to the adhesive tape.

- 48. A method according to any of the above 44 to 47, wherein the chucking to the lower surface of the rubber chip in the steps (c) and (f) is done mainly by physical chucking.

- 49. A method according to any of the above 44 to 48, wherein the vacuum chucking is turned OFF in the steps (c) to (d) and (f) to (g).

- o 50. A method according to any of the above 44 and 46 to 49, wherein the rubber chip contains elastomer as a principal component and has a hardness of 10 or higher and lower than 70

Next, further embodiments of the present invention as dis-15 closed herein will be outlined below.

- 51. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

- (a) supplying a plurality of chips divided in individual chip regions while being arranged substantially in their original two-dimensional layout upon a wafer, to a chip treating apparatus with their back surfaces fixed to an adhesive tape; and (b) vacuum-chucking a surface of a first chip out of the chips to a lower surface of a rubber chip of a chucking collet and peeling the adhesive tape from the back surface of the first chip in a state in which the adhesive tape over the back surface of the first chip is vacuum-chucked to an upper surface of a lower base,

the step (b) comprising a following sub-step of:

(b1) monitoring a bent state of the first chip before complete separation of the first chip from the adhesive tape by measuring the flow rate of a vacuum chucking system in the chucking collet

the rubber chip containing elastomer as a principal component and having a hardness of 10 or higher and lower than 70.

- 52. A method according to the above 51, wherein the step (b) further comprises the following sub-steps of:

- (b2) continuing or interrupting the peeling operation on the basis of the monitor information obtained in the sub-step (b1); and

- (b3) in case of interrupting the peeling operation, resuming the peeling operation on the basis of the monitor information obtained in the sub-step (b1)

- 53. A method according to the above 51 or 52, wherein the step (b) further comprises the following sub-steps of:

- (b4) continuing or decelerating the peeling operation on the basis of the monitor information obtained in the sub-step (b1); and

- (b5) in case of decelerating the peeling operation, re-accelerating the peeling operation on the basis of the monitor information obtained in the sub-step (b1).

- 54. A method according to any of the above 51 to 53, wherein the step (b) further comprises a following sub-step of:

- (b6) on the basis of the monitor information obtained in the sub-step (b1), continuing the peeling operation, or retreating the peeling operation until the bent state of the first chip falls under an allowable range.

- 55. A method according to any of the above 51 to 54, wherein the step (b) further comprises a following sub-step of:

- (b7) on the basis of the monitor information obtained in the sub-step (b1), continuing the peeling operation, or decelerating the peeling operation until the bent state of the first chip falls under an allowable range.

- 56. A method according to any of the above 51 to 55, wherein the step (b) further comprises the following sub-steps of:

- (b8) raising the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b9) after the sub-step (b8) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise of the chucking collet, or bringing down the chucking collet until the bent state of the first chip falls under the allowable range.

- 57. A method according to any of the above 51 to 56, wherein the step (b) further comprises the following sub-steps of: (b10) raising the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b11) after the sub-step (b10) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise of the chucking collet, or making the chucking collet stand by until the bent state of the first chip falls under the allowable range

- 58. A method according to any of the above 51 to 57, wherein the step (b) further comprises the following sub-steps of: (b12) raising the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b13) after the sub-step (b12) and on the basis of the monitor 20 information obtained in the sub-step (b1), continuing the rise of the chucking collet, or decelerating the chucking collet until the bent state of the first chip falls under the allowable range.

- 59. A method according to any of the above 51 to 58, wherein 25 the step (b) further comprises the following sub-steps of:

- (b14) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

- (b15) after the sub-step (b14), bringing down only the stickup block out of the stick-up block and the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b16) after the sub-step (b15) and on the basis of the monitor information obtained in the sub-step (b1), continuing the descent of the stick-up block, or raising the stick-up block until the bent state of the first chip falls under the allowable range.

- 60. A method according to any of the above 51 to 59, wherein the step (b) further comprises the following sub-steps of:

- (b17) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

- (b18) after the sub-step (b17), bringing down only the stickup block out of the stick-up block and the chucking collet until the bent state of the first chip exceeds an allowable 45 range; and

- (b19) after the sub-step (b18) and on the basis of the monitor information obtained in the sub-step (b1), continuing the descent of the stick-up block, or making the stick-up block standby until the bent state of the first chip falls under the allowable range.

- 61. A method according to any of the above 51 to 60, wherein the step (b) further comprises the following steps of:

- (b20) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

- (b21) after the sub-step (b20), bringing down only the stickup block out of the stick-up block and the chucking collet until the bent state of the first chip exceeds an allowable range; and

- (b22) after the sub-step (b21) and on the basis of the monitor information obtained in the sub-step (b1), continuing the descent of the stick-up block, or decelerating the descent of the stick-up block until the bent state of the first chip falls under the allowable range.

- 62. A method according to any of the above 51 to 61, wherein the step (b) further comprises the following steps of:

18

- (b23) causing a slide plate as a principal portion of the lower base to slide so as to decrease an overlap thereof with the first chip until the bent state of the first chip exceeds an allowable range; and

- (b24) on the basis of the monitor information obtained in the sub-step (b1), making the slide plate stand by until the bent state of the first chip falls under the allowable range.

- 63. A method according to any of the above 51 to 62, wherein the step (b) further comprises the following sub-steps of:

- (b25) continuing or interrupting the peeling operation on the basis of the monitor information obtained in the sub-step (b1); and

- (b26) in case of interrupting the peeling operation, resuming the peeling operation, or retreating the peeling operation until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the substep (b1).

- 64. A method according to any of the above 51 to 63, wherein the step (b) further comprises the following sub-steps of:

- (b27) continuing or decelerating the peeling operation on the basis of the monitor information obtained in the sub-step (b1); and

- (b28) in case of decelerating the peeling operation, re-accelerating the peeling operation, or retreating the peeling operation until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

- 65. A method according to any of the above 51 to 64, wherein the step (b) further comprises the following sub-steps of:

- (b29) raising the chucking collet until the bent state of the first chip falls under an allowable range;

- (b30) after the sub-step (b29) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise of the chucking collet, or making the chucking collet stand by until the bent state of the first chip falls under the allowable range; and

- (b31) in case of making the chucking collet standby until the bent state of the first chip falls under the allowable range, resuming the rise of the chucking collet, or bringing down the chucking collet until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

- 66. A method according to any of the above 51 to 65, wherein the step (b) further comprises the following sub-steps of:

- (b32) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

- (b33) after the step (b32), bringing down only the stick-up block out of the stick-up block and the chucking collet until the bent state of the first chip exceeds an allowable range;

- (b34) after the sub-step (b33) and on the basis of the monitor information obtained in the sub-step (b1), continuing the descent of the stick-up block, or making the stick-up block standby until the bent state of the first chip falls under the allowable range; and

- (b35) in case of making the stick-up block stand by until the bent state of the first chip falls under the allowable range, resuming the descent of the stick-up block, or raising the stick-up block until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

- 67. A method according to any of the above 51 to 66, wherein the step (b) further comprises the following sub-steps of:

- (b36) raising the chucking collet until the bent state of the first chip exceeds an allowable range;

- (b37) after the sub-step (b36) and on the basis of the monitor information obtained in the sub-step (b1), continuing the rise

of the chucking collet, or decelerating the chucking collet until the bent state of the first chip falls under the allowable

(b38) in case of decelerating the chucking collet until the bent state of the first chip falls under the allowable range, resuming 5 the rise of the chucking collet, or bringing down the chucking collet until the bent state of the first chip falls under the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

68. A method according to any of the above 51 to 67, wherein 10 the step (b) further comprises the following sub-steps of:

(b39) raising a stick-up block as a principal portion of the lower base together with the chucking collet;

(b40) after the step (b), bringing down only the stick-up block out of the stick-up block and the chucking collet until the bent 15 state of the first chip exceeds an allowable range;

(b41) after the sub-step (b40) and on the basis of the monitor information obtained in the sub-step (b1), continuing the descent of the stick-up block, or decelerating the descent of the stick-up block until the bent state of the first chip falls 20 under the allowable range; and

(b42) in case of making the stick-up block stand by until the bent state of the first chip falls under the allowable range, resuming the descent of the stick-up block, or raising the stick-up block until the bent state of the first chip falls under 25 the allowable range, on the basis of the monitor information obtained in the sub-step (b1).

69. A method according to any of the above 51 to 68, wherein an adhesive layer for die bonding is formed beforehand over the back surface of the first chip.

70. A method according to any of the above 51 to 69, wherein the elastomer has a hardness of 15 or higher and lower than 55.

71. A method according to any of the above 51 to 69, wherein the elastomer has a hardness of 20 or higher and lower than 35

Still further embodiments of the present invention as disclosed herein will be outlined below.

1. A method for manufacturing a semiconductor integrated circuit device, comprising the steps of:

(a) supplying a plurality of chips divided in individual chip regions while being arranged substantially in their original two-dimensional layout upon a wafer, to a chip treating apparatus with their back surfaces fixed to an adhesive tape;

(b) vacuum-chucking a surface of a first chip out of the chips 45 to a lower surface of a rubber chip of a chucking collet and peeling the adhesive tape from the back surface of the first chip in a state in which the adhesive tape over the back surface of the first chip is vacuum-chucked to an upper surface of a lower base,

the rubber chip containing elastomer as a principal component and having the following portions:

(i) a rubber chip main portion including a central part;

(ii) a plurality of vacuum suction holes formed in the peripheral portion of the rubber chip and extending through the 55 rubber chip main portion from an upper to a lower surface of the main portion; and

(iii) a ring-like rubber chip peripheral portion extending around the rubber chip main portion and having a thickness smaller than that of the rubber chip main portion.

2. A method according to the above 1, wherein the rubber chip further has the following portion:

(iv) a singular or plural vacuum suction grooves formed in a lower surface of the rubber chip peripheral portion and coupled with the vacuum suction holes.

3. A method according to the above 1 or 2, wherein the rubber chip has the following portion:

20

(v) the rubber chip peripheral portion lying on the lower surface side of the rubber chip main portion.

4. A method according to any of the above 1 to 3, wherein the rubber chip further has the following portion:

(vi) a ring-like groove formed between upper and lower surfaces of the rubber chip peripheral portion.

5. A method according to any of the above 1 to 4, wherein the rubber chip has a hardness of 10 or higher and lower than 70. 6. A method according to any of the above 1 to 4, wherein the rubber chip has a hardness of 15 or higher and lower than 55. 7. A method according to any of the above 1 to 4, wherein the rubber chip has a hardness of 25 or higher and lower than 65. 8. A method according to any of the above 1 to 7, wherein the peeling of the first chip from the adhesive tape in the step (b) is carried out by stick-up of a portion of the lower base toward

the first chip, the portion being located just under the first

9. A method according to any of the above 1 to 7, wherein the peeling of the first chip from the pressure-sensitive adhesive in the step (b) is carried out by sideways retraction of a portion of the lower base from under the first chip, the portion being located just under the first chip.

[Description Form, Basic Terms, and how to Use, in the Present Application]

1. An embodiment of the present invention may be described dividedly into plural sections where required for the sake of convenience, but unless otherwise mentioned, it is to be understood that the divided sections are not independent of each other, but constitute portions of a single example, or in a relation such that one is a partial detail of the other or is a modification of part or the whole of the other. As to similar portions, repetition thereof is omitted in principle. Constituent elements in an embodiment are not essential unless otherwise mentioned and except the case where they are limited theoretically to specified numbers thereof, further, except the case where they are clearly essential contextually.

2. Likewise, in the description of an embodiment or the like, as to "X comprising A" or the like with respect to material and composition, selection of any other element than A as one of principal constituent elements is not excluded unless otherwise mentioned and except the case where an opposite answer is evident contextually. For example, by the above description is meant "X including A as a principal component" when viewed from the standpoint of component. For example, "silicon member" is not limited to pure silicon, but it goes without saying that the silicon member in question covers SiGe alloy, other multi-element alloys containing silicon as a principal component, as well as those containing silicon and other additives.

50 3. Although suitable examples will be shown as to figure, position and attribute, it goes without saying that no strict limitation is made to those examples unless otherwise mentioned and except the case where it is evident contextually that limitation is made thereto.

4. When reference is made to a specific numerical value or quantity, a numerical value larger or smaller than the specific numerical value will also do unless otherwise mentioned and except the case where limitation is made to the specific numerical value theoretically, further, except the case where a negative answer is evident contextually.

5. By "wafer" is usually meant a single crystal silicon wafer with semiconductor integrated circuit devices (also true of semiconductor devices and electronic devices) formed thereon. But it goes without saying that the "wafer" in question covers an epitaxial wafer and composite wafers, e.g., a combination of an insulating substrate and a semiconductor

6. By "chip" or "die" is generally meant a completely separated one after a wafer dividing process (blade dicing, laser dicing or pelletizing process). In the present application, for the sake of convenience, each chip region before separation is also represented by the same term. For example, in the so- 5 called DBG (Dicing before Grinding) process, half-cut dicing is followed by grinding for ultimate separation into chips, then in this state the back surfaces of the chips are affixed to a pressure-sensitive adhesive tape and thereafter the processing flow advances to a peeling process. Taking such a case also into consideration, for example once "wafer" is separated, it is no longer a wafer in a strict sense Likewise, chips before separation correspond to chip regions, not chips, and the time of separation depends on each individual process, so these are comprehensively designated "wafer," "chip," or 15 "die."

21

7. By "wiring substrate" is generally meant a organic wiring substrate, a ceramic wiring substrate, a lead frame, or any other thin film-like integrated circuit device, including chip and wafer. More particularly, the stacking technique of stacking several tens of chips on a chip with use of an adhesive has recently been in wide use and the present invention as disclosed herein is applied to a wide range including such a technique.