(12)

## Patentschrift

(21) Deutsches Aktenzeichen: **11 2014 001 567.9**

(86) PCT-Aktenzeichen: **PCT/JP2014/057947**

(87) PCT-Veröffentlichungs-Nr.: **WO 2014/148640**

(86) PCT-Anmelddatum: **14.03.2014**

(87) PCT-Veröffentlichungstag: **25.09.2014**

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: **03.12.2015**

(45) Veröffentlichungstag

der Patenterteilung: **10.09.2020**

(51) Int Cl.: **G11C 11/405 (2006.01)**

**H01L 21/8242 (2006.01)**

**H01L 27/108 (2006.01)**

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

|                                                                                                       |                                                                   |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| (30) Unionspriorität:<br><b>2013-060687</b> 22.03.2013 JP                                             | (72) Erfinder:<br><b>Onuki, Tatsuya, Atsugi-shi, Kanagawa, JP</b> |

| (73) Patentinhaber:<br><b>SEMICONDUCTOR ENERGY LABORATORY CO., LTD., Atsugi-shi, Kanagawa-ken, JP</b> | (56) Ermittelter Stand der Technik:<br>US 2012 / 0 287 700 A1     |

| (74) Vertreter:<br><b>Grünecker Patent- und Rechtsanwälte PartG mbB, 80802 München, DE</b>            |                                                                   |

### (54) Bezeichnung: Halbleitervorrichtung und Verfahren zum Betreiben der Halbleitervorrichtung

(57) Hauptanspruch: Verfahren zum Betreiben einer Halbleitervorrichtung, die einen ersten Transistor (101), dessen Kanalbereich einen Oxidhalbleiter enthält, einen zweiten Transistor (102) und einen Kondensator (103) beinhaltet, dessen eine Elektrode elektrisch mit einem Anschluss von einer Source und einem Drain des ersten Transistors (101) und einem Gate des zweiten Transistors (102) verbunden ist, wobei das Verfahren umfasst:

Anlegen einer niedrigen Spannung an eine Bitleitung (113) und eine erste Leitung (114), Anlegen einer hohen Spannung an eine Wortleitung (111), um den ersten Transistor (101) einzuschalten, und Anlegen einer niedrigen Spannung an eine Kondensator-Leitung (112), so dass der zweite Transistor (102) eingeschaltet wird, wobei:

die Wortleitung (111) elektrisch mit einem Gate des ersten Transistors (101) verbunden ist,

die erste Leitung (114) elektrisch mit einem Anschluss von einer Source und einem Drain des zweiten Transistors (102) verbunden ist,

die Bitleitung (113) elektrisch mit dem anderen Anschluss von der Source und dem Drain des ersten Transistors (101) und dem anderen Anschluss von der Source und dem Drain des zweiten Transistors (102) verbunden ist, und

die Kondensator-Leitung (112) elektrisch mit der anderen Elektrode des Kondensators (103) verbunden ist;

Anlegen einer ersten Spannung an die erste Leitung (114) und Unterbrechen des Anlegens der niedrigen Spannung

an die Bitleitung (113), so dass eine Spannung, die der ersten Spannung entspricht, von der ...

**Beschreibung**

## Technisches Gebiet

**[0001]** Die vorliegende Erfindung betrifft einen Gegenstand, ein Verfahren oder ein Herstellungsverfahren. Insbesondere betrifft die vorliegende Erfindung beispielsweise eine Halbleitervorrichtung, eine Anzeigevorrichtung, eine Licht emittierende Vorrichtung, eine Energiespeichervorrichtung, ein Betriebsverfahren dafür oder ein Herstellungsverfahren dafür. Im Besonderen betrifft die vorliegende Erfindung beispielsweise eine Halbleitervorrichtung, eine Anzeigevorrichtung oder eine Licht emittierende Vorrichtung, die einen Oxidhalbleiter enthält.

## Stand der Technik

**[0002]** Patentdokument 1 beschreibt eine Halbleitervorrichtung, die einen Transistor mit einem Oxidhalbleiterfilm und einen Transistor mit einkristallinem Silizium beinhaltet. Patentdokument 1 beschreibt es auch, dass ein Transistor mit einem Oxidhalbleiterfilm sehr geringen Sperrleckstrom aufweist. US 2012/0287700 A1 zeigt eine Verstärkerzelle-Halbleiterspeichervorrichtung mit zwei Transistoren und einem Kondensator.

[Patentdokument]

**[0003]** [Patentdokument 1] Japanische Patentoffenlegungsschrift JP 2012- 256 400 A

## Offenbarung der Erfindung

**[0004]** Eine Ausführungsform der vorliegenden Erfindung stellt eine Halbleitervorrichtung zur Verfügung, die ein vorbestimmtes Potential schreiben und lesen kann. Eine Ausführungsform der vorliegenden Erfindung stellt eine Halbleitervorrichtung zur Verfügung, die keinen Prüfvorgang (verify operation) benötigt. Eine Ausführungsform der vorliegenden Erfindung stellt eine Halbleitervorrichtung zur Verfügung, die hohe Halteigenschaften beim Speichern von Multibit-Daten und hohe Zuverlässigkeit aufweist.

**[0005]** Es ist eine Aufgabe einer Ausführungsform der vorliegenden Erfindung, eine Halbleitervorrichtung oder dergleichen mit geringem Sperrstrom bereitzustellen. Eine weitere Aufgabe einer Ausführungsform der vorliegenden Erfindung ist, eine Halbleitervorrichtung oder dergleichen mit geringem Stromverbrauch bereitzustellen. Eine weitere Aufgabe einer Ausführungsform der vorliegenden Erfindung ist, eine Halbleitervorrichtung oder dergleichen bereitzustellen, die eine durchsichtige Halbleiterschicht beinhaltet. Eine weitere Aufgabe einer Ausführungsform der vorliegenden Erfindung ist, eine Halbleitervorrichtung oder dergleichen bereitzu-

stellen, die eine Halbleiterschicht mit hoher Zuverlässigkeit beinhaltet.

**[0006]** Es sei angemerkt, dass die Beschreibungen dieser Aufgaben dem Vorhandensein weiterer Aufgaben nicht im Wege stehen. Bei einer Ausführungsform der vorliegenden Erfindung ist es unnötig, alle Aufgaben zu erfüllen. Weitere Aufgaben werden aus der Erläuterung der Beschreibung, der Zeichnungen, der Patentansprüchen und dergleichen ersichtlich und können davon abgeleitet werden.

**[0007]** Eine Ausführungsform der vorliegenden Erfindung ist eine Halbleitervorrichtung, die einen ersten Transistor, einen zweiten Transistor und einen Kondensator beinhaltet. Ein Bereich, in dem ein Kanal des ersten Transistors gebildet wird, umfasst einen Oxidhalbleiterfilm. Ein Gate des ersten Transistors ist elektrisch mit einer Wortleitung verbunden. Ein Anschluss von einer Source und einem Drain des ersten Transistors ist elektrisch mit einer Bitleitung verbunden. Der andere Anschluss von der Source und dem Drain des ersten Transistors ist elektrisch mit einer Elektrode des Kondensators und einem Gate des zweiten Transistors verbunden. Die andere Elektrode des Kondensators ist elektrisch mit einer Kondensator-Leitung verbunden. Ein Anschluss von einer Source und einem Drain des zweiten Transistors ist elektrisch mit einer ersten Leitung verbunden. Der andere Anschluss von der Source und dem Drain des zweiten Transistors ist elektrisch mit der Bitleitung verbunden. Ein Vorgang zum Schreiben von Daten umfasst einen ersten Schritt und einen zweiten Schritt. In dem ersten Schritt wird eine niedrige Spannung an die Bitleitung und die erste Leitung angelegt, eine hohe Spannung wird an die Wortleitung angelegt, um den ersten Transistor einzuschalten, und eine niedrige Spannung wird an die Kondensator-Leitung angelegt, so dass der zweite Transistor eingeschaltet wird. In dem zweiten Schritt wird eine erste Spannung an die erste Leitung angelegt, und das Anlegen der niedrigen Spannung an die Bitleitung wird unterbrochen. Um die Daten zu speichern, wird eine niedrige Spannung an die Wortleitung angelegt, um den ersten Transistor auszuschalten, eine niedrige Spannung wird an die Bitleitung und die erste Leitung angelegt, und eine hohe Spannung wird an die Kondensator-Leitung angelegt, um den zweiten Transistor auszuschalten. Ein Vorgang zum Lesen von Daten umfasst einen dritten Schritt und einen vierten Schritt. In dem dritten Schritt wird eine hohe Spannung an die erste Leitung angelegt. In dem vierten Schritt wird das Anlegen der hohen Spannung an die erste Leitung unterbrochen, und eine niedrige Spannung wird an die Kondensator-Leitung angelegt. Durch den zweiten Schritt wird eine Spannung, die der ersten Spannung entspricht, von der ersten Leitung an das Gate des zweiten Transistors über die Source und den Drain des zweiten Transistors, die Bitleitung und die Source und den Drain des ersten

Transistors angelegt. Durch den vierten Schritt ändert sich eine Spannung der ersten Leitung von der hohen Spannung zu der ersten Spannung.

**[0008]** Eine Ausführungsform der vorliegenden Erfindung ist eine Halbleitervorrichtung, die einen ersten Transistor, einen zweiten Transistor, einen dritten Transistor und einen Kondensator beinhaltet. Ein Bereich, in dem ein Kanal des ersten Transistors gebildet wird, umfasst einen Oxidhalbleiterfilm. Ein Gate des ersten Transistors ist elektrisch mit einer ersten Wortleitung verbunden. Ein Anschluss von einer Source und einem Drain des ersten Transistors ist elektrisch mit einer Bitleitung verbunden. Der andere Anschluss von der Source und dem Drain des ersten Transistors ist elektrisch mit einer Elektrode des Kondensators und einem Gate des zweiten Transistors verbunden. Eine niedrige Spannung wird an die andere Elektrode des Kondensators angelegt. Ein Anschluss von einer Source und einem Drain des zweiten Transistors ist elektrisch mit einer ersten Leitung verbunden. Der andere Anschluss von der Source und dem Drain des zweiten Transistors ist elektrisch mit einem Anschluss von einer Source und einem Drain des dritten Transistors verbunden. Ein Gate des dritten Transistors ist elektrisch mit einer zweiten Wortleitung verbunden. Der andere Anschluss von der Source und dem Drain des dritten Transistors ist elektrisch mit der Bitleitung verbunden. Ein Vorgang zum Schreiben von Daten umfasst einen ersten Schritt und einen zweiten Schritt. In dem ersten Schritt wird eine niedrige Spannung an die Bitleitung und die erste Leitung angelegt, eine hohe Spannung wird an die erste Wortleitung angelegt, um den ersten Transistor einzuschalten, die niedrige Spannung der Bitleitung wird an das Gate des zweiten Transistors angelegt, um den zweiten Transistor einzuschalten, und eine niedrige Spannung wird an die zweite Wortleitung angelegt, um den dritten Transistor einzuschalten. In dem zweiten Schritt wird die erste Spannung an die erste Leitung angelegt, und das Anlegen der niedrigen Spannung an die Bitleitung wird unterbrochen. Um die Daten zu speichern, wird eine niedrige Spannung an die erste Wortleitung angelegt, um den ersten Transistor auszuschalten, eine niedrige Spannung wird an die Bitleitung und die erste Leitung angelegt, und eine hohe Spannung wird an die zweite Wortleitung angelegt, um den dritten Transistor auszuschalten. Ein Vorgang zum Lesen der Daten umfasst einen dritten Schritt und einen vierten Schritt. In dem dritten Schritt wird eine hohe Spannung an die erste Leitung angelegt. In dem vierten Schritt wird das Anlegen der hohen Spannung an die erste Leitung unterbrochen, und eine niedrige Spannung wird an die zweite Wortleitung angelegt, um den dritten Transistor einzuschalten. Durch den zweiten Schritt wird eine Spannung, die der ersten Spannung entspricht, von der ersten Leitung an das Gate des zweiten Transistors über die Source und den Drain des zweiten Transistors, die Source und den Drain des

dritten Transistors, die Bitleitung und die Source und den Drain des ersten Transistors angelegt. Durch den vierten Schritt ändert sich eine Spannung der ersten Leitung von der hohen Spannung zu der ersten Spannung.

**[0009]** Eine Ausführungsform der vorliegenden Erfindung ist eine Halbleitervorrichtung, die einen ersten Transistor, einen zweiten Transistor und einen Kondensator beinhaltet. Ein Bereich, in dem ein Kanal des ersten Transistors gebildet wird, umfasst einen Oxidhalbleiterfilm. Ein Gate des ersten Transistors ist elektrisch mit einer Wortleitung verbunden. Ein Anschluss von einer Source und einem Drain des ersten Transistors ist elektrisch mit einer Bitleitung verbunden. Der andere Anschluss von der Source und dem Drain des ersten Transistors ist elektrisch mit einer Elektrode des Kondensators und einem Gate des zweiten Transistors verbunden. Die andere Elektrode des Kondensators ist elektrisch mit einer Kondensator-Leitung verbunden. Ein Anschluss von einer Source und einem Drain des zweiten Transistors ist elektrisch mit einer ersten Leitung verbunden. Der andere Anschluss von der Source und dem Drain des zweiten Transistors ist elektrisch mit der Bitleitung verbunden. Ein Vorgang zum Schreiben von Daten umfasst einen ersten Schritt und einen zweiten Schritt. In dem ersten Schritt wird eine hohe Spannung an die Bitleitung und die erste Leitung angelegt, eine hohe Spannung wird an die Wortleitung angelegt, um den ersten Transistor einzuschalten, und eine hohe Spannung wird an die Kondensator-Leitung angelegt, so dass der zweite Transistor eingeschaltet wird. In dem zweiten Schritt wird eine erste Spannung an die erste Leitung angelegt, und das Anlegen der hohen Spannung an die Bitleitung wird unterbrochen. Um die Daten zu speichern, wird eine niedrige Spannung an die Wortleitung angelegt, um den ersten Transistor auszuschalten, eine hohe Spannung wird an die Bitleitung und die erste Leitung angelegt, und eine niedrige Spannung wird an die Kondensator-Leitung angelegt, um den zweiten Transistor auszuschalten. Ein Vorgang zum Lesen der Daten umfasst einen dritten Schritt und einen vierten Schritt. In dem dritten Schritt wird eine niedrige Spannung an die erste Leitung angelegt. In dem vierten Schritt wird das Anlegen der niedrigen Spannung an die erste Leitung unterbrochen, und eine hohe Spannung wird an die Kondensator-Leitung angelegt. Durch den zweiten Schritt wird eine Spannung, die der ersten Spannung entspricht, von der ersten Leitung an das Gate des zweiten Transistors über die Source und den Drain des zweiten Transistors, die Bitleitung und die Source und den Drain des ersten Transistors angelegt. Durch den vierten Schritt ändert sich eine Spannung der ersten Leitung von der niedrigen Spannung zu der ersten Spannung.

**[0010]** Eine Ausführungsform der vorliegenden Erfindung ist eine Halbleitervorrichtung, die einen ers-

ten Transistor, einen zweiten Transistor, einen dritten Transistor und einen Kondensator beinhaltet. Ein Bereich, in dem ein Kanal des ersten Transistors gebildet wird, umfasst einen Oxidhalbleiterfilm. Ein Gate des ersten Transistors ist elektrisch mit einer ersten Wortleitung verbunden. Ein Anschluss von einer Source und einem Drain des ersten Transistors ist elektrisch mit einer Bitleitung verbunden. Der andere Anschluss von der Source und dem Drain des ersten Transistors ist elektrisch mit einer Elektrode des Kondensators und einem Gate des zweiten Transistors verbunden. Eine niedrige Spannung wird an die andere Elektrode des Kondensators angelegt. Ein Anschluss von einer Source und einem Drain des zweiten Transistors ist elektrisch mit einer ersten Leitung verbunden. Der andere Anschluss von der Source und dem Drain des zweiten Transistors ist elektrisch mit einem Anschluss von einer Source und einem Drain des dritten Transistors verbunden. Ein Gate des dritten Transistors ist elektrisch mit einer zweiten Wortleitung verbunden. Der andere Anschluss von der Source und dem Drain des dritten Transistors ist elektrisch mit der Bitleitung verbunden. Ein Vorgang zum Schreiben von Daten umfasst einen ersten Schritt und einen zweiten Schritt. In dem ersten Schritt wird eine hohe Spannung an die Bitleitung und die erste Leitung angelegt, eine hohe Spannung wird an die erste Wortleitung angelegt, um den ersten Transistor einzuschalten, die hohe Spannung der Bitleitung wird an das Gate des zweiten Transistors angelegt, um den zweiten Transistor einzuschalten, und eine hohe Spannung wird an die zweite Wortleitung angelegt, um den dritten Transistor einzuschalten. In dem zweiten Schritt wird die erste Spannung an die erste Leitung angelegt, und das Anlegen der hohen Spannung an die Bitleitung wird unterbrochen. Um die Daten zu speichern, wird eine niedrige Spannung an die erste Wortleitung angelegt, um den ersten Transistor auszuschalten, eine hohe Spannung wird an die Bitleitung und die erste Leitung angelegt, und eine niedrige Spannung wird an die zweite Wortleitung angelegt, um den dritten Transistor auszuschalten. Ein Vorgang zum Lesen der Daten umfasst einen dritten Schritt und einen vierten Schritt. In dem dritten Schritt wird eine niedrige Spannung an die erste Leitung angelegt. In dem vierten Schritt wird eine hohe Spannung an die zweite Wortleitung angelegt, um den dritten Transistor einzuschalten, und das Anlegen der niedrigen Spannung an die erste Leitung wird unterbrochen. Durch den zweiten Schritt wird eine Spannung, die der ersten Spannung entspricht, von der ersten Leitung an das Gate des zweiten Transistors über die Source und den Drain des zweiten Transistors, die Source und den Drain des dritten Transistors, die Bitleitung und die Source und den Drain des ersten Transistors angelegt. Durch den vierten Schritt ändert sich eine Spannung der ersten Leitung von der niedrigen Spannung zu der ersten Spannung.

**[0011]** Eine Ausführungsform der vorliegenden Erfindung ist ein Verfahren zum Betreiben einer Halbleitervorrichtung. Die Halbleitervorrichtung beinhaltet einen ersten Transistor, dessen Kanalbereich einen Oxidhalbleiter enthält, einen zweiten Transistor und einen Kondensator, dessen eine Elektrode elektrisch mit einem Anschluss von einer Source und einem Drain des ersten Transistors und einem Gate des zweiten Transistors verbunden ist. Bei dem Verfahren wird eine erste Spannung an eine Bitleitung und eine zweite Spannung wird an eine Wortleitung angelegt, um den ersten Transistor einzuschalten, und eine dritte Spannung wird an eine Kondensator-Leitung angelegt, so dass der zweite Transistor eingeschaltet wird. Die Wortleitung ist elektrisch mit einem Gate des ersten Transistors verbunden. Die erste Leitung ist elektrisch mit einem Anschluss von einer Source und einem Drain des zweiten Transistors verbunden. Die Bitleitung ist elektrisch mit dem anderen Anschluss von der Source und dem Drain des ersten Transistors und dem anderen Anschluss von der Source und dem Drain des zweiten Transistors verbunden. Die Kondensator-Leitung ist elektrisch mit der anderen Elektrode des Kondensators verbunden. Bei dem Verfahren wird eine vierte Spannung an die erste Leitung angelegt, und das Anlegen der ersten Spannung an die Bitleitung wird unterbrochen, so dass eine Spannung, die der vierten Spannung entspricht, von der ersten Leitung an das Gate des zweiten Transistors über die Source und den Drain des zweiten Transistors, die Bitleitung und die Source und den Drain des ersten Transistors angelegt wird. Eine fünfte Spannung wird an die Wortleitung angelegt, um den ersten Transistor auszuschalten, eine sechste Spannung wird an die Bitleitung und die erste Leitung angelegt, und eine siebte Spannung wird an die Kondensator-Leitung angelegt, um den zweiten Transistor auszuschalten. Eine achte Spannung wird an die erste Leitung angelegt. Das Anlegen der achten Spannung an die erste Leitung wird unterbrochen, und eine neunte Spannung wird an die Kondensator-Leitung angelegt, so dass sich eine Spannung der ersten Leitung von der achten Spannung zu der vierten Spannung ändert.

**[0012]** Bei der einen Ausführungsform der vorliegenden Erfindung ist die zweite Spannung vorzugsweise höher als die fünfte Spannung. Die siebte Spannung ist vorzugsweise höher als die dritte Spannung und die neunte Spannung. Die erste Spannung und die sechste Spannung sind jeweils vorzugsweise eine Stromversorgungsspannung oder eine Bezugsspannung. Die achte Spannung ist vorzugsweise höher als die vierte Spannung.

**[0013]** Bei der einen Ausführungsform der vorliegenden Erfindung ist die zweite Spannung vorzugsweise höher als die fünfte Spannung. Die siebte Spannung ist vorzugsweise niedriger als die dritte Spannung und die neunte Spannung. Die erste Spannung,

die sechste Spannung und die achte Spannung sind jeweils vorzugsweise eine Stromversorgungsspannung oder eine Bezugsspannung.

**[0014]** Eine Ausführungsform der vorliegenden Erfindung ist ein Verfahren zum Betreiben einer Halbleitervorrichtung. Die Halbleitervorrichtung beinhaltet einen ersten Transistor, dessen Kanalbereich einen Oxidhalbleiter enthält, einen zweiten Transistor, einen dritten Transistor und einen Kondensator, dessen eine Elektrode elektrisch mit einem Anschluss von einer Source und einem Drain des ersten Transistors und einem Gate des zweiten Transistors verbunden ist. Bei dem Verfahren wird eine erste Spannung an eine Bitleitung und eine erste Leitung angelegt, eine zweite Spannung wird an eine erste Wortleitung angelegt, um den ersten Transistor einzuschalten, die erste Spannung der Bitleitung wird an das Gate des zweiten Transistors angelegt, um den zweiten Transistor einzuschalten, und eine dritte Spannung wird an eine zweite Wortleitung angelegt, um den dritten Transistor einzuschalten. Die erste Wortleitung ist elektrisch mit einem Gate des ersten Transistors verbunden. Die zweite Wortleitung ist elektrisch mit einem Gate des dritten Transistors verbunden. Die erste Leitung ist elektrisch mit einem Anschluss von einer Source und einem Drain des zweiten Transistors verbunden. Ein Anschluss von einer Source und einem Drain des dritten Transistors ist elektrisch mit dem anderen Anschluss von der Source und dem Drain des zweiten Transistors verbunden. Die Bitleitung ist elektrisch mit dem anderen Anschluss von der Source und dem Drain des ersten Transistors und dem anderen Anschluss von der Source und dem Drain des dritten Transistors verbunden. Die andere Elektrode des Kondensators ist elektrisch mit einem Bezugspotentialanschluss oder einem Stromversorgungspotentialanschluss verbunden. Bei dem Verfahren wird eine vierte Spannung an die erste Leitung angelegt, und das Anlegen der ersten Spannung an die Bitleitung wird unterbrochen, so dass eine Spannung, die der vierten Spannung entspricht, von der ersten Leitung an das Gate des zweiten Transistors über die Source und den Drain des zweiten Transistors, die Source und den Drain des dritten Transistors, die Bitleitung und die Source und den Drain des ersten Transistors angelegt wird. Eine fünfte Spannung wird an die erste Wortleitung angelegt, um den ersten Transistor auszuschalten, eine sechste Spannung wird an die Bitleitung und die erste Leitung angelegt, und eine siebte Spannung wird an die zweite Wortleitung angelegt, um den dritten Transistor auszuschalten. Eine achte Spannung wird an die erste Leitung angelegt. Das Anlegen der achten Spannung an die erste Leitung wird unterbrochen, und eine neunte Spannung wird an die zweite Wortleitung angelegt, um den dritten Transistor einzuschalten, so dass sich eine Spannung der ersten Leitung von der achten Spannung zu der vierten Spannung ändert.

**[0015]** Bei der einen Ausführungsform der vorliegenden Erfindung ist die zweite Spannung vorzugsweise höher als die fünfte Spannung. Die siebte Spannung ist vorzugsweise höher als die dritte Spannung und die neunte Spannung. Die sechste Spannung ist vorzugsweise eine Stromversorgungsspannung oder eine Bezugsspannung.

**[0016]** Bei der einen Ausführungsform der vorliegenden Erfindung ist die zweite Spannung vorzugsweise höher als die fünfte Spannung. Die siebte Spannung ist vorzugsweise niedriger als die dritte Spannung und die neunte Spannung. Die sechste Spannung und die achte Spannung sind jeweils vorzugsweise eine Stromversorgungsspannung oder eine Bezugsspannung.

**[0017]** Bei einer Halbleitervorrichtung einer Ausführungsform der vorliegenden Erfindung können Schwankungen einer Lesespannung gering sein. Eine Halbleitervorrichtung einer Ausführungsform der vorliegenden Erfindung benötigt keinen Prüfvorgang. Eine Halbleitervorrichtung einer Ausführungsform der vorliegenden Erfindung weist hohe Halteigenschaften beim Speichern von Multibit-Daten und hohe Zuverlässigkeit auf.

#### Figurenliste

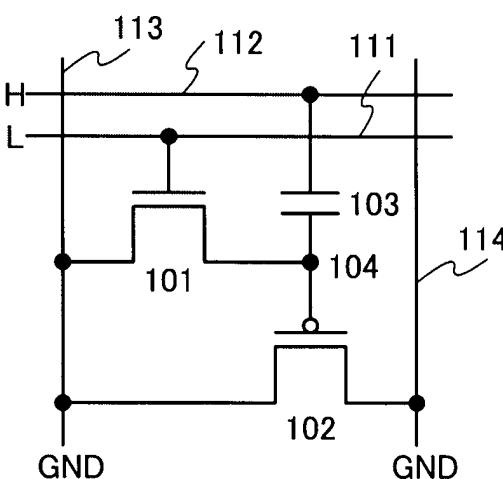

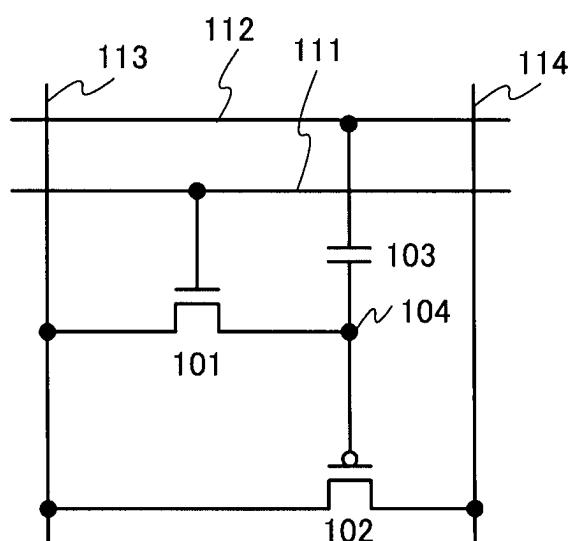

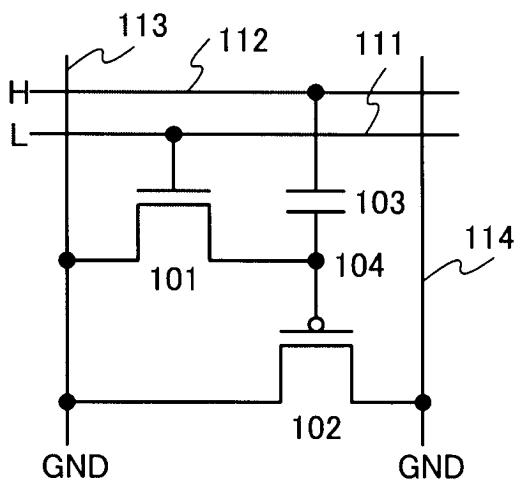

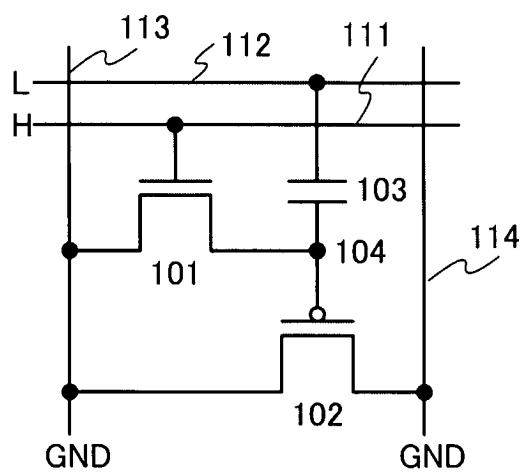

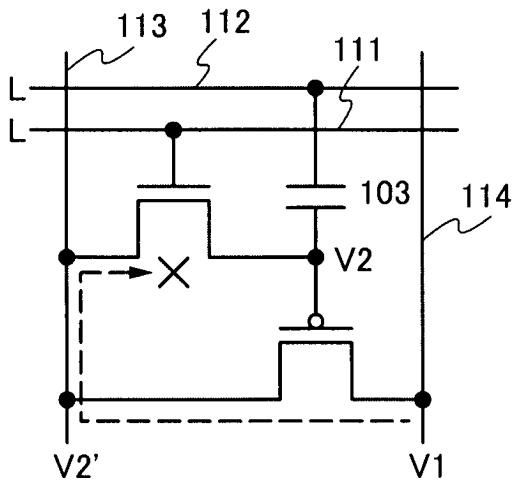

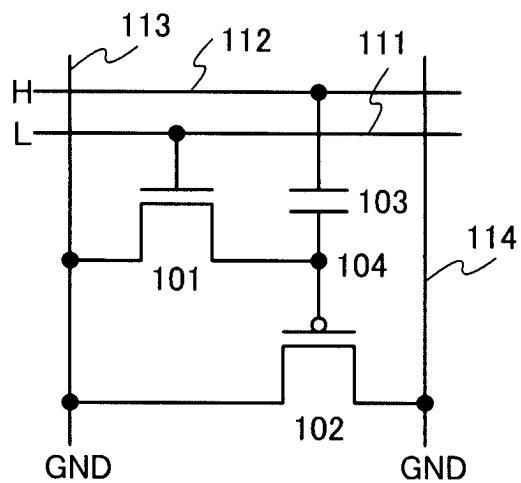

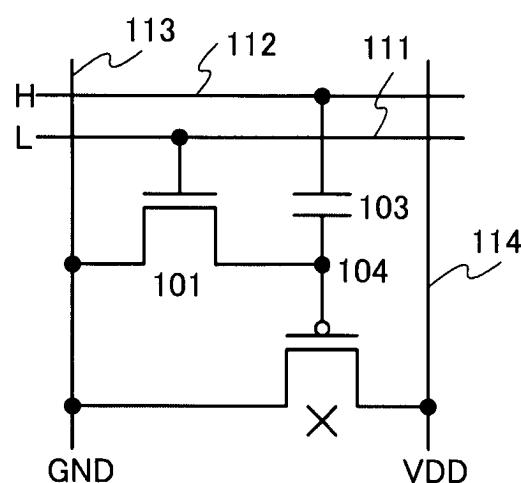

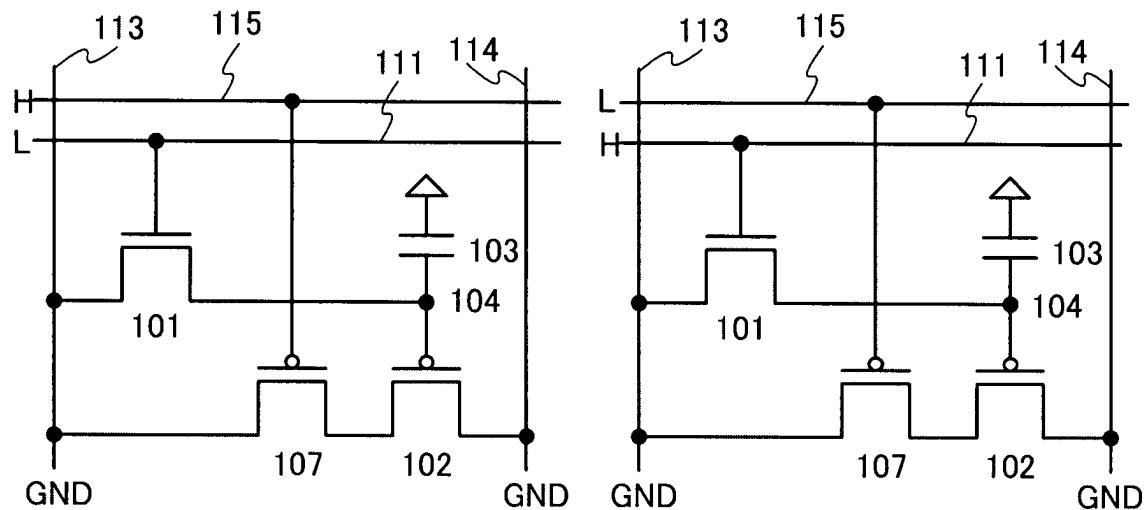

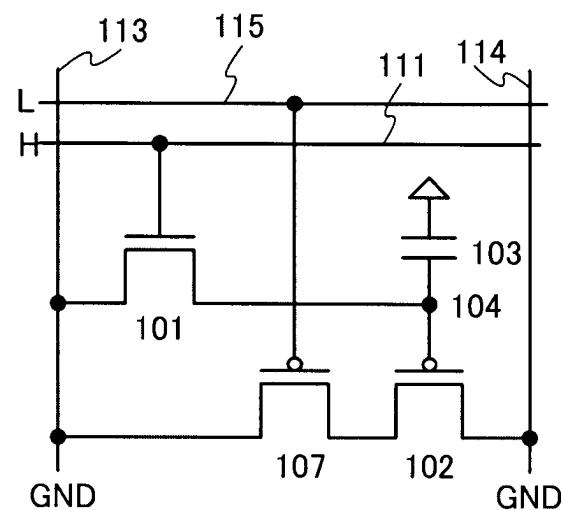

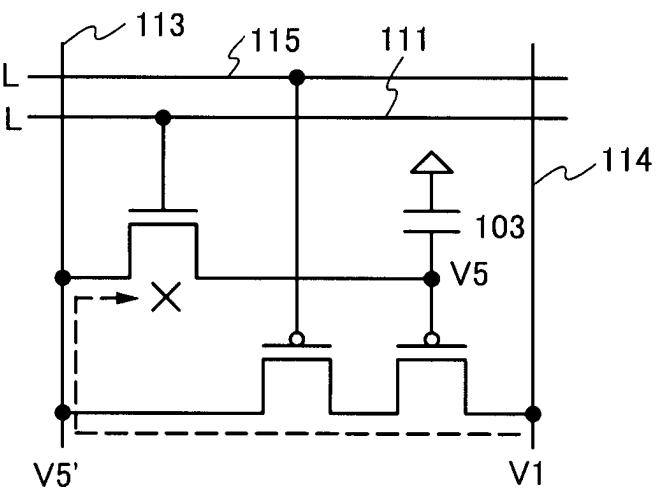

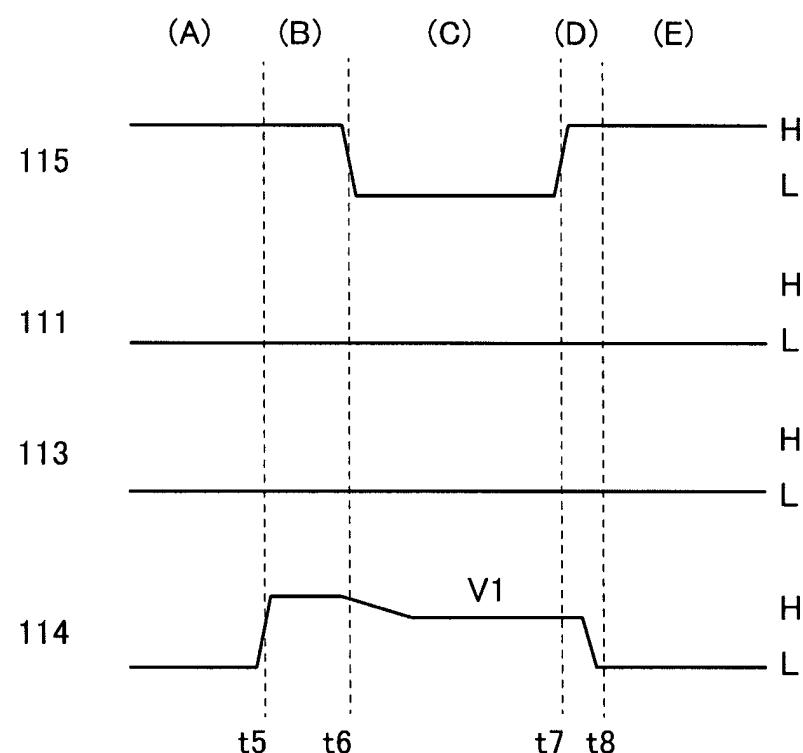

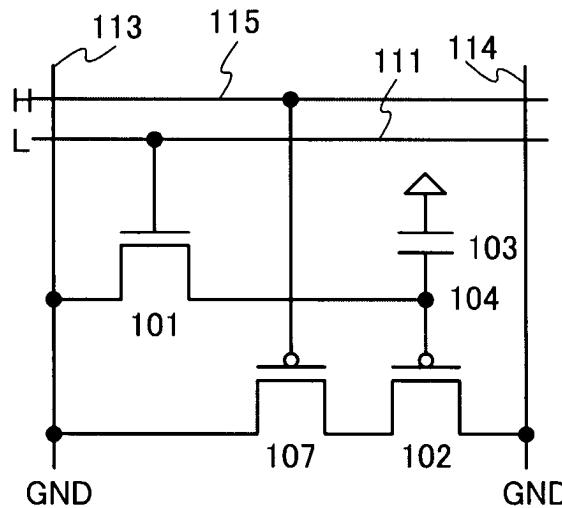

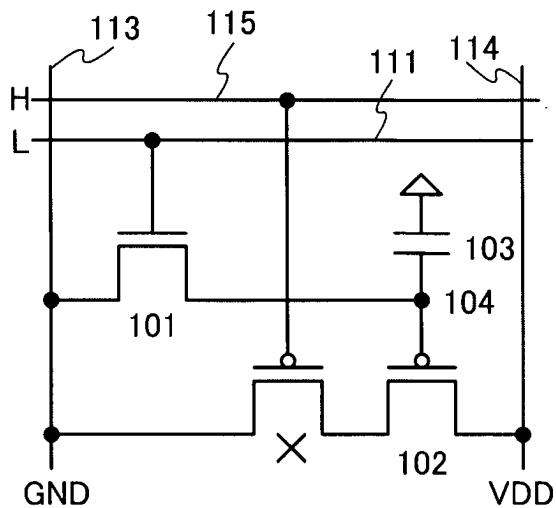

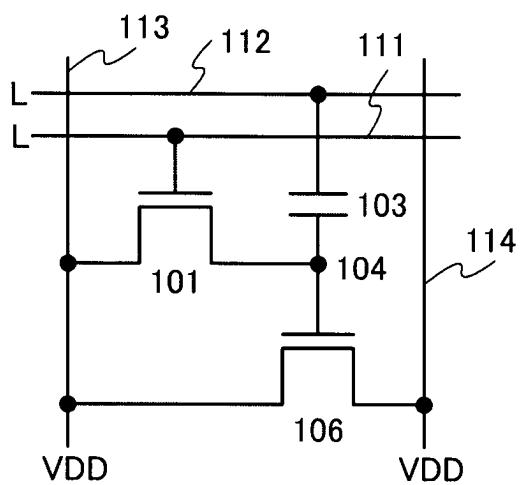

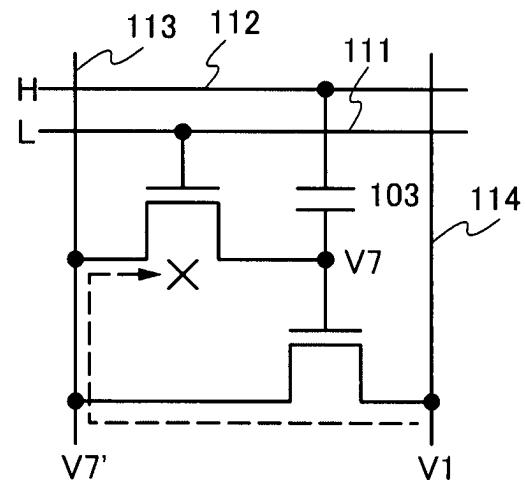

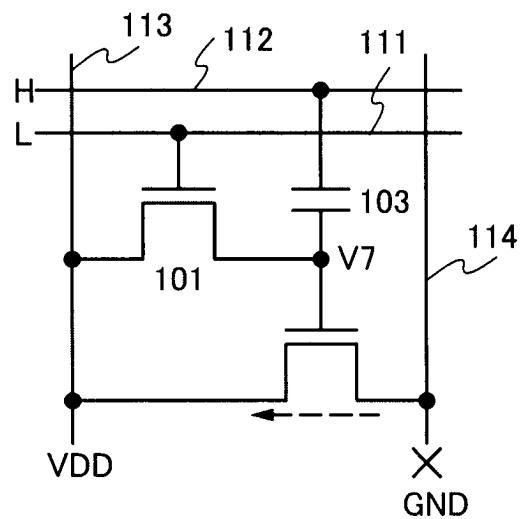

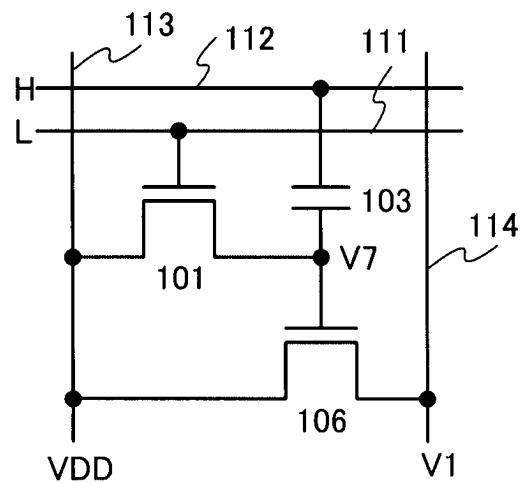

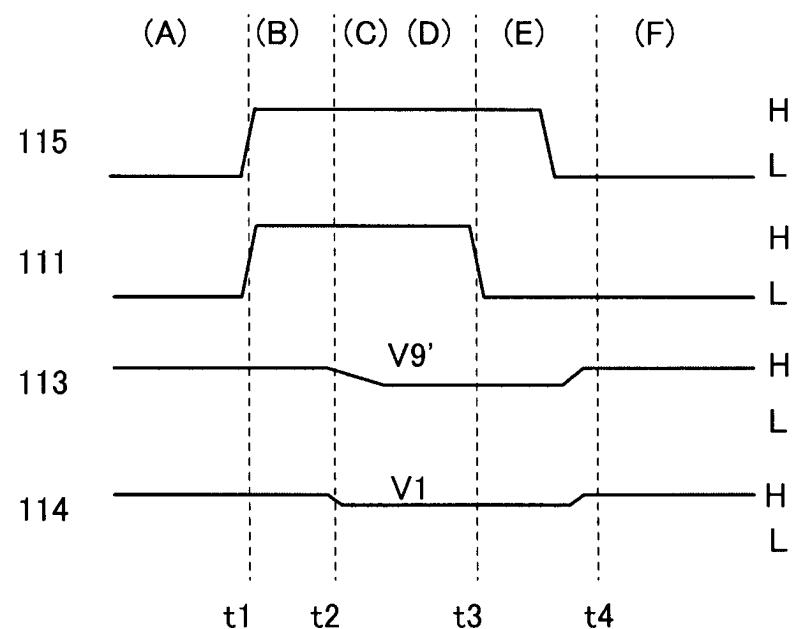

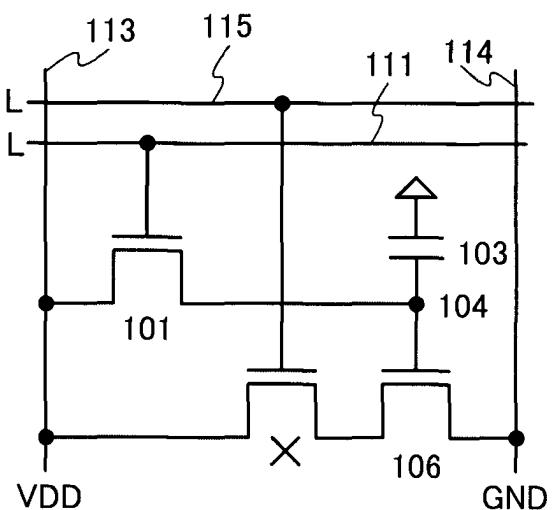

**Fig. 1** ist ein Schaltplan einer Halbleitervorrichtung.

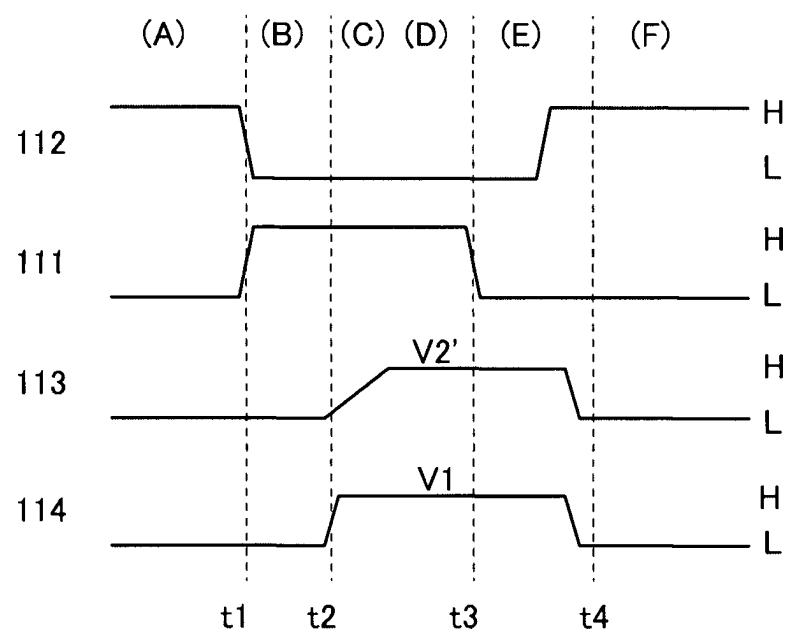

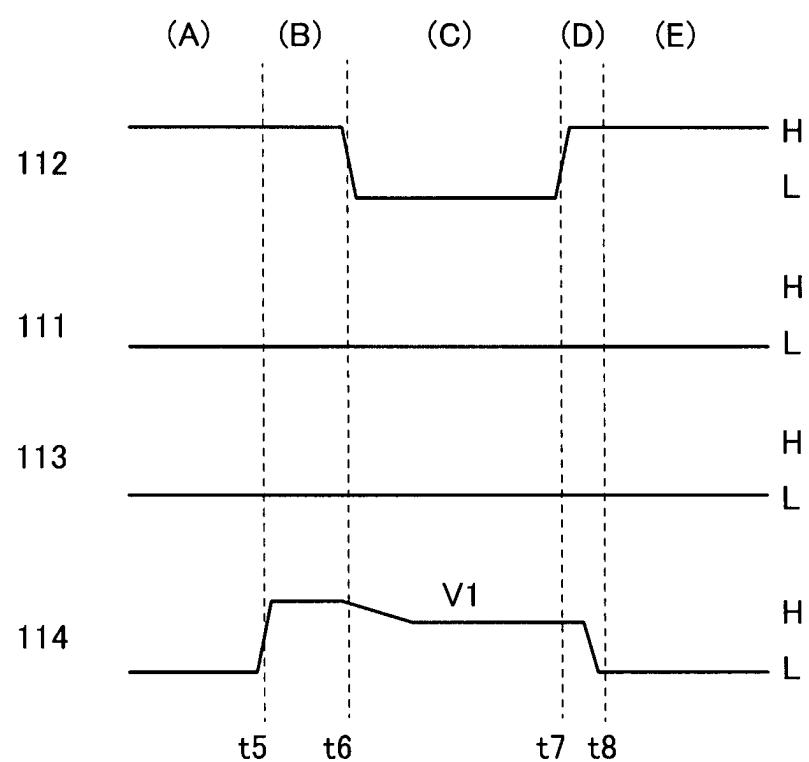

**Fig. 2** ist ein Ablaufdiagramm.

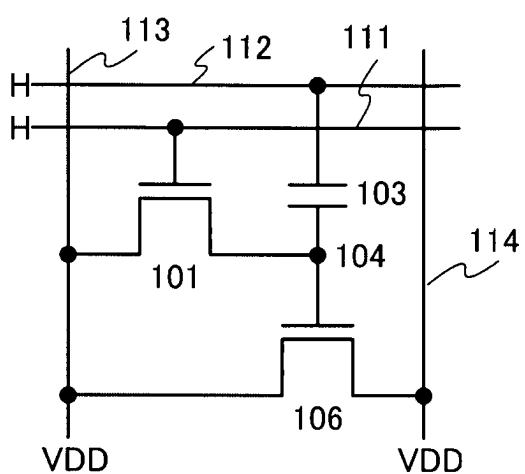

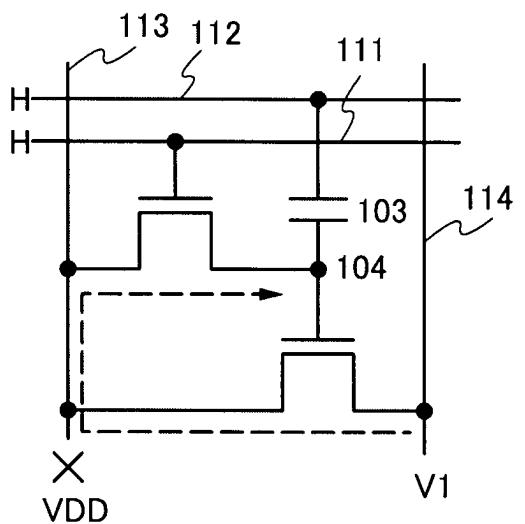

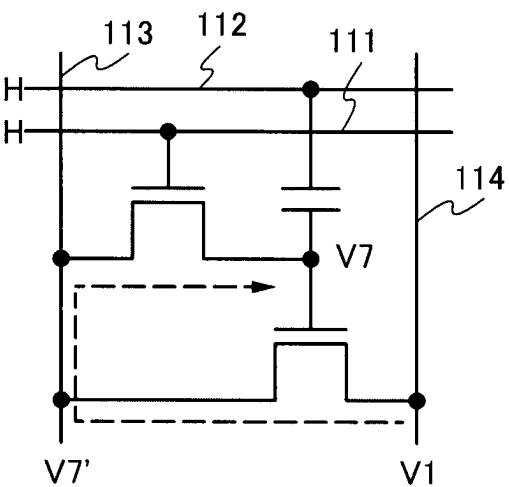

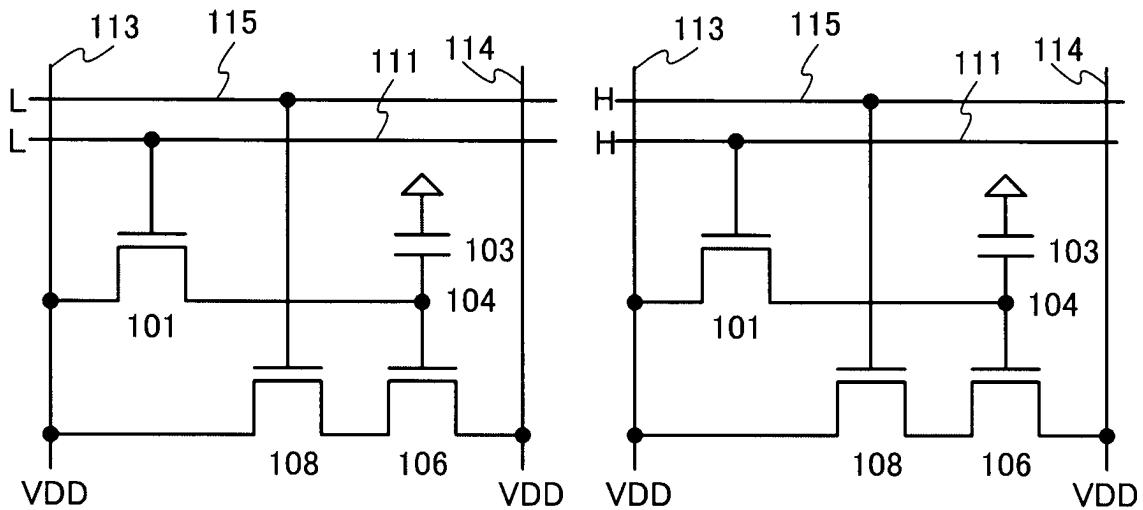

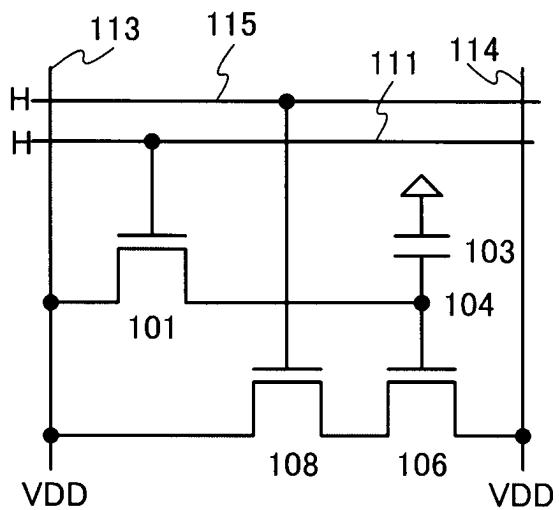

**Fig. 3A** bis **Fig. 3E** zeigen eine Arbeitsweise einer Halbleitervorrichtung.

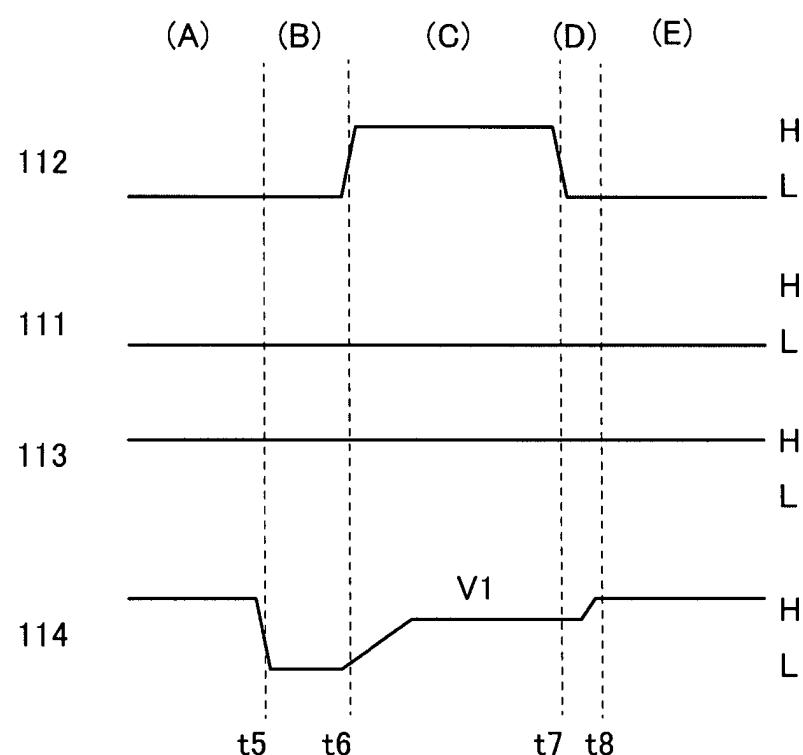

**Fig. 4** ist ein Ablaufdiagramm.

**Fig. 5A** bis **Fig. 5D** zeigen eine Arbeitsweise einer Halbleitervorrichtung.

**Fig. 6** ist ein Schaltplan einer Halbleitervorrichtung.

**Fig. 7** ist ein Schaltplan eines Zeilenauswahltreibers (row selection driver).

**Fig. 8** ist ein Schaltplan eines Spaltenauswahltreibers (column selection driver).

**Fig. 9** ist ein Schaltplan eines A/D-Wandlers.

**Fig. 10** ist ein Schaltplan einer Halbleitervorrichtung.

**Fig. 11** ist ein Ablaufdiagramm.

**Fig. 12** ist ein Ablaufdiagramm.

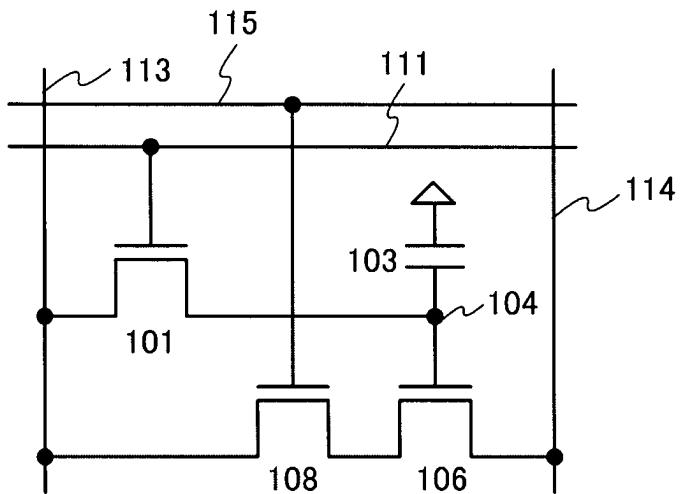

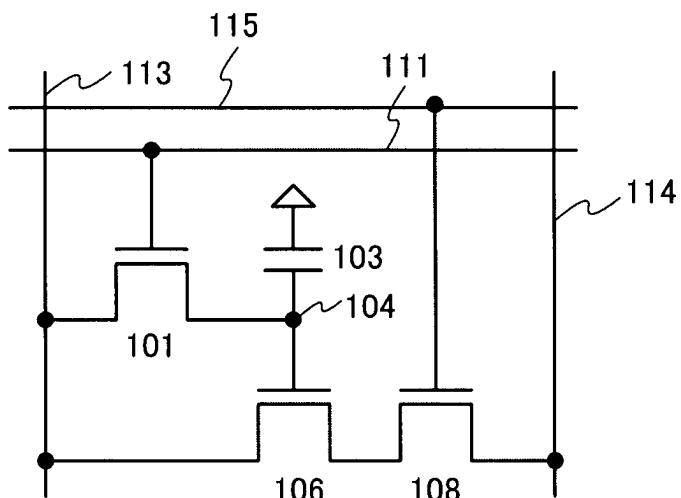

**Fig. 13A** und **Fig. 13B** sind Schaltpläne einer Halbleitervorrichtung.

**Fig. 14** ist ein Ablaufdiagramm.

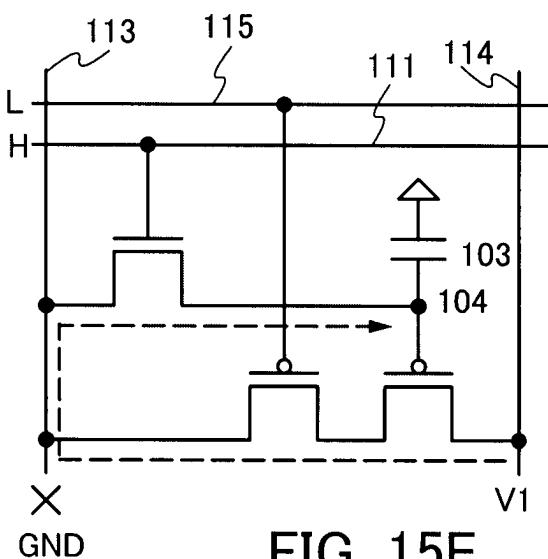

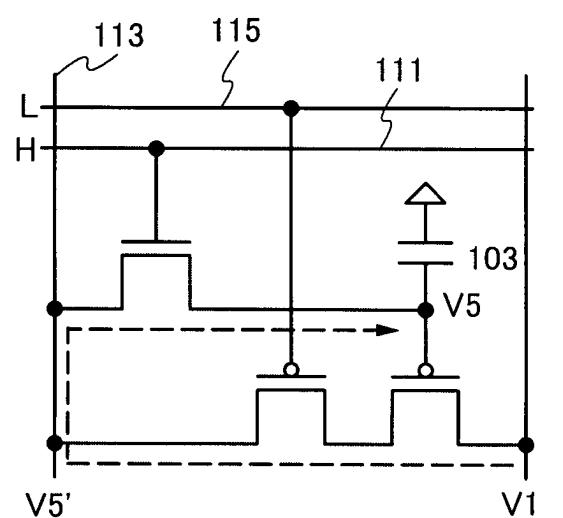

**Fig. 15A** bis **Fig. 15E** zeigen eine Arbeitsweise einer Halbleitervorrichtung.

**Fig. 16** ist ein Ablaufdiagramm.

**Fig. 17A** bis **Fig. 17D** zeigen eine Arbeitsweise einer Halbleitervorrichtung.

**Fig. 18** ist ein Schaltplan einer Halbleitervorrichtung.

**Fig. 19** ist ein Ablaufdiagramm.

**Fig. 20A** bis **Fig. 20E** zeigen eine Arbeitsweise einer Halbleitervorrichtung.

**Fig. 21** ist ein Ablaufdiagramm.

**Fig. 22A** bis **Fig. 22D** zeigen eine Arbeitsweise einer Halbleitervorrichtung.

**Fig. 23A** und **Fig. 23B** sind Schaltpläne einer Halbleitervorrichtung.

**Fig. 24** ist ein Ablaufdiagramm.

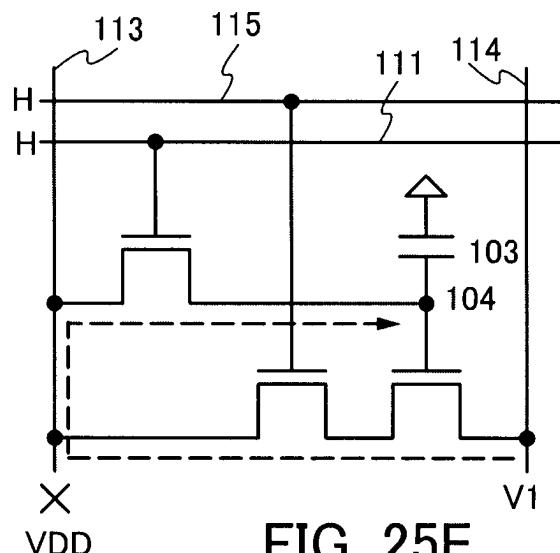

**Fig. 25A** bis **Fig. 25E** zeigen eine Arbeitsweise einer Halbleitervorrichtung.

**Fig. 26** ist ein Ablaufdiagramm.

**Fig. 27A** bis **Fig. 27D** zeigen eine Arbeitsweise einer Halbleitervorrichtung.

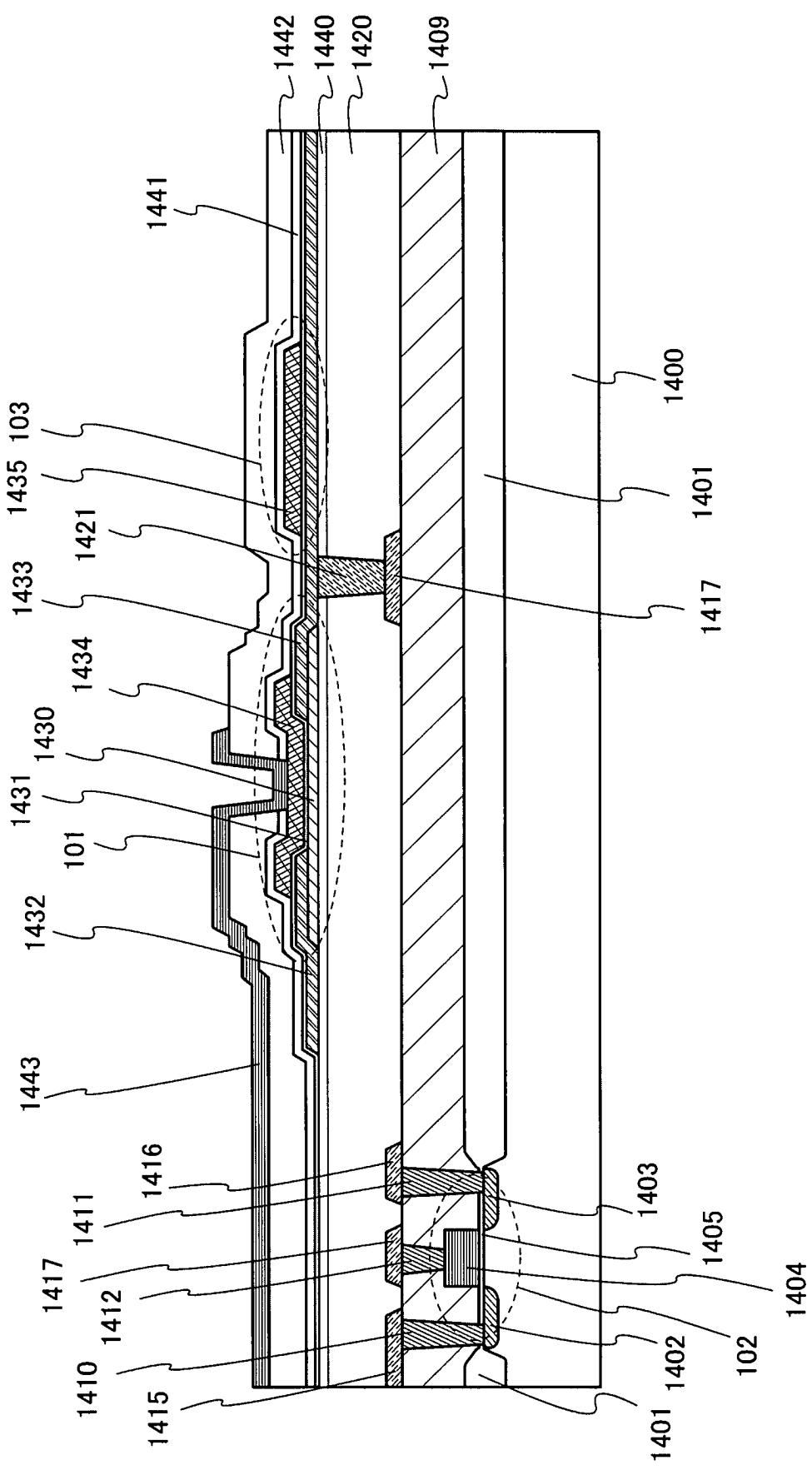

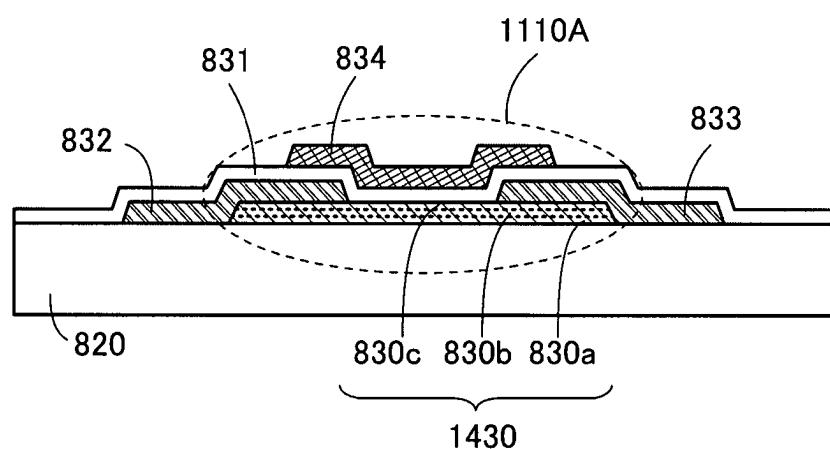

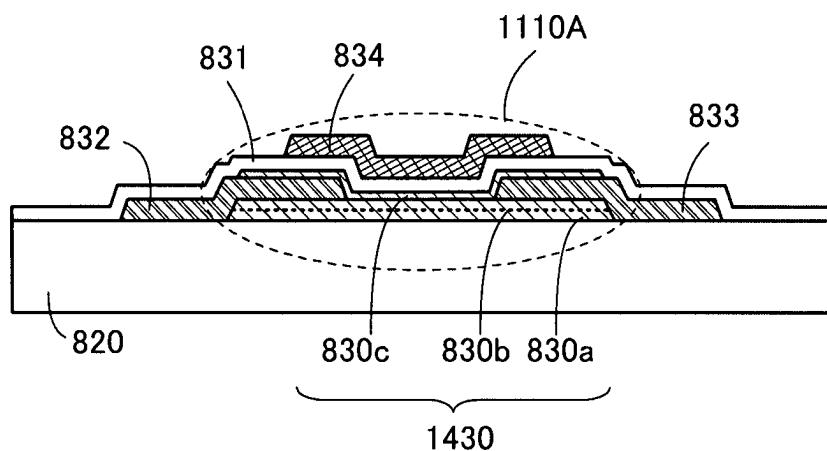

**Fig. 28** ist eine Querschnittsansicht einer Halbleitervorrichtung.

**Fig. 29A** und **Fig. 29B** sind Querschnittsansichten von Transistoren.

**Fig. 30A** bis **Fig. 30F** stellen elektronische Geräte dar.

Beste Art zum Ausführen der Erfindung

**[0018]** Nachfolgend werden Ausführungsformen und Beispiele der vorliegenden Erfindung anhand der Zeichnungen beschrieben. Es sei angemerkt, dass die vorliegende Erfindung nicht auf die folgende Beschreibung beschränkt ist. Es ist für den Fachmann leicht ersichtlich, dass verschiedene Veränderungen und Abwandlungen vorgenommen werden können, ohne vom Erfindungsgedanken und Schutzbereich der vorliegenden Erfindung abzuweichen. Daher sollte die vorliegende Erfindung nicht als auf die folgende Beschreibung der Ausführungsformen beschränkt angesehen werden. Es sei angemerkt, dass beim Beschreiben der Struktur der vorliegenden Erfindung anhand der Zeichnung Bezugszeichen für die gleichen Teile in verschiedenen Zeichnungen gemeinsam verwendet werden.

**[0019]** In dieser Beschreibung bedeutet der Begriff „Verbindung“ eine elektrische Verbindung und entspricht dem Zustand, in dem ein Strom, eine Spannung oder ein Potential zugeführt oder übertragen werden kann. Demgemäß ist mit einem Verbindungs- zustand nicht nur ein Zustand einer direkten Verbindung gemeint, sondern auch ein Zustand einer elektrischen Verbindung über ein Schaltungselement wie

z. B. eine Leitung, einen Widerstand, eine Diode oder einen Transistor, so dass ein Strom, eine Spannung oder ein Potential zugeführt oder übertragen werden kann.

**[0020]** Obwohl das Blockdiagramm, das dieser Beschreibung beigefügt ist, Bestandteile zeigt, die entsprechend ihren Funktionen in unabhängige Blöcke klassifiziert sind, ist es schwierig, tatsächliche Bestandteile vollständig entsprechend ihren Funktionen zu klassifizieren, und ein Bestandteil kann eine Vielzahl von Funktionen aufweisen.

**[0021]** Es sei angemerkt, dass eine „Source“ eines Transistors einen Source-Bereich, der ein Teil eines Halbleiterfilms ist, der als aktive Schicht dient, oder eine Source-Elektrode bedeutet, die elektrisch mit dem Halbleiterfilm verbunden ist. Ähnlicherweise bedeutet ein „Drain“ eines Transistors einen Drain-Bereich, der ein Teil eines Halbleiterfilms ist, der als aktive Schicht dient, oder eine Drain-Elektrode, die elektrisch mit dem Halbleiterfilm verbunden ist. Ein „Gate“ bedeutet eine Gate-Elektrode.

**[0022]** Die Begriffe „Source“ und „Drain“ eines Transistors werden in Abhängigkeit von dem Typ des Kanals des Transistors oder Levels von Potentialen, die an die Anschlüsse angelegt werden, ausgetauscht. Im Allgemeinen wird bei einem n-Kanal-Transistor ein Anschluss, an den ein niedrigeres Potential angelegt wird, als Source bezeichnet, und ein Anschluss, an den ein höheres Potential angelegt wird, wird als Drain bezeichnet. Ferner wird bei einem p-Kanal-Transistor ein Anschluss, an den ein niedrigeres Potential angelegt wird, als Drain bezeichnet, und ein Anschluss, an den ein höheres Potential angelegt wird, wird als Source bezeichnet. Obwohl in dieser Beschreibung eine Verbindungsbeziehung des Transistors in einigen Fällen der Einfachheit halber in der Annahme beschrieben wird, dass die Source und der Drain festgelegt sind, werden tatsächlich die Namen, die Source und der Drain, in Abhängigkeit von der Beziehung der Potentiale ausgetauscht.

**[0023]** Es sei angemerkt, dass, was bei einer Ausführungsform beschrieben wird (oder ein Teil davon), auf, mit oder durch einen anderen Inhalt der gleichen Ausführungsform und/oder was bei einer anderen Ausführungsform oder anderen Ausführungsformen beschrieben wird (oder einen Teil davon), angewendet, kombiniert oder ersetzt werden kann.

**[0024]** Es sei angemerkt, dass die Größe, die Dicke von Schichten oder Bereiche in den Zeichnungen der Einfachheit halber manchmal übertrieben ist/ sind. Somit sind Ausführungsformen der vorliegenden Erfindung nicht auf solche Größenverhältnisse beschränkt.

**[0025]** Es sei angemerkt, dass Zeichnungen schematische Ansichten idealer Beispiele sind und die Ausführungsformen der vorliegenden Erfindung nicht auf die Form oder den Wert in den Zeichnungen beschränkt sind. Beispielsweise können die folgenden Schwankungen enthalten sein: Schwankungen der Form wegen einer Herstellungstechnik oder dimensionaler Abweichung, oder Schwankungen eines Signals, einer Spannung oder eines Stroms wegen eines Rauschens oder eines Zeitunterschiedes.

**[0026]** Eine Spannung bezeichnet im Allgemeinen einen Potentialunterschied zwischen einem bestimmten Potential und einem Bezugspotential (z. B. einem Source-Potential oder einem Erdpotential (GND)). Eine Spannung kann Potential genannt werden und umgekehrt. Hier ist die Spannung jeder Leitung oder jedes Anschlusses eine relative Spannung, und es ist wichtig, ob die Spannung höher oder niedriger ist als eine Bezugsspannung. Daher bedeutet GND nicht immer 0 V. Das Gleiche gilt auch für die Zeichnungen; GND in den Zeichnungen bedeutet nicht immer 0 V.

**[0027]** Auch wenn der Ausdruck „elektrisch verbinden“ in dieser Beschreibung verwendet wird, gibt es einen Fall, in dem in einer realen Schaltung keine physikalische Verbindung gebildet ist und eine Leitung einfach verlängert ist.

**[0028]** Es sei angemerkt, dass die Ordnungszahlen wie z. B. „erster“ und „zweiter“ in dieser Beschreibung aus Gründen der Einfachheit benutzt werden und nicht die Reihenfolge von Schritten oder die Reihenfolge der angeordneten Schichten bezeichnen. Des Weiteren bezeichnen die Ordnungszahlen in dieser Beschreibung keine besonderen Namen, die die vorliegende Erfindung bestimmen.

**[0029]** Es sei angemerkt, dass ein „Halbleiter“ in einigen Fällen Eigenschaften eines „Isolators“ aufweist, wenn z. B. die Leitfähigkeit genügend niedrig ist. Des Weiteren kann man einen „Halbleiter“ und einen „Isolator“ in einigen Fällen nicht genau voneinander unterscheiden, da eine Grenze zwischen dem „Halbleiter“ und dem „Isolator“ nicht eindeutig ist. Dementsprechend kann ein „Halbleiter“ in dieser Beschreibung in einigen Fällen als „Isolator“ bezeichnet werden. Ähnlicherweise kann ein „Isolator“ in dieser Beschreibung in einigen Fällen als „Halbleiter“ bezeichnet werden.

**[0030]** Ferner weist ein „Halbleiter“ in einigen Fällen Eigenschaften eines „Leiters“ auf, wenn z. B. die Leitfähigkeit genügend hoch ist. Des Weiteren kann man einen „Halbleiter“ und einen „Leiter“ in einigen Fällen nicht genau voneinander unterscheiden, da eine Grenze zwischen dem „Halbleiter“ und dem „Isolator“ nicht eindeutig ist. Dementsprechend kann ein „Halbleiter“ in dieser Beschreibung in einigen Fällen als „Leiter“ bezeichnet werden. Ähnlicherweise kann

ein „Leiter“ in dieser Beschreibung in einigen Fällen als „Halbleiter“ bezeichnet werden.

**[0031]** In dieser Beschreibung bedeutet der Begriff „parallel“, dass der Winkel, der zwischen zwei geraden Linien gebildet ist, größer als oder gleich  $-10^\circ$  und kleiner als oder gleich  $10^\circ$  ist, und umfasst daher auch den Fall, in dem der Winkel größer als oder gleich  $-5^\circ$  und kleiner als oder gleich  $5^\circ$  ist. Außerdem bedeutet der Begriff „senkrecht“, dass der Winkel, der zwischen zwei geraden Linien gebildet ist, größer als oder gleich  $80^\circ$  und kleiner als oder gleich  $100^\circ$  ist, und umfasst daher auch den Fall, in dem der Winkel größer als oder gleich  $85^\circ$  und kleiner als oder gleich  $95^\circ$  ist.

**[0032]** In dieser Beschreibung sind trigonale und rhomboedrische Kristallsysteme in einem hexagonalen Kristallsystem enthalten.

(Ausführungsform 1)

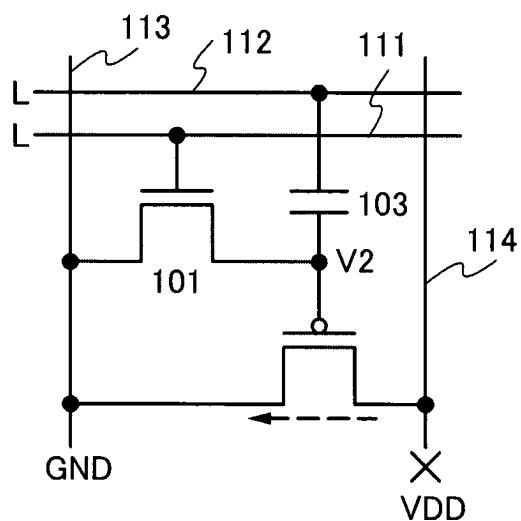

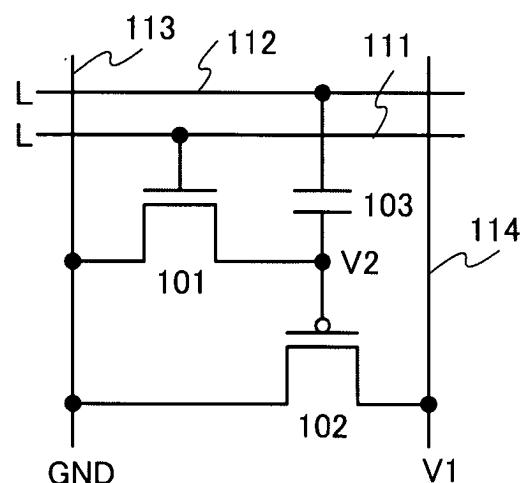

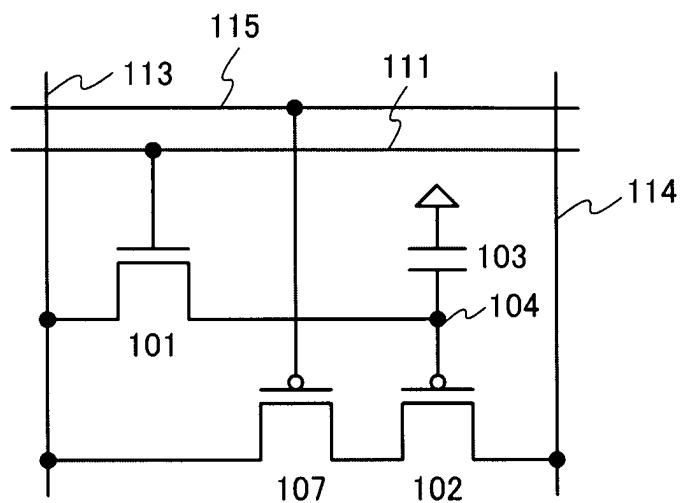

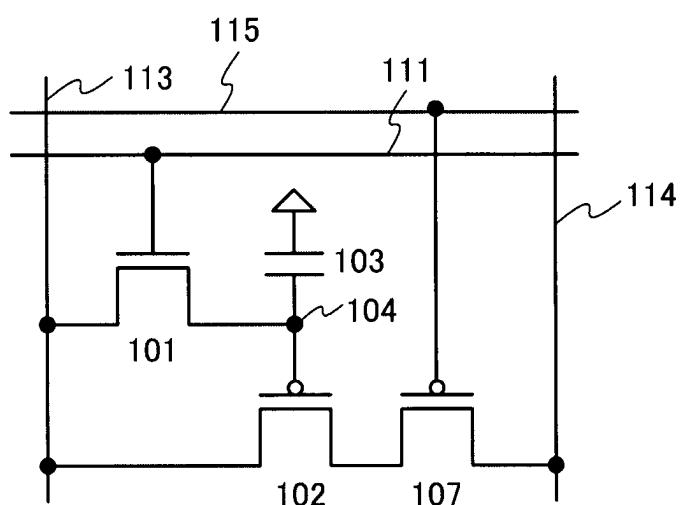

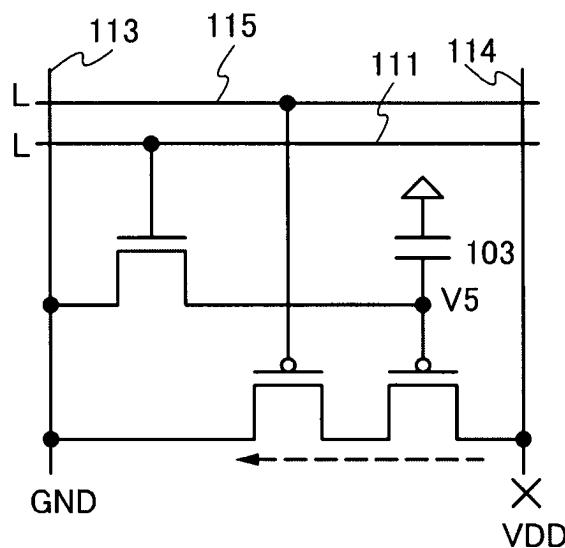

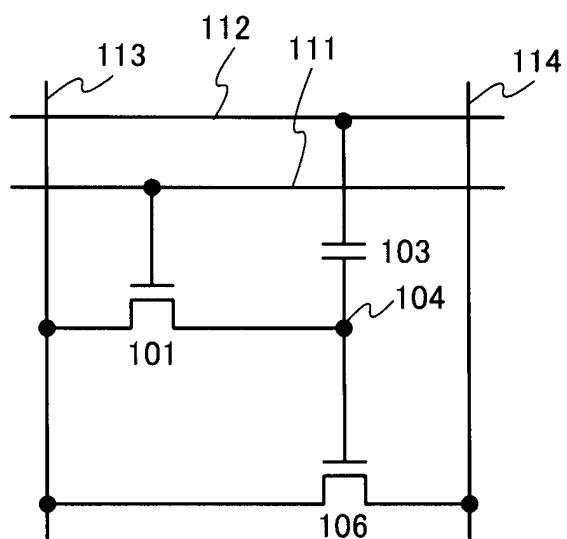

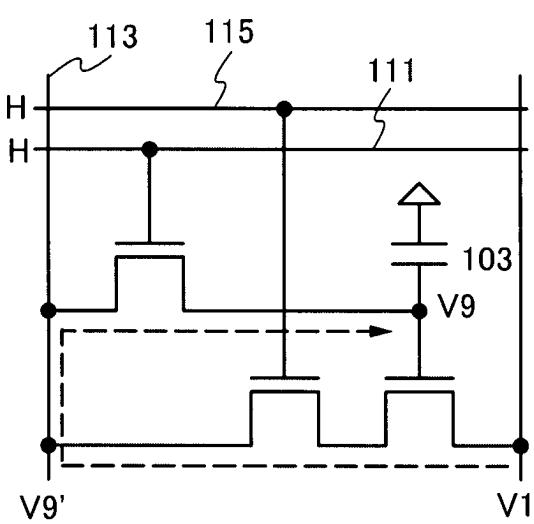

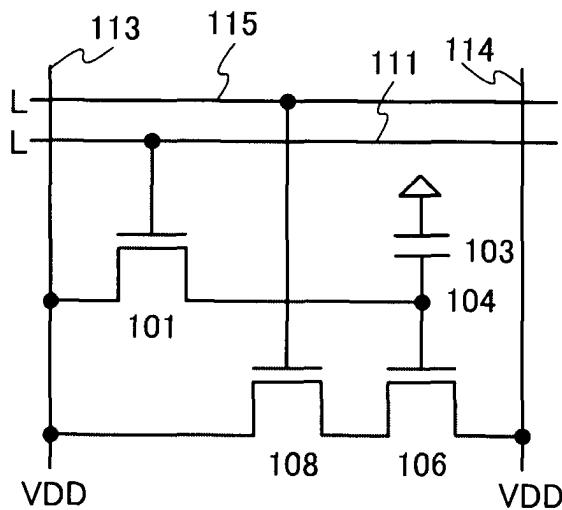

**[0033]** Fig. 1 stellt eine Halbleitervorrichtung **100** dar. Die Halbleitervorrichtung **100** beinhaltet einen Transistor **101**, einen Transistor **102** und einen Kondensator **103**. Die Halbleitervorrichtung **100** kann als Speicherzelle dienen und wird auch als Speicherzelle **100** bezeichnet.

**[0034]** Ein Bereich, in dem ein Kanal des Transistors **101** gebildet wird, weist eine Oxidhalbleiterschicht auf. Der Transistor **101** beinhaltet die Oxidhalbleiterschicht. Folglich ist der Sperrstrom des Transistors **101** sehr gering.

**[0035]** Der Transistor **101** ist ein n-Kanal-Transistor oder ein p-Kanal-Transistor. Nachfolgend wird der Fall beschrieben, in dem der Transistor **101** ein n-Kanal-Transistor ist.

**[0036]** Ein Gate des Transistors **101** ist elektrisch mit einer Leitung **111** verbunden. Die Leitung **111** kann als Wortleitung dienen.

**[0037]** Ein Anschluss von einer Source und einem Drain des Transistors **101** ist elektrisch mit einer Leitung **113** verbunden. Die Leitung **113** kann als Bitleitung dienen.

**[0038]** Der andere Anschluss von der Source und dem Drain des Transistors **101** ist elektrisch mit einer Elektrode des Kondensators **103** verbunden. Der andere Anschluss von der Source und dem Drain des Transistors **101** ist elektrisch mit einem Gate des Transistors **102** verbunden.

**[0039]** Eine Schicht, die verschiedene Materialien, wie z. B. einen Oxidhalbleiter und Silizium, enthält, kann für einen Bereich, in dem ein Kanal des Transis-

tors **102** gebildet wird, verwendet werden. Der Transistor **102** ist ein p-Kanal-Transistor.

**[0040]** Ein Anschluss von einer Source und einem Drain des Transistors **102** ist elektrisch mit einer Leitung **114** verbunden. Die Leitung **114** kann als Signalleitung, Source-Leitung oder Stromversorgungsleitung dienen.

**[0041]** Der andere Anschluss von der Source und dem Drain des Transistors **102** ist elektrisch mit der Leitung **113** verbunden. Der andere Anschluss von der Source und dem Drain des Transistors **102** ist elektrisch mit dem einen Anschluss von der Source und dem Drain des Transistors **101** verbunden.

**[0042]** Die eine Elektrode des Kondensators **103** ist elektrisch mit dem anderen Anschluss von der Source und dem Drain des Transistors **101** verbunden. Die eine Elektrode des Kondensators **103** ist elektrisch mit dem Gate des Transistors **102** verbunden.

**[0043]** Die andere Elektrode des Kondensators **103** ist elektrisch mit einer Leitung **112** verbunden. Die Leitung **112** kann als Kondensator-Leitung dienen.

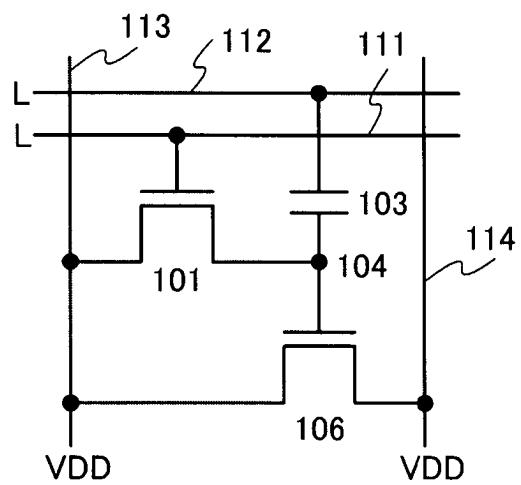

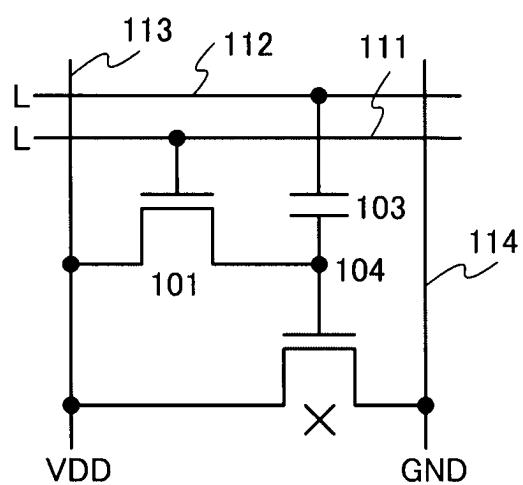

**[0044]** Ein Vorgang zum Schreiben von Daten in die Halbleitervorrichtung **100** und ein Vorgang zum Lesen von Daten von der Halbleitervorrichtung **100** werden beschrieben.

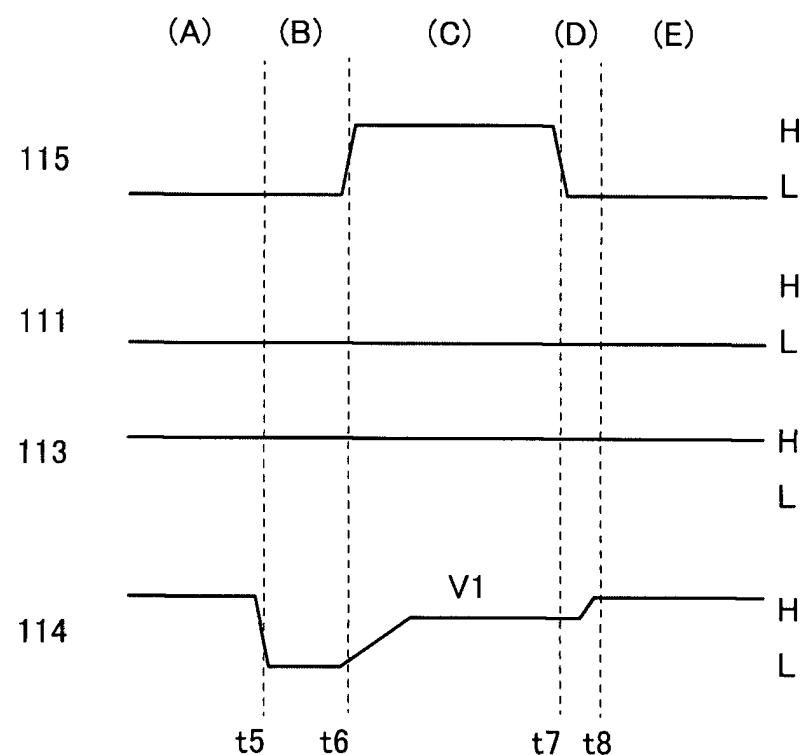

#### (Schreibvorgang)

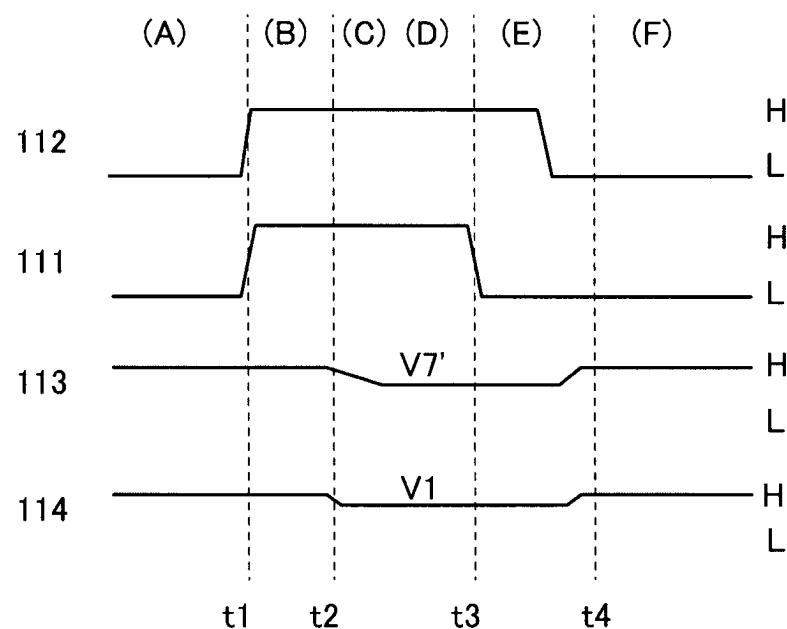

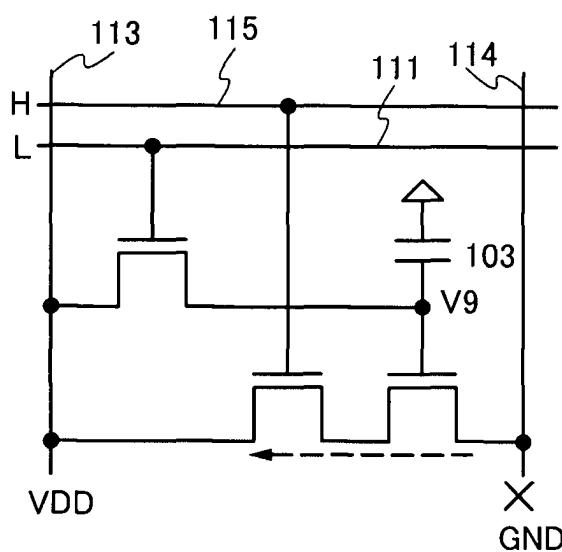

**[0045]** Zuerst wird ein Beispiel für den Schreibvorgang beschrieben. **Fig. 2** ist ein Ablaufdiagramm. **Fig. 3A** bis **Fig. 3E** stellen eine Arbeitsweise der Halbleitervorrichtung **100** dar. Als Beispiel wird eine zu lesende Spannung als **V1** bezeichnet, und ein Vorgang zum Schreiben von Daten durch Änderung des Potentials eines Knotens **104** (des Gate-Potentials des Transistors **102**) auf **V2** wird beschrieben. Da verschiedene Spannungen beim Speichern von Multibit-Daten angelegt werden müssen, ist es vorteilhaft, dass man **V1** frei einstellen kann.

**[0046]** Ein Vorgang zum Schreiben von Daten wird durch einen ersten Schritt und einen zweiten Schritt durchgeführt. In dem ersten Schritt wird eine niedrige Spannung an die Leitungen **113** und **114** angelegt, eine hohe Spannung wird an die Leitung **111** angelegt, um den Transistor **101** einzuschalten, und eine niedrige Spannung wird an die Leitung **112** angelegt, so dass der Transistor **102** eingeschaltet wird. In dem zweiten Schritt wird die Spannung **V1** an die Leitung **114** angelegt, und das Anlegen der niedrigen Spannung an die Leitung **113** wird unterbrochen.

**[0047]** Durch den zweiten Schritt wird ein Potential **V2**, das den Daten (der Spannung **V1**) entspricht, von der Leitung **114** an den Knoten **104** über die Source

und den Drain des Transistors **102**, die Leitung **113** und die Source und den Drain des Transistors **101** angelegt. Dann wird das Potential **V2** an das Gate des Transistors **102** angelegt. Eine elektrische Ladung, die **V2** entspricht, wird in dem Kondensator **103** akkumuliert.

**[0048]** **Fig. 3A** zeigt einen Anfangszustand der Halbleitervorrichtung **100**. In **Fig. 2** ist der Anfangszustand durch (A) dargestellt.

**[0049]** Ein Signal bei einer niedrigen Spannung (auch als L-Spannung bezeichnet) wird an die Leitung **111** eingegeben, und demzufolge wird der Transistor **101** ausgeschaltet. Die niedrige Spannung ist eine Spannung, bei der der Transistor **101** ausgeschaltet wird. Die niedrige Spannung kann eine Bezugsspannung (GND), eine Stromversorgungsspannung (VDD oder VSS) oder eine weitere Spannung sein.

**[0050]** Ein Signal bei einer hohen Spannung (auch als H-Spannung bezeichnet) wird an die Leitung **112** eingegeben. Eine Spannung, die dem Kapazitätswert des Kondensators **103** entspricht, wird an den Knoten **104** angelegt, und demzufolge wird der Transistor **102** ausgeschaltet. Die hohe Spannung ist eine Spannung, bei der der Transistor **102** ausgeschaltet wird. Die hohe Spannung kann eine Stromversorgungsspannung (VDD) oder eine weitere Spannung sein.

**[0051]** Eine niedrige Spannung (GND) wird an die Leitungen **113** und **114** angelegt. Folglich können die Leitungen **113** und **114** mit der niedrigen Spannung vorgeladen (precharged) werden. Die niedrige Spannung ist hier die Bezugsspannung (GND) aber kann eine Stromversorgungsspannung (VSS) oder eine weitere Spannung sein.

**[0052]** **Fig. 3B** zeigt einen Schreibvorbereitungszustand. In **Fig. 2** ist der Zustand durch (B) dargestellt.

**[0053]** Zu einem Zeitpunkt **t1** wird ein Signal bei einer hohen Spannung an die Leitung **111** eingegeben, und demzufolge wird der Transistor **101** eingeschaltet. Die hohe Spannung ist eine Spannung, bei der der Transistor **101** eingeschaltet wird. Die hohe Spannung kann eine Stromversorgungsspannung (VDD) oder eine weitere Spannung sein.

**[0054]** Der Transistor **101** wird eingeschaltet, so dass die Leitung **113** und der Knoten **104** elektrisch miteinander verbunden werden. Das Potential des Knotens **104** wird auf die niedrige Spannung (GND) verringert.

**[0055]** Zu dem Zeitpunkt **t1** wird ein Signal bei einer niedrigen Spannung an die Leitung **112** eingegeben. Eine Spannung, die dem Kapazitätswert des Konden-

sators **103** entspricht, wird an den Knoten **104** angelegt. Der Transistor **101** wird eingeschaltet, und eine niedrige Spannung wird an die Leitung **112** angelegt, so dass der Transistor **102** eingeschaltet wird. Die niedrige Spannung ist eine Spannung, bei der der Transistor **102** eingeschaltet wird. Die niedrige Spannung kann eine Bezugsspannung (GND), die Stromversorgungsspannung (VSS) oder eine weitere Spannung sein.

**[0056]** Eine niedrige Spannung wird an die Leitungen **113** und **114** angelegt, und die Transistoren **101** und **102** werden eingeschaltet. So wird der erste Schritt abgeschlossen.

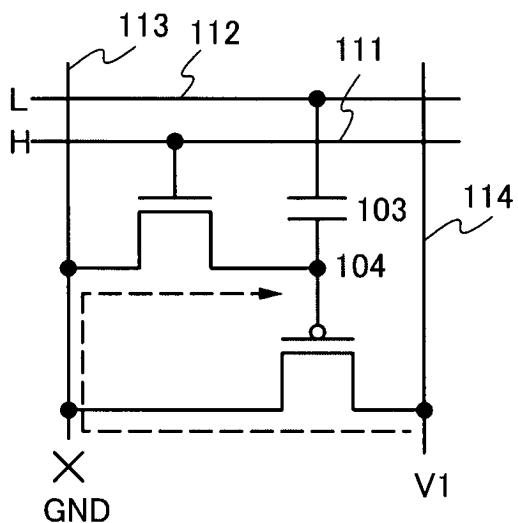

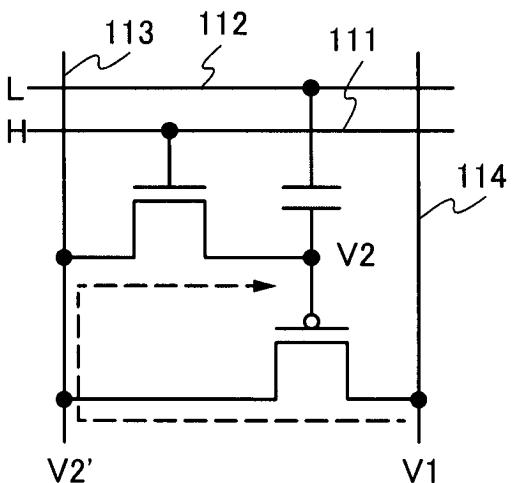

**[0057]** **Fig. 3C** und **Fig. 3D** zeigen einen Schreibzustand. In **Fig. 2** ist der Zustand durch (C) und (D) dargestellt.

**[0058]** Zu einem Zeitpunkt  $t_2$  wird die Spannung **V1** an die Leitung **114** angelegt (**Fig. 3C**). Die Spannung **V1** ist eine durch einen Lesevorgang zu lensende Spannung. Der Level von **V1** kann in Abhängigkeit von zu schreibenden Daten frei eingestellt werden.

**[0059]** Zu dem Zeitpunkt  $t_2$  wird eine Zuführung der niedrigen Spannung (GND) zu der Leitung **113** unterbrochen (**Fig. 3C**). Dabei wird die Leitung **113** von der vorgeladenen Spannung in einen elektrisch schwebenden Zustand versetzt. Mit anderen Worten wird das Potential der Leitung **113** leicht durch Laden oder Entladen von einer elektrischen Ladung geändert. Dieser schwebende Zustand kann erhalten werden, indem der Schalter zum Zuführen des Potentials der Leitung **113** ausgeschaltet wird.

**[0060]** Da der Transistor **102** eingeschaltet ist, ist die Leitung **113** elektrisch mit der Leitung **114** verbunden. Die Spannung der Leitung **113** wird von der vorgeladenen niedrigen Spannung (GND) auf **V2'** geändert (**Fig. 3D**). Es sei angemerkt, dass der Unterschied zwischen **V2'** und **V1** ungefähr die Schwellenspannung des Transistors **102** ist.

**[0061]** Da der Transistor **101** eingeschaltet ist, werden Daten von der Leitung **114** in den Knoten **104** (das Gate des Transistors **102**) über die Source und den Drain des Transistors **102**, die Leitung **113** und die Source und den Drain des Transistors **101** geschrieben. Eine elektrische Ladung wird in dem Kondensator **103** akkumuliert. Das Potential des Knotens **104** wird auf **V2** geändert.

**[0062]** Das Potential des Knotens **104** wird auf **V2** geändert, und folglich wird ein Potentialunterschied zwischen dem Gate des Transistors **102** und der Source des Transistors **102** klein; als Ergebnis wird ein Strom ( $I_d$ ) gering, der zwischen der Source und dem Drain des Transistors **102** fließt. Der Transistor **102** wird schließlich ausgeschaltet.

**[0063]** Bei der Halbleitervorrichtung **100** werden **V1**, **V2'** und **V2** an die Leitung **114**, die Leitung **113** bzw. den Knoten **104** angelegt.

**[0064]** Die Spannung **V1** wird an die Leitung **114** angelegt, und das Anlegen der niedrigen Spannung an die Leitung **113** wird unterbrochen, so dass der zweite Schritt abgeschlossen wird.

**[0065]** Durch die vorstehenden Schritte wird die zu lesende Spannung **V1** an die Leitung **114** angelegt, und das Potential des Knotens **104** wird auf **V2** geändert, so dass der Schreibvorgang abgeschlossen wird.

**[0066]** **Fig. 3E** zeigt einen Zustand nach dem Schreibvorgang und vor der Datenhaltung. In **Fig. 2** ist der Zustand durch (E) dargestellt.

**[0067]** Zu einem Zeitpunkt  $t_3$  wird ein Signal bei einer niedrigen Spannung an die Leitung **111** eingegeben. Der Transistor **101** wird ausgeschaltet. Der Knoten **104** und die Leitung **113** sind elektrisch nicht verbunden. Der Transistor **101** weist ein Merkmal, einen sehr geringen Sperrstrom, auf, und daher wird das Potential (**V2**) des Knotens **104** gehalten.

**[0068]** Vor einem Zeitpunkt  $t_4$  wird die hohe Spannung an die Leitung **112** angelegt, die niedrige Spannung (GND) wird an die Leitung **113** angelegt, und die niedrige Spannung (GND) wird an die Leitung **114** angelegt.

**[0069]** Die hohe Spannung wird an die Leitung **112** angelegt, so dass das Potential des Knotens **104** von **V2** auf eine Spannung, bei der der Transistor **102** ausgeschaltet wird, geändert wird.

**[0070]** Zu dem Zeitpunkt  $t_4$  wird der Zustand zu dem Haltezustand. In **Fig. 2** ist der Zustand durch (F) dargestellt. Der Zustand der Halbleitervorrichtung **100** ist gleich dem Zustand der Halbleitervorrichtung **100** in **Fig. 3A**, außer dass die Knoten **104** unterschiedliche Potentiale aufweisen. Der Transistor **101** ist ausgeschaltet.

**[0071]** Es sei angemerkt, dass eine niedrige Spannung an die Leitung **114** in (A) und (F) in **Fig. 2** angelegt wird, aber eine hohe Spannung kann an die Leitung **114** in (A) und (F) in **Fig. 2** angelegt werden. In dem Fall, in dem eine hohe Spannung an die Leitung **114** angelegt ist, kann die Spannung in einigen Fällen schnell geändert werden, wenn der Zustand von dem Zustand (E) zu dem Zustand (F) geändert wird, d. h. eine hohe Spannung an die Leitung **114** angelegt wird.

(Lesevorgang)

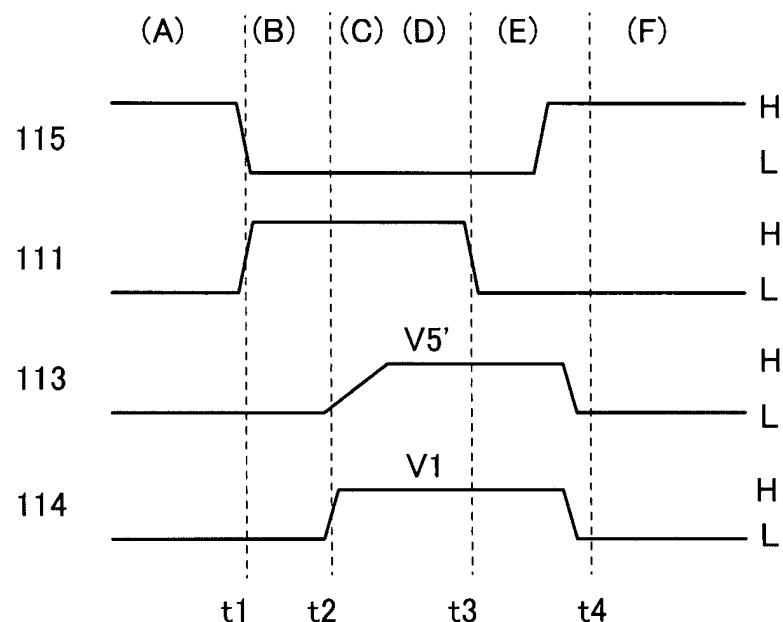

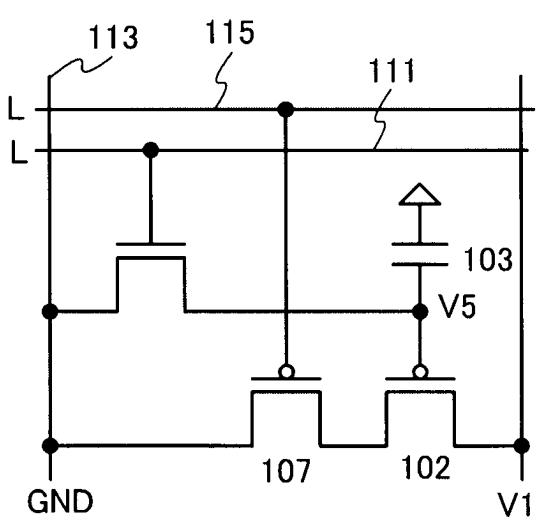

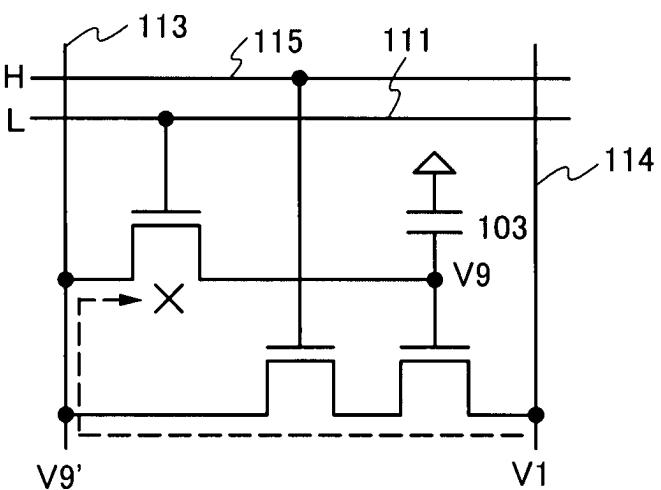

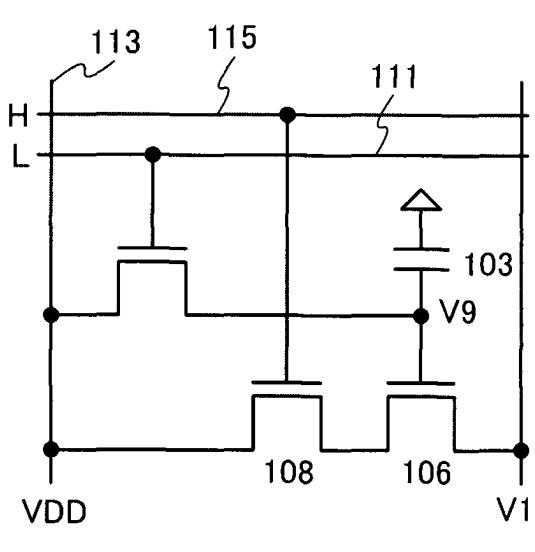

**[0072]** Als Nächstes wird ein Beispiel für einen Vorgang zum Lesen der Spannung **V1** basierend auf einer elektrischen Ladung beschrieben, die durch den Schreibvorgang geschrieben worden ist. **Fig. 4** ist ein Ablaufdiagramm. **Fig. 5A** bis **Fig. 5D** zeigen eine Arbeitsweise der Halbleitervorrichtung **100**.

**[0073]** Ein Vorgang zum Lesen von Daten wird durch einen dritten Schritt, in dem eine hohe Spannung an die Leitung **114** angelegt wird, und einen vierten Schritt durchgeführt, in dem das Anlegen der hohen Spannung an die Leitung **114** unterbrochen wird und eine niedrige Spannung an die Leitung **112** angelegt wird. Durch den vierten Schritt wird die Spannung der Leitung **114** von der hohen Spannung zu der Spannung **V1** geändert.

**[0074]** **Fig. 5A** zeigt einen Haltezustand der Halbleitervorrichtung **100**. In **Fig. 4** ist der Haltezustand durch (A) dargestellt.

**[0075]** **Fig. 5B** zeigt einen Lesevorbereitungszustand. In **Fig. 4** ist der Zustand durch (B) dargestellt.

**[0076]** Zu dem Zeitpunkt  $t_5$  wird eine hohe Spannung (VDD) an die Leitung **114** angelegt. Die Leitung **114** kann mit der hohen Spannung vorgeladen werden. Die hohe Spannung ist hier die Stromversorgungsspannung (VDD) aber kann eine weitere Spannung sein. Die hohe Spannung ist vorzugsweise höher als **V1**.

**[0077]** Es sei angemerkt, dass die Transistoren **101** und **102** von dem Haltezustand an ausgeschaltet bleiben.

**[0078]** Die hohe Spannung wird an die Leitung **114** angelegt, so dass der dritte Schritt abgeschlossen wird.

**[0079]** **Fig. 5C** und **Fig. 5D** zeigen einen Lesezustand. In **Fig. 4** ist der Zustand durch (C) dargestellt.

**[0080]** Zu einem Zeitpunkt  $t_6$  wird eine Zuführung der hohen Spannung (VDD) zu der Leitung **114** unterbrochen (**Fig. 5C**). Dabei wird die Leitung **114** von der vorgeladenen Spannung in einen elektrisch schwebenden Zustand versetzt. Mit anderen Worten wird das Potential der Leitung **114** leicht durch Laden und Entladen von einer elektrischen Ladung geändert. Dieser schwebende Zustand kann erhalten werden, indem der Schalter zum Zuführen des Potentials der Leitung **114** ausgeschaltet wird.

**[0081]** Zu dem Zeitpunkt  $t_6$  wird ein Signal bei einer niedrigen Spannung an die Leitung **112** eingegeben. Das Potential des Knotens **104** wird auf **V2** beim Schreiben von Daten geändert. Als Ergebnis fließt

ein Strom ( $I_d$ ), der dem Gate-Potential des Transistors **102** (**V2**) und dem Potential der Leitung **114** entspricht. Es sei angemerkt, dass die niedrige Spannung, die an die Leitung **112** eingegeben wird, vorzugsweise gleich der niedrigen Spannung ist, die beim Schreibvorgang an die Leitung **112** eingegeben worden ist.

**[0082]** Das Potential der Leitung **114** ändert sich von der vorgeladenen hohen Spannung (VDD) auf **V1** als Reaktion auf die Gate-Spannung **V2** (**Fig. 5D**). Ein Potentialunterschied zwischen dem Gate und der Source des Transistors **102** wird im Laufe der Zeit kleiner, und folglich wird der Transistor **102** ausgeschaltet.

**[0083]** Die Leitung **114** ist elektrisch mit einer Beurteilungsschaltung (discrimination circuit) oder dergleichen verbunden, um **V1** zu lesen. Folglich kann die Spannung **V1** gelesen werden.

**[0084]** Das Anlegen der hohen Spannung an die Leitung **114** wird unterbrochen, und die niedrige Spannung wird an die Leitung **112** angelegt. Folglich wird der vierte Schritt abgeschlossen.

**[0085]** Nachdem Daten gelesen worden sind, wird zu einem Zeitpunkt  $t_7$  ein Signal bei einer hohen Spannung an die Leitung **112** eingegeben. Die hohe Spannung wird an die Leitung **112** angelegt, so dass das Potential des Knotens **104** von **V2** um die hohe Spannung geändert wird. Folglich wird der Transistor **102** ausgeschaltet.

**[0086]** Eine niedrige Spannung (GND) wird vor einem Zeitpunkt  $t_8$  an die Leitung **114** angelegt.

**[0087]** Zu dem Zeitpunkt  $t_8$  ist der Zustand der Haltezustand. In **Fig. 4** ist der Zustand durch (E) dargestellt. Die Halbleitervorrichtung **100** befindet sich in dem in **Fig. 5A** gezeigten Zustand.

**[0088]** Es sei angemerkt, dass eine niedrige Spannung an die Leitung **114** in (A) und (E) in **Fig. 4** angelegt wird, aber eine hohe Spannung kann an die Leitung **114** in (A) und (E) in **Fig. 4** angelegt werden. In dem Fall, in dem eine hohe Spannung an die Leitung **114** angelegt ist, kann die Spannung schnell geändert werden, wenn der Zustand von dem Zustand (A) zu dem Zustand (B) geändert wird, d. h. VDD an die Leitung **114** angelegt wird.

**[0089]** Es sei angemerkt, dass in dem Fall, in dem das Potential des Knotens **104**, d. h. das Potential, das an das Gate des Transistors **102** angelegt wird, zurückgesetzt wird, beispielsweise die niedrige Spannung an die Leitung **112** angelegt wird und ein Signal bei einer hohen Spannung an die Leitung **111** eingegeben wird. Folglich wird der Transistor **101** eingeschaltet, so dass der Knoten **104** elektrisch mit der

Leitung **113** verbunden ist. Da GND an die Leitung **113** angelegt wird, wird das Potential des Knotens **104** zurückgesetzt.

**[0090]** Bei dieser Ausführungsform dient das Potential (**V1**), das beim Schreiben von Daten an die Leitung **114** angelegt wird, als Lesepotential.

**[0091]** Bei einer herkömmlichen Technik weist eine Lesespannung eine Verteilung auf. Beispielsweise ist eine tatsächliche Lesespannung aufgrund der Schwankungen des Schwellenwertes eines Lese-transistors oder dergleichen  $V1 \pm \Delta V$  auch in dem Fall, in dem  $V1$  zu lesen ist. Mit anderen Worten hat die Lesespannung die Ausbreitung von  $\Delta V$ . Im Gegen- teil dazu kann bei dieser Ausführungsform ein gewünschtes Potential **V1**, das an die Leitung **114** angelegt wird, gelesen werden. Folglich kann  $\Delta V$  kleiner werden, und daher kann die Ausbreitung der Verteilung der Lesespannung verkleinert werden.

**[0092]** In dem Fall, in dem Multibit-Daten in der Halbleitervorrichtung **100** gespeichert werden, muss eine vorbestimmte Spannung korrekt geschrieben und gelesen werden. Deshalb ist eine hohe Genauigkeit erforderlich. Bei dieser Ausführungsform kann ein vorbestimmtes Potential angelegt und gelesen werden. Folglich weist die Halbleitervorrichtung **100** beim Speichern von Multibit-Daten hohe Halteigenschaf- ten und hohe Zuverlässigkeit auf.

**[0093]** Ein Prüfvorgang ist herkömmlich durchge- führt worden, um zu prüfen, ob Daten korrekt ge- schrieben werden. Im Gegenteil dazu ist bei dieser Ausführungsform kein Prüfvorgang nötig. Daher kann ein Hochgeschwindigkeitsbetrieb erzielt werden.

**[0094]** Diese Ausführungsform kann in Kombination mit jeder der anderen Ausführungsformen in dieser Beschreibung nach Bedarf implementiert werden.

#### (Ausführungsform 2)

**[0095]** Bei dieser Ausführungsform wird ein Beispiel für eine Halbleitervorrichtung beschrieben, bei der ein anhand von **Fig. 1** beschriebenes Betriebsverfahren verwendet werden kann. Nachstehend wird eine Be- schreibung anhand von **Fig. 6**, **Fig. 7**, **Fig. 8**, **Fig. 9**, **Fig. 10**, **Fig. 11** und **Fig. 12** gegeben.

(Strukturbeispiel für Halbleitervorrichtung)

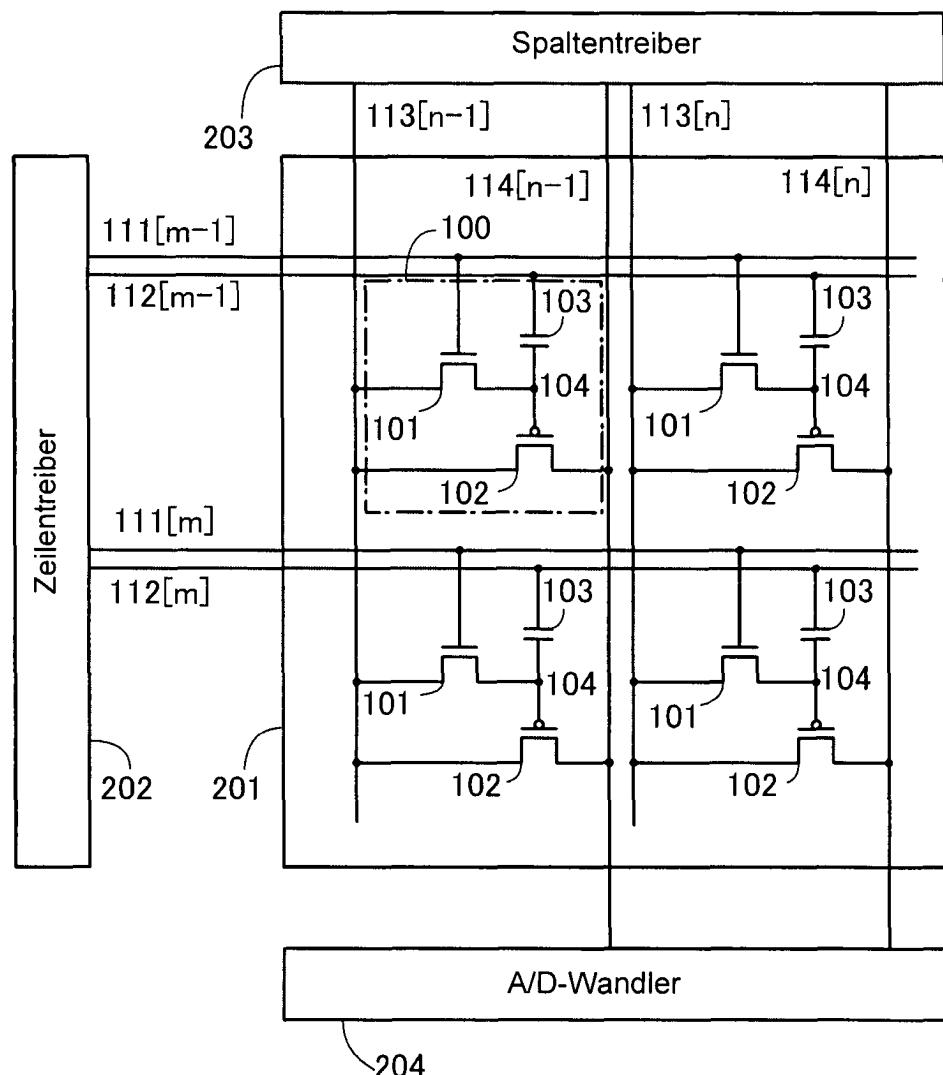

**[0096]** **Fig. 6** ist ein Blockdiagramm eines Struktur- beispiels für eine Halbleitervorrichtung **200**, die die anhand von **Fig. 1** beschriebene Speicherzelle **100** beinhaltet.

**[0097]** Die Halbleitervorrichtung **200** in **Fig. 6** be-inhaltet ein Speicherzellenarray **201**, in dem die Viel- zahl von anhand von **Fig. 1** beschriebenen Speicher-

zellen **100** angeordnet ist, einen Zeilenauswahltreiber **202**, einen Spaltenauswahltreiber **203** und einen A/D-Wandler **204**. Es sei angemerkt, dass die Halbleitervorrichtung **200** die Speicherzellen **100** beinhaltet, die in einer Matrix von  $m$  Zeilen und  $n$  Spalten angeordnet sind. In **Fig. 6** sind als die Leitung **111** eine Leitung  $111[m-1]$  in der  $(m-1)$ -ten Zeile und eine Leitung  $111[m]$  in der  $m$ -ten Zeile bereitgestellt. Als die Leitung **112** sind eine Leitung  $112[m-1]$  in der  $(m-1)$ -ten Zeile und eine Leitung  $112[m]$  in der  $m$ -ten Zeile bereitgestellt. Als die Leitung **113** sind eine Leitung  $113[n-1]$  in der  $(n-1)$ -ten Spalte und eine Leitung  $113[n]$  in der  $n$ -ten Spalte bereitgestellt. Als die Leitung **114** sind eine Leitung  $114[n-1]$  in der  $(n-1)$ -ten Spalte und eine Leitung  $114[n]$  in der  $n$ -ten Spalte bereitge- stellt.

**[0098]** In dem Speicherzellenarray **201** in **Fig. 6** sind die anhand von **Fig. 1** beschriebenen Speicherzel- len **100** in einer Matrix angeordnet. Es sei angemerkt, dass die Beschreibung der Bestandteile in der Speicherzelle **100** gleich wie in **Fig. 1** und daher wegge- lassen ist. Es wird auf die Beschreibung anhand von **Fig. 1** Bezug genommen.

**[0099]** Der Zeilenauswahltreiber **202** ist eine Schal- tung, die Funktionen aufweist, um selektiv die Transistoren **101** in jeder Zeile der Speicherzellen **100** ein- zuschalten und selektiv das Potential des Knotens **104** in jeder Zeile der Speicherzellen **100** zu ändern. Insbesondere ist der Zeilenauswahltreiber **202** eine Schaltung, die den Leitungen **111** und den Leitungen **112** Signale zuführt. Der Zeilenauswahltreiber **202** ermöglicht es der Halbleitervorrichtung **200**, Daten in die Speicherzellen **100** in jeder ausgewählten Zeile zu schreiben oder Daten von den Speicherzellen **100** in jeder ausgewählten Zeile zu lesen.

**[0100]** Der Spaltenauswahltreiber **203** ist eine Schaltung, die Funktionen aufweist, um die Leitungen **113** und die Leitungen **114** in den Speicherzel- len **100** mit Potentialen vorzuladen, die Potentiale der Leitungen **113** und der Leitungen **114** zu initialisieren, und die Leitungen **113** und die Leitungen **114** in einen elektrisch schwebenden Zustand zu versetzen. Der Spaltenauswahltreiber **203** ermöglicht es der Halbleitervorrichtung **200**, eine Spalte auszuwählen, um Daten in die Speicherzellen **100** in jeder ausgewählten Spalte zu schreiben oder Daten von den Speicherzel- len **100** in jeder ausgewählten Spalte zu lesen.

**[0101]** Der A/D-Wandler **204** ist eine Schaltung, die Funktionen aufweist, um die Potentiale der Leitungen **114**, die analoge Werte sind, in digitale Werte um- zuwandeln und die digitalen Werte nach außen aus- zugeben. Insbesondere ist der A/D-Wandler **204** eine Schaltung, die einen Flash-A/D-Wandler beinhaltet. Der A/D-Wandler **204** ermöglicht es der Halbleitervorrichtung **200**, das Potential der Leitung **114**, das

den von der Speicherzelle **100** gelesenen Daten entspricht, nach außen auszugeben.

**[0102]** Es sei angemerkt, dass der A/D-Wandler 204 als Flash-A/D-Wandler beschrieben wird. Jedoch kann der A/D-Wandler 204 ein sukzessiver Annäherungs-A/D-Wandler (successive approximation A/D converter), ein Multi-Slope-A/D-Wandler oder ein Delta-Sigma-A/D-Wandler sein.

(Strukturbeispiel für Zeilenauswahltreiber)

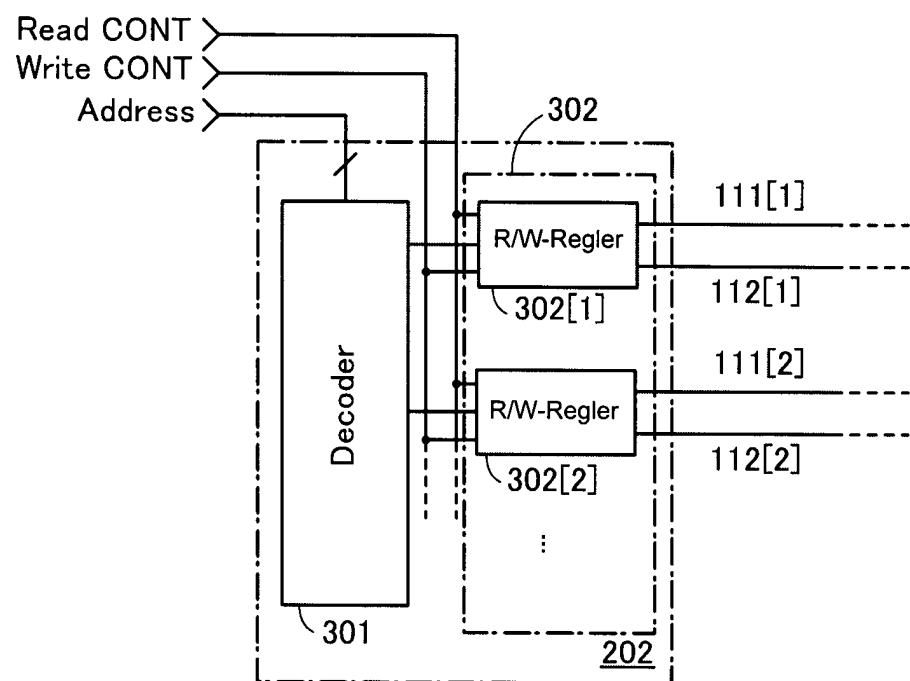

**[0103]** **Fig. 7** ist ein Blockdiagramm, das ein Strukturbeispiel für den anhand von **Fig. 6** beschriebenen Zeilenauswahltreiber **202** darstellt.

**[0104]** Der Zeilenauswahltreiber **202** in **Fig. 7** beinhaltet einen Decoder **301** und eine Steuerschaltung **302**. Die Steuerschaltung **302** ist in jeder Zeile bereitgestellt, in der die Leitung **111** und die Leitung **112** bereitgestellt sind. Die Steuerschaltung **302[1]** (R/W-Regler in **Fig. 7**) ist in der ersten Zeile bereitgestellt. Die Steuerschaltung **302[2]** ist in der zweiten Zeile bereitgestellt. Die Steuerschaltung **302** in jeder Zeile ist mit der Leitung **111** und der Leitung **112** verbunden.

**[0105]** Der Decoder **301** ist eine Schaltung, die eine Funktion aufweist, um ein Signal zum Auswählen einer Zeile, in der die Leitung **111** und die Leitung **112** bereitgestellt sind, auszugeben.

**[0106]** Die Steuerschaltung **302** ist eine Schaltung, die eine Funktion aufweist, um ein Signal an die Zeile auszugeben, die durch den Decoder **301** ausgewählt wird und in der die Leitung **111** und die Leitung **112** bereitgestellt sind.

(Strukturbeispiel für Spaltenauswahltreiber)

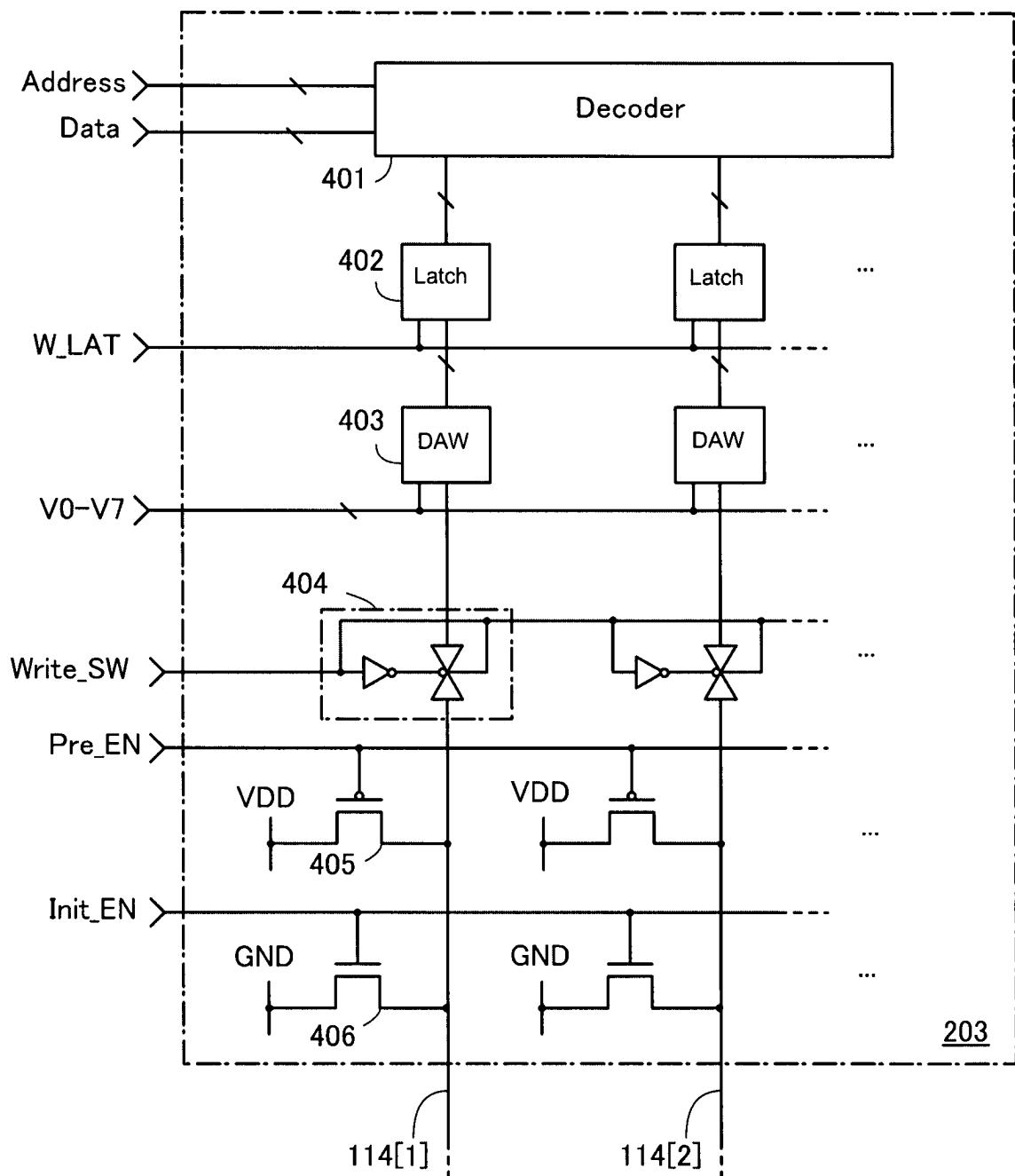

**[0107]** **Fig. 8** ist ein Blockdiagramm, das ein Strukturbeispiel für den anhand von **Fig. 6** beschriebenen Spaltenauswahltreiber **203** darstellt.

**[0108]** Der Spaltenauswahltreiber **203** in **Fig. 8** beinhaltet einen Decoder **401**, eine Latch-Schaltung **402**, einen D/A-Wandler **403**, einen Schalterstromkreis **404**, einen Transistor **405** und den Transistor **406**. Die Latch-Schaltung **402**, der Schalterstromkreis **404**, der Transistor **405** und der Transistor **406** sind in jeder Spalte bereitgestellt. Der Schalterstromkreis **404**, der Transistor **405** und der Transistor **406** in jeder Spalte sind mit der Leitung **114** verbunden.

**[0109]** Der Decoder **401** ist eine Schaltung, die Funktionen aufweist, um eine Spalte, in der die Leitung **114** bereitgestellt ist, auszuwählen und eingegebene Daten zu verteilen, um die Daten auszugeben. Insbesondere ist der Decoder **401** eine Schaltung, in die ein Adressensignal „Address“ und Daten „Data“

eingegeben werden und die die Daten „Data“ in die Latch-Schaltung **402** in einer Zeile entsprechend dem Adressensignal „Address“ ausgibt. Der Decoder **401** ermöglicht es dem Spaltenauswahltreiber **203**, eine vorbestimmte Spalte auszuwählen und Daten in die Spalte zu schreiben.

**[0110]** Es sei angemerkt, dass es sich bei den Daten „Data“, die in den Decoder **401** eingegeben werden, um k-Bit-Digitaldaten handelt. Es handelt sich bei den k-Bit-Digitaldaten um ein Signal, das durch Binärdaten dargestellt wird, in denen jedes Bit durch „1“ oder „0“ dargestellt wird. Beispielsweise handelt es sich bei 2-Bit-Digitaldaten um Daten, die durch „00“, „01“, „10“ oder „11“ dargestellt werden.

**[0111]** Die Latch-Schaltung **402** ist eine Schaltung, die eine Funktion aufweist, um vorübergehend die eingegebenen Daten „Data“ zu speichern. Insbesondere ist die Latch-Schaltung **402** eine Flip-Flop-Schaltung, in die ein Latch-Signal **W\_LAT** eingegeben wird und die die Daten „Data“ entsprechend dem Latch-Signal **W\_LAT** speichert und die Daten **DATA** in den D/A-Wandler **403** ausgibt. Die Latch-Schaltung **402** ermöglicht es dem Spaltenauswahltreiber **203**, Daten zu einem beliebigen Zeitpunkt zu schreiben.

**[0112]** Der D/A-Wandler **403** ist eine Schaltung, die eine Funktion aufweist, um die Daten **Data**, die ein einzugebender digitaler Wert sind, in Daten **Vdata** umzuwandeln, die ein analoger Wert sind. Insbesondere ist der D/A-Wandler **403** eine Schaltung, die beispielsweise die 3-Bit-Daten **Data** in eines von acht Potentialen (Potentialen **V0** bis **V7**) umwandelt und das Potential in den Schalterstromkreis **404** ausgibt. Der D/A-Wandler **403** ermöglicht es dem Spaltenauswahltreiber **203**, Daten, die in die Speicherzelle **100** geschrieben werden, in ein Potential umzuwandeln, das Multilevel-Daten entspricht.

**[0113]** Es sei angemerkt, dass es sich bei **Vdata**, die von dem D/A-Wandler **403** ausgegeben werden, um Daten handelt, die durch verschiedene Spannungswerte dargestellt werden können. Im Falle von 2-Bit-Daten handelt es sich beispielsweise bei **Vdata** um Daten mit vier Werten, z. B. 0,5 V, 1,0 V, 1,5 V und 2,0 V, und um Daten, die durch einen der Spannungswerte dargestellt werden.

**[0114]** Der Schalterstromkreis **404** ist eine Schaltung, die Funktionen aufweist, um der Leitung **114** die eingegebenen Daten **Vdata** zuzuführen und die Leitung **114** in einen elektrisch schwebenden Zustand zu versetzen. Insbesondere ist der Schalterstromkreis **404** eine Schaltung, die einen Analogschalter und einen Wechselrichter beinhaltet und die der Leitung **114** die Daten **Vdata** entsprechend einem Schaltersteuersignal **Write\_SW** zuführt; der Analogschalter wird dann ausgeschaltet, so dass die Leitung **114** in einen elektrisch schwebenden Zustand versetzt wird.

Der Spaltenauswahltreiber **203** ermöglicht es dem Spaltenauswahltreiber **203**, die Leitung **114** in einem elektrisch schwebenden Zustand zu halten, nachdem der Leitung **114** die Daten Vdata zugeführt worden sind.

**[0115]** Der Transistor **405** ist ein Transistor, der Funktionen aufweist, um der Leitung **114** eine Vorladespannung VDD zuzuführen und die Leitung **114** in einen elektrisch schwebenden Zustand zu versetzen. Insbesondere ist der Transistor **405** ein Schalter, der eine Zuführung der Vorladespannung VDD zu der Leitung **114** durch Steuern mit einem Vorladesteuersignal Pre\_EN ermöglicht und die Leitung **114** nach der Zuführung in einen elektrisch schwebenden Zustand versetzt. Der Transistor **405** ermöglicht es dem Spaltenauswahltreiber **203**, der Leitung **114** die Vorladespannung VDD zuzuführen und dann die Leitung **114** in einem elektrisch schwebenden Zustand zu halten.

**[0116]** Der Transistor **406** ist ein Transistor, der eine Funktion aufweist, um der Leitung **114** eine Initialisierungsspannung GND zuzuführen. Insbesondere ist der Transistor **406** ein Schalter, der eine Zuführung der Initialisierungsspannung GND zu der Leitung **114** durch Steuern mit einem Initialisierungssteuersignal Init\_EN ermöglicht. Der Transistor **406** ermöglicht es dem Spaltenauswahltreiber **203**, der Leitung **114** die Initialisierungsspannung GND zuzuführen.

**[0117]** Es sei angemerkt, dass, obwohl nicht dargestellt ist, der Spaltenauswahltreiber **203** Funktionen aufweist, um eine Vorladespannung (GND) an die Leitung **113** anzulegen und die Leitung **113** in einen elektrisch schwebenden Zustand zu versetzen. Diese Funktionen können durch eine Struktur, die der Struktur der Leitung **114** ähnlich ist, erzielt werden; daher wird auf die Beschreibung der Leitung **114** Bezug genommen.

(Strukturbeispiel für A/D-Wandler)

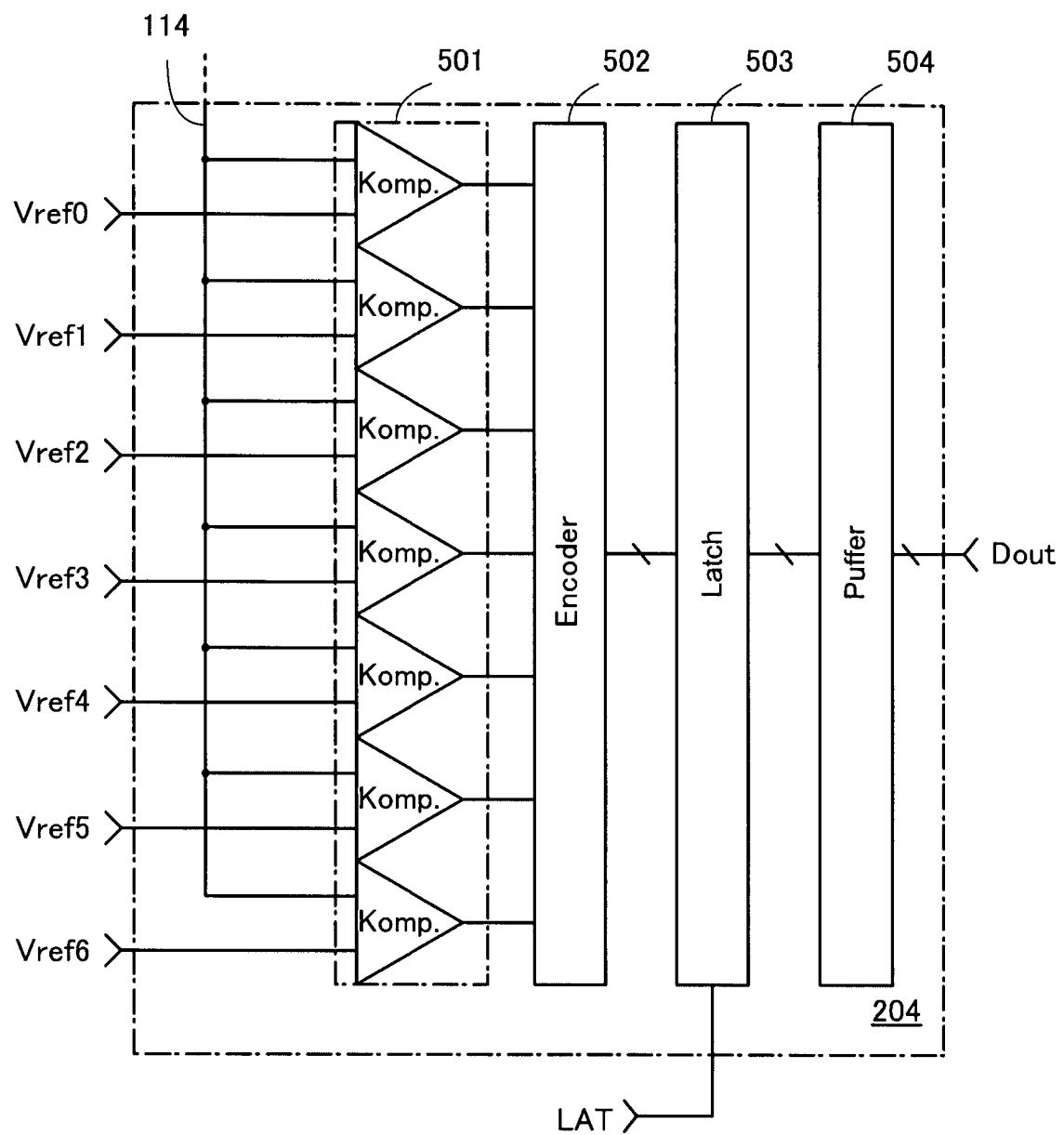

**[0118]** **Fig. 9** ist ein Blockdiagramm eines Strukturbeispiels für den anhand von **Fig. 6** beschriebenen A/D-Wandler 204.

**[0119]** Der A/D-Wandler 204 in **Fig. 9** beinhaltet einen Komparator **501**, einen Encoder **502**, eine Latch-Schaltung **503** und einen Puffer **504**. Der Komparator **501**, der Encoder **502**, die Latch-Schaltung **503** und der Puffer **504** sind in jeder Spalte bereitgestellt. Der Puffer **504** in jeder Spalte gibt Daten Dout aus.

**[0120]** Der Komparator **501** ist eine Schaltung, die Funktionen aufweist, um Potentiallevels zwischen dem Potential der Leitung **114** und Bezugspotentialen Vref0 bis Vref6 zu vergleichen und zu bestimmen, ob das Potential der Leitung **114** beliebigen Daten von Multilevel-Daten entspricht. Insbesondere ist der Komparator **501** eine Schaltung, die die Vielzahl von

Komparatoren beinhaltet, zu denen das Potential der Leitung **114** und die verschiedenen Bezugspotentiale Vref0 bis Vref6 zugeführt werden, und ist eine Schaltung, die bestimmt, ob das Potential der Leitung **114** zwischen den Potentialen liegt. Der Komparator **501** ermöglicht es dem A/D-Wandler 204, zu bestimmen, ob das Potential der Leitung **114** einem Potential von Multilevel-Daten entspricht.

**[0121]** Es sei angemerkt, dass beispielhaft die Bezugsspannungen Vref0 bis Vref6 in **Fig. 9** Potentiale sind, die in dem Fall zugeführt werden, in dem Multilevel-Daten 3-Bit-Daten, d. h. 8-Level-Daten, sind.

**[0122]** Der Encoder **502** ist eine Schaltung, die eine Funktion aufweist, um ein Multibit-Digitalsignal aufgrund eines Signals zum Bestimmen des Potentials der Leitung **114**, das von dem Komparator **501** ausgegeben wird, zu erzeugen. Insbesondere ist der Encoder **502** eine Schaltung, die ein H-Level- oder L-Level-Signal encodiert, das von der Vielzahl von Komparatoren ausgegeben wird, um ein Digitalsignal zu erzeugen. Der Encoder **502** ermöglicht es dem A/D-Wandler 204, Daten, die von der Speicherzelle **100** gelesen werden, in Daten mit einem digitalen Wert umzuwandeln.

**[0123]** Die Latch-Schaltung **503** ist eine Schaltung, die eine Funktion aufweist, um vorübergehend einzugebende Daten von einem digitalen Wert zu speichern. Insbesondere ist die Latch-Schaltung **503** eine Flip-Flop-Schaltung, in die ein Latch-Signal LAT eingegeben wird und die die Daten, die entsprechend dem Latch-Signal LAT gespeichert sind, in den Puffer **504** ausgibt. Die Latch-Schaltung **503** ermöglicht es dem A/D-Wandler 204, Daten zu einem beliebigen Zeitpunkt auszugeben. Es sei angemerkt, dass die Latch-Schaltung **503** weggelassen werden kann.

**[0124]** Der Puffer **504** ist eine Schaltung, die Funktionen aufweist, um Daten, die von der Latch-Schaltung **503** ausgegeben werden, zu verstärken und die verstärkten Daten als Ausgangssignal Dout auszugeben. Insbesondere ist der Puffer **504** eine Schaltung, die eine gerade Zahl von Stufen von Wechselrichterschaltungen beinhaltet. Der Puffer **504** ermöglicht es dem A/D-Wandler 204, Rauschen eines Digitalsignals zu verringern. Es sei angemerkt, dass der Puffer **504** weggelassen werden kann.

(konkretes Beispiel für Betriebsverfahren der Halbleitervorrichtung)

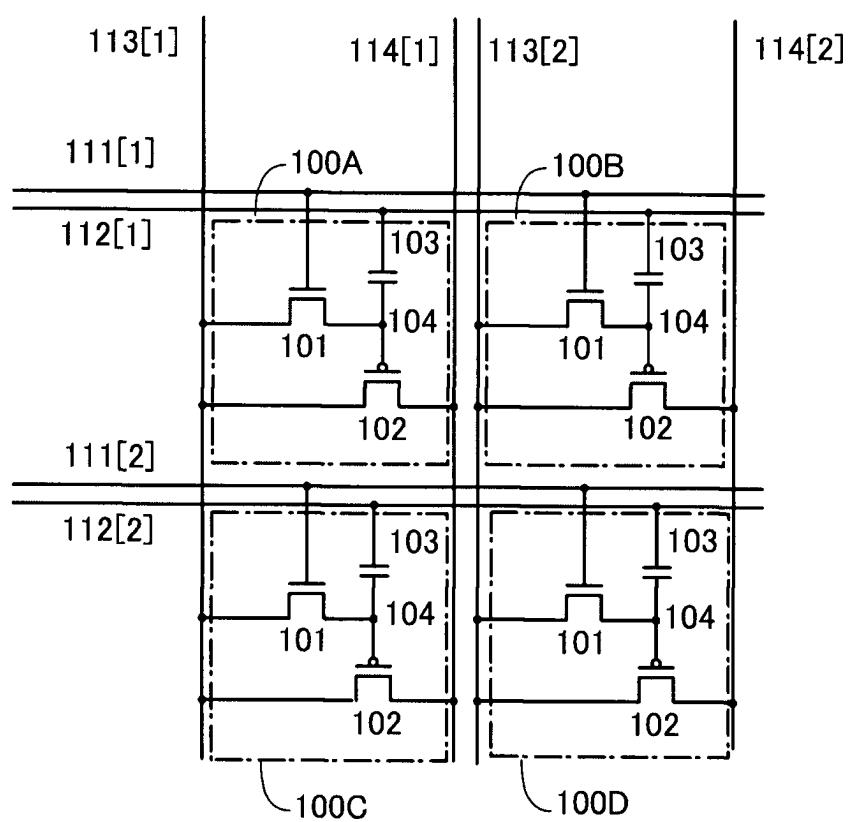

**[0125]** **Fig. 10** ist ein Schaltplan von Speicherzellen in einer Halbleitervorrichtung. Ablaufdiagramme in **Fig. 11** und **Fig. 12** zeigen eine Arbeitsweise der Speicherzellen in **Fig. 10**.

**[0126]** Bei einer Halbleitervorrichtung **600** in **Fig. 10** sind Speicherzellen **100A** bis **100D**, die jeweils die

gleiche Schaltungsstruktur aufweisen wie die anhand von **Fig. 1** beschriebene Speicherzelle, in einer Matrix von zwei Zeilen und zwei Spalten angeordnet. In **Fig. 10** sind als die Leitung **111** eine Leitung 111[1] in der ersten Zeile und eine Leitung 111[2] in der zweiten Zeile bereitgestellt. Als die Leitung **112** sind eine Leitung 112[1] in der ersten Zeile und eine Leitung 112[2] in der zweiten Zeile bereitgestellt. Als die Leitung **113** sind eine Leitung 113[1] in der ersten Spalte und eine Leitung 113[2] in der zweiten Spalte bereitgestellt. Als die Leitung **114** sind eine Leitung 114[1] in der ersten Spalte und eine Leitung 114[2] in der zweiten Spalte bereitgestellt.

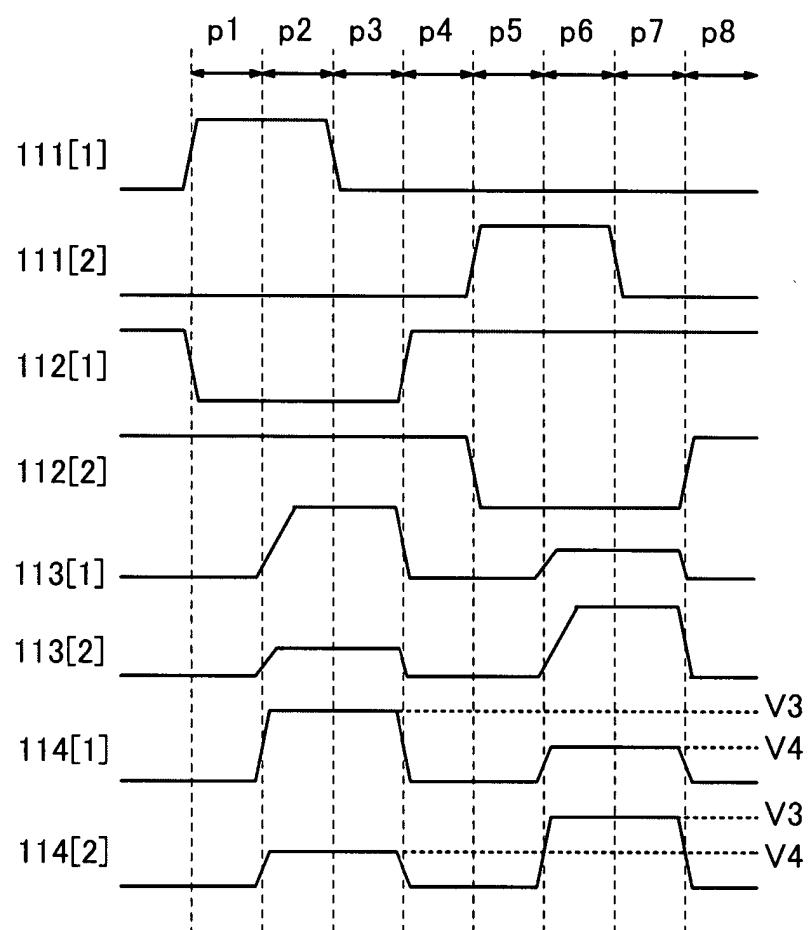

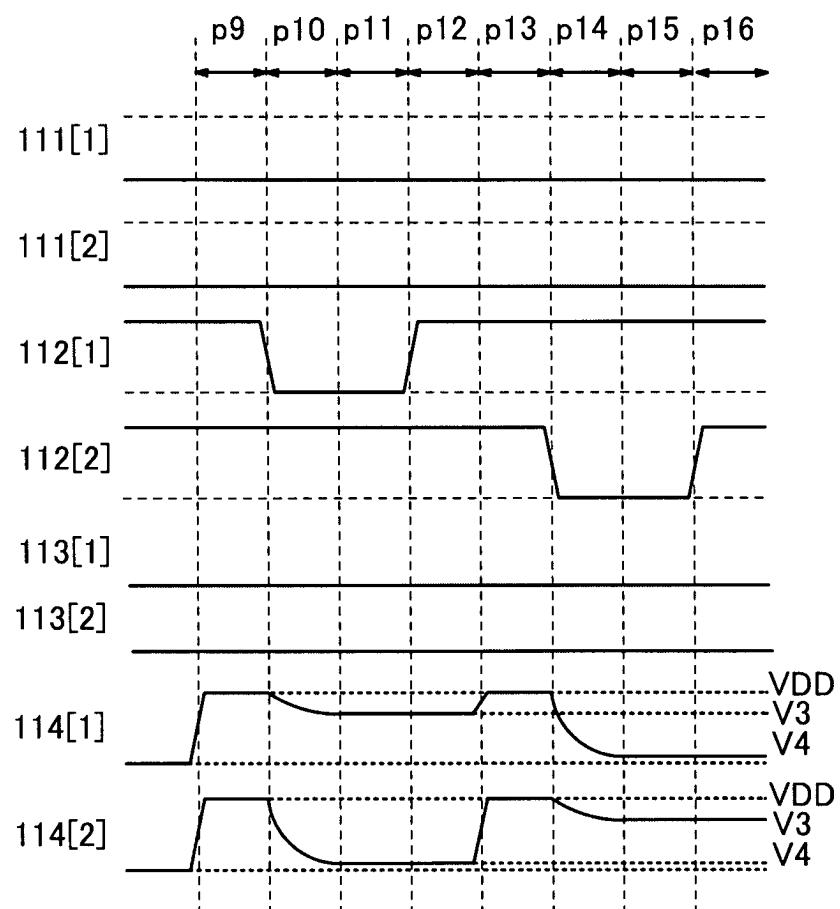

**[0127]** Das Ablaufdiagramm in **Fig. 11** zeigt eine Arbeitsweise in Perioden p1 bis p8, in denen das Schreiben von Daten durchgeführt wird. Das Ablaufdiagramm in **Fig. 12** zeigt eine Arbeitsweise in Perioden p9 bis p16, in denen das Lesen von Daten durchgeführt wird. Es sei angemerkt, dass **Fig. 11** und **Fig. 12** Änderungen der Spannungen der Leitung 111[1], der Leitung 111[2], der Leitung 112[1], der Leitung 112[2], der Leitung 113[1], der Leitung 113[2], der Leitung 114[1] und der Leitung 114[2] in **Fig. 10** zeigen.

**[0128]** In der Periode p1 in **Fig. 11** wird die Leitung 111[1] auf einen H-Level eingestellt, und die Leitung 112[1] wird auf einen L-Level eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[2], die Leitung 112[2], die Leitung 113[1], die Leitung 113[2], die Leitung 114[1] und die Leitung 114[2]) Spannungen in der vorhergehenden Periode halten. Die Transistoren **101** und die Transistoren **102** in den Speicherzellen **100A** und **100B** werden eingeschaltet.

**[0129]** Dann wird in der Periode p2 in **Fig. 11** das Anlegen der Spannungen an die Leitung 113[1] und die Leitung 113[2] unterbrochen, um die Leitungen in einen elektrisch schwebenden Zustand zu versetzen. Die Spannung der Leitung 114[1] wird auf V3 eingestellt. Die Spannung der Leitung 114[2] wird auf V4 eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1] und die Leitung 112[2]) Spannungen in der vorhergehenden Periode halten.

**[0130]** Die Spannung der Leitung 113[1] wird entsprechend der Spannung **V3** der Leitung 114[1] geändert. Die Spannung der Leitung 113[2] wird entsprechend der Spannung **V4** der Leitung 114[2] geändert. Daten, die der Spannung **V3** entsprechen, werden in den Knoten **104** in der Speicherzelle **100A** geschrieben. Daten, die der Spannung **V4** entsprechen, werden in den Knoten **104** in der Speicherzelle **100B** geschrieben.

**[0131]** Als Nächstes wird in der Periode p3 in **Fig. 11** das Potential der Leitung 111[1] auf einen L-Level

eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[2], die Leitung 112[1], die Leitung 112[2], die Leitung 113[1], die Leitung 113[2], die Leitung 114[1] und die Leitung 114[2]) Spannungen in der vorhergehenden Periode halten. Die Transistoren **101** in den Speicherzellen **100A** und **100B** werden ausgeschaltet.

**[0132]** Dann wird in der Periode p4 in **Fig. 11** das Potential der Leitung 112[1] auf einen H-Level eingestellt. Die Spannungen der Leitung 113[1], der Leitung 113[2], der Leitung 114[1] und der Leitung 114[2] werden auf eine niedrige Spannung (GND) eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2] und die Leitung 112[2]) Spannungen in der vorhergehenden Periode halten. Die Transistoren **102** in den Speicherzellen **100A** und **100B** werden ausgeschaltet.

**[0133]** Als Nächstes wird in der Periode p5 in **Fig. 11** das Potential der Leitung 111[2] auf einen H-Level eingestellt, und das Potential der Leitung 112[2] wird auf einen L-Level eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 112[1], die Leitung 113[1], die Leitung 113[2], die Leitung 114[1] und die Leitung 114[2]) Spannungen in der vorhergehenden Periode halten. Die Transistoren **101** und die Transistoren **102** in den Speicherzellen **100C** und **100D** werden eingeschaltet.

**[0134]** Dann wird in der Periode p6 in **Fig. 11** das Anlegen der Spannungen an die Leitung 113[1] und die Leitung 113[2] unterbrochen, um die Leitungen in einen elektrisch schwebenden Zustand zu versetzen. Die Spannung der Leitung 114[1] wird auf V4 eingestellt. Die Spannung der Leitung 114[2] wird auf V3 eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1] und die Leitung 112[2]) Spannungen in der vorhergehenden Periode halten.

**[0135]** Die Spannung der Leitung 113[1] wird entsprechend der Spannung **V4** der Leitung 114[1] geändert. Die Spannung der Leitung 113[2] wird entsprechend der Spannung **V3** der Leitung 114[2] geändert. Daten, die der Spannung **V4** entsprechen, werden in den Knoten **104** in der Speicherzelle **100C** geschrieben. Daten, die der Spannung **V3** entsprechen, werden in den Knoten **104** in der Speicherzelle **100D** geschrieben.

**[0136]** Als Nächstes wird in der Periode p7 in **Fig. 11** das Potential der Leitung 111[2] auf einen L-Level eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 112[1], die Leitung 112[2], die Leitung 113[1], die Leitung 113[2], die Leitung 114[1] und die Leitung 114[2]) Spannungen in der vorhergehenden Periode halten. Die Transistoren **101** in den Speicherzellen **100C** und **100D** werden ausgeschaltet.

**[0137]** Dann wird in der Periode p8 in **Fig. 11** das Potential der Leitung 112[2] auf einen H-Level eingestellt. Die Spannungen der Leitung 113[1], der Leitung 113[2], der Leitung 114[1] und der Leitung 114[2] werden auf eine niedrige Spannung (GND) eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2] und die Leitung 112[1]) Spannungen in der vorhergehenden Periode halten. Die Transistoren **102** in den Speicherzellen **100A** und **100B** werden ausgeschaltet.

**[0138]** Als Ergebnis von Schreiben von Daten in den Perioden p1 bis p8 werden Daten, die der Spannung **V3** entsprechen, in die Speicherzellen **100A** und **1000** in **Fig. 10** geschrieben, und Daten, die der Spannung **V4** entsprechen, werden in die Speicherzellen **100B** und **100C** in **Fig. 10** geschrieben.

**[0139]** In der Periode p9 in **Fig. 12** werden die Leitung 114[1] und die Leitung 114[2] mit einer Vorladespannung (hier VDD) versorgt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1], die Leitung 112[2], die Leitung 113[1] und die Leitung 113[2]) Spannungen in der vorhergehenden Periode halten.

**[0140]** Dann wird in der Periode p10 in **Fig. 12** das Anlegen der Spannungen an die Leitung 114[1] und die Leitung 114[2] unterbrochen, um die Leitungen in einen elektrisch schwebenden Zustand zu versetzen. Die Leitung 112[1] wird auf einen L-Level eingestellt. Die Transistoren **102** in den Speicherzellen **100A** und **100B** werden eingeschaltet. Dann werden die Spannungen der Leitung 114[1] und der Leitung 114[2] aufgrund einer Spannung verringert, die den Daten entspricht, die in die Speicherzellen **100A** und **100B** geschrieben worden sind. Die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[2], die Leitung 113[1] und die Leitung 113[2]) halten Spannungen in der vorhergehenden Periode. Es sei angemerkt, dass die Spannung auf einem L-Level, die an die Leitung 112[1] eingegeben wird, vorzugsweise gleich der Spannung auf dem L-Level ist, die beim Schreibvorgang an die Leitung 112[1] eingegeben worden ist.

**[0141]** Als Nächstes wird in der Periode p11 in **Fig. 12** eine Verringerung der Spannungen der Leitung 114[1] und der Leitung 114[2] in der Periode p10 unterbrochen, so dass Spannungen der Leitung 114[1] und der Leitung 114[2] zu der Spannung **V3** bzw. der Spannung **V4** werden. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1], die Leitung 112[2], die Leitung 113[1] und die Leitung 113[2]) Spannungen in der vorhergehenden Periode halten.

**[0142]** Als Nächstes wird in der Periode p12 in **Fig. 12** das Potential der Leitung 112[1] auf einen H-Level eingestellt. Es sei angemerkt, dass die ande-

ren Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1], die Leitung 113[1], die Leitung 113[2], die Leitung 114[1] und die Leitung 114[2]) Spannungen in der vorhergehenden Periode halten. Die Transistoren **102** in den Speicherzellen **100A** und **100B** werden ausgeschaltet.

**[0143]** In der Periode p13 in **Fig. 12** werden die Leitung 114[1] und die Leitung 114[2] mit der Vorladespannung VDD versorgt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1], die Leitung 112[2], die Leitung 113[1] und die Leitung 113[2]) Spannungen in der vorhergehenden Periode halten.

**[0144]** Dann wird in der Periode p14 in **Fig. 12** das Anlegen der Spannungen an die Leitung 114[1] und die Leitung 114[2] unterbrochen, um die Leitungen in einen elektrisch schwebenden Zustand zu versetzen. Die Leitung 112[2] wird auf einen L-Level eingestellt. Die Transistoren **102** in den Speicherzellen **100C** und **100D** werden eingeschaltet. Dann werden die Spannungen der Leitung 114[1] und der Leitung 114[2] aufgrund einer Spannung verringert, die den Daten entspricht, die in die Speicherzellen **100C** und **100D** geschrieben worden sind. Die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1], die Leitung 113[1] und die Leitung 113[2]) halten Spannungen in der vorhergehenden Periode. Es sei angemerkt, dass die Spannung auf einem L-Level, die an die Leitung 112[2] eingegeben wird, vorzugsweise gleich der Spannung auf dem L-Level ist, die beim Schreibvorgang an die Leitung 112[2] eingegeben worden ist.

**[0145]** Als Nächstes wird in der Periode p15 in **Fig. 12** eine Verringerung der Spannungen der Leitung 114[1] und der Leitung 114[2] in der Periode p14 unterbrochen, so dass Spannungen der Leitung 114[1] und der Leitung 114[2] zu der Spannung **V4** bzw. der Spannung **V3** werden. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1], die Leitung 112[2], die Leitung 113[1] und die Leitung 113[2]) Spannungen in der vorhergehenden Periode halten.

**[0146]** Dann wird in der Periode p16 in **Fig. 12** das Potential der Leitung 112[2] auf einen H-Level eingestellt. Es sei angemerkt, dass die anderen Leitungen (d. h. die Leitung 111[1], die Leitung 111[2], die Leitung 112[1], die Leitung 113[1], die Leitung 113[2], die Leitung 114[1] und die Leitung 114[2]) Spannungen in der vorhergehenden Periode halten. Die Transistoren **102** in den Speicherzellen **100C** und **1000** werden ausgeschaltet.

**[0147]** Als Ergebnis von Schreiben von Daten in den Perioden p9 bis p16 werden Daten, die der Spannung **V3** entsprechen, von den Speicherzellen **100A** und **100D** in **Fig. 10** gelesen, und Daten, die der Span-

nung **V4** entsprechen, werden von den Speicherzellen **100B** und **100C** in **Fig. 10** gelesen.

**[0148]** Die oben beschriebene Struktur bei dieser Ausführungsform kann mit jeder der bei den anderen Ausführungsformen beschriebenen Strukturen nach Bedarf kombiniert werden.

(Ausführungsform 3)