(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6338436号

(P6338436)

(45) 発行日 平成30年6月6日(2018.6.6)

(24) 登録日 平成30年5月18日(2018.5.18)

(51) Int.Cl.

F 1

H04N 5/343 (2011.01)

H04N 5/343

H04N 5/345 (2011.01)

H04N 5/345

H04N 5/347 (2011.01)

H04N 5/347

請求項の数 11 (全 22 頁)

(21) 出願番号

特願2014-92002(P2014-92002)

(22) 出願日

平成26年4月25日(2014.4.25)

(65) 公開番号

特開2015-211351(P2015-211351A)

(43) 公開日

平成27年11月24日(2015.11.24)

審査請求日

平成29年4月21日(2017.4.21)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像装置及びその制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が第1の光電変換部及び第2の光電変換部を有する複数の画素部が行列状に配列された画素領域と、前記画素領域から読み出した信号を保持するための列毎に配置された保持手段とを含む像素子と、

複数行ずつ間引きながら、前記第1の光電変換部及び前記第2の光電変換部の信号を画素部毎に合成して前記保持手段に読み出す第1の駆動方法と、前記間引かれた複数行毎にいづれかの行で前記第1の光電変換部から信号を前記保持手段に読み出し、前記間引かれた複数行毎の別の行で前記第2の光電変換部から信号を前記保持手段に読み出す第2の駆動方法とにより前記像素子を駆動する駆動手段と

を有し、

前記駆動手段は、前記像素子から1フレーム分の信号を読み出して位相差検出を行う場合に、前記第1の駆動方法による第1の走査と前記第2の駆動方法による第2の走査とを連続して行い、前記像素子を駆動することを特徴とする撮像装置。

## 【請求項 2】

前記第1の駆動方法により読み出された信号に基づいて、画像データを生成する生成手段と、

前記第2の駆動方法により読み出された信号に基づいて、焦点状態を検出する焦点検出手段と

を更に有することを特徴とする請求項1に記載の撮像装置。

10

20

**【請求項 3】**

静止画撮影モードと動画撮影モードとを有し、

前記静止画撮影モードが選択されている場合に、前記生成手段は前記第2の駆動方法で読み出された信号を補正し、該補正した信号を用いて画像データを生成することを特徴とする請求項2に記載の撮像装置。

**【請求項 4】**

前記駆動手段は、前記生成手段により生成する画像データによる画像の画質、位相差検出の精度の少なくともいずれかに応じて、前記複数行の行数を決定することを特徴とする請求項2または3に記載の撮像装置。

**【請求項 5】**

前記複数行は2行であって、前記第2の駆動方法では、前記2行のうち、先に走査する1行で前記第1の光電変換部から信号を前記保持手段に読み出し、後に走査する1行で第2の光電変換部から信号を前記保持手段に読み出すことを特徴とする請求項1乃至4のいずれか1項に記載の撮像装置。

**【請求項 6】**

前記複数行は4行であって、前記第2の駆動方法では、前記4行のうち、先に走査する2行で前記第1の光電変換部から信号を前記保持手段に読み出し、後に走査する2行で第2の光電変換部から信号を前記保持手段に読み出すことを特徴とする請求項1乃至4のいずれか1項に記載の撮像装置。

**【請求項 7】**

静止画撮影モードと動画撮影モードとを有し、

前記駆動手段は、前記静止画撮影モードが選択されている場合に、前記画素部から間引かずに、前記第1の光電変換部及び前記第2の光電変換部の信号を画素部毎に合成して前記保持手段に読み出す第3の駆動方法により前記撮像素子を制御し、前記動画撮影モードが選択されている場合に、前記第1の駆動方法と前記第2の駆動方法を交互に繰り返すことを特徴とする請求項1乃至6のいずれか1項に記載の撮像装置。

**【請求項 8】**

前記第1の駆動方法では前記画素領域の予め決められた第1の領域から信号を読み出し、前記第2の駆動方法では、前記第1の領域よりも狭い第2の領域から信号を読み出すことを特徴とする請求項1乃至7のいずれか1項に記載の撮像装置。

**【請求項 9】**

焦点検出領域を設定する設定手段を更に有し、

前記第2の領域は、前記焦点検出領域を含むことを特徴とする請求項8に記載の撮像装置。

**【請求項 10】**

前記撮像素子は、ベイヤー配列のカラーフィルタにより覆われていることを特徴とする請求項1乃至9のいずれか1項に記載の撮像装置。

**【請求項 11】**

各々が第1の光電変換部及び第2の光電変換部を有する複数の画素部が行列状に配列された画素領域と、前記画素領域から読み出した信号を保持するための列毎に配置された保持手段とを含む撮像素子を有する撮像装置の制御方法であって、

複数行ずつ間引きながら、前記第1の光電変換部及び前記第2の光電変換部の信号を画素部毎に合成して前記保持手段に読み出す第1の駆動方法と、前記間引かれた複数行毎にいずれかの行で前記第1の光電変換部から信号を前記保持手段に読み出し、前記間引かれた複数行毎の別の行で前記第2の光電変換部から信号を前記保持手段に読み出す第2の駆動方法とにより前記撮像素子を駆動する駆動工程を有し、

前記駆動工程では、前記撮像素子から1フレーム分の信号を読み出して位相差検出を行う場合に、前記第1の駆動方法による第1の走査と前記第2の駆動方法による第2の走査とを連続して行い、前記撮像素子を駆動することを特徴とする撮像装置の制御方法。

**【発明の詳細な説明】**

10

20

30

40

50

**【技術分野】****【0001】**

本発明は、撮像装置及びその制御方法に関するものである。

**【背景技術】****【0002】**

従来、撮像装置の自動焦点検出及び自動焦点調節において、撮影レンズを通過した光束を用いる一般的な方式として、コントラスト検出方式が知られている。この方式は撮像素子を焦点検出用センサとして用いるもので、撮像素子の出力信号を評価して、そのコントラスト情報が最大となるように撮影レンズの位置を動かすことで焦点調節が可能となる。

**【0003】**

しかしながら、撮影レンズを動かしてはコントラスト情報を評価する必要があるとともに、その評価結果としてコントラストが最大であったことが分かった後に、再度コントラスト最大の位置に撮影レンズを移動させるため、時間を要する。従って、高速な動作は困難であった。

**【0004】**

このような欠点を改善するために撮像素子に位相差検出機能を組み込むことで、撮像素子を焦点検出素子として用いながら、なおかつ撮影レンズのピントずれ量を直接求めることを可能とする技術が提案されている。

**【0005】**

例えば特許文献1では、撮像素子の一部の受光素子に、オンチップマイクロレンズの光軸に対して受光部の感度領域を偏心させることで瞳分割機能を持たせている。これらの画素を撮像素子中に所定の間隔で配置することで位相差検出機能を実現している。

**【0006】**

また、例えば特許文献2では、撮像素子の一つのマイクロレンズに対応する各画素にA画素、B画素という複数の光電変換素子を設け、A画素出力とA+B画素出力を読み出している。この2つの出力を減算処理することでB画素出力を求め、位相差検出機能を実現している。

**【先行技術文献】****【特許文献】****【0007】**

【特許文献1】特開2010-219958号公報

【特許文献2】特開2013-106194号公報

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

特許文献1の実施例中には、いわゆるローリングシャッタ駆動におけるリセットラインを通常画素行と位相差検出画素を含む行とでそれぞれ独立に走査する案が開示されている。この場合、位相差検出画素を含む行において、同一行内に配置された位相差検出画素と通常画素とで、撮像素子内部での信号の読み出し方法は変わらない。

**【0009】**

位相差検出画素は撮像信号としては使用できないため、通常画像を取得する目的では欠陥画素として扱われ、周辺画素から補間処理を行う必要があり、位相差検出画素の配置割合を極端に大きくすることは困難である。そのため、位相差検出画素を含まない場合と同じ読み出し回路構成で実現可能ではあるが、位相差検出のための分解能は低くなる。

**【0010】**

一方で上述の特許文献2に開示された従来技術では、すべての画素を複数の光電変換素子で形成することで、すべての画素が位相差検出素子として利用可能となるため、水平方向の分解能も向上する。しかしながら、すべての画素の複数の光電変換素子からA+B信号とA信号を読み出すために、撮像素子はA+B画素とA画素をそれぞれ読み出すための読み出し回路が必要となる。特に、撮像素子内で比較的大きな面積を必要とする保持容量

10

20

30

40

50

を2倍必要とすること、また制御線も複雑となることから、撮像素子周辺部の回路面積の増大が懸念される。

#### 【0011】

また、特許文献2に示すように、すべての撮像素子の撮像画素が複数の光電変換素子手段から形成される撮像素子では、周辺読み出し回路における回路構成が複雑となり、とくに保持容量といった面積的に比較的大きな回路素子が必要となる。

#### 【0012】

さらにシステム全体としてA+B信号からA信号を減算しB信号を算出する仕組みが必要であり、回路規模の大きさ、コストが課題であった。また、A+B信号とA(またはB)信号を読み出すためには、単純に画素数が2倍になったことと等価であるため、読み出し時間が2倍必要となる。このように、列回路への書き込み時間が増加し、水平転送時間が単純に2倍となるため、高速読み出しが困難となる課題が生じる。10

#### 【0013】

なお、すべての画素からA+B信号と、A信号の両方を読み出すことをせず、特定の行のみA+B信号と、A信号の両方を読み出そうとすると、特定行のみ水平転送時間が長くなる。しかしながら、特定行のみ水平同期の周期を変えることはシステムとしての負荷が非常に大きい。

#### 【0014】

本発明は上記問題点を鑑みてなされたものであり、撮像素子の回路規模、コスト及び読み出し時間を増大することなく、画像の画質を落とさずに、位相差検出に十分な精度で必要な画素信号を読み出すことを目的とする。20

#### 【課題を解決するための手段】

#### 【0015】

上記目的を達成するために、本発明の撮像装置は、各々が第1の光電変換部及び第2の光電変換部を有する複数の画素部が行列状に配列された画素領域と、前記画素領域から読み出した信号を保持するための列毎に配置された保持手段とを含む撮像素子と、複数行ずつ間引きながら、前記第1の光電変換部及び前記第2の光電変換部の信号を画素部毎に合成して前記保持手段に読み出す第1の駆動方法と、前記間引かれた複数行毎にいずれかの行で前記第1の光電変換部から信号を前記保持手段に読み出し、前記間引かれた複数行毎の別の行で前記第2の光電変換部から信号を前記保持手段に読み出す第2の駆動方法とにより前記撮像素子を駆動する駆動手段とを有し、前記駆動手段は、前記撮像素子から1フレーム分の信号を読み出して位相差検出を行う場合に、前記第1の駆動方法による第1の走査と前記第2の駆動方法による第2の走査とを連続して行い、前記撮像素子を駆動する30。

#### 【発明の効果】

#### 【0016】

撮像素子の回路規模、コスト及び読み出し時間を増大することなく、画像の画質を落とさずに、位相差検出に十分な精度で必要な画素信号を読み出すことができる。

#### 【図面の簡単な説明】

#### 【0017】

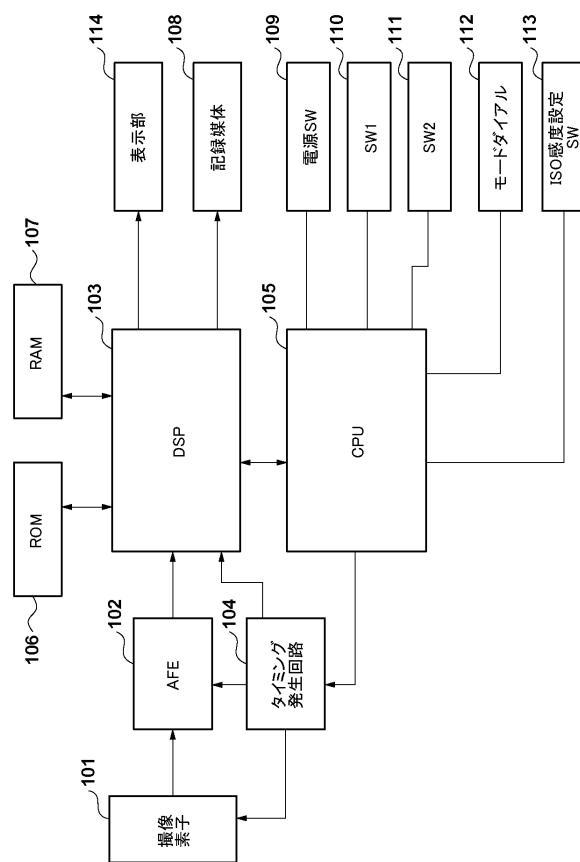

【図1】本発明の実施形態における撮像装置の構成を示すブロック図。40

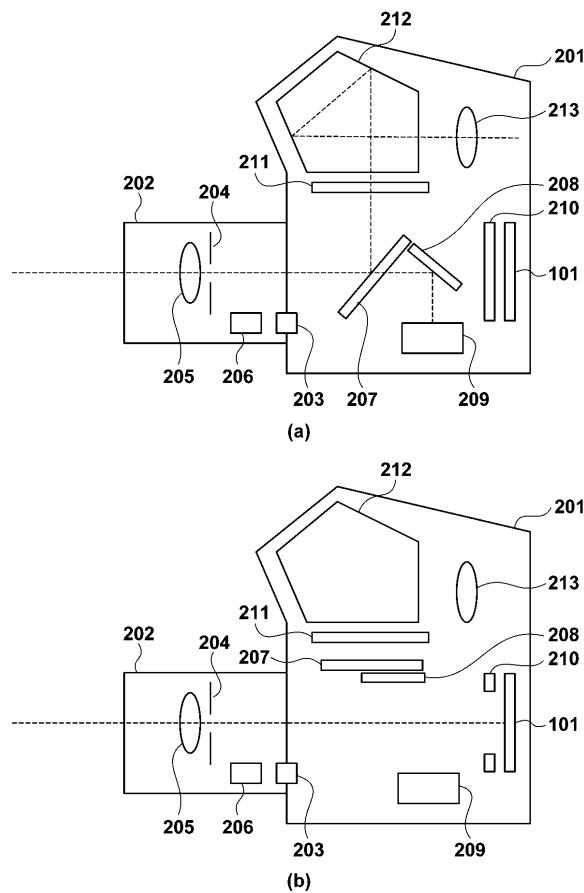

【図2】本実施形態における撮像装置の概略構成を示す側断面図。

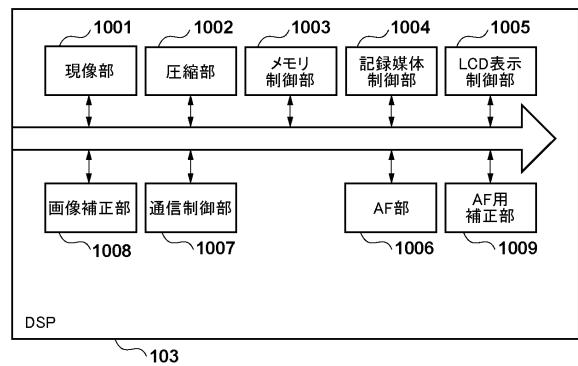

【図3】本実施形態におけるDSP内部の機能を示すブロック図。

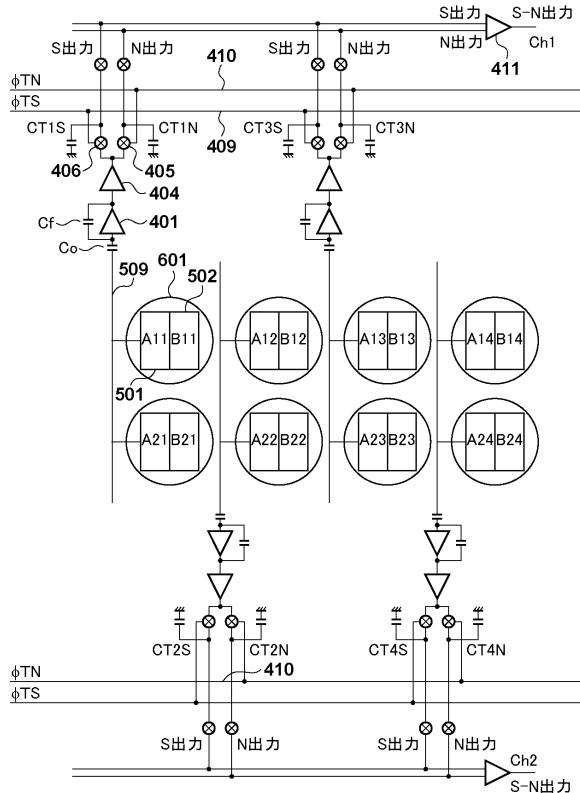

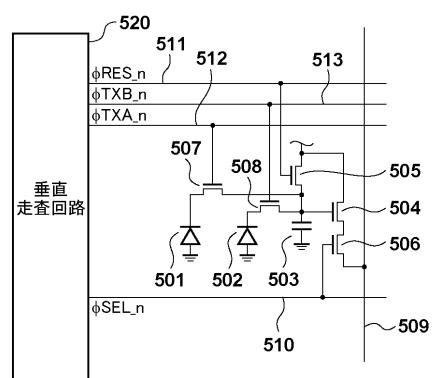

【図4】本実施形態における撮像素子の回路図。

【図5】本実施形態における撮像素子の単位画素の回路図。

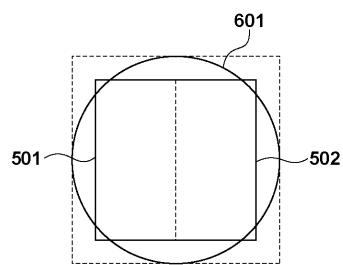

【図6】本実施形態における撮像素子の単位画素の平面図。

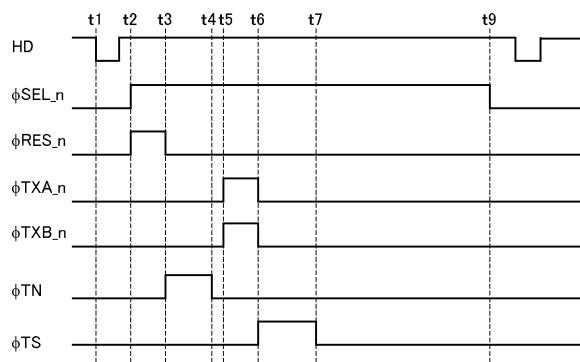

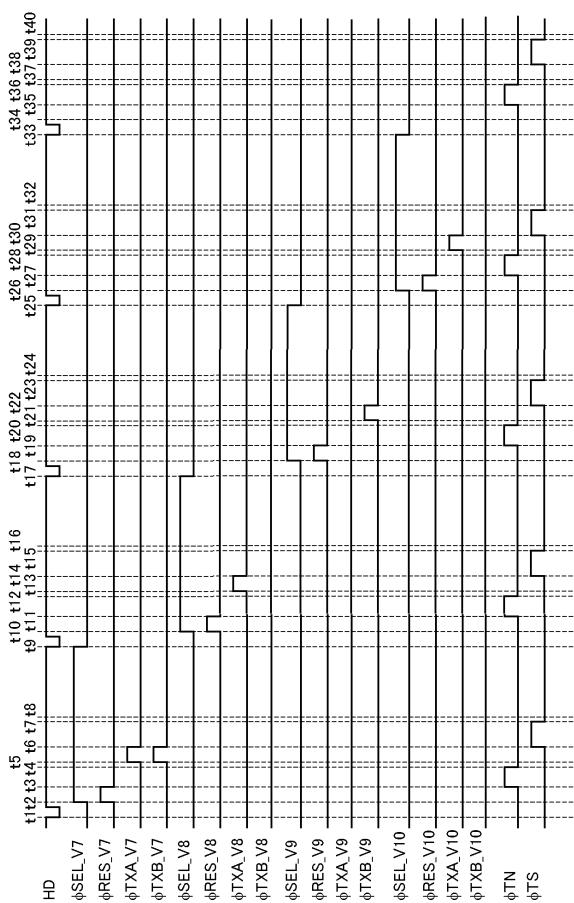

【図7】第1の実施形態における位相差検出を行わない場合の撮像素子の駆動を示すタイミングチャート。

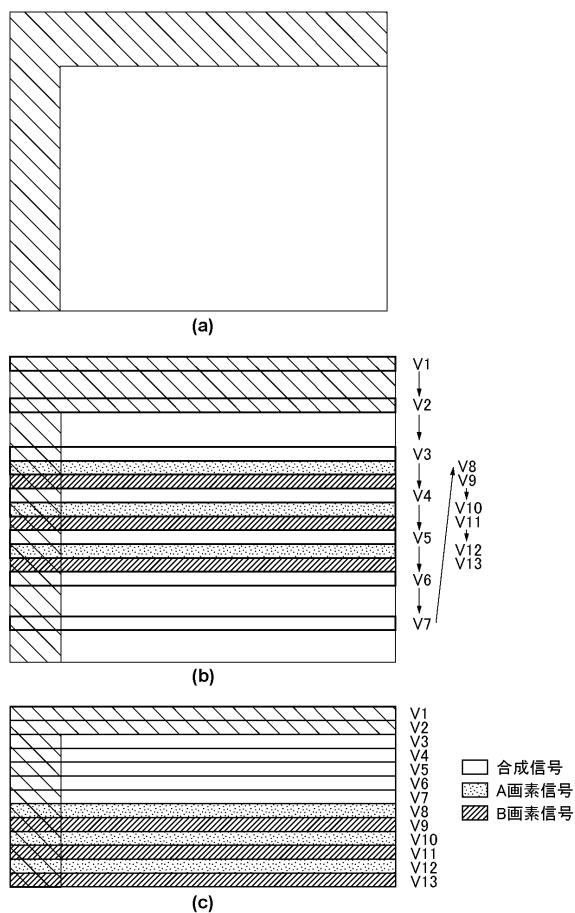

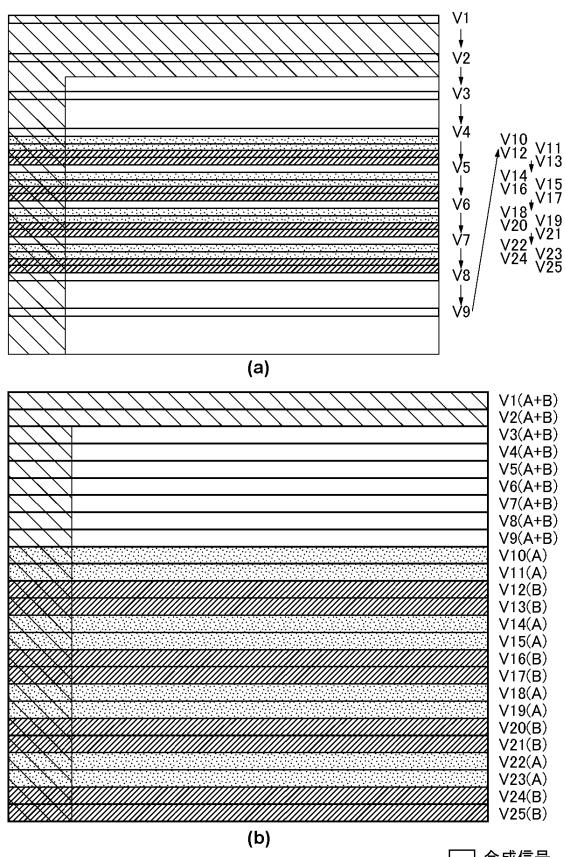

【図8】第1の実施形態における撮像素子の読み出し方法を説明するための模式図。

【図9】第1の実施形態における位相差検出を行う場合の撮像素子の駆動を示すタイミン50

グチャート。

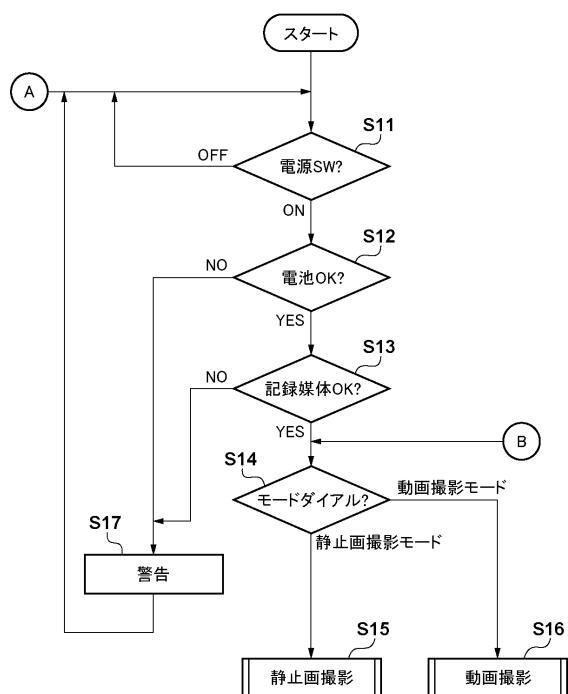

【図10】第1の実施形態における撮像装置の撮影動作を示すフローチャート。

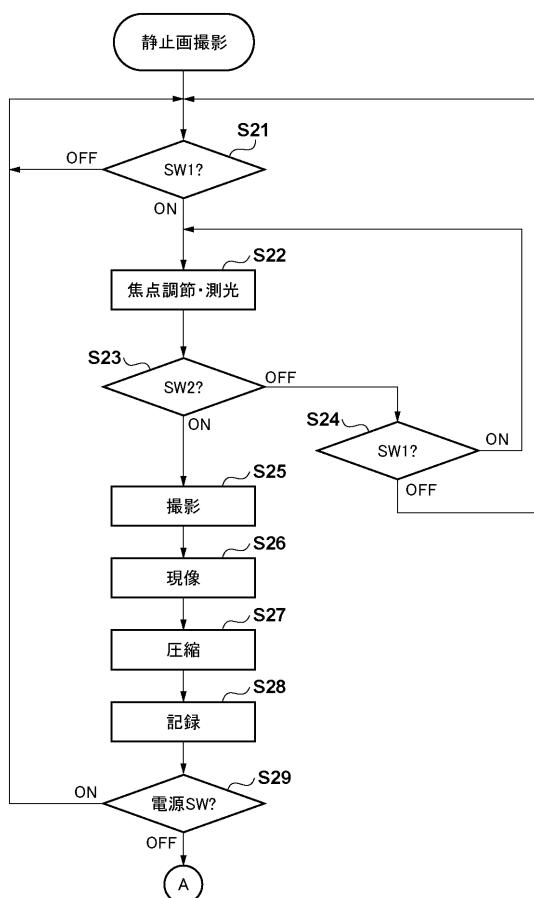

【図11】第1の実施形態における静止画撮影処理を示すフローチャート。

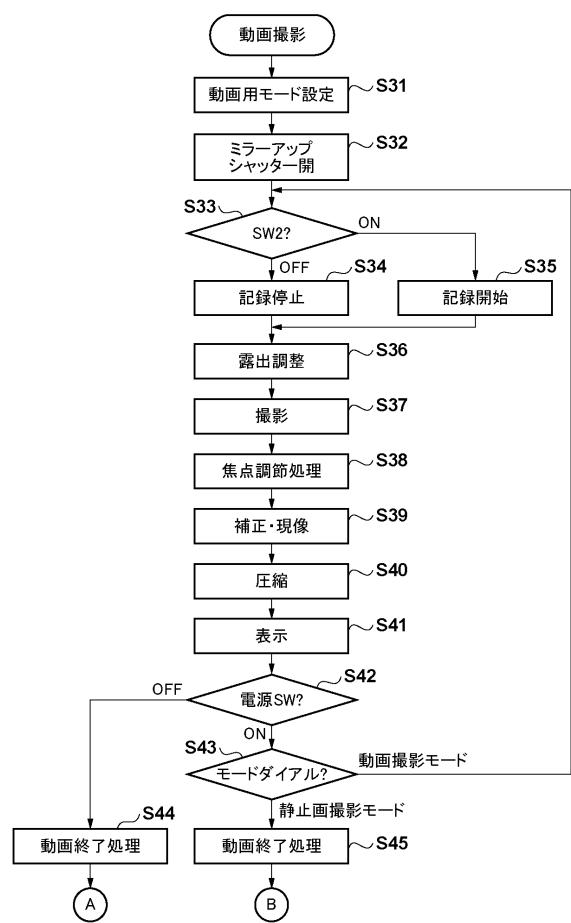

【図12】第1の実施形態における動画撮影処理を示すフローチャート。

【図13】第2の実施形態における像素子の読み出し方法を説明するための模式図。

【図14】任意の画素毎にA画素、B画素を切り替えることが可能な像素子の単位画素の回路図。

【発明を実施するための形態】

【0018】

以下、添付図面を参照して本発明を実施するための最良の形態を詳細に説明する。ただし、本形態において例示される構成部品の寸法、形状、それらの相対配置などは、本発明が適用される装置の構成や各種条件により適宜変更されるべきものであり、本発明がそれらの例示に限定されるものではない。 10

【0019】

<第1の実施形態>

図1は、本発明の第1の実施形態にかかる撮像装置のブロック図である。像素子101は、ISO感度に応じてゲインを切り替える不図示のアンプ回路を内蔵している。アナログフロントエンド(AFE)102は、像素子101からのアナログ信号をデジタル信号に変換するA/D変換器を内蔵し、また、ダークオフセットレベルをクランプする機能を有している。 20

【0020】

DSP(Digital Signal Processor)103は、AFE102から出力されたデータ信号に対して、各種の補正処理、現像処理、圧縮処理を行う。また、DSP103は、RAM107上の画像データに対して各種の補正処理を行うことも可能である。更に、DSP103は、像素子101で発生する各種ノイズの補正処理、欠陥画素の検出及び欠陥画素と位相差検出用画素からの出力の補正処理、位相差検出用画素の周辺画素に対する補正処理等を行う。また、DSP103は、位相差検出用画素からの出力を用いてオートフォーカス情報を算出する演算処理も行う。なお、これらの処理についての詳細は後述する。 30

【0021】

また、DSP103は、ROM106、RAM107等の各種メモリに対するアクセス処理、記録媒体108への画像データの書き込み処理、表示部114に対する各種データの表示処理等を行う。なお、本第1の実施形態ではアナログ出力のCMOS型像素子101とAFE102の組み合わせからなる例を示しているが、デジタル出力タイプのCMOS型像素子を用い、DSP103に直接接続するものであっても構わない。

【0022】

タイミング発生回路104は、CPU105の制御の下、像素子101、AFE102及びDSP103にクロック信号や制御信号を供給し、DSP103と協働して、像素子101の各種読み出しモードに対応したタイミング信号を生成する。 40

【0023】

CPU105は、DSP103及びタイミング発生回路104の制御、並びに測光、焦点調節等のカメラ機能の制御を行う。焦点調節では、像素子101とは別に構成された位相差AFを行なうための不図示の像素子の出力を用いたAFや、像素子101に組み込まれた位相差検出用画素の出力を用いて演算されるオートフォーカス情報を用いたAF等を行うことができる。

【0024】

CPU105には、電源スイッチ109、第1段目のシャッタスイッチSW1(110)、第2段目のシャッタスイッチSW2(111)、モードダイアル112及びISO感度設定スイッチ113等の各種スイッチが接続されている。CPU105は、これらのスイッチ及びダイアルの設定状態に応じた処理を実行する。 50

## 【0025】

R O M 1 0 6 は、撮像装置の制御プログラム、すなわち、C P U 1 0 5 が実行するプログラム、及び各種の補正用データ等を記憶しており、一般的にはフラッシュメモリにより構成されている。R A M 1 0 7 は、R O M 1 0 6 よりも高速にアクセスできるように構成されている。R A M 1 0 7 は、ワークエリアとして利用され、D S P 1 0 3 により処理される画像データ等を一時的に記憶する。記録媒体 1 0 8 としては、例えば撮影された画像データを保存するメモリカード等が用いられ、例えば不図示のコネクタを介してD S P 1 0 3 に接続される。L C D 等により構成される表示部 1 1 4 は、撮像装置の情報を表示したり、撮影した画像を再生表示したり、或いは動画像データを表示するために用いられる。

10

## 【0026】

電源スイッチ 1 0 9 は、撮像装置を起動させる際にユーザにより操作される。不図示のリリーズボタンを操作することにより第1段目のシャッタースイッチ S W 1 ( 1 1 0 ) がオンされた場合は、測光処理、測距処理等の撮影前処理が実行される。更に、第2段目のシャッタースイッチ S W 2 ( 1 1 1 ) がオンされた場合は、不図示のミラー及びシャッタを駆動し、撮像素子 1 0 1 により撮像した画像データをA F E 1 0 2 及びD S P 1 0 3 を介して記録媒体 1 0 8 に書込む一連の撮像動作が開始される。モードダイアル 1 1 2 は、撮像装置の各種の動作モードを設定するために用いられる。I S O 感度設定スイッチ 1 1 3 は、撮像装置の撮影 I S O 感度を設定するために用いられる。

## 【0027】

20

図2は図1に示す撮像装置の概略構成を示す側断面図である。この撮像装置においては静止画を撮影する光学ファインダー使用時の状態と、動画撮影あるいはライブビュー使用時のミラーアップ、シャッタ開状態がある。光学ファインダー使用時の状態を図2 ( a ) に、動画撮影及びライブビュー時のミラーアップ、シャッタ開状態を図2 ( b ) に示す。

## 【0028】

図2に示すように、第1の実施形態における撮像装置は、主に、カメラ本体 2 0 1 と、その前面に装着された撮影レンズ 2 0 2 とからなる。撮影レンズ 2 0 2 は交換可能であり、カメラ本体 2 0 1 と撮影レンズ 2 0 2 はマウント接点群 2 0 3 を介して電気的に接続される。

## 【0029】

30

撮影レンズ 2 0 2 には、絞り 2 0 4 、焦点調整用レンズ群 2 0 5 等が配置されており、いずれもレンズ制御部 2 0 6 により制御される。

## 【0030】

カメラ本体 2 0 1 は、ハーフミラーであるメインミラー 2 0 7 を有し、図2 ( a ) に示す光学ファインダー使用時の状態では、撮影光路上に斜設されて撮影レンズ 2 0 2 からの光をファインダー光学系へ反射する。反射光はピント板 2 1 1 に投影され、撮影者は光路変更用のペントプリズム 2 1 2 、接眼レンズ群 2 1 3 を介して、ピント板 2 1 1 に投影された被写体像を確認することができる。

## 【0031】

40

一方、メインミラー 2 0 7 を透過した一部の光はサブミラー 2 0 8 を介してA F ユニット 2 0 9 に入射する。A F ユニット 2 0 9 は位相差検出方式のA F センサである。位相差 A F については詳細な説明は省略するが、この検出結果を基に、撮影レンズ 2 0 2 の焦点調整用レンズ群 2 0 5 を制御することでA F 動作を行う。

## 【0032】

不図示のリリーズボタンに連動し、半押しでオンするS W 1 ( 1 1 0 ) によりA E やA F 等の撮影準備動作が行われる。全押しでオンするS W 2 ( 1 1 1 ) がONすると、図2 ( b ) に示すように、メインミラー 2 0 7 及びサブミラー 2 0 8 が光路から退避するよう動作し、その後フォーカルプレーンシャッタ 2 1 0 が所定時間開いて、撮像素子 1 0 1 が露光されることとなる。なお、フォーカルプレーンシャッタ 2 1 0 は図2 ( a ) に示すように通常閉状態であり、撮影時のみ指定された秒時の露光を行うよう開動作を行う。

50

## 【0033】

また、モードダイアル112によりモードが切り替えられ、例えばライブビュー状態になると、SW2がONした時の静止画撮影時と同様に、図2(b)に示すように、メインミラー207及びサブミラー208が光路から退避し、その状態が保持される。さらにフォーカルプレーンシャッタ210も開状態を保持し、撮像素子101が常時露光された状態となる。そして、撮像素子101から得られた信号を表示部114に表示することでライブビューモードが実現される。また、この状態で動画像を記録することで、動画モードに対応できる。

## 【0034】

この場合、サブミラー208も光路から退避しているため、AFユニット209へ被写体像が入射しないため、AFユニット209を用いた位相差AFは不可能となる。またメインミラー207も光路から退避しているため、光学ファインダーを用いて被写体像を確認することもできない。

## 【0035】

次に図3を参照して、DSP103の構成について説明する。DSP103は先に説明した画像処理の基本となる現像部1001、圧縮部1002のほかにメモリ制御部1003、記録媒体制御部1004、LCD表示制御部1005がある。さらに、後述する位相差検出用画素の出力からオートフォーカス情報を算出するAF部1006、算出したオートフォーカス情報をCPU105に送信したり、全般的にCPU105と双方向の通信を行う通信制御部1007がある。

10

20

## 【0036】

また、画像生成を行う際に撮像素子101が有する理想状態からの感度や、ダークレベルの誤差をデジタル的に補正するための画像補正部1008、更に、AF用補正部1009を有する。AF用補正部1009は、位相差検出用画素の出力からオートフォーカス情報を算出するために、AF部1006にデータを送出する前に、光学条件の補正をデジタル的に行う。光学条件の補正としては、例えば、位相差検出用画素の理想状態からの感度や、ダークレベルの誤差の補正や、撮影時の撮影レンズ202の焦点距離や絞り値などの補正を含む。

## 【0037】

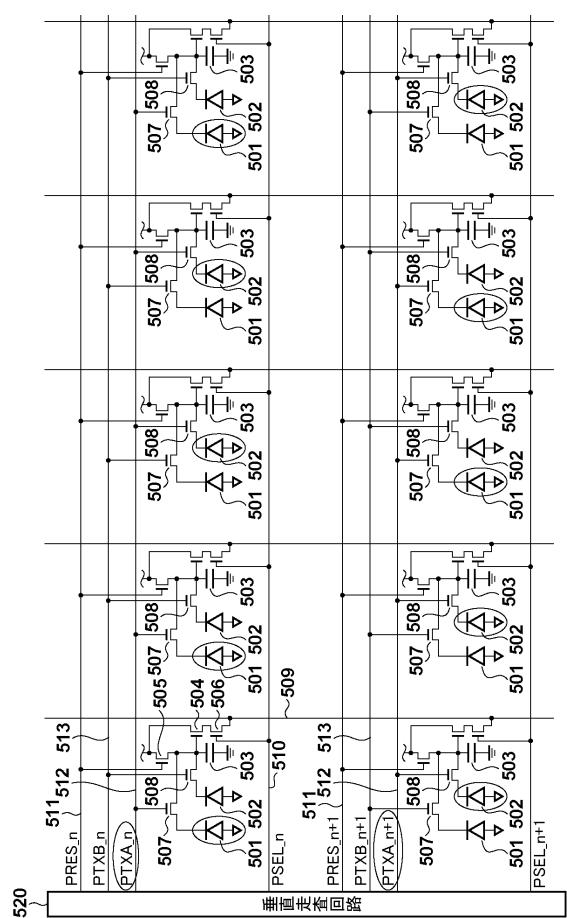

次に、撮像素子101の画素構造について説明する。図4は本第1の実施形態における撮像素子101の構成の一例を示す等価回路図である。画素領域には複数の光電変換部を含む単位画素が、水平及び垂直方向に等間隔で行列状に配列されている。

30

## 【0038】

ここで単位画素の構成について説明する。図5は撮像素子101の第n行目の単位画素の構成を説明するための等価回路図、図6は単位画素の平面図である。図5及び図6において、光電変換部501(第1の光電変換部)及び、光電変換部502(第2の光電変換部)はフォトダイオードにより構成される。光電変換部501及び502は単位画素上部に配置された一つのマイクロレンズ601に対応する領域内部に2つに分割されて配置されており、便宜的に光電変換部501をA画素、光電変換部502をB画素と呼ぶこととする。マイクロレンズ601は点線で示した画素ピッチに接するように形成されている。

40

## 【0039】

マイクロレンズ601に対してオフセットして配置されていることから、A画素とB画素は分割された瞳領域を透過した被写体像を光電変換することとなり、A画素出力、B画素出力を読み出すことで位相差検出が可能となり、焦点検出動作が可能となる。即ち、A画素及びB画素が位相差検出用画素である。

## 【0040】

光電変換部501及び502で発生した電荷は、それぞれ転送トランジスタ507、508を介してフローティングディフュージョン(FD)部503に転送される。FD部503は増幅トランジスタ504のゲートに接続され、画素アンプを構成すると共に、電荷電圧変換部としても機能する。

50

## 【0041】

各転送トランジスタ507、508は垂直走査回路520から制御線512に出力される制御信号TXA\_n、及び、制御線513に出力される制御信号TXB\_nにより制御される。転送トランジスタ507、508は、制御信号TXA\_n、TXB\_nがHのときオン、Lのときオフとなる。なお、各制御信号におけるnは行を示しており、例えば、制御信号TXA\_nは、第n行目の単位画素に対して出力する制御信号TXAであることを表している。

## 【0042】

また垂直走査回路520より出力される制御線511に出力される制御信号RES\_nをHとすることで、リセットトランジスタ505がオンとなり、FD部503をリセットすることができる。また、制御信号TXA\_n及びTXB\_nがHの期間の光電変換部501、502の電荷をリセットすることができる。

10

## 【0043】

垂直走査回路520より出力される制御線510に出力される制御信号SEL\_nがHになると、選択トランジスタ506がオンとなり、増幅トランジスタ504の出力が垂直出力線509に現れる。垂直出力線509には不図示の定電流源が接続され、この垂直出力線509に接続された列ごとの増幅トランジスタ504とからソースフォロワ回路を構成することとなる。

## 【0044】

図4は、上述した単位画素が水平方向に4画素、垂直方向に2画素配置された場合を示す模式図である。なお、実際の撮像素子では、このような画素が数十万から数千万画素程度、配置されている。図4では各単位画素のマイクロレンズ601と、その下のA画素、B画素を模式的に示している。各単位画素は列毎に垂直出力線509に接続されている。

20

## 【0045】

垂直出力線509は各列に用意された列アンプ401に接続する。この列アンプ401は各垂直出力線509の出力に入力容量C0と帰還容量Cfにより定まる所定のゲインを乗じて、後段のフォロワ404に出力する。フォロワ404はこの出力をアナログスイッチ405または406を介して、ノイズ成分保持容量CTkNまたは信号成分保持容量CTkSに出力する。なお、kは、図4に示す例では列を表し、k=1~4である。アナログスイッチ405、406は制御信号TS409またはTN410により制御される。

30

## 【0046】

列毎に第n行目の画素のノイズ成分と信号成分を保持した保持容量CTkN、CTkSは、不図示の水平走査回路によって出力アンプ411の入力に順次接続される。例えば保持容量CT1N、CT1Sが出力アンプ411に接続されると、出力アンプ411は1列目の電圧の差分に対して所定ゲインを乗じて撮像素子101の外部へ出力する。水平走査回路により次の時刻に保持容量CT3N、CT3Sが出力アンプ411に接続され、これを1行の列数分だけ繰り返し一行分の水平走査動作を終える。この動作を撮像素子101の特定行の選択動作を順次垂直方向に進めることで、撮像素子101の所定の画素の出力を得ることが可能となる。

40

## 【0047】

また、このときに各単位画素のA画素とB画素の両方の出力を同時に転送すると、画像生成に好適な同一マイクロレンズ601の下部に配置された画素全体に生じる電荷信号を出力することができる。

## 【0048】

特許文献2の撮像素子とは異なり、第1の実施形態の列回路ではA+B信号またはA信号、またはB信号のいずれかを読み出すための1対の保持容量CTkN、CTkSしか必要としない。すなわち、第1の実施形態の列回路においては、列回路は、位相差検出のために光電変換素子を分離しない、位相差検出を行わない通常の撮像素子のものと同じ回路構成である。

50

**【0049】**

位相差検出を伴わない場合

まず、位相差検出を行わない場合の動作（第3の駆動方法）について、図7に示すタイミングチャートに従って説明する。図7において、時刻t1で水平同期信号HDが入力されると、所定時間後の時刻t2に第n行目の画素群を選択するSEL\_nがHとなり、第n行目の画素の選択トランジスタ506がONとなる。これにより、増幅トランジスタ504の入力に応じた信号が、垂直出力線509に現れる。

**【0050】**

同時に第n行目の画素のリセット信号RES\_nがHとなり、第n行目の画素のリセットトランジスタ505をオンする。その後、所定時間後の時刻t3でリセット信号RES\_nをLとし、リセット動作を解除する。すると垂直出力線509にはリセット解除した状態での信号レベルが現れる。10

**【0051】**

時刻t3で同時に制御信号TNがHとなり、リセット解除時の垂直出力線509の信号レベルが列アンプ401により増幅された信号が、ノイズ成分保持容量CTkNに現れる。時刻t4で制御信号TNをLにすると、リセット解除後の信号レベルが、ノイズ成分保持容量CTkNにホールドされることとなる。

**【0052】**

次に時刻t5で第n行目の画素のA画素及びB画素それぞれの転送トランジスタ507、508をオンにすべく、制御信号TXA\_n、TXB\_nをHとする。この動作によりA画素及びB画素の信号電荷が、共にFD部503へ転送される。20

**【0053】**

所定時間後の時刻t6で制御信号TXA\_n、TXB\_nをLにして転送トランジスタ507、508をオフにし、更に、制御信号TSがHになる。これにより、信号電荷に応じた垂直出力線509の信号レベルが列アンプ401により増幅された信号が、信号成分保持容量CTkSに現れる。そして、時刻t7で制御信号TSをLにすると、信号電荷に応じた信号レベルが、信号成分保持容量CTkSにホールドされることとなる。

**【0054】**

ここまでで第n行目の各画素のリセット解除直後の出力が各列のノイズ成分保持容量CTkNに、信号電荷に応じた出力が各列の信号成分保持容量CTkSに保持されたことになる。この後、不図示の水平転送回路によって、各列のノイズ成分保持容量CTkNと、信号成分保持容量CTkSを順次出力アンプ411に接続し、この差分を所定ゲインを乗じて出力することで第n行目のA画素+B画素の信号（合成信号）の読み出しを完了する。位相差検出が不要な場合はこれまで説明した読み出し動作を行うことで実現できる。30

**【0055】**

上述した駆動方法の概念を図8(a)に示す。図8(a)において、撮像素子101の画素部を示す図である。図中の斜め斜線部は遮光されたオプティカルブラック部(OB部)を示している。先に説明したように、位相差検出を行わない場合には、画素部を構成するすべての画素から、A画素+B画素の信号（合成信号）を読み出す。

**【0056】**

位相差検出を伴う場合

次に位相差検出動作を行う場合の動作について説明する。第1の実施形態で位相差検出動作を行う場合には、垂直方向に所定行数（複数行）ずつ間引きながら、A画素+B画素の信号（合成信号）を読み出す。そして、全面（第1の領域）を垂直方向に走査したのち、再度垂直走査を垂直方向の上部の行に戻し、今度は先に読み出さなかった行のみを再度走査する垂直方向走査を行う。1度目の走査時は対象行の画素から合成信号を読み出し、2度目の走査時には対象行の画素のA画素またはB画素から信号（位相差検出用信号）を読み出す。そして、読み出した位相差検出用信号を用いて位相差検出を行う。このような読み出し方法は動画モード時に好適であるため、第1の実施形態でも動画モードでの適用を想定して説明する。4050

## 【0057】

垂直方向の間引き読み出しを行う場合の読み出し行の模式図を図8(b)に示す。図8(b)において、太枠で囲まれた行が読み出し対象行であり、太枠になつてない部分は読み出し時に間引かれる行である。図8(b)に示す例では、V1行目のA画素及びB画素から合成信号を読み出した後、垂直走査回路520は3行後のV2行目から合成信号を読み出す。引き続き同じ間引き率でV3、V4、V5、V6、V7行目から合成信号を読み出す。ここまで読み出しきを、以下、第1の走査方法(第1の駆動方法)と呼ぶ。第1の走査方法により読み出される行は、画像生成に好適な同一マイクロレンズ601の下部に配置された画素全体に生じる電荷信号を出力することとなり、同じ間引き率で読み出したV1～V7行目の合成信号から、画像データを生成することが可能となる。

10

## 【0058】

なお、第1の実施形態では水平方向には間引きせずに読み出しを行っているため、水平方向と垂直方向の読み出し画素数が異なり、画像の縦横比が異なってしまう。しかしながら後段で縦横比の変換を行ってもよいし、水平方向も同じ比率で一般的な間引き読み出し、あるいは加算間引き読み出しを行ってもよく、任意の方法で縦横比の変換が可能である。

## 【0059】

V7行目まで第1の走査方法で読み出した後、垂直走査回路520はV8行目まで戻り、V8行目に含まれる画素のうち、A画素から位相差検出用信号を読み出す。その後、V8行の次の行であるV9行目に含まれる画素のうち、B画素から位相差検出用信号を読み出す。その後すでに第1の走査方法で読み出しているV4行目をスキップし、V10行目のA画素及び次のV11行目のB画素を読み出す。同様にすでに第1の走査方法で読み出しているV5行目をスキップし、V12行目及び次のV13行目を読み出す。V8以降の駆動方法をここでは第2の走査方法(第2の駆動方法)と呼ぶ。このように、第2の走査方法では、2行連続で読み出す行の組の内、最初に読み出す行ではA画素の信号のみを読み出し、後で読み出す行ではB画素の信号のみを読み出す。なお、第2の走査方法で読み出す領域(第2の領域)は、焦点状態を検出するために予め設定された焦点検出領域を含む、第1の走査方法で読み出す領域(第1の領域)よりも狭い領域である。焦点検出領域は、不図示の操作部によりユーザが所望の領域を指定しても良いし、被写体検出等による公知の方法により自動的に設定しても良いし、あるいは、固定の領域であっても良い。第2の走査方法では焦点検出用信号を読み出すことが目的であるため、第2の領域は焦点検出領域を含む最も狭い領域とすることが好ましい。

20

## 【0060】

こうして読み出した順序に従って処理される順序に画素配置を並べ替えると、図8(c)に示す模式図のようになる。先に説明したように、V1～V7行目は第1の走査方法によりA画素及びB画素から合成信号を読み出しているため、この出力を用いて通常の画像生成が可能である。V8～V13行目は第2の走査方法によりA画素またはB画素から焦点検出用信号を読み出しているため、この2行毎に得られるペアのA画素出力とB画素出力を用いて位相差検出が可能である。

30

## 【0061】

この場合の位相差検出の方法としては、撮像素子101がベイヤー配列のカラーフィルタが形成されている場合、2行連続で読み出す行の組のうち、最初にA画素から読み出す行のG画素信号と、後でB画素から読み出す行のG画素信号の相関を算出する。

40

## 【0062】

次に、第1の走査方法による駆動について図9に示すタイミングチャートを参照して説明する。ここでは、第1の走査方法で読み出す最終行のV7行目からの読み出し動作について説明する。図9において、時刻t1で水平同期信号HDが入力されると、所定時間後の時刻t2にV7行目の画素群を選択するSEL\_V7がHとなり、V7行目の画素の選択トランジスタ506がONとなる。これにより増幅トランジスタ504の入力に応じた信号が垂直出力線509に現れる。同時にV7行目の画素のリセット信号RES\_V

50

V7がHとなり、V7行目の画素のリセットトランジスタ505をオンする。

#### 【0063】

その後、所定時間後の時刻t3でリセット信号RES\_V7をLとし、リセット動作を解除する。すると垂直出力線509にはリセット解除した状態での信号レベルが現れる。時刻t3で同時に制御信号TNがHとなり、リセット解除時の垂直出力線509の信号レベルが列アンプ401で増幅された信号がノイズ成分保持容量CTkNに現れる。時刻t4で制御信号TN410をLにすると、リセット解除後の信号レベルが、ノイズ成分保持容量CTkNにホールドされることとなる。

#### 【0064】

次に時刻t5でV7行目のA画素及びB画素それぞれの転送トランジスタ507、508をオンにすべく、制御信号TXA\_V7、TXB\_V7をHとする。この動作によりA画素及びB画素の信号電荷がともにFD部503に転送される。さらに所定時間後の時刻t6で転送トランジスタ507、508をオフにすると、A画素及びB画素の信号電荷がともにFD部503にホールドされる。さらに時刻t6で制御信号TSがHになると、信号電荷に応じた垂直出力線509の信号レベルが列アンプ401で増幅された信号が信号成分保持容量CTkSに現れる。時刻t7で制御信号TSをLにすると、信号電荷に応じた信号レベルが、信号成分保持容量CTkSにホールドされることとなる。

10

#### 【0065】

ここまででV7行目の各画素のリセット解除直後の出力が各列のノイズ成分保持容量CTkNに、信号電荷に応じた出力が各列の信号成分保持容量CTkSに保持されたことになる。この後、不図示の水平転送回路によって、各列のノイズ成分保持容量CTkNと、信号成分保持容量CTkSを順次出力アンプ411に接続し、この差分を所定ゲインを乗じて出力することでV7行目の合成信号の読み出しを完了する。ここではV7行目の動作を説明したがV1～V6行での動作も同様である。

20

#### 【0066】

次に時刻t9で次の水平同期信号HD信号が入力すると、それまで第V7行目を選択していたSEL\_V7がLとなる。そして所定時間後の時刻t10にV8行目の画素群を選択するSEL\_V8がHとなり、V8行目の画素の選択トランジスタ506がONとなる。これにより増幅トランジスタ504の入力に応じた信号が垂直出力線509に現れる。同時にV8行目の画素のリセット信号RES\_V8がHとなり、V8行目の画素のリセットトランジスタ505をオンする。

30

#### 【0067】

その後、所定時間後の時刻t11でリセット信号RES\_V8をLとし、リセット動作を解除する。すると、垂直出力線509にはリセット解除した状態での信号レベルが現れる。時刻t11で同時に制御信号TNがHとなり、リセット解除時の垂直出力線509の信号レベルが列アンプ401で増幅された信号がノイズ成分保持容量CTkNに現れる。時刻t12で制御信号TNをLにすると、リセット解除後の信号レベルが、ノイズ成分保持容量CTkNにホールドされることとなる。

#### 【0068】

次に時刻t13でV8行目の画素のA画素のみの転送トランジスタ507をオンにすべく、制御信号TXA\_V8をH、TXB\_V8をLとする。この動作によりA画素のみの信号電荷がFD部503へ転送される。さらに所定時間後の時刻t14で転送トランジスタ507をオフにすると、この動作によりA画素のみの信号電荷がFD部503にホールドされることとなる。さらに時刻t14で制御信号TSがHになると、信号電荷に応じた垂直出力線509の信号レベルが列アンプ(401)で増幅された信号が信号成分保持容量CTkSに現れる。時刻t15で制御信号TSをLにすると、信号電荷に応じた信号レベルが、信号成分保持容量CTkSにホールドされることとなる。

40

#### 【0069】

ここまででV8行の各画素のリセット解除直後の出力が各列のノイズ成分保持容量CTkNに、信号電荷に応じた出力が各列の信号成分保持容量CTkSに保持されたことにな

50

る。この後、不図示の水平転送回路によって、各列のノイズ成分保持容量 C T k N と、信号成分保持容量 C T k S を順次出力アンプ 4 1 1 に接続し、この差分を所定ゲインを乗じて出力することで V 8 行目の A 画素のみの信号読み出しを完了する。

#### 【 0 0 7 0 】

次に時刻 t 1 7 で次の水平同期信号 H D 信号が入力すると、それまで V 8 行目を選択していた S E L \_ V 8 が L となる。そして所定時間後の時刻 t 1 8 に V 9 行目の画素群を選択する S E L \_ V 9 が H となり、V 9 行目の画素の選択トランジスタ 5 0 6 が O N となる。これにより増幅トランジスタ 5 0 4 の入力に応じた信号が垂直出力線 5 0 9 に現れる。同時に V 9 行目の画素のリセット信号 R E S \_ V 9 が H となり、V 9 行目の画素のリセットトランジスタ 5 0 5 をオンする。その後、所定時間後の時刻 t 1 9 でリセット信号 R E S \_ V 9 を L とし、リセット動作を解除する。すると垂直出力線 5 0 9 にはリセット解除した状態での信号レベルが現れる。時刻 t 1 9 で同時に制御信号 T N が H となり、リセット解除時の垂直出力線 5 0 9 の信号レベルが列アンプ 4 0 1 で増幅された信号がノイズ成分保持容量 C T k N に現れる。時刻 t 2 0 で T N を L にすると、リセット解除後の信号レベルが、ノイズ成分保持容量 C T k N にホールドされることとなる。10

#### 【 0 0 7 1 】

次に時刻 t 2 1 で V 9 行目の画素の B 画素のみの転送トランジスタ 5 0 7 をオンにすべく、制御信号 T X A \_ V 9 を L 、 T X B \_ V 9 を H とする。さらに所定時間後の時刻 t 2 2 で制御信号 T X B \_ V 9 を L にし、転送トランジスタ 5 0 7 をオフにすると、この動作により B 画素のみの信号電荷が F D 部 5 0 3 へ転送される。さらに時刻 t 2 2 で制御信号 T S が H になると、信号電荷に応じた垂直出力線 5 0 9 の信号レベルが列アンプ 4 0 1 で増幅された信号が信号成分保持容量 C T k S に現れる。時刻 t 2 3 で制御信号 T S を L にすると、信号電荷に応じた信号レベルが、信号成分保持容量 C T k S にホールドされることとなる。20

#### 【 0 0 7 2 】

ここまでで V 9 行目の各画素のリセット解除直後の出力が各列のノイズ成分保持容量 C T k N に、信号電荷に応じた出力が各列の信号成分保持容量 C T k S に保持されたことになる。この後、不図示の水平転送回路によって、各列のノイズ成分保持容量 C T k N と、信号成分保持容量 C T k S を順次出力アンプ 4 1 1 に接続し、この差分を所定ゲインを乗じて出力することで V 9 行目の B 画素のみの信号読み出しを完了する。30

#### 【 0 0 7 3 】

以下同様に V 1 0 行目は A 画素の信号のみを読み出し、V 1 1 行目は B 画素の信号のみを読み出す動作を繰り返すことで、所望の読み出し動作が完了する。

#### 【 0 0 7 4 】

##### 撮影動作

次に、本第 1 の実施形態における撮像装置の撮影動作の概要を図 1 0 のフローチャートに基づいて説明する。C P U 1 0 5 は、電源スイッチ 1 0 9 がオンされると ( S 1 1 ) 、撮影に必要な電気エネルギーがバッテリに残存しているか否かを判別する ( S 1 2 ) 。その結果、撮影に必要な電気エネルギーがバッテリに残存していないければ、C P U 1 0 5 は、その旨の警告メッセージを表示部 1 1 4 に表示して ( S 1 7 ) 、S 1 1 に戻り、電源スイッチ 1 0 9 が再度オンされるのを待つ。40

#### 【 0 0 7 5 】

撮影に必要な電気エネルギーがバッテリに残存していれば、C P U 1 0 5 は、記録媒体 1 0 8 をチェックする ( S 1 3 ) 。このチェックは、所定容量以上のデータを記録可能な記録媒体 1 0 8 が撮像装置に装着されているか否かを判断することにより行う。所定容量以上のデータを記録可能な記録媒体 1 0 8 が撮像装置に装着されていない場合は、C P U 1 0 5 は、その旨の警告メッセージを表示部 1 1 4 に表示して ( S 1 7 ) 、S 1 1 に戻る。50

#### 【 0 0 7 6 】

所定容量以上のデータを記録可能な記録媒体 1 0 8 が撮像装置に装着されている場合は

、C P U 1 0 5 は、モードダイアル 1 1 2 により設定された撮影モードが静止画撮影モード、動画撮影モードの何れであるかを判別する ( S 1 4 )。そして、C P U 1 0 5 は、静止画撮影モードが設定されていれば、静止画撮影処理を行い ( S 1 5 )、動画撮影モードが設定されていれば、動画撮影処理を行う ( S 1 6 )。

#### 【 0 0 7 7 】

ここで、S 1 5 で行われる静止画撮影の詳細について、図 1 1 のフローチャートを参照して説明する。静止画撮影処理では、C P U 1 0 5 は、まず、シャッタスイッチ S W 1 がオンされるのを待つ ( S 2 1 )。シャッタスイッチ S W 1 がオンされると、C P U 1 0 5 は、不図示の測光制御部からの測光情報を用いて、撮影レンズ 2 0 2 の絞り 2 0 4 の絞りとシャッタ速度を決定する測光処理を行う。更に、A F ユニット 2 0 9 からの焦点検出情報を用いて、撮影レンズ 2 0 2 の焦点調整用レンズ群 2 0 5 を被写体位置に合わせる焦点調節処理を行う ( S 2 2 )。

#### 【 0 0 7 8 】

次に、C P U 1 0 5 は、シャッタスイッチ S W 2 がオンされたか否かを判別する ( S 2 3 )。その結果、シャッタスイッチ S W 2 がオンされていなければ、C P U 1 0 5 は、シャッタスイッチ S W 1 のオン状態が継続しているか否かを判別する ( S 2 4 )。シャッタスイッチ S W 1 のオン状態が継続していれば、S 2 3 に戻って、シャッタスイッチ S W 2 がオンされたか否かを判別する。一方、シャッタスイッチ S W 1 のオン状態が継続していなければ、S 2 1 に戻って、シャッタスイッチ S W 1 が再度オンされるのを待つ。

#### 【 0 0 7 9 】

S 2 3 にて、シャッタスイッチ S W 2 がオンされたと判別された場合は、C P U 1 0 5 は、撮影処理を実行する ( S 2 5 )。静止画の撮影時には、上述した位相差検出を伴わない駆動方法により、図 8 ( a ) に示すように撮像素子 1 0 1 の全領域から A 画素と B 画素の合成信号を読み出す。これにより画像生成に好適な同一マイクロレンズ 6 0 1 の下部に配置された画素全体に生じる電荷信号を出力することができる。

#### 【 0 0 8 0 】

次に、C P U 1 0 5 は、D S P 1 0 3 に得られた合成信号 ( 画像データ ) に対する現像処理を実行させる ( S 2 6 )。更に C P U 1 0 5 は、D S P 1 0 3 に現像処理が施された画像データに圧縮処理を実行させて、その圧縮処理が施された画像データを R A M 1 0 7 の空き領域に格納させる ( S 2 7 )。次に、C P U 1 0 5 は、D S P 1 0 3 により R A M 1 0 7 に格納されている画像データの読み出しと、記録媒体 1 0 8 への記録処理を実行する ( S 2 8 )。

#### 【 0 0 8 1 】

そして、C P U 1 0 5 は、電源スイッチ 1 0 9 のオン / オフ状態をチェックする ( S 2 9 )。電源スイッチ 1 0 9 がオンのままであれば S 2 1 へ戻り、C P U 1 0 5 は次の撮影に備える。一方、電源スイッチ 1 0 9 がオフされていれば、図 6 の S 1 1 に戻り、電源スイッチが再度オンされるのを待つ。

#### 【 0 0 8 2 】

次に、S 1 6 で行われる動画撮影処理の詳細について、図 1 2 のフローチャートを参照して説明する。なお、第 1 の実施形態では、動画撮影モードになると、シャッタ 2 1 0 を開き、撮像素子 1 0 1 から読み出される画像データを現像して表示部 1 1 4 上に表示し続けるモニタ動作を行う。また、シャッタスイッチ S W 2 がオンしている間は、動画データを記録媒体 1 0 8 に記録し続けるものとする。動画撮影モードから抜け出るには、モードダイアル 1 1 2 の設定を動画撮影モード以外に変更するか、電源スイッチ 1 0 9 をオフする。

#### 【 0 0 8 3 】

まず、C P U 1 0 5 は、モードダイアル 1 1 2 により選択された動画撮影モードに設定され ( S 3 1 )、メインミラー 2 0 7 、サブミラー 2 0 8 、フォーカルプレーンシャッタ 2 1 0 の開動作を行う ( S 3 2 )。これにより、図 2 ( b ) に示すように、撮像素子 1 0 1 に常時被写体像が入射するようになる。

10

20

30

40

50

## 【0084】

次に、CPU105は、シャッタスイッチSW2がオンされているか否かを判別する(S33)。シャッタスイッチSW2がオンされている場合には、CPU105は、記録媒体108に動画像データを書き込む記録動作を開始する(S35)。一方、シャッタスイッチSW2がオフされている場合には、CPU105は、記録媒体108に動画像データを書き込む記録動作が現在実行されていれば、その記録動作を停止する(S34)。このように、CPU105は、シャッタスイッチSW2がオンされている間は、動画像データの記録処理を継続し、シャッタスイッチSW2がオフされた時点で動画像データの記録処理を停止する。ただし、シャッタスイッチSW2がオフされなくても、所定時間が経過した時点や、記録媒体108の残容量が少なくなった時点で、記録動作を停止するように制御してもよい。

10

## 【0085】

S34またはS35の後、CPU105は、表示部114への画像データのモニタ表示を繰り返すモニタ動作を行うべく、露出調整を行う(S36)。この露出調整では、直前に撮影した画像データから露光量を判断し、適切な露光量となるように、撮影レンズ202の絞り204やAFE102内部のゲインを設定する。ただし、最初の動画撮影時には直前のデータが存在しないため、レンズの絞り204やAFE102内部のゲインとしては、初期値が設定される。

## 【0086】

次に、S37において、CPU105は撮影処理を行う。動画撮影モードでは、上述した位相差検出を伴う駆動を行う。まず、撮像素子101上の画素を、そして図8(b)及び(c)で説明したように、第1の走査方法で垂直方向に3行毎に1行読み出す。第1の走査方法による走査終了後、位相差検出用信号を得るために、第2の走査方法による読み出しを行う。なお、第2の走査方法で読み出しを行う(第2の領域)は、AFを行う焦点検出領域に応じて指定される。

20

## 【0087】

第2の走査方法により読み出した位相差検出用信号は、DSP103内のAF用補正部1009に転送される。そして、このうちのペイヤー配列のGフィルタが配置された画素信号のみを選択して、画素毎の補正や、撮影時の光学条件に対応する補正が行われる。

## 【0088】

その後、その補正結果をAF部1006に転送し、異なる瞳領域から形成された2種類の画素出力であるA画素系列とB画素系列の信号を基に、ここで既知の相関演算等を用いて位相差検出結果を算出し、焦点検出動作を行う。その算出結果をCPU105が受け取り、撮影レンズ202内の焦点調整用レンズ群205の位置制御を行うことで、オートフォーカス制御を行う(S38)。

30

## 【0089】

一方、撮像素子101中の第1の走査方法で得られる合成信号に対して、画像補正部1008で撮像素子101が有する理想状態からの感度や、ダークレベルの誤差をデジタル的に補正する。更に、現像部1001で撮像素子101の欠陥画素の補正処理を行い、さらに現像処理(S39)、圧縮部1002での圧縮処理(S40)を行う。この際に、シャッタスイッチSW2がオン状態で動画記録中であれば、圧縮した画像信号を記録媒体108に記録する。そして、これらの処理結果を、LCD表示制御部1005を用いて表示部114に表示する(S41)。上述の動作を表示に必要なフレームレートで繰り返すことで、動画用の動作が可能となる。

40

## 【0090】

次に、CPU105は、電源スイッチ109がオフされているかの判断を行い(S42)、オフされていれば動画終了処理を行って(S44)、図12のS11にリターンする。一方、電源スイッチ109がオン状態のままであれば(S42)、CPU105は、モードダイアル112をチェックする(S43)。モードダイアル112が動画撮影モードのままであれば、S33に戻り、モードダイアル112が静止画モードに切り替えられて

50

いれば、動画終了処理を行って（S45）、図10のS14にリターンする。

【0091】

S44、S45の動画終了処理では、現在記録動作中であれば記録動作の停止、撮像素子101の駆動停止、DSP103の処理の停止を行う。更に、フォーカルプレーンシャッタ210を閉じるとともにメインミラー207、サブミラー208をダウンする。

【0092】

このように動画撮影モード時には、第1の走査方法で垂直方向に間引きながら読み出した合成信号を用いて動画像を生成するとともに、後半の第2の走査方法で読み出した位相差検出用信号を用いて位相差を算出することが可能となる。そして、動画撮影が行われている間、第1の走査方法と第2の走査方法が交互に繰り返されることにより、動画像の画像データとしての品質を保持したまま、撮像素子の出力のみを用いたオートフォーカス制御を実現することができる。10

【0093】

また、このように画像データが、画像生成用の合成信号、位相差検出用信号の順序で出力されることから、その処理内容、補正処理も時間で分離できる。そのため、読み出した信号から位相差検出用信号を分離して、一方は現像処理、一方は位相差検出演算のためAF部に振り分けるといった処理を行ったり、画像データ生成のために位相差検出用信号を補正したりする処理が不要となる。このため、大幅な処理の効率化が可能となる。

【0094】

また、第1の実施形態における動画撮影モード時の撮像素子の読み出し方では、動画像用の合成信号の読み出し時に、位相差検出用信号を読み出さないように制御している。そのため、動画像の画像データを得る際に、位相差検出用信号により生じる画質の低下について懸念する必要が無い。更に、位相差検出動作も垂直走査回路の操作方法の切り替えにより、任意の領域での検出が可能になる。20

【0095】

また、本第1の実施形態では、動画撮影モード時には前半の第1の走査方法で合成信号を読み出して動画像を生成し、後半の第2の走査方法で位相差検出用信号を読み出してオートフォーカス情報を算出するように説明している。しかしながら本発明はこれに限るものではなく、前半に第2の走査方法で位相差検出用信号を読み出してオートフォーカス情報を算出し、その後、第1の走査方法で合成信号を読み出して動画像を生成してもよい。この場合にはオートフォーカス情報が先に検出できるため、より早くレンズの駆動ができるというメリットがある。これは、垂直走査回路520による走査順序を変更するだけであるので、容易に実現することができる。また、CPU105からどちらの駆動方法から行うかを、例えばフレーム毎に設定し切り替えることも可能である。30

【0096】

上記の通り本第1の実施形態によれば、複数の光電変換部を有する画素部を有し、垂直走査回路内のロジック回路の機能追加で、読み出し行ごとにA+B画素の出力を読み出すか、A画素またはB画素のいずれかを読み出すか切り替え可能とする。これにより、回路規模を大きくせずに、画像の画質を落とすこと無く、位相差検出に十分な精度で必要な画素信号を読み出すことが可能となる。40

【0097】

また必要な領域のみ位相差検出用の画素信号を読み出すため、すべての画素の合成信号と、位相差検出用信号を読み出す必要が無く、読み出し時間が大幅に短縮され、読み出し動作の高速化を実現することができる。

【0098】

また特定行のみ、すべての画素の画像用信号と、位相差検出用信号を読み出す必要が無いため、特定行のみ水平走査期間が変化するような複雑な制御を行う必要が無く、従来システムからの対応が容易である。

【0099】

<第2の実施形態>

10

20

30

40

50

次に、本発明の第2の実施形態について説明する。第1の実施形態においては第2の走査方法で2行連続で読み出し、先に読み出す行のGフィルタ画素出力のA画素信号と、次行のGフィルタ画素出力のB画素信号を用いて位相差検出を行うものとして説明した。これに対し、本第2の実施形態では、まず、4行ずつ間引きながら画像データ用の合成信号を読み出し、次に、間引いた4行を連続で読み出す。その際に、先に読み出す2行はA画素から信号を読み出し、次の2行はB画素から信号を読み出すように撮像素子を駆動し、ベイヤーフィルタ配置のすべての画素情報を用いて位相差検出を行う。このときの読み出した画像の概念を図13(a)および(b)に示す。

#### 【0100】

なお、合成信号を読み出すための駆動制御及び位相差検出用信号を読み出すための駆動制御は第1の実施形態で説明したものと同様であり、垂直走査回路により自由に切り替えることができる。10

#### 【0101】

図13(a)は、本第2の実施形態における位相差検出を伴う場合の読み出し行の模式図を示している。図13(a)の中で太枠で囲まれた行が読み出し対象行であり、太枠になっていない部分は読み出し時に間引かれる行である。すなわちV1行目を読み出した後、垂直走査回路520は3行後のV2行目を読み出す。引き続き同じ間引き率でV3、V4、V5、V6、V7、V8、V9行目の読み出しを行う。ここまでを第3の走査方法(第1の駆動方法)と呼ぶ。

#### 【0102】

V9行目まで第3の走査方法で読み出した後、垂直走査回路520はV10行目まで戻り、V10行目を読み出した後、続けてV11、V12、V13行目を読み出す。その後、すでに第3の走査方法で読み出しているV5行目をスキップし、V14～V17行目を読み出す。その後、同様にすでに第3の走査方法で読み出しているV6行目をスキップし、V18～V21行目を読み出す。その後すでに第3の走査方法で読み出しているV7行目をスキップしV22～V25行目を読み出す。V10行目以降の駆動方法を、第4の走査方法(第2の駆動方法)と呼ぶ。20

#### 【0103】

次にそれぞれの読み出し行ごとの画素読み出しについて説明する。第3の走査方法では、先に説明したように各行のA画素及びB画素から合成信号を読み出すようとする。第3の走査方法で読み出される行は、画像生成に好適な同一マイクロレンズ601の下部に配置された画素全体に生じる電荷信号を出力することとなる。そのため、第3の走査方法で読み出したV1～V9行目の合成信号から、画像データを生成することが可能である。30

#### 【0104】

なお、第2の実施形態では水平方向には間引きせずに読み出しを行っているため、水平方向と垂直方向の読み出し画素数が異なり、画像の縦横比が異なってしまう。しかしながら後段の縦横比の変換を行ってもよいし、水平方向も同じ比率で一般的な間引き読み出し、あるいは加算間引き読み出しを行ってもよく、任意の方法で縦横比の変換が可能である。

#### 【0105】

次に第4の走査方法で4行連続で読み出す行の組のうち、先に読み出す2行は画素信号のうちA画素のみ読み出し、後で読み出す2行は画素信号のうちB画素のみ読み出す。このようにして読み出した順序に従って、処理される順序に画素配置を並べ替えると図13(b)に示す模式図のようになる。40

#### 【0106】

先に説明したように、V1～V9行目は第1の走査方法によりA画素及びB画素の合成信号を読み出しており、この出力を用いて通常の画像生成が可能である。一方、V10～V25行目は第4の走査方法によりA画素のみを読み出す連続した2行と、B画素を読み出す隣接する連続した2行からなる。この2行ペア同志のA画素出力とB画素出力を用いることで位相差検出が可能である。この場合の位相差検出の方法としては、A画素信号、50

B 画素信号のいずれにもペイヤーフィルタ配置のすべての画素情報が含まれているので、これらの色情報をすべてを用いて位相差検出を行うことが可能となる。

#### 【0107】

もちろんこれ以外の対応も垂直走査回路 520 の設定変更だけで可能であり、第3の走査方法における垂直方向の間引き率を 1 / 5 としながら、第4の走査方法を第1の実施形態と同様に連続した2画素を A 画素を読む行と、B 画素を読む行にしてもよい。

#### 【0108】

上記の通り、本第2の実施形態によれば、上述した第1の実施形態の効果に加え、第4の走査方法により読み出したすべての画素信号を位相差検出に使用することができる。このように、垂直走査回路 520 の設定次第で、画像生成に使用する行の設定、位相差検出に使用する行の設定は非常に自由度が高く、画像の品質、位相差検出の精度、検出領域、合わせた読み出し速度（フレームレート）等に応じて任意の設定が可能である。10

#### 【0109】

##### <変形例>

上述した第1及び第2の実施形態のほかにも自由な展開が可能であり、位相差検出を実行するときの画像生成用領域の画像の画質、位相差検出の精度等に応じて自由に設定することが可能となる。

#### 【0110】

また、撮像素子の画素はカラーフィルタを除いて同様の構成を有するので、垂直走査回路 520 の構成次第で、位相差検出を行う読み出し行を任意に選択することが可能となる。20

#### 【0111】

また、上述した実施形態では水平方向の読み出し方法については言及していないが、水平方向を間引きしたり、同色の加算、加算平均処理を行っても本実施形態における発明を適用することができる。

#### 【0112】

また、上述した実施形態では、垂直方向に全行読み出す静止画時の適用については言及していないが、全行読み出す中で特定行のみを A 画素信号のみ、また別の特定行を B 画素信号のみ読み出し、位相差検出を行うこともできる。ただしこの場合には画像生成に使用する領域の画像データを A 画素、B 画素として兼用することになる。また、この場合、A 画素、B 画素出力は、本来の画像用の出力に対して情報量が欠落しているため、画像生成時に該当画素に対して何らかの補正処理を行うことが必要となる。このような補正処理を行うことで静止画読み出し時にも適用可能である。30

#### 【0113】

また本実施形態の説明の中では必ず画像生成用の第1の駆動方法と位相差検出用の第2の駆動方法をセットで動作する説明を行っている。しかしながら、これに限られるものではなく、位相差検出が不要な場合は第1の駆動方法のみを繰り返し行うことが可能である。また、一方で画像信号が不要で位相差検出のみを行う必要がある場合には、第2の駆動方法のみを繰り返すよう動作させることも容易に実現可能である（A F 専用の読み出しを行う場合）。40

#### 【0114】

各読み出しモードごとの垂直走査回路における転送スイッチの制御を、行ごとに A + B 画素を読み出すのか、A 画素のみを読み出すのか、B 画素のみ読み出すのかを排他的にいずれか一つを選択可能とする。

#### 【0115】

さらにはここまで実施形態では、行ごとに A 画素のみ、B 画素のみに出力するものとして説明してきたが、これに限定されるものではなく、対象行の画素ごとに A 画素、B 画素を切り替えることも可能である。これは撮像素子の転送信号と、画素毎の転送スイッチの接続関係で決めることができる。

#### 【0116】

10

20

30

40

50

ここまで実施形態では、図5で説明したように第n行におけるTXA\_nはすべての画素においてA画素(501)用の転送トランジスタ507に接続され、TXB\_nはすべての画素においてB画素(502)用の転送スイッチ508に接続されている。

### 【0117】

この接続関係を同一行の中において入れ替えることで、任意の画素毎にA画素、B画素を切り替えることが可能となる。

この様子を図14に示す。図14において撮像素子101の第n行と第n+1行を模式的に示している。第n行および第n+1行とも、PTXAのみ有効とする動作モードを仮定する。従来であれば第n行、n+1行ともA画素出力が選択され出力されるケースであるが、図14に示すように画素毎にPTXA、PTXBと、各画素の転送トランジスタとの配線を切り替える。これにより、PTXAが有効の場合にA画素用の転送トランジスタのゲート端子に接続されればA画素出力が転送されるし、B画素用の転送トランジスタに接続されれば、B画素出力が転送される。もちろんPTXAとPTXBが同時に有効になる場合には、従来と変わらずA+Bの合成結果が得られることに変わりがない。

### 【0118】

このように画素毎の配線切り替えを実施することで、AFの要求仕様に対してさらに自由度の高い画素の選択が可能となる。

### 【符号の説明】

### 【0119】

101：撮像素子、103：DSP、104：タイミング発生回路、105：CPU、

113：モードダイアル、501、502：光電変換部、601：マイクロレンズ、1001：現像部、1002：圧縮部、1006：AF部、1008：画像補正部、1009：AF用補正部、CTkS：信号成分保持容量、CTkN：ノイズ成分保持容量

【図1】

【図2】

【図3】

103

【図4】

【図5】

【図7】

【図6】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 木谷 一成

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 松永 隆志

(56)参考文献 特開2012-191401(JP,A)

特開2001-124984(JP,A)

特開2013-235053(JP,A)

国際公開第2014/006784(WO,A1)

(58)調査した分野(Int.Cl., DB名)

H04N 5/225-5/378

H04N 9/00-9/11