(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6028018号

(P6028018)

(45) 発行日 平成28年11月16日(2016.11.16)

(24) 登録日 平成28年10月21日(2016.10.21)

|                          |                    |

|--------------------------|--------------------|

| (51) Int.Cl.             | F 1                |

| HO 1 L 21/8246 (2006.01) | HO 1 L 27/10 4 4 7 |

| HO 1 L 27/105 (2006.01)  | HO 1 L 29/82 Z     |

| HO 1 L 29/82 (2006.01)   | HO 1 L 43/08 Z     |

| HO 1 L 43/08 (2006.01)   | HO 1 L 43/08 M     |

| HO 1 L 43/10 (2006.01)   |                    |

請求項の数 10 (全 19 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-510243 (P2014-510243)  |

| (86) (22) 出願日 | 平成24年4月30日 (2012.4.30)        |

| (65) 公表番号     | 特表2014-517516 (P2014-517516A) |

| (43) 公表日      | 平成26年7月17日 (2014.7.17)        |

| (86) 國際出願番号   | PCT/KR2012/003345             |

| (87) 國際公開番号   | W02012/153926                 |

| (87) 國際公開日    | 平成24年11月15日 (2012.11.15)      |

| 審査請求日         | 平成27年1月16日 (2015.1.16)        |

| (31) 優先権主張番号  | 10-2011-0044587               |

| (32) 優先日      | 平成23年5月12日 (2011.5.12)        |

| (33) 優先権主張国   | 韓国 (KR)                       |

|           |                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 503447036<br>サムスン エレクトロニクス カンパニー<br>リミテッド<br>大韓民国・4 4 3 - 7 4 2 ・キョンギード<br>・スウォンーシ・ヨントンク・サムスン<br>一口・1 2 9 |

| (74) 代理人  | 100110364<br>弁理士 実広 信哉                                                                                    |

| (72) 発明者  | キュンジン・イ<br>大韓民国・1 3 6 - 7 8 0 ・ソウル・ソン<br>ブクグ・ジョンガム・1-ドン・(番地<br>なし) ・サムスン・レミアン・アパート・<br>1 0 4 - 1 3 0 1    |

最終頁に続く

(54) 【発明の名称】磁気共鳴歳差現象と2重スピンドル効果を利用したスピン伝達トルク磁気メモリ素子

## (57) 【特許請求の範囲】

## 【請求項 1】

第1固定磁性層、第1自由磁性層、及び第2自由磁性層を含む磁気メモリ素子であって、

前記第1固定磁性層は固定磁化方向を有し、膜面に対して垂直方向に磁化される物質から形成された薄膜であり、

前記第1自由磁性層は外部から印加される電流によって磁化方向が変わり、膜面に対して垂直方向に磁化される物質から形成された薄膜であり、

前記第2自由磁性層は外部から印加される電流によって磁化方向が変わり、膜面に対して水平方向に磁化される物質から形成された薄膜であり、

前記第1固定磁性層と第1自由磁性層との間及び第1自由磁性層と第2自由磁性層との間に各々第1非磁性層及び第2非磁性層を含み、

前記第1非磁性層及び前記第2非磁性層の電気伝導度は、前記第1固定磁性層、前記第1自由磁性層及び前記第2自由磁性層の電気伝導度と異なることを特徴とする磁気メモリ素子。

## 【請求項 2】

前記磁気メモリ素子は第2固定磁性層をさらに含み、前記第2自由磁性層と第2固定磁性層との間に第3非磁性層をさらに含み、

前記第2固定磁性層は前記第1固定磁性層と反対になる固定磁化方向を有し、膜面に対して垂直方向に磁化される物質から形成された薄膜であることを特徴とする請求項1に記

10

20

載の磁気メモリ素子。

**【請求項 3】**

前記水平方向に磁化される物質の飽和磁化値は300 - 2000 kA/mであることを特徴とする請求項1に記載の磁気メモリ素子。

**【請求項 4】**

前記第1固定磁性層及び第2固定磁性層全て又はこの中でいずれか1つは反強磁性層、第1磁性層、非磁性層、及び第2磁性層から形成された交換バイアスされた反磁性体構造素子であって、

前記反強磁性層はIr、Pt、Mn、及びこれらの混合物の中から選択された物質から形成され、前記第1磁性層及び第2磁性層は各々独立的にFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質から形成されたことを特徴とする請求項2に記載の磁気メモリ素子。10

**【請求項 5】**

前記第1磁性層及び第2磁性層の中の少なくとも1つ以上はX層及びY層から形成された2重層がn個積層されて形成された多層薄膜(n>1)であり、前記X層及びY層は各々独立的にFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質から形成されたことを特徴とする請求項4に記載の磁気メモリ素子。

**【請求項 6】**

前記第1自由磁性層はFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質から形成されたことを特徴とする請求項1に記載の磁気メモリ素子。20

**【請求項 7】**

前記第1自由磁性層はFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択される物質から形成された層と、X層及びY層から形成された2重層がn個積層されて形成された層(n>1)と、から形成された多層薄膜であり、前記X層及びY層は各々独立的にFe、Co、Ni、B、Si、Zr、Pt、及びPdの中から選択された物質から形成されたことを特徴とする請求項1に記載の磁気メモリ素子。

**【請求項 8】**

前記第1非磁性層、第2非磁性層、及び第3非磁性層は互いに異なる物質から形成され、各々独立的にRu、Cu、Al、Ta、Au、Ag、Al<sub>2</sub>O<sub>3</sub>、MgO、Ta<sub>2</sub>O<sub>5</sub>、ZrO<sub>3</sub>、及びこれらの混合物の中から選択された物質から形成されることを特徴とする請求項2に記載の磁気メモリ素子。30

**【請求項 9】**

前記第1非磁性層、第2非磁性層、及び第3非磁性層は前記第1固定磁性層、第1自由磁性層、第2自由磁性層、及び第2固定磁性層より電気伝導度が高いことを特徴とする請求項2に記載の磁気メモリ素子。

**【請求項 10】**

前記第1非磁性層、第2非磁性層、及び第3非磁性層は前記第1固定磁性層、第1自由磁性層、第2自由磁性層、及び第2固定磁性層より電気伝導度が低いことを特徴とする請求項2に記載の磁気メモリ素子。40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は磁気メモリ素子に関し、より詳細には垂直異方性を有する自由層に水平異方性を有する自由磁性層を挿入して、電流注入の時に素子自体的に交流磁気場を誘導させて、臨界電流密度を低くすることができ、磁化の方向が互いに反対である2つの固定磁性層を含んで固定磁性層から発生する漏洩磁気場による素子の特性が劣化されないスピンドルク磁気メモリ素子に関する。

**【背景技術】**

**【0002】**

50

強磁性体とは、外部から強い磁気場を印加されなくとも自発的に磁化なる物質を言う。2つの強磁性体の間に非磁性体を挿入したスピンバルブ構造（第1磁性体／非磁性体／第2磁性体）で2つの磁性層の相対的な磁化方向に沿って電気抵抗が異なるになる巨大な磁気抵抗効果が発生し、これはスピンバルブ構造でアップスピンドウンスピンドとが感じる電気抵抗が異なるので、発生する。このような巨大な磁気抵抗効果はハードディスクに記録された情報を読み出すためのセンサーの核心技術として広く利用されている。

#### 【0003】

巨大な磁気抵抗効果は2つの磁性層の相対的な磁化方向が電流の流れを制御する現象を記述する反面、ニュートンの第3法則である作用・反作用の法則にしたがって印加された電流を利用して磁性層の磁化方向を制御することもやはり可能である。スピンバルブ構造に電流を印加して、第1磁性体（固定磁性層）によってスピン分極された電流が第2磁性体（自由磁性層）を通過しながら、自分のスピン角運動量を伝達するようになり、これをスピン伝達トルク（Spin-transfer-torque）と称する。スピン伝達トルクを利用して自由磁性層の磁化を反転させるか、或いは持続的に回転させる素子がIBM社から提案され、以後実験的に糾明された。特に、スピン伝達トルク現象を利用する磁気メモリ素子はDRAM（dynamics random access memory）を代替する新しいメモリ素子として脚光を浴びている。

#### 【0004】

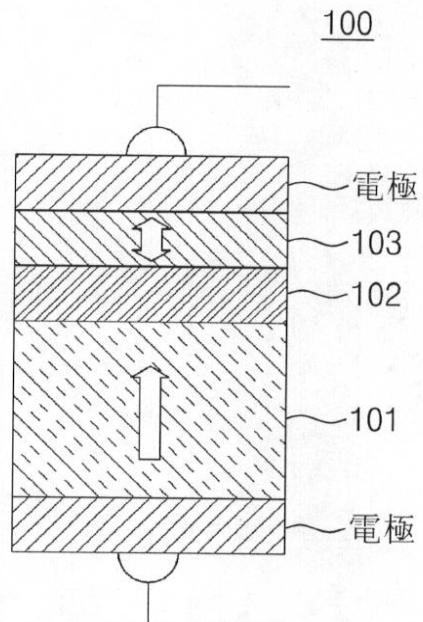

基本的な磁気メモリ素子は前記記述したようにスピンバルブ構造を有する。即ち、下記の図1のように従来の磁気メモリ素子100は下部電極／第1磁性体（固定磁性層）101／非磁性体102／電流によって磁化の方向が変わる第2磁性体（自由磁性層）103／上部電極の構造を有する。外部から印加される電流又は磁気場によって第2磁性体の磁化反転が誘導され、前記記述したように巨大な磁気抵抗効果によって高い抵抗と低い抵抗とが現われる。これを“0”又は“1”的情報として記録する磁気メモリ素子に応用が可能である。

#### 【0005】

自由層の磁化を制御するために外部磁気場を利用する場合、素子の大きさが小さくなるほど、半選択セル（half-selected cell）の問題が発生して素子の高集積化に制約を伴う。反面、素子に電圧を印加して発生するスピン伝達トルクを利用する場合には、素子の大きさに関わらず、選択的なセルの磁化反転が容易である。前記記述したスピン伝達トルクの物理的な器具にしたがえば、自由磁性層で発生するスピン伝達トルクの大きさは印加された電流密度（又は電圧）の量に比例し、自由磁性層の磁化反転のための臨界電流密度 $J_c$ は下記の[式1]の通りである。

#### 【0006】

##### 【数1】

[式1]

$$J_c = \frac{2e\alpha M_s d}{\hbar\eta} (H_{K,\text{eff}})$$

前記[式1]で、 $\alpha$ はギルバート（Gilbert）減衰常数であり、 $\hbar (= 1.05 \times 10^{-34} \text{ J} \cdot \text{s})$ はPlanck常数を $2\pi$ で分けた値であり、 $e (= 1.6 \times 10^{-19} \text{ C})$ は電子の電荷量、 $\eta$ は物質及び素子の構造によって決定されるスピン分極効率常数、 $M_s$ は自由磁性層の飽和磁化量、 $d$ は自由磁性層の厚さ、 $H_{K,e_f}$ は膜の垂直方向の有効異方性磁界として $H_{K,e_f} = H_{K\perp} - 4\pi M_s$ で定義される。

#### 【0007】

素子の高集積化のためにセルの大きさを小さくすれば、常温での熱エネルギーによって記録された磁化方向が任意的に変わる現象が発生する。これは越常磁性限界として、記録

10

20

30

40

50

された磁気情報が望まないよう消える問題を生じる。熱エネルギーを克服して平均的に磁化方向が維持される時間( )は下記の[数式2]の通りである。

## 【0008】

## 【数2】

## [数式2]

$$\tau = \tau_0 \exp\left(\frac{K_{eff}V}{k_B T}\right) = \tau_0 \exp\left(\frac{H_{K,eff} M_S V}{2k_B T}\right)$$

10

## 【0009】

前記[数式2]で、 $\tau_0$ は試験周波数の逆数に1ns程度であり、 $K_{eff}$ は自由磁性層の有効磁気異方性エネルギー密度( $= H_{K,eff} M_S / 2$ )、Vは素子の体積、 $k_B$ はボルツマン常数( $= 1.381 \times 10^{-16}$  erg/K)、Tはケルビン温度である。

## 【0010】

ここで、 $K_{eff}V / k_B T$ を磁気メモリ素子の熱的安定性ファクタ( )として定義する。磁気メモリ素子が不揮発性特性を維持するためには一般的に  $> 50$  の条件が満足されなければならない。セルの大きさの減少にしたがって自由層の体積(V)が減少すれば、 $> 50$  を満足させるために、 $K_{eff}$ を増加させなければならない。その結果、前記[数式1]にしたがって $J_c$ が増加するようになる。

20

## 【0011】

このように、磁気メモリ素子のと $J_c$ とが全て $K_{eff}$ に比例するので、素子を商用化するためには十分に高いと十分に低い $J_c$ を満足させなければならない。のみならず、一般的にCMOS(Complementary metal-oxide-semiconductor)トランジスター素子で提供できる電流の量は制限されるので、自由磁性層の磁化反転のための低い臨界電流密度が要求され、素子駆動に必要である消費電力を低減側面で臨界電流密度を低くすることは必須要素である。

## 【0012】

即ち、メモリ素子の大きさを減少しながら、高集積化を具現するためには自由層の磁化反転臨界電流密度を低くしなければならなく、自由層の磁化反転臨界電流密度を低くして、記録の時に使用される電力が低減効果まで発揮することができなければならない。

30

## 【0013】

前記記述したように磁気メモリ素子の臨界電流密度は有効磁気異方性磁界( $H_{K,eff}$ )に比例するので、素子の臨界電流密度を低くするためには有効磁気異方性磁界( $H_{K,eff}$ )を効果的に減少しなければならなく、このような方案としてハードディスクドライブの記録ヘッドから発生する磁気場に加えて高周波変調磁気場を同時に印加して記録磁気場の大きさを低減させる方案が提案されたが、これは印加された交流磁気場の周波数が記録媒体磁化の共振周波数に近接して元来に $H_{K,eff}$ より低い磁気場で磁化反転が生じる原理を利用することであって、電流駆動形磁気メモリ素子に同一の原理を適用して臨界電流密度を低くする方案が実験的に検証された。しかし、このような原理及び構造は変調磁気場を誘導するための追加的な素子が必ず必要とし、全体に素子の観点で見れば、駆動電力の減少効果は、微々たるものと判明された。

40

## 【0014】

また、下記の図1に記述された従来の技術は第1磁性体から発生する漏洩磁気場(stay field)によって第2磁性体が第2磁性体の磁化方向に沿って変わるようになる。より具体的に第1磁性体の磁化方向が膜の厚さ方向である+ $z$ 軸の場合、漏洩磁気場の方向も+ $z$ 軸になる。このような条件下では漏洩磁気場の影響に因って第2磁性体の磁化方向が- $z$ 軸である場合のが+ $z$ 軸である場合のに比べて小さくなる。磁気メモリ素子は第2磁性体の方向が+ $z$ 及び- $z$ 方向を全て有することができる所以、磁化の熱的安定性は2つの場合の中でより小さいによって決定される。したがって、第1磁性体

50

から発生する漏洩磁気場によって素子の特性が劣化される問題点がある。

**【0015】**

また、磁性層の飽和磁化値が  $650 \text{ emu/cm}^3$  以上であれば、該当磁性層が周囲の磁性層に及ぶ影響が大きくなつて素子の特性上の問題を起こす可能性が高くなる短所がある。

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0016】**

したがつて、本発明が解決しようとする課題はスピン伝達トルクを利用する磁気メモリ素子において、素子の高集積化具現を可能するようするために、より低い臨界電流密度を有し、固定磁性層から発生する漏洩磁気場による素子特性の劣化がない磁気メモリ素子を提供することである。

**【課題を解決するための手段】**

**【0017】**

本発明は前記課題を達成するために、

第1固定磁性層、第1自由磁性層、及び第2自由磁性層を含む磁気メモリ素子であつて

、前記第1固定磁性層は固定磁化方向を有し、膜面に対して垂直方向に磁化される物質から形成された薄膜であり、

前記第1自由磁性層は外部から印加される電流によって磁化方向が変わり、膜面に対して垂直方向に磁化される物質から形成された薄膜であり、

前記第2自由磁性層は外部から印加される電流によって磁化方向が変わり、膜面に対して水平方向に磁化される物質から形成された薄膜であり、

前記第1固定磁性層と第1自由磁性層との間及び第1自由磁性層と第2自由磁性層との間には各々第1非磁性層及び第2非磁性層を含むことを特徴とする磁気メモリ素子を提供する。

**【0018】**

本発明の一実施形態によれば、前記磁気メモリ素子は第2固定磁性層をさらに包含でき、これによって前記第2自由磁性層と第2固定磁性層との間には第3非磁性層をさらに包含でき、前記第2固定磁性層は前記第1固定磁性層と反対になる固定磁化方向を有し、膜面に対して垂直方向に磁化される物質から形成された薄膜であり得る。

**【0019】**

また、前記第2自由磁性層をなす水平方向に磁化される物質の飽和磁化値は  $300 - 2000 \text{ kA/m}$  であり得る。

**【0020】**

本発明の一実施形態によれば、前記第1固定磁性層及び第2固定磁性層は各々独立的に Fe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質からなり得る。

**【0021】**

また、前記第1固定磁性層及び第2固定磁性層は X 層及び Y 層から形成された 2 重層が  $n$  個積層されて形成された多層薄膜 ( $n > 1$ ) であり、前記 X 層及び Y 層は各々独立的に Fe、Co、Ni、B、Si、Nb、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質からなり得る。

**【0022】**

本発明の一実施形態によれば、前記第1固定磁性層及び第2固定磁性層の全て又はこの中のいずれか 1 つは第1磁性層、非磁性層、及び第2磁性層から形成された反磁性体構造であり得、前記第1磁性層及び第2磁性層は各々独立的に Fe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質からなり得る。

**【0023】**

本発明の一実施形態によれば、前記第1磁性層及び第2磁性層の中の少なくとも 1 つ以

10

20

30

40

50

上はX層及びY層から形成された2重層がn個積層されて形成された多層薄膜(n=1)であり、前記X層及びY層は各々独立的にFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質からなり得る。

#### 【0024】

本発明の一実施形態によれば、前記第1固定磁性層及び第2固定磁性層の全て又はこの中のいずれか1つは反強磁性層、第1磁性層、非磁性層、及び第2磁性層から形成された交換バイアスされた反磁性体構造であり得、前記反強磁性層はIr、Pt、Mn、及びこれらの混合物の中から選択された物質から形成され、前記第1磁性層及び第2磁性層は各々独立的にFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質からなり得る。 10

#### 【0025】

本発明の一実施形態によれば、前記第1磁性層及び第2磁性層の中の少なくとも1つ以上はX層及びY層から形成された2重層がn個積層されて形成された多層薄膜(n=1)であり、前記X層及びY層は各々独立的にFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質からなり得る。

#### 【0026】

このように本発明の一実施形態によれば、前記第1固定磁性層及び第2固定磁性層は互いに異なる物質から形成され得、互いに異なる多層薄膜構造であり得る。

#### 【0027】

本発明の一実施形態によれば、前記第1自由磁性層はFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択された物質からなり得る。 20

#### 【0028】

本発明の他の一実施形態によれば、前記第1自由磁性層はFe、Co、Ni、B、Si、Zr、Pt、Pd、及びこれらの混合物の中から選択される物質から形成された層と、X層及びY層から形成された2重層がn個積層されて形成された層(n=1)と、から形成された多層薄膜であり得、前記X層及びY層は各々独立的にFe、Co、Ni、B、Si、Zr、Pt、及びPdの中から選択された物質からなり得る。

#### 【0029】

本発明の他の一実施形態によれば、前記第2自由磁性層はFe、Co、Ni、B、Si、Zr、及びこれらの混合物の中から選択された物質からなり得る。 30

#### 【0030】

本発明の他の一実施形態によれば、前記第1非磁性層、第2非磁性層、及び第3非磁性層は互いに異なる物質から形成され、各々独立的にRu、Cu、Al、Ta、Au、Ag、Al<sub>x</sub>O<sub>y</sub>、MgO、Ta<sub>x</sub>O<sub>y</sub>、Zr<sub>x</sub>O<sub>y</sub>、及びこれらの混合物の中から選択された物質からなり得る。

#### 【0031】

本発明の他の一実施形態によれば、前記第1非磁性層、第2非磁性層、及び第3非磁性層は前記第1固定磁性層、第1自由磁性層、第2自由磁性層、及び第2固定磁性層より電気伝導度が高いか、又は低いことがあり得る。

#### 【0032】

本発明の他の一実施形態によれば、前記磁気メモリ素子は素子に電流を供給する上部電極と下部電極とをさらに包含することができる。 40

#### 【発明の効果】

#### 【0033】

本発明による新しい構造の磁気メモリ素子は一定な飽和磁化値を有する水平方向可変磁化層である自由磁性層をさらに包含して、従来の磁気メモリ素子に比べてスイッチング電流が顕著に減少して素子の高集積化具現が可能であり、磁化反転に必要である臨界電流密度を低くして素子の消費電力を低減させることができる。また、固定磁性層から発生する漏洩磁気場効果を低減して記録された磁化情報が熱的に安定性を有する。

#### 【図面の簡単な説明】

## 【0034】

【図1】従来のスピン伝達トルクを利用する磁気メモリ素子の構造を示した断面図である。

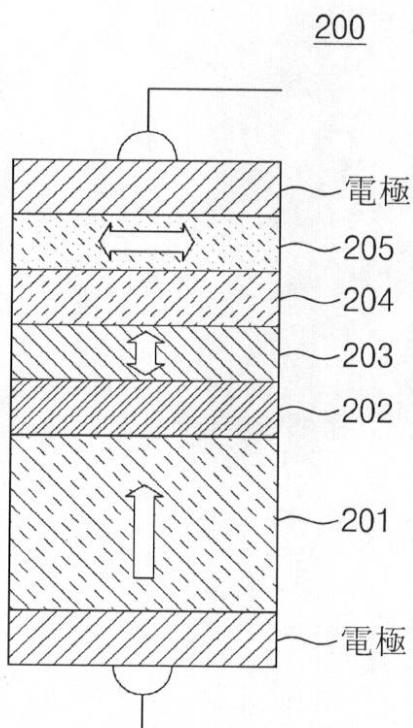

【図2】本発明の一実施形態によるスピン伝達トルクを利用する磁気メモリ素子の構造を示した断面図である。

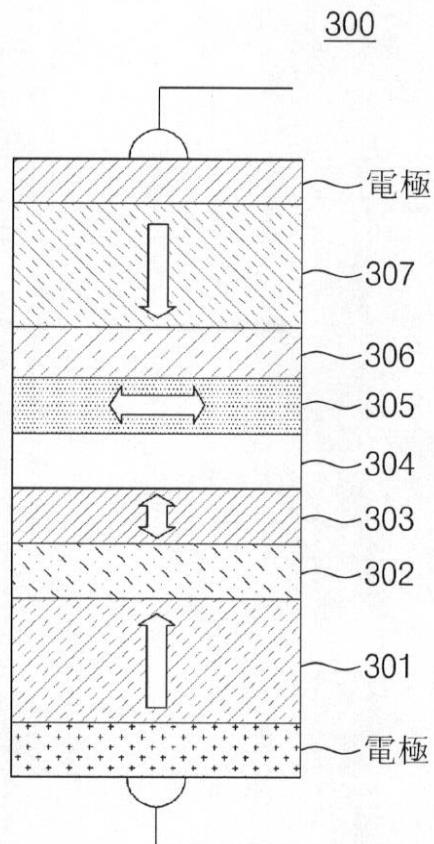

【図3】本発明の他の一実施形態によるスピン伝達トルクを利用する磁気メモリ素子の構造を示した断面図である。

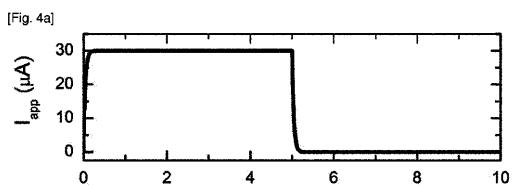

【図4A】図2にしたがう素子に対して時間にしたがう印加された電流を示したグラフである。

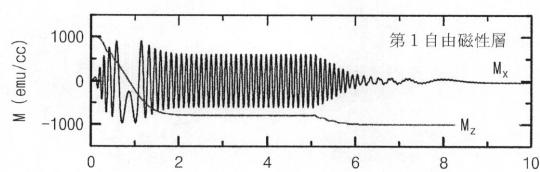

【図4B】図2にしたがう素子に対して第1自由磁性層の時間にしたがう磁化挙動を示したグラフである。 10

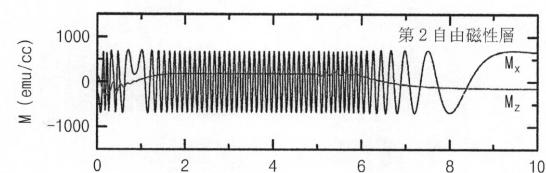

【図4C】図2にしたがう素子に対して第2自由磁性層の時間にしたがう磁化挙動を示したグラフである。

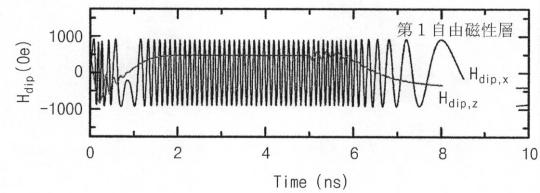

【図4D】図2にしたがう素子に対して第2自由磁性層の歳差運動にしたがって第1自由磁性層に発生する交流磁気場を示したグラフである。

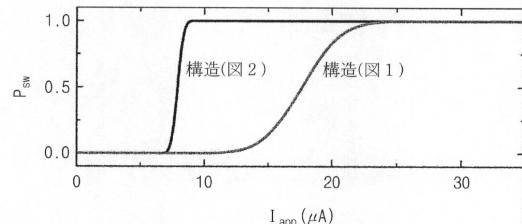

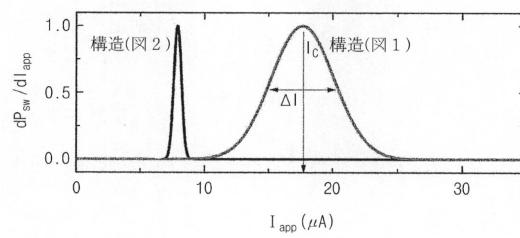

【図5A】図1の構造と図2の構造とに対して印加された電流に対するスイッチング確率を示したグラフである。

【図5B】図1の構造と図2の構造とに対して印加された電流に対してスイッチング確率を電流に微分した値を示したグラフである。

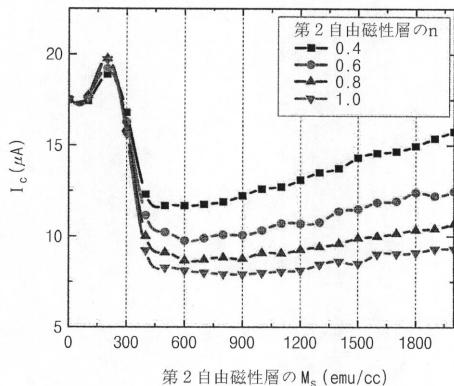

【図6】図2にしたがう素子に対して第2自由磁性層の飽和磁化値及びスピン分極効率に対する磁気メモリ素子のスイッチング電流を示したグラフである。 20

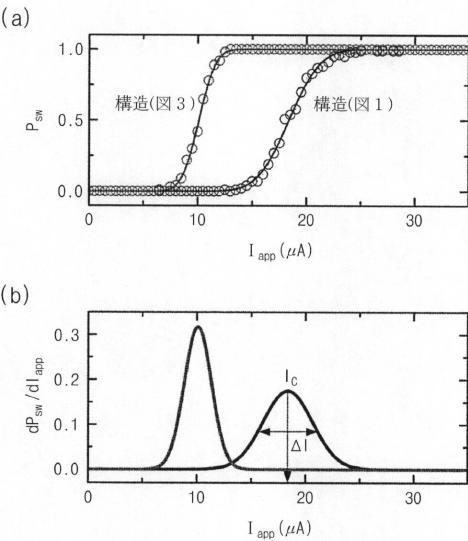

【図7】(a)は図1の構造と図3の構造とに対して印加された電流に対するスイッチング確率を示したグラフであり、(b)は図1の構造と図3の構造とに対して印加された電流に対するスイッチング確率を電流に微分した値を示したグラフである。

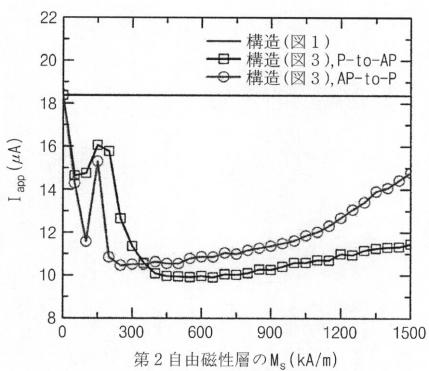

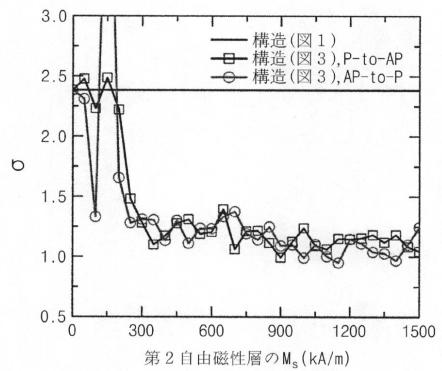

【図8A】図1構造の磁気メモリ素子のスイッチング電流密度と図3構造の磁気メモリ素子に対して第2自由磁性層の飽和磁化値に対するスイッチング電流を示したグラフである。

【図8B】図1構造の磁気メモリ素子のスイッチング電流密度分布図と図3構造の磁気メモリ素子に対して第2自由磁性層の飽和磁化値に対するスイッチング電流密度分布図と示したグラフである。 30

## 【発明を実施するための形態】

## 【0035】

以下、本発明を詳細に説明する。

## 【0036】

本発明は磁気メモリ素子において、熱的安定性を維持しながら、素子の臨界電流密度を低くして素子の大きさを減らして高集積化具現が可能であり、記録の時の使用電力消耗を減少させたことを特徴とする。また、固定磁性層から発生する漏洩磁気場による素子の特性が劣化されないことを特徴とする。本発明はこれのために素子自体的に交流磁気場を誘導し、これを制御するための新しい構造の磁気メモリ素子を提供する。

## 【0037】

本発明の望ましい一具現例にしたがう磁気メモリ素子200は固定磁性層201、第1非磁性層202、第1自由磁性層203、第2非磁性層204、及び第2自由磁性層205を含み、前記固定磁性層は固定磁化方向を有し、膜面に対して垂直方向に磁化される物質から形成された薄膜であり、前記第1自由磁性層は外部から印加される電流によって磁化方向が変わり、膜面に対して垂直方向に磁化される物質から形成された薄膜であり、前記第2自由磁性層は外部から印加される電流によって磁化方向が変わり、膜面に対して水平方向に磁化される物質から形成された薄膜であることを特徴とする。 40

## 【0038】

即ち、垂直異方性を有する第1自由磁性層203に水平異方性を有する第2自由磁性層205を追加的に挿入して、電流を印加の時にスピン伝達トルクの効果によって第2自由

磁性層磁化が回転運動をするようにされ、直流電流を印加して面内磁化を有する自由層が高い周波数に回転するようにされ、その結果、高い周波数を有する交流磁気場が自体的に発生するようにされて素子の臨界電流密度を効果的に低くすることができる。

#### 【0039】

また、本発明の望ましい他の具現例にしたがう磁気メモリ素子300は第1固定磁性層301、第1非磁性層302、第1自由磁性層303、第2非磁性層304、第2自由磁性層305、第3非磁性層306、及び第2固定磁性層307を含み、前記第1及び第2固定磁性層は互いに反対である固定磁化方向を有し、膜面に対して垂直方向に磁化される物質から形成された薄膜であり、前記第1自由磁性層は外部から印加される電流によって磁化方向が変わり、膜面に対して垂直方向に磁化される物質から形成された薄膜であり、前記第2自由磁性層は外部から印加される電流によって磁化方向が変わり、膜面に対して水平方向に磁化される物質から形成された薄膜であることを特徴とする。10

#### 【0040】

即ち、垂直異方性を有する第1自由磁性層303に水平異方性を有する第2自由磁性層305を追加に挿入して、電流印加の時に発生するスピンドルトルク効果を通じて第2自由磁性層が歳差運動をし、これを通じて発生する高周波交流磁気場が素子の臨界電流密度を低くすることができる。

#### 【0041】

また、第2自由磁性層の歳差運動による交流磁気場は外部から印加した電流と第2自由磁性層の有効磁気場とによって決定される。特に、第2固定磁性層を挿入することによって第2自由磁性層の膜面に垂直方向に誘導磁気場を発生させ得る。したがって、第2固定自由層の構造及び物性値にしたがって第2自由磁性層の歳差運動を調節することができる。即ち、外部電流のみならず、素子の構造及び物性値に素子内に発生する交流磁気場を調節することができる。20

#### 【0042】

また、第1固定磁性層の磁化方向と第2固定磁性層の磁化方向とを調節して第1自由磁性層に印加される漏洩磁気場を従来の素子に比べて減らすことができる。これを通じて素子に記録された磁化情報の熱的安定性を改善することができる。

#### 【0043】

下記の図2は本発明の一具現例にしたがうスピンドルトルク磁気メモリ素子200の構造を示す断面図であって、本発明による素子は基本的に下部電極、垂直方向の磁化を有する固定磁性層201、第1非磁性層202、垂直異方性を有し、電流によって磁化の方向が変わる第1自由磁性層203、第2非磁性層204、水平磁化を有し、電流によって磁化の方向が変わる第2自由磁性層205及び上部電極を含む構造を有する。30

#### 【0044】

第1自由磁性層203は一般的に磁化を垂直に立てようとする垂直結晶異方性磁界( $H_K = 2K / M_S$ )が磁化を水平に横たえようとする形状異方性磁界( $H_d = 4M_S$ )に比べて著しく大きいので、磁化の方向が薄膜の垂直方向に安定化される。(即ち、 $H_K - H_d = H_K - 4M_S > 0$ )。40

#### 【0045】

第2自由磁性層205は形状異方性磁界が磁気異方性磁界に比べて著しく大きいので、磁化の方向が薄膜の面内で安定化される。したがって、第1自由磁性層203と第2自由磁性層205との磁化は電流を印加しない状態でも大きい角度を維持するようになる。

#### 【0046】

磁化スイッチングのために電流が印加されれば、第1自由磁性層203は固定磁性層201によってスピンドルトルクが印加され、第1自由磁性層203は垂直方向に回転する。また、第1自由磁性層203と第2自由磁性層205とは第2非磁性層204を介しているので、第2自由磁性層205は第1自由磁性層203によってスピンドルトルクが印加され、第2自由磁性層205の磁化は垂直方向に近いスピンドルトルクを受ける。即ち、磁気メモリ素子に電圧が印加されれば、第2自由磁性層205の磁化は垂直方向に近いスピンドルトルクを受けることになって、高速回転するようにな50

なる。

#### 【0047】

したがって、高速回転する第2自由磁性層205は素子に変調磁気場を提供して、第1自由磁性層203の臨界電流密度を効果的に低くする効果を得られる。素子の全体抵抗が低ければ、同一の印加電圧でより多い量の電流が流すようになって、磁化反転に必要である電力を減少させ得る。第1非磁性層202と第2非磁性層204とは電気伝導度が顕著に高い金属を使用することができる。

#### 【0048】

下記の図3は本発明の他の具現例にしたがうスピン伝達トルク磁気メモリ素子300の構造を示す断面図であって、本発明による素子は基本的に下部電極、垂直方向の磁化を有する第1固定磁性層301、第1非磁性層302、垂直異方性を有し、電流によって磁化の方向が変わる第1自由磁性層303、第2非磁性層304、水平異方性を有し、電流によって磁化の方向が変わる第2自由磁性層305、第3非磁性層306、垂直方向の磁化を有する第2固定磁性層307、及び上部電極を包含する構造を有する。

10

#### 【0049】

第1自由磁性層303は磁化を垂直に立てようとする垂直結晶異方性磁界( $H_K = 2_{K} / M_S$ )が磁化を水平に横たえようとする形状異方性磁界( $H_d = 4 M_S$ )に比べて著しく大きいので、磁化の方向が膜面に対して垂直方向に安定化される。(即ち、 $H_{K_{eff}} = H_K - H_d = H_K - 4 M_S > 0$ )。反面、第2自由磁性層305は形状異方性磁界によって薄膜の面内で安定化され、その結果外部磁気場又は電流を印加されなくとも2つの自由磁性層は大きい角度を維持するようになる。

20

#### 【0050】

磁化反転のために電流が印加されれば、第1自由磁性層303は第1固定磁性層301によってスピン分極された電流からスピン伝達トルクを受けることになり、第1自由磁性層303と第2自由磁性層305とは第2非磁性層304を介しているので、第2自由磁性層305は第1自由磁性層303によってスピン分極された電流からスpin伝達トルクを受ける。したがって、磁気メモリ素子に電圧が印加されれば、第2自由磁性層305の磁化は垂直方向に近い成分のスピン伝達トルクを受けるようになり、その結果、磁化が高速回転するようになる。

#### 【0051】

また、第2自由磁性層305と第2固定磁性層307とは第3非磁性層306を介しているので、第2固定磁性層307によってスpin分極された電流からスpin伝達トルク及び誘導磁気場を受けるようになり、これらは印加された電流の方向によって互いに平行又は反並行であり、膜面の垂直方向に作用する。したがって、前記記述した高周波交流磁気場の周波数及び大きさに影響を及ぶ。

30

#### 【0052】

したがって、高速回転する第2自由磁性層305は素子に変調磁気場を提供して、第1自由磁性層303の臨界電流密度を効果的に減少させる効果を提供し、第2固定磁性層を通じて印加された電流及び誘導磁気場を利用して変調磁気場を効果的に調節することができる。また、第1固定磁性層の磁化方向と第2固定磁性層の相対的な磁化方向を調節して第1自由磁性層に印加される漏洩磁気場を従来の素子に比べて減らすことができる。これを通じて素子に記録された磁化情報の熱的安定性を改善することができる。

40

#### 【0053】

第1非磁性層202、302、第2非磁性層204、304、及び第3非磁性層306は電気伝導度が顕著に高い金属を使用することができる。のみならず、電気伝導度が顕著に低い物質を使用することができるが、これは同一の電圧下で電流は減少するが、電子のトンネルリング効果によって磁化回転にしたがう磁気抵抗の差異が非常に大きくなるので、高い磁気抵抗比を得られる。したがって、第1非磁性層202、第2非磁性層204、及び第3非磁性層306の中の少なくとも1つ又は前記3つの非磁性層全てに電気伝導度が顕著に低い物質を使用することができる。

50

## 【0054】

本発明による磁気メモリ素子では高い電流密度を得るために、パターニング技術を利用してできる限り、小さい大きさの構造を具現しなければならない。この時、面内磁気形状異方性がいずれかの方向でも同一であって、第1自由磁性層203、303、及び第2自由磁性層205、305の磁化の高速回転が容易にするように素子の断面が可能であるだけ円に近いことが望ましい。

## 【0055】

以下、望ましい実施例をあげて本発明をさらに詳細に説明する。しかし、これらの実施形態は本発明をより具体的に説明するためのものであり、実験条件、物質種類等によって本発明が制限されるか、或いは限定されないことは当業界の通常の知識を有する者に自明なことである。

10

## 【0056】

## &lt;実施例&gt;

本発明による磁気メモリ素子の効果を磁化の運動方程式を利用する微小磁気モデリングを通じて確認した。このような方式は既存のコンピューターハードディスク開発及びスピニ伝達トルク研究を通じて正当性が十分に確保された。

## 【0057】

磁化の運動方程式は下記の〔数式3〕の通りである。

## 【0058】

## 〔数式3〕

20

[数式3]

$$\frac{\partial \mathbf{m}_1}{\partial t} = -\gamma(\mathbf{m}_1 \times \mathbf{H}_2^{\text{eff}}) + \alpha \mathbf{m}_1 \times \frac{\partial \mathbf{m}_1}{\partial t} - \frac{\hbar \eta_1 j_e}{2eM_{s1}d_1} \mathbf{m}_1 \times (\mathbf{m}_1 \times \mathbf{p}_1) + \frac{\hbar \eta_2 j_e}{2eM_{s1}d_1} \mathbf{m}_1 \times (\mathbf{m}_1 \times \mathbf{m}_2)$$

$$\frac{\partial \mathbf{m}_2}{\partial t} = -\gamma(\mathbf{m}_2 \times \mathbf{H}_2^{\text{eff}}) + \alpha \mathbf{m}_2 \times \frac{\partial \mathbf{m}_2}{\partial t} - \frac{\hbar \eta_2 j_e}{2eM_{s2}d_2} \mathbf{m}_2 \times (\mathbf{m}_2 \times \mathbf{m}_1) + \frac{\hbar \eta_3 j_e}{2eM_{s2}d_2} \mathbf{m}_1 \times (\mathbf{m}_1 \times \mathbf{p}_2)$$

$$\mathbf{p}_1 = \hat{z}, \quad \mathbf{p}_2 = -\hat{z}$$

$\mathbf{m}_1$ と $\mathbf{m}_2$ とは各々第1自由磁性層203、303及び第2自由磁性層205、305の単位磁化ベクトル、 $\gamma$ は磁回転常数、 $\mathbf{H}_1^{\text{eff}}$ と $\mathbf{H}_2^{\text{eff}}$ は各々第1自由磁性層203、303及び第2自由磁性層205、305のすべての有効磁気場ベクトル、 $\alpha$ はGibert減衰常数であり、 $\hbar (= 1.05 \times 10^{-34} \text{ J} \cdot \text{s})$ はPlanck常数を $2\pi$ で分けた値であり、 $e (= 1.6 \times 10^{-19} \text{ C})$ は電子の電荷量、 $\eta_1$ 、 $\eta_2$ 及び $\eta_3$ は物質及び素子の全体構造によって決定される第1自由磁性層203、303及び第2自由磁性層205、305でのスピニ分極効率常数、 $j_e$ は印加電流密度、 $M_{s1}$ と $M_{s2}$ とは第1自由磁性層203、303及び第2自由磁性層205、305の飽和磁化値、 $d_1$ と $d_2$ とは各々第1自由磁性層203、303及び第2自由磁性層205、305の厚さを示す。 $\mathbf{P}_1$ は第1固定磁性層201、301から第1自由磁性層203、303に入射するスピニ分極電流のスピニ方向を示す単位ベクトルであり、 $\mathbf{P}_2$ は第2固定磁性層307から第2自由磁性層305に入射するスピニ分極電流のスピニ方向を示す単位ベクトルである。ここで、 $\mathbf{P}_1$ 及び $\mathbf{P}_2$ は膜の厚さ方向である $z$ -軸に平行な単位ベクトルである。

30

## 【0059】

実験例1. 本発明による素子に対して電流を印加することによって発生する第1自由磁性層及び第2自由磁性層磁化の時間にしたがう挙動

(1) 下記の図2のように本発明の一実施形態による磁気メモリ素子に対して電流を印加する場合、垂直異方性を有する第1自由磁性層及び水平異方性を有する第2自由磁性層の磁化挙動が開示される。

(2) 素子の構造と物性値とは次の通りである。

40

全体構造の断面積 = 3 1 4 n m<sup>2</sup>、

固定磁性層 2 0 1 / 第 1 非磁性層 2 0 2 / 第 1 自由磁性層 2 0 3：“厚さ ( t ) = 3 n m、垂直異方性常数 ( K<sub>1</sub> ) = 6 × 1 0<sup>6</sup> e r g / c m<sup>3</sup>、飽和磁化値 ( M<sub>s1</sub> ) = 1 0 0 0 e m u / c m<sup>3</sup>、G i l b e r t 減衰常数 ( γ<sub>1</sub> ) = 0 . 0 1、スピン分極効率常数 ( η<sub>1</sub> ) = 1 . 0 ”

第 2 非磁性層 2 0 4：厚さ t = 1 n m

第 2 自由磁性層 2 0 5：“厚さ ( t ) = 1 n m、垂直異方性常数 ( K<sub>2</sub> ) = 0 e r g / c m<sup>3</sup>、飽和磁化値 ( M<sub>s2</sub> ) = 7 0 0 e m u / c m<sup>3</sup>、G i l b e r t 減衰常数 ( γ<sub>2</sub> ) = 0 . 0 1、スピン分極効率常数 ( η<sub>2</sub> ) = 1 . 0 ”

( 3 ) 下記の図 4 A は時間にしたがう印加された電流を示したグラフである。磁化のスイッチング挙動を観察するために、rise time が 4 0 p s であり、幅が 5 n s である電流パルスを印加した。 10

#### 【 0 0 6 0 】

下記の図 4 B は時間にしたがう第 1 自由磁性層 2 0 3 の磁化挙動を示したグラフである。

。

#### 【 0 0 6 1 】

下記の図 4 B を参照すれば、膜面に水平方向である x - 成分は時間に対して振動をし、t = 1 n s 付近で、z - 成分が + 1 0 0 0 e m u / c m<sup>3</sup> で - 1 0 0 0 e m u / c m<sup>3</sup> に変わることを見ることができる。これは磁化成分が印加された電流によってスイッチングが行ったことを意味する。 20

#### 【 0 0 6 2 】

下記の図 4 C は時間にしたがう第 2 自由磁性層 2 0 5 の磁化挙動を示したグラフである。

。

#### 【 0 0 6 3 】

下記の図 4 C を参照すれば、第 2 自由磁性層 2 0 5 は、磁化の面内成分 ( = x 軸成分 ) が垂直成分 ( = z 軸成分 ) に比べて非常に大きくて、第 1 自由磁性層 2 0 3 の磁化のような周期に時間に対して振動する挙動を示す。このような第 2 自由磁性層 2 0 5 の時間にしたがう振動、即ち歳差運動は、全体構造に電流を印加する時、垂直方向に磁化されている第 1 自由磁性層 2 0 3 によるスピン分極された垂直方向スピントルクによって発生する。 30

#### 【 0 0 6 4 】

下記の図 4 D は時間にしたがう第 2 自由磁性層 2 0 5 の歳差運動によって第 1 自由磁性層 2 0 3 に発生する交流磁気場を示したグラフである。このような交流磁気場は第 2 自由磁性層 2 0 5 の磁化が第 1 自由磁性層 2 0 3 の位置に作り出す磁気場であり、これは第 2 自由磁性層 2 0 5 磁化の時間にしたがう歳差運動をするので、発生する。

#### 【 0 0 6 5 】

下記の図 4 D を参照すれば、x - 成分を有する 2 0 0 0 e 程度大きさの交流磁気場が本発明による磁気メモリ素子構造で自体的に発生することを意味する。したがって、従来の素子構造と異なりに、本発明による素子構造では、第 1 自由磁性層 2 0 3 の磁化を反転させるための電流密度を低くするために、素子の外部に追加的に交流磁気場を作り出す装置が必要としないことである。 40

#### 【 0 0 6 6 】

即ち、第 2 自由磁性層 2 0 5 は面内成分が大きい歳差運動をするので、第 1 自由磁性層に誘導された交流磁気場は x - 成分が z - 成分に比べて非常に大きく現われる。結果的に誘導磁気場は第 1 自由磁性層 2 0 3 の磁化容易軸 ( z - 軸 ) の異方性エネルギーを減少させて、第 1 自由磁性層 2 0 3 の磁化スイッチングを容易にする。

#### 【 0 0 6 7 】

実験例 2 . 従来の構造にしたがう素子及び本発明による素子に対して印加された電流に対するスイッチング確率測定

( 1 ) 下記の図 1 の従来の構造と下記の図 2 に開示された本発明による新しい構造の素子に対してスイッチング電流を開示する。 50

(2) 素子の構造と物性値とは次の通りである。

全体構造の断面積は2つの構造で同様に $314\text{ nm}^2$ である。

下記の図1の従来の構造は固定磁性層101/非磁性層102/自由磁性層103：“厚さ( $t$ )= $3\text{ nm}$ 、垂直異方性常数( $K$ )= $6 \times 10^6\text{ erg/cm}^3$ 、飽和磁化値( $M_{s1}$ )= $1000\text{ emu/cm}^3$ 、Gillbert減衰常数( $\alpha$ )= $0.01$ 、スピニ分極効率常数( $\gamma_1$ )= $1.0$ ”

下記の図2の本発明による新しい構造の物性値は次の通りである。

固定磁性層201/第1非磁性層202/第1自由磁性層203：“厚さ( $t$ )= $3\text{ nm}$ 、垂直異方性常数( $K$ )= $6 \times 10^6\text{ erg/cm}^3$ 、飽和磁化値( $M_{s1}$ )= $1000\text{ emu/cm}^3$ 、Gillbert減衰常数( $\alpha$ )= $0.01$ 、スピニ分極効率常数( $\gamma_1$ )= $1.0$ ”10

第2非磁性層204：厚さ $t=1\text{ nm}$

第2自由磁性層205：“厚さ( $t$ )= $1\text{ nm}$ 、垂直異方性常数( $K$ )= $0\text{ erg/cm}^3$ 、飽和磁化値( $M_{s2}$ )= $700\text{ emu/cm}^3$ 、Gillbert減衰常数( $\alpha$ )= $0.01$ 、スピニ分極効率常数( $\gamma_2$ )= $1.0$ ”

従来の構造と本発明による新しい構造で共通的に含まれた固定磁性層、第1非磁性層(非磁性層)及び自由磁性層(第1自由磁性層)は同一な構造及び物性値を有する。

(3) 本実験例で考慮した素子の温度は $300\text{ K}$ であり、各々の印加電流で100回の実験を反復して磁化がスイッチングされる確率を測定した。

#### 【0068】

20

下記の図5Aは本発明による新しい構造(図2)と従来の構造(図1)に対して印加された電流にしたがうスイッチング確率( $P_{sw}$ )を示したグラフである。

#### 【0069】

下記の図5Aを参照すれば、スイッチング電流はスイッチング確率( $P_{sw}$ )が $0.5$ である電流として定義されるが、新しい構造ではスイッチング電流が $7.9\mu\text{A}$ であり、既存構造では $17.6\mu\text{A}$ であった。即ち、スイッチング電流が約 $55\%$ 程度減少したことを意味する。

#### 【0070】

下記の図5Bは下記の図5Aに図示されたスイッチング確率を電流に微分した値を示したグラフである。

30

#### 【0071】

下記の図5Bを参照すれば、一般的な確率分布でQ-因子はピークのx-軸値をy-軸値が $0.5$ である地点(FWHM、full width half maximum)で分布関数の幅に分けた値であり、本実験例では $I_c/I$ として定義される。本発明による下記の図2の新しい構造の場合、Q-因子は $13.5$ であり、図1の従来の構造は $3.6$ を示す。

#### 【0072】

即ち、本発明による磁気メモリ素子構造の高いQ-因子はスイッチング確率分布が小さいことを意味し、これは磁化状態を変わるために印加しなければならない電流の分散が小さいことを意味することであり、本発明による磁気メモリ素子構造が商用化の観点で非常に優秀であることを分かる。

40

#### 【0073】

実験例3. 本発明による素子に対する第2自由磁性層205の飽和磁化値にしたがうスイッチング電流測定

(1) 本発明による新しい構造で第2自由磁性層205の飽和磁化値( $M_{s2}$ )にしたがうスイッチング電流の変化を開示する。

(2) 素子の構造と物性値は次の通りである。

全体構造の断面積= $314\text{ nm}^2$

固定磁性層201/第1非磁性層202/第1自由磁性層203：“厚さ( $t$ )= $3\text{ nm}$ 、垂直異方性常数( $K$ )= $6 \times 10^6\text{ erg/cm}^3$ 、飽和磁化値( $M_{s1}$ )= $1000\text{ emu/cm}^3$ ”50

$0.0 \text{ emu/cm}^3$ 、Gilbert減衰常数( $\gamma$ ) = 0.01、スピン分極効率常数( $\alpha_1$ ) = 1.0”

第2非磁性層204：厚さ $t = 1 \text{ nm}$

第2自由磁性層205：“厚さ( $t$ ) = 1 nm、垂直異方性常数( $K_u$ ) = 0 erg/ $\text{cm}^3$ 、飽和磁化値( $M_{s2}$ ) = 0 - 2000 emu/ $\text{cm}^3$ 、Gilbert減衰常数( $\gamma$ ) = 0.01、スピン分極効率常数( $\alpha_2$ ) = 0 - 1.0”

(3) 本実験例で考慮した素子の温度は300Kであり、スイッチング電流は前記実験例2のように、各々の印加電流で実験を100回実施した後、スイッチング確率を測定した。

#### 【0074】

10

下記の図6は第2自由磁性層205の飽和磁化値及びスピン分極効率に対するスイッチング電流を示したグラフである。

#### 【0075】

下記の図6を参照すれば、水平異方性を有する第2自由磁性層205の飽和磁化値( $M_{s2}$ )にしたがってスイッチング電流が変わることを分かる。ここで、 $M_{s2}$ が $0 \text{ emu/cm}^3$ である場合が水平異方性を有する第2自由磁性層が無い構造、即ち下記の図1に開示された従来磁気メモリ素子構造に該当する。本発明によれば、 $M_{s2}$ が $300 \text{ emu/cm}^3$ 以上である場合、第2自由磁性層205のスピン分極効率と関わらず、既存構造に比ベスイッチング電流が減少し、特に $M_{s2}$ が $300 \sim 500 \text{ emu/cm}^3$ でスイッチング電流の低減効果が最も大きく現れることを分かる。

20

#### 【0076】

このように、第1自由磁性層203のスイッチング電流を減少させるためには第2自由磁性層205の誘導交流磁気場が必要である。本実験例のように第2自由磁性層205の飽和磁化値( $M_{s2}$ )が $300 \text{ emu/cm}^3$ 以上でスイッチング電流密度減少効果が現れることを分かる。

#### 【0077】

本発明による新しい磁気メモリ素子構造は一定の以上の飽和磁化値を有し、水平磁化を有する第2自由磁性層205を挿入することによって、既存構造に比ベスイッチング電流が効果的に減少したことが分かる。

#### 【0078】

30

実験例4. 従来の構造にしたがう素子及び本発明による素子に対して印加された電流に対するスイッチング確率測定

(1) 下記の図1の従来の構造と下記の図3に開示された本発明による新しい構造の素子に対して印加された電流に対するスイッチング確率を開示する。

(2) 素子の構造と物性値とは次の通りである。

全体構造の断面積は2つの構造で同様に $314 \text{ nm}^2$ である。

下記の図1の従来の構造は固定磁性層101/非磁性層102/自由磁性層103 [ 厚さ( $t$ ) = 3 nm、垂直異方性常数( $K_u$ ) =  $7 \times 10^5 \text{ J/m}^3$ 、飽和磁化値( $M_{s1}$ ) = 1100 kA/m、Gilbert減衰常数( $\gamma$ ) = 0.01、スピン分極効率常数( $\alpha_1$ ) = 1.0] である。

40

下記の図3の本発明による新しい構造は第1固定磁性層301/第1非磁性体302 [ 厚さ( $t$ ) = 1 nm ] / 第1自由磁性層303 [ 厚さ( $t$ ) = 3 nm、垂直異方性常数( $K_u$ ) =  $7 \times 10^5 \text{ J/m}^3$ 、飽和磁化値( $M_{s1}$ ) = 1100 kA/m、Gilbert減衰常数( $\gamma$ ) = 0.01、スピン分極効率常数( $\alpha_1$ ) = 1.0 ] / 第2非磁性層304 [ 厚さ( $t$ ) = 1 ] / 第2自由磁性層305 [ 厚さ( $t$ ) = 1、垂直異方性常数( $K_u$ ) = 0 erg/、飽和磁化値( $M_{s2}$ ) = 800 / m、Gilbert減衰常数( $\gamma$ ) = 0.01、第1自由磁性層によるスピン分極効率常数( $\alpha_2$ ) = 1.0 ] / 第2固定磁性層によるスピン分極効率常数( $\alpha_3$ ) = 0 ] / 第3非磁性層306 [ 厚さ( $t$ ) = 1 nm ] / 第2固定磁性層307 [ 厚さ( $t$ ) = 3 nm、飽和磁化値( $M_{s3}$ ) = 1100 kA/m ] である。したがって、従来の構造と本発明による新しい構造で共通的に含まれた固定層(

50

第1固定磁性層)、非磁性層(第1非磁性層)及び自由磁性層(第1自由磁性層)は同一な構造及び物性値を有する。

(3) 本実験例で素子の温度は300Kであり、各々の印加電流で100回の実験を反復して自由層(第1自由層)の磁化の方向が初期方向で反対方向にスイッチングが行われる確率を測定した。

#### 【0079】

下記の図7の(a)は図1の従来の構造と図3の本発明による新しい構造とに対して印加された電流にしたがうスイッチング確率( $P_{sw}$ )を示したグラフである。ここで、実線は下記の累積分布関数である[式4]をフィッティング(fitting)した値を示す。

10

#### 【0080】

##### 【数4】

[式4]

$$P_{sw} = \frac{1}{2} \left\{ 1 + \operatorname{erf} \left( \frac{I_{app} - I_{sw}}{\sigma \sqrt{2}} \right) \right\}$$

#### 【0081】

前記[式4]で、 $I_{app}$ は印加された電流密度、 $I_{sw}$ はスイッチング電流密度、 $\sigma$ は確率分布の標準偏差である。

20

#### 【0082】

下記の図7の(a)を参照すれば、スイッチング電流はスイッチング確率( $P_{sw}$ )が0.5である電流として定義され、前記[式4]をフィッティング(fitting)して得られる。本発明による構造ではスイッチング電流が10.1μAであり、従来の構造では18.36μAである。即ち、本発明による構造を適用した磁気メモリ素子のスイッチング電流が約45%程度減少した。

#### 【0083】

下記の図7の(b)は図1の従来の構造と図3の本発明による新しい構造とに対して印加された電流にしたがうスイッチング確率( $P_{sw}$ )を電流に微分した値を示したグラフである。

30

#### 【0084】

下記の図7の(b)を参照すれば、一般的な確率分布でQ-因子はピークのx-軸値をy-軸値が0.5である地点(FWHM、full width half maximum)で分布関数の幅に分けた値であり、本実験例では $I_{sw}/I$ として定義される。本発明による下記の図3の新しい構造の場合、Q-因子は7.14であり、図1の従来の構造は3.43である。また、前記[式4]から求めた標準偏差( )は新しい構造は1.21であり、従来の構造の場合、2.26である。

#### 【0085】

本発明による磁気メモリ素子構造は高いQ-因子の特性を有する。したがって、新しい構造で磁化状態を変わるために必要である電流の分散が小さいことを意味することであつて、これは商用化の観点で非常に優れた特性である。

40

#### 【0086】

実験例5. 従来の構造にしたがう素子のスイッチング電流及び本発明による素子に対する第2自由磁性層305の飽和磁化値にしたがうスイッチング電流及び分布図測定

(1) 下記の図1の従来の構造のスイッチング電流及び分布図を開示する。

(2) 下記の図3に開示された本発明による新しい構造の素子に対する第2自由磁性層305の飽和磁化値( $M_{s2}$ )にしたがうスイッチング電流及び分布図の変化を開示する。

(3) 素子の構造と物性値とは次の通りである。

50

全体構造の断面積は2つの構造で同様に $314\text{ nm}^2$ である。

下記の図1の従来の構造は固定磁性層101/非磁性層102/自由磁性層103[厚さ( $t$ )= $3\text{ nm}$ 、垂直異方性常数( $K$ )= $7 \times 10^5\text{ J/m}^3$ 、飽和磁化値( $M_{s1}$ )= $1100\text{ kA/m}$ 、 $Gilbert$ 減衰常数( $\gamma$ )= $0.01$ 、スピン分極効率常数( $\alpha_1$ )= $1.0$ ]である。即ち、前記実験例1で考慮した構造及び物性値と同一である。

下記の図3の本発明にしたがう新しい構造は第1固定磁性層301/第1非磁性体302[厚さ( $t$ )= $1\text{ nm}$ ]／第1自由磁性層303[厚さ( $t$ )= $3\text{ nm}$ 、垂直異方性常数( $K$ )= $7 \times 10^5\text{ J/m}^3$ 、飽和磁化値( $M_{s1}$ )= $1100\text{ kA/m}$ 、 $Gilbert$ 減衰常数( $\gamma$ )= $0.01$ 、スピン分極効率常数( $\alpha_1$ )= $1.0$ ]／第2非磁性層304[厚さ( $t$ )= $1\text{ nm}$ ]／第2自由磁性層305[厚さ( $t$ )= $1\text{ nm}$ 、垂直異方性常数( $K$ )= $0\text{ J/m}^3$ 、飽和磁化値( $M_{s2}$ )= $0-1500\text{ kA/m}$ 、 $Gilbert$ 減衰常数( $\gamma$ )= $0.01$ 、第1自由磁性層によるスピン分極効率常数( $\alpha_2$ )= $1.0$ 、第2固定磁性層によるスピン分極効率常数( $\alpha_3$ )= $0$ ]／第3非磁性層306[厚さ( $t$ )= $1\text{ nm}$ ]／第2固定磁性層307[厚さ( $t$ )= $3\text{ nm}$ 、飽和磁化値( $M_s$ )= $1100\text{ kA/m}$ ]である。

(4) 本実験例で素子の温度は $300\text{ K}$ であり、各々の印加電流で100回の実験を反複して自由層(第1自由磁性層)の磁化の方向が初期方向で反対方向にスイッチングが行われる確率を測定した。

(5) 磁気メモリ素子は固定磁性層と自由磁性層との相対的な方向に沿って2つの場合のスイッチングが発生する。

#### 【0087】

P-t o - A Pは電流を印加する前の自由磁性層(第1自由磁性層)と固定磁性層(第1固定磁性層)との相対的な方向が平行な状態で、印加電流によって自由磁性層(第1自由磁性層)の磁化スイッチングが発生して反平行な状態に磁化が配列される場合である。

#### 【0088】

A P - t o - Pは電流を印加する前の自由磁性層(第1自由磁性層)と固定磁性層(第1固定磁性層)との相対的な方向が反平行な状態で、印加電流によって自由磁性層(第1自由磁性層)の磁化スイッチングが発生して平行な状態に磁化が配列される場合である。

#### 【0089】

下記の図8Aは従来の構造(図1)の磁気メモリ素子に対するスイッチング電流及び分布図、新しい構造(図3)の磁気メモリ素子に対して第2自由磁性層305の飽和磁化値にしたがうスイッチング電流を示したグラフである。

#### 【0090】

下記の図8Aを参照すれば、水平異方性を有する第2自由磁性層305の飽和磁化値( $M_{s2}$ )にしたがってスイッチング電流が変わることを分かる。本実験例によれば、第2自由磁性層305の飽和磁化値と関わらずに本発明による新しい構造(図3)の磁気メモリ素子のスイッチング電流は黒色実線で表示された従来の構造(図1)の値に比べて常に低い値を有する。特に、 $M_{s2}$ が $300-500\text{ kA/m}$ でスイッチング電流の低減効果が最も大きく現れることを分かる。

#### 【0091】

また、下記の図8Bは従来の構造(図1)の磁気メモリ素子のスイッチング電流の分布図及び本発明による構造(図3)の磁気メモリ素子に対して第2自由磁性層305の飽和磁化値にしたがうスイッチング電流の分布図を示したグラフである。

#### 【0092】

下記の図8Bを参照すれば、前記例示されたスイッチング電流値と類似な傾向性が現われる。本発明にしたがって新しい構造を適用した磁気メモリ素子の場合、従来の構造に比べ、小さいスイッチング電流分布図を有することを分かる。特に、 $M_{s2}$ が $300\text{ kA/m}$ 以上で $50\%$ 程度減少することと現れた。

#### 【産業上の利用可能性】

10

20

30

40

50

## 【0093】

このように、本発明による新しい構造の磁気メモリ素子は一定の以上の飽和磁化値を有し、水平磁化を有する第2自由磁性層305によって、既存構造に比べスイッチング電流及び分布図が効果的に減少したことを分かる。

## 【符号の説明】

## 【0094】

100 磁気メモリ素子

101 第1磁性体（固定磁性層）

102 非磁性体

103 第2磁性体（自由磁性層）

10

【図4A】

【図1】

【図2】

【図3】

【図4B】

【図4C】

【図4D】

【図5A】

【図5B】

【図6】

【図7】

【図8 A】

【図8 B】

---

フロントページの続き

(72)発明者 ソー・マン・ソ

大韓民国・142-751・ソウル・カンブク・グ・ミア・4-ドン・(番地なし)・ギヨンナム

・オーナーズヴィル・アパート・110-403

審査官 佐藤 靖史

(56)参考文献 特開2009-231753(JP,A)

特開2010-016408(JP,A)

特開2012-064863(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/10

29/82

43/08