## (12) 发明专利

(10) 授权公告号 CN 109524288 B

(45) 授权公告日 2021.01.05

(21) 申请号 201711453386.1

H01L 21/3065 (2006.01)

(22) 申请日 2017.12.27

(56) 对比文件

(65) 同一申请的已公布的文献号

US 2017169996 A1, 2017.06.15

申请公布号 CN 109524288 A

CN 106024569 A, 2016.10.12

(43) 申请公布日 2019.03.26

CN 104871430 A, 2015.08.26

(30) 优先权数据

US 2006144519 A1, 2006.07.06

2017-179665 2017.09.20 JP

US 2015014276 A1, 2015.01.15

(73) 专利权人 株式会社日立高新技术

JP 2007067037 A, 2007.03.15

地址 日本东京都

JP 2004022822 A, 2004.01.22

(72) 发明人 山田一也 山本浩一 安井尚辉

JP 2005071872 A, 2005.03.17

池田纪彦 森功

JP 2008027816 A, 2008.02.07

(74) 专利代理机构 中科专利商标代理有限责任

公司 11021

JP 2011017076 A, 2011.01.27

代理人 李国华

JP 2016162759 A, 2016.09.05

US 2016351404 A1, 2016.12.01

审查员 丁瑞平

(51) Int.Cl.

H01J 37/32 (2006.01)

权利要求书2页 说明书8页 附图4页

(54) 发明名称

等离子体处理装置以及等离子体处理方法

(57) 摘要

本发明提供一种提高了样品的处理的均匀性的等离子体处理装置以及等离子体处理方法。等离子体处理装置具备:处理室;设置在该处理室的内部并载置样品的被电分割成多个区域的样品台;将电磁波导入至处理室的内部的电磁波导入部;以及向样品台施加偏置电力的偏置电力施加部,偏置电力施加部具备:向样品台的被电分割成多个的区域之中的第一区域施加第一高频电力的第一高频电力施加部;向样品台的被电分割成多个的区域之中的第二区域施加第二高频电力的第二高频电力施加部;以及对第一高频电力施加部和第二高频电力施加部进行控制从而使第一高频电力和第二高频电力的相位偏移给定量的相位调整部。

1. 一种等离子体处理装置,具备:

处理室,其对样品进行等离子体处理;

高频电源,其供给用于生成等离子体的高频电力;

样品台,其具备用于使所述样品静电吸附的第一电极和第二电极并载置所述样品;

第一高频电源,其向所述第一电极供给第一高频电力;

第二高频电源,其向所述第二电极供给第二高频电力;以及

控制装置,其对所述第一高频电力的相位与所述第二高频电力的相位之差即相位差进行控制,

所述等离子体处理装置的特征在于,

还具备:电极间电路部,其配置在将所述第一高频电力供给至所述第一电极的第一传送路与将所述第二高频电力供给至所述第二电极的第二传送路之间,

所述电极间电路部的一个连接部连接在所述样品台与所述第一高频电源的匹配器之间,

所述电极间电路部的另一个连接部连接在所述样品台与所述第二高频电源的匹配器之间,

所述控制装置对所述相位差进行控制,使得施加至所述第一电极的高频电压的峰-峰值电压与施加至所述第二电极的高频电压的峰-峰值电压之差即电压差成为给定值。

2. 根据权利要求1所述的等离子体处理装置,其特征在于,

所述电极间电路部具有电感。

3. 根据权利要求1所述的等离子体处理装置,其特征在于,

还具备:

监视部,其对所述一个连接部与所述样品台之间的所述第一高频电力的相位、以及所述另一个连接部与所述样品台之间的所述第二高频电力的相位进行监视,

所述控制装置基于由所述监视部监视到的所述第一高频电力的相位、由所述监视部监视到的所述第二高频电力的相位、以及所述给定值来控制所述相位差。

4. 根据权利要求1所述的等离子体处理装置,其特征在于,

所述控制装置对所述相位差进行控制,使得所述相位差成为与基于所述电压差与所述相位差的相关关系而求出的所述给定值对应的相位差。

5. 根据权利要求1所述的等离子体处理装置,其特征在于,

所述第一高频电力的频率与所述第二高频电力的频率相同。

6. 一种使用了等离子体处理装置的等离子体处理方法,所述等离子体处理装置具备:

处理室,其对样品进行等离子体处理;

高频电源,其供给用于生成等离子体的高频电力;

样品台,其具备用于使所述样品静电吸附的第一电极和第二电极并载置所述样品;

第一高频电源,其向所述第一电极供给第一高频电力;

第二高频电源,其向所述第二电极供给第二高频电力;以及

控制装置,其对所述第一高频电力的相位和所述第二高频电力的相位之差即相位差进行控制;以及

电极间电路部,其配置在将所述第一高频电力供给至所述第一电极的第一传送路与将

所述第二高频电力供给至所述第二电极的第二传送路之间，

所述电极间电路部的一个连接部连接在所述样品台与所述第一高频电源的匹配器之间,所述电极间电路部的另一个连接部连接在所述样品台与所述第二高频电源的匹配器之间，

所述等离子体处理方法的特征在于，

对所述相位差进行控制,使得施加至所述第一电极的高频电压的峰-峰值电压与施加至所述第二电极的高频电压的峰-峰值电压之差即电压差成为给定值。

7.根据权利要求6所述的等离子体处理方法,其特征在于,

基于由对所述一个连接部与所述样品台之间的所述第一高频电力的相位以及所述另一个连接部与所述样品台之间的所述第二高频电力的相位进行监视的监视部监视到的所述第一高频电力的相位、由所述监视部监视到的所述第二高频电力的相位、以及所述给定值,对所述相位差进行控制。

8.根据权利要求6所述的等离子体处理方法,其特征在于,

对所述相位差进行控制,使得所述相位差成为与基于所述电压差与所述相位差的相关关系而求出的所述给定值对应的相位差。

## 等离子体处理装置以及等离子体处理方法

### 技术领域

[0001] 本发明涉及使用具备真空容器内部的处理室和配置在其内侧并将半导体晶片等基板状的样品载置在其上表面上的样品台的等离子体处理装置,在处理室内形成等离子体的同时向配置在样品台的内部的电极供给高频电力来实施样品的处理的等离子体处理装置以及等离子体处理方法。

### 背景技术

[0002] 在利用处理室内产生的等离子体对半导体元件等样品进行加工的等离子体蚀刻装置中,已知如下方法,即,例如专利文献1以及2所记载的那样,使用形成为同心圆状的多个基板电极,在产生了等离子体的状态下对基板电极施加高频偏置电力,由此对微细图案高精度地实施蚀刻处理。

[0003] 专利文献

[0004] 专利文献1:JP特开2007-67037号公报

[0005] 专利文献2:JP特开2004-22822号公报

[0006] 专利文献1记载了以下技术,即,在使用作为被两分割成同心圆状的电极的样品台来加工样品的等离子体处理装置中,分别独立地控制从两个高频偏置电源向作为电极的样品台的中心侧的样品台区块和外周侧的样品台区块施加的RF偏置电力。

[0007] 此外,专利文献2记载了以下结构,即,在使用呈同心圆状地两分割成中心侧的内侧台和外周侧的外侧台的电极台来加工样品的等离子体处理装置中,将从两个高频偏置电源供给的各个高频电力的相位设为相同而施加于电极台的内侧台和外侧台。通过将各个高频电力的相位设为相同来施加,从而在内侧台和外侧台的各个电力产生差异,由此能够在电极台使施加于样品的高频电力的峰-峰值电压(原文:ピーク・トゥ・ピーク电压) (以下,称为V<sub>PP</sub>)在内侧台和外侧台产生差异。

[0008] 但是,若对样品施加来自两个高频偏置电源的电力,则存在如下这样的两个课题。

[0009] 首先,若如专利文献2记载的那样,将两个高频偏置电源的输出供给至电极台的内侧台和外侧台,并试图使施加至样品的V<sub>PP</sub>在中心侧和外周侧产生差异,则会出现以下问题,即,在来自各个高频偏置电源的输出的相位相同的情况下,需要增大两个高频偏置电源的输出差,则一个高频偏置电源需要额定输出较大的高频偏置电源。

[0010] 此外,即使在通过来自外部的相位控制装置使两个高频偏置电源的输出成为相同的情况下,若各个偏置电源内部的相位的旋转方式存在机械差异,也会出现以下问题,即,实际施加至电极台的内侧台和外侧台的高频电力不成为相同相位。

[0011] 此外,在专利文献1公开的结构中,由于在各个分割出的中心侧的样品台区块和外周侧的样品台区块的电极间流动电流而成为电压差的起因的电极间电路不足,因而会出现在电极间无法对V<sub>PP</sub>赋予足够的差这样的问题。

## 发明内容

[0012] 本发明提供一种能够解决上述现有技术的课题,提高样品的处理的均匀性,并使成本得到抑制的等离子体处理装置以及等离子体处理方法。

[0013] 为了解决上述课题,在本发明中为一种等离子体处理装置,该等离子体处理装置构成为,具备:处理室,其对样品进行等离子体处理;高频电源,其供给用于生成等离子体的高频电力;样品台,其具有被电分割出的第一区域和第二区域并载置样品;第一高频电源,其向第一区域供给第一高频电力;第二高频电源,其向第二区域供给第二高频电力;以及控制装置,其对第一高频电力的相位与第二高频电力的相位之差即相位差进行控制,在该等离子体处理装置中,还具备配置在第一高频电源对第一区域进行供给的第一传送路与第二高频电源对第二区域进行供给的第二传送路之间的电极间电路部,电极间电路部的一个连接部连接在样品台与第一高频电源的匹配器之间,电极间电路部的另一个连接部连接在样品台与第二高频电源的匹配器之间,控制装置对相位差进行控制,使得施加至第一区域的高频电压的峰-峰值电压与施加至第二区域的高频电压的峰-峰值电压之差即电压差成为给定值。

[0014] 此外,为了解决上述课题,在本发明中为一种使用了等离子体处理装置的等离子体处理方法,该等离子体处理装置具备:处理室,其对样品进行等离子体处理;高频电源,其供给用于生成等离子体的高频电力;样品台,其具有被电分割出的第一区域和第二区域并载置样品;第一高频电源,其向第一区域供给第一高频电力;第二高频电源,其向第二区域供给第二高频电力;控制装置,其对第一高频电力的相位与第二高频电力的相位之差即相位差进行控制;以及电极间电路部,其配置在第一高频电源对第一区域进行供给的第一传送路与第二高频电源对第二区域进行供给的第二传送路之间,电极间电路部的一个连接部连接在样品台与第一高频电源的匹配器之间,电极间电路部的另一个连接部连接在样品台与第二高频电源的匹配器之间,对所述相位差进行控制,使得施加至第一区域的高频电压的峰-峰值电压与施加至第二区域的高频电压的峰-峰值电压之差即电压差成为给定值。

[0015] 发明效果

[0016] 根据本发明,能够使用比较小的额定输出的高频偏置电源来改善从晶片的中心部到外周部的蚀刻速率的均匀性,能够抑制等离子体处理装置的成本。

## 附图说明

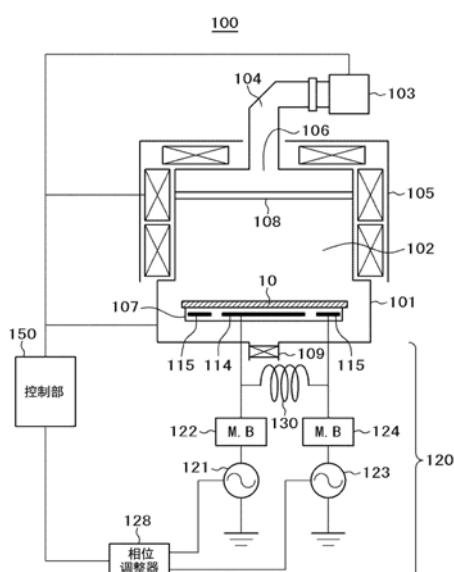

[0017] 图1是示意性表示本发明的实施例1涉及的等离子体处理装置的结构的概略的纵剖面图。

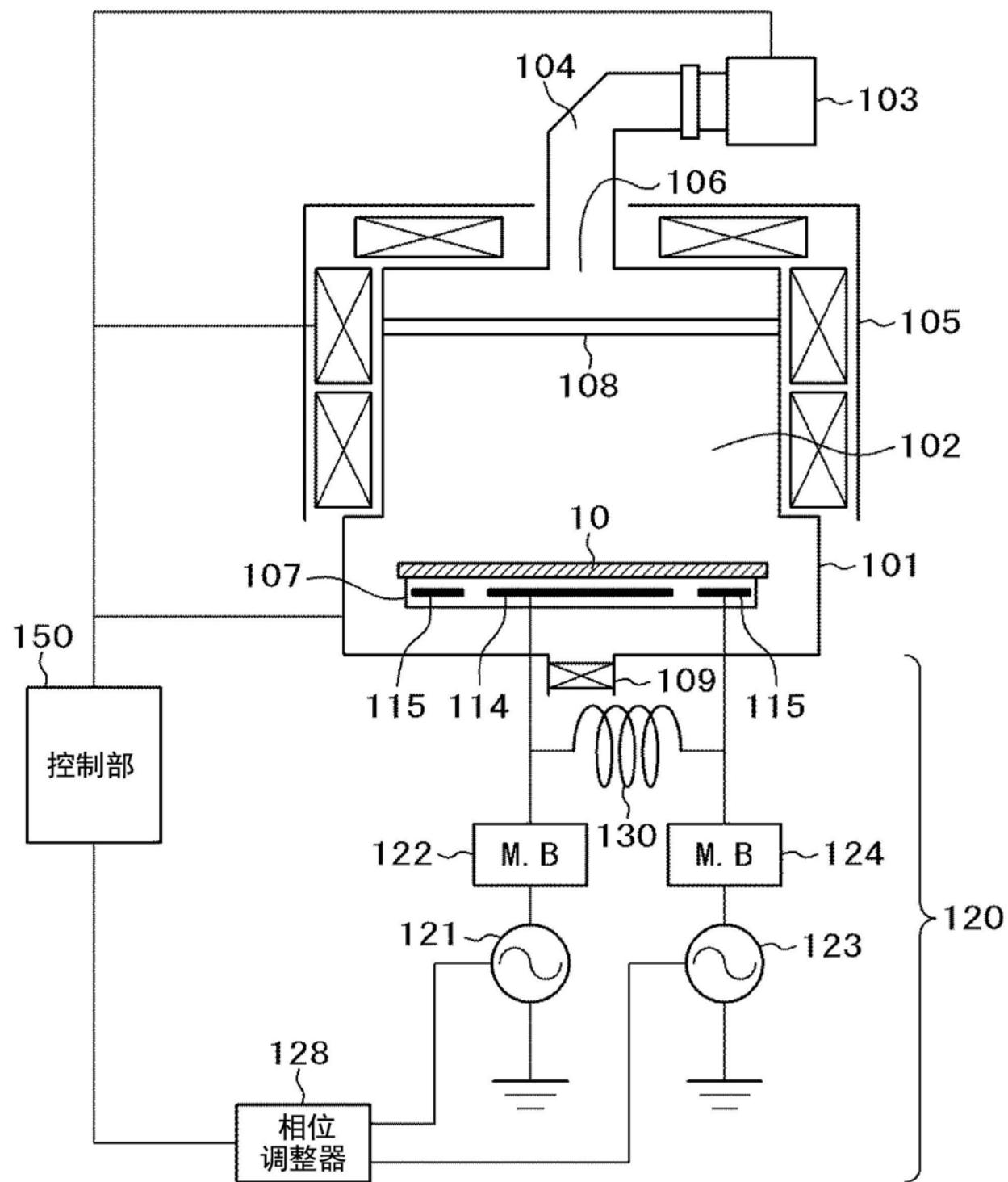

[0018] 图2是表示本发明的实施例1涉及的等离子体处理装置的高频偏置电力施加电路结构的详细情况的框图。

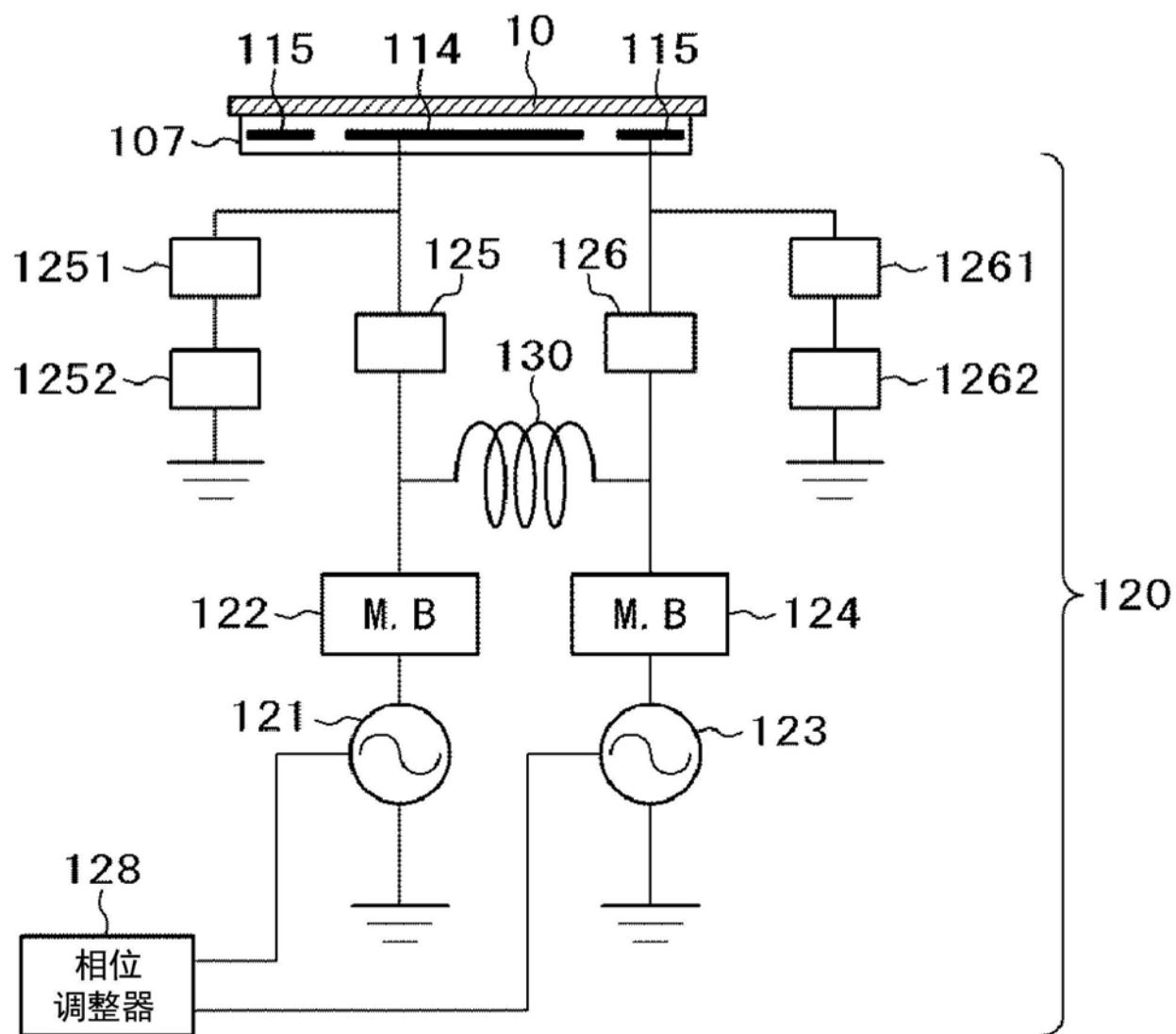

[0019] 图3是表示本发明的实施例1涉及的高频偏置电力施加电路的相位调整器的结构的框图。

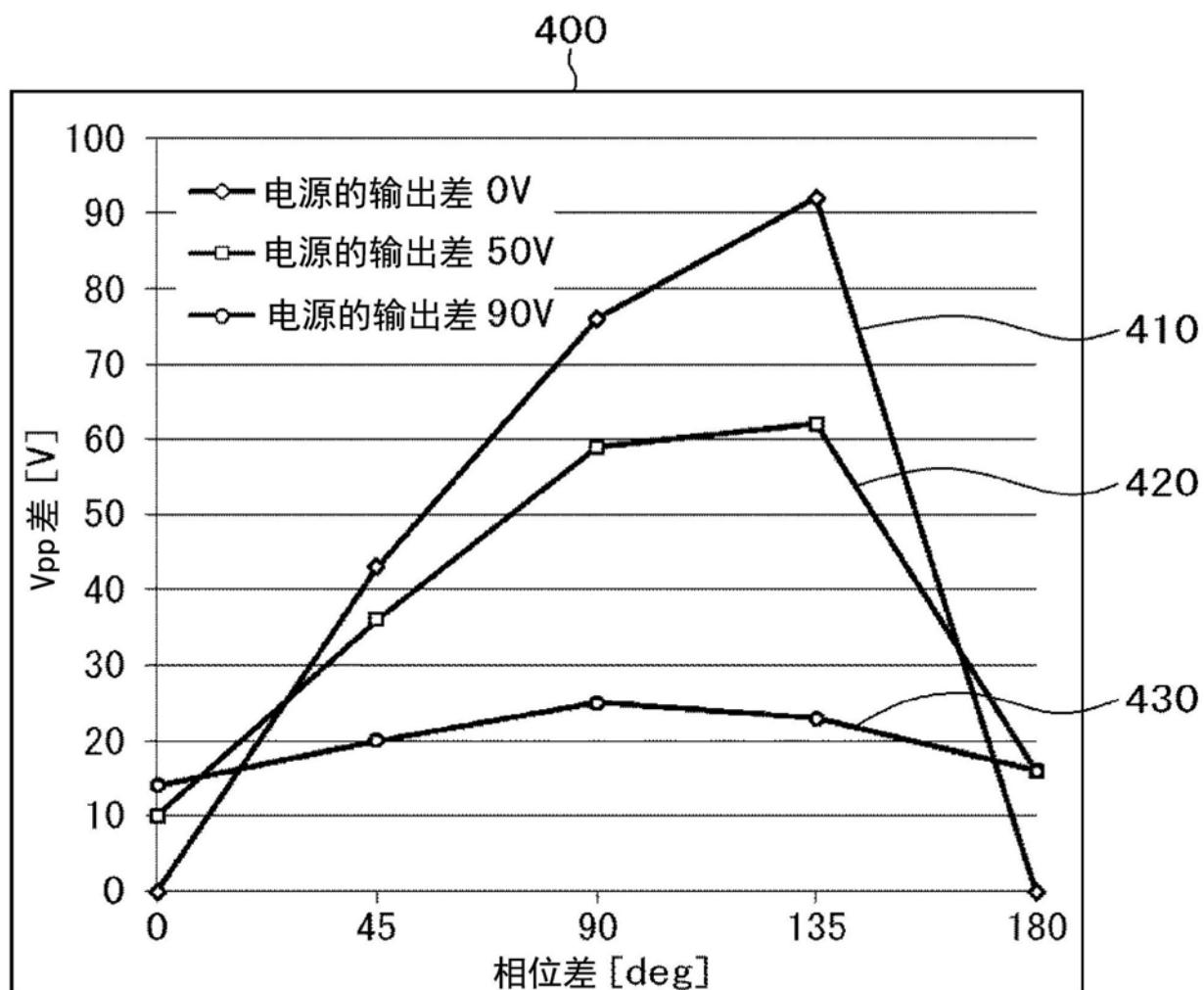

[0020] 图4是表示基于本发明的实施例1中的高频偏置电力施加电路,通过电路模拟器而求出的施加至晶片的高频偏置电力的相位差与在晶片的面内产生的 $V_{pp}$ 的差的关系的曲线图。

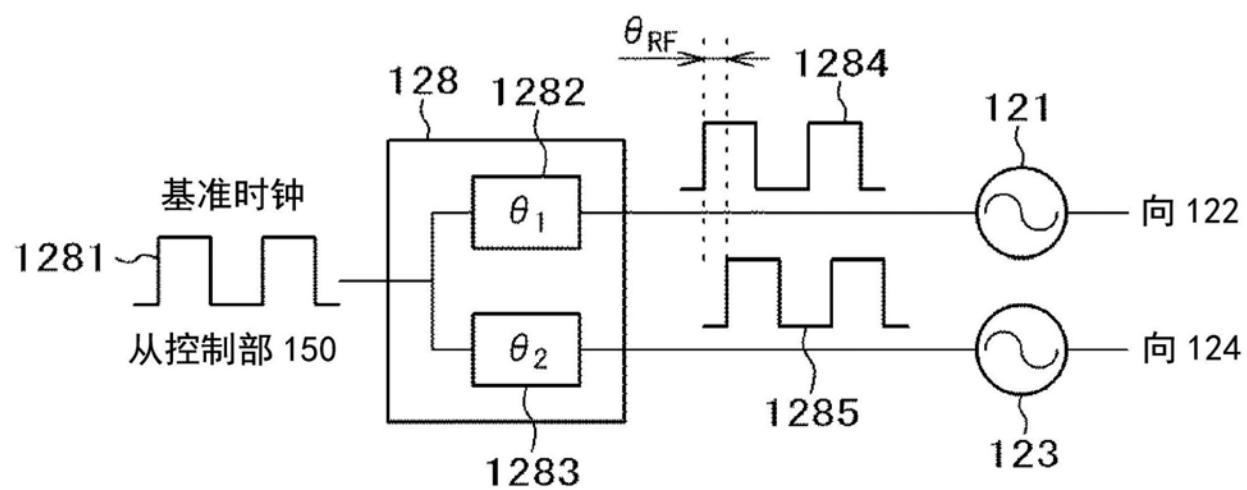

[0021] 图5是表示本发明的实施例2涉及的等离子体处理装置的高频偏置电力施加电路

的结构的框图。

- [0022] 附图标记说明

- [0023] 100: 蚀刻装置;

- [0024] 101: 真空容器;

- [0025] 102: 处理室;

- [0026] 103: 电磁波产生用电源;

- [0027] 104: 波导管;

- [0028] 105: 磁场产生线圈;

- [0029] 107: 样品载置用电极;

- [0030] 108: 电介质窗;

- [0031] 114: 中心侧电极;

- [0032] 115: 外周侧电极;

- [0033] 120、500: 高频偏置电力施加电路部;

- [0034] 121、501: 第一高频偏置电源;

- [0035] 122、502: 第一匹配电路;

- [0036] 123、503: 第二高频偏置电源;

- [0037] 124、504: 第二匹配电路;

- [0038] 125: 第一直流截止用滤波器电路;

- [0039] 1251: 第一高频截止滤波器;

- [0040] 1252: 第一直流电源;

- [0041] 126: 第二直流截止用滤波器电路;

- [0042] 1261: 第二高频截止滤波器;

- [0043] 1262: 第二直流电源;

- [0044] 128、505: 相位调整器;

- [0045] 130、510: 电极间电路;

- [0046] 506: 相位差测定器;

- [0047] 507: 相位差信号设定部。

### 具体实施方式

[0048] 本发明涉及能够以比较廉价的结构来提高样品的处理的均匀性的等离子体处理装置以及等离子体处理方法。

[0049] 在本发明中构成为,在分别向构成载置样品的样品台的内侧电极和外侧电极施加高频电力的高频电力施加电路间设置电极间电路,进而能够对分别施加至内侧电极和外侧电极的高频电力的相位差进行控制。

[0050] 由此,即使不使用额定输出大的高频电源,通过对施加至内侧电极和外侧电极的高频电力的相位差进行控制,也能够控制内侧电极和外侧电极的V<sub>PP</sub>的差。

[0051] 结果,在本发明中,能够对载置于样品台的晶片的面内的V<sub>PP</sub>分布进行控制,能够使用更小的额定输出的高频偏置电源改善从晶片的中心部到外周部的蚀刻速率的均匀性。

[0052] 以下,使用附图说明本发明的实施例。

[0053] 【实施例1】

[0054] 使用图1至图3说明本发明的第一方式。图1是作为本实施例涉及的等离子体处理装置的例子而示出ECR (Electron Cyclotron Resonance: 电子回旋共振) 方式的微波等离子体蚀刻装置(以下, 记载为蚀刻装置) 100的纵剖面的简要结构的图。

[0055] 本实施例涉及的蚀刻装置100具备: 真空容器101、作为等离子体生成用高频电源的电磁波产生用电源103、波导管104、磁场产生线圈105、样品载置用电极107、高频偏置电力施加电路部120、以及对整体进行控制的控制部150。

[0056] 在真空容器101的上部设置电介质窗108, 对内部进行密封, 由此形成处理室102。对处理室102连接用于流动在作为样品的晶片10的蚀刻处理中使用的蚀刻气体的气体供给装置(省略图示)。此外, 对真空容器101经由排气用开闭阀109连接真空排气装置(省略图示)。

[0057] 在处理室102内通过将排气用开闭阀109设为开, 并驱动真空排气装置, 从而减压而成为真空状态。蚀刻气体从未图示的气体供给装置导入到处理室102内, 并由未图示的真空排气装置排气。

[0058] 作为样品台的样品载置用电极107在处理室102的内部与电介质窗108对置地设置在真空容器101的下部。

[0059] 由作为等离子体生成用高频电源的电磁波产生用电源103振荡出的电磁波被传送至波导管104。波导管104将电磁波从形成在真空容器101的上部的开口部106传送至真空容器101的内部。传送至真空容器101的内部的电磁波透过电介质窗108而供给至处理室102的内部。另外, 本实施例的效果虽然并不特别受电磁波的频率限定, 但在本实施例中使用2.45GHz的微波。

[0060] 磁场产生线圈105在真空容器101的处理室102的上部在电介质窗108的附近, 形成针对从开口部106传送的电磁波ECR条件成立这样的强度的磁场。

[0061] 由电磁波产生用电源103振荡出的电磁波通过与由磁场产生线圈105在电介质窗108的附近形成的满足ECR条件这样的强度的磁场之间的相互作用, 从而在处理室102内生成高密度等离子体。通过该生成的高密度等离子体, 对配置在样品载置用电极107上的样品即晶片10实施蚀刻处理。

[0062] 样品载置用电极107、磁场产生线圈105、排气用开闭阀109以及载置于样品载置用电极107的晶片10相对于处理室102的中心轴上同轴地配置, 因此蚀刻气体的流动、等离子体产生的自由基和离子、以及蚀刻产生的反应生成物相对于晶片10同轴地被导入、排气。该同轴配置使蚀刻速率、蚀刻形状的晶片面内均匀性接近于轴对称, 具有使晶片处理均匀性得到提高的效果。

[0063] 样品载置用电极107具有: 在电介质膜(省略图示)的内部配置在中心侧的膜状的电极即中心侧电极114; 以及配置在其外周侧且形成为环状的膜状的电极即外周侧电极115。这些被施加了高频电力的中心侧电极114和外周侧电极115与载置于样品载置用电极107的晶片10电连接。

[0064] 中心侧电极114经由第一匹配电路122连接了高频偏置电力施加电路部120的第一高频偏置电源121。通过经由第一匹配电路122从第一高频偏置电源121向中心侧电极114施加高频电力, 从而形成用于向载置于样品载置用电极107的晶片10的中心部引入离子的电

场。

[0065] 外周侧电极115经由第二匹配电路124连接了高频偏置电力施加电路部120的第二高频偏置电源123。通过经由第二匹配电路124从第二高频偏置电源123向外周侧电极115施加高频电力,从而形成用于向载置于样品载置用电极107的晶片10的外周部引入离子的电场。

[0066] 此外,被施加了高频电力的中心侧电极114与外周侧电极115之间由电极间电路130连接。通过该电极间电路130,从而在中心侧电极114与外周侧电极115之间流动电流,在中心侧电极114与外周侧电极115之间产生电位差。在本实施例中,作为该电极间电路130,使用线圈,对于高频电力形成电感。

[0067] 在本实施例中,这样构成为,通过设置电极间电路130而对在内侧电极与外侧电极之间流动的电流进行规定,并通过对分别施加至内侧电极和外侧电极的高频电力的相位差进行控制,从而能够控制 $V_{PP}$ 差。

[0068] 另外,关于本实施例的效果,虽然并不特别受从第一高频偏置电源121以及第二高频偏置电源123输出的高频偏置电力的频率限定,但在本实施例中使用400kHz的高频电力。

[0069] 使用图2更详细地说明与本实施例的样品载置用电极107连接的高频偏置电力施加电路部120的电路结构。

[0070] 在中心侧电极114与第一匹配电路122之间连接第一直流截止用滤波器电路125,在该第一直流截止用滤波器电路125与中心侧电极114之间,经由第一高频截止滤波器1251而连接有第一直流电源1252。第一直流截止用滤波器电路125设置为向第一高频偏置电源121以及第一匹配电路122施加直流电压且不破损。第一高频截止滤波器1251设置为向第一直流电源1252施加作为偏置电力的高频电力且不破损。

[0071] 同样地,在外周侧电极115与第二匹配电路124之间连接第二直流截止用滤波器电路126,在该第二直流截止用滤波器电路126与外周侧电极115之间,经由第二高频截止滤波器1261而连接有第二直流电源1262。第二直流截止用滤波器电路126设置为向第二高频偏置电源123以及第二匹配电路124施加直流电压且不破损。第二高频截止滤波器1261设置为向第二直流电源1262施加作为偏置电力的高频电力且不破损。通过向该中心侧电极114和外周侧电极115分别从第一直流电源1252和第二直流电源1262施加极性不同的直流电压,从而在覆盖中心侧电极114的电介质膜以及覆盖外周侧电极115的电介质膜产生介电极化。通过这样产生介电极化,从而在覆盖中心侧电极114的电介质膜内以及覆盖外周侧电极115的电介质膜的上表面载置的晶片10通过静电力而被吸附(静电吸附)在覆盖中心侧电极114的电介质膜内以及覆盖外周侧电极115的电介质膜的上表面,由此晶片10被保持在样品载置用电极107上。

[0072] 第一匹配电路122与第一直流截止用滤波器电路125之间、以及第二匹配电路124与第二直流截止用滤波器电路126之间,由电极间电路130连接。

[0073] 进而,对第一高频偏置电源121以及第二高频偏置电源123连接相位调整器128。

[0074] 接着,使用图3说明在本实施例中对施加至晶片10的中心侧以及外周侧的高频电力的 $V_{PP}$ 进行控制的方法。

[0075] 图3是表示图2所示的相位调整器128的相位控制的图。从控制部150向该相位调整器128输入基准时钟1281(例如400kHz的矩形波)。从相位调整器128的内部的第一相位信号

产生部1282,与该基准时钟1281同步地,输出与基准时钟1281没有相位差的信号1284,并输入到第一高频偏置电源121。

[0076] 另一方面,从相位调整器128的内部的第二相位信号产生部1283,与基准时钟1281同步地,输出相对于基准时钟1281相位差有 $\theta_{RF}$ 的信号1285,并输入到第二高频偏置电源123。

[0077] 第一高频偏置电源121以及第二高频偏置电源123基于从相位调整器128输入的信号,对输出至中心侧电极114以及外周侧电极115的电力进行振荡,所以在各个输出之间产生 $\theta_{RF}$ 的相位差。

[0078] 在本实施例的电路中,通过与第一高频偏置电源121连接的中心侧电极114,施加至晶片10的中心侧的电压 $V_{IN}$ 以由公式(数学式1)示出的形式来表达。

[0079] 【数学式1】

$$[0080] V_{IN} = \sqrt{V_a^2 + V_b^2 + 2V_a V_b \cos(\theta_{RF} + \theta_\alpha)} \quad \cdots \text{ (数学式 1)}$$

[0081] 此外,通过与第二高频偏置电源123连接的外周侧电极115,施加至晶片10的外周侧的电压 $V_{OUT}$ 以由公式(数学式2)示出的形式来表达。

[0082] 【数学式2】

$$[0083] V_{OUT} = \sqrt{V_a^2 + V_b^2 + 2V_a V_b \cos(\theta_{RF} - \theta_\alpha)} \quad \cdots \text{ (数学式 2)}$$

[0084] 在 $V_{IN}$ 以及 $V_{OUT}$ 的每一个中, $\theta_{RF}$ 包含在 $\cos$ 之中,并且各自的 $\cos$ 项的 $\theta_a$ 的符号相反。这里,由于一般 $\theta_a$ 的值不是0,因此在中心侧的 $V_{PP}$ (=2 $V_{IN}$ )与外周侧的 $V_{PP}$ (=2 $V_{OUT}$ )之间产生差。

[0085] 图4示出通过电路模拟器而求出搭载于样品载置用电极107的晶片10的中心侧与外周侧之间的 $V_{PP}$ 的差的曲线图。在图4的曲线图400示出第一高频偏置电源121和第二高频偏置电源123的输出电压的差为0V时的数据410、为50V时的数据420、为90V时的数据430。

[0086] 根据图4所示的结果可知,第一高频偏置电源121和第二高频偏置电源123的输出电压的差为0V时的数据410与其他数据420以及430相比, $V_{PP}$ 相对于相位差的变化量较大。此外,在第一高频偏置电源121和第二高频偏置电源123的输出电压的差为0V时的数据410中,与相位差为0度的情况相比,相位差为135度时 $V_{PP}$ 的差变大。此外,电极间电路130的常数(原文:定数)(本实施例的情况是构成电极间电路130的线圈的电感)也可以是不固定的,在常数变更的情况下,施加至晶片的 $V_{PP}$ 差的分布就会与图4所示的结果不同。

[0087] 根据该结果可知,在图2以及图3所示那样的本实施例的高频偏置电力施加电路部120的结构中,通过由控制部150将第一高频偏置电源121和第二高频偏置电源123的输出电力的差以及相位差设定为合适的值,与不赋予相位差的情况相比较,能够增大晶片10的中心侧与外周侧之间的 $V_{PP}$ 差的调整幅度。

[0088] 根据本实施例,在高频电力施加电路间形成了电极间电路的状态下,控制第一高频偏置电源121和第二高频偏置电源123的相位差,对构成载置样品的样品台的内侧电极和外侧电极施加具有相位差的高频电力,由此能够控制分别施加至内侧电极和外侧电极的 $V_{PP}$ 的差。

[0089] 由此,即使不使用额定输出大的高频电源,也能够可靠地控制施加至内侧电极和

外侧电极的高频电力的输出差以及相位差,从而可靠地控制内侧电极和外侧电极的V<sub>PP</sub>的差。

[0090] 结果,根据本实施例,能够对载置在样品台的晶片的面内的V<sub>PP</sub>分布进行控制,能够使用额定输出比较小的多个高频偏置电源来改善从晶片的中心部到外周部的蚀刻速率的均匀性。

[0091] 由此,能够改善从晶片的中心部到外周部的蚀刻速率的均匀性,并且,通过使用比较小的额定输出的高频偏置电源,从而能够抑制等离子体处理装置的装置成本。

[0092] 【实施例2】

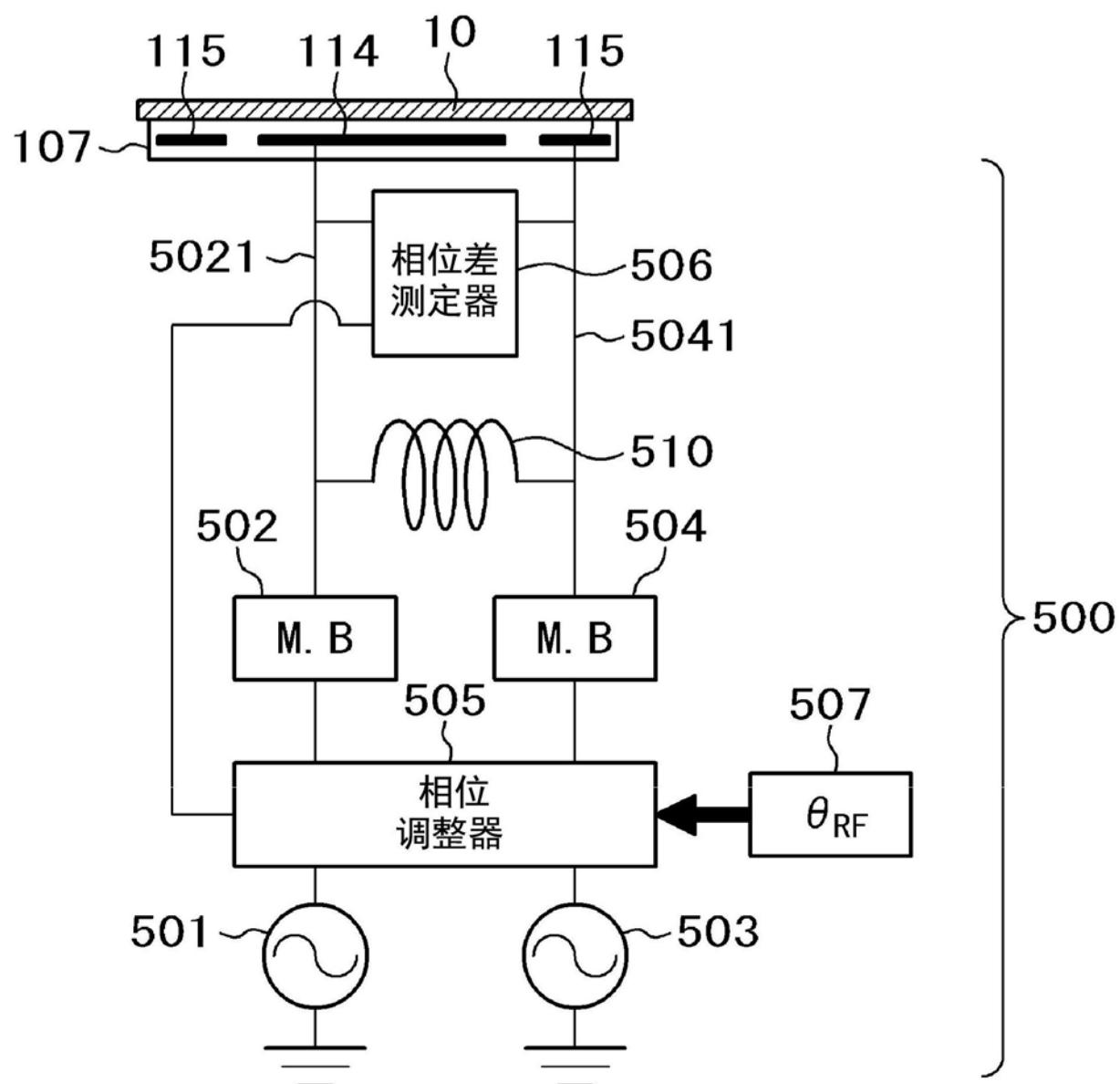

[0093] 使用图5说明本发明的第二实施例。本实施例将实施例1中的图1所示的蚀刻装置100中的高频偏置电力施加电路部120置换为图5所示的高频偏置电力施加电路部500。除了高频偏置电力施加电路部500以外,由于与实施例1相同的结构,故而省略图示以及重复的说明。

[0094] 图5所示的本实施例涉及的高频偏置电力施加电路部500对中心侧电极114与外周侧电极115之间的相位差进行测定,并能够自动地调整从两个偏置电源输出的高频电力的相位差。

[0095] 在图5所示的本实施例涉及的高频偏置电力施加电路部500中,构成为在第一高频偏置电源501与第一匹配电路502之间、以及第二高频偏置电源503与第二匹配电路504之间,连接相位调整器505。

[0096] 进而,在将第一匹配电路502和中心侧电极114相连的线路5021与将第二匹配电路504和外周侧电极115相连的线路5041之间,连接相位差测定器506。此外,在第一匹配电路502以及第二匹配电路504与相位差测定器506之间,设置将来自第一匹配电路502的输出和来自第二匹配电路504的输出连结的电极间电路510。

[0097] 接着,在图5所示的结构中,在实施例1中使用图1说明的在真空容器101的内部的样品载置用电极107载置了作为样品的晶片10的状态下,在真空容器101的内部产生等离子体,分别从第一高频偏置电源501和第二高频偏置电源503向样品载置用电极107的中心侧电极114和外周侧电极115施加高频偏置电力。

[0098] 在该状态下,通过相位差测定器506来测定施加至中心侧电极114的高频电力和施加至外周侧电极115的高频电力的相位差。将由该相位差测定器506测定的相位差的信号输入至相位调整器505。

[0099] 在相位调整器505中,对从相位差测定器506输入的相位差的信号与从相位差信号设定部507输入的相位差信号的设定值:θ<sub>RF</sub>进行比较,如在实施例1中使用图3说明的那样,对从第一高频偏置电源501输出的高频电力的相位和从第二高频偏置电源503输出的高频电力的相位进行调整,使得两者的相位差信号的差成为零。

[0100] 这样,根据本实施例,能够基于在蚀刻处理中检测出的由相位差测定器506测定的施加至中心侧电极114的高频电力与施加至外周侧电极115的高频电力的相位差的信息、以及与在相位差信号设定部507中预先设定的相位差信号的设定值θ<sub>RF</sub>之差,由相位调整器505对从第一高频偏置电源501输出的高频电力的相位与从第二高频偏置电源503输出的高频电力的相位之差进行调整。

[0101] 由此,在对晶片10进行蚀刻处理中,能够将施加至中心侧电极114的高频电力和施

加至外周侧电极115的高频电力的相位差维持为由相位差信号设定部507设定的值。

[0102] 结果,根据本实施例,能够在对载置于样品载置用电极的晶片进行蚀刻处理中,对晶片的面内的 $V_{PP}$ 分布进行控制,能够不需要额定输出比较大的高频偏置电源而使用额定输出比较小的多个高频偏置电源来改善从晶片的中心部到外周部的蚀刻速率的均匀性。

[0103] 由此,能够改善从晶片的中心部直至外周部的蚀刻速率的均匀性,并且,通过使用比较小的额定输出的高频偏置电源就能够抑制等离子体处理装置的装置成本。

[0104] 以上,基于实施例具体说明了由本发明者完成的发明,但是本发明并不限定于所述实施例,当然能够在不脱离其要旨的范围内进行各种变更。例如,上述的实施例是为了以容易理解本发明的方式来进行说明而详细说明的例子,不一定限定于具备所说明的全部结构。此外,针对各实施例的结构的一部分,也可以进行其他结构的追加、删除、置换。

100

冬 1

图2

图3

图4

图5