(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2017/048500 A1

(43) International Publication Date 23 March 2017 (23.03.2017)

(51) International Patent Classification: *H01P 7/06* (2006.01)

(21) International Application Number:

PCT/US2016/049440

(22) International Filing Date:

30 August 2016 (30.08.2016)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

14/853,802 14 September 2015 (14.09.2015)

5) US

- (71) Applicant: QUALCOMM INCORPORATED [US/US]; ATTN: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

- (72) Inventors: LEE, John, Jong-Hoon; 5775 Morehouse Drive, San Diego, California 92121 (US). SONG, Young, Kyu; 5775 Morehouse Drive, San Diego, California 92121 (US). JOW, Uei-Ming; 13015 Evening Creek Drive South, Unit 17, San Diego, California 92128 (US). CHOI, Sangjo; 5775 Morehouse Drive, San Diego, California 92121 (US). ZHANG, Xiaonan; 5775 Morehouse Drive, San Diego, California 92121 (US).

- (74) Agent: TERRANOVA, Steven, N.; Withrow & Terranova, PLLC, 106 Pinedale Springs Way, Cary, North Carolina 27511 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### Published:

— with international search report (Art. 21(3))

(54) Title: FLIP-CHIP EMPLOYING INTEGRATED CAVITY FILTER, AND RELATED COMPONENTS, SYSTEMS, AND METHODS

FIG. 1A

(57) Abstract: A flip-chip employing an integrated cavity filter is disclosed comprising an integrated circuit (IC) chip comprising a semiconductor die and a plurality of conductive bumps. The plurality of conductive bumps is interconnected to at least one metal layer of the semiconductor die to provide a conductive "fence" that defines an interior resonator cavity for providing an integrated cavity filter in the flip-chip. The interior resonator cavity is configured to receive an input RF signal from an input transmission line through an input signal transmission aperture provided in an internal layer in the semiconductor die. The interior resonator cavity resonates the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and couples the output RF signal on an output signal transmission line in the flip-chip through an output transmission aperture provided in the aperture layer.

# FLIP-CHIP EMPLOYING INTEGRATED CAVITY FILTER, AND RELATED COMPONENTS, SYSTEMS, AND METHODS

## **PRIORITY APPLICATION**

[0001] The present application claims priority to U.S. Patent Application Serial No. 14/853,802 filed on September 14, 2015 and entitled "FLIP-CHIP EMPLOYING INTEGRATED CAVITY FILTER, AND RELATED COMPONENTS, SYSTEMS, AND METHODS," which is incorporated herein by reference in its entirety.

#### **BACKGROUND**

#### I. Field of the Disclosure

[0002] The technology of the disclosure relates generally to structures and methods for filtering radio frequency (RF) signals, and more specifically to cavity filters for filtering RF signals.

## II. Background

[0003] Wireless computing devices have become common in contemporary society. These computing devices receive and/or transmit wireless signals, such as radiofrequency (RF) signals, and rely on microprocessors and other integrated circuits (ICs) for signal processing. In both mobile devices, like smart phones, and stationary computing devices, such as desktop computers, there is a general trend toward decreasing the size of such ICs. As device sizes decrease, the available space for individual components has also decreased. There is also a trend towards providing integrated circuits for mobile devices in a system-on-a-chip (SoC). An SoC is an integrated circuit (IC) that integrates components of a computer and other electronic systems into a single chip. The SoC may contain digital, analog, mixed-signal, and often radio-frequency functions all on a single chip substrate.

[0004] In many ICs including SoCs, RF filters are commonly used to pass and/or block specific frequencies or frequency bands in an RF signal or signals. For example, a signal of interest may be contained in a sixty (60) GigaHertz (GHz) band, but a device antenna may receive frequencies across a significantly larger portion of the RF spectrum. An appropriately configured RF filter can pass the band containing the signal

of interest while effectively rejecting or blocking other signals and noise contained in frequencies above and below the desired band. It is generally desirable that an RF filter pass as much of the signal in the desired pass frequency band as possible while also blocking as much of the outside spectrum as possible.

[0005] Different types of RF filters have varying filtering quality levels, referred to as a 'Q' factor (Q), which is inversely proportional to the fractional bandwidth. While it is generally desired to employ RF filters in circuits that have the highest 'Q' factor, different types of RF filters also have different drawbacks, which may affect the type of RF filter employed. For example, conventional waveguide-type filters have high-Q factor, but are relatively large in size, and therefore unsuitable for many ICs that require smaller component sizes. On the other hand, conventional microstrip-based filters are compact and easily integrated into silicon layers of a semiconductor component, but microstrip-based filters have relatively low-Q factor with relatively high signal loss. Microstrip-based filters may also be relatively difficult to isolate from nearby components, thus resulting in undesired coupling and interference with those components.

[0006] Another type of RF filter with a high-Q factor is a cavity filter. A cavity filter employs a resonator cavity that is tuned to the desired frequencies or frequency bands and able to pass those bands with low insertion loss and with high isolation from nearby components. However, if the cavity filter is desired to be employed in a circuit in a small package or application, such as a mobile application, there must be room to provide a resonator cavity. Further, the dimensions for the resonator cavity are tied to the desired frequency bands and therefore present additional design challenges for mobile applications and other applications where space and component sizes are limited.

#### **SUMMARY OF THE DISCLOSURE**

**[0007]** Aspects disclosed in the detailed description include a flip-chip employing an integrated cavity filter. Related components, systems, and methods are also disclosed. In one aspect, a flip-chip is provided that includes an integrated circuit (IC) chip comprising a semiconductor die and a plurality of conductive bumps. The semiconductor die comprises at least one semiconductor layer and a plurality of metal

layers for providing interconnections to the at least one semiconductor layer. plurality of conductive bumps is interconnected to at least one metal layer. The plurality of conductive bumps provides a conductive "fence" that defines an interior resonator cavity for providing an integrated cavity filter in the flip-chip. arrangement of package design allows the flip-chip be designed to include an integrated high-Q factor (Q) cavity filter with little or no increase in component size over a conventional flip-chip design. In this regard, interior resonator cavity is configured to receive an input RF signal from an input transmission line through an input signal transmission aperture provided in an internal layer in the flip-chip. The interior resonator cavity resonates the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and couples the output RF signal on an output signal transmission line in the flip-chip through an output transmission aperture provided in the aperture layer. The filtered RF signal can then be coupled through the metal layers to the internal circuitry in semiconductor layer(s) of the flipchip for processing. The flip-chip components can be customized in the design phase so that the conductive bumps define the internal resonator cavity having dimensions corresponding to a cavity filter designed to filter a RF signal in a predetermined frequency band.

[0008] In this regard, in one aspect, an integrated circuit (IC) chip is disclosed. The flip-chip IC comprises a semiconductor die. The semiconductor die comprises at least one semiconductor layer. The semiconductor layer further comprises a plurality of metal layers for providing interconnections to the at least one semiconductor layer. The semiconductor die further comprises an aperture layer comprising an input signal transmission aperture configured to pass an input radio frequency (RF) signal therethrough, and an output signal transmission aperture configured to pass an output RF signal therethrough. The semiconductor die further comprises at least one back endof-line interconnect layer disposed between the at least one semiconductor layer and the aperture layer. The at least one back end-of-line interconnect layer comprises an input transmission line configured to transmit the input RF signal through the input signal transmission aperture. The at least one back end-of-line interconnect layer further comprises an output transmission line configured to receive the output RF signal through the output signal transmission aperture. The flip-chip IC further comprises a

plurality of conductive bumps interconnected to at least one metal layer, the plurality of conductive bumps and the aperture layer defining an interior resonator cavity. The interior resonator cavity is configured to receive the input RF signal from the input transmission line through the input signal transmission aperture, resonate the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and couple the output RF signal on the output transmission line through the output signal transmission aperture.

[0009] In another aspect, an integrated circuit (IC) chip is disclosed. The flip-chip IC comprises a means for providing at least one semiconductor layer in a semiconductor die. The flip-chip IC further comprises a means for providing a plurality of metal layers for providing interconnections to the means for providing a semiconductor layer. The flip-chip IC further comprises a means for providing an aperture layer comprising an input signal transmission aperture configured to pass an input radio-frequency (RF) signal therethrough, and an output signal transmission aperture configured to pass an output RF signal therethrough. The flip-chip IC further comprises a means for providing at least one back end-of-line interconnect layer disposed between the at least one semiconductor layer and the aperture layer, the at least one back end-of-line interconnect layer. The at least one back end-of-line interconnect layer comprises an input transmission line configured to transmit the input RF signal through the input signal transmission aperture. The at least one back end-of-line interconnect layer further comprises an output transmission line configured to receive the output RF signal through the output signal transmission aperture. The flip-chip IC further comprises a means for providing a plurality of conductive connections interconnected to at least one metal layer. The flip-chip IC further comprises a means for providing an interior resonator cavity from the means for providing the plurality of conductive connections and the means for providing an aperture layer, for providing the interior resonator cavity for receiving the input RF signal from the input transmission line through the input signal transmission aperture, resonating the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and coupling the output RF signal on the output transmission line through the output signal transmission aperture.

[0010]In another aspect, a method of forming a flip-chip IC is disclosed. The method comprises providing at least one semiconductor layer. The method further comprises disposing a plurality of metal layers above the at least one semiconductor layer for providing interconnections to the at least one semiconductor layer. method further comprises disposing at least one back end-of-line interconnect layer above the plurality of metal layers. The at least one back end-of-line interconnect layer comprises an input transmission line configured to transmit an input RF signal. The at least one back end-of-line interconnect layer further comprises an output transmission line configured to receive an output RF signal. The method further comprises disposing an aperture layer above the at least one back end-of-line interconnect layer, the aperture layer comprising an input signal transmission aperture configured to pass the input RF signal therethrough, and an output signal transmission aperture configured to pass the output RF signal therethrough. The method further comprises disposing a plurality of conductive bumps above the aperture layer, the plurality of conductive bumps interconnected to at least one metal layer, the plurality of conductive bumps and the aperture layer defining an interior resonator cavity. The interior resonator cavity is configured to receive the input RF signal from the input transmission line through the input signal transmission aperture, resonate the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and couple the output RF signal on the output transmission line through the output signal transmission aperture.

[0011] In another aspect, a flip-chip system having an integrated cavity filter is disclosed. The flip-chip system comprises a flip-chip IC. The flip-chip IC comprises a semiconductor die. The semiconductor die comprises at least one semiconductor layer. The semiconductor die further comprises a plurality of metal layers for providing interconnections to the at least one semiconductor layer. The semiconductor die further comprises an aperture layer comprising an input signal transmission aperture configured to pass an input RF signal therethrough, and an output signal transmission aperture configured to pass an output RF signal therethrough. The semiconductor die further comprises at least one back end-of-line interconnect layer disposed between the at least one semiconductor layer and the aperture layer. The at least one back end-of-line interconnect layer comprises an input transmission line configured to transmit the input

RF signal through the input signal transmission aperture. The at least one back end-ofline interconnect layer further comprises an output transmission line configured to

receive the output RF signal through the output signal transmission aperture. The flipchip system further comprises a plurality of conductive bumps interconnected to at least

one metal layer. The flip-chip system further comprises an external circuit

interconnected to the plurality of conductive bumps. The flip-chip system further

comprises an external circuit interconnected to the plurality of conductive bumps, the

plurality of conductive bumps, the aperture layer, and at least a portion of the external

circuit defining an interior resonator cavity. The interior resonator cavity is configured

to receive the input RF signal from the input transmission line through the input signal

transmission aperture, resonate the input RF signal to generate the output RF signal

comprising a filtered RF signal of the input RF signal, and couple the output RF signal

on the output transmission line through the output signal transmission aperture

## **BRIEF DESCRIPTION OF THE FIGURES**

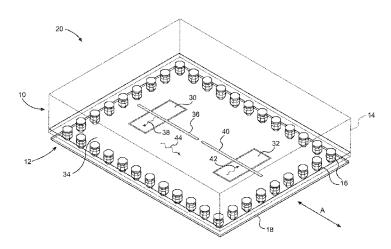

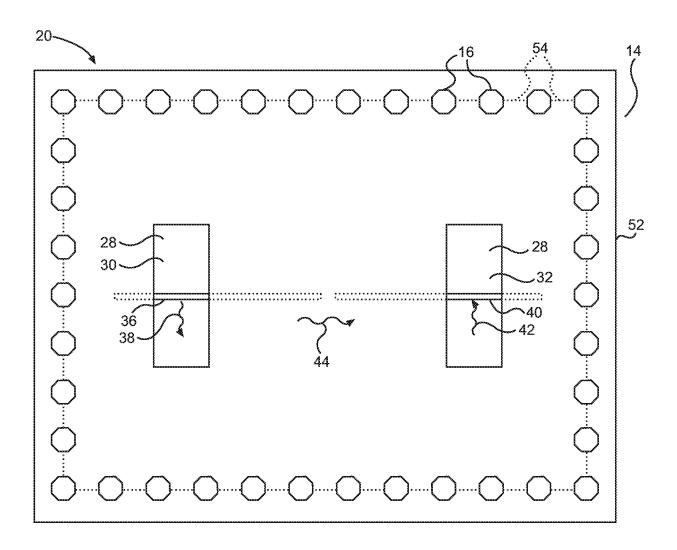

**[0012]** Figure 1A illustrates a perspective view of an exemplary flip-chip integrated circuit (IC) having an integrated cavity filter provided by a plurality of conductive bumps of the flip-chip forming a cavity between opposing surfaces of a silicon die and a semiconductor package;

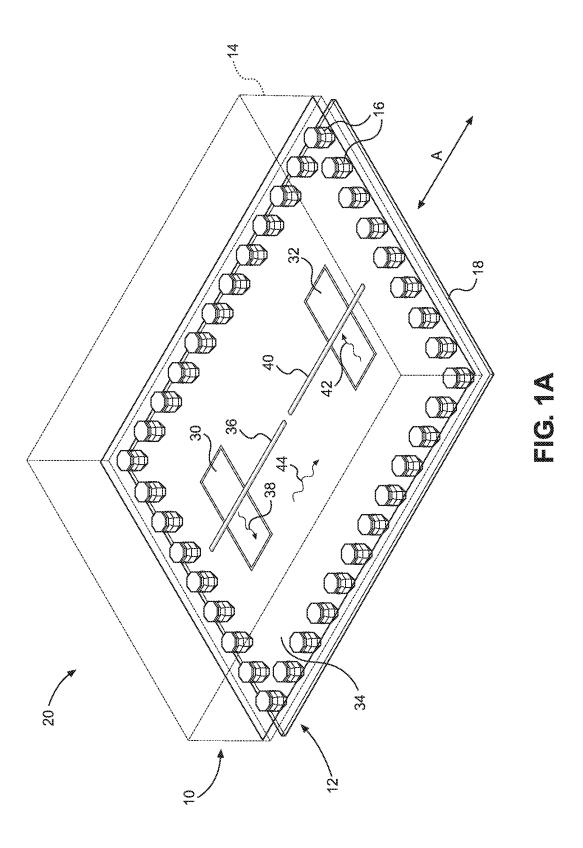

[0013] Figure 1B illustrates a side cross-sectional view of a portion of the flip-chip IC having the integrated cavity filter in Figure 1A, and further illustrating an exemplary location of the transmission lines and apertures within the layers of the semiconductor die;

[0014] Figure 1C illustrates a top cross-sectional view of the flip-chip IC of Figure 1A prior to mounting the flip-chip IC on an external circuit, illustrating input and output transmission lines and respective apertures for allowing the transmission lines to filter an RF signal through the resonator cavity;

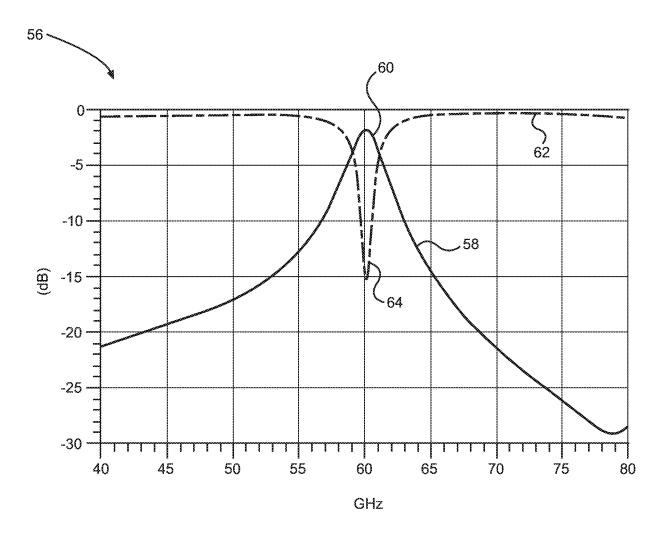

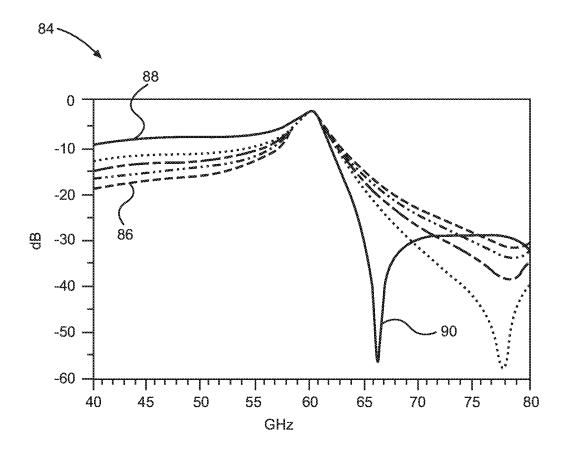

[0015] Figure 2 is a graph illustrating an exemplary frequency response for the flipchip IC having the integrated cavity filter of Figures 1A-1C, tuned to pass radio frequency (RF) signals in a sixty (60) GigaHertz (GHz) band;

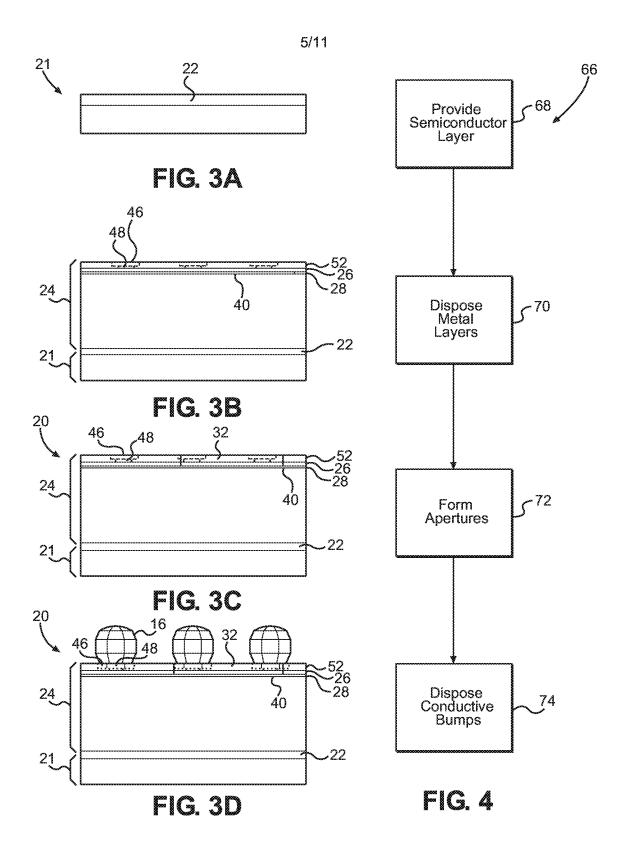

[0016] Figures 3A-3D illustrate exemplary fabrication stages for fabricating the flipchip IC of Figures 1A-1C;

[0017] Figure 4 is a flowchart describing exemplary process steps for performing the IC fabrication stages in Figures 3A-3D for fabricating the flip-chip IC of Figures 1A-1C:

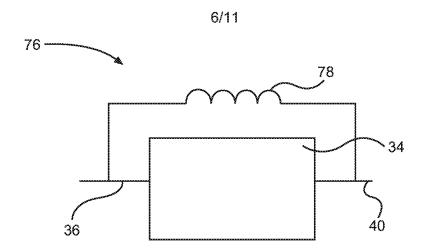

[0018] Figure 5A illustrates a schematic diagram of another exemplary flip-chip IC having an integrated cavity filter that additionally includes an inductance blocker coupled between the input and output transmission lines of the integrated cavity filter;

[0019] Figure 5B is a graph of an exemplary frequency response of the flip-chip IC of Figure 5A having the integrated cavity filter with the inductance blocker of Figure 5A;

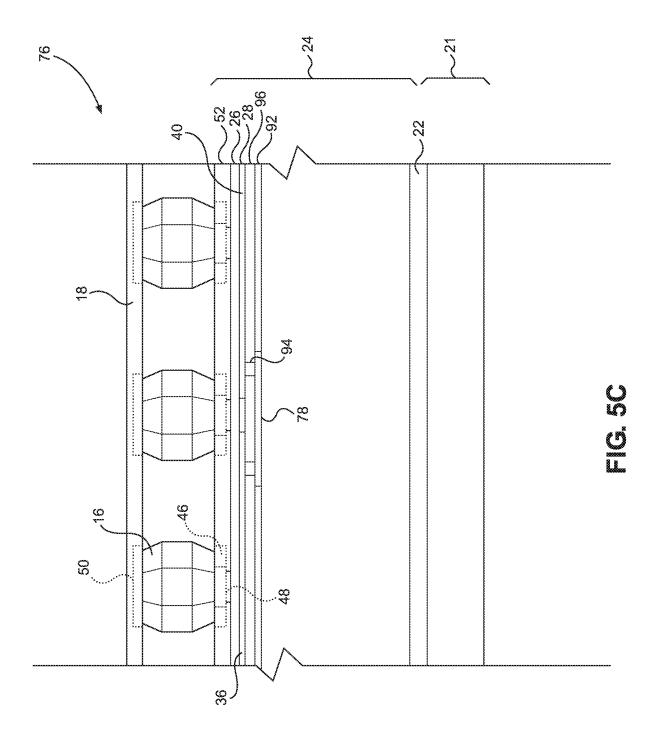

[0020] Figure 5C illustrates a partial side cross-sectional view of the flip-chip IC of Figure 5A having the integrated cavity filter with the inductance blocker of Figure 5A;

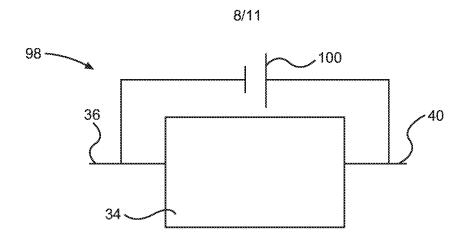

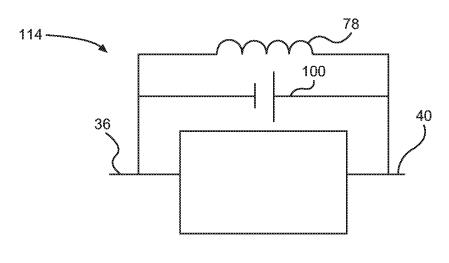

[0021] Figure 6A illustrate a schematic diagram of another exemplary IC flip-chip having an integrated cavity filter that additionally includes a capacitance blocker coupled between the input and output transmission lines of the integrated cavity filter;

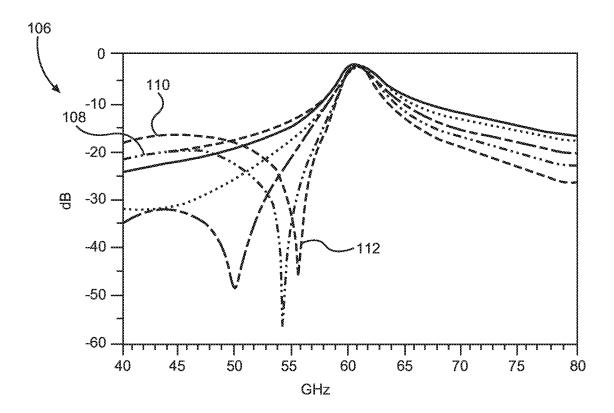

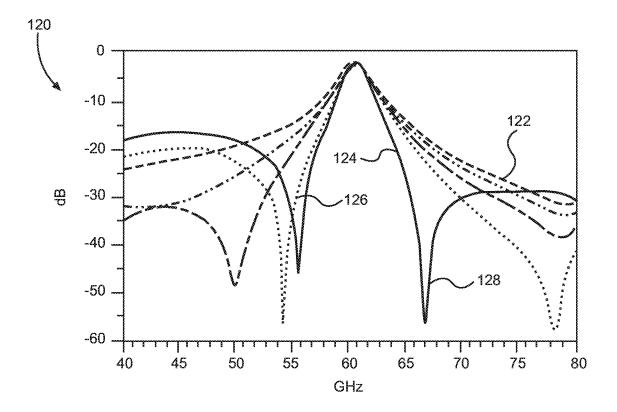

[0022] Figure 6B is a graph of an exemplary frequency response for the IC flip-chip of Figure 6A having the integrated cavity filter with the capacitance blocker of Figure 6A;

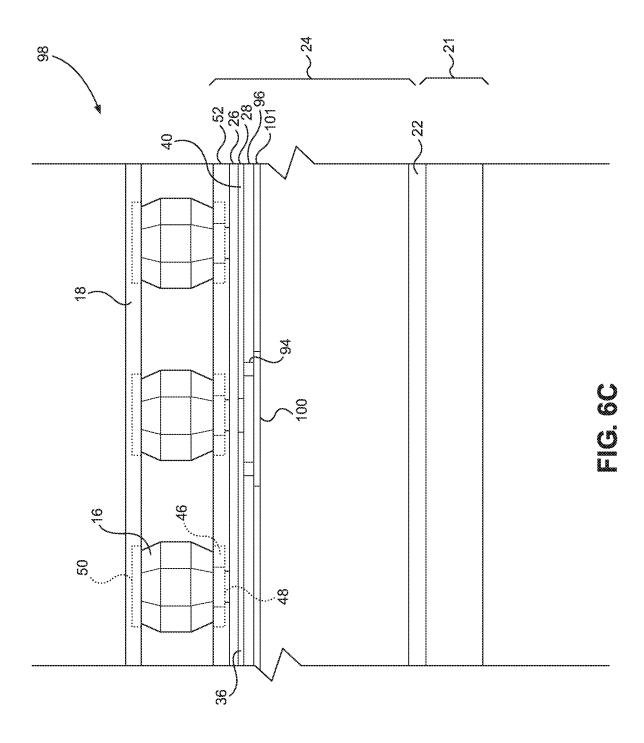

[0023] Figure 6C illustrates a partial side cross-sectional view of the IC flip-chip of Figure 6A having the integrated cavity filter with the capacitance blocker of Figure 6A;

**[0024]** Figure 7A illustrates a schematic diagram of another exemplary IC flip-chip having an integrated cavity filter that additionally includes an inductance blocker and a capacitance blocker coupled between the input and output transmission lines of the integrated cavity filter;

[0025] Figure 7B illustrates a frequency response graph for the flip-chip of Figure 7A having a cavity filter with the inductance and capacitance blockers of Figure 7A; and

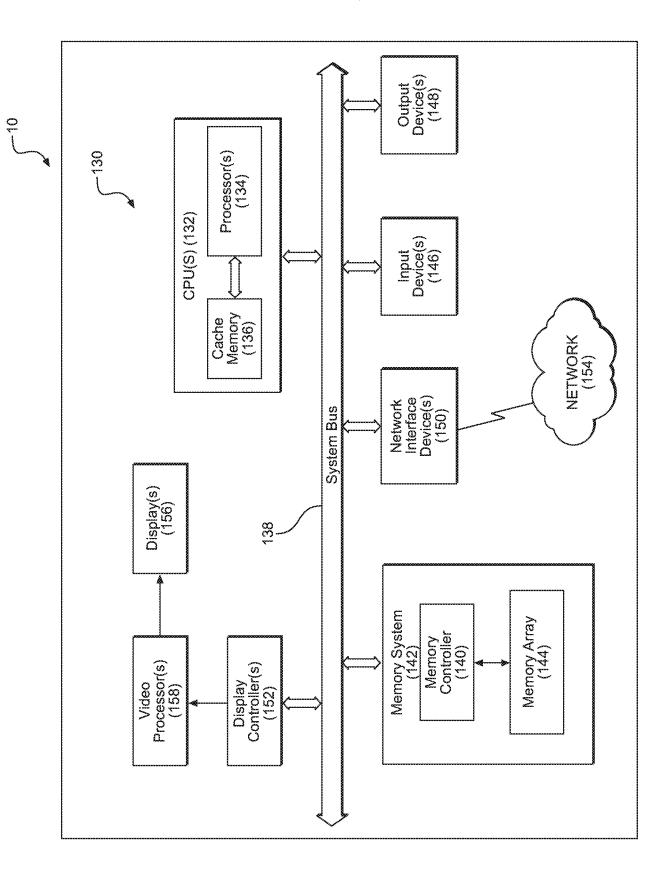

[0026] Figure 8 is a block diagram of an exemplary processor-based system-on-a-chip (SoC) that can be contained in the flip-chip IC with an integrated cavity filter according to any of the aspects disclosed herein.

## **DETAILED DESCRIPTION**

[0027] With reference now to the drawing figures, several exemplary aspects of the present disclosure are described. The word "exemplary" is used herein to mean "serving as an example, instance, or illustration." Any aspect described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other aspects.

[0028] Aspects disclosed in the detailed description include a flip-chip employing an integrated cavity filter. Related components, systems, and methods are also disclosed. In one aspect, a flip-chip is provided that includes an integrated circuit (IC) chip comprising a semiconductor die and a plurality of conductive bumps. semiconductor die comprises at least one semiconductor layer and a plurality of metal layers for providing interconnections to the at least one semiconductor layer. plurality of conductive bumps is interconnected to at least one metal layer. The plurality of conductive bumps provides a conductive "fence" that defines an interior resonator cavity for providing an integrated cavity filter in the flip-chip. arrangement of package design allows the flip-chip be designed to include an integrated high-Q factor (Q) cavity filter with little or no increase in component size over a conventional flip-chip design. In this regard, interior resonator cavity is configured to receive an input RF signal from an input transmission line through an input signal transmission aperture provided in an internal layer in the flip-chip. The interior resonator cavity resonates the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and couples the output RF signal on an output signal transmission line in the flip-chip through an output transmission aperture provided in the aperture layer. The filtered RF signal can then be coupled through the metal layers to the internal circuitry in semiconductor layer(s) of the flipchip for processing. The flip-chip components can be customized in the design phase so that the conductive bumps define the internal resonator cavity having dimensions corresponding to a cavity filter designed to filter a RF signal in a predetermined frequency band.

[0029] In this regard, Figures 1A-1C illustrate a flip-chip integrated circuit (IC) 10 having an integrated cavity filter 12 according to one aspect of the disclosure. The flip-chip IC 10 comprises a semiconductor die 14 and a plurality of conductive bumps 16

interconnecting the flip-chip IC 10 to an external circuit 18. The plurality of conductive bumps 16 forms a flip-chip assembly 20. As used herein, the term "flip-chip" refers to a flip-chip IC employing a controller collapse chip connection (C4), a well-known technique for interconnecting semiconductors to external circuitry. In a flip-chip arrangement, a semiconductor package includes a plurality of metal pads or contacts, with a conductive bump, which is typically a solder bump or solder ball deposited on each pad. The package is then "flipped" so that the conductive bumps are face down, and the package is aligned with respect to an external circuit 18 having complementary pads or contacts corresponding to each of the solder bumps. The solder bumps are then reflowed to complete the interconnect.

**[0030]** With continuing reference to Figure 1A, the semiconductor die 14 comprises a silicon layer 21 having a semiconductor layer 22 and a plurality of metal interconnect layers 24 (see Figure 1B) for providing interconnections to the semiconductor layer 22 and the conductive bumps 16. The semiconductor die 14 also comprises an aperture layer 26 and a back end-of-line interconnect layer 28, which is disposed between the semiconductor layer 22 and the aperture layer 26.

[0031] As discussed in more detail below, the plurality of conductive bumps 16 in the flip-chip IC 10 in Figure 1 are used to provide a conductive "fence" that provides an integrated interior resonator cavity 34 for an integrated cavity filter 12. This allows the integrated cavity filter 12 to be provided in the flip-chip IC 10 with little or no increase in component size over a conventional flip-chip design, and without the need for a separate component to provide high-Q filtering. However, to provide the integrated cavity filter 12 employing the interior resonator cavity 34, a method of directing an input RF signal into the interior resonator cavity 34 to be filtered into a filtered output RF signal to be coupled to a metal layer(s) to be interconnected to a semiconductor layer in the flip-chip IC for signal processing is provided.

[0032] In this regard, the flip-chip IC 10 in Figure 1A includes an aperture layer 26. The aperture layer 26 comprises an input signal transmission aperture 30 and an output signal transmission aperture 32. The aperture layer 26 and the conductive bumps 16 together define an interior resonator cavity 34. By interconnecting the conductive bumps 16 with the external circuit 18, the interior resonator cavity 34 is fully enclosed.

[0033] To use the interior resonator cavity 34 provided in the flip-chip IC to provide integrated cavity filter 12 in this example, an input transmission line 36 and an output transmission line 40 are provided in the back end-of-line interconnect layer 28. The input transmission line 36 is configured to transmit an input RF signal 38 into the interior resonator cavity 34 through the input signal transmission aperture 30. The output transmission line 40 is configured to receive an output RF signal 42 through the output signal transmission aperture 32. The interior resonator cavity 34 is configured to receive the input RF signal 38 from the input transmission line 36 through the input signal transmission aperture 30, resonate the input RF signal 38 to generate the output RF signal 42 comprising a filtered RF signal 44 of the input RF signal 38, and couple the output RF signal 42 on the output transmission line 40 through the output signal transmission aperture 32. By customizing the dimensions of the interior resonator cavity 34 in the design phase, the interior resonator cavity 34 can be tuned to resonate at a predetermined center frequency, thereby allowing the interior resonator cavity 34 to function as the integrated cavity filter 12 for the predetermined frequency band. In this manner, a package design employing a flip-chip technique can be designed to also include a high-Q cavity filter with little or no increase in component size over a conventional flip-chip design.

[0034] Existing flip-chip techniques can be easily adapted to include an integrated cavity filter, because these conventional techniques typically results in a gap between opposing metal layers of the semiconductor package and the external circuit. By arranging the conductive bumps, such as the conductive bumps 16 of Figures 1A-1C, sufficiently close to each other to enclose a portion of the gap, the conductive bumps 16 and opposing metal layers will act as a faraday cage around the enclosed portion, e.g., the interior resonator cavity 34 of Figures 1A-1C. Within the interior space defined by the enclosed portion, external electromagnetic (EM) radiation, including external RF signals, are blocked from entering. In addition, any RF signals inside the interior cavity are confined therein, with the interior cavity functioning as a resonator cavity with respect to the RF signals. Thus, by designing the dimensions of the cavity to define a desired resonant frequency, the cavity can be used as a cavity filter. This allows any package design employing a flip-chip technique to also include a high-Q cavity filter with little or no increase in component size.

[0035] In this regard, Figure 1B illustrates a side cross-sectional view of two portions of the flip-chip having the integrated cavity filter 12 of Figure 1A, taken along the vertical plane containing axis A. In particular, the left portion of Figure 1B illustrates the center of the flip-chip IC 10, including the input transmission line 36 and the output transmission line 40. The right portion of Figure 1B illustrates the output transmission line 40 and the output signal transmission aperture 32. As discussed above, the metal interconnect layers 24 include the aperture layer 26 and the back endof-line interconnect layer 28, and the input transmission line 36 and output transmission line 40 may be interconnected with the metal interconnect layers 24 to interconnect with the semiconductor layer 22 and/or one or more conductive bumps 16. In this aspect, the aperture layer 26 and the back end-of-line interconnect layer 28 are adjacent to each other such that a portion of the input transmission line 36 is adjacent to the input signal transmission aperture 30 (not shown) and the output transmission line 40 is adjacent to the output signal transmission aperture 32. In this aspect as well, top layers 46 are disposed between the aperture layer 26 and the conductive bumps 16. The top layers 46 also include conductive contacts 48 and metal interconnects 50, which interconnect with the aperture layer 26 and other metal interconnect layers 24.

[0036] In this aspect, the aperture layer 26 and top layers 46 may be considered to be a single layer for the purposes of defining the interior resonator cavity 34. In this regard, the aperture layer 26, the back end-of-line interconnect layer 28, and the top layers 46 may be considered to be included among the metal interconnect layers 24. In this aspect, the input signal transmission aperture 30 and output signal transmission aperture 32 extend through the top layers 46 as well as the aperture layer 26. In this manner, the input transmission line 36 and output transmission line 40 are able transmit and receive signals, such as input RF signal 38 and output RF signal 42, into and out of the interior resonator cavity 34. In another aspect, the top layers 46 may be instead formed from a non-metal material, such as a material that is transparent to radio frequencies, such that the dimensions of the interior resonator cavity 34 are defined by the aperture layer 26 rather than the combination of the aperture layer 26 and the top layers 46. In both aspects, the interior resonator cavity 34 is defined by a metal layer defining at least one dimension of the interior resonator cavity 34, and by the

electromagnetic fence 54 formed by the conductive bumps 16. To enclose the interior resonator cavity 34, the conductive bumps 16 interconnect to the external circuit 18.

[0037] In this regard, as shown in Figure 1B, the conductive bumps 16, such as solder balls, for example, interconnect the conductive contacts 48 of the flip-chip IC 10 with conductive pads 52 formed as part of the external circuit 18. In this aspect, the external circuit 18 is a printed circuit board (PCB), but it should be understood that other types of external circuits may be used. Here, the external circuit 18 defines the opposite boundary of interior resonator cavity 34.

[0038] As shown in Figure 1B, gaps exist between the individual conductive bumps 16 at the horizontal boundaries of the interior resonator cavity 34. However, the conductive bumps 16 are arranged such that the conductive bumps 16, the external circuit 18, and the aperture layer 26 (or a combination of the aperture layer 26 and the top layers 46) form a faraday cage around the interior resonator cavity 34. In this regard, Figure 1C illustrates a top view of the flip-chip IC 10 of Figure 1A prior to mounting the flip-chip IC 10 on the external circuit 18. Here, the conductive bumps 16 are arranged such that the conductive bumps 16 form an electromagnetic "fence" 54 around the interior resonator cavity 34. In this manner, the electromagnetic fence 54 keeps out unwanted electromagnetic radiation that may interfere with the input RF signal 38, the output RF signal 42, or the filtered RF signal 44, and also forms the interior resonator cavity 34 that is effectively closed with respect to the RF frequencies of the input RF signal 38, the output RF signal 42, and the filtered RF signal 44. As discussed above, the interior resonator cavity 34 is effectively closed with respect to these RF signals 38, 42, 44, when the input RF signal 38 is introduced into the interior resonator cavity 34 through the input signal transmission aperture 30. As a result, the input RF signal 38 is resonated by the interior resonator cavity 34 to generate the filtered RF signal 44, which is output to the output transmission line 40 through the output signal transmission aperture 32 as part of output RF signal 42.

[0039] The filtered RF signal 44 is tied to the dimensions of the interior resonator cavity 34, which determines which frequencies of the input RF signal 38 are resonated by the interior resonator cavity 34. In this regard, the dimensions of interior resonator cavity 34 may be customized, or "tuned," to resonate RF frequencies within a predetermined frequency band. For example, in the aspect of Figures 1A-1C, the

interior resonator cavity 34 has a substantially rectangular cross-section in a plane parallel to the aperture layer 26, and is dimensioned to correspond to a predetermined RF frequency band. In this aspect, for example, the predetermined RF frequency band has a center frequency of sixty (60) GigaHertz (GHz) by having a width dimension corresponding to 1/2 of a fundamental mode of the center frequency (i.e., 60GHz) of the predetermined frequency band. In this manner, the interior resonator cavity 34 is configured to resonate frequencies of the input RF signal 38 in the predetermined frequency band to generate the filtered RF signal 44.

[0040] In this regard, Figure 2 illustrates a graph 56 showing frequency response for the integrated cavity filter 12 according to Figures 1A-1C, tuned to pass RF signals in the 60 GHz band. As shown by graph 56, a plot 58 of insertion loss for the filtered RF signal 44 (not shown) with respect to the input RF signal 38 shows that the frequencies outside the 60 GHz band are significantly attenuated by the interior resonator cavity 34 (not shown), while frequencies around the 60 GHz center frequency 60 are minimally attenuated, with insertion loss at 60 GHz being approximately 1.86 decibels (dB) in this example. In addition, a plot 62 of return loss shows that the return loss around the 60 GHz center frequency 64, approximately 15.4 dB. In this example, the 3 dB bandwidth for the integrated cavity filter 12 approximately 2.62 dB. In this regard, the interior resonator cavity 34 results in the integrated cavity filter 12 having low insertion loss and return loss, with little or no increase in size for the flip-chip assembly 20 (not shown).

[0041] In addition to the size benefits of using a flip-chip IC 10 with an integrated cavity filter 12, fabrication of the flip-chip IC 10 may also be achieved with only minimal changes to existing fabrication processes. In this regard, referring now to Figures 3A-3D, exemplary fabrication stages for fabricating the flip-chip IC 10 of Figures 1A-1C are illustrated. In this regard as well, Figure 4 illustrates a flowchart 66 setting out exemplary method steps corresponding to the illustrated process steps of Figures 3A-3D. Referring now to Figure 3A, the semiconductor layer 22 is first provided in the silicon layer 21 or other substrate (block 68 of Figure 4). Next, as shown by Figure 3B, the plurality of metal interconnect layers 24 are disposed over the semiconductor layer 22 (block 70 of Figure 4) according to the design parameters of the flip-chip IC 10. In addition to the interconnects for the flip-chip IC 10 (not shown), this process step includes providing the input transmission line 36 and output transmission

line 40 (not shown) in the back end-of-line interconnect layer 28, providing the aperture layer 26 over the back end-of-line interconnect layer 28, and disposing the top layers 46, including the conductive contacts 48 and metal interconnects 50, over the aperture layer 26. Next the input signal transmission aperture 30 (not shown) and the output signal transmission aperture 32 are formed in the aperture layer 26 and top layers 46 (block 72 of Figure 4) to expose the input transmission line 36 and output transmission line 40 (not shown) at the back end-of-line interconnect layer 28. Finally, as shown in Figure 3D, the conductive bumps 16 are disposed on the respective metal interconnects 50 (block 74 of Figure 4). In this matter, the flip-chip IC 10 is now ready to be interconnected with an external circuit, such as external circuit 18.

[0042] It may also be advantageous to include additional components, such as inductance and/or capacitance blockers, in the flip-chip arrangement to improve and enhance the functionality of the integrated cavity filter 12. In this regard, Figure 5A illustrates a schematic diagram of a flip-chip IC 76 having the interior resonator cavity 34 according to the aspect of Figures 1A-1C, and also having an inductor 78 interconnected between the input transmission line 36 and output transmission line 40. As shown by the graph 84 of Figure 5B, the inductor 78 or inductive material operates as an inductance blocker, to increase the rejection of frequencies above the center frequency of the predetermined frequency band. Comparing plot 86, which represents the flip-chip IC 76 without the inductor 78, with plot 88, which represents the flip-chip IC 76 with the inductor 78 included, shows that adding the inductor 78 moves an upper transmission zero 90 of a filtered signal significantly closer to the center frequency, 60 GHz in this example, thereby increasing the filtering quality of the integrated cavity filter 12 of the flip-chip IC 76.

[0043] The inductor 78 may be included as a separate component, or may be included as part of the flip-chip IC 76. In this regard, Figure 5C illustrates a partial side cross-sectional view of the flip-chip IC 76 of Figure 5A showing the inductor 78 included in one of the metal interconnect layers 24, such as inductor layer 92 of the flip-chip IC 76. The inductor 78 is interconnected with the input transmission line 36 and output transmission line 40 via interconnects 94. The interconnects 94 are disposed in intervening interconnection layers 96 disposed between the inductor layer 92 and the back end-of-line interconnect layer 28. It should be understood, however, that

inductance may be provided in other ways as well, such as by an inductive component connected to the input transmission line 36 and output transmission line 40 via the external circuit 18, for example.

[0044] In another aspect, a capacitance blocker may also be used to improve the performance of the integrated cavity filter. In this regard, Figure 6A illustrates an alternative flip-chip IC 98 having a capacitor 100 disposed between the input transmission line 36 and output transmission line 40. Similar to the aspect of Figures 5A-5C, the capacitor 100 acts to attenuate frequencies closer to the center frequency, 60 GHz, in this example. Here, however, the capacitor 100 attenuates frequencies below the center frequency, as shown by graph 106 of Figure 6B. Here, graph 106 illustrates a plot 108 corresponding to the flip-chip IC 98 without the capacitor 100 interconnecting the input transmission line 36 and output transmission line 40, and plot 110 representing the flip-chip IC 98 with the capacitor 100 included. As can be seen by Figure 6B, the capacitor 100 causes a lower transmission zero 112 to be significantly closer to the center frequency of the desired frequency band, thereby improving performance of the integrated cavity filter 12.

[0045] As with the inductor 78 of Figures 5A-5C, the capacitor 100 of Figures 6A may also be included as a separate component, or may be included as part of the flip-chip IC 98. In this regard, Figure 6C illustrates the capacitor 100 included in one of the metal interconnect layers 24 of the flip-chip IC 98, such as capacitor layer 101, similar to the inductor 78 of Figure 5C. In Figure 6C, the capacitor 100 is interconnected with the input transmission line 36 and output transmission line 40 via interconnects 94. The interconnects 94 are disposed in intervening interconnection layers 96 disposed between the capacitor layer 101 and the back end-of-line interconnect layer 28. It should be understood, however, that capacitance may be provided in other ways as well, such as by a capacitive component connected to the input transmission line 36 and output transmission line 40 via the external circuit 18 for example.

**[0046]** The aspects of Figures 5A-5C and 6A-6C may also be combined to include an inductance blocker and capacitance blocker connected in parallel to better attenuate frequencies on either side of the frequency band. In this regard, Figure 7A illustrates an alternative flip-chip IC 114 having both the inductor 78 and the capacitor 100 connected in parallel between the input transmission line 36 and output transmission line 40. As

shown by graph 120 in Figure 7B, comparing the plot 122, which represents the flip-chip IC 114 without the inductor 78 or capacitor 100 included, plot 124, which represents the flip-chip IC 114 with both the inductor 78 and capacitor 100 connected in parallel between the input transmission line 36 and output transmission line 40, shows that frequencies nearer to the center frequencies are attenuated to a greater degree. Here, the lower transmission zero 126 below the center frequency and the upper transmission zero 128 above the center frequency are both nearer to the center frequency of the desired frequency band than using the interior resonator cavity 34 alone.

[0047] The aspects disclosed herein may be provided in or integrated into any processor-based device. Examples, without limitation, include a set top box, an entertainment unit, a navigation device, a communications device, a fixed location data unit, a mobile location data unit, a mobile phone, a cellular phone, a smart phone, a tablet, a phablet, a computer, a portable computer, a desktop computer, a personal digital assistant (PDA), a monitor, a computer monitor, a television, a tuner, a radio, a satellite radio, a music player, a digital music player, a portable music player, a digital video player, a video player, a digital video disc (DVD) player, a portable digital video player, and an automobile.

[0048] In this regard, Figure 8 is a block diagram of an exemplary processor-based system-on-a-chip (SoC) that can be contained in the flip-chip IC 10 with an integrated cavity filter according to any of the aspects disclosed herein. As used herein, the term "system-on-a-chip (SoC)" refers to a plurality of functional elements contained on a single chip, such as the flip-chip IC 10, the plurality of functional elements being configured to interoperate in a self-contained manner. In this example, the processor-based system 130 includes one or more central processing units (CPUs) 132, each including one or more processors 134. The CPU(s) 132 may have cache memory 136 coupled to the processor(s) 134 for rapid access to temporarily stored data. The CPU(s) 132 is coupled to a system bus 138 and can intercouple master and slave devices included in the processor-based system 130. As is well known, the CPU(s) 132 communicates with these other devices by exchanging address, control, and data information over the system bus 138. For example, the CPU(s) 132 can communicate bus transaction requests to a memory controller 140 in a memory system 142 as an

example of a slave device. Although not illustrated in Figure 8, multiple system buses 138 could be provided, wherein each system bus 138 constitutes a different fabric. In this example, the memory controller 140 is configured to provide memory access requests to a memory array 144 in the memory system 142.

[0049] Other devices can be connected to the system bus 138. As illustrated in Figure 8, these devices can include the memory system 142, one or more input devices 146, one or more output devices 148, one or more network interface devices 150, and one or more display controllers 152, as examples. The input device(s) 146 can include any type of input device, including but not limited to input keys, switches, voice processors, etc. The output device(s) 148 can include any type of output device, including but not limited to audio, video, other visual indicators, etc. The network interface device(s) 150 can be any devices configured to allow exchange of data to and from a network 154. The network 154 can be any type of network, including but not limited to a wired or wireless network, a private or public network, a local area network (LAN), a wide local area network (WLAN), and the Internet. The network interface device(s) 150 can be configured to support any type of communications protocol desired.

[0050] The CPU(s) 132 may also be configured to access the display controller(s) 152 over the system bus 138 to control information sent to one or more displays 156. The display controller(s) 152 sends information to the display(s) 156 to be displayed via one or more video processors 158, which process the information to be displayed into a format suitable for the display(s) 156. The display(s) 156 can include any type of display, including but not limited to a cathode ray tube (CRT), a liquid crystal display (LCD), a plasma display, etc.

[0051] Those of skill in the art will further appreciate that the various illustrative logical blocks, modules, circuits, and algorithms described in connection with the aspects disclosed herein may be implemented as electronic hardware, instructions stored in memory or in another computer readable medium and executed by a processor or other processing device, or combinations of both. The devices described herein may be employed in any circuit, hardware component, IC, or flip-chip IC, as examples. Memory disclosed herein may be any type and size of memory and may be configured to store any type of information desired. To clearly illustrate this interchangeability,

various illustrative components, blocks, modules, circuits, and steps have been described above generally in terms of their functionality. How such functionality is implemented depends upon the particular application, design choices, and/or design constraints imposed on the overall system. Skilled artisans may implement the described functionality in varying ways for each particular application, but such implementation decisions should not be interpreted as causing a departure from the scope of the present disclosure.

[0052] The various illustrative logical blocks, modules, and circuits described in connection with the aspects disclosed herein may be implemented or performed with a processor, a Digital Signal Processor (DSP), an Application Specific Integrated Circuit (ASIC), a Field Programmable Gate Array (FPGA) or other programmable logic device, discrete gate or transistor logic, discrete hardware components, or any combination thereof designed to perform the functions described herein. A processor may be a microprocessor, but in the alternative, the processor may be any conventional processor, controller, microcontroller, or state machine. A processor may also be implemented as a combination of computing devices (e.g., a combination of a DSP and a microprocessor, a plurality of microprocessors, one or more microprocessors in conjunction with a DSP core, or any other such configuration).

[0053] The aspects disclosed herein may be embodied in hardware and in instructions that are stored in hardware, and may reside, for example, in Random Access Memory (RAM), flash memory, Read Only Memory (ROM), Electrically Programmable ROM (EPROM), Electrically Erasable Programmable ROM (EEPROM), registers, a hard disk, a removable disk, a CD-ROM, or any other form of computer readable medium known in the art. An exemplary storage medium is coupled to the processor such that the processor can read information from, and write information to, the storage medium. In the alternative, the storage medium may be integral to the processor. The processor and the storage medium may reside in a remote station. In the alternative, the processor and the storage medium may reside as discrete components in a remote station, base station, or server.

[0054] It is also noted that the operational steps described in any of the exemplary aspects herein are described to provide examples and discussion. The operations

described may be performed in numerous different sequences other than the illustrated sequences. Furthermore, operations described in a single operational step may actually be performed in a number of different steps. Additionally, one or more operational steps discussed in the exemplary aspects may be combined. It is to be understood that the operational steps illustrated in the flowchart diagrams may be subject to numerous different modifications as will be readily apparent to one of skill in the art. Those of skill in the art will also understand that information and signals may be represented using any of a variety of different technologies and techniques. For example, data, instructions, commands, information, signals, bits, symbols, and chips that may be referenced throughout the above description may be represented by voltages, currents, electromagnetic waves, magnetic fields or particles, optical fields or particles, or any combination thereof.

[0055] The previous description of the disclosure is provided to enable any person skilled in the art to make or use the disclosure. Various modifications to the disclosure will be readily apparent to those skilled in the art, and the generic principles defined herein may be applied to other variations without departing from the spirit or scope of the disclosure. Thus, the disclosure is not intended to be limited to the examples and designs described herein, but is to be accorded the widest scope consistent with the principles and novel features disclosed herein.

#### What is claimed is:

- 1. A flip-chip integrated circuit (IC) comprising:

- a semiconductor die, comprising:

- at least one semiconductor layer;

- a plurality of metal layers for providing interconnections to the at least one semiconductor layer;

- an aperture layer comprising an input signal transmission aperture configured to pass an input radio-frequency (RF) signal therethrough, and an output signal transmission aperture configured to pass an output RF signal therethrough; and

- at least one back end-of-line interconnect layer disposed between the at least one semiconductor layer and the aperture layer, the at least one back end-of-line interconnect layer, comprising:

- an input transmission line configured to transmit the input RF signal through the input signal transmission aperture; and an output transmission line configured to receive the output RF signal through the output signal transmission aperture; and

- a plurality of conductive bumps interconnected to at least one metal layer, the plurality of conductive bumps and the aperture layer defining an interior resonator cavity;

- the interior resonator cavity configured to receive the input RF signal from the input transmission line through the input signal transmission aperture, resonate the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and couple the output RF signal on the output transmission line through the output signal transmission aperture.

- 2. The flip-chip IC of claim 1, wherein the interior resonator cavity is dimensioned to correspond to a predetermined RF frequency band, such that the interior resonator

cavity is configured to resonate frequencies of the input RF signal in the predetermined RF frequency band to generate the filtered RF signal.

- 3. The flip-chip IC of claim 2, wherein the predetermined RF frequency band has a center frequency of sixty (60) GigaHertz (GHz).

- 4. The flip-chip IC of claim 2, wherein the interior resonator cavity has a substantially rectangular cross-section in a plane parallel to the aperture layer.

- 5. The flip-chip IC of claim 4, wherein the substantially rectangular cross-section has a width dimension corresponding to 1/2 of a fundamental mode of a center frequency of the predetermined RF frequency band.

- 6. The flip-chip IC of claim 1, wherein the plurality of conductive bumps are comprised of a plurality of solder balls.

- 7. The flip-chip IC of claim 1, wherein the plurality of conductive bumps are configured to interconnect with complementary contacts of an external circuit such that the aperture layer, the plurality of conductive bumps, and at least a portion of the external circuit define a faraday cage around the interior resonator cavity.

- 8. The flip-chip IC of claim 1, wherein the output transmission line interconnects with the plurality of metal layers.

- 9. The flip-chip IC of claim 8, wherein the output transmission line interconnects with at least one of the plurality of conductive bumps via the plurality of metal layers.

- 10. The flip-chip IC of claim 8, wherein the input transmission line interconnects with the plurality of metal layers.

- 11. The flip-chip IC of claim 10, wherein the input transmission line interconnects with at least one of the plurality of conductive bumps via the plurality of metal layers.

12. The flip-chip IC of claim 11, wherein the output transmission line interconnects with at least one of the plurality of conductive bumps via the plurality of metal layers.

- 13. The flip-chip IC of claim 1, wherein the aperture layer defines an external surface of the semiconductor die, wherein the input and output signal transmission apertures are formed in the external surface of the semiconductor die.

- 14. The flip-chip IC of claim 1, wherein the at least one back end-of-line interconnect layer is adjacent to the aperture layer,

- at least a portion of the input transmission line is adjacent the input signal transmission aperture, and

- at least a portion of the output transmission line is adjacent the output signal transmission aperture.

- 15. The flip-chip IC of claim 1, further comprising an inductance blocker comprising at least one inductor interconnected between the input transmission line and the output transmission line.

- 16. The flip-chip IC of claim 15, wherein the at least one inductor is disposed in at least one of the plurality of metal layers of the semiconductor die.

- 17. The flip-chip IC of claim 15, further comprising a capacitance blocker comprising at least one capacitor interconnected between the input transmission line and the output transmission line in parallel with the inductor.

- 18. The flip-chip IC of claim 1, further comprising a capacitance blocker comprising at least one capacitor interconnected between the input transmission line and the output transmission line.

- 19. The flip-chip IC of claim 18, wherein the at least one capacitor is disposed in at least one of the plurality of metal layers of the semiconductor die.

20. The flip-chip IC of claim 1, wherein the semiconductor die comprises system-on-a-chip (SoC) having a plurality of functional elements configured to interoperate in a self-contained manner.

- 21. The flip-chip IC of claim 1 integrated into a device selected from the group consisting of: a set top box; an entertainment unit; a navigation device; a communications device; a fixed location data unit; a mobile location data unit; a mobile phone; a cellular phone; a computer; a portable computer; a desktop computer; a personal digital assistant (PDA); a monitor; a computer monitor; a television; a tuner; a radio; a satellite radio; a music player; a digital music player; a portable music player; a digital video player; a video player; a digital video disc (DVD) player; and a portable digital video player.

- 22. A flip-chip integrated circuit (IC) comprising:

- a means for providing at least one semiconductor layer in a semiconductor die;

- a means for providing a plurality of metal layers for providing interconnections to the means for providing a semiconductor layer;

- a means for providing an aperture layer comprising an input signal transmission aperture configured to pass an input radio-frequency (RF) signal therethrough, and an output signal transmission aperture configured to pass an output RF signal therethrough; and

- a means for providing at least one back end-of-line interconnect layer disposed between the at least one semiconductor layer and the aperture layer, the at least one back end-of-line interconnect layer, comprising:

- an input transmission line configured to transmit an input RF signal through the input signal transmission aperture; and

- an output transmission line configured to receive the output RF signal through the output signal transmission aperture; and

- a means for providing a plurality of conductive connections interconnected to at least one metal layer,

- a means for providing an interior resonator cavity from the means for providing the plurality of conductive connections and the means for providing an aperture layer,

for providing the interior resonator cavity for receiving the input RF signal from the input transmission line through the input signal transmission aperture, resonating the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and coupling the output RF signal on the output transmission line through the output signal transmission aperture.

23. A method of forming an integrated circuit (IC) chip, the method comprising: providing at least one semiconductor layer;

disposing a plurality of metal layers above the at least one semiconductor layer for providing interconnections to the at least one semiconductor layer;

disposing at least one back end-of-line interconnect layer above the plurality of metal layers, the at least one back end-of-line interconnect layer comprising:

an input transmission line configured to transmit an input radio frequency (RF) signal; and

an output transmission line configured to receive an output RF signal;

disposing an aperture layer above the at least one back end-of-line interconnect layer, the aperture layer comprising an input signal transmission aperture configured to pass the input RF signal therethrough, and an output signal transmission aperture configured to pass the output RF signal therethrough; and

disposing a plurality of conductive bumps above the aperture layer, the plurality of conductive bumps interconnected to at least one metal layer, the plurality of conductive bumps and the aperture layer defining an interior resonator cavity;

the interior resonator cavity configured to receive the input RF signal from the input transmission line through the input signal transmission aperture, resonate the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and couple the output RF signal on the output transmission line through the output signal transmission aperture.

#### 24. The method of claim 23, further comprising:

interconnecting the plurality of conductive bumps with an external circuit, such that the aperture layer, the plurality of conductive bumps, and at least a portion of the external circuit define a faraday cage around the interior resonator cavity.

25. The method of claim 23, wherein disposing the plurality of metal layers above the at least one semiconductor layer comprises disposing at least one inductor in the plurality of metal layers, such that disposing at least one back end-of-line interconnect layer above the plurality of metal layers interconnects the at least one inductor between the input transmission line and the output transmission line.

- 26. The method of claim 25, wherein disposing the plurality of metal layers above the at least one semiconductor layer further comprises disposing at least one capacitor in the plurality of metal layers, such that disposing at least one back end-of-line interconnect layer above the plurality of metal layers interconnects the at least one inductor and the at least one capacitor in parallel between the input transmission line and the output transmission line.

- 27. The method of claim 23, wherein disposing the plurality of metal layers above the at least one semiconductor layer further comprises disposing at least one capacitor in the plurality of metal layers, such that disposing at least one back end-of-line interconnect layer above the plurality of metal layers interconnects the at least one capacitor between the input transmission line and the output transmission line.

- 28. A circuit board having an integrated cavity filter, the circuit board comprising: an integrated circuit (IC) chip comprising:

- a semiconductor die, comprising:

- at least one semiconductor layer;

- a plurality of metal layers for providing interconnections to the at least one semiconductor layer;

- an aperture layer comprising an input signal transmission aperture configured to pass an input radio frequency (RF) signal therethrough, and an output signal transmission aperture configured to pass an output RF signal therethrough; and at least one back end-of-line interconnect layer disposed between the at least one semiconductor layer and the aperture

layer, the at least one back end-of-line interconnect layer comprising:

an input transmission line configured to transmit an input RF signal through the input signal transmission aperture; and

an output transmission line configured to receive the output RF signal through the output signal transmission aperture; and

- a plurality of conductive bumps interconnected to at least one metal layer,

- the plurality of conductive bumps and the aperture layer defining an interior resonator cavity configured to receive the input RF signal from the input transmission line through the input signal transmission aperture, resonate the input RF signal to generate the output RF signal comprising a filtered RF signal of the input RF signal, and couple the output RF signal on the output transmission line through the output signal transmission aperture; and

- an external circuit interconnected to the plurality of conductive bumps, wherein the external circuit, the plurality of conductive bumps, and at least a portion of the external circuit define a faraday cage around the interior resonator cavity.

- 29. The circuit board of claim 28, wherein the interior resonator cavity is dimensioned to correspond to a predetermined RF frequency band, such that the interior resonator cavity is configured to resonate frequencies of the input RF signal in the predetermined RF frequency band to generate the filtered RF signal.

3/11

FIG. 1C

4/11

FIG. 2

FIG. 5A

FIG. 5B

7/11

FIG. 6A

FIG. 6B

10/11

FIG. 7A

FIG. 7B

Ø Ç L

#### INTERNATIONAL SEARCH REPORT

International application No PCT/US2016/049440

a. classification of subject matter INV. H01P7/06

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

H01P H01Q

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                              | Relevant to claim No. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 2010/308925 A1 (SONG SANG SUB [KR] ET AL) 9 December 2010 (2010-12-09) figure 1 paragraphs [0046] - [0051]                                                                                                                                                                                                                   | 1-29                  |

| A         | LEE J-H ET AL: "LOW-LOSS LTCC CAVITY FILTERS USING SYSTEM-ON-PACKAGE TECHNOLOGY AT 60 GHZ", IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, IEEE SERVICE CENTER, PISCATAWAY, NJ, US, vol. 53, no. 12, 1 December 2005 (2005-12-01), pages 3817-3829, XP001240896, ISSN: 0018-9480, DOI: 10.1109/TMTT.2005.859864 figure 2 | 1-29                  |

| X Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "A" document defining the general state of the art which is not considered to be of particular relevance  "E" earlier application or patent but published on or after the international filing date  "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)  "O" document referring to an oral disclosure, use, exhibition or other means  "P" document published prior to the international filing date but later than the priority date claimed | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention  "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone  "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art  "&" document member of the same patent family |

| Date of the actual completion of the international search  23 November 2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Date of mailing of the international search report $30/11/2016$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Authorized officer

Niemeijer, Reint

Form PCT/ISA/210 (second sheet) (April 2005)

1

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016

# **INTERNATIONAL SEARCH REPORT**

International application No

PCT/US2016/049440

|          |                                                                                                                              | <u> </u>              |

|----------|------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| ategory* | Citation of document, with indication, where appropriate, of the relevant passages                                           | Relevant to claim No. |

| 1        | US 2008/238792 A1 (HEINRICH WOLFGANG [DE]<br>ET AL) 2 October 2008 (2008-10-02)<br>figures 1,2<br>paragraphs [0024] - [0027] | 1-29                  |

| 4        | figures 1,2                                                                                                                  | 1-29                  |

|          |                                                                                                                              |                       |

|          |                                                                                                                              |                       |

|          |                                                                                                                              |                       |

|          |                                                                                                                              |                       |

|          |                                                                                                                              |                       |

1

## **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2016/049440

| Patent document cited in search report |    | Publication<br>date | Patent family<br>member(s)                                                                                    | Publication<br>date                                                              |

|----------------------------------------|----|---------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| US 2010308925                          | A1 | 09-12-2010          | KR 20100132237 A<br>US 2010308925 A1                                                                          | 17-12-2010<br>09-12-2010                                                         |

| US 2008238792                          | A1 | 02-10-2008          | AT 366465 T<br>DE 102004014018 B3<br>EP 1726063 A1<br>JP 2007529930 A<br>US 2008238792 A1<br>WO 2005091438 A1 | 15-07-2007<br>11-08-2005<br>29-11-2006<br>25-10-2007<br>02-10-2008<br>29-09-2005 |

| US 9123983                             | B1 | 01-09-2015          | NONE                                                                                                          |                                                                                  |