(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5676945号

(P5676945)

(45) 発行日 平成27年2月25日(2015.2.25)

(24) 登録日 平成27年1月9日(2015.1.9)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| H01L 21/76 (2006.01)  | H01L 21/76 S    |

| H01L 21/336 (2006.01) | H01L 29/78 621  |

| H01L 29/786 (2006.01) | H01L 29/78 618B |

| G09F 9/30 (2006.01)   | G09F 9/30 338   |

| G09F 9/35 (2006.01)   | G09F 9/35       |

請求項の数 16 (全 18 頁)

(21) 出願番号 特願2010-155920 (P2010-155920)

(22) 出願日 平成22年7月8日(2010.7.8)

(65) 公開番号 特開2012-19092 (P2012-19092A)

(43) 公開日 平成24年1月26日(2012.1.26)

審査請求日 平成25年7月4日(2013.7.4)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100096828

弁理士 渡辺 敏介

(74) 代理人 100110870

弁理士 山口 芳広

(72) 発明者 鈴木 翔

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 安部 勝美

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】電子装置、電子装置の素子分離方法、電子装置の製造方法、及び電子装置を備えた表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の電子素子を複数備える電子装置であって、

前記複数の電子素子の素子間に素子分離領域が配置され、

前記素子分離領域は、絶縁体膜を挟んで積層され、かつバンドギャップが1.95 eV

以上の酸化物半導体を含有する酸化物半導体膜と、素子分離電極と、を備え、

前記酸化物半導体膜は、前記素子分離領域に含まれる部分と、該部分に連なり前記電子

素子に含まれる部分と、を有し、

前記素子分離電極は、前記絶縁体膜によって前記酸化物半導体膜と隔てられ、

前記素子分離電極は、電圧を印加することで、前記素子分離領域に含まれる前記酸化物

半導体膜を電界効果を利用して高抵抗化させ、前記電子素子間を電気的に分離させるため

の電極であり、

前記酸化物半導体膜は、前記素子分離領域と前記電気素子に含まれる部分とのそれ

において、抵抗値を制御するドーパントが含まれていないことを特徴とする電子装置。

## 【請求項 2】

前記酸化物半導体膜において、前記電子素子に含まれる部分と、前記素子分離領域に含

まれる部分とは、一体的に形成された連続層をなしていることを特徴とする請求項 1 に記

載の電子装置。

## 【請求項 3】

前記酸化物半導体膜は、2.5 eV 以上のバンドギャップを有することを特徴とする請

求項 1 又は 2 に記載の電子装置。

【請求項 4】

前記酸化物半導体膜のキャリア密度が  $10^{18} \text{ cm}^{-3}$  以下であることを特徴とする請求項 1 乃至 3 のいずれか一項に記載の電子装置。

【請求項 5】

前記酸化物半導体膜のキャリア密度が  $10^{16} \text{ cm}^{-3}$  以下であることを特徴とする請求項 4 に記載の電子装置。

【請求項 6】

前記電子素子は、前記酸化物半導体膜、ゲート絶縁層、及び、ゲート電極が積層された薄膜トランジスタであることを特徴とする請求項 1 乃至 5 のいずれか一項に記載の電子装置。

10

【請求項 7】

前記素子分離領域に含まれる酸化物半導体膜と、前記薄膜トランジスタのチャネルを構成する酸化物半導体膜と、が同一の主成分材料及び同一の極性を有することを特徴とする請求項 6 に記載の電子装置。

【請求項 8】

前記素子分離電極は、前記素子分離領域に含まれる部分と、該部分に連なり前記電子素子に含まれる部分と、を有し、

前記電子素子は、前記ゲート絶縁層と、前記ゲート電極を挟む対向絶縁層と、を有し、

前記素子分離電極のうち前記電子素子に含まれる部分は、前記対向絶縁層が前記ゲート電極と接する側とは反対側において、前記対向絶縁層に接していることを特徴とする請求項 6 又は 7 に記載の電子装置。

20

【請求項 9】

それが画素電極を有する複数の表示素子と、請求項 6 乃至 8 のいずれか 1 項に記載の電子装置と、を備え、

前記複数の電子素子のうちの少なくとも 2 つの電子素子は、前記複数の表示素子から駆動する表示素子を選択するスイッチングトランジスタと、前記画素電極に電気的に接続され、かつ前記スイッチングトランジスタにより選択された表示素子を駆動する駆動トランジスタと、にそれぞれ対応していることを特徴とする表示装置。

30

【請求項 10】

前記表示素子はエレクトロルミネッセンス素子であることを特徴とする請求項 9 に記載の表示装置。

【請求項 11】

前記表示素子は液晶セルであることを特徴とする請求項 9 に記載の表示装置。

【請求項 12】

複数の電子素子を備える電子装置の素子分離方法であって、

前記複数の電子素子の素子間に素子分離領域が配置され、

前記素子分離領域は、バンドギャップが  $1.95 \text{ eV}$  以上であって酸化物半導体を含有する酸化物半導体膜と、絶縁体膜と、素子分離電極と、をこの順で積層された構成を備え、

40

前記酸化物半導体膜は、前記素子分離領域に含まれる部分と、該部分に連なり前記電子素子に含まれる部分と、を有し、

前記素子分離領域に含まれる部分と前記電子素子に含まれる部分とのそれぞれにおいて、抵抗値を制御するドーパントが含有されておらず、

前記絶縁体膜によって前記素子分離領域に含まれる半導体膜と隔てられた前記素子分離電極に一定電圧を印加することにより、前記素子分離領域に含まれる半導体膜を電界効果を利用して高抵抗化し、前記電子素子間を電気的に分離することを特徴とする電子装置の素子分離方法。

【請求項 13】

前記電子素子に含まれる部分と、前記素子分離領域に含まれる部分とは、それぞれ、共

50

通の半導体膜から構成されていることを特徴とする請求項1\_2に記載の電子装置の素子分離方法。

**【請求項 1 4】**

複数の電子素子と、前記複数の電子素子の間に位置する素子分離領域と、を備える電子装置の製造方法であって、

ゲート用端子を形成する工程と、

前記ゲート用端子の上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の上にソース端子を形成する工程と、

前記ゲート絶縁膜及び前記ソース端子の上にバンドギャップが $1.95\text{ eV}$ 以上である酸化物半導体を含む酸化物半導体膜を形成する工程と、

前記酸化物半導体膜の上に絶縁体膜を形成する工程と、

前記絶縁体膜の上であって前記ゲート用端子及び前記ソース端子が設けられていない素子分離領域に素子分離電極を形成する工程と、

を備え、

前記酸化物半導体膜は、前記電子素子に含まれる部分と、前記素子分離領域に含まれる部分と、を有するように形成され、

前記電子素子に含まれる酸化物半導体膜と、前記素子分離領域に含まれる半導体膜とは一体形成され、

前記酸化物半導体膜の前記素子分離領域に含まれる部分及び前記電子素子に含まれる部分のそれぞれに対して、抵抗値を制御するドーパントを導入する工程を有さないことを特徴とする、電界効果型素子分離領域を有する電子装置の製造方法。

**【請求項 1 5】**

複数の電子素子と、前記複数の電子素子の素子間にフィールドシールド素子分離領域とを有する電子装置であって、

前記電子素子は、バンドギャップが $1.95\text{ eV}$ 以上の酸化物半導体を含有する酸化物半導体膜をチャネル層に備える薄膜トランジスタであって、

隣接する一対の前記電子素子のそれぞれが備える前記酸化物半導体膜は、一方の前記酸化物半導体膜から他方の前記酸化物半導体膜に延在する領域を有し、

前記フィールドシールド素子分離領域は、前記延在する領域の部分に位置する前記酸化物半導体層を備え、

前記酸化物半導体膜は、前記素子分離領域に含まれる部分と前記電子素子に含まれる部分とのそれぞれにおいて、抵抗値を制御するドーパントが含有されていないことを特徴とする電子装置。

**【請求項 1 6】**

それが画素電極を有する複数の表示素子と、請求項15に記載の電子装置と、を備え、

前記複数の電子素子のうちの少なくとも2つの電子素子は、前記複数の表示素子から駆動する表示素子を選択するスイッチングトランジスタと、前記画素電極に電気的に接続され前記スイッチングトランジスタにより選択された表示素子を駆動する駆動トランジスタと、にそれぞれ対応していることを特徴とする表示装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体電子素子を含む電子装置に係り、詳しくは、電子素子間の素子分離構造を改良した電子装置、電子装置の素子分離方法、電子装置の製造方法、及び電子装置を備えた表示装置に関する。

**【背景技術】**

**【0002】**

近年、液晶セルやエレクトロルミネッセンス素子(EL素子)などの表示素子を備える表示装置には、表示素子を駆動する電子素子として、アモルファスシリコンやポリシリコ

10

20

30

40

50

ン等をチャネル領域に用いた複数の薄膜トランジスタ（TFT）が用いられている。

#### 【0003】

現在、液晶ディスプレイ等の表示装置の高精細化が求められている。この高精細化を阻む大きな要因の一つが TFT のサイズである。また、TFT が正常に動作するためには、各 TFT が電気的に分離されなければならない。TFT 等の電子素子間を電気的に分離する技術を素子分離という。TFT では、一般にフォトリソグラフィ法と、ドライエッチングまたはウエットエッチングを用いて、各 TFT のチャネル領域を互いに電気的に独立な島状にパターニングすることにより、素子分離が実現される。

#### 【0004】

TFT の半導体膜を島状にパターニングする素子分離では、ドライエッチングを用いることで、現状、最も小さな素子サイズが得られる。しかし、ドライエッチングは高価な真空装置を用いるため、製造コストを増大させる要因となる。また、半導体膜の大きさは、半導体膜の加工精度のみでは決まらず、半導体膜と電極とのコンタクトを考慮して決める必要がある。低コスト化を図るにはウエットエッチングを用いることが有効である。しかし、ウエットエッチングはドライエッチングに比べて加工精度が低下する場合がある。また、チャネル領域に用いる半導体材料として水分の影響により電気特性が変化する材料を用いる場合には、ウェットプロセスによるチャネル領域への水分吸着等によって微細化に一定の制限が加わったり、乾燥プロセスの付加等スループットを低下させることがある。

10

#### 【0005】

また、上記以外の独立な島状のチャネル領域の形成方法として、成膜時にシャドウマスク用いて素子分離を行う方法があるが、ウエットエッチングよりもさらに加工精度が低くなる。

20

#### 【0006】

一方、半導体膜を島状にパターニングしない素子分離の技術として、隔壁を用いて素子分離を行う方法（特許文献 1 参照）や、素子分離領域の半導体膜に不純物を添加することにより高抵抗化し、素子分離を行う方法（特許文献 2 参照）がある。

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

【特許文献 1】特開 2007 - 220713 号公報

30

【特許文献 2】特公平 8 - 4131 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

ところで、半導体膜を島状にパターニングしない特許文献 1 及び特許文献 2 に記載の技術は、隔壁の形成や不純物ドーピングなどを要するため、加工精度の点で半導体膜を島状にパターニングする技術に対する優位性はない。従って、TFT 等の半導体電子素子の微細化における更なる加工精度の向上や、低コスト化が求められている。

#### 【0009】

そこで、本発明は、半導体電子素子の微細化における加工精度の向上、及び低コスト化を可能とし、かつ素子分離が行える電子装置、電子装置の素子分離方法、電子装置の製造方法、及び電子装置を備えた表示装置を提供することを目的とする。

40

#### 【課題を解決するための手段】

#### 【0010】

上記の目的を達成すべく成された本発明の構成は以下の通りである。

#### 【0011】

即ち、本発明に係る電子装置は、

複数の電子素子を複数備える電子装置であって、

前記複数の電子素子の素子間に素子分離領域が配置され、

前記素子分離領域は、絶縁体膜を挟んで積層され、かつバンドギャップが 1.95 eV

50

以上の酸化物半導体を含有する酸化物半導体膜と、素子分離電極と、を備え、

前記酸化物半導体膜は、前記素子分離領域に含まれる部分と、該部分に連なり前記電子

素子に含まれる部分と、を有し、

前記素子分離電極は、前記絶縁体膜によって前記酸化物半導体膜と隔てられ、

前記素子分離電極は、電圧を印加することで、前記素子分離領域に含まれる前記酸化物

半導体膜を電界効果を利用して高抵抗化させ、前記電子素子間を電気的に分離させ

るための電極であり、

前記酸化物半導体膜は、前記素子分離領域と前記電気素子に含まれる部分とのそれ

において、抵抗値を制御するドーパントが含まれていない

ことを特徴とする電子装置である。

10

#### 【0012】

また、本発明に係る電子装置の素子分離方法は、

複数の電子素子を備える電子装置の素子分離方法であって、

前記複数の電子素子の素子間に素子分離領域が配置され、

前記素子分離領域は、バンドギャップが1.95eV以上であって酸化物半導体を含有

した酸化物半導体膜と、絶縁体膜と、素子分離電極と、をこの順で積層された構成を備え

、

前記酸化物半導体膜は、前記素子分離領域に含まれる部分と、該部分に連なり前記電子

素子に含まれる部分と、を有し、

前記素子分離領域に含まれる部分と前記電子素子に含まれる部分とにおいて、ドーパン

トが含有されておらず、

20

前記絶縁体膜によって前記素子分離領域に含まれる半導体膜と隔てられた前記素子分離

電極に一定電圧を印加することにより、前記素子分離領域に含まれる半導体膜を電界効果

を利用して高抵抗化し、前記電子素子間を電気的に分離することを特徴とする電子装置の

素子分離方法である。

#### 【0013】

さらに、本発明に係る電子装置の製造方法は、

複数の電子素子と、前記複数の電子素子の間に位置する素子分離領域と、を備える電子

装置の製造方法であって、

ゲート用端子を形成する工程と、

前記ゲート用端子の上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜の上にソース端子を形成する工程と、

前記ゲート絶縁膜及び前記ソース端子の上にバンドギャップが1.95eV以上である

酸化物半導体を含む酸化物半導体膜を形成する工程と、

前記酸化物半導体膜の上に絶縁体膜を形成する工程と、

前記絶縁体膜の上であって前記ゲート用端子及び前記ソース端子が設けられていない素

子分離領域に素子分離電極を形成する工程と、

を備え、

前記酸化物半導体膜は、前記電子素子に含まれる部分と、前記素子分離領域に含まれる

部分と、を有するように形成され、

40

前記電子素子に含まれる酸化物半導体膜と、前記素子分離領域に含まれる半導体膜と、

は一体形成され、

前記酸化物半導体膜の前記素子分離領域に含まれる部分及び前記電子素子に含まれる部

分に対して、抵抗値を制御するドーパントを導入する工程を有しないことを特徴とする、

電界効果型素子分離領域を有する電子装置の製造方法である。

#### 【発明の効果】

#### 【0014】

本発明によれば、絶縁体膜によってバンドギャップ1.95eV以上の半導体膜と隔て

て素子分離電極を形成し、素子分離電極に電圧を印加することで、バンドギャップ1.9

5eV以上の半導体膜を高抵抗化し、電界効果により電子素子間を電気的に分離できる。

50

従って、半導体膜を島状にパターニングする技術に比して、半導体電子素子の微細化における加工精度の向上、及び低コスト化が可能であるという優れた効果を発揮する。

**【図面の簡単な説明】**

**【0015】**

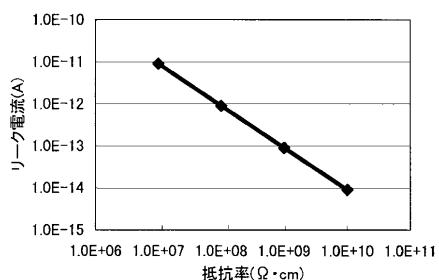

【図1】半導体膜の抵抗率とTFT間のリーク電流との関係を示す図である。

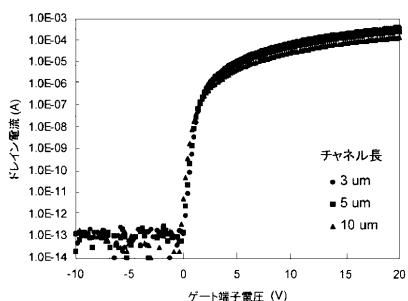

【図2】TFTの伝達特性の例を示す説明図である。

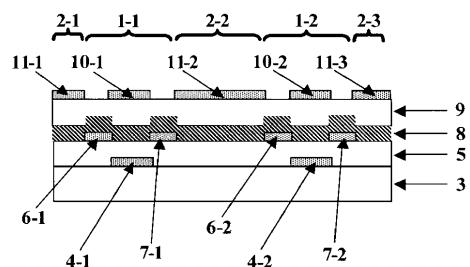

【図3】実施例1の電子装置の積層構成を示す概略断面図である。

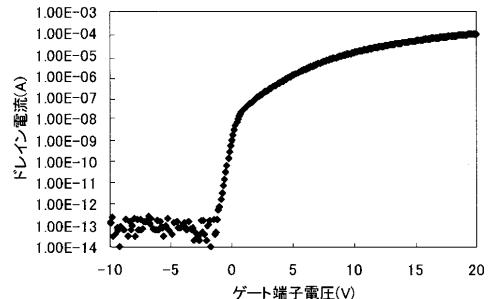

【図4】実施例1の電子装置におけるTFTの伝達特性を示す説明図である。

【図5】コブラナー型TFTを含む電子装置の積層構成を示す概略断面図である。

【図6】実施例2の電子装置の積層構成を示す概略断面図である。

10

【図7】素子分離用電極をパターニングしない場合の電子装置の積層構成である。

【図8】実施例3の電子装置の積層構成を模式的に示す概略断面図である。

【図9】実施例4の電子装置の積層構成を模式的に示す概略断面図である。

**【発明を実施するための形態】**

**【0016】**

以下、図面を参照して、本発明の実施の形態を説明するが、本発明は本実施形態に限定されない。また、本明細書で特に図示または記載されない部分に関しては、当該技術分野の周知または公知技術を適用する。

**【0017】**

まず、本発明に係る電子装置の一実施形態について説明する。なお、本発明に係る電子装置の具体的な積層構成については、後述の実施例1から4で詳細に説明する。

20

**【0018】**

本実施形態の電子装置は、半導体膜を含む電子素子、具体的には薄膜トランジスタ(TFT)、ダイオード、抵抗等を複数備える電子装置であって、電子素子の素子間に素子分離領域が存在する。素子分離領域は、バンドギャップが1.95eV以上である半導体膜、絶縁体膜及び素子分離電極を有する。

**【0019】**

素子分離領域の半導体膜と電子素子のチャネルを構成する半導体膜は、同一の主成分材料及び同一の極性(n型またはp型)からなる半導体膜としても良いし、同一の主成分材料及び同一の極性からなる半導体膜としなくても良い。両者を同一の主成分材料及び同一極性とすれば、従来知られている素子分離用のpnp接合を形成する必要がなく、電子素子のチャネルを構成する半導体膜と素子分離領域の半導体膜の成膜を1つのプロセスで行える点でより好ましい。

30

**【0020】**

絶縁体膜は、一般的な絶縁体膜であればどのような材料でも良く、SiO<sub>2</sub>、SiN、HfO<sub>2</sub>、Y<sub>2</sub>O<sub>3</sub>等の無機材料や、ポリイミド、ポリビニルアルコール等の有機材料でも良い。

**【0021】**

素子分離電極は、絶縁体膜によって素子分離領域の半導体膜と隔てられ、電圧が印加されて電界効果により素子分離領域の半導体膜を高抵抗化し、電子素子間を電気的に分離するための電極である。素子分離電極は絶縁体膜を挟んで半導体膜の上部にあっても下部にあっても良い。素子分離電極を複数に分割して、動作している電子素子が含まれる領域のみに素子分離をするための電圧を印加し、それ以外の領域には電圧を印加しないようにすることもできる。こうすることにより、素子分離電極への電圧印加に必要な電力消費を抑えることができる。また、素子分離電極は、例えばAl、Au、Cu、Mo、Ti等の金属材料や、それらの積層膜でも良く、ITO(インジウム錫酸化物)やIZO(インジウム亜鉛酸化物)等の導電性酸化物でも良い。

40

**【0022】**

従来の方法では、TFTの半導体膜のパターニング精度と、電極あるいはコンタクトホールとTFTの半導体膜との重ね合わせ(位置合わせ:アライメント)のマージンとの和

50

により、素子分離領域が決定されていた。これに対し、本発明では素子分離領域がTFTのソース・ドレイン端子のみのパターニング精度、あるいは素子分離電極のみのパターニング精度により決定できるので、素子の微細化、高集積化が可能となる。なお、電気的に素子分離を行うため、素子分離電極はパターニングされていても、パターニングされていなくても良い。

#### 【0023】

電子素子がTFTの場合、TFTはボトムゲート構造でも良いし、トップゲート構造でも良い。また、TFTに遮光膜が必要な場合、素子分離電極はTFTの遮光膜と同一膜とすることもできる。遮光膜と同一膜を用いることで成膜プロセスを減らすことができる。

#### 【0024】

まず、図1を用いて素子分離領域の半導体膜の高抵抗化について説明する。なお、「高抵抗化」とは、素子分離電極に電圧を印加することにより、素子分離領域の半導体膜が空乏化することを意味する。

#### 【0025】

図1は、精細度211ppi程度の表示装置の各画素に、駆動トランジスタとして複数個のTFTを配置した場合における、TFT間に存在する素子分離領域の半導体膜の抵抗率とTFT間のリーク電流との関係を示す図である。なお、TFTの半導体膜及び素子分離領域の半導体膜の膜厚を30nm、TFTのソース・ドレイン端子間電圧を10Vと仮定している。

#### 【0026】

精細度211ppi程度の表示装置において、赤(R)、緑(G)、青(B)の3色でフルカラー表示する場合の画素サイズは、短辺方向に40μmピッチ、長辺方向に120μmピッチのサブピクセル(3色で1画素を構成するときの1色分のピクセル)となる。このサブピクセルに複数個のTFTを配置した場合、隣り合うTFTのソース・ドレイン端子間距離は10μm程度、ソース・ドレイン端子の幅は30μm程度になる。

#### 【0027】

ここで、TFT及びTFT間のリーク電流は、階調を決める階調電圧を保持する条件により制限される。例えば、階調保持容量が0.2pF、リーク電流が $10^{-11}A$ 以下の場合、1フレーム(1/60秒)の間の階調電圧変動は、 $10^{-11} \cdot (1/60) \cdot (1/(0.2 \cdot 10^{-12})) = 0.83V$ より、1V以下に抑えることができる。

#### 【0028】

従って、階調電圧変動を1V以下にするためには、リーク電流が $10^{-11}A$ 以下であれば良く、図1より、半導体膜は $10^7 \cdot cm$ 以上の抵抗率であれば良い。さらに、半導体膜の抵抗率が $10^{10} \cdot cm$ 以上の場合、ソース・ドレイン端子間距離が1μmでも、リーク電流を $10^{-12}A$ 以下に抑えることが可能となる。

#### 【0029】

このように、本実施形態では、素子分離電極に一定電圧を印加することにより、素子分離領域の半導体膜が高抵抗化、即ち空乏化する。このため、上記のようにリーク電流を抑制でき、素子分離が可能となる。空乏化したときの素子分離領域の半導体膜の抵抗率は、上記のように $10^7 \cdot cm$ 以上であることが好ましく、 $10^{10} \cdot cm$ 以上であることがより好ましい。

#### 【0030】

次に、素子分離電極に印加する電圧について説明する。

#### 【0031】

素子分離電極に印加する電圧は、半導体膜がn型であれば素子駆動用電極に直接印加される最低電圧以下、p型であれば素子駆動用電極に直接印加される最高電圧以上であることが好ましい。従って、素子分離電極に印加する電圧は、半導体膜がフラットバンドとなる電圧に対し、n型半導体の場合はより低い電圧、p型半導体の場合はより高い電圧である必要がある。半導体膜がフラットバンドになる電圧は、電極材料の仕事関数、半導体膜のフェルミ準位、半導体膜中や半導体膜と絶縁体膜との界面のトラップ等に依存する。電

10

20

30

40

50

極材料の仕事関数と半導体膜のフェルミ準位が一致し、トラップ等の影響がない最も簡単な場合には、素子駆動用電極に直接印加されている電圧が 0 V とすると、素子分離電極に 0 V を印加したとき、半導体膜はフラットバンドになる。このとき、素子分離電極に印加する電圧を、半導体膜が n 型であれば 0 V 以下、p 型であれば 0 V 以上とすることで、半導体膜を空乏化することができる。

#### 【0032】

素子分離領域の半導体膜の空乏化に必要な電圧は、電界が印加されていない状態の半導体膜のキャリア密度  $N_D$  と半導体膜の膜厚  $t_s$  に依存する。キャリア密度が低いほど、また膜厚が薄いほど、空乏化に必要な電圧は小さい。例えば、半導体膜中や界面にトラップがなく、半導体膜と、半導体膜を空乏化するための素子分離電極と、のフラットバンド電圧が 0 という理想的な場合、半導体膜全体を空乏化するために必要な電圧の絶対値  $|V_B|$  は、次の式(1)及び式(2)で表される。

10

$$|V_B| = (q \cdot N_D / (2 \cdot s)) \cdot (t_s^2 + 2 \cdot t_s \cdot s / C) \quad \text{式(1)}$$

$$|V_B| \sim t_s \cdot q \cdot N_D / C \quad \text{式(2)}$$

#### 【0033】

ここで、 $q$  は電気素量、 $s$  は半導体膜の誘電率、 $C$  は半導体膜と素子分離電極間の絶縁体膜の単位面積あたりの容量である。また、式(2)は式(1)右辺の第二項のみを考慮した場合の近似で、半導体膜の膜厚が絶縁体膜の膜厚と同等あるいは絶縁体膜の膜厚より薄く、半導体膜の誘電率が絶縁体膜の誘電率より大きいときに成立する。

#### 【0034】

式(2)によれば、絶縁体膜が 100 nm の酸化 Si で形成されている場合、 $t_s \cdot N_D$  が  $10^{12} \text{ cm}^{-2}$  以下のとき、 $|V_B|$  が 5 V 以下となる。即ち、真空の誘電率、酸化 Si の比誘電率 = 3.9、絶縁体膜の膜厚 100 nm、を用いて単位面積あたりの容量を計算すると、 $C = 3.45 \times 10^{-8} \text{ F/cm}^2$  となるため、 $|V_B| = 4.6 \text{ V}$  となる。このとき、 $N_D$  が  $10^{18} \text{ cm}^{-3}$  ならば、 $t_s$  は 10 nm 以下にしなければならない。一般に、半導体膜の膜厚は 10 nm 以上が必要であるので、電界が印加されていない場合の半導体膜のキャリア密度は、 $10^{18} \text{ cm}^{-3}$  以下とすることが好ましい。電界が印加されていない場合の半導体膜のキャリア密度が  $10^{16} \text{ cm}^{-3}$  以下ならば、絶縁体膜を 200 nm、半導体膜を 100 nm としても、 $|V_B|$  を 5 V 以下に抑えることができる。

20

#### 【0035】

このように、本実施形態では、電界が印加されていない場合、半導体膜のキャリア密度が  $10^{18} \text{ cm}^{-3}$  以下であるのが好ましく、 $10^{16} \text{ cm}^{-3}$  以下であるのがより好ましい。半導体膜のキャリア密度を  $10^{18} \text{ cm}^{-3}$  以下、より好ましくは  $10^{16} \text{ cm}^{-3}$  以下にすることにより、素子分離電極に印加する電圧を 5 V 以下に抑えることができる。

30

#### 【0036】

ところで、液晶セルやエレクトロルミネッセンス素子(EL 素子)等の表示素子のアクティブマトリックス回路に対し、前述の特許文献 2 の様に電界効果型トランジスタのオフ動作を用いる場合、素子分離のためのゲート端子に印加できる電位の数は制限を受ける。異なる電位を印加する数だけ、素子分離電極配線数やそのスペース、配線間絶縁のためのプロセス数が増大するからである。このため、素子分離電極に印加する電圧は、一定電圧であることが重要である。

40

#### 【0037】

表示素子として有機 EL 素子を備える表示装置の最も簡単な画素回路を例に説明する。有機 EL 素子の画素回路は 2 個のトランジスタ素子、1 個のキャパシタ素子、及び有機 EL 素子から構成され、1 つ目のトランジスタを画素選択のためのスイッチングトランジスタとし、2 つ目のトランジスタを有機 EL 素子の駆動トランジスタとする。

#### 【0038】

この画素回路がアクティブマトリックスを構成しているとき、ある瞬間では 2 つのトランジスタのソース電位は異なっており、隣接する画素の駆動トランジスタのソース電位とも異なった電位を持つことになる。表示素子のアクティブマトリックス回路に一般的に用

10

20

30

40

50

いられるアモルファスシリコンや低温ポリシリコンの場合、オフ電流の最小値を決定する最適な素子分離電極の電位が各素子のソース電位の差分だけ異なることになる。

#### 【0039】

n型のアモルファスシリコンや低温ポリシリコンTFTにおいては、オフ電流の最小値を決定する最適な素子分離電極の電位よりも負側にゲート電位を大きくすると、ホールの注入による逆極性の電流が流れ始める。p型の低温ポリシリコンTFTにおいても、オフ電流の最小値を決定する最適な素子分離電極の電位よりも正側にゲート電位を大きくすると、電子の注入による逆極性の電流が流れ始める。つまり、アモルファスシリコンや低温ポリシリコンを用いて素子分離電極に一定電圧を印加すると、オフ電流の最小値を決定する最適な素子分離電極の電位が各素子のソース電位の差分だけ異なることになる。このため、いずれかの素子間で素子分離のリーク電流が増加することになる。従って、素子分離領域の幅を増大させて半導体膜の抵抗率を稼ぐなど、リーク電流抑制のための設計制限が大きくなり、本発明の微細化の効果を得ることが難しい。10

#### 【0040】

上記のように、半導体膜としてアモルファスシリコンや低温ポリシリコンを用いた場合には、半導体膜の極性と逆極性のキャリアの注入による電流が流れるため、本実施形態では、バンドギャップが広い半導体膜を用いる。素子分離領域の半導体膜が空乏化したときの、半導体膜のキャリア密度の最小値は、真性キャリア密度、つまりバンドギャップにより決まり、バンドギャップが広いほど、半導体膜の極性と逆極性のキャリアの注入による電流が抑制できるからである。20

#### 【0041】

バンド理論に拠れば、真性キャリア密度  $n_i$  とバンドギャップ  $E_g$  の関係は、次の式(3)で表される。

$$n_i = (N_C \cdot N_V)^{1/2} \cdot e \times p (-E_g / (2 \cdot k \cdot T)) \quad \text{式(3)}$$

#### 【0042】

ここで、 $N_C$ 、 $N_V$  は、それぞれ伝導帯と価電子帯の有効状態密度、 $k$  はボルツマン定数、 $T$  は絶対温度である。 $N_C$ 、 $N_V$  は、半導体材料により異なるが、Siの場合、室温(300K)において、ともに  $3 \times 10^{19} \text{ cm}^{-3}$  程度となる。バンドギャップ  $E_g$  が 1.65 eV の場合、上記数値を用いると、真性キャリア密度が  $4 \times 10^5 \text{ cm}^{-3}$  となる。また、抵抗率: 、電気素量:  $q$ 、キャリア密度:  $n_i$ 、移動度:  $\mu$  についての式( $= 1 / (q \cdot n_i \cdot \mu)$ )より、移動度  $\mu = 1.07 \times 10^3 \text{ cm}^2 / (V \cdot s)$  とすると、半導体膜の抵抗率が  $1.46 \times 10^{10} \text{ } \cdot \text{cm}$  となり、高抵抗化を実現できる。しかし、実際には温度依存性を考慮する必要があり、半導体電子素子に用いられる動作範囲温度の最大値は 85 (358K) である。温度 85 (358K)において上記移動度を用いると、バンドギャップ  $E_g$  が 1.95 eV の場合、真性キャリア密度が  $6 \times 10^5 \text{ cm}^{-3}$ 、半導体膜の抵抗率の最大値が  $10^{10} \text{ } \cdot \text{cm}$  となり、高抵抗化を実現できる。即ち、バンドギャップ  $E_g$  が 1.65 eV の場合でも本発明を実現できるが、温度依存性を考慮すると、バンドギャップ  $E_g$  が 1.95 eV の場合の方が確実に本発明を実現できる点で好ましい。30

#### 【0043】

以上より、本実施形態では、バンドギャップが 1.95 eV 以上、より好ましくは 2.5 eV 以上の、金属酸化物半導体、化合物半導体等を半導体膜として用いる。

#### 【0044】

上記条件を満たす金属酸化物半導体は、例えばZnの酸化物であるZnO、Inの酸化物であるIn<sub>2</sub>O<sub>3</sub>、In、Znの酸化物であるIn-Zn-O (IZO)、In、Ga、Znの酸化物であるIn-Ga-Zn-O (IGZO) などである。これらの金属酸化物半導体の構造は、単結晶、多結晶、アモルファス(非晶質)のいずれでも良いが、非晶質の場合、結晶化のためのプロセスが不要であり、平坦性及び均一性も高いため、さらに好ましい。

#### 【0045】

10

20

30

40

50

また、上記条件を満たす化合物半導体としては、例えばSiC、GaN等である。その他のバンドギャップが広い材料としてはダイヤモンド(C)が挙げられ、これについても本発明は適用可能である。

#### 【0046】

図2は、キャリア密度が約 $10^{15} \text{ cm}^{-3}$ 、バンドギャップ約3eVのn型アモルファスIGZO膜を半導体膜に用いたTFTのドレイン端子電圧12Vにおける伝達特性の例を示す説明図である。

#### 【0047】

図2に示すように、ゲート端子に-1V以下の負の電圧を印加することにより、チャネル長 $10\mu\text{m}$ のTFTにおいて、半導体膜が空乏化して抵抗率が $10^7 \cdot \text{cm}$ 以上となり、ドレイン電流が $10^{-12}\text{A}$ 以下に抑えられている。また、ゲート端子電圧が-1V以下の場合のドレイン電流は、チャネル長によらず $10^{-12}\text{A}$ 以下となるため、チャネル長が $3\mu\text{m}$ より短い場合も、 $10^{-12}\text{A}$ 以下となることが期待される。従って、n型アモルファスIGZO膜を素子分離領域の半導体膜とし、素子分離用電極に-1V以下の負電圧を印加すると、素子間の距離が $3\mu\text{m}$ 、あるいはそれ以下の場合でも、リーク電流を $10^{-12}\text{A}$ 以下に抑えることが可能である。この低いリーク電流は、前述の通り、アモルファスIGZO膜の広いバンドギャップに起因する。

#### 【0048】

次に、本発明に係る電子装置の素子分離方法の一実施形態について説明する。

#### 【0049】

本実施形態の電子装置の素子分離方法は、半導体膜を含む電子素子を複数備えた電子装置の素子間に、半導体膜、絶縁体膜及び素子分離電極を有する素子分離領域が存在し絶縁体膜によって素子分離領域の半導体膜と隔てられた素子分離電極に一定電圧を印加する。素子分離領域の半導体膜は、バンドギャップが1.95eV以上である半導体膜である。上記のように素子分離電極に一定電圧を印加することにより、素子分離領域の半導体膜を高抵抗化し、電子素子間を電気的に分離する。素子分離領域の半導体膜としては、バンドギャップが1.95eV以上、より好ましくは2.5eV以上の、金属酸化物半導体、化合物半導体等を用いる。半導体膜、絶縁体膜、素子分離電極の材料としては、上記に挙げた材料が用いられる。

#### 【0050】

続いて、本発明に係る電子装置の製造方法の一実施形態について説明する。

#### 【0051】

本実施形態の電子装置の製造方法は、半導体膜を含む電子素子を複数備える電子装置の製造方法であって、バンドギャップが1.95eV以上である半導体膜を形成する工程、絶縁体膜を形成する工程及び素子分離電極を形成する工程を実施する。これらの工程を実施することにより、素子分離電極が絶縁体膜によってバンドギャップが1.95eV以上である半導体膜と隔てられ、バンドギャップが1.95eV以上である半導体膜、絶縁体膜及び素子分離電極を有する素子分離領域を形成する。素子分離電極には一定電圧が印加されて素子分離領域の半導体膜を高抵抗化し、電子素子間を電気的に分離する。素子分離領域の半導体膜としては、バンドギャップが1.95eV以上、より好ましくは2.5eV以上の、金属酸化物半導体、化合物半導体等を用いる。半導体膜、絶縁体膜、素子分離電極の材料としては、上記に挙げた材料が用いられる。

#### 【0052】

最後に、本発明に係る電子装置を用いた表示装置の一実施形態について説明する。

#### 【0053】

本実施形態の電子装置を用いた表示装置は、アクティブマトリックス型表示装置の構成要素としてTFTを含み、TFT間に素子分離領域が存在し、絶縁体膜によって素子分離領域の半導体膜と隔てられた素子分離電極に一定電圧を印加する。素子分離領域の半導体膜は、バンドギャップが1.95eV以上である半導体膜である。上記のように素子分離電極に一定電圧を印加することにより、素子分離領域の半導体膜を高抵抗化し、TFT

10

20

30

40

50

間の素子分離を実現する。更に本実施形態の表示装置は、表示素子として有機EL素子を備え、有機EL素子の輝度を電気的に制御する。本実施形態では、素子分離領域の半導体膜とTFTの半導体膜とを共通にすることもでき、素子分離領域の半導体膜とTFTの半導体膜とを共通にすれば、異なるTFTのソース・ドレイン端子の間隔、あるいは素子分離電極の幅により素子分離領域を決定できる。従って、本実施形態の表示装置は、半導体膜のパターニング工程の削減、及び素子分離領域面積の低減が可能となり、製造コストの低減及び高精細化を可能とする。

#### 【0054】

以上、本発明の好適な実施形態を説明したが、これは本発明の説明のための例示であり、本発明の要旨を逸脱しない範囲で、上記実施形態とは異なる種々の態様で実施することができる。10

#### 【0055】

例えば、上記の実施形態では、表示素子として有機EL素子を例示したが、表示素子は液層セルを用いることもできる。この場合には、別途バックライトとして、例えばEL素子等を備える必要がある。

#### 【実施例】

#### 【0056】

以下に、実施例を示して、本発明に係る電子装置をより詳細に説明するが、本発明はこれらの実施例に限定されない。

#### 【0057】

##### 〔実施例1〕

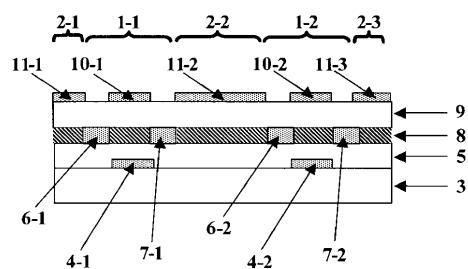

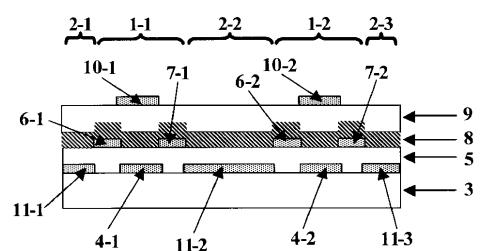

図3から図5を参照して、本実施例の電子装置の構成を説明する。図3は、本実施例の電子装置の積層構成を模式的に示す概略断面図である。図4は、本実施例の電子装置におけるTFTの伝達特性を示す説明図である。図5は、本実施例の変形例として、ボトムゲート・コプラナー型TFTを含む電子装置の積層構成を模式的に示す概略断面図である。

#### 【0058】

本実施例の電子装置は、素子分離領域の半導体膜とTFTの半導体膜を一体形成し、遮光膜と同一膜である素子分離電極に電圧を印加することにより素子分離を行う、逆スタガ型TFTを含む電子装置である。即ち図3に示すように、半導体膜8としてバンドギャップが約3eVのアモルファスIGZO膜を用い、2つの逆スタガ（ボトムゲート）型TFT素子1-1、1-2と、電界効果による素子分離領域2-1～2-3とを備える。30

#### 【0059】

まず、ガラス基板3（コーニング社製1737）上に、スパッタ法により膜厚100nmのMo膜を堆積し、フォトリソグラフィ法とドライエッチングによりパターニングしてゲート端子4-1、4-2を形成した。

#### 【0060】

次に、ゲート絶縁体膜5として、CVD法により膜厚200nmのアモルファスSiO<sub>x</sub>膜を堆積した。その上に、スパッタ法により膜厚30nmのITO（インジウム錫酸化物）膜を堆積し、フォトリソグラフィ法とウエットエッチングによりパターニングしてソース端子6-1、6-2及びドレイン端子7-1、7-2を形成した。40

#### 【0061】

続いて、半導体膜8（素子分離領域の半導体膜及びTFTの半導体膜）として、スパッタ法により膜厚30nmのアモルファスIGZO膜を室温にて堆積した。その際、スパッタガスとして酸素流量比2%の酸素アルゴン混合ガスを用い、酸素アルゴン混合ガスの全圧は $5.0 \times 10^{-1}$ Paとした。

#### 【0062】

さらに、絶縁体膜9として、CVD法により膜厚200nmのアモルファスSiO<sub>x</sub>膜を堆積した。

#### 【0063】

その後、スパッタ法により膜厚200nmのMo膜を堆積し、フォトリソグラフィ法と50

ドライエッティングによりパターニングして遮光膜 10 - 1、10 - 2 と素子分離電極 11 - 1 ~ 11 - 3 を同時に形成した。

#### 【0064】

最後に、大気中で 250 °C、1 時間の熱処理を行なった。以上の一連の工程により、図 3 の積層構成の電子装置を形成した。

#### 【0065】

本実施例の電子装置における TFT の伝達特性を図 4 に示す。なお、図 4 の伝達特性において、TFT のチャネル長は 10 μm、チャネル幅は 60 μm、ソース端子電圧は 0 V、ドレイン端子電圧は 12 V であり、遮光膜の電圧は 0 V である。

#### 【0066】

図 4 に示すように、本実施例における TFT も、前述した図 2 の TFT の伝達特性と同様に、ゲート端子に -2 V 以下の電圧を印加すると、半導体膜が空乏化して抵抗率は  $10^7 \Omega \cdot cm$  以上となり、ドレイン電流が  $10^{-12} A$  以下に抑えることができた。従って、幅 10 μm 以上の素子分離電極 11 - 2 に、-2 V 以下の負電圧を印加した場合、TFT 素子 1 - 1 のドレイン端子 7 - 1 と、TFT 素子 1 - 2 のソース端子 6 - 2 の間に流れるリーケ電流は  $10^{-12} A$  以下となり、実用上十分な素子分離機能を有する。

10

#### 【0067】

半導体電子素子をパターニングして素子分離を行う場合は、一般に隣り合う TFT 間の距離は 10 μm 以上になるが、本実施例では隣り合う TFT 間の距離を 5 μm 以下にすることが可能となる。また、半導体電子素子のパターニング工程が省略されたことにより、より低コストで TFT を含む電子装置を製造することができる。

20

#### 【0068】

本実施例では、TFT はボトムコンタクト型のソース・ドレイン端子を備えているが、ソース・ドレイン端子はトップコンタクト型でも良く、図 5 のような低抵抗の半導体膜をソース・ドレイン端子とするコプラナー構造でも良い。即ち図 5 は、半導体膜 8（素子分離領域の半導体膜及び TFT の半導体膜）を一体形成し、遮光膜 10 - 1、10 - 2 と同一膜である素子分離電極 11 - 1 ~ 11 - 3 に一定電圧を印加して素子分離を行うボトムゲート・コプラナー型 TFT を含む電子装置である。

#### 【0069】

また、本実施例における TFT は遮光膜を備えているが、遮光膜は必ずしも必要ではない。遮光膜を備える場合、遮光膜に印加する電圧は、素子分離電極と同電圧でも良く、異なる電圧でも良い。また、遮光膜を備える場合、本実施例の構造では素子分離電極は遮光膜と一緒に成膜、パターニングすることが可能であり、素子分離電極を導入することによる工程数の増加は生じない。

30

#### 【0070】

##### 〔実施例 2〕

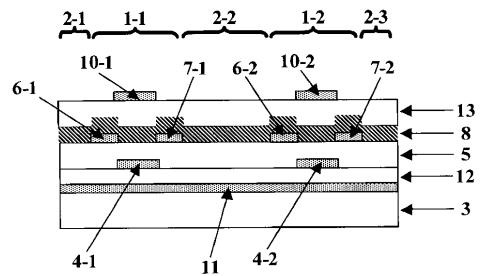

図 6 及び図 7 を参照して、本実施例の電子装置の構成を説明する。図 6 は、本実施例の電子装置の積層構成を模式的に示す概略断面図である。図 7 は、本実施例の変形例として、素子分離電極のパターニングを行なわない場合の電子装置の積層構成を模式的に示す概略断面図である。

40

#### 【0071】

本実施例の電子装置は、素子分離領域の半導体膜と TFT の半導体膜を一体形成し、ゲート端子の下部に形成した素子分離電極に電圧を印加することにより素子分離を行う逆スタガ型 TFT を含む電子装置である。即ち図 6 に示すように、本実施例の電子装置は、半導体膜 8 としてバンドギャップが約 3 eV のアモルファス IGZO 膜を用いる 2 つの逆スタガ型 TFT 素子 1 - 1、1 - 2 と、電界効果による素子分離領域 2 - 1 ~ 2 - 3 を備える。

#### 【0072】

まず、ガラス基板 3（コーニング社製 1737）上に、スパッタ法により膜厚 100 nm の Mo 膜を堆積し、フォトリソグラフィ法とドライエッティングによりパターニングして

50

素子分離電極 11 - 1 ~ 11 - 3 を形成した。

【0073】

次に、第一の絶縁体膜 12 として、CVD法により膜厚 200 nm のアモルファス SiO<sub>x</sub> 膜を堆積した。再度、スパッタ法により膜厚 100 nm のMo 膜を堆積し、フォトリソグラフィ法とドライエッチングによりパターニングしてゲート端子 4 - 1、4 - 2 を形成した。

【0074】

さらに、ゲート絶縁体膜 5 として、CVD法により膜厚 200 nm のアモルファス SiO<sub>x</sub> 膜を堆積した。その上に、スパッタ法により膜厚 30 nm のITO 膜を堆積し、フォトリソグラフィ法とウエットエッチングによりパターニングすることでソース端子 6 - 1、6 - 2 及びドレイン端子 7 - 1、7 - 2 を形成した。

10

【0075】

続いて、半導体膜 8 (素子分離領域の半導体膜及びTFTの半導体膜) として、スパッタ法により膜厚 30 nm のアモルファスIGZO 膜を室温にて堆積した。その際、スパッタガスとして酸素流量比 2 % の酸素アルゴン混合ガスを用い、酸素アルゴン混合ガスの全圧は  $5.0 \times 10^{-1}$  Pa とした。

【0076】

さらに、第二の絶縁体膜 13 として、CVD法により膜厚 200 nm のアモルファス SiO<sub>x</sub> 膜を堆積した。

20

【0077】

その後、スパッタ法により膜厚 200 nm のMo 膜を堆積し、フォトリソグラフィ法とドライエッチングによりパターニングして遮光膜 10 - 1、10 - 2 を形成した。以上の一連の工程により、図 6 の積層構成の電子装置を形成した。

【0078】

本実施例では、半導体膜のエッチングプロセスを用いることなく素子分離領域の半導体膜と TFT の半導体膜を一体形成した図 6 に示す逆スタガ型の TFT 素子を完成することが可能である。

【0079】

本実施例の電子装置では、実施例 1 と同様に、TFT 素子 1 - 1 のドレイン端子 7 - 1 と、TFT 素子 1 - 2 のソース端子 6 - 2 の間に流れるリーク電流を  $10^{-12}$  A 以下に抑えることができ、実用上十分な素子分離機能を有する。

30

【0080】

半導体電子素子をパターニングして素子分離を行う場合、一般に隣り合う TFT 間の距離は 10 μm 以上になるが、本実施例を用いることで隣り合う TFT 間の距離を 5 μm 以下にすることが可能である。

【0081】

本実施例の素子分離電極 11 - 1 ~ 11 - 3 は、図 7 に示すようにパターニングを行なわなくても良い。即ち図 7 は、半導体膜 8 (素子分離領域の半導体膜及びTFTの半導体膜) を一体形成し、ゲート端子 4 - 1、4 - 2 の下部にパターニングを行わずに形成した素子分離電極 11 に電圧を印加して素子分離を行う逆スタガ型 TFT を含む電子装置である。このように素子分離電極 11 のパターニングを行なわない場合、素子分離領域は、TFT 素子 1 - 1 のドレイン端子 7 - 1 と TFT 素子 1 - 2 のソース端子 6 - 2 の間隔となる。このとき、ソース・ドレイン端子のパターニング精度により、最小の素子分離領域の大きさが決まる。

40

【0082】

また、図 6 における TFT はボトムコンタクト型のソース・ドレイン端子を備えているが、ソース・ドレイン端子はトップコンタクト型でも良く、図 5 に示したコプラナー構造でも良い。

【0083】

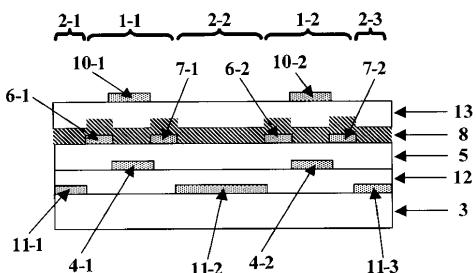

〔実施例 3〕

図8を参照して、本実施例の電子装置の構成を説明する。図8は、本実施例の電子装置の積層構成を模式的に示す概略断面図である。

#### 【0084】

本実施例の電子装置は、素子分離領域の半導体膜とTFTの半導体膜を一体形成し、半導体の下部に形成した遮光膜と同一膜である素子分離電極に電圧を印加することにより素子分離領域を形成したスタガ型TFTを含む電子装置である。即ち図8に示すように、本実施例の電子装置は、半導体膜8としてバンドギャップが約3eVのアモルファスIGZO膜を用いる2つのスタガ(トップゲート)型TFT素子1-1、1-2と、電界効果による素子分離領域2-1~2-3を備える。

#### 【0085】

まず、ガラス基板3(コーニング社製1737)上に、スパッタ法により膜厚200nmのMo膜を堆積した。続いて、フォトリソグラフィ法とドライエッチングによりMoをパターニングして遮光膜10-1、10-2と素子分離電極11-1~11-3を同時に形成した。

#### 【0086】

次に、絶縁体膜9として、CVD法により膜厚200nmのアモルファスSiO<sub>x</sub>膜を堆積した。その上に、スパッタ法により膜厚30nmのITO膜を堆積し、フォトリソグラフィ法とウエットエッチングによりパターニングしてソース端子6-1、6-2及びドレイン端子7-1、7-2を形成した。

#### 【0087】

続いて、半導体膜8(素子分離領域の半導体膜及びTFTの半導体膜)として、スパッタ法により膜厚30nmのアモルファスIGZO膜を室温にて堆積した。その際、スパッタガスとして酸素流量比2%の酸素アルゴン混合ガスを用い、酸素アルゴン混合ガスの全圧は $5.0 \times 10^{-1}$ Paとした。

#### 【0088】

さらに、ゲート絶縁体膜5として、CVD法により膜厚200nmのアモルファスSiO<sub>x</sub>膜を堆積した。その後、スパッタ法により膜厚100nmのMo膜を堆積し、フォトリソグラフィ法とドライエッチングによりパターニングしてゲート端子4-1、4-2を形成した。以上の一連の工程により、図8の積層構成の電子装置を形成した。

#### 【0089】

本実施例では、半導体膜のエッチングプロセスを用いることなく素子分離領域の半導体膜とTFTの半導体膜を一体形成した図8に示すスタガ型のTFT素子を完成することが可能である。

#### 【0090】

本実施例の電子装置では、実施例1と同様に、TFT素子1-1のドレイン端子7-1と、TFT素子1-2のソース端子6-2の間に流れるリーク電流を $10^{-12}$ A以下に抑えることができ、実用上十分な素子分離機能を有する。

#### 【0091】

半導体電子素子をパターニングして素子分離を行う場合、一般に隣り合うTFT間の距離は10μm以上になるが、本実施例の手法を用いることで隣り合うTFT間の距離を5μm以下にすることが可能である。半導体電子素子のパターニング工程が省略されたことにより、より低コストでTFTを含む電子装置を製造することが可能である。

#### 【0092】

本実施例において、遮光膜を備える場合、遮光膜に印加する電圧は、素子分離電極と同電圧でも良く、異なる電圧でも良い。また、実施例1及び実施例2と同様に、遮光膜を備える場合、本実施例の構造では素子分離電極は遮光膜と同時に成膜、パターニングすることが可能であり、素子分離電極の導入による工程数の増加は生じない。

#### 【0093】

また、実施例2の図7の素子分離電極と同様に、素子分離電極と遮光膜を共通にすることも可能である。さらに、本実施例の図8におけるTFTはボトムコンタクト型のソース

10

20

30

40

50

・ドレイン端子を備えているが、ソース・ドレイン端子はトップコンタクト型でも良く、前述の図5のコプラナー構造でも良い。

#### 【0094】

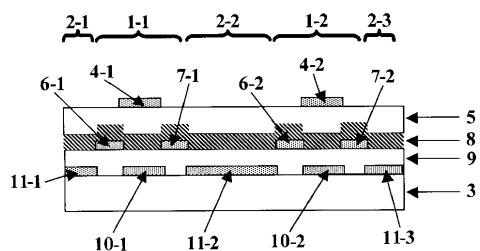

##### 〔実施例4〕

図9を参照して、本実施例の電子装置の構成を説明する。図9は、本実施例の電子装置の積層構成を模式的に示す概略断面図である。

#### 【0095】

本実施例の装置は、素子分離領域の半導体膜とTFTの半導体膜を一体形成し、ゲート端子と同一膜である素子分離電極に電圧を印加することにより素子分離領域を形成した逆スタガ型TFTを含む電子装置である。即ち図9に示すように、本実施例の電子装置は、半導体膜8としてバンドギャップが約3eVのアモルファスIGZO膜を用いる2つの逆スタガ型TFT素子1-1、1-2と、電界効果による素子分離領域2-1～2-3を備える。

10

#### 【0096】

まず、ガラス基板3(コーニング社製1737)上に、スパッタ法により膜厚100nmのMo膜を堆積した。続いて、フォトリソグラフィ法とドライエッチングにより、Moをパターニングすることでゲート端子4-1、4-2と、素子分離電極11-1～11-3を同時に形成した。

#### 【0097】

次に、ゲート絶縁体膜5として、CVD法により膜厚200nmのアモルファスSiO<sub>x</sub>膜を堆積した。その上に、スパッタ法により膜厚30nmのITO膜を堆積し、フォトリソグラフィ法とウエットエッチングによりパターニングしてソース端子6-1、6-2及びドレイン端子7-1、7-2を形成した。

20

#### 【0098】

続いて、半導体膜8(素子分離領域の半導体膜及びTFTの半導体膜)として、スパッタ法により膜厚30nmのアモルファスIGZO膜を室温にて堆積した。その際、スパッタガスとして酸素流量比2%の酸素アルゴン混合ガスを用い、酸素アルゴン混合ガスの全圧は $5.0 \times 10^{-1}$ Paとした。

#### 【0099】

さらに、絶縁体膜9として、CVD法により膜厚200nmのアモルファスSiO<sub>x</sub>膜を堆積した。その後、膜厚200nmのMo膜をスパッタ法により堆積し、フォトリソグラフィ法とドライエッチングによりパターニングして遮光膜10-1、10-2を形成した。以上の一連の工程により、図9の積層構成の電子装置を形成した。

30

#### 【0100】

本実施例では、半導体膜のエッチングプロセスを用いることなく素子分離領域の半導体膜とTFTの半導体膜を一体形成した図9に示す逆スタガ型のTFT素子を完成することが可能である。

#### 【0101】

本実施例の電子装置では、実施例1と同様に、TFT素子1-1のドレイン端子7-1と、TFT素子1-2のソース端子6-2の間に流れるリーク電流を $10^{-12}$ A以下に抑えることができ、実用上十分な素子分離機能を有する。

40

#### 【0102】

半導体電子素子をパターニングして素子分離を行う場合、一般に隣り合うTFT間の距離は10μm以上になるが、本実施例の手法を用いることで隣り合うTFT間の距離を5μm以下にすることが可能である。半導体電子素子のパターニング工程が省略されたことにより、より低コストでTFTを含む電子装置を製造することが可能である。

#### 【0103】

本実施例の積層構造では、素子分離電極はゲート端子と同時に成膜、パターニングすることが可能であり、遮光膜がない場合でも、素子分離電極を導入することによる工程数の増加が生じない。

50

## 【0104】

また、本実施例の図9におけるTFTはボトムコンタクト型のソース・ドレイン端子を備えているが、ソース・ドレイン端子はトップコンタクト型でも良く、前述の図5のコブラナー構造でも良い。

## 【符号の説明】

## 【0105】

1 - 1、1 - 2 : TFT素子、2 - 1 ~ 2 - 3 : 素子分離領域、4 - 1、4 - 2 : ゲート端子、5 : ゲート絶縁体膜、6 - 1、6 - 2 : ソース端子、7 - 1、7 - 2 : ドレイン端子、8 : 半導体膜、9 : 絶縁体膜、11、11 - 1 ~ 11 - 3 : 素子分離電極

【図1】

【図3】

【図2】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9】

---

フロントページの続き

(72)発明者 林 享

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 雲見 日出也

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 右田 勝則

(56)参考文献 特開平11-317506(JP,A)

特開2000-223701(JP,A)

特開2000-323484(JP,A)

特開2006-114859(JP,A)

特開2005-072610(JP,A)

特表2008-544522(JP,A)

特開2007-109918(JP,A)

特開2006-120885(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/76

G09F 9/30

G09F 9/35

H01L 21/336

H01L 29/786