(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-8772

(P2010-8772A)

(43) 公開日 平成22年1月14日(2010.1.14)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>G03F 1/08</b> (2006.01)   | G03F 1/08  | A 2H095     |

| <b>H01L 21/027</b> (2006.01) | H01L 21/30 | 502P 5FO38  |

| <b>H01L 21/822</b> (2006.01) | H01L 27/04 | D 5FO64     |

| <b>H01L 27/04</b> (2006.01)  | H01L 21/82 | W           |

| <b>H01L 21/82</b> (2006.01)  |            |             |

審査請求 未請求 請求項の数 10 O L (全 12 頁)

|           |                              |          |                                                      |

|-----------|------------------------------|----------|------------------------------------------------------|

| (21) 出願番号 | 特願2008-168725 (P2008-168725) | (71) 出願人 | 308014341<br>富士通マイクロエレクトロニクス株式会社<br>東京都新宿区西新宿二丁目7番1号 |

| (22) 出願日  | 平成20年6月27日 (2008.6.27)       | (74) 代理人 | 100068755<br>弁理士 恩田 博宣                               |

|           |                              | (74) 代理人 | 100105957<br>弁理士 恩田 誠                                |

|           |                              | (72) 発明者 | 鈴木 健次<br>愛知県春日井市高蔵寺町二丁目1844番<br>2 富士通VLSI株式会社内       |

|           |                              | (72) 発明者 | 堀江 志定<br>愛知県春日井市高蔵寺町二丁目1844番<br>2 富士通VLSI株式会社内       |

最終頁に続く

(54) 【発明の名称】 レチクルデータ作成方法、レチクルデータ作成装置及びウェハ

## (57) 【要約】

【課題】マルチダイ用レチクルを使用して製造されるチップの歩留まりを向上させ得るマルチダイ用レチクルのデータ作成方法を提供する。

【解決手段】プロセスパターンからメインチップの未配置領域を検出する工程と、未配置領域を矩形に分割する工程と、分割された矩形をダミーチップとしてスクリーブデータを発生させる工程と、ダミーチップにダミーパターンを発生させる工程とを備えた。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

プロセスパターンからメインチップの未配置領域を検出する工程と、

前記未配置領域を矩形に分割する工程と、

前記分割された矩形をダミーチップとしてスクライブデータを発生させる工程と、

前記ダミーチップにダミーパターンを発生させる工程と

を備えたことを特徴とするレチカルデータ作成方法。

**【請求項 2】**

前記ダミーパターンとして、少なくとも 1 層の金属配線を生成することを特徴とする請求項 1 記載のレチカルデータ作成方法。 10

**【請求項 3】**

前記ダミーパターンとして、メインチップと同一の配線層を生成することを特徴とする請求項 1 記載のレチカルデータ作成方法。

**【請求項 4】**

前記ダミーチップのスクライブデータを発生させる工程において、

前記ダミーチップのスクライブ領域にすべてのマークを配置できるか否かを判定する工程と、

すべてのマークを配置できないとき、前記ダミーチップの領域内に前記マークを配置する工程と

を備えたことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載のレチカルデータ作成方法。 20

**【請求項 5】**

前記未配置領域を矩形に分割する工程において、

前記未配置領域を分割する方向は、前記メインチップのスクライブ領域の幅が広い方向に一致させる方向とすることを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載のレチカルデータ作成方法。

**【請求項 6】**

プロセスパターンからメインチップの未配置領域を検出する未配置領域検出手段と、

前記未配置領域を矩形に分割する矩形分割手段と、

前記分割された矩形をダミーチップとしてスクライブデータを発生させるスクライブデータ発生手段と、

前記ダミーチップにダミーパターンを発生させるダミーパターン発生手段と

を備えたことを特徴とするレチカルデータ作成装置。 30

**【請求項 7】**

前記スクライブデータ発生手段は、

前記ダミーチップのスクライブ領域にすべてのマークを配置できるか否かを判定する判定手段と、

すべてのマークを配置できないとき、前記ダミーチップの領域内に前記マークを配置する再配置手段と

を備えたことを特徴とする請求項 6 記載のレチカルデータ作成装置。 40

**【請求項 8】**

前記未配置領域検出手段で検出された未配置領域データを格納する記憶手段と、

前記矩形分割手段で矩形に分割された未配置領域データを格納する記憶手段と、

前記プロセスパターンのマークデータを格納した記憶手段と、

前記ダミーパターンを発生させるためのルールを格納した記憶手段と

を備えたことを特徴とする請求項 6 又は 7 記載のレチカルデータ作成装置。

**【請求項 9】**

請求項 1 乃至 5 のいずれか 1 項に記載のレチカルデータ作成方法に基づいて生成されたレチカルを使用して露光処理を行うことを特徴とするウェハ。

**【請求項 10】**

10

20

30

40

50

メインチップの未配置領域を矩形に分割した矩形分割領域を備えたダミーチップと、前記ダミーチップに設けたダミーパターンとを備えたことを特徴とするウェハ。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、半導体装置の露光工程で使用するレチクルを作成するためのデータ作成方法に関するものである。

【背景技術】

【0002】

近年の半導体集積回路装置の微細化によるレチクルコストの高騰にともない、複数の異なる種類のチップを1つのレチクルで露光するマルチチップ用レチクルが採用されている。また、マルチチップの中でも、チップの種類が異なるだけでなく、サイズも異なるチップを同一レチクルで露光するマルチダイ用レチクルも採用されている。

【0003】

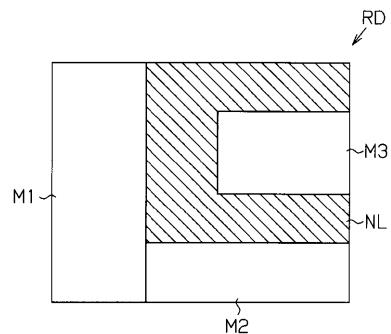

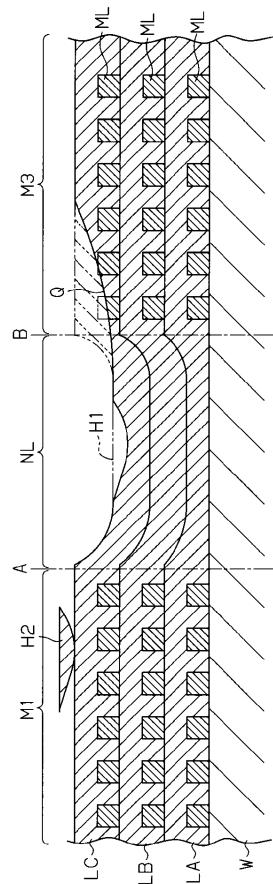

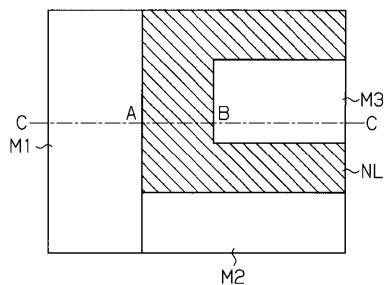

図16は、マルチダイ用レチクルのイメージを示す。図中、M1, M2, M3は、メインチップを露光するためのパターン、すなわち基板に所要のデバイスパターンを露光するためのパターンが生成される領域であり、さらに多数層の配線層を露光するための露光パターンが生成される領域である。

【0004】

メインチップ領域M1～M3以外の領域は、チップが形成されない未配置領域NLであり、デバイスを露光するための露光パターン及び配線層を露光するための露光パターンは生成されず、基板上には配線間絶縁層のみが積層され、配線層は生成されない。

【0005】

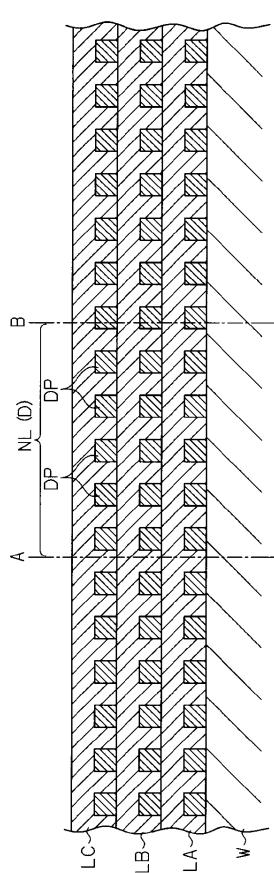

図15は、上記のようなマルチダイ用レチクルを使用して形成されたウェハ基板Wのメインチップ領域及び未配置領域の断面図を示し、図16におけるC-C線に対応する基板断面を示す。同図に示すように、メインチップ領域M1, M3では複数層の配線層LA～LCにおいてそれぞれ金属配線MLが形成されるが、未配置領域NLでは、配線間絶縁層のみが積層されている。

【0006】

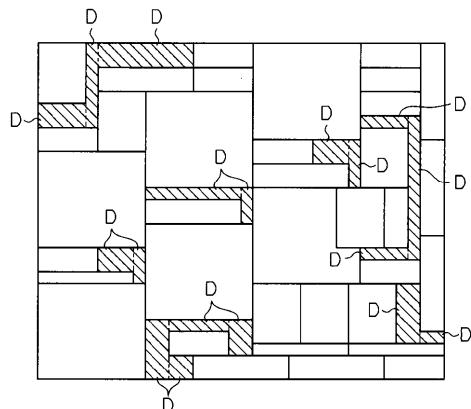

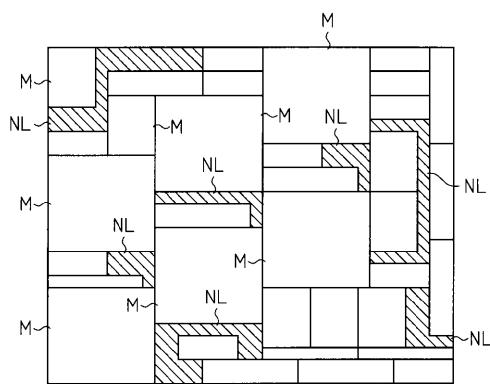

図17は、マルチダイ用レチクルのCADデータイメージを示す。種々のメインチップMとともに、いろいろな形状の未配置領域NLが点在している。

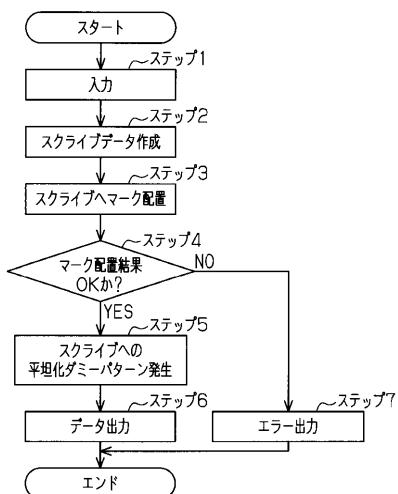

上記のようなマルチダイ用レチクルを生成するためのCADデータを生成する工程におけるスクライブデータの作成工程を図18に示す。

【0007】

まず、プロセス仕様データ及びプロセスパターンマークデータを取り込み（ステップ1）、スクライブラインを生成するためのデータを作成する（ステップ2）。次いで、スクライブラインにアライメントマークや検査マーク等のマークを配置する（ステップ3）。

【0008】

そして、スクライブライン上に各マークを配置できた場合には、スクライブラインとメインチップ領域とを平坦化するためのダミーパターンをスクライブライン上に生成し（ステップ4, 5）、生成されたCADデータを出力して（ステップ6）、データ生成工程を終了する。

【0009】

また、ステップ4において、スクライブラインに各マークを配置できない場合には、エラーを出力して（ステップ7）、終了する。

このような処理により、スクライブライン上へ各種マークを配置し、スクライブ領域とメインチップ領域とを平坦化する処理が行われる。

【特許文献1】特開昭56-12644号公報

【特許文献2】特開昭63-236045号公報

10

20

30

40

50

【特許文献3】特開昭62-54921号公報

【特許文献4】特開2000-147742号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

図15に示すように、上記のようなマルチダイ用レチクルで生成されたウェハ基板Wでは、未配置領域NLに金属配線MLが形成されないことから、メインチップ領域M1,M3と未配置領域NLとの間に段差が発生する。近年、配線層が多層化されている現状では、この段差によりメインチップ領域の配線間絶縁層に凹み部Qが生じ、金属配線の絶縁不良の原因となる。

【0011】 10

また、未配置領域NLでは配線間絶縁層のみが積層されているが、近年の配線層の多層化により、配線間絶縁層に物理的に脆弱な低誘電率物質が使用されている現状では、ダイシング時に未配置領域NLで配線間絶縁層が剥がれH1が発生し、その剥がれた低誘電率物質が飛散すると、その飛散物H2がチップの歩留まりを低下させる原因となる。

【0012】 20

特許文献1～3には、同一レチクル上にパターンの異なる2種以上のチップのパターンを生成するフォトマスクが開示されている。いずれもマルチダイ用レチクルの未配置領域に起因する上記のような問題点の開示はなく、またその問題点を解決する手段を示唆するものではない。

【0013】 20

特許文献4には、マルチダイ用レチクルのCADデータ作成方法が開示されている。しかし、デバイス領域に隣接して最適なスクライプ領域を確保するための処理であり、未配置領域に起因する上記のような問題点を解決する手段は開示されていない。

【0014】 30

この発明の目的は、マルチダイ用レチクルを使用して製造されるチップの歩留まりを向上させ得るマルチダイ用レチクルのデータ作成方法を提供することにある。

【課題を解決するための手段】

【0015】 30

上記目的は、プロセスパターンからメインチップの未配置領域を検出する工程と、前記未配置領域を矩形に分割する工程と、前記分割された矩形をダミーチップとしてスクライプデータを発生させる工程と、前記ダミーチップにダミーパターンを発生させる工程とを備えたレチクルデータ作成方法により達成される。

【発明の効果】 40

【0016】 40

開示されたマルチダイ用レチクルのデータ作成方法では、マルチダイ用レチクルを使用して製造されるチップの歩留まりを向上させることができる。

【発明を実施するための最良の形態】 40

【0017】 40

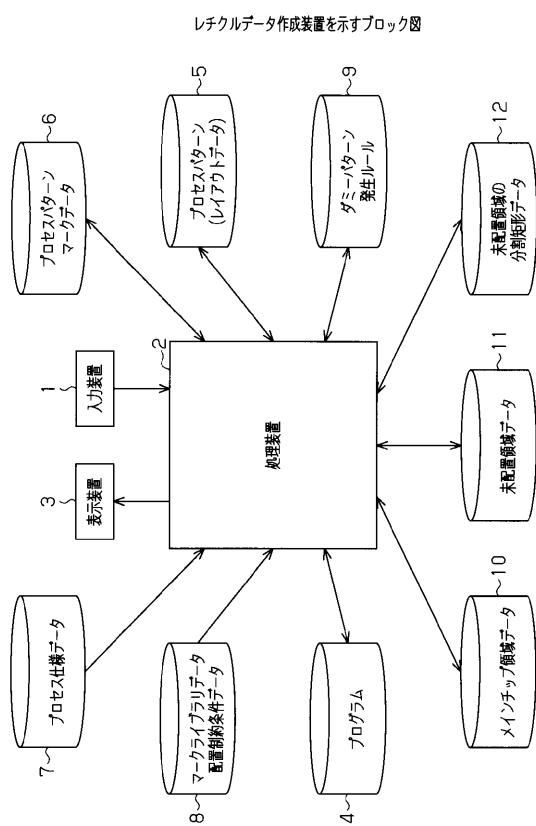

以下、この発明を具体化した一実施の形態を図面に従って説明する。図1は、マルチダイ用レチクルのCADデータ作成装置を示す。入力装置1は、処理装置(未配置領域検出手段、矩形分割手段、スクライプデータ発生手段、ダミーパターン発生手段、判定手段、再配置手段)2に種々の処理動作を指示するための入力信号を入力可能である。表示装置3は、前記処理装置2で生成されたCADデータを図形として表示する。

【0018】 40

前記処理装置2は、記憶手段としてファイル4～12が接続される。そして、ファイル4に格納されている処理プログラムに基づいてマルチダイ用レチクルのCADデータ生成処理を行う。

【0019】 50

ファイル5には、マルチダイ用レチクルを作成するための多数のメインチップのプロセ

パターン(レイアウトデータ)が格納され、前記処理装置2はそのプロセスパターンを取り込んでCADデータの生成処理を行う。

【0020】

ファイル6にはプロセスパターンマークデータが格納され、前記処理装置2はそのプロセスパターンマークデータを取り込んで、スクライプ領域へのアライメントマークあるいは検査マーク等の配置を行う。

【0021】

ファイル7にはプロセス仕様データが格納され、処理装置2は当該プロセス仕様に沿ってCADデータの生成処理を行う。

ファイル8にはスクライプ領域に配置するマークに関するライブラリデータと、各マークを配置する際の配置制約条件データが格納され、前記処理装置2はその配置制約条件データに基づいてマークの配置処理を行う。

【0022】

ファイル9にはダミーパターン発生ルールが格納され、前記処理装置2はそのダミーパターン発生ルールに従って未配置領域あるいはスクライプ領域にダミーパターンを生成する。

【0023】

ファイル10には前記処理装置2で生成されたメインチップ領域データが一時的に格納される。また、ファイル11には前記処理装置2で生成された未配置領域データが一時的に格納される。

【0024】

ファイル12には前記処理装置2で生成された未配置領域の分割矩形データが一時的に格納される。

次に、上記のようなCADデータ作成装置の処理装置2でレチクルのチップ未配置領域へのデータ生成動作を図2～図4に示すフローチャートと図5～図12に示すレチクルイメージを示す説明図に基づいて説明する。

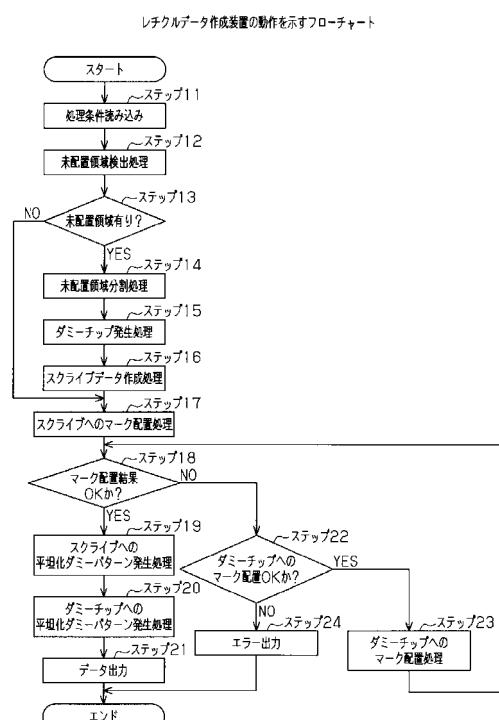

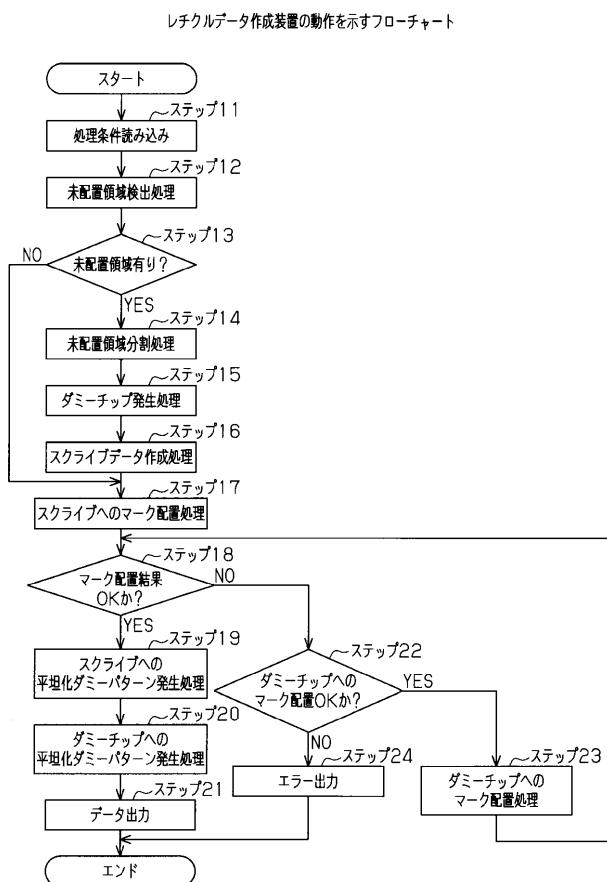

【0025】

図2に示すように、CADデータの生成処理が開始されると、前記処理装置2への処理条件の読み込みが行われる(ステップ11)。ここでは、ファイル5に格納されているプロセスパターン、ファイル7に格納されているプロセス仕様データ等が処理装置2に取り込まれる。

【0026】

次いで、ステップ12に移行して未配置領域の検出処理が行われる。ここでは、図5に示す1ショットのレチクルデータRDについて説明する。図5において、M1～M3はチップを生成するためのメインチップ領域であり、そのメインチップ領域M1～M3間にチップが形成されない未配置領域NLが存在している。

【0027】

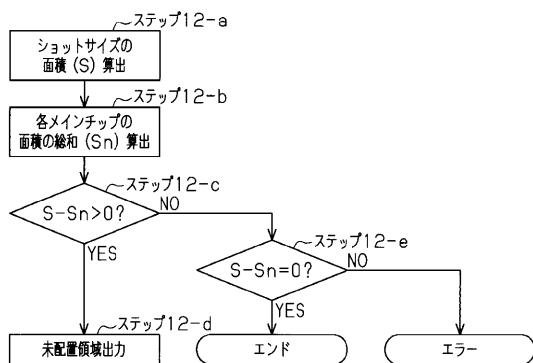

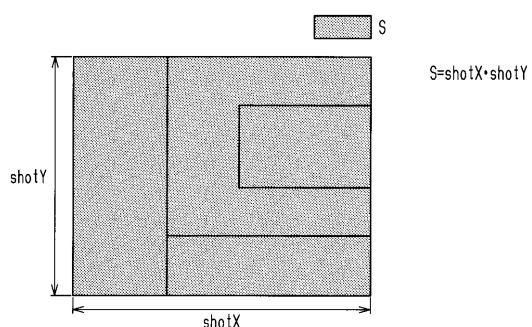

ステップ12の処理の詳細を図3に示す。すなわち、ステップ12ではまずレチクルデータRDのショットサイズの面積Sの算出が行われる(ステップ12-a)。その面積Sは、図6に示すように、レチクルデータのX軸方向の長さshotXとY軸方向の長さshotYとの積により算出される。

【0028】

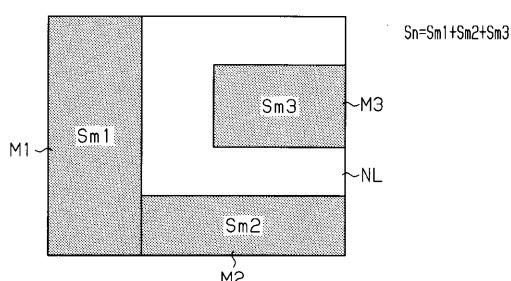

次いで、図7に示すように、前記メインチップ領域M1～M3の面積の総和Snを算出する(ステップ12-b)。各メインチップ領域M1～M3の面積Sm1, Sm2, Sm3は、ショットサイズの面積Sと同様に、各チップのX軸方向の長さとY軸方向の長さの積で算出される。そして、総和SnはSm1+Sm2+Sm3で算出される。

【0029】

次いで、ショットサイズの面積Sからメインチップ領域M1～M3の面積の総和Snを減算した値が0より大きいか否かを判定する(ステップ12-c)。そして、S-Snが0より大きい場合には未配置領域NLが存在するため、ステップ12-dに移行してその

10

20

30

40

50

未配置領域を出力してファイル 1 1 に一時的に格納する。

#### 【0 0 3 0】

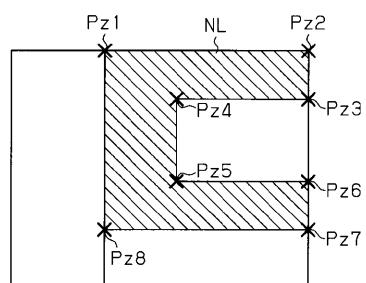

未配置領域 N L の出力は、図 8 に示すように、未配置領域 N L の各頂点 P z 1 ~ P z 8 の X - Y 座標を出力する。

ステップ 1 2 - c において、S - S n が 0 以下である場合にはステップ 1 2 - e に移行し、S - S n が 0 である場合には未配置領域 N L がないので、次のステップに移行する。また、S - S n が 0 未満である場合には、エラーを出力する。

#### 【0 0 3 1】

ステップ 1 2 で、未配置領域 N L が出力されると、ステップ 1 3 からステップ 1 4 に移行する。なお、ステップ 1 2 で未配置領域が出力されない場合には、ステップ 1 7 へ移行する。

10

#### 【0 0 3 2】

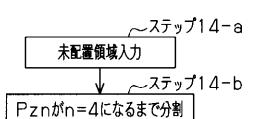

ステップ 1 4 では、未配置領域 N L の分割処理を行う。ステップ 1 4 の詳細を図 4 に示す。ステップ 1 4 - a では、ファイル 1 1 から未配置領域データを取り込み、ステップ 1 4 - b では未配置領域 N L を頂点 P z の数が 4 となる単純矩形に分割する。

20

#### 【0 0 3 3】

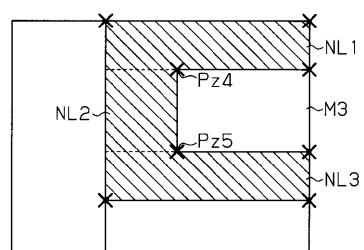

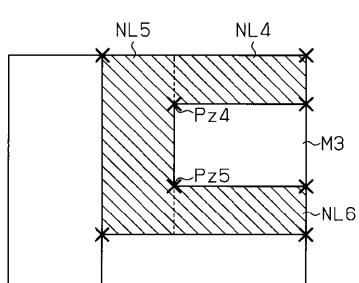

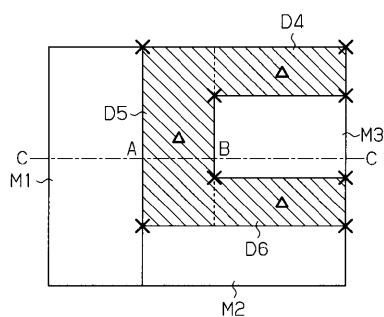

図 9 は、未配置領域 N L を頂点 P z 4 を含む X 軸方向の線分と、頂点 P z 5 を含む X 軸方向の線分で未配置領域（矩形分割領域）N L 1 ~ N L 3 に分割した例を示す。図 1 0 は、未配置領域 N L を頂点 P z 4 を含む Y 軸方向の線分と、頂点 P z 5 を含む Y 軸方向の線分で未配置領域（矩形分割領域）N L 4 ~ N L 6 に分割した例を示す。

20

#### 【0 0 3 4】

X 軸方向に分割するか Y 軸方向に分割するかは、メインチップ M 3 の X 軸方向のスクライプ領域の幅と Y 軸方向のスクライプ領域の幅の広い方に連なる線分を優先して選択する。スクライプ領域の幅の広い方を選択することにより、スクライプ領域に配置するマークの数を増加させることができるからである。

#### 【0 0 3 5】

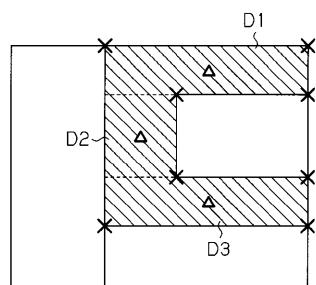

ついで、ステップ 1 5 に移行して、ダミーチップの発生処理を行う。図 1 1 では、分割した未配置領域 N L 1 ~ N L 3 をダミーチップ D 1 ~ D 3 とした場合を示し、図 1 2 は、未配置領域 N L 4 ~ N L 6 をダミーチップ D 4 ~ D 6 とした場合を示す。

30

#### 【0 0 3 6】

次いで、各ダミーチップ間のスクライプ領域のデータを作成し（ステップ 1 6）、そのスクライプ領域へマークを配置する処理を行う（ステップ 1 7）。

次いで、必要なマークを配置できたか否かを判定し（ステップ 1 8）、配置できている場合にはステップ 1 9 に移行して、スクライプ領域に平坦化用のダミーパターンを生成する。そして、ダミーチップ D 1 ~ D 3 あるいは同 D 4 ~ D 6 に平坦化用のダミーパターン生成する（ステップ 2 0）。

30

#### 【0 0 3 7】

そして、このように生成されたダミーチップのデータ及びダミーチップのスクライプ領域のデータを出力して（ステップ 2 1）、処理動作を終了する。

ステップ 1 8 において、必要なマークが配置できていない場合には、ステップ 2 2 に移行して、ステップ 1 5 で生成したダミーチップにマークを配置可能か否かをファイル 8 の配置制約条件データに基づいて判定する。そして、配置可能であれば、ダミーチップ領域にマークを配置し（ステップ 2 3）、再度ステップ 1 8 に移行して、マーク配置結果を判定する。

40

#### 【0 0 3 8】

また、ステップ 2 2 において、ダミーチップ領域へのマーク配置が不可となったときは、エラーを出力して（ステップ 2 4）処理動作を終了する。

図 1 3 は、上記のような処理により、未配置領域を矩形に分割し、さらに多数のダミーチップ D として平坦化ダミーパターンを生成した C A D データを示す。このような処理により、すべての未配置領域にダミーチップを生成可能としたレチカルデータが生成される

50

。

### 【0039】

上記のようなマルチダイ用レチクルの C A D データ作成装置及びその C A D データで作成されたレチクルを使用して作成されたウェハでは、次に示す作用効果を得ることができる。

(1) マルチダイ用レチクルのチップ未配置領域にダミーパターンを備えたダミーチップ領域を生成することができる。従って、このマルチダイ用レチクルで生成したウェハのメインチップ領域と未配置領域を平坦化することができる。

(2) 未配置領域にダミーパターンを備えたダミーチップをレイアウトすることができる。従って、図 14 に示すように、ウェハ上の未配置領域に形成されるダミーパターン D P により、未配置領域の配線間絶縁層の物理的強度を確保して、ダイシング時の配線間絶縁層の剥がれを防止することができる。10

(3) ダミーチップ領域にもプロセスパターンのマークを配置することができる。従って、ダイシング領域に配置しきれないマークをダミーチップ領域に配置して、マーク数の増大に対処することができる。

(4) 未配置領域を矩形に分割し、その矩形をダミーチップとしてスクライブ領域を生成するので、ウェハ基板上に形成されたメインチップ及びダミーチップは、スクライブ領域に沿ってダイシングすることにより容易に取り出すことができる。

### 【0040】

上記実施の形態は、以下の態様で実施してもよい。

- ・ダミーチップに生成するダミーパターンは、平坦化の観点からメインチップと同一数の配線層を形成することが望ましいが、少なくとも 1 層、任意の層に生成すれば、配線間絶縁層の剥がれを防止することができる。

### 【図面の簡単な説明】

#### 【0041】

【図 1】レチクルデータ作成装置を示すブロック図である。

【図 2】レチクルデータ作成装置の動作を示すフローチャートである。

【図 3】レチクルデータ作成装置の動作を示すフローチャートである。

【図 4】レチクルデータ作成装置の動作を示すフローチャートである。

【図 5】レチクルデータ作成処理動作を示す説明図である。30

【図 6】レチクルデータ作成処理動作を示す説明図である。

【図 7】レチクルデータ作成処理動作を示す説明図である。

【図 8】レチクルデータ作成処理動作を示す説明図である。

【図 9】レチクルデータ作成処理動作を示す説明図である。

【図 10】レチクルデータ作成処理動作を示す説明図である。

【図 11】レチクルデータ作成処理動作を示す説明図である。

【図 12】レチクルデータ作成処理動作を示す説明図である。

【図 13】マルチダイレチクル用の C A D データイメージを示す説明図である。

【図 14】ウェハ基板のメインチップ領域及び未配置領域を示す断面図である。

【図 15】従来のメインチップ領域及び未配置領域を示す断面図である。

【図 16】マルチダイ用レチクルのイメージを示す説明図である。

【図 17】従来のマルチダイレチクル用の C A D データイメージを示す説明図である。

【図 18】従来のレチクルデータ作成動作を示すフローチャートである。

### 【符号の説明】

#### 【0042】

2 未配置領域検出手段、矩形分割手段、スクライブデータ発生手段、ダミーパターン発生手段(処理装置)

4 ~ 1 2 記憶手段

M , M 1 ~ M 3 メインチップ

N L 未配置領域

10

20

30

40

50

D , D 1 ~ D 6      ダミーチップ

DP            ダミーパターン

【図 1】

【図 2】

【図3】

レチクルデータ作成装置の動作を示すフローチャート

【図5】

レチクルデータ作成処理動作を示す説明図

【図6】

レチクルデータ作成処理動作を示す説明図

【図4】

レチクルデータ作成装置の動作を示すフローチャート

【図7】

レチクルデータ作成処理動作を示す説明図

【図9】

レチクルデータ作成処理動作を示す説明図

【図8】

レチクルデータ作成処理動作を示す説明図

【図10】

レチクルデータ作成処理動作を示す説明図

【図 1 1】

レチクルデータ作成処理動作を示す説明図

【図 1 3】

マルチダイレチクル用のCADデータイメージを示す説明図

【図 1 2】

レチクルデータ作成処理動作を示す説明図

【図 1 5】

ウェハ基板のメインチップ領域及び未配置領域を示す断面図

従来のメインチップ領域及び未配置領域を示す断面図

【図16】

マルチダイ用レチクルのイメージを示す説明図

【図17】

従来のマルチダイレチクル用のCADデータイメージを示す説明図

【図18】

従来のレチクルデータ作成動作を示すフローチャート

---

フロントページの続き

(72)発明者 小島 勝人

愛知県春日井市高蔵寺町二丁目1844番2 富士通VLSI株式会社内

Fターム(参考) 2H095 BA01 BA02 BB01 BB02

5F038 CA13 CD10 EZ09 EZ20

5F064 EE23 EE32 EE51 HH06 HH12