US00RE50129E

## (19) United States

## (12) Reissued Patent

#### Park et al.

### (10) Patent Number: US RE50,129 E

### (45) Date of Reissued Patent: Sep. 17, 2024

#### (54) STORAGE DEVICE HAVING VARIOUS RECOVERY METHODS AND RECOVERY MODES

(71) Applicant: **SAMSUNG ELECTRONICS CO., LTD.**, Suwon-si (KR)

(72) Inventors: Ji Hyung Park, Yongin-si (KR);

HyunJung Shin, Yongin-si (KR); Isaac Baek, Hwaseong-si (KR); Jeonguk Kang, Bucheon-si (KR); Minseok Ko,

Seoul (KR)

(73) Assignee: SAMSUNG ELECTRONICS CO.,

LTD., Suwon-si (KR)

(21) Appl. No.: 17/501,403

(22) Filed: Oct. 14, 2021

#### Related U.S. Patent Documents

Reissue of:

(64) Patent No.: 10,445,200 Issued: Oct. 15, 2019 Appl. No.: 15/651,342 Filed: Jul. 17, 2017

U.S. Applications:

(63) Continuation-in-part of application No. 15/481,781, filed on Apr. 7, 2017, now Pat. No. 10,372,558.

#### (30) Foreign Application Priority Data

(51) Int. Cl.

**G06F 11/00** (2006.01) **G06F 11/07** (2006.01)

(Continued)

(52) U.S. Cl.

CPC ...... **G06F 11/0751** (2013.01); **G06F 11/0727** (2013.01); **G06F 11/2094** (2013.01); (Continued)

(58) Field of Classification Search

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

6,038,679 A 3/2000 Hanson 6,487,677 B1 11/2002 Jantz et al. (Continued)

#### FOREIGN PATENT DOCUMENTS

CN 103019873 4/2013 CN 103093818 5/2013 (Continued)

#### OTHER PUBLICATIONS

Office Action issued in corresponding U.S. Appl. No. 15/481,781 dated Nov. 19, 2018.

(Continued)

Primary Examiner — Matthew E Heneghan (74) Attorney, Agent, or Firm — F. CHAU & ASSOCIATES, LLC

#### (57) ABSTRACT

A storage device including: a nonvolatile memory device including a plurality of nonvolatile memory cells, a partial storage area and an overprovision storage area; and a controller configured to control the nonvolatile memory device, wherein when the controller detects a fault of the nonvolatile memory device, the controller negates the partial storage area, reassigns the overprovision storage area, which corresponds to a size of a user area, among the partial storage area, determines a device fail if the overprovision storage area is less than an overprovision threshold after the reassigning of the partial storage area, and determines a recovery success if the overprovision storage area is equal to or greater than the overprovision threshold after the reassigning of the partial storage area.

#### 12 Claims, 22 Drawing Sheets

# US RE50,129 E Page 2

| (20<br>11/0773<br>(58) <b>Field of Cla</b> s<br>CPC G06                                                                                                                                                                                                                       | (2006.01)<br>(2006.01)<br>(2006.01)<br>. G11C 29/44 (2013.01); G11C 29/88<br>13.01); G11C 29/883 (2013.01); G06F<br>(2013.01); G06F 2201/805 (2013.01);<br>G06F 2201/81 (2013.01)<br>sification Search<br>G 2201/805; G11C 29/88; G11C 29/44;<br>G11C 29/883; G11C 29/76<br>on file for complete search history. | 2012/0089767 A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (56)                                                                                                                                                                                                                                                                          | References Cited                                                                                                                                                                                                                                                                                                 | FOREIGN PATENT DOCUMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7,526,675 B2 7,962,807 B2 8,041,916 B2 8,041,991 B2 8,065,492 B2 8,151,137 B2*  8,201,024 B2 8,214,580 B2*  8,812,933 B2 9,081,753 B2 9,213,598 B2 9,229,854 B1 9,244,766 B2 9,268,487 B2 9,697,071 B2 9,728,277 B2 9,812,224 B2 10,372,558 B2 10,445,200 B2 2005/0044454 A1* | AZENT DOCUMENTS  4/2009 Mambakkam et al. 6/2011 Nakamura 10/2011 McKean 11/2011 Moshayedi 4/2012 McKean                                                                                                                                                                                                          | CN 105097034 11/2015 CN 105229615 1/2016 JP H09198884 7/1997 JP 2007079762 3/2007 JP 2009015553 1/2009 JP 2013149112 8/2013 JP 2013175118 9/2013 JP 2015118664 6/2015 KR 10-2013-0124010 11/2013 KR 10-2014-0103756 8/2014 KR 10-2014-0103756 8/2014 KR 10-2016-0016422 2/2016 KR 20160044289 4/2016  OTHER PUBLICATIONS  Office Action issued in corresponding U.S. Appl. No. 15/651,342 dated Jan. 18, 2019. Fan et al. "Transaction Recovery Model of Databases Based on PCM and Flash Memory", Chinese Journal of Computers, vol. 36 No. 8, Aug. 2013, pp. 1582-1591. Monazzah et al., "FTSPM: A Fault-Tolerant ScratchPad Memory", IEEE, 2013, 10 pages. |

| 2011/0083047 A1<br>2012/0017116 A1                                                                                                                                                                                                                                            | 4/2011 Stenfort<br>1/2012 Matsuyama et al.                                                                                                                                                                                                                                                                       | * cited by examiner                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

FIG. 2

FIG. 3

FIG. 4

FIG. 5

ü Access request (\$520) Access result(\$530) -S540 Detect fault based on access result E3d 8 Access result or fault information (S550) Access request (S510) ENG

FIG. 7

Access request (S740) Access result(S750) Detect fault based on access result 120 Read result or fault information (S770) Scrub information (S720) Access request (S730) Trigger scrub operation E E

FIG. 9

Sep. 17, 2024

| Types of fault                            |

|-------------------------------------------|

| Level of fault                            |

| Size of storage area of fault             |

| Address of storage area of fault          |

| Physical feature of storage area of fault |

| History of fault                          |

FIG. 10

FIG. 11

FIG. 12

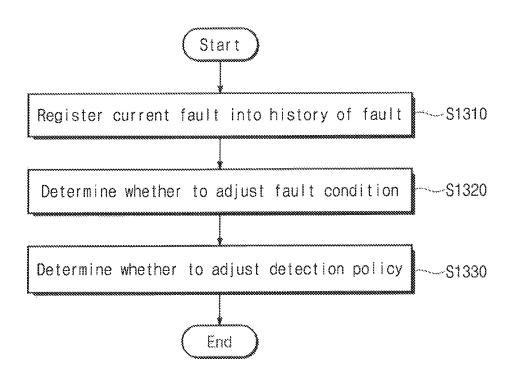

FIG. 13

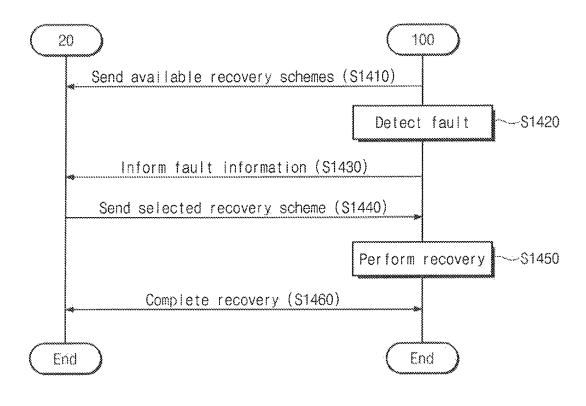

FIG. 14

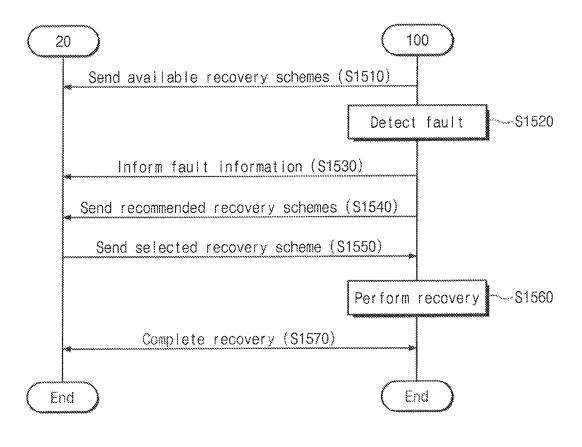

FIG. 15

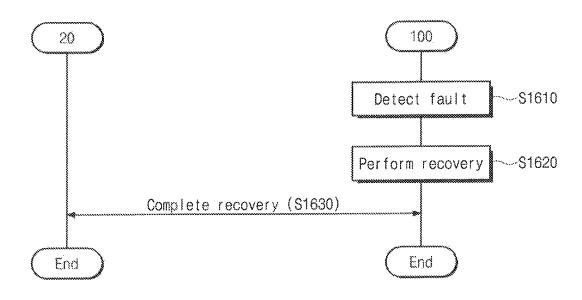

FIG. 16

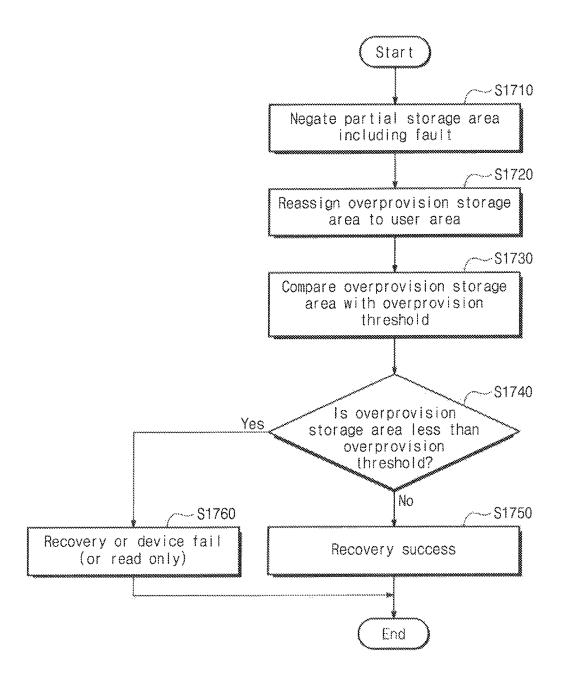

FIG. 17

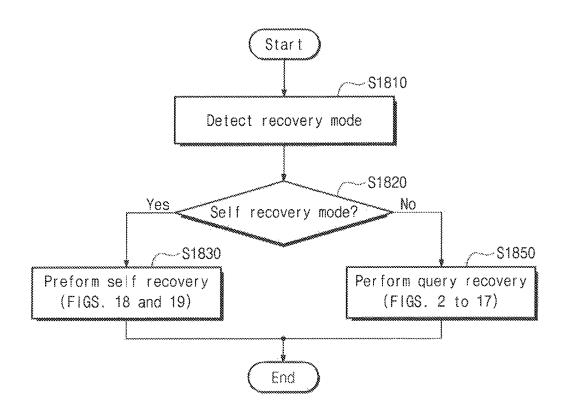

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 23

Sep. 17, 2024

# STORAGE DEVICE HAVING VARIOUS RECOVERY METHODS AND RECOVERY MODES

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held 10 invalid by a prior post-patent action or proceeding.

## CROSS-REFERENCE TO RELATED APPLICATIONS

This U.S. non-provisional application is a continuation-in-part of U.S. application Ser. No. 15/481,781 filed on Apr. 7, 2017 which claims priority under 35 U.S.C. § 119 to Korean Patent Application No. 10-2016-0054113 filed May 2, 2016, in the Korean Intellectual Property Office, the disclosures of which are incorporated by reference herein in their entireties. This U.S. non-provisional application also claims priority under 35 U.S.C. § 119 to Chinese Patent Application No. 201710301025.9 filed May 2, 2017 in the Chinese Patent Office, the disclosure of which is incorporated by reference herein in its entirety.

#### TECHNICAL FIELD

Exemplary embodiments of the inventive concept <sup>30</sup> described herein relate to a semiconductor device, and more particularly, to a storage device having various recovery methods and various recovery modes.

#### DISCUSSION OF RELATED ART

A storage device may refer to a device that stores data under control of a host device such as a computer, a smartphone, or a smart pad. The storage device may include a device, which stores data on a magnetic disk, such as a 40 hard disk drive (HDD). The storage device may also include a device, which stores data on a semiconductor memory, in particular, a nonvolatile memory, such as a solid state drive (SSD) or a memory card.

The nonvolatile memory may include a read only memory 45 (ROM), a programmable ROM (PROM), an electrically programmable ROM (EPROM), an electrically erasable and programmable ROM (EEPROM), a flash memory device, a phase-change RAM (PRAM), a magnetic RAM (MRAM), a resistive RAM (RRAM), or a ferroelectric RAM (FRAM). 50 RAM may refer to a random access memory.

High-end storage devices with high capacity and high performance are being researched and developed. Manufacturing costs of high-end storage devices are higher than general storage devices. If a high-end storage device is 55 defective, it costs a lot to replace.

#### **SUMMARY**

An exemplary embodiment of the inventive concept provides a storage device including: a nonvolatile memory device including a plurality of nonvolatile memory cells, a partial storage area and an overprovision storage area; and a controller configured to control the nonvolatile memory device, wherein when the controller detects a fault of the 65 nonvolatile memory device, the controller negates the partial storage area, reassigns the overprovision storage area, which

2

corresponds to a size of a user area, among the partial storage area, determines a device fail if the overprovision storage area is less than an overprovision threshold after the reassigning of the partial storage area, and determines a recovery success if the overprovision storage area is equal to or greater than the overprovision threshold after the reassigning of the partial storage area.

An exemplary embodiment of the inventive concept provides a storage device including: a nonvolatile memory device including a plurality of nonvolatile memory cells; and a controller configured to control the nonvolatile memory device, wherein when the controller detects a fault of the nonvolatile memory device, the controller selects a recovery method among a plurality of recovery methods, and recovers the fault using the selected recovery method.

An exemplary embodiment of the inventive concept provides a storage device including: a nonvolatile memory device including a plurality of nonvolatile memory cells; and a controller configured to control the nonvolatile memory device, wherein when the controller detects a fault of the nonvolatile memory device, the controller detects a recovery mode upon detecting the fault, selects a recovery method and performs a recovery of the fault itself if the recovery mode is a first recovery mode, and queries the recovery method to an external host device if the recovery mode is a second recovery mode.

#### BRIEF DESCRIPTION OF THE FIGURES

The above and other features of the inventive concept will become more apparent by describing in detail exemplary embodiments thereof with reference to the following figures, in which:

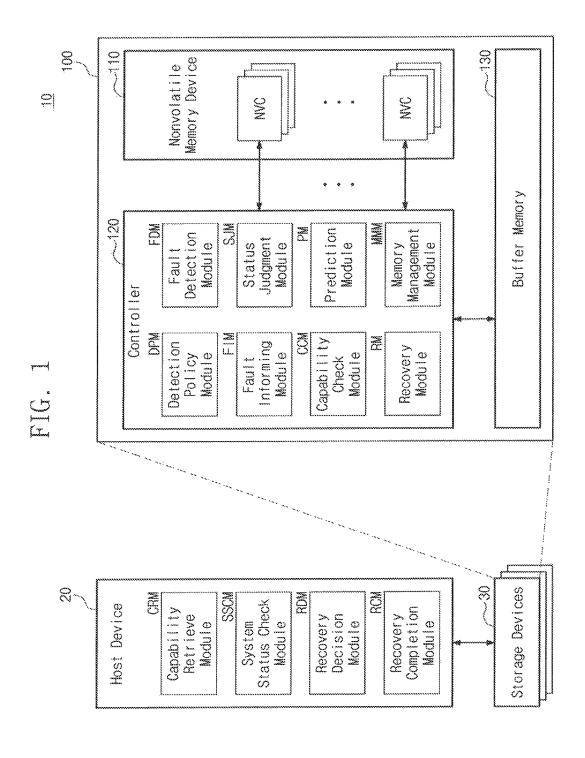

FIG. 1 is a block diagram illustrating a computing device according to an exemplary embodiment of the inventive concept;

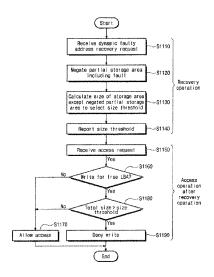

FIG. 2 is a flowchart illustrating an operating method of the computing device of FIG. 1 according to an exemplary embodiment of the inventive concept;

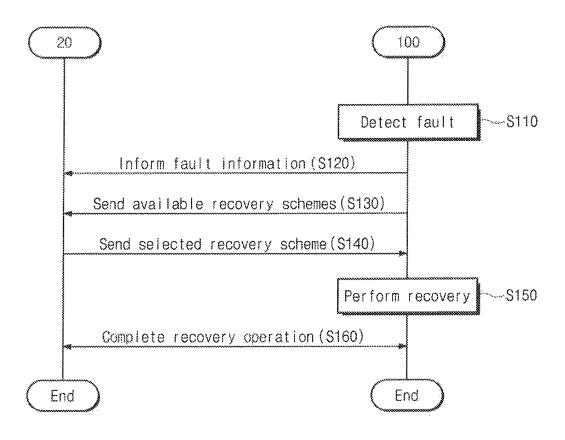

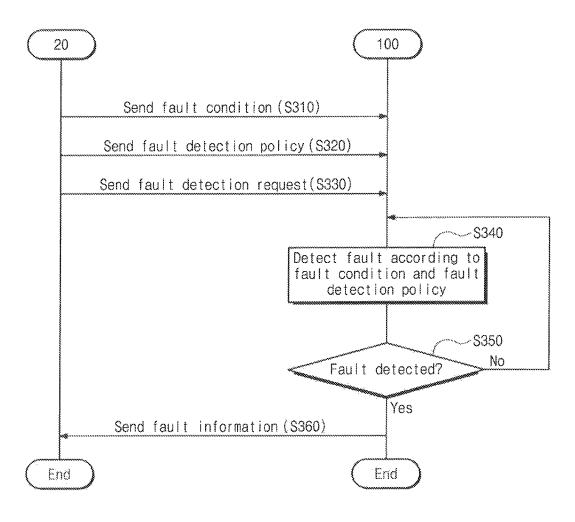

FIG. 3 is a flowchart illustrating a method in which a storage device detects a fault and informs fault information according to an exemplary embodiment of the inventive concept;

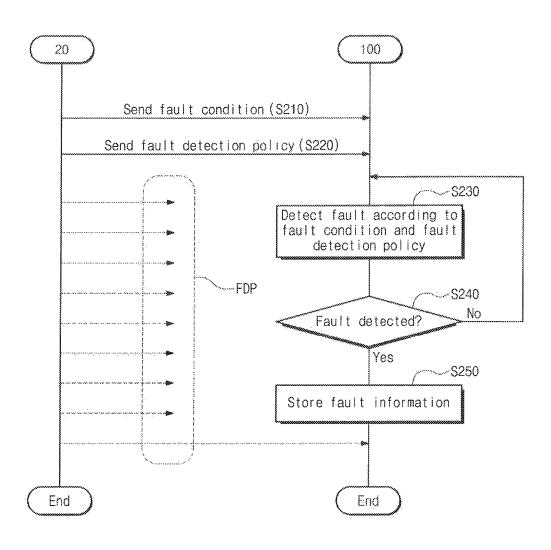

FIG. 4 is a flowchart illustrating a method in which a storage device detects a fault and informs fault information according to an exemplary embodiment of the inventive concept;

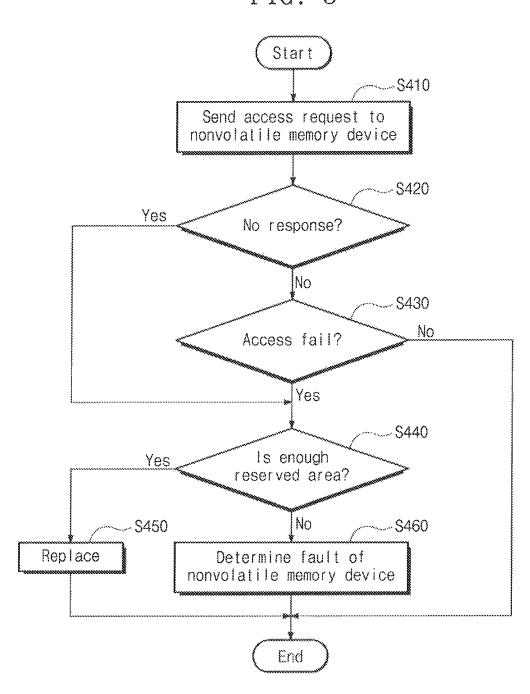

FIG. 5 is a flowchart illustrating a method in which a controller detects a fault according to an exemplary embodiment of the inventive concept;

FIG. 6 illustrates a fault detection module detecting a fault based on a detection policy according to an exemplary embodiment of the inventive concept;

FIG. 7 illustrates a fault detection module detecting a fault based on a detection policy according to an exemplary embodiment of the inventive concept;

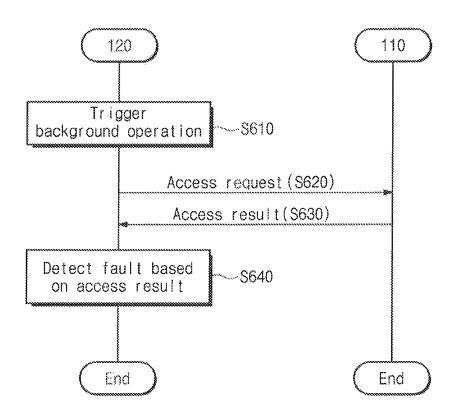

FIG. 8 illustrates a fault detection module detecting a fault based on a detection policy according to an exemplary embodiment of the inventive concept;

FIG. 9 illustrates fault information that a fault informing module sends according to an exemplary embodiment of the inventive concept;

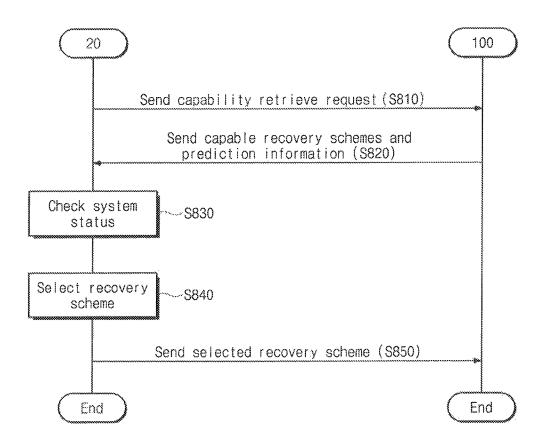

FIG. 10 illustrates a host device retrieving one or more recovery schemes and selecting one of the obtained recovery schemes according to an exemplary embodiment of the inventive concept;

FIG. 11 illustrates a recovery operation performed at a host device and a storage device according to an exemplary embodiment of the inventive concept;

FIG. 12 illustrates a recovery operation performed at a host device and a storage device according to an exemplary embodiment of the inventive concept;

FIG. 13 illustrates a recovery operation performed at a host device and a storage device according to an exemplary embodiment of the inventive concept;

FIG. 14 illustrates a recovery operation performed at a host device and a storage device according to an exemplary embodiment of the inventive concept;

FIG. 15 illustrates a recovery operation performed at a host device and a storage device according to an exemplary 15 embodiment of the inventive concept;

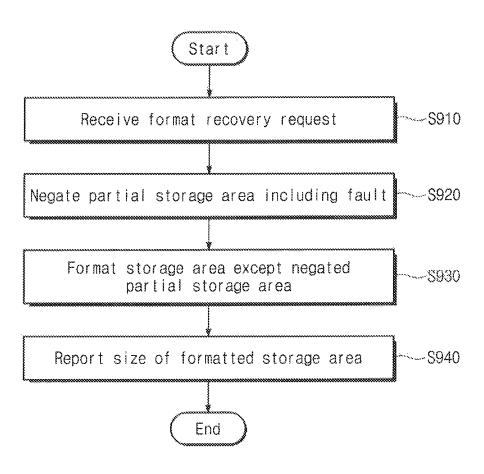

FIG. 16 is a flowchart illustrating an operating method of the computing device of FIG. 1 according to an exemplary embodiment of the inventive concept;

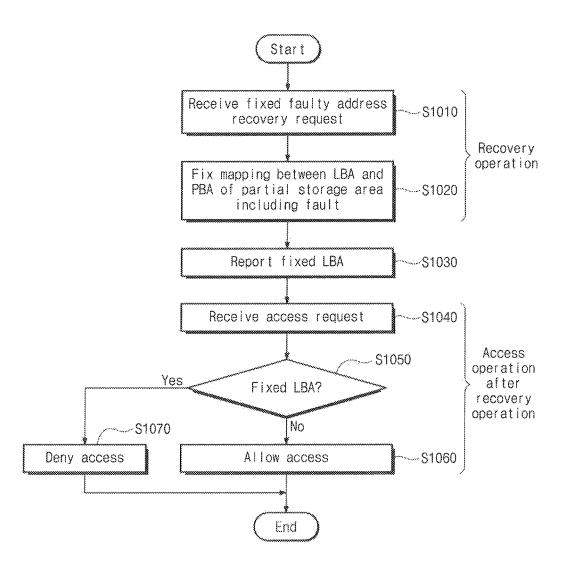

FIG. 17 is a flowchart illustrating an operating method of 20 the computing device of FIG. 1 according to an exemplary embodiment of the inventive concept;

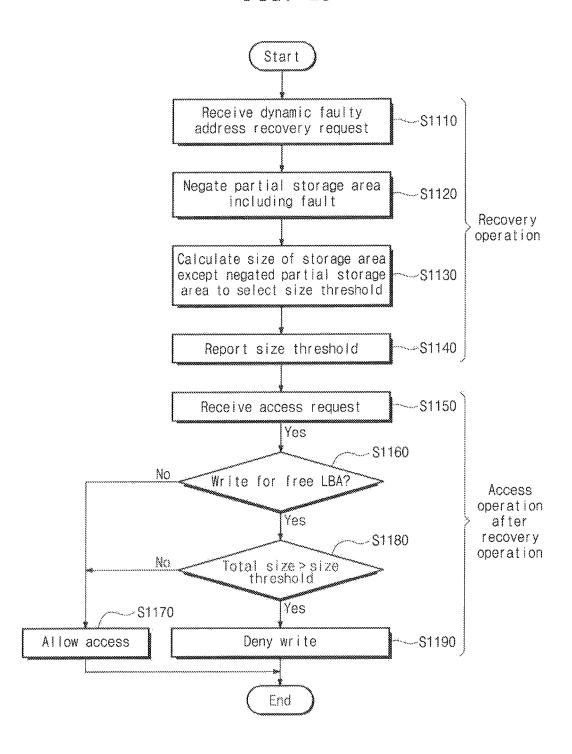

FIG. 18 is a flowchart illustrating an operating method of the computing device of FIG. 1 according to an exemplary embodiment of the inventive concept.

FIG. 19 illustrates recovery operations according to an exemplary embodiment of the inventive concept.

FIG. 20 illustrates a computing device operating in two modes according to an exemplary embodiment of the inventive concept.

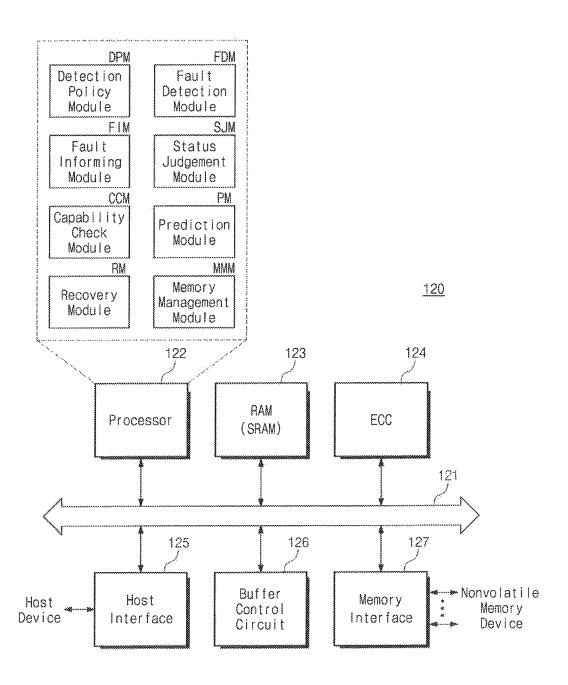

FIG. 21 is a block diagram illustrating a controller according to an exemplary embodiment of the inventive concept;

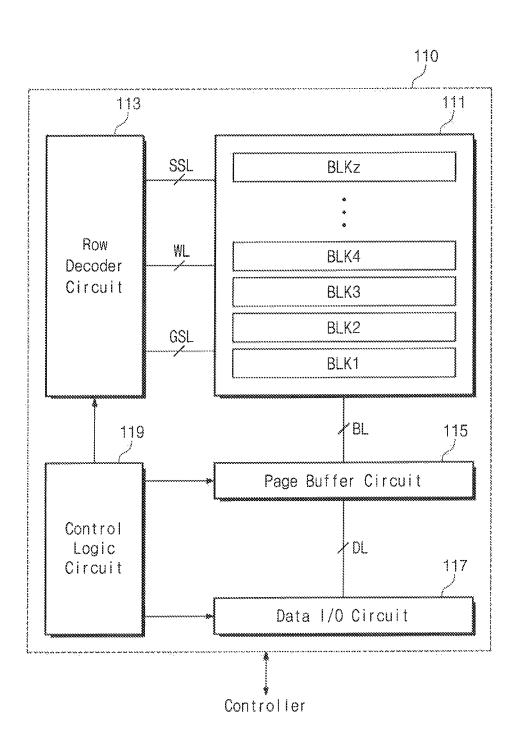

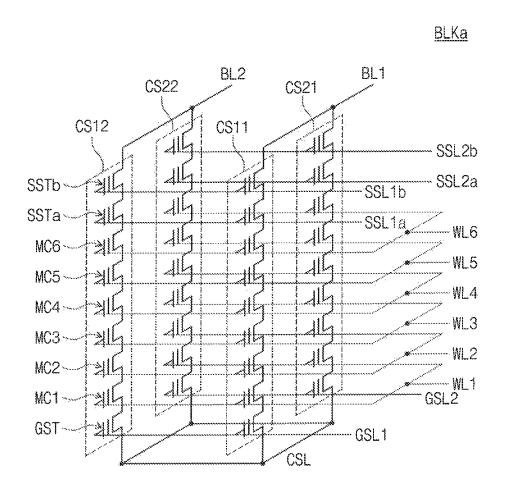

FIG. 22 is a block diagram illustrating a nonvolatile the inventive concept; and

FIG. 23 is a circuit diagram illustrating a memory block according to an exemplary embodiment of the inventive concept.

Like reference numerals refer to like elements in the 40 figures unless otherwise noted.

#### DETAILED DESCRIPTION OF THE **EMBODIMENTS**

FIG. 1 is a block diagram illustrating a computing device 10 according to an exemplary embodiment of the inventive concept. Referring to FIG. 1, the computing device 10 includes a host device 20, storage devices 30, and a storage device 100.

The host device 20 may write data to the storage devices 30, read data from the storage devices 30, and erase data from the storage devices 30.

The storage devices 30 may include a hard disk drive, a solid state drive, etc. The storage devices 30 may include 55 homogeneous or heterogeneous storage devices. The storage device 100 separately illustrated in FIG. 1 is an example of one of the storage devices 30.

The storage device 100 may be a solid state drive. The storage device 100 includes a nonvolatile memory device 60 110, a controller 120, and a buffer memory 130.

The nonvolatile memory device 110 may include a plurality of nonvolatile memory chips NVC. The nonvolatile memory chips NVC may communicate with the controller 120 through two or more channels (indicated by arrows in 65 FIG. 1). For example, two or more nonvolatile memory chips NVC may be connected to one channel. Nonvolatile

memory chips NVC connected to different channels may communicate with the controller 120 in parallel with each

The controller 120 may be configured to control the nonvolatile memory device 110 and the buffer memory 130. The controller 120 may control a program operation, a read operation, and an erase operation of the nonvolatile memory device 110. The controller 120 may temporarily store data, which it exchanges with the nonvolatile memory device 110, in the buffer memory 130. The controller 120 may use the buffer memory 130 as a working memory that stores codes or metadata. For example, the buffer memory 130 may include a volatile or nonvolatile random access memory (RAM).

In general, the controller 120 may divide a storage space of the nonvolatile memory device 110 into a user area and a reserved area. The user area may be recognized by the host device 20. For example, the controller 120 may notify the host device 20 of a storage capacity of the user area as a storage capacity of the storage device 100. The host device 20 may assign logical addresses to the user area. The controller 120 may map the logical addresses assigned by the host device 20 to physical addresses of the user area of the nonvolatile memory device 110.

When the user area is unavailable due to deterioration, wear-out, or damage to a portion thereof, the controller 120 may determine that a fault (e.g., a local fault) is present in a particular portion of the user area. The controller 120 may negate the portion of the user area at which the fault is detected and reassign a portion of the reserved area as the user area. The reassignment may make it possible to maintain the entire storage capacity of the user area.

If all of the reserved area is used, even though a fault is generated at a particular portion (again, a local fault) of the memory device according to an exemplary embodiment of user area, the controller 120 cannot use the reserved area for a reassignment. If the local fault is generated after all the reserved area is used, the controller 120 may determine that a global fault has occurred. In the event of a global fault, a conventional storage device enters a device fail state where the storage device can no longer be used.

> However, the storage device 100 according to an exemplary embodiment of the inventive concept may prevent the storage device 100 from entering the device fail state when there is no reserved area left and a local fault occurs. For example, in a case in which the global fault traditionally occurs, the storage device 100 may perform a recovery operation to treat the global fault as a local fault. For example, during the recovery operation, the controller 120 may prohibit an access to a storage space at which a fault is generated and set the storage device 100 such that the storage device 100 operates with the remaining storage space. Accordingly, the life cycle of the storage device 100 may be extended, and costs associated with operating the storage device 100 may be reduced.

> With regard to the above-described recovery operation, the host device 20 may include a capability retrieve module CRM, a system status check module SSCM, a recovery decision module RDM, and a recovery completion module RCM. The capability retrieve module CRM may retrieve information about recovery capabilities that the storage device 100 supports. The system status check module SSCM may collect information about a status or resource of the host device 20. The recovery decision module RDM may select a recovery scheme. The recovery completion module RCM may control settings of the host device 20 such that the storage device 100 is driven normally after completion of the recovery operation. The recovery completion module

RCM may also control settings of the storage device 100 to perform an additional recovery such as data recovery for the host device 20.

With regard to the above-described recovery operation, the controller 120 may include a detection policy module 5 DPM, a fault detection module FDM, a fault informing module FIM, a status judgment module SJM, a capability check module CCM, a prediction module PM, a recovery module RM, and a memory management module MMM. The detection policy module DPM may store information 10 about a fault detection policy of the controller 120. In other words, on which basis the controller 120 detects a fault. The fault detection module FDM may detect whether a fault (a local fault or a global fault) is generated at the elements of the storage device 100, for example, the nonvolatile memory 15 device 110, the controller 120, or the buffer memory 130. The fault informing module FIM may inform the host device 20 of information about the detected fault, for example, the global fault. The status judgment module SJM may determine a fault status. The capability check module CCM may 20 store information about recovery schemes that the controller 120 supports. The prediction module PM may predict how the performance of the storage device 100, for example, an operating speed and a capacity, vary when each recovery scheme is performed. The recovery module RM may per- 25 form recovery based on the selected recovery scheme. The memory management module MMM may manage the nonvolatile memory device 110. For example, the memory management module MMM may manage mapping information between logical addresses assigned by the host device 30 20 and physical addresses of the nonvolatile memory device 110. The memory management module MMM may update the mapping information based on the recovery result.

Operations of modules associated with the recovery operation will be described later with reference to accompanying drawings.

The modules of the host device 20 or the controller 120 illustrated in FIG. 1 are exemplary, and the inventive concept may not be limited thereto. In an exemplary embodiment of the inventive concept, at least one of the modules of 40 the controller 120 or the host device 20 may be omitted. Two or more of the modules of the controller 120 or the host device 20 may be integrated into a single module. At least one of the modules of the controller 120 or the host device 20 may be divided into two or more sub-modules. Additionally, each of the modules may be implemented in hardware as a circuit.

In the following detailed description, exemplary embodiments of the inventive concept will be described under the condition that respective modules of the host device 20 and 50 respective modules of the controller 120 communicate with each other. Respective modules of the host device 20 and respective modules of the controller 120 may communicate with each other by using a shared physical channel connecting the host device 20 and the storage device 100. For 55 example, respective modules of the host device 20 may send information to respective modules of the controller 120 in the form of an application program interface (API), a command and an address or an argument associated with the command, a packet suitable for a shared channel, etc. The 60 information transmitted from the host device 20 to the controller 120 may be referred to as a "request". Each module of the controller 120 may send a response to each module of the host device 20 in response to a request of each module of the host device 20.

FIG. 2 is a flowchart illustrating an operating method of the computing device 10 of FIG. 1 according to an exem-

6

plary embodiment of the inventive concept. Referring to FIGS. 1 and 2, in operation S110, the storage device 100, for example, the controller 120 may detect a fault of the storage device 100, for example, a local fault (or a local fault causing a global fault). For example, the fault may be detected by the fault detection module FDM. The fault detection module FDM may perform fault detection based on a fault detection policy stored in the detection policy module DPM.

In operation S120, the storage device 100, for example, the controller 120 may notify the host device 20 of fault information. For example, the fault informing module FIM may collect the fault information and send the collected fault information to the host device 20.

In operation S130, the storage device 100, for example, the controller 120 may provide the host device 20 with available recovery schemes for recovering a fault. For example, the capability check module CCM may manage the available recovery schemes and provide them to the host device 20. For example, the capability check module CCM may provide the host device 20 or the capability retrieve module CRM of the host device 20 with the recovery schemes in response to a request of the capability retrieve module CRM. For example, the capability check module CCM may provide the host device 20 with one or more recovery schemes. The capability check module CCM may inform the host device 20 of all recovery schemes or those which are more suitable for recovering a current fault, from among all supportable recovery schemes.

In operation S140, the host device 20 may select one of the recovery schemes from the storage device 100. For example, the recovery scheme may be selected by the recovery decision module RDM. The recovery decision module RDM may provide the selected recovery scheme to the storage device 100, for example, the controller 120.

In operation S150, the storage device 100, for example, the controller 120 may perform a recovery operation based on the selected recovery scheme. The recovery operation may be performed by the recovery module RM.

In operation S160, the storage device 100 and the host device 20 may complete the recovery operation. The completion of the recovery operation may be performed by the recovery completion module RCM of the host device 20 and the memory management module MMM of the controller 120. For example, the recovery completion module RCM and the memory management module MMM may share information about the performance or resource of the storage device 100, which varies according to the recovery operation. If the recovery operation is completed, the host device 20 may normally access the storage device 100. While the storage device 100 performs the recovery operation, the storage device 100 may permit the host device 200 to access normal storage spaces at which the local fault is not generated. For example, the storage device 100 may permit reading and writing with respect to the normal storage spaces, prohibit the writing, permit the reading, or prohibit both the reading and the writing while permitting exchange of status information. For example, a permitted access level may be determined by the storage device 100 or the host device 20.

FIG. 3 is a flowchart illustrating a method in which the storage device 100 detects a fault (operation S110 of FIG. 2) and informs fault information (operation S120 of FIG. 2) according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 3, in operation S210, the host device 20 may send a fault condition to the storage device 100. For example, the host device 20 may send a

condition determined as a fault to the fault detection module FDM of the controller 120. For example, operation S210 may be performed when the computing device 10 performs an initialization or power-on reset operation at power-on. If the fault detection module FDM is configured to detect a 5 fault by using a previously stored default condition, operation S210 may be skipped.

In operation S220, the host device 20 may send a fault detection policy to the storage device 100. For example, the host device 20 may send a fault detection policy, which 10 includes information about timing when fault detection is performed, to the detection policy module DPM of the controller 120. For example, operation S220 may be performed when the computing device 10 performs an initialization or power-on reset operation at power-on. If the 15 detection policy module DPM is configured to detect a fault by using a previously stored default condition, operation S220 may be skipped.

After the detection condition and the fault detection fault detection polling (FDP). The fault detection polling (FDP) may include an operation in which the host device 20 periodically or frequently checks whether a fault is detected from the storage device 100. The host device 20 may perform the fault detection polling (FDP) as a background 25 operation while normally performing a write, read, or erase operation with respect to the storage device 100. In an exemplary embodiment of the inventive concept, arrows, which are not connected to an operation flow of the storage device 100, illustrate the fault detection polling (FDP) when 30 a fault is not detected.

While the host device 20 performs the fault detection polling (FDP), in operation S230, the storage device 100, for example, the controller 120 may detect a fault based on the fault condition and fault detection policy. For example, the 35 fault detection may be performed by the fault detection module FDM. The fault detection may be performed as a background operation while the storage device 100 performs a write, read, or erase operation with respect to the nonvolatile memory device 110.

In operation S240, if the fault is not detected, the fault detection module FDM may continue to perform the fault detection (operation S230). If the fault is detected, operation S250 is performed.

In operation S250, the fault informing module FIM may 45 collect and store fault information. Afterwards, the fault informing module FIM may send the fault information to the host device 20 in response to the first performed fault detection polling (FDP). Arrows, which are connected to the operation flow of the storage device 100, illustrate the fault 50 detection polling (FDP) after the fault is detected.

FIG. 4 is a flowchart illustrating a method in which the storage device 100 detects a fault (operation S110 of FIG. 2) and informs fault information (operation S120 of FIG. 2) according to an exemplary embodiment of the inventive 55 concept. Referring to FIGS. 1 and 4, in operation S310, the host device 20 may send a fault detection condition to the storage device 100. If the fault detection module FDM is configured to detect a fault by using a previously stored default condition, operation S310 may be skipped.

In operation S320, the host device 20 may send a fault detection policy to the storage device 100. If the detection policy module DPM is configured to detect a fault by using a previously stored default condition, operation S320 may be skipped.

After the detection condition and fault detection policy are completely set, in operation S330, the host device 20

may send a fault detection request to the storage device 100. For example, the fault detection request may not have a timeout condition until a response is received.

In operation S340, the storage device 100, for example, the controller 120 may detect a fault based on the fault condition and fault detection policy. For example, the fault detection may be performed by the fault detection module FDM. The fault detection may be performed as a background operation while the storage device 100 performs a write, read, or erase operation with respect to the nonvolatile memory device 110. For example, if the fault is not detected, the controller 120 performs scheduling such that a write, read, or erase request is performed prior to the fault detection request of operation S330.

In operation S350, if the fault is not detected, the fault detection module FDM may continue to perform the fault detection (operation S340). If the fault is detected, operation S360 is performed.

In operation S360, the fault informing module FIM may policy are completely set, the host device 20 may perform 20 collect fault information. The fault informing module FIM may send the collected fault information to the host device 20 as a response to the fault detection request received in operation S330.

> In an exemplary embodiment of the inventive concept, the storage device 100 may perform the fault detection by using a predefined fault detection condition or a fault detection condition controlled according to an internal determination of the storage device 100, without having to send the fault detection condition from the host device 20.

> FIG. 5 is a flowchart illustrating a method in which the controller 120 detects a fault (operation S110 of FIG. 2) according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 5, in operation S410, the controller 120 may send an access request to the nonvolatile memory device 110. For example, the controller 120 may send the access request to one of the nonvolatile memory chips NVC. The access request may include a write request, a read request, or an erase request.

In operation S420, if a response from a nonvolatile 40 memory chip NVC to which the access request is sent, is absent, the fault detection module FDM may determine that a local fault is generated at the nonvolatile memory chip NVC. For example, in the case where a response is not received from a nonvolatile memory chip NVC, the fault detection module FDM may determine that the local fault is generated at the nonvolatile memory chip NVC or a package, a way, or a channel to which the nonvolatile memory chip NVC belongs. For example, fault detection may be performed with respect to nonvolatile memory chips NVC (or a package, a way, or a channel) physically associated with the nonvolatile memory chip NVC, or it may be determined that the local fault is generated at the associated nonvolatile memory chips NVC (or a package, a way, or a channel). Afterwards, operation S440 may be performed. If a response is received from the nonvolatile memory chip NVC to which the access request is sent, operation S430 is

In operation S430, the fault detection module FDM may determine whether an access fails. For example, the access 60 fail may be determined according to a fault condition.

For example, in the case where the access request is a write request, a program operation may be performed in a nonvolatile memory chip NVC. The program operation may include a plurality of program loops. Each program loop may include a program operation of increasing threshold voltages of memory cells by applying a program voltage thereto and a verification operation of determining whether

the threshold voltages of the memory cells reach a target level. When the memory cells are not completely programmed until the program loop reaches the maximum program loop, or when the memory cells are completely programmed after the program loop is performed more than a predetermined number of times, the fault detection module FDM may determine that the write has failed. As another example, when the number of events that the memory cells are completely programmed after the program loop is performed above the predetermined threshold frequency and when the memory cells are programmed or erased is less than a threshold value, the fault detection module FDM may determine that the write has failed.

For example, in the case where the access request is a read request, a read operation may be performed in a nonvolatile 15 memory chip NVC. When the number of errors detected from the read result is greater than or equal to a threshold value, the fault detection module FDM may determine that the read has failed. For example, when a time passing after data is written in memory cells is within a threshold time and 20 the number of errors is greater than or equal to a threshold value (or the maximum number of correctable errors), the fault detection module FDM may determine that the read has failed.

For example, in the case where the access request is an 25 erase request, an erase operation may be performed in a nonvolatile memory chip NVC. An erase operation may include a plurality of erase loops. Each program loop may include an erase operation of decreasing threshold voltages of memory cells by applying an erase voltage thereto and a 30 verification operation of determining whether the threshold voltages of the memory cells reach a target level. When the memory cells are not completely erased until the erase loop reaches the maximum erase loop, or when the memory cells are completely erased after the erase loop is performed more 35 than a predetermined number of times, the fault detection module FDM may determine that an erase has failed. As another example, when the number of events that the memory cells are completely erased after the erase loop is performed above the predetermined threshold frequency and 40 when the memory cells are programmed or erased is less than a threshold value, the fault detection module FDM may determine that the erase has failed.

As described above, the access fail may be detected when fail probability is high as well as when a write, a read, or an 45 erase fail is generated. The detect condition, which is used for the fault detection module FDM to determine the access fail may be stored in the fail detection module FDM and may be set by the host device 20. In an exemplary embodiment of the inventive concept, a characteristic of the detected fail 50 may be tested by internal logic. The fail detection module FDM may again perform the fail detection based on the tested characteristic. For example, the fail detection module FDM may again perform the fail detection with respect to a greater storage space (e.g., a physical storage space distin- 55 guishable by a physical address) including a storage space at which a fail is detected. For example, the fault detection module FDM may again perform the fail detection based on units, by which various operations of the nonvolatile memory device 110 are performed, such as a memory block. 60 For example, when a fail is detected from a memory cell, the fail detection may be again performed with respect to one or more pages including the fail memory cell or a memory block including the fail memory cell. When a fail is detected from a page, the fail detection may be again performed with 65 respect to one or more pages including the fail page or a memory block including the fail page. As another example,

10

the fail detection module FDM may determine that a greater storage space (e.g., a physical storage space distinguishable by a physical address) including a storage space, at which a fail is detected, fails based on the characteristic of the tested fail. For example, the determination of the fail may be performed according to units, by which various operations of the nonvolatile memory device 110 are performed, such as a memory block.

If the access fail is generated, the fault detection module FDM may determine that the local fault is generated. Afterwards, operation S440 is performed. If the access fail is not generated, the fault is not detected.

In operation S440, the memory management module MMM determines whether the reserved area is present. If the reserved area is sufficient, in other words, if a reserved area of a size corresponding to a size of a storage area at which a fault is generated is present, operation S450 is performed. In operation S450, the memory management module MMM may replace the storage area, at which the fault is generated, with the reserved area. For example, the memory management module MMM may release a mapping between physical addresses and logical addresses of the fault storage area. The memory management module MMM may map logical addresses of a fault area to physical addresses of the reserved area. In the case where the global fault is not detected because the local fault is detected but the reserved area is sufficient, the memory management module MMM may finally determine that a fault is not generated.

When the reserved area is not sufficient, in other words, in the case where a size of the fault storage area is greater than a size of the reserved area, operation S460 is performed. In operation S460, the fault detection module FDM may detect the global fault and finally determine that the fault is generated. Afterwards, as described with reference to operation S120 of FIG. 2, the fault informing module FIM may send the fault information to the host device 20.

In an exemplary embodiment of the inventive concept, the fault detection module FDM may detect a fault generated at any other element(s) of the storage device 100 as well as the nonvolatile memory device 110. For example, when the buffer memory 130 does not respond or when an access of the buffer memory 130 fails, the fault detection module FDM may determine that the global fault is generated. In addition, when a super capacitor or a tantalum capacitor is present in the storage device 100, the fault detection module FDM may receive a fail signal from an auxiliary power supply. In response to the fail signal, the fault detection module FDM may determine whether the global fault is generated. If the global fault is generated, the fault informing module FIM may send the fault information to the host device 20.

FIG. 6 illustrates the fault detection module FDM detecting a fault based on a detection policy according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 6, the fault detection module FDM may perform fault detection based on a direct detection policy set in the detection policy module DPM.

In operation S510, the host device 20 may send an access request to the controller 120.

In operation S520, the host device 20 may send the access request to the nonvolatile memory device 110 in response to the access request of the host device 20.

In operation S530, the controller 120 may receive the access result from the nonvolatile memory device 110.

In operation S540, the fault detection module FDM may perform fault detection based on the access result. For example, the fault detection module FDM may detect a fault

depending on whether the nonvolatile memory device 110 does not respond, or if a read, a write, or an erase fail occurs.

In operation S550, the controller 120 may send the access result or fault information to the host device 20. For example, when the local fail or global fail does not occur or when a local fail occurs but a global fail does not occur, the controller 120 may send the access result to the host device 20. In the case where the global fail occurs, the controller 120 may provide the fault information to the host device 20.

In other words, the fault detection module FDM may perform the fault detection during an access performed by a request of the host device 20.

FIG. 7 illustrates the fault detection module FDM detecting a fault based on a detection policy according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 7, the fault detection module FDM may perform fault detection based on a background detection policy set to the detection policy module DPM.

In step S610, the controller 120 may trigger a background 20 operation. For example, the background operation may be an operation in which the controller 120 or the memory management module MMM by itself accesses the nonvolatile memory device 110 to manage the nonvolatile memory device 110 without a request of the host device 20. The 25 background operation may be performed during an idle time between operations that are performed according to a request of the host device 20. The background operation may include garbage collection, refresh (or read reclaim), wear leveling, etc. Here, the garbage collection may be performed to generate a free storage area by integrating valid data in used storage area to obtain a storage area that is filled with invalid data and erasing the obtained storage area. The refresh (or read reclaim) may be performed to increase the integrity of data by rewriting data of the low integrity in a free storage area, and the wear leveling may be performed to swap data in a storage area of a high wear-out level for data in a storage area of a low wear-out level.

In step S620, the controller 120 may send an access  $_{40}$  request to the nonvolatile memory device 110 based on the procedure of the background operation.

In step S630, the controller 120 may receive the access result from the nonvolatile memory device 110.

In operation S640, the controller 120 may detect a fault 45 based on the access result.

In other words, the fault detection module FDM may perform the fault detection during an access that is performed by the controller 120 by itself without a request of the host device 20.

FIG. 8 illustrates the fault detection module FDM detecting a fault based on a detection policy according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 8, the fault detection module FDM may perform fault detection based on a scrub detection policy set 55 in the detection policy module DPM.

In step S710, the controller 20 may trigger a scrub operation. For example, the scrub operation may be an operation in which the host device 20 scans data written in the storage devices 30 or the storage device 100 and checks 60 integrity.

In operation S720, the host device 20 may send scrub information, which informs that the scrub operation begins, to the controller 120.

In operation S730, the host device 20 may send an access 65 request to the controller 120 based on a predetermined sequence of the scrub operation.

12

In operation S740, the controller 120 may send the access request to the nonvolatile memory device 110 in response to the access request of the host device 20.

In operation S750, the controller 120 may receive the access result from the nonvolatile memory device 110.

In operation S760, the fault detection module FDM may perform fault detection based on the access result. For example, the fault detection module FDM may detect a fault depending on whether the nonvolatile memory device 110 does not respond, or if a read, a write, or an erase fail occurs.

In operation S770, the controller 120 may send the access result or fault information to the host device 20. For example, when the local fail or global fail does not occur or when a local fail occurs but a global fail does not occur, the controller 120 may send the access result to the host device 20. When the global fail occurs, the controller 120 may provide the fault information to the host device 20.

In other words, while the host device 20 performs the scrub operation, the fault detection module FDM may perform the fault detection during an access performed by a request of the host device 20.

As another example of the fault detection operation, the fault detection module FDM may perform fault detection based on an explicit detection policy set in the detection policy module DPM. For example, the host device 20 may notify the storage device 100 of execution of the scrub operation before performing the scrub operation. While the host device 20 accesses the storage device 100 may collect a fault detection result without sending it to the host device 20. If a scrub operation is completed, when an access is performed by a predetermined frequency, a predetermined time elapses, or a predetermined checkpoint (e.g., a checkpoint determined on a sequence of the scrub operation) arrives, the storage device 100 may notify the host device 20 of the collected fault detection result.

For example, the host device 20 may request the storage device 100 to perform explicit detection with respect to a portion of a storage space of the storage device 100 instead of the entire storage space of the storage device 100. For example, the storage device 100 may not perform the fault detection while the host device 20 performs the scrub operation with respect to a storage space to which the fault detection is not requested. While the host device 20 performs the scrub operation with respect to a storage space to which the fault detection is not requested, the storage device 100 may perform the fault detection and collect the fault detection result.

For example, the scrub operation may include a read operation that is performed with respect to a storage space where data is stored. The scrub operation may include a write operation of writing dummy data in a storage space where data is not stored. The scrub operation may include an erase operation that is performed with respect to a storage space where invalid data is stored.

As another example of the fault detection operation, the fault detection module FDM may perform fault detection based on a request detection policy set in the detection policy module DPM. For example, the fault detection module FDM may determine a storage space, of which a probability of fault occurrence is greater than or equal to a threshold value, based on an access result obtained when the host device 20 accesses the storage device 100 or the result of a fault detection performed by the fault detection module FDM. The fault detection module FDM may inform the host device 20 of information about the determined storage space. If the host device 20 requests the storage device 100

to perform the fault detection, the fault detection module FDM may perform the fault detection.

In an exemplary embodiment of the inventive concept, the detection policy module DPM may include all the fault policies that are described with reference to FIGS. 6 to 8. 5 Policies, which are to be enabled, from among the detection policies, which the detection policy module DPM supports, may be selected by the host device 20. For example, the direct detection policy of FIG. 6 and the background detection policy of FIG. 7 may be enabled at the same time. In an 10 exemplary embodiment of the inventive concept, a detection policy of the detection policy module DPM may be changed by the host device 20. For example, the host device 20 may select the direct detection policy as a default policy. If a fault is detected once or by a predetermined frequency, the host 15 device 20 may change the detection policy into at least one of the background detection policy, the scrub detection policy, and the explicit detection policy or may further enable at least one policy thereof. If a fault is not detected during a predetermined time after the detection policy is 20 changed, the host device 20 may reset the detection policy to the direct detection policy. In an exemplary embodiment of the inventive concept, the detection policy may be changed under control of the host device 20 or may be changed by a request of the storage device 100 or when the 25 host device 20 permits changing the detection policy.

FIG. 9 illustrates fault information that the fault informing module FIM sends (operation S120 of FIG. 2) according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 9, fault information may include types of fault. For example, the types of fault may indicate a kind of local fail causing a global fail, such as no response, a write fail, a read fail, and an erase fail.

The fault information may further include a level of fault. For example, the level of fault may include how serious the fault is. In an exemplary embodiment of the inventive concept, the fault detection module FDM may perform fault detection based on a plurality of conditions. For example, when a write or erase fail is detected, the fault detection module FDM may make a fault level low if a program or erase loop is performed above a threshold value. When a write or erase a fault level high if a program or erase operation is not completed even though a program or erase loop is performed above a threshold value.

The predicti the storage descendence is selected as the storage device variation of the inventive of the storage descendence is selected. The prediction of the storage device variation of the inventive of the inventive of the storage device or erase operation is completed after a program or erase loop is performed above a threshold value.

For example, when a read fail is detected, the fault detection module FDM may set a fault level based on whether a time passing after data is written in a memory cells belongs to a particular range, whether the number of 50 errors belongs to a particular range, or whether an uncorrectable error is generated.

For example, the fault detection module FDM may set a fault level, based on an occurrence history of a global fault. For example, a user area of the nonvolatile memory device 55 110 may be divided into a plurality of zones. The fault detection module FDM may determine a fault level for each zone, based on the number of times that the global fault occurs.

The fault information may further include a size of a 60 storage area where a fault is generated. The fault information may further include an address of a storage area where a fault is generated, for example, a physical address or logical address thereof.

The fault information may further include a physical 65 characteristic (e.g., feature) of a storage area where a fault is generated. For example, in the case where a fault is

14

generated at interconnections, for example, bit lines or word lines instead of memory cells of the nonvolatile memory device 110, information about the bit lines or word lines, where the fault is generated, may be included in the fault information.

The fault information may further include a fault history. For example, a list of logical addresses or physical addresses, where a fault is generated, may be included in the fault information.

For example, when the capability check module CCM sends available recovery schemes to the host device 20 (operation S130 of FIG. 2), it may select some of the recovery schemes supported by the controller 120. The capability check module CCM may provide the host device 20 with the selected recovery schemes as recommended recovery schemes.

FIG. 10 illustrates the host device 20 retrieving one or more recovery schemes (operation S130 of FIG. 2) and selecting one of the obtained recovery schemes. Referring to FIGS. 1 and 10, in operation S810, the host device 20 may send a capability retrieve request to the storage device 100. For example, the capability retrieve request may be generated and provided by the capability retrieve module CRM.

In operation S820, the storage device 100 may send available recovery schemes and prediction information to the host device 20. For example, the available recovery schemes may include all or some of the recovery schemes supported by the controller 120. For example, each recovery scheme may be provided together with information of one (or two) or more recovery ranges. For example, the recovery range may be presented in the form of a wide storage area including a storage area, at which a fault is generated, and a storage area physically adjacent thereto. The available recovery schemes may be provided by the capability check module CCM.

The prediction information may include a characteristic of the storage device 100 that varies when each recovery scheme is selected. For example, the prediction information may include a performance (or speed) variation of the storage device 100 after the recovery operation, a capacity variation of the storage device 100 after the recovery operation, a life cycle variation of the storage device 100 after the recovery operation, or a time needed to perform the recovery operation, when each recovery scheme and a recovery range associated with each recovery scheme are selected. In addition, information about changed specifications among specifications initially provided by the storage device 100 may be included in the prediction information. The prediction information may be provided by the prediction module PM.

In step S830, the host device 20 may check a system status. For example, the host device 20 may include the number of spare storage devices 30 associated with the host device 20, a ratio of used resources to unused resources of the host device 20, the number of times that the host device 20 is called by external client devices, the number of times that the host device 20 accesses the storage device 100 at which a fault is generated, etc. The system status may be checked by the system status check module SSCM.

In step S840, the host device 20 may select a recovery scheme. For example, the host device 20 may select one of the one or more recovery schemes provided in operation S820. For example, the host device 20 may select a recovery scheme based on the fault information, the prediction information, and the system status. For example, when a call frequency of the host device 20 or an access frequency to the storage device 100 is high, the host device 20 may select a recovery scheme having a short recovery time. When a

system, to which the host device 20 belongs, needs a high speed, the host device 20 may select a recovery scheme in which a decrease of a speed is low. When a system, to which the host device 20 belongs, increases resource efficiency, the host device 20 may select a recovery scheme in which a 5 capacity decrease is low. For example, when a status of the storage device 100 changes after the recovery operation, the host device 20 may select a recovery scheme capable of optimizing a resource of the computing device 10. The recovery scheme may be selected by the recovery decision 10 module RDM. For example, a reference of the recovery decision module RDM for selecting the recovery scheme may be stored in the recovery decision module RDM and may be updated or set by an external device or a user of the host device 20.

In operation S850, the host device 20 may send the selected recovery scheme to the storage device 100. In an exemplary embodiment of the inventive concept, before sending the selected recovery scheme to the storage device storage device 100. For example, in the case where data of a storage space, at which a fault of a low level is generated, is readable, the storage device 20 may read data of the storage space, at which the fault is generated, and may store the read data in a normal storage space of the storage device 25 100 or another storage medium. As another example, in the case where it is impossible to read data from a storage area due to a fault of a high level, the host device 20 may recover data by using a data recovery device such as redundant array of independent disks (RAID) and backup the recovered data. 30

FIG. 11 illustrates a recovery operation is performed at the host device 20 and the storage device 100 according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 11, in step S910, the controller 120 may receive a format recovery request. For example, the recovery 35 decision module RDM may select a format recovery scheme and send the format recovery request to the controller 120 based on the selected format recovery scheme. The recovery module RM may perform format recovery based on the received format recovery request.

In operation S920, the recovery module RM may negate a portion of a storage area corresponding to a recovery range included in the format recovery request, in other words, a portion of a storage area including a storage area at which a fault is generated. For example, under control of the recov- 45 ery module RM, the memory management module MMM may release a mapping between logical addresses and physical addresses corresponding to the recovery range and mark the physical addresses in the recovery range as impossible to use.

In operation S930, the recovery module RM may format the remainder of the storage area other than the negated portion of the storage area. For example, under control of the recovery module RM, the memory management module MMM may update mapping information to indicate that 55 valid data is not present in the remaining storage area.

In operation S940, the recovery module RM may report a size of the formatted storage area to the host device 20. The recovery completion module RCM may determine that valid data is not stored in the storage area of the storage device 60 100, change a size of the storage area of the storage device 100 into the reported size and modify or regenerate a file system associated with the storage device 100.

In an exemplary embodiment of the inventive concept, before format recovery is performed, the host device 20 may back up data stored in the remaining storage area of the storage device 100.

16

If the format recovery is performed, a range of logical addresses of the storage device 100 may be reduced, and logical addresses within the reduced range may be consecutive. The controller 120 may permit write, read, and erase operations with respect to the logical addresses, which belong to the range of the reduced logical addresses, without restriction.

FIG. 12 illustrates a recovery operation performed at the host device 20 and the storage device 100 according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 12, in step S1010, the controller 120 may receive a fixed faulty address recovery request. For example, the recovery decision module RDM may select a fixed faulty address recovery scheme and send the fixed faulty address recovery request to the controller 120 based on the selected fixed faulty address recovery scheme. The recovery module RM may perform fixed faulty address recovery based on the selected fixed faulty address recovery request.

In operation S1020, the recovery module RM may negate 100, the host device 20 may backup data stored in the 20 a portion of a storage area corresponding to a recovery range included in the fixed faulty address recovery request, in other words, a portion of a storage area including a storage area at which a fault occurs. For example, under control of the recovery module RM, the memory management module MMM may fix mapping between logical addresses and physical addresses corresponding to the recovery range and create a list of fixed logical address LBA corresponding to the recovery range.

> In operation S1030, the recovery module RM may report the list of the fixed logical addresses LBA to the host device **20** or internally manage the list of the fixed logical addresses LBA. The recovery completion module RCM may mark the reported logical address LBA as impossible to use. In an exemplary embodiment of the inventive concept, the list of the fixed logical address LBA may be managed by the storage device 100 or by both the storage device 100 and the host device 20.

> Fixed faulty address recovery may be completed through operation S1010 to operation S1030. Afterwards, the host device 20 may normally access the storage device 100.

> In operation S1040, the controller 120 may receive an access request from the host device 20. In operation S1050, the controller 120 may determine whether a logical address of the received access request is a fixed logical address. If the logical address of the received access request is not the fixed logical address, in operation S1060, the controller 120 may permit an access. If the logical address of the received access request corresponds to the fixed logical address, in operation S1070, the controller 120 may deny an access. For example, the controller 120 may send an error message to the host device 20.

> As described above, if the fixed faulty address recovery is performed, a range of logical addresses of the storage device 100 may not be reduced but maintained. Within the range of logical addresses, the storage device  $100\,\mathrm{may}$  deny an access to logical addresses at which a fault is generated and may permit write, read, and erase operations with respect to the remaining logical addresses without restriction.

FIG. 13 illustrates a recovery operation performed at the host device 20 and the storage device 100 according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 13, in step S1110, the controller 120 may receive a dynamic faulty address recovery request. For example, the recovery decision module RDM may select a dynamic faulty address recovery scheme and send the dynamic faulty address recovery request to the controller 120 based on the selected dynamic faulty address recovery

scheme. The recovery module RM may perform dynamic faulty address recovery based on the selected dynamic faulty address recovery request.

In operation S1120, the recovery module RM may negate a portion of a storage area corresponding to a recovery range 5 included in the dynamic faulty address recovery request, in other words, a portion of a storage area including a storage area at which a fault is generated. For example, under control of the recovery module RM, the memory management module MMM may release a mapping between logical addresses and physical addresses corresponding to the recovery range and mark the physical addresses in the recovery range as impossible to use.

In operation S1130, the recovery module RM may compute the remainder of the storage area other than the negated portion of the storage area to select a size threshold. For example, the size threshold may be a size of the remaining storage area. For example, the size threshold may be set to indicate a reserved area, in consideration of parameters of the storage device 100 such as performance and life cycle. 20 For example, a portion of the remaining storage area may be assigned to the reserved area. In the remaining storage area, a final storage area except for the reserved area may be set as the size threshold.

In operation S1140, the recovery module RM may report 25 the computed size threshold to the host device 20. The recovery completion module RCM may recognize the received size threshold as the maximum value of data capable of being stored in the storage device 100.

The dynamic faulty address recovery may be completed 30 through operation S1110 to operation S1140. Afterwards, the host device 20 may normally access the storage device 100.

In operation S1150, the controller 120 may receive an access request from the host device 20. In operation S1160, the controller 120 may determine whether the received 35 access request is a write request for a free logical address LBA. If the received access request is not the write request for the free logical address LBA, in operation S1170, the controller 120 may allow an access. For example, read and update operations, which do not affect a size of data stored 40 in the storage device 100, and an erase operation, which causes a decrease in a size of data stored in the storage device 100, may be permitted at the storage device 100 without restriction. If the received access request is the write request for the free logical address LBA, operation S1180 is 45 performed.

In operation S1180, the controller 120 determines whether the total size of data previously stored in the storage device 100 and write-requested data is greater than the size threshold. If the total size is not greater than the size threshold, in operation S1170, the controller 120 may permit a write operation. If the total size is greater than the size threshold, in operation S1190, the controller 120 may deny a write request. For example, the controller 120 may send an error message to the host device 20.

As described above, if the dynamic faulty address recovery is performed, a range of logical addresses of the storage device 100 may be not reduced but maintained. As long as the total capacity of data written in the storage device 100 is less than or equal to the size threshold, the storage device 60 100 may permit write, read, and erase operations with respect to logical addresses within a range of logical addresses without restriction.

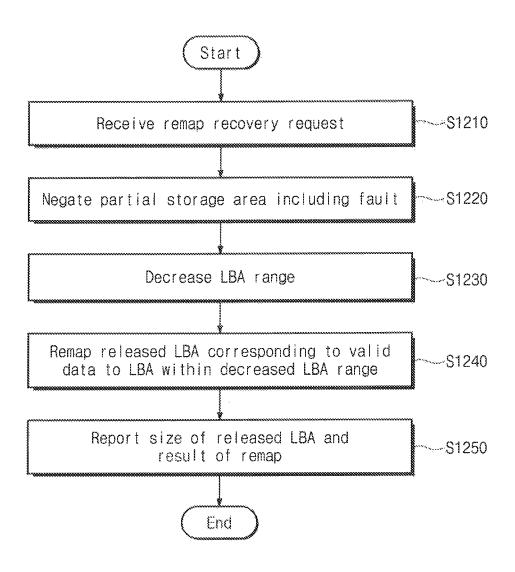

FIG. 14 illustrates a recovery operation performed at the host device 20 and the storage device 100 according to an 65 exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 14, in step S1210, the controller 120 may

18

receive a remap recovery request. For example, the recovery decision module RDM may select a remap recovery scheme and send the remap recovery request to the controller 120 based on the selected remap recovery scheme. The recovery module RM may perform remap recovery based on the remap recovery request.

In operation S1220, the recovery module RM may negate a portion of a storage area corresponding to a recovery range included in the remap recovery request, in other words, a portion of a storage area including a storage area at which a fault is generated. For example, under control of the recovery module RM, the memory management module MMM may release a mapping between logical addresses and physical addresses corresponding to the recovery range and mark the physical addresses in the recovery range as impossible to use.

In operation S1230, the memory management module MMM may reduce a range of logical addresses LBA under control of the recovery module RM. For example, the memory management module MMM may reduce a maximum value of the logical addresses LBA by a size of a portion of a storage area.

In operation S1240, under control of the recovery module RM, the memory management module MMM may remap the released logical address LBA corresponding to valid data to a logical address LBA within a range of the reduced logical addresses LBA. For example, as the range of logical addresses LBA is reduced, some of the logical addresses LBA may be released such that they are not used. Valid data may be stored at some of the released logical addresses LBA. The memory management module MMM may remap a corresponding logical address to a free logical address within the reduced range of logical addresses LBA. For example, the memory management module MMM may update logical addresses LBA in mapping information between physical addresses PBA and logical addresses LBA

In operation S1250, the recovery module RM may report a size of the released logical addresses LBA or the reduced range of logical addresses LBA to the host device 20. In addition, the recovery module RM may report the remapping result to the host device 20.

The recovery completion module RCM may change a range of logical addresses LBA in a file system of the storage device 100 and modify logical addresses of remapped data.

In an exemplary embodiment of the inventive concept, when a free logical address LBA to be remapped is insufficient, the recovery module RM may notify the host device 20 that a capacity is insufficient. The host device 20 may copy all or a part of data stored in the storage device 100 to the storage devices 30 and request the storage device 100 to continue recovery.

As described above, if the remap recovery is performed, a range of logical addresses of the storage device 100 may be reduced. Unlike the format recovery, data stored in the storage device 100 may be maintained.

In an exemplary embodiment of the inventive concept, the remapping of the reduced logical addresses LBA may be performed by the host device 20. When a fault is detected, the storage device 100 may notify the host device 20 that the fault is detected and inform the host device 20 that a capacity decreases according to a request (e.g., a recovery request) of the host device 20. The host device 20 may request information about the reduced range of logical addresses LBA from the storage device 100. The storage device 100 may send a range or list of faulty logical addresses LBA to the host device 20. The host device 20 may request the storage

device 100 to unmap logical addresses LBA included in the range or list of faulty logical addresses LBA. The host device 20 may recover data stored at the unmapped logical addresses LBA by using a separate data recovery scheme, such as RAID. The recovered data may be written in a 5 storage space within an updated range of logical addresses of the storage device 100, of which the capacity decreases, or in any other storage medium. In the case where data is previously written out of the updated range of logical addresses, the host device 20 may request the storage device 10 100 to remap a logical address of corresponding data within the updated range of logical addresses. Afterwards, the unmapping may be requested with respect to a logical address that leaves the updated range of logical addresses.

FIG. 15 illustrates a recovery operation completed at the 15 host device 20 and the storage device 100 according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 15, in step S1310, the controller 120 may register a current fault in a fault history. The controller 120 may report the updated fault history to the host device 20. 20 device 20 may complete the recovery operation.

In operation S1320, whether to adjust a fault condition may be determined based on the fault history. For example, the controller 120 may adjust the fault condition by itself or adjust the fault condition based on a request of the host device 20. For example, the fault condition may be adjusted 25 according to the number of times that a fault is generated. For example, a physical storage space of the nonvolatile memory device 110 may be divided into zones, and a fault condition of each zone may be adjusted according to the number of times that a fault is generated at each zone. For 30 example, the fault condition may be reinforced as the number of times that a fault is generated increases. For example, a threshold frequency of a program loop where a write fail is determined may decrease, a threshold frequency of an erase loop where an erase fail is determined may 35 decrease, or a threshold time when a read fail is determined may decrease.

In operation S1330, whether to adjust a detection policy may be determined based on the fault history. For example, the controller 120 may adjust the fault policy by itself or 40 adjust the fault policy based on a request of the host device 20. For example, the fault policy may be adjusted according to the number of times that a fault is generated. For example, a physical storage space of the nonvolatile memory device 110 may be divided into zones, and a fault policy of each 45 zone may be adjusted according to the number of times that a fault is generated at each zone. For example, the number of enabled fault policies may increase as the number of times that a fault is generated increases.

the computing device 10 of FIG. 1 according to an exemplary embodiment of the inventive concept. Referring to FIGS. 1 and 16, in operation S1410, the storage device 100, for example, the controller 120 may provide the host device 20 with available recovery schemes for recovering a fault. 55 For example, the capability check module CCM may provide the host device 20 with one or more recovery schemes. For example, the available recovery schemes may be sent at power-on or according to a request of the host device 20.

In operation S1420, the storage device 100, for example, 60 the controller 120 may detect a fault of the storage device 100, for example, a global fault.

In operation S1430, the storage device 100, for example, the controller 120 may notify the host device 20 of fault information. For example, the storage device 100 may 65 provide the host device 20 with each recovery scheme and a speed variation, a capacity variation, or a recovery time of

20 the storage device 100 according to each recovery scheme together with the fault information.